(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4403597号

(P4403597)

(45) 発行日 平成22年1月27日(2010.1.27)

(24) 登録日 平成21年11月13日(2009.11.13)

(51) Int.Cl.

F 1

B 41 J 2/16 (2006.01)

B 41 J 3/04 103H

B 41 J 2/045 (2006.01)

B 41 J 3/04 103A

B 41 J 2/055 (2006.01)

請求項の数 5 (全 11 頁)

(21) 出願番号

特願平11-100815

(22) 出願日

平成11年4月8日(1999.4.8)

(65) 公開番号

特開2000-289204 (P2000-289204A)

(43) 公開日

平成12年10月17日(2000.10.17)

審査請求日

平成17年11月28日(2005.11.28)

(73) 特許権者 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100083116

弁理士 松浦 憲三

(72) 発明者 栗原 和明

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 朽綱 道徳

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 西沢 元亨

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】 インクジェットヘッドの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

1枚の方形の基板に複数のインク噴出用ノズル、前記複数のインク噴出用ノズルに対応する複数の個別インク流路、前記複数の個別インク流路に対応する複数のインク供給路、及び前記インク供給路を介して前記複数の個別インク流路のそれぞれに対してインクを供給する共通インク室となる形状をパターンニングする工程と、

前記複数の個別インク流路、前記複数のインク供給路、及び共通インク室となる形状に犠牲層を埋め込む工程と、

前記犠牲層が埋め込まれた前記基板に振動板を形成する工程と、

前記振動板に圧電体膜を成膜した後に、前記個別インク流路に対応する形状にパターンニングして、前記複数の個別インク流路のそれぞれに対応する複数の圧電アクチュエータを形成する工程と、10

前記圧電アクチュエータを形成する工程の次に、前記圧電アクチュエータに上部電極となる金属膜を成膜する工程と、

前記金属膜を成膜する工程の次に、前記振動板上に成膜によって薄膜トランジスタ回路を形成する工程と、

前記上部電極が成膜された後の前記基板に保護膜を成膜する工程と、

前記保護膜が成膜された後の前記基板に、前記上部電極及び前記薄膜トランジスタ回路に接続される配線を形成するとともに、前記圧電アクチュエータの上部電極に接続される配線となる配線層を形成し、前記配線層を所定のパターンにパターンニングする工程と、20

残存する犠牲層を除去する工程と、

を含み、

前記薄膜トランジスタ回路を形成する工程は、前記圧電アクチュエータを駆動する駆動回路を形成する工程、及び前記複数のインク噴出ノズルに対応する複数の圧電アクチュエータの中からいずれかを選択するための駆動ノズル選択回路を形成する工程を含むことを特徴とするインクジェットヘッドの製造方法。

**【請求項 2】**

前記上部電極に接続される配線を形成する工程は、前記保護膜を貫通するように前記配線層と導通するピアを形成した後に、前記ピアと前記圧電アクチュエータの上部電極を導通させる圧電アクチュエータ用配線を形成する工程を含むことを特徴とする請求項1記載のインクジェットヘッドの製造方法。 10

**【請求項 3】**

前記基板は、感光ガラス基板であることを特徴とする請求項1又は2記載のインクジェットヘッドの製造方法。

**【請求項 4】**

前記基板を切断して個別のヘッドとした後に、インク導入接続口及び配線部材を接続してヘッドセグメントとする工程を含むことを特徴とする請求項1乃至3のいずれかに記載のインクジェットヘッドの製造方法。

**【請求項 5】**

前記ヘッドセグメントを前記インク噴出用ノズルが順次ずれるように位置合わせをして接着し、一体化したインクジェットヘッドとする工程を含むことを特徴とする請求項4記載のインクジェットヘッドの製造方法。 20

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明はインクジェットヘッド及びインクジェットプリンタに関するものであり、特に、インク噴出駆動源を駆動する駆動用の薄膜トランジスタ回路を積み重ねプロセスによって基板上に設けた点に特徴のあるインクジェットヘッド及びインクジェットプリンタに関するものである。 30

**【0002】**

**【従来の技術】**

従来、パーソナルコンピュータ等の情報機器端末としてのプリンタ装置として、ワイヤを磁気駆動し、インクリボン及び記録媒体としての用紙を介してプラテンに押圧することによって印字を行うワイヤ駆動型の記録ヘッドを用いたプリンタ装置や、インクをノズルから噴射するインクジェット型の記録ヘッドを用いたプリンタ等が用いられているが、印字に伴う騒音の発生しないインクジェット型プリンタ装置がオフィス内での使用に適していると注目されている。

**【0003】**

この様なインクジェット型プリンタ装置としては、インクを加熱素子によって瞬間加熱、気化させて気泡を発生させ、その圧力でインクをノズルから飛翔させるバブルジェット方式と、インクを圧電素子の変形を利用し、その変形力でノズルから飛翔させるピエゾ方式があり、これらのプリンタは、インク粒子を噴出させる発熱素子や圧電素子を駆動する電子回路、即ち、ドライバとしてシリコン半導体を用いている。 40

**【0004】**

従来、ピエゾ方式の場合、ドライバを印字ヘッドと別部品としてケーブルにより接続したり、或いは、印字ヘッド上に実装している。

また、バブルジェット方式の場合には、シリコン基板にドライバとなる電子回路を形成し、このドライバを形成したシリコン基板を印字ヘッドの基板とし、その上に発熱素子やノズル等を形成していた。

**【0005】**

10

20

30

40

50

この様な従来のインクジェット型の記録ヘッドは、ノズル、インク流路、インク供給系、インクタンク、発熱素子或いは圧電素子等のインク噴出駆動源等を備え、インク噴出駆動源で発生した発熱或いは変位・圧力をインク流路に伝達することによって、ノズルからインク粒子を噴出させ、紙等の記録媒体の上に文字や画像を記録するものである。

【0006】

【発明が解決しようとする課題】

しかしながら、ドライバを別部品とする方法は、配線が長くなったり、或いは、配線の取り回しが困難になる等の実装上の問題があり、全体が複雑化して高コストになるほか、高ノズル密度の実現が難しいという問題がある。

【0007】

また、ドライバをシリコン基板に形成する方法は、シリコンウェハの大きさが最大でも15インチ(38cm)で、しかも円形であるため、ある程度の長さが必要なラインヘッドでは製造効率が悪く、さらに、現状では、A4サイズが長さの限界であった。

10

【0008】

したがって、本発明は、ヘッドサイズに制限のない、ドライバ一体型インクジェットヘッドを提供することを目的とする。

【0009】

【課題を解決するための手段】

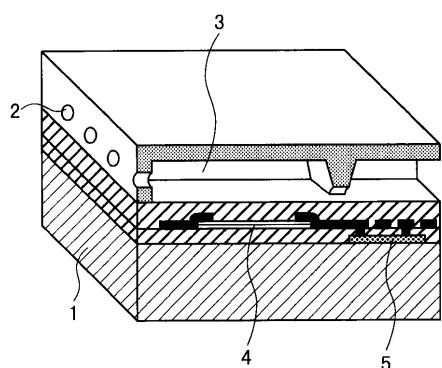

図1は本発明の原理的構成の説明図であり、この図1を参照して本発明における課題を解決するための手段を説明する。なお、図1は、バブルジェット方式ラインヘッドの要部断面斜視図である。

20

本発明は、インクジェットヘッドの製造方法において、1枚の方形の基板に複数のインク噴出用ノズル、前記複数のインク噴出用ノズルに対応する複数の個別インク流路、前記複数の個別インク流路に対応する複数のインク供給路、及び前記インク供給路を介して前記複数の個別インク流路のそれぞれに対してインクを供給する共通インク室となる形状をパターンニングする工程と、前記複数の個別インク流路、前記複数のインク供給路、及び共通インク室となる形状に犠牲層を埋め込む工程と、前記犠牲層が埋め込まれた前記基板に振動板を形成する工程と、前記振動板に圧電体膜を成膜した後に、前記個別インク流路に対応する形状にパターンニングして、前記複数の個別インク流路のそれぞれに対応する複数の圧電アクチュエータを形成する工程と、前記圧電アクチュエータを形成する工程の次に、前記圧電アクチュエータに上部電極となる金属膜を成膜する工程と、前記金属膜を成膜する工程の次に、前記振動板上に成膜によって薄膜トランジスタ回路を形成する工程と、前記上部電極が成膜された後の前記基板に保護膜を成膜する工程と、前記保護膜が成膜された後の前記基板に、前記上部電極及び前記薄膜トランジスタ回路に接続される配線を形成するとともに、前記圧電アクチュエータの上部電極に接続される配線となる配線層を形成し、前記配線層を所定のパターンにパターンニングする工程と、残存する犠牲層を除去する工程と、を含み、前記薄膜トランジスタ回路を形成する工程は、前記圧電アクチュエータを駆動する駆動回路を形成する工程、及び前記複数のインク噴出ノズルに対応する複数の圧電アクチュエータの中からいずれかを選択するための駆動ノズル選択回路を形成する工程を含むことを特徴とする。また、本発明の一態様に係るインクジェットヘッドの製造方法は、前記上部電極に接続される配線を形成する工程は、前記保護膜を貫通するように前記配線層と導通するビアを形成した後に、前記ビアと前記圧電アクチュエータの上部電極を導通させる圧電アクチュエータ用配線を形成する工程を含むことを特徴とする。前記基板は、感光ガラス基板である態様が好ましい。また、前記基板を切断して個別のヘッドとした後に、インク導入接続口及び配線部材を接続してヘッドセグメントとする工程を含むこと態様も好ましい。さらに、前記ヘッドセグメントを前記インク噴出用ノズルが順次ずれるように位置合わせをして接着し、一体化したインクジェットヘッドとする工程を含む態様も好ましい。

30

【0010】

この様に、複数のインク噴出用ノズル2、インク噴出用ノズル2に接続する個別インク

40

50

流路、インク噴出駆動源4を配置した基板1上に、積み重ねプロセスで形成した薄膜トランジスタ回路5を設けることによって、ドライバとなる薄膜トランジスタ回路5を別部品ではなく、基板1と一緒に形成することができ、それによって、低コスト化、高ノズル密度化が可能になる。また、ドライバとして薄膜トランジスタ回路5を用いているので、基板1は、単結晶シリコン基板である必要はなく、ガラス等の方形の基板1を用いることによってヘッドサイズに制限がなくなるとともに、製造効率も向上する。また、薄膜トランジスタ回路5として、単結晶シリコンではなく、アモルファスシリコン、多結晶シリコン、或いは、微結晶シリコン等の非単結晶シリコンで構成することにより、ガラス等の基板との一体化が可能になる。

**【0011】**

10

前記インク噴出駆動源が、抵抗加熱源または圧電アクチュエータのいずれかである態様が好ましい。

**【0012】**

この様に、薄膜トランジスタ回路5を一体化したドライバ一体型ヘッドは、インク噴出駆動源4として抵抗加熱源を用いたバブルジェット方式インクジェットヘッド及びインク噴出駆動源4として圧電アクチュエータを用いたピエゾ方式インクジェットヘッドに適用されるものである。

**【0013】**

(3) また、本発明は、上記(1)または(2)において、薄膜トランジスタ回路5が、インク噴出駆動源4を駆動する駆動回路及び駆動ノズル選択回路の少なくとも一方を含んでいることを特徴とする。

20

**【0014】**

この様に、基板1に一体化する薄膜トランジスタ回路5には、少なくともインク噴出駆動源4を駆動する駆動回路及び駆動ノズル選択回路の一方を含んでいれば良い。

**【0015】**

前記基板は、単結晶シリコン基板及びガラス基板のうち少なくとも何れか一方を含む態様が好ましい。

**【0016】**

30

この様に、半導体製造プロセスを用いて、薄膜トランジスタ回路等を構成しているので、別部品の実装工程或いは配線工程が不要になり、製造工程が簡素化され、且つ、高ノズル密度化が可能になる。

**【0017】**

(5) また、本発明は、インクジェットプリンタにおいて、上記(1)乃至(4)のいずれかのインクジェットヘッドを搭載したことを特徴とする。

**【0018】****【発明の実施の形態】**

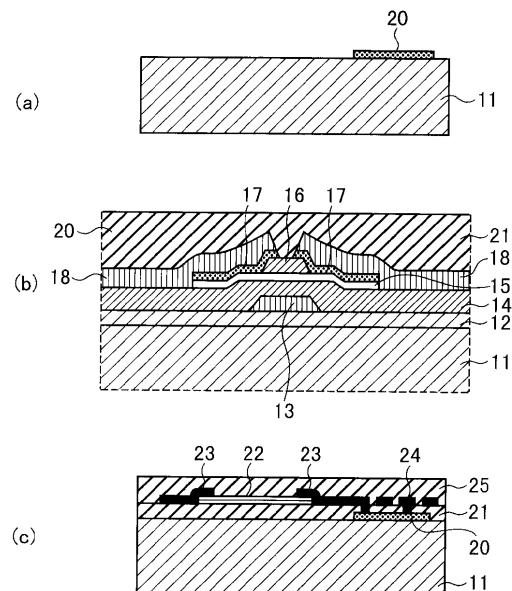

ここで、図2及び図3を参照して、本発明の第1の実施の形態のバブルジェット方式ラインヘッドの製造工程を説明する。

なお、このバブルジェット方式ラインヘッドの仕様としては、印字幅200mm、ノズルピッチ2,400dpi(1,200dpi×2列/色)，インク流量2plである。

40

図2(a)参照

まず、250×250×2mmの正方形形状のソーダガラス基板11上に、TFT駆動液晶表示装置と同様の方法でTFT回路20を形成する。

**【0019】**

図2(b)参照

図2(b)は、図2(a)におけるTFT回路20の拡大断面図であり、例えば、厚さが300nmの下地SiO<sub>2</sub>膜12をPCVD法(プラズマCVD法)によって堆積させたのち、スピッタ法によって厚さが150nmのTa膜を堆積させ、所定の形状にパターニングすることによってTaゲート電極13及びゲートバスラインを形成し、次いで、PCVD法を用いて、例えば、厚さが400nmのSiN膜を堆積させてSiNゲート絶縁膜

50

14を形成する。

**【0020】**

次いで、P C V D法を用いて、例えば、厚さが15nmのアンドープの-Si膜15、厚さが120nmのSiN膜を順次堆積させたのち、Taゲート電極13をマスクとしたセルファーライン露光を行うことによってSiN膜を所定形状にパターニングしてチャネル保護膜16を形成し、再び、P C V D法を用いて、例えば、厚さが30nmのn<sup>+</sup>型-Si膜17を堆積させたのち、反応性イオンエッチングを施すことによって、n<sup>+</sup>型-Si膜17及び-Si膜15を一個のTFTを形成するようにパターニングする。

**【0021】**

次いで、全面に、例えば、厚さが150nmのTa膜をスパッタ法によって堆積させたのち、n<sup>+</sup>型-Si膜17も含めてパターニングしてソース・ドレイン電極18を形成することによってTFT回路20の基本構成が完成し、最後に、ソーダガラス基板11の全面にSiON保護膜21を設ける。

**【0022】**

図2(c)参照

次いで、例えば、厚さが、200nmの耐久性のあるTiN膜を堆積させたのち、個別のインク流路に対応するようにパターニングすることによってTiN発熱層パターン22を形成する。

次いで、SiON保護膜21にTFT回路20に達するビアホールを形成したのち、A1膜を全面に堆積させ、パターニングすることによってA1ヒータ用配線層23及びA1配線層24を形成し、次いで、再び、全面に、例えば、厚さが、500nm SiON保護膜25を設ける。

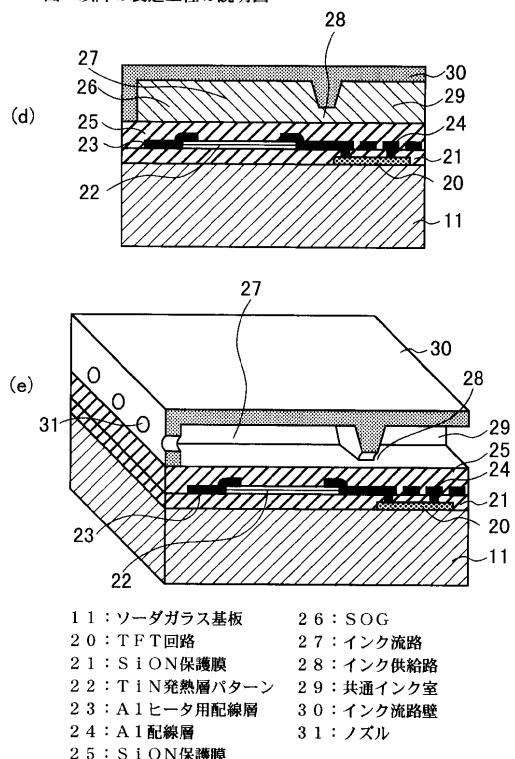

**【0023】**

図3(d)参照

次いで、全面にSOG(スピノングラス)26を堆積させたのち、残存部がインク流路27、インク供給路28、及び、共通インク室29を形成するようにパターニングし、インクと反応せず且つ硬いCrをメッキすることによりインク流路壁30を形成する。

**【0024】**

図3(e)参照

図3(e)は、要部断面斜視図であり、エキシマレーザを照射して複数カ所にノズル31を形成したのち、ノズル31等を介して残存するSOG26をエッチング除去する。

以降は図示しないものの、ソーダガラス基板を切断して個別のヘッドとしたのち、インク導入接続口及びフレキシブルケーブルを接続してヘッドセグメントとする。

この様なヘッドセグメントを、紙送り機構、インクタンク、ヘッドクリーニング・ページ機構を有するプリンタ装置に取り付けることによって、バブルジェット方式のインクジェットプリンタが完成する。

**【0025】**

この様に、本発明の第1の実施の形態においては、基板として、方形のソーダガラス基板11を用いているので、任意の大きさの基板を使用することができ、ヘッドサイズに制限のないドライバ一体型ヘッドを効率良く製造することができる。

**【0026】**

また、本発明は、Crからなるインク流路壁30をSOGの塗布及びパターニングという半導体技術を用いて形成しているので、インク流路壁部材の実装等の作業・位置合わせが不要となり、且つ、TiN発熱層パターン22を駆動するためのA1ヒータ用配線層23も半導体技術を用いて形成しているのでフレキシブルケーブルとの接続等の作業が不要になるので、製造工程が簡素化され、且つ、高ノズル密度化が可能になる。

**【0027】**

なお、上記の第1の実施の形態の説明においては、発熱層としてTiN膜を用いているが、TiN膜の代わりにSiC膜を用いても良いものであり、また、インク流路壁30をCrによって形成している、Crの代わりにNiを用いても良いものである。

10

20

30

40

50

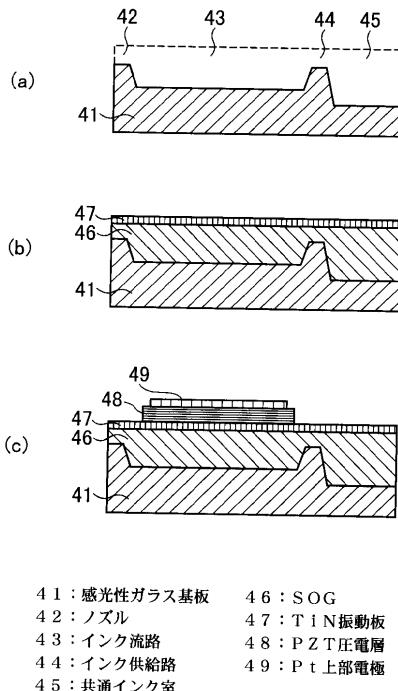

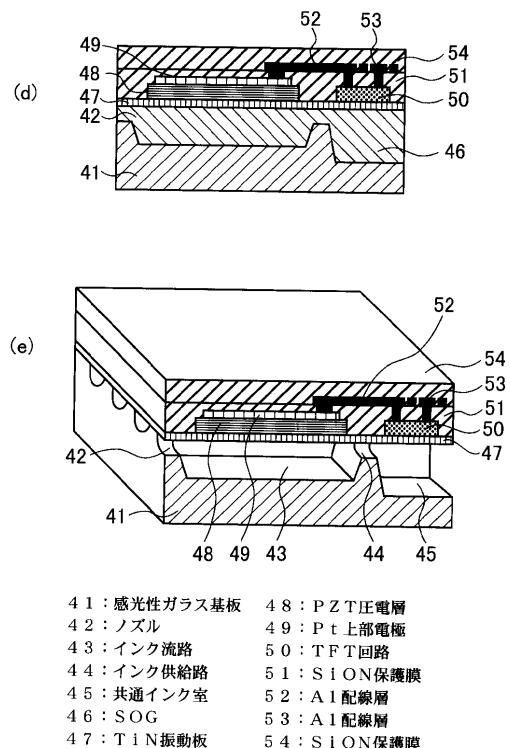

## 【0028】

次に、図4及び図5を参照して、本発明の第2の実施の形態のピエゾ方式ラインヘッドの製造工程を説明する。

なお、このバブルジェット方式ラインヘッドの仕様としては、印字幅300mm(A3対応)、ノズルピッチ2,400dpi(600dpi×4列/色)，インク流量2plである。

## 図4(a)参照

まず、 $350 \times 350 \times 2$ mmの正方形の感光性ガラス基板41に、ノズル42、インク流路43、インク供給路44、及び、共通インク室45を形成するパターンに露光を行って、露光箇所を結晶化し、結晶化領域をエッチング除去することによって、ノズル42、インク流路43、インク供給路44、及び、共通インク室45を形成する。

なお、各領域を異なった深さに形成するために、露光量を調整すれば良い。

## 【0029】

## 図4(b)参照

次いで、ディップコートによって感光性ガラス基板41に形成したノズル42、インク流路43、インク供給路44、及び、共通インク室45をSOG46で埋め込んだ後、CMP(Chemical Mechanical Polishing)法を用いて表面を平坦化する。

次いで、スパッタ法を用いて、平坦化したSOG46上に、厚さが、0.1~10μm、例えば、1.0μmの硬いTiN膜を堆積させて、TiN振動板47を形成する。

## 【0030】

## 図4(c)参照

次いで、ECRスパッタ法によって、全面に、厚さが、0.2~20μm、例えば、1.0μmのPZT(PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>)膜を堆積させ、個別のインク流路43に対応する形状にパターニングすることによって、PZT圧電層48を形成し、次いで、マスクを用いたマスクスパッタ法によって厚さが、例えば、100nmのPt上部電極49を形成する。

## 【0031】

## 図5(d)参照

次いで、図2(b)に示した形成方法と同様な方法で、TiN振動板47上にTFT回路50を形成する。

即ち、TiN振動板47上に、例えば、厚さが100nmの下地SiO<sub>2</sub>膜をPCVD法によって堆積させたのち、スパッタ法によって厚さが150nmのTa膜を堆積させ、所定の形状にパターニングすることによってTaゲート電極及びゲートバスラインを形成し、次いで、PCVD法を用いて、例えば、厚さが400nmのSiN膜を堆積させてSiNゲート絶縁膜を形成する。

次いで、PCVD法を用いて、例えば、厚さが15nmのアンドープの-Si膜、厚さが120nmのSiN膜を順次堆積させたのち、Taゲート電極をマスクとしたセルファライン露光を行うことによってSiN膜を所定形状にパターニングしてチャネル保護膜を形成し、再び、PCVD法を用いて、例えば、厚さが30nmのn<sup>+</sup>型-Si膜17を堆積させたのち、反応性イオンエッティングを施すことによって、n<sup>+</sup>型-Si膜及び-Si膜を一個のTFTを形成するようにパターニングする。

次いで、全面に、例えば、厚さが150nmのTa膜をスパッタ法によって堆積させたのち、n<sup>+</sup>型-Si膜も含めてパターニングしてソース・ドレイン電極を形成することによってTFT回路50を形成する。

## 【0032】

次いで、全面に、例えば、厚さが、100nm SiON保護膜51を設け、Pt上部電極49及びTFT回路50の達するビアホールを形成したのち、Al膜を全面に堆積させ、パターニングすることによってAl配線層52及びAl配線層53を形成し、次いで、再び、全面に、例えば、厚さが、100nm SiON保護膜54を設ける。

## 【0033】

図5(e)参照

図5(e)は、要部断面斜視図であり、ノズル42等を介して残存するSOG46をエッティング除去する。

以降は図示しないものの、感光性ガラス基板41を切断して個別のヘッドとしたのち、インク導入接続口及びフレキシブルケーブルを接続してヘッドセグメントとする。

この様なヘッドセグメントをマゼンタ、イエロー、シアンの各色毎に4個ずつ、ノズル42の位置が順次ずれるように位置合わせし、接着、一体化することによってカラー印字ヘッドとし、このカラー印字ヘッドを、紙送り機構、インクタンク、ヘッドクリーニング・バージ機構を有するプリンタ装置に取り付けることによって、ピエゾ方式のインクジェットプリンタが完成する。

## 【0034】

この様に、本発明の第2の実施の形態においては、基板として、方形の感光性ガラス基板41を用いているので、任意の大きさの基板を使用することができ、ヘッドサイズに制限のないドライバ一体型ヘッドを効率良く製造することができる。

## 【0035】

また、本発明は、感光性ガラス基板41に、堆積工程及びエッティング工程という半導体製造プロセスを用いて、インク流路等、振動板、圧電アクチュエータ、TFT回路を構成しているので、別部品の実装工程或いは配線工程が不要になり、製造工程が簡素化され、且つ、高ノズル密度化が可能になる。

10

## 【0036】

以上、本発明の各実施の形態を説明してきたが、本発明は各実施の形態における構成に限定されるものではなく、各種の変形が可能である。

例えば、上記の第1の実施の形態においては、基板としてソーダガラス基板を用いているが、ソーダガラス基板に限られるものではなく、ソーダガラスと同等若しくはそれ以上の耐熱性及び強度を有するものであれば良く、例えば、石英ガラスやパイレックスガラスを用いても良いものである。

20

## 【0037】

また、方形で、大口径の単結晶シリコン基板が安価に製造されるようになった場合には、基板として単結晶シリコン基板を用いても良いものであり、特に、上記の第2の実施の形態の様に、基板にインク流路等をエッティングで形成する場合に好適である。

30

## 【0038】

また、上記各実施の形態においては、TFT回路を-Siによって構成しているが、-Siに限られるものではなく、多結晶シリコン或いは微結晶シリコンを用いても良いものである。また、個々のTFTの形状も、ゲート電極を基板側に設ける構造に限られるものではなく、基板上に非単結晶シリコン層を堆積させ、その上にゲート絶縁膜を介してゲート電極を形成した構造のTFTを用いても良いものである。

## 【0039】

また、上記の各実施の形態においては、発熱層或いは圧電層を全面に堆積させたのちパターニングしているが、リフトオフ法やマスクスパッタ法等を用いて、最初から選択的に形成しても良いものである。

40

## 【0040】

また、上記の第2の実施の形態においては、圧電層となるPZTをECRスパッタ法で堆積させているが、MOCVD法を用いて堆積させても良いものであり、また、圧電材料はPZTに限られるものではなく、PZTと同系のNbを含むペロブスカイト酸化物を用いても良いものである。

## 【0041】

また、上記の第2の実施の形態においては、振動板として導電性のあるTiNを用いているので下部電極を省略しているが、振動板は絶縁体でも良いものであり、絶縁体で構成する場合には、圧電層を堆積させる前に下部電極を形成する必要がある。

50

## 【0042】

また、本発明は、ヘッドを固定または微小移動させるラインプリンタを前提にしているが、必ずしも、ラインプリンタに限られるものではなく、シャトルに搭載して駆動しながら印字を行うインクジェットプリンタにも適用されるものである。

## 【0043】

## 【発明の効果】

本発明によれば、基板として方形で且つ大面積の安価な基板を用いるとともに、インク噴出駆動源を駆動するドライバを薄膜トランジスタによって形成しているので、ドライバの一体化が可能になり、インクジェットラインプリンタの大型化、低コスト化が可能になり、それによって、インクジェットプリンタの小型化、軽量化を図ることができ、インクジェットプリンタの微細化、高速化に寄与するところが大きい。10

## 【図面の簡単な説明】

【図1】本発明の原理的構成の説明図である。

【図2】本発明の第1の実施の形態のバブル方式ラインヘッドの途中までの製造工程の説明図である。

【図3】本発明の第1の実施の形態のバブル方式ラインヘッドの図2以降の製造工程の説明図である。

【図4】本発明の第2の実施の形態のピエゾ方式ラインヘッドの途中までの製造工程の説明図である。

【図5】本発明の第2の実施の形態のピエゾ方式ラインヘッドの図4以降の製造工程の説明図である。20

## 【符号の説明】

- |     |                         |                                       |

|-----|-------------------------|---------------------------------------|

| 1   | 基板                      |                                       |

| 2   | インク噴出用ノズル               |                                       |

| 3   | 個別インク流路                 |                                       |

| 4   | インク噴出駆動源                |                                       |

| 5   | 薄膜トランジスタ回路              |                                       |

| 1 1 | ソーダガラス基板                |                                       |

| 1 2 | 下地 SiO <sub>2</sub> 膜   |                                       |

| 1 3 | T a ゲート電極               | <span style="float: right;">30</span> |

| 1 4 | SiN ゲート絶縁膜              |                                       |

| 1 5 | - Si 膜                  |                                       |

| 1 6 | チャネル保護膜                 |                                       |

| 1 7 | n <sup>+</sup> 型 - Si 膜 |                                       |

| 1 8 | ソース・ドレイン電極              |                                       |

| 2 0 | TFT回路                   |                                       |

| 2 1 | SiON 保護膜                |                                       |

| 2 2 | TiN 発熱層パターン             |                                       |

| 2 3 | Al ヒータ用配線層              |                                       |

| 2 4 | Al 配線層                  | <span style="float: right;">40</span> |

| 2 5 | SiON 保護膜                |                                       |

| 2 6 | SOG                     |                                       |

| 2 7 | インク流路                   |                                       |

| 2 8 | インク供給路                  |                                       |

| 2 9 | 共通インク室                  |                                       |

| 3 0 | インク流路壁                  |                                       |

| 3 1 | ノズル                     |                                       |

| 4 1 | 感光性ガラス基板                |                                       |

| 4 2 | ノズル                     |                                       |

| 4 3 | インク流路                   | <span style="float: right;">50</span> |

- 4 4 インク供給路

4 5 共通インク室

4 6 S O G

4 7 T i N 振動板

4 8 P Z T 压電層

4 9 P t 上部電極

5 0 T F T 回路

5 1 S i O N 保護膜

5 2 A l 配線層

5 3 A l 配線層

5 4 S i O N 保護膜

10

【図1】

本発明の原理的構成の説明図

- 1 : 基板

2 : インク噴出用ノズル

3 : 個別インク流路

4 : インク噴出駆動源

5 : 薄膜トランジスタ回路

【図2】

本発明の第1の実施の形態のバブル方式ラインヘッドの途中までの製造工程の説明図

- |                                |                     |

|--------------------------------|---------------------|

| 1 1 : ソーダガラス基板                 | 1 8 : ソース・ドレイン電極    |

| 1 2 : 下地 S i O <sub>2</sub> 膜  | 2 0 : T F T 回路      |

| 1 3 : T a ゲート電極                | 2 1 : S i O N 保護膜   |

| 1 4 : S i N ゲート絶縁膜             | 2 2 : T i N 発熱層バターン |

| 1 5 : α-S i 膜                  | 2 3 : A l ヒータ用配線層   |

| 1 6 : チャネル保護膜                  | 2 4 : A l 配線層       |

| 1 7 : n <sup>+</sup> 型 α-S i 膜 | 2 5 : S i O N 保護膜   |

【図3】

本発明の第1の実施の形態のバブル方式ラインヘッドの

図2以降の製造工程の説明図

【図4】

本発明の第2の実施の形態のピエゾ方式ラインヘッドの

途中までの製造工程の説明図

【図5】

本発明の第2の実施の形態のピエゾ方式ラインヘッドの

図4以降の製造工程の説明図

---

フロントページの続き

(72)発明者 谷口 修

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 門 良成

(56)参考文献 特開平10-337868(JP,A)

特開平09-156103(JP,A)

(58)調査した分野(Int.Cl., DB名)

B41J 2/16

B41J 2/045

B41J 2/055