(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2013/046160 A1

(43) International Publication Date

4 April 2013 (04.04.2013)

(51) International Patent Classification:

*H02M 1/15* (2006.01)    *H05B 33/08* (2006.01)

(21) International Application Number:

PCT/IB2012/055180

(22) International Filing Date:

28 September 2012 (28.09.2012)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/541,343 30 September 2011 (30.09.2011) US

(71) Applicant (for all designated States except DE):

**KONINKLIJKE PHILIPS ELECTRONICS N.V.**

[NL/NL]; High Tech Campus 5, NL-5656 AE Eindhoven (NL).

(71) Applicant (for DE only): **PHILIPS INTELLECTUAL PROPERTY & STANDARDS GMBH** [DE/DE];

Lübecktordamm 5, 20099 Hamburg (DE).

(72) Inventors: **ELFERICH, Reinhold**; c/o High Tech Campus, Building 44, NL-5656AE Eindhoven (NL). **LOPEZ, Toni**; c/o High Tech Campus, Building 44, NL-5656AE Eindhoven (NL).

(74) Agents: **VAN EEUWIJK, Alexander Henricus Walterus** et al.; High Tech Campus Building 44, NL-5656 AE Eindhoven (NL).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: ACTIVE CAPACITOR CIRCUIT

FIG. 2

(57) Abstract: The present invention relates to an active capacitor circuit (40) for use in a driver device for driving a load (22), in particular an LED unit comprising one or more LEDs (23). Further, the present invention relates to a driver device comprising such an active capacitor circuit. The proposed active capacitor circuit comprises coupling terminals (41, 42) for providing a drive voltage (vD) and/or drive current (iD) for driving a load (22) to be coupled between said coupling terminals (41, 42), an output power stage (50) coupled between said coupling terminals (41, 42) for converting said periodic current (iA) into said drive current (iD), a low frequency capacitor (46) coupled between a capacitor output terminal (48) of said output power stage (50) and a coupling terminal (42), and a control unit (60) for controlling said output power stage (50) by use of a control signal (Sd) obtained from a feedback of the drive voltage (vD), a capacitor voltage (vC) across said low frequency capacitor (46) and/or a capacitor current (iC) through said low frequency capacitor (46).

WO 2013/046160 A1

## Active Capacitor Circuit

### FIELD OF THE INVENTION

The present invention relates to an active capacitor circuit for use in a driver device for driving a load, in particular an LED unit comprising one or more LEDs. The present invention relates further to a driver device for driving a load. Still further, the present 5 invention relates to a light apparatus.

### BACKGROUND OF THE INVENTION

In the field of LED drivers for offline applications such as retrofit lamps, solutions are demanded to cope with high efficiency, high power density, long lifetime, high 10 power factor and low cost, among other relevant features. While practically all existing solutions compromise one or the other requirement, it is essential that the proposed driver circuits properly condition the mains power into the form required by the LEDs while maintaining compliance with present and future power mains regulations. It is of critical importance to guarantee that the perceptible light flicker does not exceed a maximum value 15 (preferably zero) when the power factor is maintained above a certain limit.

Further, in off-line converters, energy from the power mains often needs to be drawn synchronously in proportion to the supplied voltage waveform in order to achieve a high power factor and low harmonic distortion. Power converter architectures with an independent preconditioner stage are traditionally employed to best accomplish this task 20 without compromising the proper form of the energy to be supplied to the load.

Typically, two series-connected power stages are employed to obtain a high power factor while keeping the output power constant throughout a mains cycle (or supply cycle, i.e. the cycle of the mains voltage or the supply voltage). In those architectures, the first stage shapes the mains current and the second stage performs the power conversion to 25 the load.

Nonetheless, for reasons related to complexity and cost, simplified powertrain solutions are adopted known conventionally as single-stage, where either of the two stages may essentially not be incorporated. As a consequence of such simplification, the aforementioned requirements may be largely compromised and/or converter performance 30 highly degraded, particularly in terms of size, reliability and lifetime. The latter is usually

mainly attributed to the need for using a bulky low frequency storage capacitor in parallel to the load when constant output power delivery is to be guaranteed.

Single stage solutions are common in literature. One reference example is given in the work of Robert Erickson and Michael Madigan, entitled “Design of a simple 5 high-power-factor rectifier based on the flyback converter”, IEEE Proceedings of the Applied Power Electronics Conferences and Expositions, 1990, pp. 792-801.

An intermediate solution, half-way between the two-stage and single-stage approaches, is the single-stage converter with integrated preconditioner. Such solutions can feature reduced component count and high power density while keeping compliance with 10 both load and power mains requirements. Other embodiments with a single power converting stage allow high power factors (HPF) by means of integrating a boost converter operating in discontinuous conduction mode. These converters actually combine the above mentioned two power conversion stages.

Typically, high power factor operation of driver devices for driving a load, 15 such as LED units comprising one or more LEDs, causes strong 100Hz output current ripple even if large filter capacitors are used. These filters are almost ineffective if employed parallel to LED loads with steep IV (current versus voltage) characteristics (also called “diode characteristics”). It is known from electric vehicles and photovoltaic systems that dc/dc-converters between load and capacitor improve the exploitation of (super-) capacitors.

20 Q. Hu and R. Zane, “A 0.9 PF LED Driver with Small LED Current Ripple Based on Series-input Digitally-controlled Converter”, Proceeding of the APEC 2010, pp.2314-2320 describe a two-stage LED driver using a bidirectional step down converter as second power stage, which connects the 120Hz capacitor to the LED load, which also is connected to the output of the first power stage.

25

## SUMMARY OF THE INVENTION

It is an object of the present invention to provide an active capacitor circuit for use in a driver device for driving a load, in particular an LED unit comprising one or more LEDs, which avoids the use of an ever larger electrolytic capacitor as is typically employed 30 in parallel with offline driven LED loads, and which leads to virtually no 100/120Hz-ripple/flicker (e.g. < 1%) even at the low dynamic resistance of modern power LEDs.

It is a further object of the present invention to provide a driver device for driving a load and a light apparatus.

In a first aspect of the present invention, an active capacitor circuit is presented that comprises

- coupling terminals for providing a drive voltage and/or drive current for driving a load to be coupled between said coupling terminals,

- 5 - an output power stage coupled between said coupling terminals for converting said periodic current into said drive current,

- a low frequency capacitor coupled between a capacitor output terminal of said output power stage and a coupling terminal, and

- a control unit for controlling said output power stage by use of a control signal obtained from a feedback of the drive voltage, a capacitor voltage across said low frequency capacitor and/or a capacitor current through said low frequency capacitor.

In a further aspect of the present invention, a driver device is presented comprising

- power input terminals for receiving a periodic supply voltage from an external power supply,

- an input converter stage coupled to said power input terminals for converting said periodic supply voltage into said drive voltage and for outputting an intermediate current at converter output terminals, and

- an active capacitor circuit according to the present invention coupled to said converter output terminals of said input converter stage.

In a still further aspect of the present invention, a light apparatus is presented comprising

- a light assembly comprising one or more light units, in particular an LED unit comprising one or more LEDs, and

- 25 - a proposed driver device for driving said light assembly.

Preferred embodiments of the invention are defined in the dependent claims. It shall be understood that the claimed driver device and the claimed light apparatus have similar and/or identical preferred embodiments as the claimed active capacitor circuit and as defined in the dependent claims.

30 The proposed active capacitor circuit represents a module that is coupled in parallel to the load (e.g. one or more LEDs or LED packages) or that is integrated into the load and to which a small capacitor is connected, which also could be integrated into the load. By contrast, in most prior art approaches the power stages are arranged in cascade.

Further, the proposed active capacitor circuit can be regarded as an independent, highly compact, high-order-low-pass filter element (i.e. effectively removing all AC components of a first stage from the load). In one embodiment, however, some bands of the spectrum may be passed, thus enabling some level of load modulation.

5 According to the driver disclosed by Q. Hu and R. Zane cited above, both first and second stages are in parallel with the load. The advantage of the proposed active capacitor circuit with respect to this prior art is that the proposed active capacitor circuit can operate stand-alone, i.e. like a passive filter circuit, but with significantly enhanced performance. Such operation facilitates modularity, integrability, and plug&play usage like 10 easy replacement of existing output filter circuits. Further, it requires neither a measurement of load current or other power stage current nor a signal connection to any power stage.

Preferably, one or more feedback loops, in particular two cascaded feedback loops, are provided according to the present invention for controlling said capacitor current and/or capacitor voltage. In particular, according to a preferred embodiment said control unit 15

comprises a first feedback loop for controlling said capacitor current to follow a reference capacitor current. Preferably, said control unit is configured to determine said reference capacitor current from said drive voltage by high-pass filtering said drive voltage and amplifying the high-pass filtered drive voltage by a drive voltage amplification factor. Still further, in an embodiment said control unit is configured to determine said drive voltage 20 amplification factor in dependence on the voltage drop of the dynamic resistance of said load to be coupled between said coupling terminals.

Assuming that the active capacitor circuit is used in a driver device for driving one or more LEDs, depending on LED technology (and also drive current) the LED can be considered to be composed of an ideal voltage source and a series resistance, the latter being 25 called dynamic resistance. To determine the drive voltage amplification factor in dependence on the voltage drop of the dynamic resistance of said load thus means that the control could be somehow adapted to the LED, either by a preset value (hard- or software) or automatically (adaptively) or not at all.

According to another embodiment, said control unit comprises a second 30 feedback loop for controlling said capacitor voltage to swing around a reference capacitor voltage. Preferably, said control unit is configured to determine said reference capacitor voltage in relation to the voltage rating of said low frequency capacitor.

In order to effectively filter most or all mains ripple, the capacitor is preferably capable of storing at least energy  $E_{capmin} > P_o / (2 \pi f_m)$ , wherein  $P_o$  is the output power and

fm the mains frequency. Such a capacitor, however, would lead to 100% ripple (ratio of peak to average voltage is 2). In order to cope with tolerances, aging, and also to relax component stress in the output power stage, the capacitor preferably shows a somewhat higher storage capability  $E_{capact}=N*E_{capmin}$ . This results in a peak to average voltage of about 5  $V_{pk}/V_{avg}=2/(1+\sqrt{1-1/N})$ . N=2, e.g. means  $V_{pk}/V_{avg}=1.2$ . Practical ratios preferably lie between 1.05 and 1.3.

Preferably, as mentioned briefly above, said first feedback loop and said second feedback loop are cascaded such that the first feedback loop forms an inner loop to derive an inner control signal and the second feedback loop forms an outer loop to derive an 10 outer control signal. Further, preferably said reference capacitor current is determined from said drive voltage by high-pass filtering said drive voltage, amplifying the high-pass filtered drive voltage by a drive voltage amplification factor, and subtracting said outer control signal from said amplified high-pass filtered drive voltage.

An advantage of cascading is that two control tasks can be dealt with 15 separately: controlling the load current to be constant and controlling the storage capacitor voltage to stay within predefined limits. An advantage of the first feedback loop (inner loop) is that by controlling the capacitor current, which is easily measurable within the output power stage, the load current becomes virtually constant in steady state operation. An advantage of the second feedback loop (outer loop) is that it can easily derive said reference 20 current by taking into account, firstly, a steady state current ripple of an input converter stage (via the high-pass filtered load voltage), secondly, the average capacitor voltage and, in doing so, is also capable of dealing with transients of the input converter stage current (e.g. turn on/off).

In an embodiment, said control unit is configured to add a modulation signal 25 to said reference capacitor current before using it in said first control loop for controlling said capacitor current. Preferably, said control unit is configured to determine said modulation signal from said drive voltage and/or said capacitor voltage. The modulation signal is generally an external signal that is e.g. used to send data via invisible light fluctuations. In order to avoid visible distortions, i.e. to make the light response equal to the modulation 30 signal, a feed forward transfer function for pre-compensation may be applied to the modulation signal, resulting in a modified modulation signal, which is injected into the reference current joint.

There are various implementations for the output power stage, mainly depending on the kind of application of the active capacitor circuit and the kind of load.

According to preferred embodiments, said output power stage comprises a bidirectional converter, in particular a bidirectional boost converter, bidirectional buck converter or a bidirectional buck-boost converter. For instance, in an implementation of the bidirectional converter as a bidirectional boost converter, it comprises an output inductor coupled between 5 a switching node of said bidirectional converter and a coupling terminal, and an output capacitor coupled between said coupling terminals.

Advantageously, said control unit is configured to control said bidirectional converter to operate in a quasi square-wave mode. This enables obtaining ZVS (zero voltage switching) and thus enables high switching frequencies (e.g. >1MHz) still at a high 10 efficiency.

In another embodiment, said control unit is configured to control said bidirectional converter to operate at a higher (preferably much higher) switching frequency than the input converter stage provided in preferred embodiments of the proposed driver device. This may allow completely skipping an output filter of the input converter stage.

15 The paper "Single Stage Isolated PFC with AC Line Ripple Steering", Bogdan Bucheru, Ionel Dan Jitaru, Delta Energy Systems, USA, PCIM Europe 2011, 17-19 May 2011, Nuremberg, Germany discloses a power architecture providing a solution for low frequency ripple steering. The proposed architecture, however, unlike the present invention, refers to a charger circuit with output voltage control (not current), and to a particular 20 combination of first and second stage, and uses a combined control of both stages. In particular the first stage controls the capacitor voltage of the second stage, which controls the output voltage of the first stage.

According to still another aspect of the present invention, a light apparatus is proposed comprising:

25 - power input terminals for receiving a periodic supply voltage from an external power supply,

- an input converter stage coupled to said power input terminals for converting said periodic supply voltage into said drive voltage and for outputting an intermediate current at converter output terminals,

30 - coupling terminals coupled to said converter output terminals of said input converter stage for providing a drive voltage and/or drive current for driving a load to be coupled between said coupling terminals,

- an output power stage coupled between said coupling terminals for converting said periodic current into said drive current,

- a low frequency capacitor coupled between a capacitor output terminal of said output power stage and a coupling terminal, and

- a control unit for controlling said output power stage by use of a control signal obtained from a feedback of the drive voltage, a capacitor voltage across said low frequency capacitor and/or a capacitor current through said low frequency capacitor, and

- a light assembly comprising one or more light units, in particular an LED unit comprising one or more LEDs, coupled to said coupling terminals.

Consequently, according to various embodiments of the light apparatus of the present invention, the control unit and/or the output power stage may be part of the active capacitor circuit or the light assembly.

According to still another aspect of the present invention, the input converter stage is not part of the light apparatus, i.e. the light apparatus which is proposed comprises:

- power input terminals for receiving a periodic supply voltage from an external power supply,

- coupling terminals coupled to said power input terminals for providing a drive voltage and/or drive current for driving a load to be coupled between said coupling terminals,

- an output power stage coupled between said coupling terminals for converting said periodic current into said drive current,

- a low frequency capacitor coupled between a capacitor output terminal of said output power stage and a coupling terminal, and

- a control unit for controlling said output power stage by use of a control signal obtained from a feedback of the drive voltage, a capacitor voltage across said low frequency capacitor and/or a capacitor current through said low frequency capacitor, and

- a light assembly comprising one or more light units, in particular an LED unit comprising one or more LEDs, coupled to said coupling terminals.

Consequently, according to various embodiments of the light apparatus of the present invention, the control unit and/or the output power stage may be part of the active capacitor circuit or the light assembly.

### 30 BRIEF DESCRIPTION OF THE DRAWINGS

These and other aspects of the invention will be apparent from and elucidated with reference to the embodiment(s) described hereinafter. In the following drawings

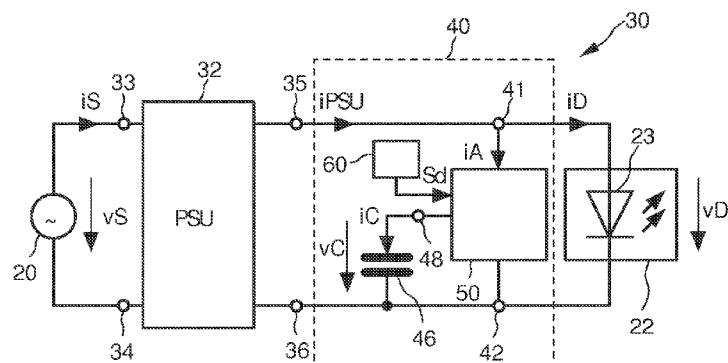

Fig. 1 shows a schematic diagram of a known driver device,

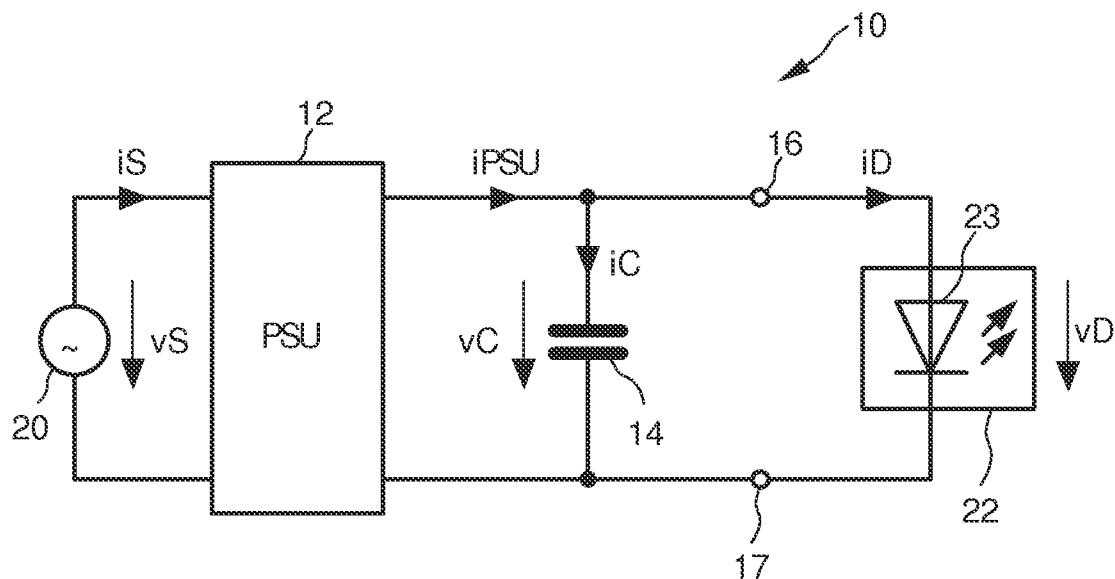

Fig. 2 shows a schematic diagram of a first embodiment of a proposed

driver device including an embodiment of a proposed active capacitor

circuit,

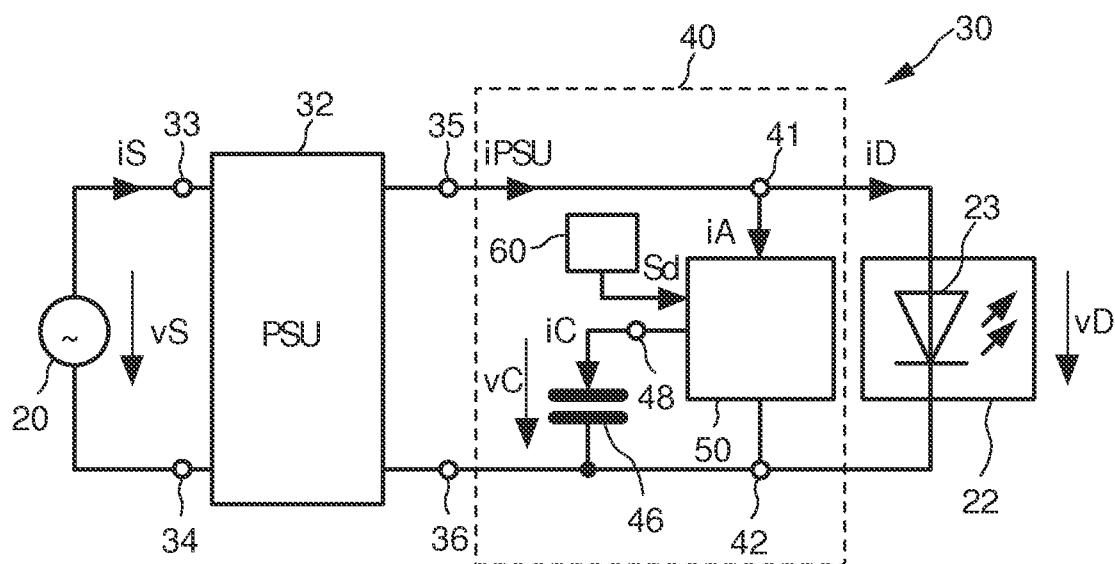

5 Fig. 3 shows a schematic diagram of a first embodiment of a proposed

driver device,

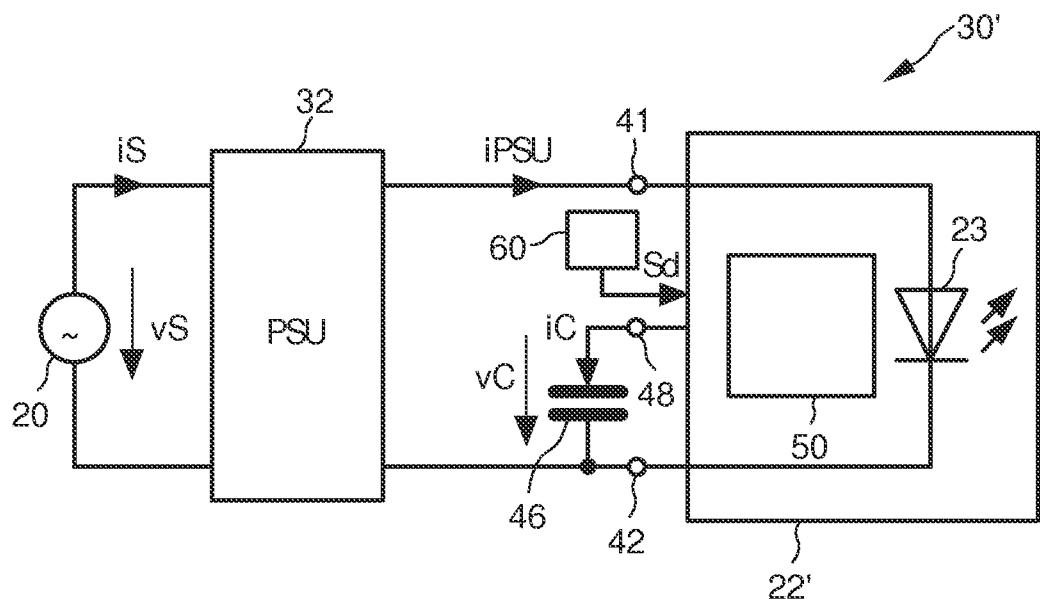

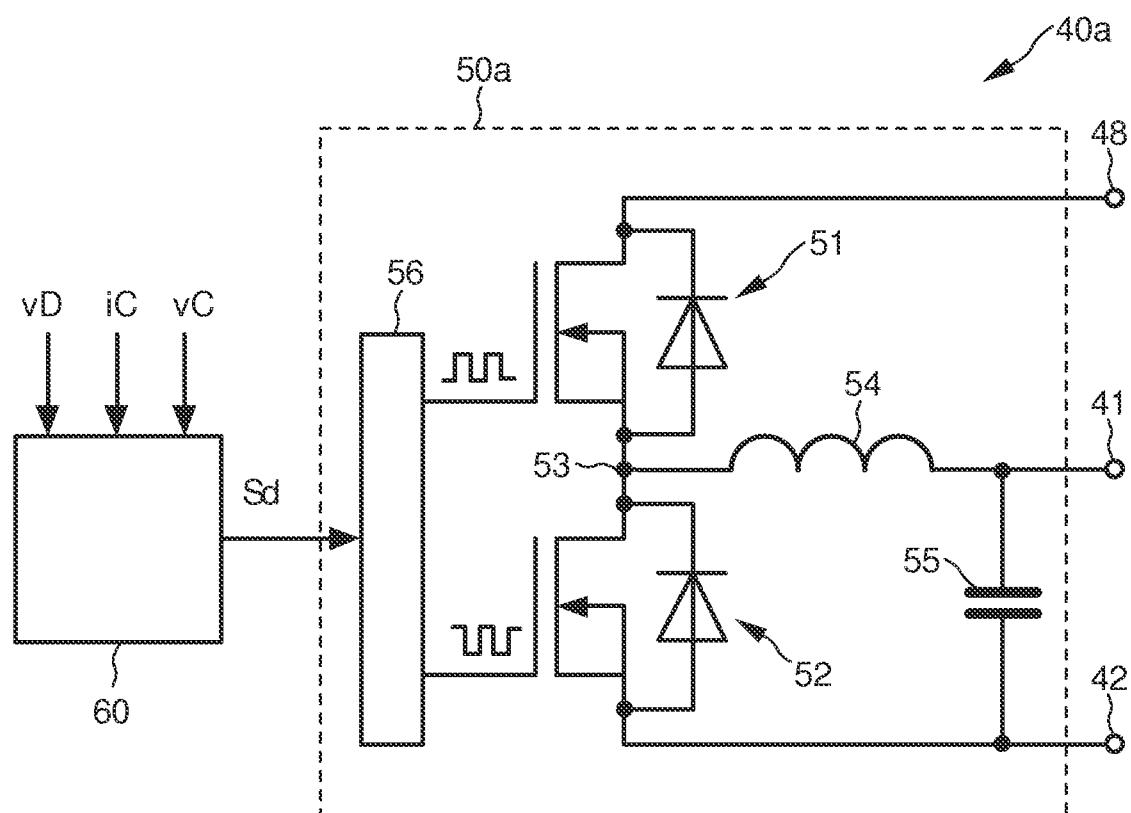

Fig. 4 shows a circuit diagram of an embodiment of a proposed active

capacitor circuit,

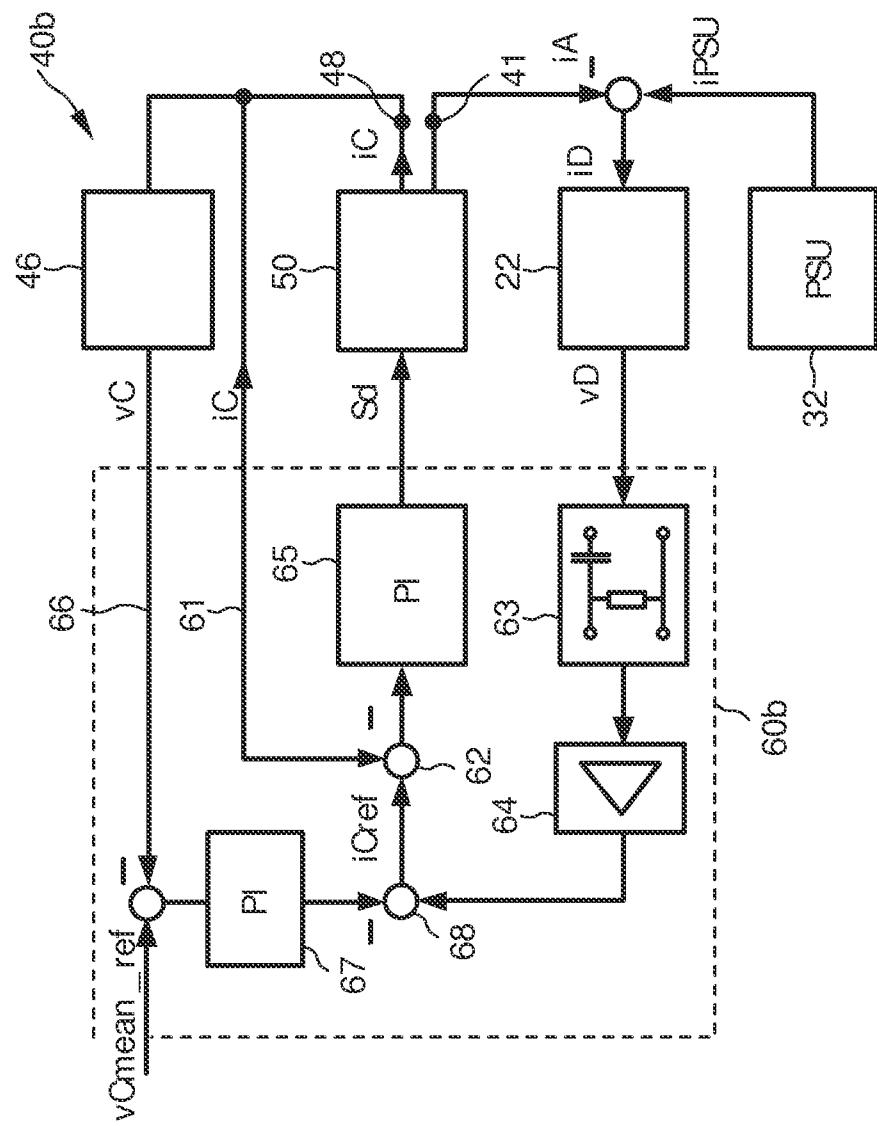

Fig. 5 shows a circuit diagram of another embodiment of a proposed active

10 capacitor circuit showing details of an embodiment of the proposed

control unit,

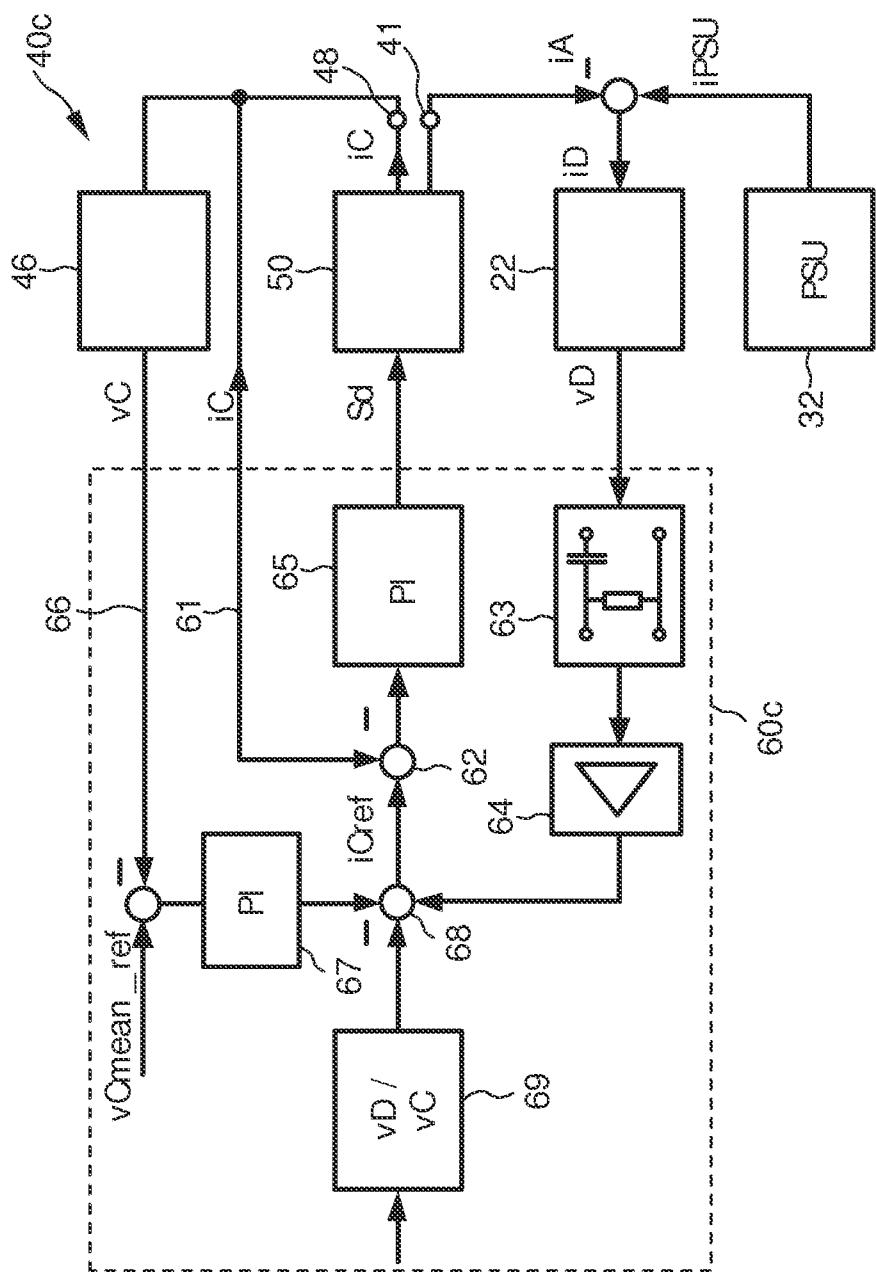

Fig. 6 shows a circuit diagram of another embodiment of a proposed active

capacitor circuit showing details of another embodiment of the

proposed control unit,

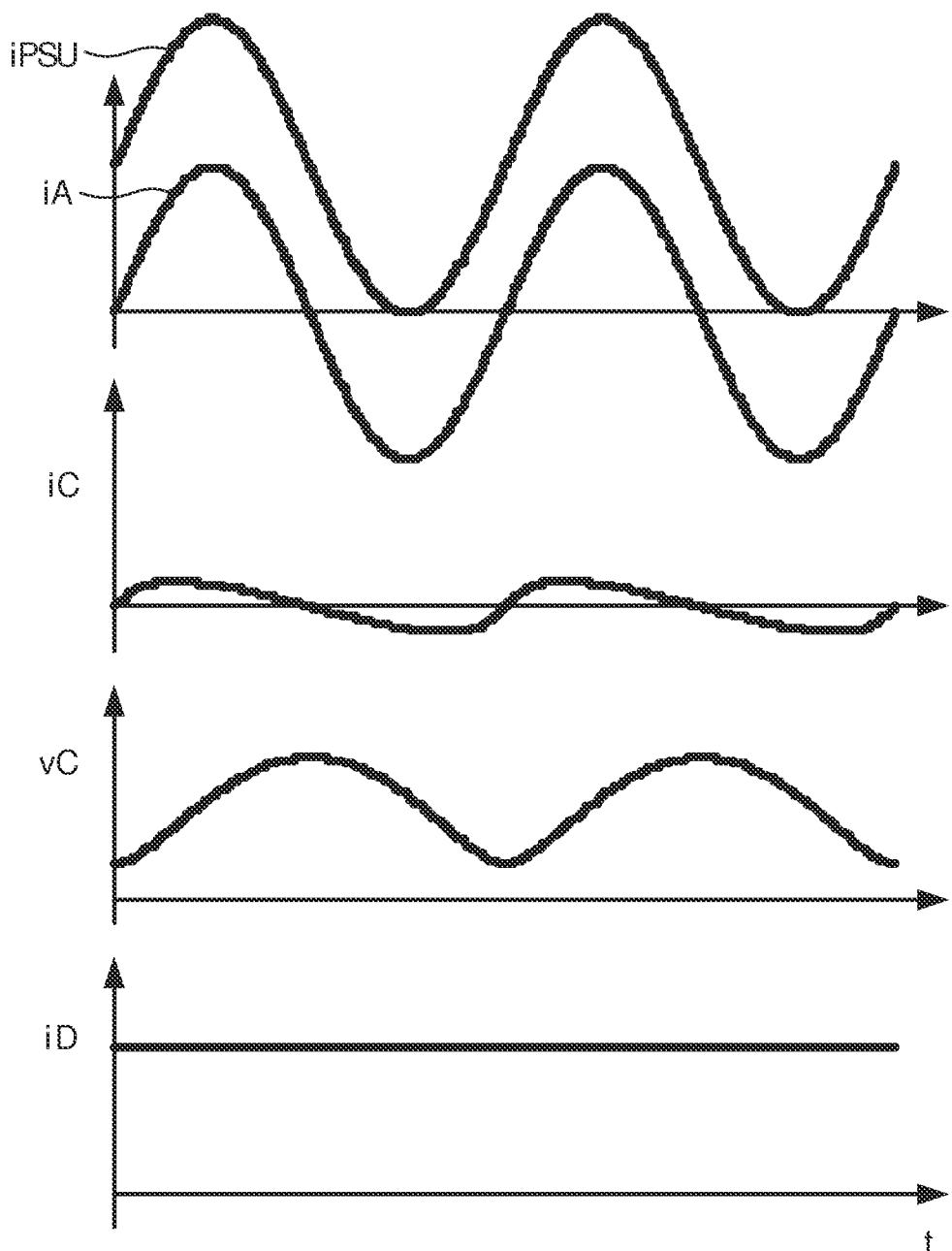

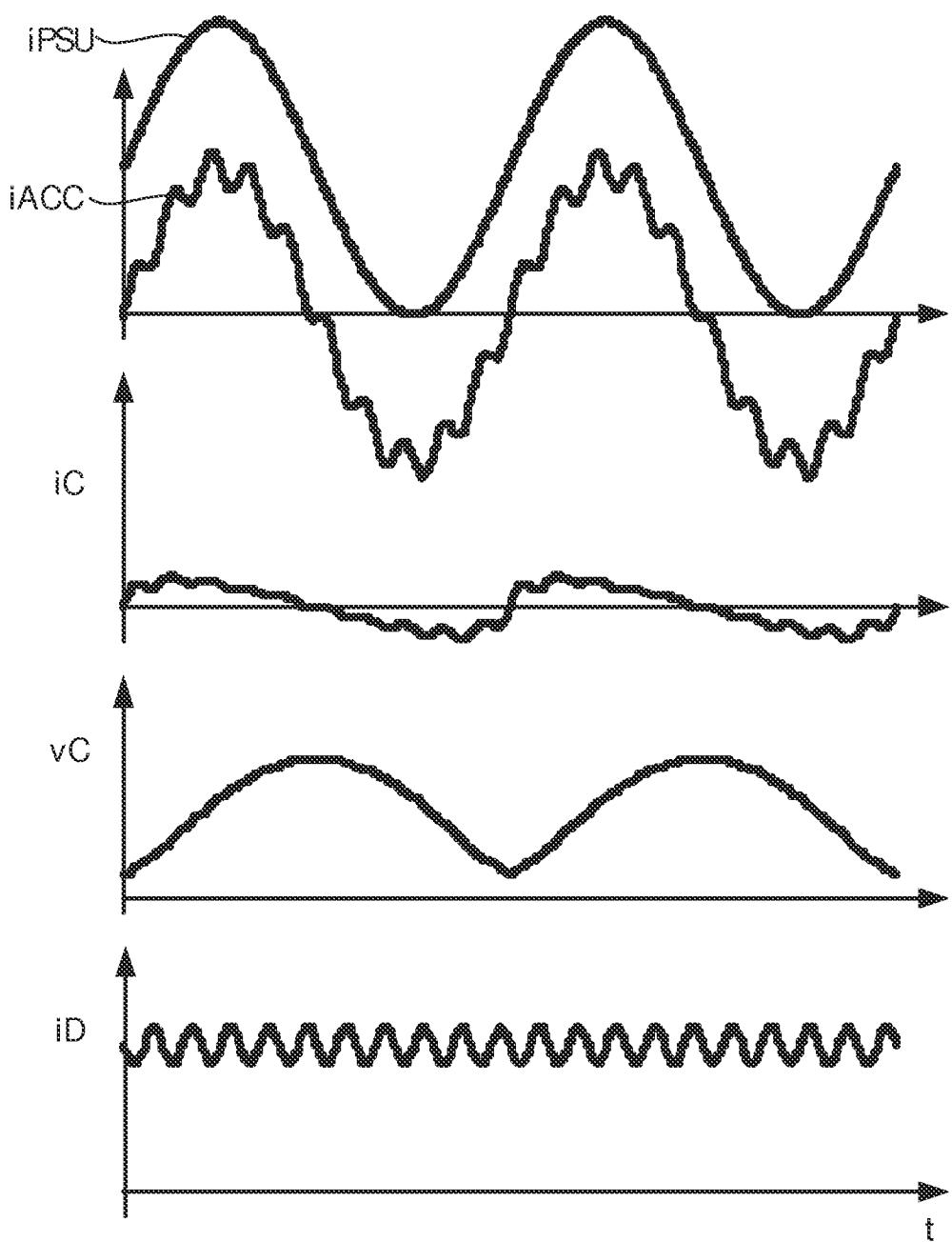

15 Fig. 7 shows a signal diagram of various signals in a driver device as shown

in Figs. 2 or 3, controlled by a control unit as shown in Fig. 5, and

Fig. 8 shows a signal diagram of various signals in a driver device as shown

in Figs. 2 or 3, controlled by a control unit as shown in Fig. 6.

## 20 DETAILED DESCRIPTION OF THE INVENTION

Fig. 1 shows a schematic diagram of a known LED driver device 10 connected to an external power supply 20 (e.g. mains voltage supply). The driver device 10 comprises an input converter stage 12 (also called power supply unit PSU) and an output filter capacitor 14 coupled in parallel to an external load 22, e.g. comprising one or more LEDs 23. The 25 input converter stage 12 converts a supply current  $i_S$  and a periodic supply voltage  $v_S$  into an intermediate current  $i_{PSU}$  that equals the sum of the drive current (or output current)  $i_D$  provided to the load and the capacitor current  $i_C$ . The drive voltage  $v_D$  across power output terminals 16, 17 equals the capacitor voltage  $v_C$ .

Here, the average output current  $i_D$  is preferably controlled by the input 30 converter stage 12, e.g. using load current feedback. For this purpose an (optional) current sensor may be provided in the load which is connected to the input converter stage 12. Accordingly, the average output power is not regulated by the active capacitor circuit.

Fig. 2 shows a schematic diagram of a first embodiment of a proposed driver device 30 including an input converter stage 32 (also called input power stage) and an

embodiment of a proposed active capacitor circuit 40 replacing the capacitor 14 of the known driver device 10. The input converter stage 32 is identical or similar to the input converter stage 12 of the known driver device. It shall be noted, however, that the active capacitor circuit 40 may also be used in other driver devices, including driver devices having no input converter stages. At power input terminals 33, 34 the supply unit 20 is coupled to converter input terminals of said input converter stage 32. At converter output terminals 35, 36 of the input converter stage 32 the proposed active capacitor circuit 40 is coupled. Also here, the average output current  $i_D$  is preferably controlled by the input converter stage 32, e.g. by feeding back the load current, for which purpose an (optional) current sensor may be provided in the load which is connected to the input converter stage 32.

The proposed active capacitor circuit 40 comprises coupling terminals 41, 42 coupled to the converter output terminals 35, 36 of the input converter stage 32 for receiving a periodic input current, in this embodiment the intermediate current  $i_{PSU}$ . Further, at said coupling terminals 41, 42, the drive voltage  $v_D$  and drive current  $i_D$  are provided for driving the load 23 that is coupled between said coupling terminals 41, 42, which correspond to the power output terminals of the driver device 30.

The proposed active capacitor circuit 40 further comprises an output power stage 50 coupled between said coupling terminals 41, 42 for converting said periodic input current  $i_{PSU}$  into said drive current  $i_D$ . The output power stage 50 particularly receives a power stage current  $i_A$ . A low frequency capacitor 46 is coupled between a capacitor output terminal 48 of said output power stage 50 and the coupling terminal 42.

Finally, a control unit 60 is provided for controlling said output power stage 50 by use of a control signal  $S_d$  obtained from a feedback of the drive voltage  $v_D$ , a capacitor voltage  $v_C$  across said low frequency capacitor 46 and/or a capacitor current  $i_C$  through said low frequency capacitor 46.

While in the embodiment shown in Fig. 2 the output power stage 50 is included in the active capacitor circuit 40, in an alternative embodiment shown in Fig. 3 the output power stage 50 is integrated into the load 22', i.e. is part of the external elements, not of the driver device 30' shown in Fig. 3. Furthermore (but not shown), in still other embodiments, not only the output power stage 50 but also the control unit 60 is integrated into the load 22' or only the control unit (but not the output power stage 50) is integrated into the load 22'.

For unity power factor operation of the input power stage 32, the intermediate current  $i_{PSU}$  exhibits 100% ripple at 100Hz as shown in Fig. 7.

Fig. 4 shows a circuit diagram of an embodiment of a proposed active capacitor circuit 40a comprising an embodiment of an output power stage 50a which may be used in embodiments of the driver device 30, 30' as shown in Figs. 2 and 3. The output power stage 50a comprises a bidirectional boost converter, which is preferably used in the 5 case of low voltage LEDs as load. The boost (step up) conversion refers to capacitor charge phases, where the LED voltage is step-up converted to the higher capacitor voltage, whereas during capacitor discharge phases the capacitor voltage is step-down (buck) converted to the LED voltage. In the case of high voltage LEDs, a bidirectional buck converter is preferably used. Other bidirectional converters, such as a buck-boost converter, can also be used in other 10 embodiments.

The bidirectional boost converter comprises two switching elements 51, 52 coupled in series between said capacitor output terminal 48 and the coupling terminal 42 and forming a switch node 53 interposed between them. Further, between said switching node 53 and the coupling terminal 41 a high frequency inductor (choke) 54 is coupled. Between said 15 coupling terminals a high frequency capacitor (input filter capacitor) 55 is coupled. A driver 56 controls said switching elements 51, 52, based on control signals  $S_d$  received from the control unit 60. The driver 56 is preferably a gate driver in this embodiment, which is used to drive the gates of the half bridge inverter formed by the switching elements 51, 52 and which follows the switching pattern  $S_d$ .  $S_d$  generally is a driving signal, which in this example is a 20 PWM switching pattern for the inverter of the output power stage and which determines the average switch node voltage.

Preferably, the converter is operated in a quasi square-wave mode to obtain zero voltage switching (ZVS) and thus enable high switching frequencies (e.g. >1MHz) still at high efficiency. That switching frequency further allows integration of choke 54 and input 25 filter capacitor 55, which, however, could also be located externally. In addition, a switching frequency much higher than the switching frequency of the input power stage 32 also allows completely skipping the output filter that is preferably included in the input power stage 32.

Fig. 5 shows a circuit diagram of another embodiment of an active capacitor circuit 40b showing details of an embodiment of the proposed control unit 60b. Using the 30 control scheme shown in Fig. 5, the ripple current through the load 22 (LED) can be virtually eliminated even if capacitor 46 is only as small as, or a little larger than, the theoretical minimum given by the energy required for zero ripple operation  $E_{capmin} > P_o / (2 \pi f_m)$ , with  $f_m$  being the mains frequency.

Fig. 6 shows a circuit diagram of still another embodiment of an active capacitor circuit 40c showing details of another embodiment of the proposed control unit 60c. Like in the example of Fig. 5, LED current  $i_D$  is 1A and supply current ripple amplitude  $i_A$  is 1A too. Capacitor 46 is  $22\mu F$  and exhibits a voltage swing from about 5V to 35V. In the 5 example, a 10mF (6.3V) capacitor in the circuit shown in Fig. 1 would still result in a 20% ripple.

The control units 60b, 60c each comprise two cascaded feedback loops. The core is the inner feedback loop 61 which controls current  $i_C$  to follow reference current  $i_{Cref}$  (subtraction unit 62). The reference current  $i_{Cref}$  in turn is derived from the drive voltage  $v_D$  10 by means of high pass filtering in a high pass filter 63 and a proportional factor of amplification in amplifier 64, which is higher according as the voltage drop of the load's dynamic resistance is smaller. The control signal  $S_d$  (also called inner control signal) is then generated in a PI controller 65. An outer feedback loop 66 controls capacitor voltage  $v_C$  to swing around a preset value  $v_{Cmean\_ref}$ , which may be related to the capacitor's voltage 15 rating. Another PI controller 67 generates a correction signal (also called outer control signal). Regarding the control strategy, it is important to note that the average (DC) current delivered to the load still is controlled by the input power stage 32. Further, the active capacitor only eliminates ripple from the load current.

In the control unit 60c shown in Fig. 6 an additional modulation unit 69 is 20 provided by which a modulation signal  $i_{Dmod}$  is added in addition unit 68 to the reference  $i_{Cref}$ . Said modulation unit 69 preferably comprises a multiplier that depends on voltages  $v_D$  and  $v_C$ . This multiplier compensates for the relation of  $i_C$  to  $i_{LED}$ . Fig. 8 shows waveforms resulting from modulation signal  $i_{Dmod}$  of about 1kHz.

In this application and in the case of low modulation frequencies (e.g. 1kHz) 25 an extra inductor (not shown) between the input power stage 32 and the load 22 is preferably provided in an embodiment in order to avoid that the modulation current flows through the input power stage 32. In this case, also a relatively low inductive connection of the load 22 to the active capacitor circuit 40c is of advantage.

The modulation signal  $i_{Dmod}$  is an external signal (used e.g. to send data via 30 invisible light fluctuations). In order to avoid visible distortions, i.e. to make the light response equal to  $i_{Dmod}$ , a feed forward transfer function may be applied to  $i_{Dmod}$ , resulting in  $i_{Dmod\_1}$ , which is injected into the reference current node (i.e. the addition unit 68), namely  $i_{Dmod\_1} = i_{Dmod} * v_D / v_C$ .

As mentioned above, Fig. 7 shows a signal diagram of various signals in a driver device as shown in Figs. 2 or 3, controlled by a control unit as shown in Fig. 5, and Fig. 8 shows a signal diagram of various signals in a driver device as shown in Figs. 2 or 3, controlled by a control unit as shown in Fig. 6. The drive voltage  $v_D$ , which is not explicitly shown, basically is a constant, because the drive current is constant. Only a tiny variation of the current  $i_D$  remains, which via the rather small dynamic resistance results in a tiny voltage variation of  $v_D$ , which in turn shows the shape that the current  $i_C$  follows.

With respect to typical single-stage high power factor drivers, problems overcome by the present invention include:

- 10 - high ripple of output current even in the case of large capacitors, which worsens LED utilization and which causes visible flicker;

- high volume and lifetime limitations of electrolytic capacitors;

- hot swapping issues (in the case that a passive capacitor is connected to the load only, that capacitor is typically very large (as explained above) to be effective at all, which results in

- 15 high inrush currents) and a low response time to dimming signals.

With respect to the above mentioned converter disclosed in the paper of Hu and Zane, the present invention provides an individual module that can be used either stand-alone or integrated into the load (e.g. an LED package). A connection of the control unit with the input power stage (for combined control) is not required, but only a measurement of the

20 power supply and/or the load current is required.

Regarding the load current (e.g. LED current) modulation (“coded light”) no extra components are required and no extra losses exist due to light modulation even at high modulation ratios and high modulation frequencies.

Further, according to preferred embodiments of the present invention,

25 feedback controls derive a reference for the capacitor current from a high-pass filtered load voltage (drive voltage). An extra input allows adding a signal to the reference that translates into current modulation, as it may be used for “coded light”.

The present invention is preferably applied in consumer and professional drivers, in particular in professional single-stage HPF flicker-free LED drivers. The active

30 capacitor circuit may be used as an added value system in an LED package (with or without a miniaturized filter capacitor). Further, the active capacitor circuit may be used as stand-alone module (with or without miniaturized filter capacitor). Still further, the present invention may also be used for driving OLEDs.

While the invention has been illustrated and described in detail in the drawings and foregoing description, such illustration and description are to be considered illustrative or exemplary and not restrictive; the invention is not limited to the disclosed embodiments. Other variations to the disclosed embodiments can be understood and effected by those skilled in the art in practicing the claimed invention, from a study of the drawings, the disclosure, and the appended claims.

In the claims, the word "comprising" does not exclude other elements or steps, and the indefinite article "a" or "an" does not exclude a plurality. A single element or other unit may fulfill the functions of several items recited in the claims. The mere fact that certain measures are recited in mutually different dependent claims does not indicate that a combination of these measures cannot be used to advantage.

Any reference signs in the claims should not be construed as limiting the scope.

## CLAIMS:

1. Active capacitor circuit (40) for use in a driver device for driving a load (22), in particular an LED unit comprising one or more LEDs (23), said active capacitor circuit comprising:

- coupling terminals (41, 42) for providing a drive voltage ( $v_D$ ) and/or drive current ( $i_D$ ) for driving a load (22) to be coupled between said coupling terminals (41, 42),

- an output power stage (50) coupled between said coupling terminals (41, 42) for converting said periodic current ( $i_A$ ) into said drive current ( $i_D$ ),

- a low frequency capacitor (46) coupled between a capacitor output terminal (48) of said output power stage (50) and a coupling terminal (42), and

- a control unit (60) for controlling said output power stage (50) by use of a control signal ( $S_d$ ) obtained from a feedback of the drive voltage ( $v_D$ ), a capacitor voltage ( $v_C$ ) across said low frequency capacitor (46) and/or a capacitor current ( $i_C$ ) through said low frequency capacitor (46).

15 2. Active capacitor circuit (40) as claimed in claim 1, wherein said control unit (60b) comprises a first feedback loop (61) for controlling said capacitor current ( $i_C$ ) to follow a reference capacitor current ( $i_{Cref}$ ).

3. Active capacitor circuit (40) as claimed in claim 2, 20 wherein said control unit (60b) is configured to determine said reference capacitor current ( $i_{Cref}$ ) from said drive voltage ( $v_D$ ) by high-pass filtering said drive voltage ( $v_D$ ) and amplifying the high-pass filtered drive voltage by a drive voltage amplification factor.

4. Active capacitor circuit (40) as claimed in claim 3, 25 wherein said control unit (60b) is configured to determine said drive voltage amplification factor in dependence on the voltage drop of the dynamic resistance of said load to be coupled between said coupling terminals.

5. Active capacitor circuit (40) as claimed in claim 1,

wherein said control unit (60b) comprises a second feedback loop (66) for controlling said

capacitor voltage (vC) to swing around a reference capacitor voltage (vCmean\_ref).

5

6. Active capacitor circuit (40) as claimed in claim 5,

wherein said control unit (60b) is configured to determine said reference capacitor voltage

(vCmean\_ref) in relation to the voltage rating of said low frequency capacitor (46).

10

7. Active capacitor circuit (40) as claimed in claims 2 and 5,

wherein said first feedback loop (61) and said second feedback loop (66) are cascaded such

that the first feedback loop (61) forms an inner loop to derive an inner control signal (Sd) and

the second feedback loop (66) forms an outer loop to derive an outer control signal, wherein

said reference capacitor current (iCref) is determined from said drive voltage (vD) by high-

15 pass filtering said drive voltage (vD), amplifying the high-pass filtered drive voltage by a

drive voltage amplification factor, and subtracting said outer control signal from said

amplified high-pass filtered drive voltage.

15

20

8. Active capacitor circuit (40) as claimed in claim 2,

wherein said control unit (60b) is configured to add a modulation signal (iDmod) to said

reference capacitor current (iCref) before using it in said first control loop (61) for controlling

said capacitor current (iC).

25

9. Active capacitor circuit (40) as claimed in claim 8,

wherein said control unit (60c) is configured to determine said modulation signal (iDmod)

from said drive voltage (vD) and/or said capacitor voltage (vC).

30

10. Active capacitor circuit (40) as claimed in claim 1,

wherein said output power stage (50a) comprises a bidirectional converter, in particular a

bidirectional boost converter, a bidirectional buck converter or a bidirectional buck-boost

converter.

11. Active capacitor circuit (40) as claimed in claim 10,

wherein said control unit (60) is configured to control said bidirectional converter to operate

in a quasi square-wave mode.

5

12. Active capacitor circuit (40) as claimed in claim 10,

wherein said bidirectional converter comprises an output inductor (54) coupled between a

switching node (53) of said bidirectional converter and a coupling terminal (41) and an

output capacitor (55) coupled between said coupling terminals (41, 42).

10

13. Driver device (30) for driving a load (22), in particular an LED unit

comprising one or more LEDs (23), said driver device comprising:

- power input terminals (33, 34) for receiving a periodic supply voltage from an external power supply (20),

- an input converter stage (32) coupled to said power input terminals (33, 34) for converting said periodic supply voltage (vS) into said drive voltage (vD) and for outputting an intermediate current (iPSU) at converter output terminals (35, 36), and

- an active capacitor circuit (40) as claimed in any one of claims 1 to 12 coupled to said converter output terminals (35, 36) of said input converter stage (32).

20

14. Driver device (30) as claimed in claim 13,

wherein said control unit (60) is configured to control said bidirectional converter to operate

at a higher switching frequency than the input converter stage (32).

25

15. A light apparatus comprising:

- power input terminals (33, 34) for receiving a periodic supply voltage from an external power supply (20),

- an input converter stage (32) coupled to said power input terminals (33, 34) for converting said periodic supply voltage (vS) into said drive voltage (vD) and for outputting an intermediate current (iPSU) at converter output terminals (35, 36),

- coupling terminals (41, 42) coupled to said converter output terminals (35, 36) of said input converter stage (32) for providing a drive voltage (vD) and/or drive current (iD) for driving a load (22) to be coupled between said coupling terminals (41, 42),

- an output power stage (50) coupled between said coupling terminals (41, 42) for converting said periodic current (iA) into said drive current (iD),

- a low frequency capacitor (46) coupled between a capacitor output terminal (48) of said output power stage (50) and a coupling terminal (42), and

- 5 - a control unit (60) for controlling said output power stage (50) by use of a control signal (Sd) obtained from a feedback of the drive voltage (vD), a capacitor voltage (vC) across said low frequency capacitor (46) and/or a capacitor current (iC) through said low frequency capacitor (46), and

- a light assembly (22) comprising one or more light units, in particular an LED 10 unit comprising one or more LEDs (23), coupled to said coupling terminals (41, 42).

1/6

FIG. 1

FIG. 2

2/6

FIG. 3

FIG. 4

3/6

5

G

E

4/6

FIG. 6

5/6

FIG. 7

6/6

FIG. 8

# INTERNATIONAL SEARCH REPORT

International application No

PCT/IB2012/055180

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H02M1/15 H05B33/08

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H02M H05B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                 | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | <p>BLANCO C ET AL: "A single stage fluorescent lamp ballast with high power factor", APPLIED POWER ELECTRONICS CONFERENCE AND EXPOSITION, 1996. APEC '96. CONFERENCE PROCEEDINGS 1996., ELEVENTH ANNUAL SAN JOSE, CA, USA 3-7 MARCH 1996, NEW YORK, NY, USA, IEEE, US, vol. 2, 3 March 1996 (1996-03-03), pages 616-621, XP010159848, DOI: 10.1109/APEC.1996.500504 ISBN: 978-0-7803-3044-3 the whole document</p> <p style="text-align: center;">-----</p> <p style="text-align: center;">-/-</p> | 1-15                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

|                                                                                                                                                                      |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                            | Date of mailing of the international search report |

| 14 January 2013                                                                                                                                                      | 21/01/2013                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Morrish, Ian             |

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/IB2012/055180 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | <p>RIBAS J ET AL: "A new discharge lamp ballast based on a self-oscillating full-bridge inverter integrated with a buck-type PFC circuit",<br/>           APEC 2001. 16TH. ANNUAL IEEE APPLIED POWER ELECTRONICS CONFERENCE AND EXPOSITION.<br/>           ANAHEIM, CA, MARCH 4 - 8, 2001; [ANNUAL APPLIED POWER ELECTRONICS CONFERENCE], NEW YORK, NY : IEEE, US, vol. 2, 4 March 2001 (2001-03-04), pages 688-694, XP010536070, DOI: 10.1109/APEC.2001.912444 ISBN: 978-0-7803-6618-3 the whole document</p> <p>-----</p> <p>US 5 345 376 A (NOURBAKHS FARHAD [US])<br/>           6 September 1994 (1994-09-06)<br/>           pages 1, 2; figure 1</p> <p>-----</p> | 1-15                  |

| A         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-15                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/IB2012/055180

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 5345376                             | A 06-09-1994     | NONE                    |                  |