(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4369710号

(P4369710)

(45) 発行日 平成21年11月25日(2009.11.25)

(24) 登録日 平成21年9月4日(2009.9.4)

(51) Int.Cl.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36  |      |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G02F | 1/133 | 550  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 611A |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20  | 621B |

|             |              |                  | G09G | 3/20  | 624B |

請求項の数 6 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2003-309472 (P2003-309472)

(22) 出願日

平成15年9月2日(2003.9.2)

(65) 公開番号

特開2005-77864 (P2005-77864A)

(43) 公開日

平成17年3月24日(2005.3.24)

審査請求日

平成18年1月24日(2006.1.24)

(73) 特許権者 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100093506

弁理士 小野寺 洋二

(72) 発明者 宮沢 敏夫

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

審査官 堀部 修平

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の走査線と複数の信号線が交差する部分に対応して設けた画素を有し、前記画素は画素電極と該画素電極を選択するスイッチング素子と前記画素電極と前記スイッチング素子の間に設けて前記画素電極に書き込むデータを記憶する記憶回路とで構成され、

前記記憶回路に互いに逆極性で変化する交番電圧を印加する一対の交番電圧電源線を備え、

前記記憶回路は前記一対の交番電圧電源線を橋絡して直列接続したN M O SトランジスタとP M O Sトランジスタの第1のトランジスタ対と、前記一対の交番電圧電源線を橋絡して直列接続したN M O SトランジスタとP M O Sトランジスタの第2のトランジスタ対を有し、

前記第1のトランジスタ対の制御電極の共通接続点を前記第2のトランジスタ対の直列接続中間点に接続し、前記第2のトランジスタ対の制御電極の共通接続点を前記第1のトランジスタ対の直列接続中間点に接続してなり、

前記第1のトランジスタ対を構成するN M O SトランジスタとP M O Sトランジスタのそれぞれと直列にダイオードが接続され、

前記ダイオードの導通方向は、前記第1のトランジスタ対を構成するP M O Sトランジスタ側からN M O Sトランジスタ側へ向かう方向であり、

前記スイッチング素子の出力点は前記第1のトランジスタ対の接続点に接続されると共

10

20

に、前記第2のトランジスタ対の直列接続中間点は前記画素電極に接続され、

前記第2のトランジスタ対の制御電極の共通接続点と前記第2のトランジスタ対の直列接続中間点の間に容量が接続されていることを特徴とする表示装置。

#### 【請求項2】

前記ダイオードは、前記第1のトランジスタ対の直列接続中間点との間にそれぞれ接続されていることを特徴とする請求項1に記載の表示装置。

#### 【請求項3】

前記ダイオードは、前記第1のトランジスタ対を構成するN M O SトランジスタとP M O Sトランジスタのそれぞれと前記一対の交番電圧電源線との間にそれぞれ接続されていることを特徴とする請求項1に記載の表示装置。 10

#### 【請求項4】

前記画素を1色の単位画素として複数の前記単位画素を1カラー画素としたことを特徴とする請求項1～3の何れかに記載の表示装置。

#### 【請求項5】

前記1カラー画素を構成する各単位画素の画素電極を面積が異なる複数の電極で構成したことを特徴とする請求項4に記載の表示装置。

#### 【請求項6】

前記複数の電極が2ビット以上の階調表示に対応して前記スイッチング素子により選択されることを特徴とする請求項5に記載の表示装置。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、アクティブマトリックス型の表示装置に関するが、特に高開口率で高精細な画素メモリ方式の多階調表示を可能とした表示装置に好適なものである。 30

##### 【背景技術】

##### 【0002】

ノート型コンピュータやディスプレイメニター用の高精細かつカラー表示が可能な表示装置として液晶パネルを用いた表示装置やエレクトロルミネッセンス（特に、有機E L）等を用いた様々な方式の表示装置が実用化または実用化のための研究がなされている。現在最も広く用いられているのが液晶表示装置であり、ここでは表示装置の典型例として所謂アクティブマトリックス型の液晶表示装置を例として説明する。 30

##### 【0003】

アクティブマトリックス型液晶表示装置として代表的な薄膜トランジスタ（T F T）型は、画素毎に設けた薄膜トランジスタT F Tをスイッチング素子として画素電極に信号電圧（映像信号電圧：階調電圧）を印加するものであるため、画素間のクロストークがなく、高精細で多階調表示が可能である。

##### 【0004】

一方、この種の液晶表示装置を携帯型の情報端末など、電源にバッテリーを用いる電子装置に実装した場合、その表示に伴う消費電力の低減化が必要になる。そのために、液晶表示装置の各画素にメモリ機能を持たせようというアイデアが従来より多くの提案がなされている。 40

##### 【0005】

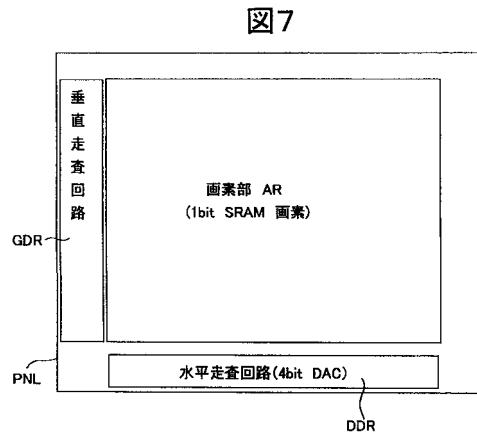

図7は各画素に1ビットのスタティックラムを内蔵した低温ポリシリコン薄膜トランジスタ方式の液晶表示装置を構成する液晶パネルの構成例を説明する模式図である。液晶パネルは第1基板と第2基板の対向間隙に液晶を挟持して構成される。図中、参照符号P N Lは液晶パネルであり、平面の大部分を占める画素部（表示領域）A Rの周辺に垂直走査回路G D Rと水平走査回路D D Rを第1基板に有する。画素部（画素アレー）A Rの各画素は1ビット（b i t）の画像メモリ（スタティックラム：S R A M）を有する。この液晶パネルP N Lは、その水平走査回路D D Rに4 b i t程度のデジタル-アナログ変換回路（D A C）を内蔵しているが、必須ではない。 50

## 【0006】

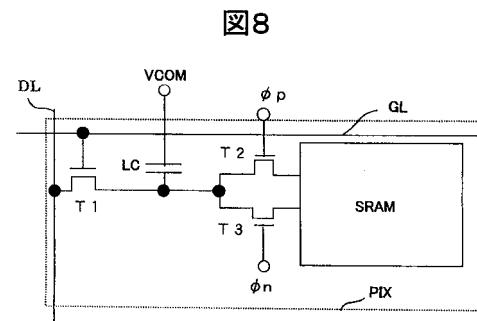

図8は図7における1ビットSRAM画像メモリの概要を説明する回路図である。図中、 $G_L$ はゲート線(走査線)、 $D_L$ はドレイン線(信号線)、 $L_C$ は液晶、 $V_{COM}$ はコモン電圧である。参照符号PIXは画素回路を示す。画素回路PIXはドレイン線 $D_L$ から入力する表示信号をゲート線 $G_L$ に印加される走査電圧に基づいて取り込むスイッチング用のトランジスタT1、液晶 $L_C$ 、映像信号の画像メモリSRAMへの取込みと読み出しを行う一対のトランジスタT2、T3で構成される。画素回路PIXは外部からの4ビット～6ビットの階調アナログ電圧をそのまま液晶駆動用電極に供給する通常のサンプリング機能と、外部1ビットデータを一旦SRAMに格納し、その1ビットデータに準じた交番電圧 $p$ 、 $n$ を液晶駆動用電極に出力する画像メモリ機能とを有する。

10

## 【0007】

サンプリング機能と画像メモリ機能の動作選択は外部から制御される。なお、交番電圧 $p$ と $n$ は液晶交番電圧周期に同期し互いに逆極性で交番する交流信号であり、 $n$ は $p$ の反転波形で示される。この画素構成を採用することで、例えば携帯電話機の待ち受け時等にSRAMに格納されている1ビットデータを表示することでデータ書き込み等の消費電力の低減が可能となる。

## 【0008】

なお、1ビットメモリを持った面積階調表示構造の表示装置を開示したものとしては、例えば特許文献1を挙げることができる。

【特許文献1】特開2002-175040号公報

20

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

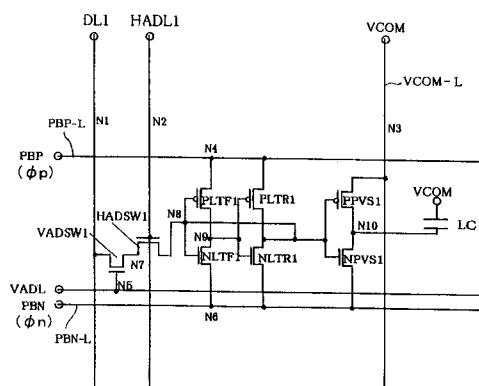

図9は本出願人の既提案にかかる画像メモリ回路を有する液晶表示装置の1画素回路の構成例を説明する回路図である。この液晶表示装置を構成する第1基板において、多数のドレイン線 $D_L$ を構成するドレイン線 $D_L$ 1は画素に映像信号を供給する配線を構成し、選択信号線HADL1とVADLは映像信号を印加する画素を選択するための配線である。参照符号 $V_{COM}$ は固定電圧であるコモン電圧で、所謂TN型液晶パネルでは第2基板側に有する。画素は、次に選択されて書き換えるまでの間印加された映像信号を保持する機能を持つ。なお、液晶 $L_C$ を有機エレクトロルミネッセンス素子(有機EL)等に置き換えれば、有機EL表示装置等になる。

30

## 【0010】

固定電圧 $V_{COM}$ は固定電圧線 $V_{COM}-L$ に印加される。固定電圧 $V_{COM}$ は液晶 $L_C$ を挟む第2基板に形成した電極に接続されている。交番電圧PBP(図8における $p$ に相当)とPBN(同 $n$ に相当)は、交番電圧線PBP-LとPBN-Lに印加される。

## 【0011】

画素への映像信号の書き込みは、選択信号線HADLを構成する選択信号線HADL1と選択信号線VADLに印加される各選択信号で2つのNMOSトランジスタVADS1とHADSW1がオン状態となることにより行われる。

40

## 【0012】

書き込まれた映像信号電位を入力ゲート(電圧ノードN8)電位とし、一对のp型電界効果トランジスタ(PMOS)PLTF1とn型電界効果トランジスタ(NMOS)NLTF1の各々のソースあるいはドレインとなる電極もしくは拡散領域が電気的に接続されて出力部(電圧ノードN9)を形成する第1のインバータを構成する。以下、電圧ノードを、単にノードと称する。

## 【0013】

第1のインバータを構成する一对のp型電界効果トランジスタ(PMOS)PLTF1とn型電界効果トランジスタ(NMOS)NLTF1の各々のソースまたはドレインとなる電極もしくは拡散領域が電気的に接続された出力部(ノードN9)の電位を入力ゲート

50

電位とする一対の p 型電界効果トランジスタ (PMOS) P L T R 1 と n 型電界効果トランジスタ (NMOS) N L T R 1 で第 2 のインバータを構成する。

【0014】

第 2 のインバータを構成する一対の p 型電界効果トランジスタ P L T R 1 と n 型電界効果トランジスタ N L T R 1 の各々のソースまたはドレインとなる電極もしくは拡散領域が電気的に接続された出力部 (ノード N 8 ) の電位を入力ゲート電位とする一対の p 型電界効果トランジスタ (PMOS) P P V S 1 と n 型電界効果トランジスタ (NMOS) N P V S 1 で第 3 のインバータを構成する。

【0015】

そして、第 2 のインバータを構成する一対の p 型電界効果トランジスタ P L T R 1 と n 型電界効果トランジスタ N L T R 1 の出力部 (ノード N 8 ) は、同時に第 1 のインバータの入力ゲート (ノード N 8 ) と電気的に接続される。第 1 と第 2 のインバータを構成する n 型電界効果トランジスタ N L T F 1 と N L T R 1 の、インバータの出力でないソースあるいはドレインもしくは拡散領域 (ノード N 6 ) が前記一対の交番電圧線の一方 (P B N ) に接続される。

【0016】

さらに、第 1 と第 2 のインバータを構成する p 型電界効果トランジスタ P L T F 1 と P L T R 1 の、インバータの出力でないソースあるいはドレインもしくは拡散領域 (ノード N 4 ) が前記第 1 および第 2 のインバータの n 型電界効果トランジスタのインバータ出力でないソースとなる電極あるいはドレインもしくは拡散領域が接続された交番電圧線 (ノード N 6 ) と対をなす電圧の交番電圧線 P B P に接続される。

【0017】

第 3 のインバータを構成する一対の p 型電界効果トランジスタ P P V S 1 と n 型電界効果トランジスタ N P V S 1 のインバータ出力部 (ノード N 10 ) でない各々のソースあるいはドレインとなる電極 (ノード N 6 および N 10 ) もしくは拡散領域の一方 (ノード N 6 ) は、前記交番電圧線のいずれか一方 (P B N ) に接続され、他方は固定電圧線 V C O M に接続される。

【0018】

1 ビット S R A M で実現できる色数は R 、 G 、 B 各色について各 2 であり、合計で  $2 \times 2 \times 2 = 8$  色であるが、カラー表示としては色数が少なすぎ、前記したような携帯電話機の待ち受け時等、 S R A M に格納された 1 ビットデータを表示することでデータの書き込み電力の低減という利用方法に限定される。

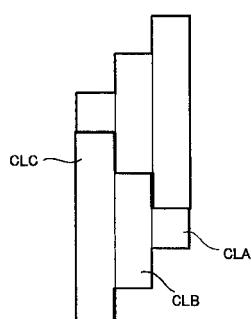

【0019】

図 10 は図 9 で説明した単位画素を組合せた面積階調画素の構成例の説明図である。この例では、各単位画素を構成する画素電極の面積を面積が異なるセル C L - A 、セル C L - B 、セル C L - C の 3 種の組合せとしたものである。これらの面積が異なるセルを選択的に組み合わせて 3 ビット 8 階調表示を可能としている。これを各色 (R , G , B ) について構成しさらに多色表示を可能とした 1 カラー画素とすることができる。

【0020】

しかし、前記図 9 で説明した画素メモリ方式ではその配線数、トランジスタ数が多くなり回路規模が大きいため、消費電力低減には限界があると共に開口率の向上が難しい。また、図 10 で説明した形式では、回路構成や画素電極の構成が複雑になり、製造コストを低減することが難しい。この対策として、本発明の出願人は次に説明する構成を提案した。

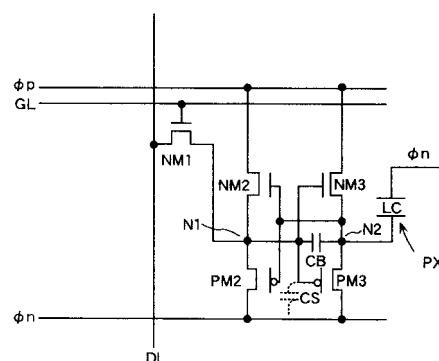

【0021】

図 11 は本出願人の既提案にかかる画像メモリ回路を有する液晶表示装置の 1 画素の他の構成例を説明する回路図である。また、図 12 はカラー表示の階調を R が 3 ビット、 G が 3 ビット、 B が 2 ビットのデータとして 256 色表示とした場合のカラー 1 画素の表示領域におけるレイアウトの一例を説明する平面図である。

【0022】

10

20

30

40

50

図11の基本的な動作は図9と同様であるが、この構成では、データ保持用のトランジスタ対(CMOSトランジスタ対)が画素電極PXへの出力回路を兼ねている点で異なる。画像メモリ(記憶回路)は一对の電源線p,nを橋絡して直列接続したトランジスタ(NMOS)NM2とトランジスタ(PMOS)PM2からなる第1のトランジスタ対と、該第1のトランジスタ対に対して前記一对の電源線p,nを橋絡して直列接続したトランジスタ(NMOS)NM3とトランジスタ(PMOS)PM3の第2のトランジスタ対を有している。

#### 【0023】

一对の電源線p,nには互いに逆極性で変化する交流電圧が供給される。メモリ回路の第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2の制御電極の共通接続点は第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3の直列接続中間点(ノード)N2に接続されている。また、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3の制御電極の共通接続点は第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2の直列接続中間点(ノード)N1に接続されている。

#### 【0024】

NMOSトランジスタNM1はスイッチング素子(トランジスタ)である。このスイッチング素子NM1はゲート線GLで選択され、ドライン線DLから供給される映像信号(データ)を第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2のノードN1に接続されている。スイッチング素子NM1の出力点は第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2のノードN1に接続され、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3のノードN2は単位画素PXの画素電極に接続されている。そして、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3のノードN2と制御電極の共通接続点の間にブーストストラップ容量CBが挿入されている。なお、参照符号CSは浮遊容量を示す。

#### 【0025】

図12において、参照符号CXはカラー1画素、R1,R2,R3およびG1,G2,G3は3ビットデータのそれぞれに対応して面積階調で制御される赤(R)と緑(G)の分割単位画素電極、B1,B2は2ビットデータのそれぞれに対応して面積階調で制御される青(B)の分割単位画素電極を示す。分割単位画素電極R1,R2,R3でRの単位画素を、分割単位画素電極G1,G2,G3でGの単位画素を、そして分割単位画素電極B1,B2でBの単位画素を構成する。分割単位画素電極は前記した液晶駆動電極である。

#### 【0026】

RおよびGの単位画素はゲート線GLと3ビットデータを供給する3本のドライン線DL(R1),(R2),(R3)およびDL(G1),(G2),(G3)にそれぞれ接続したスイッチング素子NM1で選択される。各単位画素には各スイッチング素子NM1で制御されるビット数に対応した数の画像メモリSRAMを持ち、画像メモリSRAMの出力は、図5に示したように、分割単位画素電極にコンタクトホールCTHで電気的に接続されている。

#### 【0027】

R、G、Bの各単位画素はゲート線GLの延在方向のサイズが同じで、R、Gの各単位画素はドライン線DLの延在方向に「3」、「6」、「12」の比率で分割単位画素に分割され、Bの単位画素は「7」、「14」の比率で分割単位画素に分割されている。この分割によって256色の面積階調を実現している。

#### 【0028】

図12に示したレイアウトのカラー画素により、R:3ビット、G:3ビット、B:2ビットの計8ビットデータで256色のカラー表示を実現でき、変化の無い表示データはメモリに格納されたデータを表示することでフレーム毎のデータ転送を必要としないことで消費電力を低減できる。なお、各色のビット数を増やしてさらに多くのカラー表示を実

10

20

30

40

50

現できる。

**【0029】**

このように、画素自体にデータの保持機能（メモリ機能）を持たせることで毎フレーム毎にデータを送り込む必要がなくなり、変化した部分のデータのみを書き換えればよい。また、画素毎にメモリ機能を有することで表示領域の画素をランダムに読み出して表示を行うことが可能となる。ランダムアクセス表示を行う場合、次に説明するようなランダムアクセス回路を設ければよい。

**【0030】**

上記した図11の回路構成とすることにより、図9に比べて回路規模の大幅な簡素化が実現できる。しかし、この構成においては、画像メモリにデータを保持させる際に、例えば図11における第1のトランジスタ対PM2とNM2のオン／オフ動作の遷移時に誤動作が発生する場合がある。10

**【0031】**

本発明の目的は、回路構成を簡略化して面積階調による多色化を実現すると共に、画素メモリへのデータ書き込みの誤動作を防止し、高開口率かつ多階調のカラー表示を可能とした表示装置を提供することにある。

**【課題を解決するための手段】**

**【0032】**

本発明は、映像信号を保持するCMOSトランジスタ対を画素電極への出力回路に兼ねさせ、また画素電極に容量を接続してSRAMへの書き込み状態を上記容量に蓄積された電荷を利用して制御する構成と共に、画素メモリへのデータ書き込みを制御する上記CMOSトランジスタ対に対して、それぞれ導通方向が同一のダイオードを直列に挿入した。本発明の代表的な構成を記述すれば次のとおりである。20

**【0033】**

(1)、複数の走査線と複数の信号線が交差する部分に対応して設けた画素を有し、

前記画素を画素電極と該画素電極を選択するスイッチング素子と前記画素電極と前記スイッチング素子の間に設けて前記画素電極に書き込むデータを記憶する記憶回路とで構成し、

前記記憶回路に、互いに逆極性で変化する交番電圧を印加する一対の交番電圧電源線を備え。30

前記記憶回路は、前記一対の交番電圧電源線を橋絡して直列接続したNMOStранジスタとPMOSトランジスタの第1のトランジスタ対と、該第1のトランジスタ対に対して前記一対の交番電圧電源線を橋絡して直列接続したNMOStранジスタとPMOSトランジスタの第2のトランジスタ対を備え、

前記第1のトランジスタ対の制御電極の共通接続点を前記第2のトランジスタ対の直列接続中間点に接続し、前記第2のトランジスタ対の制御電極の共通接続点を前記第1のトランジスタ対の直列接続中間点に接続し、

前記第1のトランジスタ対を構成するNMOStранジスタとPMOSトранジスタのそれぞれと直列に、当該トランジスタの導通方向と同一方向に導通方向を有するダイオードを接続し。40

前記スイッチング素子の出力点を前記第1のトランジスタ対の接続点に接続すると共に、前記第2のトランジスタ対の直列接続中間点は前記画素電極に接続し、

前記第2のトランジスタ対の制御電極の共通接続点と直列接続中間点の間に容量を接続した。

**【0034】**

前記ダイオードは、前記第1のトランジスタ対の直列接続中間点との間にそれぞれ接続するか、あるいは前記第1のトランジスタ対を構成するNMOStранジスタとPMOSトランジスタのそれぞれと前記一対の交番電圧電源線との間にそれぞれ接続する。

**【0035】**

前記画素を1色の単位画素として複数の前記単位画素を1カラー画素とし、あるいは前50

記1 カラー画素を構成する各単位画素の画素電極を面積が異なる複数の電極で構成して、前記複数の電極を2ビット以上の階調表示に対応して前記スイッチング素子で選択する。

#### 【発明の効果】

##### 【0036】

本発明によれば、配線数およびトランジスタ数が低減されると共に、画像メモリへの書き込み、読み出しの誤動作が防止され、開口率の低下が防止され、多階調かつ高精細のカラー画像表示装置を得ることができる。

##### 【0037】

なお、本発明は上記の構成および後述する実施例の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変更が可能である。

10

#### 【発明を実施するための最良の形態】

##### 【0038】

以下、本発明の表示装置の実施の形態について、実施例の図面を参照して詳細に説明する。なお、以下の実施例では、液晶表示装置を例として説明するが、有機EL等のマトリクス型表示装置にも同様に適用できることは言うまでもない。

##### 【実施例1】

##### 【0039】

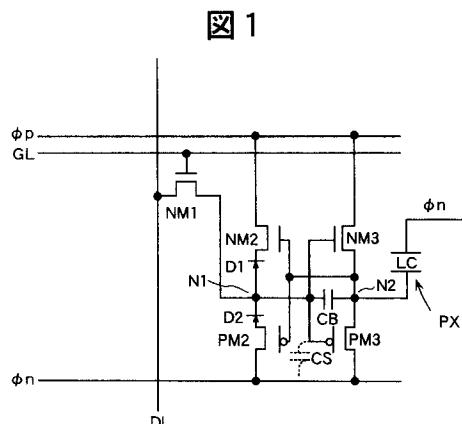

図1は本発明の実施例1を説明するための液晶表示装置の1画素の回路図である。前記の図11と同様に、画像メモリ(記憶回路)は一対の電源線p, nを橋絡して直列接続したトランジスタ(NMOS)NM2とトランジスタ(PMOS)PM2からなる第1のトランジスタ対と、該第1のトランジスタ対に対して前記一対の電源線p, nを橋絡して直列接続したトランジスタ(NMOS)NM3とトランジスタ(PMOS)PM3の第2のトランジスタ対を有している。第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2とは、各トランジスタNM2とPM2とのそれぞれの導通方向と同じ導通方向、すなわち各トランジスタNM2とPM2のドレイン側にダイオードD1、D2を介して接続される。

20

##### 【0040】

一対の電源線p, nには互いに逆極性で変化する交流電圧(交番電圧)が供給される。メモリ回路の第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2の制御電極の共通接続点は第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3の直列接続中間点(ノード)N2に接続されている。また、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3の制御電極の共通接続点は第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2の直列接続中間点であるダイオードD1とD2の順方向接続点(ノード)N1に接続されている。

30

##### 【0041】

NMOSトランジスタNM1はスイッチング素子(スイッチングトランジスタ)である。このスイッチング素子NM1の出力は、ゲート線GLで選択されてドレイン線DLから供給される映像信号(データ)を第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2の接続点すなわち、ダイオードD1とD2の接続点であるノードN1に接続されている。

40

##### 【0042】

このように、スイッチング素子NM1の出力点は第1のトランジスタ対を構成するトランジスタNM2とトランジスタPM2のノードN1に接続され、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3のノードN2は単位画素PXの画素電極に接続されている。そして、第2のトランジスタ対を構成するトランジスタNM3とトランジスタPM3のノードN2と制御電極の共通接続点の間にブーストトラップ容量CBが挿入されている。なお、参照符号CSは浮遊容量を示す。

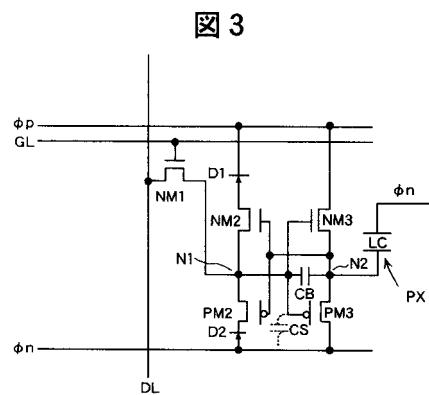

##### 【0043】

図2は電源線p, nに印加される液晶駆動用の交番電圧の一例を説明する波形図である。この電源線p, nに印加される液晶駆動用の交番電圧(説明のため、交番電圧

50

自体も  $p$ ,  $n$  として説明する)は、ハイレベルとローレベル(または、正極レベルと負極レベル)で繰り返される。図中、時刻  $t_1$  では  $p$  がハイレベル、 $n$  がローレベルとなる。そして、時刻  $t_2$  では  $p$  がローレベル、 $n$  がハイレベルとなる。

#### 【0044】

図1の回路において、画素選択のためのゲート線  $GL$  がローレベルとなり、N M O Sトランジスタ  $NM1$  がオフ状態で画像メモリが外部に対して孤立(フロー・ティング)となっている時に、液晶  $LC$  の画素電極となるノード  $N2$  の電位をゲート電圧としてノード  $N1$  に共通接続点が接続された第1のトランジスタ対のN M O Sトランジスタ  $NM2$  とP M O Sトランジスタ  $PM2$  は、時刻  $t_2$  では一般的なバイアス関係であり、時刻  $t_1$  ではドレイン・ソース電圧となる電圧  $p$ ,  $n$  が逆になる。

10

#### 【0045】

図2の時刻  $t_1$  における逆電圧の設定の際に、ノード  $N1$  の電位変化の過渡状態で動作が不安定となる場合はある。この対策として、本実施例では、ダイオード  $D1$ 、 $D2$  を第1のトランジスタ対の各トランジスタ  $NM2$  と  $PM2$  と直列に接続した。すなわち、ダイオード  $D1$  はトランジスタ  $NM2$  の導通方向に、ダイオード  $D2$  はトランジスタ  $PM2$  の導通方向に一致させて両トランジスタの共通接続点の間に挿入した。

#### 【0046】

本実施例の構成により、時刻  $t_2$  に示した第2のトランジスタ対  $NM3$  と  $PM3$  で構成されるC M O Sインバータに関して一般的な正常バイアスとなる場合にのみ、ダイオード  $D1$ 、 $D2$  の導通が順方向になり、電位保持電流(電荷)の出入りを行う。一方、時刻  $t_1$  に示したようにC M O Sインバータを構成するトランジスタ  $PM2$  と  $NM2$  に関して一般的に逆バイアスとなる場合は、ダイオード  $D1$ 、 $D2$  の導通が逆方向になり、電位保持電流(電荷)の出入りを禁止する。この動作により、画像メモリの電位保持が確実となる。

20

#### 【実施例2】

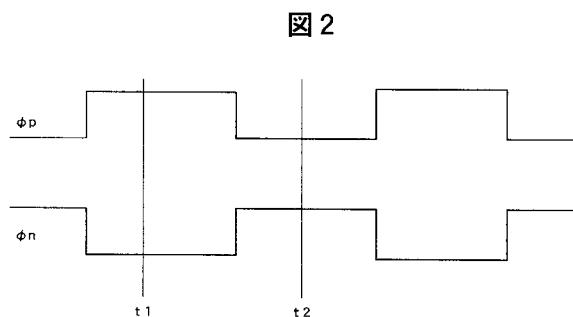

#### 【0047】

図3は本発明の実施例2を説明するための液晶表示装置の1画素の回路図である。本実施例では、図1におけるダイオード  $D1$ 、 $D2$  の挿入位置を第1のトランジスタ対を構成するトランジスタ  $NM2$  および  $PM2$  の前記電源線  $p$ ,  $n$ との間、すなわちソース側とした。その他の構成および機能は図1と同様であるので、繰り返しの説明はしない。

#### 【0048】

30

本実施例によっても、図2における時刻  $t_2$  に示した第2のトランジスタ対  $NM3$  と  $PM3$  で構成されるC M O Sインバータに関して一般的な正常バイアスとなる場合にのみ、ダイオード  $D1$ 、 $D2$  の導通が順方向になり、電位保持電流(電荷)の出入りを行う。一方、時刻  $t_1$  に示したようにC M O Sインバータを構成するトランジスタ  $PM2$  と  $NM2$  に関して一般的に逆バイアスとなる場合は、ダイオード  $D1$ 、 $D2$  の導通が逆方向になり、電位保持電流(電荷)の出入りを禁止する。この動作により、画像メモリの電位保持が確実となる。

#### 【実施例3】

#### 【0049】

本発明の実施例3として、上記のダイオード  $D1$ 、 $D2$  の一方をトランジスタ  $PM2$  と  $NM2$  の一方のドレイン側に挿入し、他方をソース側に挿入してもよく、またこの逆としても同様の効果を得ることができる。

40

#### 【0050】

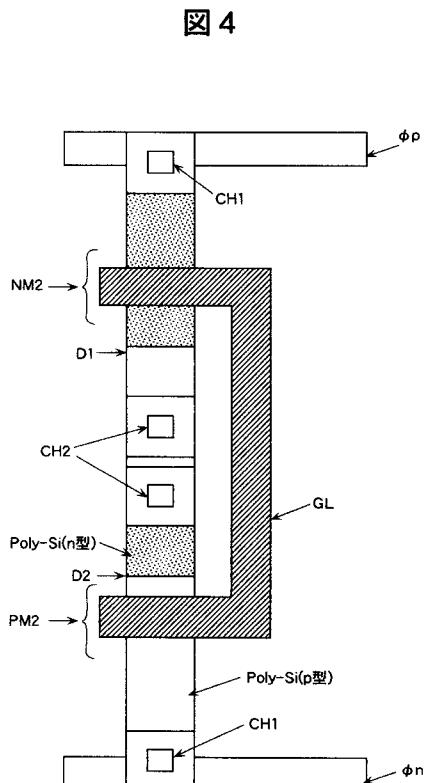

次に、本発明による画素回路における第1のトランジスタ対で構成されるインバータ回路の部分の基板上の具体的なレイアウト例を説明する。

#### 【0051】

図4は図1で説明した本発明の実施例1の第1のトランジスタ対のレイアウトを説明する要部平面図である。図中、図1と同一符号は同一機能部分に対応する。電源線  $p$  と  $n$  は例えばアルミニウム(A1)を好適とする。また、ゲート線  $GL$  はモリブデン・タンゲステン(MoW)が好適である。第1のトランジスタ対  $NM2$  と  $PM2$  およびダイオード

50

D 1 と D 2 はポリシリコン半導体層 ( p o l y - S i ) に作り込まれる。参照符号 C H 1 は半導体層と配線層の接続と取るコンタクトホール、C H 2 は n 型ポリシリコン拡散層と p 型ポリシリコン拡散層の接続と取るコンタクトホールを示す。

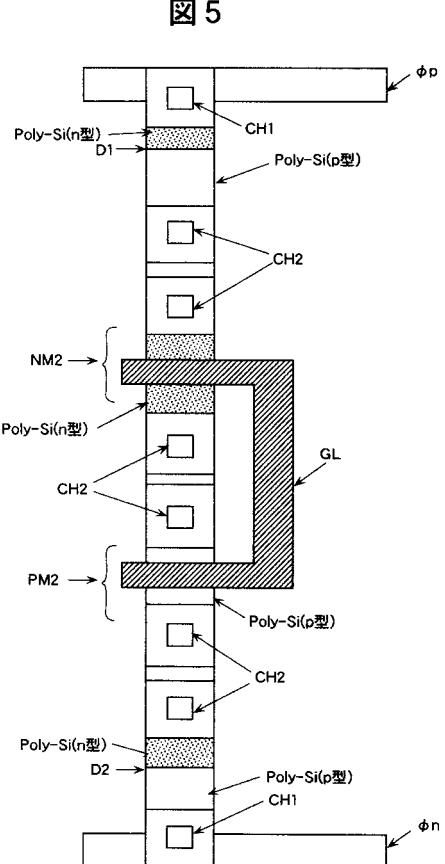

#### 【 0 0 5 2 】

図 5 は図 3 で説明した本発明の実施例 2 の第 1 の トランジスタ 対のレイアウトを説明する要部平面図である。図中、図 4 と同一符号は同一機能部分に対応する。このレイアウト例ではダイオード D 1 と D 2 を トランジスタ N M 2 と P M 2 のドレインまたはソースに接続するためにコンタクトホールの数は図 4 に比較して多くなる。特に、トランジスタ 及びダイオードを構成する半導体層と配線層との接続をとるコンタクトホールが占める面積は、1 画素に割当てられる面積に対して大である。したがって、コンタクトホールの数は少ない方が実用上、有利となる。10

#### 【 0 0 5 3 】

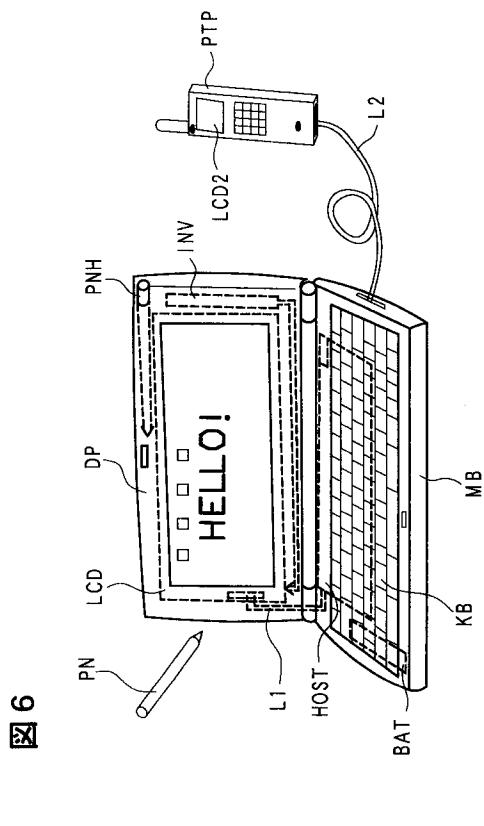

図 6 は本発明による表示装置を実装した電子機器の一例としての携帯型情報端末の構成例を説明する斜視図である。この携帯型情報端末 ( P D A ) はホストコンピュータ H O S T やバッテリー B A T を収納し、表面にキーボード K B を備えた本体部 M B と、表示装置に液晶表示装置 L C D を用いバックライト用のインバータ I N V を実装した表示部 D P で構成されている。本体部 M B には接続ケーブル L 2 を介して携帯電話機 P T P が接続できるようになっており、遠隔地との間で通信が可能となっている。

#### 【 0 0 5 4 】

表示部 D P の液晶表示装置 L C D とホストコンピュータ H O S T との間はインターフェースケーブル L 1 で接続されている。液晶表示装置 L C D は画像記憶機能を有するので、ホストコンピュータ H O S T が表示装置 L C D に送るデータは、前回の表示フレームと異なる部分だけで良く、表示に変化がない時は、データを送る必要がないので、ホストコンピュータ H O S T の負担が極めて軽くなる。従って、本発明の表示装置を用いた情報処理装置は低消費電力で、また小型化が容易であり、かつ高速化、多機能化が可能である。20

#### 【 0 0 5 5 】

なお、この携帯型情報端末の表示部 D P の一部にはペンホルダ P N H が設けてあり、ここに入力ペン P N が収納される。液晶表示装置は、キーボード K B を使用した情報の入力と入力ペン P N でタッチパネルの表面を押圧操作したり、なぞり、あるいは記入で種々の情報を入力し、あるいは液晶表示素子 P N L に表示された情報の選択、処理機能の選択、その他の各種操作を可能としてある。30

#### 【 0 0 5 6 】

なお、この種の携帯型情報端末 ( P D A ) の形状や構造は図示したものに限るものではなく、この他に多様な形状、構造および機能を具備したもののが考えられる。また、図 6 の携帯電話機 P T P の表示部に使われる表示装置 L C D 2 に本発明の表示装置を用いることにより、表示素子 L C D 2 に送る表示データの情報量を少なく出来るので、電波や通信回線で送る画像データを少なくすることが出来、携帯電話機の表示部分に多階調かつ高精細の文字や図形、写真表示、さらには動画表示を行うことが出来る。

#### 【 0 0 5 7 】

さらに、本発明の表示装置は、図 6 で説明した携帯型情報端末や携帯電話機のみならず、ディスクトップ型パソコン、ノート型パソコン、投射型液晶表示装置、その他の情報端末のモニター機器に用いることができることは言うまでもない。40

#### 【 0 0 5 8 】

そして、本発明の表示装置は、液晶表示装置に限るものではなく、有機 E L 表示装置やプラズマディスプレイ等のように、マトリックス形の表示装置であればどのようなものにも応用出来る。

#### 【 図面の簡単な説明 】

#### 【 0 0 5 9 】

【 図 1 】本発明の実施例 1 を説明するための液晶表示装置の 1 画素の回路図である。

【 図 2 】電源線 p , n に印加される液晶駆動用の交番電圧の一例を説明する波形図で50

ある。

【図3】本発明の実施例2を説明するための液晶表示装置の1画素の回路図である。

【図4】図1で説明した本発明の実施例1の第1のトランジスタ対のレイアウトを説明する要部平面図である。

【図5】図3で説明した本発明の実施例2の第1のトランジスタ対のレイアウトを説明する要部平面図である。

【図6】本発明による表示装置を実装した電子機器の一例としての携帯型情報端末の構成例を説明する斜視図である。

【図7】各画素に1ビットのスタティックラムを内蔵した低温ポリシリコン薄膜トランジスタ方式の液晶表示装置を構成する液晶パネルの構成例を説明する模式図である。 10

【図8】図7における1ビットSRAM画像メモリの概要を説明する回路図である。

【図9】本出願人の既提案にかかる画像メモリ回路を有する液晶表示装置の1画素の構成例を説明する回路図である。

【図10】図9で説明した単位画素を組合せた面積階調画素の構成例の説明図である。

【図11】本出願人の既提案にかかる画像メモリ回路を有する液晶表示装置の1画素の他の構成例を説明する回路図である。

【図12】カラー表示の階調をRが3ビット、Gが3ビット、Bが2ビットのデータとして256色表示とした場合のカラー1画素の表示領域におけるレイアウトの一例を説明する平面図である。

【符号の説明】 20

【0060】

P X . . . 単位画素(画素電極)、P IX . . . 画素回路、C X . . . カラー画素、D L . . . データ線(ドレイン線、映像信号線)、G L . . . 走査信号線(ゲート線)、V COM . . . コモン電、PNL . . . 薄膜トランジスタパネル(第1基板)、A R . . . 画素部(表示領域)、G DR . . . 垂直走査回路、D DR . . . 水平走査回路、SRAM . . . 画像メモリ、NM1, NM2, NM2 . . . n型MOSトランジスタ、PM1, PM2, PM2 . . . p型MOSトランジスタ、CB . . . 容量、CS . . . 浮遊容量、p, n . . . 電源線(交流電圧(交番電圧))。

20

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 7 0 E

H 0 5 B 33/14 A

(56)参考文献 特開2002-287695(JP,A)

特開平06-102530(JP,A)

特開2001-033760(JP,A)

特開2003-302946(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3