(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4829792号

(P4829792)

(45) 発行日 平成23年12月7日(2011.12.7)

(24) 登録日 平成23年9月22日(2011.9.22)

(51) Int.Cl.

H01L 27/04 (2006.01)

H01L 21/822 (2006.01)

F 1

H01L 27/04

C

請求項の数 14 (全 20 頁)

(21) 出願番号 特願2006-534156 (P2006-534156)

(86) (22) 出願日 平成16年9月30日 (2004.9.30)

(65) 公表番号 特表2007-521661 (P2007-521661A)

(43) 公表日 平成19年8月2日 (2007.8.2)

(86) 國際出願番号 PCT/US2004/032405

(87) 國際公開番号 WO2005/034201

(87) 國際公開日 平成17年4月14日 (2005.4.14)

審査請求日 平成19年9月21日 (2007.9.21)

(31) 優先権主張番号 10/605,444

(32) 優先日 平成15年9月30日 (2003.9.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】電子デバイス及びこれを製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に形成された層間誘電体層と、

前記層間誘電体層内に形成され、該層間誘電体層の上面より下方に凹まれた上面を有する銅製下部電極と、

前記銅製下部電極の上面と直接接し、上面が前記層間誘電体層の前記上面と同一平面にある第1導電性拡散障壁と、

前記第1導電性拡散障壁の上面と直接接する第2導電性拡散障壁と、

前記第2導電性拡散障壁の上面と直接接するMIM誘電体と、

前記MIM誘電体の上面と直接接する上部電極と

を備える電子デバイス。

10

## 【請求項 2】

前記第2導電性拡散障壁が、前記下部電極の少なくとも2つの側部を超えて前記層間誘電体層の前記上面の一部にまで延び、前記MIM誘電体が、前記下部電極の少なくとも2つの側部を超えて延びる、請求項1に記載の電子デバイス。

## 【請求項 3】

前記上部電極が、前記下部電極の少なくとも2つの側部を超えて延びる、請求項1又は請求項2に記載の電子デバイス。

## 【請求項 4】

前記第1及び第2導電性拡散障壁は、5 nmから200 nmまでの厚さのW、Ta、T

20

a N、W N、T a S i N、P t、I r O<sub>2</sub>、又はR u O<sub>2</sub>、或いはそれらの組み合わせを含む、請求項1に記載の電子デバイス。

**【請求項5】**

前記M I M誘電体は、2 nmから20 nmまでの厚さのS i O<sub>2</sub>、S i<sub>3</sub> N<sub>4</sub>又はS i C、T a<sub>2</sub> O<sub>5</sub>、B a T i O<sub>3</sub>、H f O<sub>2</sub>、Z r O<sub>2</sub>又はA l<sub>2</sub> O<sub>3</sub>、或いはこれらの組み合わせ含む、請求項1に記載の電子デバイス。

**【請求項6】**

前記上部電極は、前記M I M誘電体に直接接する下部導体、該下部導体に直接接するコア導体及び該コア導体に直接接する上部導体を有する、請求項1に記載の電子デバイス。

**【請求項7】**

前記下部導体及び前記上部導体は、T i N又はT a Nを含み、前記コア導体は、A 1又はWを含む、請求項6に記載の電子デバイス。

10

**【請求項8】**

電子デバイスを製造する方法であつて、

( a )半導体基板を準備するステップと、

( b )前記半導体基板上に第1層間誘電体層を形成するステップと、

( c )前記第1層間誘電体層内に、該第1層間誘電体層の上面より下方に凹された上面を有する銅製下部電極を形成するステップと、

( d )前記銅製下部電極の上面と直接接し、上面が前記第1層間誘電体層の前記上面と同一平面にある第1導電性拡散障壁を前記第1層間誘電体層に形成するステップと、

( e )前記第1導電性拡散障壁の上面と直接接觸する第2導電性拡散障壁を形成するステップと、

( f )前記第2導電性拡散障壁の前記上面と直接接するようにM I M誘電体を形成するステップと、

( g )前記M I M誘電体の上面と直接接するように上部電極を形成するステップとを含む方法。

20

**【請求項9】**

ステップ(g)の後に、

( h )少なくとも前記上部電極及び前記第1層間誘電体層の全ての露出された面の上に、反応性イオン・エッティング停止層を付着させるステップと、

( i )前記反応性イオン・エッティング停止層に直接接するように、第2層間誘電体層を形成するステップと、

( j )前記上部電極を露出するピアを前記第2層間誘電体層に形成するステップと、

( k )前記ピア内に導体を形成するステップとをさらに含む、請求項8に記載の方法。

30

**【請求項10】**

前記第2導電性拡散障壁が、前記下部電極の少なくとも2つの側部を超えて前記層間誘電体層の前記上面の一部にまで延び、前記M I M誘電体が、前記下部電極の少なくとも2つの側部を超えて延びる、請求項8に記載の方法。

**【請求項11】**

前記上部電極が、前記下部電極の少なくとも2つの側部を超えて延びる、請求項10に記載の方法。

40

**【請求項12】**

前記第1及び第2導電性拡散障壁は、5 nmから200 nmまでの厚さのW、T a、T a N、W N、T a S i N、P t、I r O<sub>2</sub>、又はR u O<sub>2</sub>、或いはこれらの組み合わせを含む、請求項8に記載の方法。

**【請求項13】**

前記M I M誘電体は、2 nmから20 nmまでの厚さのS i O<sub>2</sub>、S i<sub>3</sub> N<sub>4</sub>又はS i C、T a<sub>2</sub> O<sub>5</sub>、B a T i O<sub>3</sub>、H f O<sub>2</sub>、Z r O<sub>2</sub>又はA l<sub>2</sub> O<sub>3</sub>、或いはこれらの組み合わせ含む、請求項8に記載の方法。

**【請求項14】**

50

前記上部電極は、前記MIM誘電体に直接接する下部導体、該下部導体に直接接するコア導体及び該コア導体に直接接する上部導体を有する、請求項8に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体構造体及び処理の分野に関し、より具体的には、高k誘電体材料及び製銅と両立性のある金属・絶縁体・金属(MIM)キャパシタ及びMIMの製造方法に関する。

【背景技術】

【0002】

集積回路、特に無線周波数(RF)及び他の高周波の用途に用いられる集積回路においては、MIMキャパシタが、ますます用いられている。常に高周波数の用途と両立性のある高性能のキャパシタに対する要求は、業界が、MIMキャパシタ内の絶縁体のために高k誘電体材料を使用することを促進した。しかしながら、銅の相互接続を有する集積回路に用いられるとき、高k誘電体は重大な欠点を有し、最も著しくは、銅の拡散に対する耐性が弱く、このことが、歩留まり又は信頼性の問題をもたらすことがある。

【発明の開示】

【発明が解決しようとする課題】

【0003】

したがって、銅相互接続技術と両立性があるMIM構造体及びその製造方法に対する必要性がある。

【課題を解決するための手段】

【0004】

本発明の第1の態様は、半導体基板上に形成された層間誘電体層と、層間誘電体層内に形成され、上面が層間誘電体層の上面と同一平面にある銅製下部電極と、該下部電極の上面と直接接する導電性拡散障壁と、導電性拡散障壁の上面と直接接するMIM誘電体と、MIM誘電体の上面と直接接する上部電極とを含む電子デバイスである。

【0005】

本発明の第2の態様は、半導体基板上に形成された層間誘電体層と、層間誘電体層内に形成された銅製下部電極と、層間誘電体層の上面より下方に凹まされた該下部電極の上面と直接接し、上面が層間誘電体層の上面と同一平面にある導電性拡散障壁と、導電性拡散障壁の上面と直接接するMIM誘電体と、MIM誘電体の上面と直接接する上部電極とを含む電子デバイスである。

【0006】

本発明の第3の態様は、(a)半導体基板を準備することと、(b)半導体基板上に層間誘電体層を形成することと、(c)上面が層間誘電体層の上面と同一平面となるように銅製下部電極を層間誘電体層内に形成することと、(d)該下部電極の上面と直接接するように導電性拡散障壁を形成することと、(e)導電性拡散障壁の上面と直接接するようにMIM誘電体を形成することと、(f)MIM誘電体の上面と直接接するように上部電極を形成することとを含む電子デバイスを製造する方法である。

【0007】

本発明の第4の態様は、(a)半導体基板を準備することと、(b)半導体基板上に層間誘電体層を形成することと、(c)層間誘電体層内に銅製下部電極を形成することと、(d)層間誘電体層の上面より下方に凹まされた該下部電極の上面と直接接し、上面が層間誘電体層の上面と同一平面にある導電性拡散障壁を形成することと、(e)導電性拡散障壁の上面と直接接するようにMIM誘電体を形成することと、(f)MIM誘電体の上面と直接接するように上部電極を形成するステップとを含む電子デバイスを製造する方法である。

【発明を実施するための最良の形態】

【0008】

10

20

30

40

50

本発明の特徴が、添付の特許請求の範囲に述べられている。しかしながら、本発明自体は、添付の図面と併せて読むときに、例証となる実施形態についての次の詳細な説明を参照することによって、最も良く理解されるであろう。

#### 【0009】

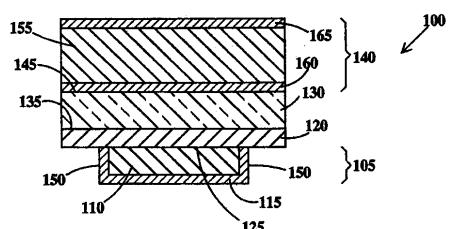

図1は、本発明による例示的なMIMキャパシタ100の断面図である。図1において、MIMキャパシタ100は、銅コア導体110及び導電性ライナ115を含む下部電極105を含む。MIMキャパシタ100は、下部電極105の上面125上に形成された導電性拡散障壁120、該導電性拡散障壁120の上面135上に形成された誘電体層130、及びMIM誘電体130の上面145上に形成された上部電極140をさらに含む。拡散障壁120は、下部電極105からの銅の拡散を防止し、かつ、MIM誘電体130が酸化物を含むときに銅コア導体110が該MIM誘電体130と反応することによってCuOが形成されることも防止するように意図される。上部電極140は、コア導体155、任意の下部導体160、及び任意の上部導体165を含む。図1において、導電性拡散障壁120は、下部電極105の側壁150を超えて延びるが、本発明のありとあらゆる実施形態においてこの特徴が生じるわけではない。下部電極105、導電性拡散障壁120、誘電体130、及び上部電極140の間の幾何学的関係については、本発明の種々の実施形態の各々との関係において下記に説明される。

#### 【0010】

一例において、導電性ライナ115は、Ta、Ta<sub>N</sub>、又はそれらの層の組み合わせを含む。一例において、導電性拡散障壁120は、W、Ta、又はTa<sub>N</sub>のような高融点金属、WN、Ta<sub>N</sub>、TaSiN、Pt、IrO<sub>2</sub>、又はRuO<sub>2</sub>のような導電性材料、或いはこれらの層の組み合わせでできた約5nmから200nmまでの厚さの層を含む。一例において、MIM誘電体130は、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>又はSiC、Ta<sub>2</sub>O<sub>5</sub>、BaTiO<sub>3</sub>、HfO<sub>2</sub>、ZrO<sub>2</sub>、又はAl<sub>2</sub>O<sub>3</sub>のような高k誘電体、或いはこれらの層の組み合わせでできた約2nmから20nmまでの厚さの層を含む。一例において、上部電極140は、約50nmから300nmまでの厚さを有し、上部電極140のコア導体155は、Al又はWを含み、下部導体160及び上部導体165は、TiN又はTa<sub>N</sub>を含む。MIMキャパシタにおいて、本発明の全ての実施形態が、これらの材料を用いる。

#### 【0011】

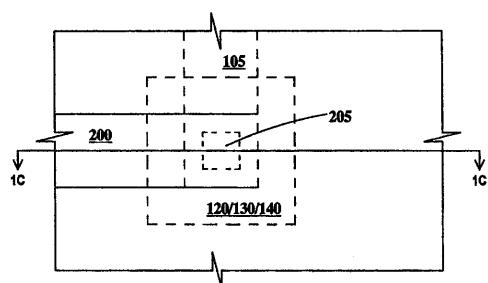

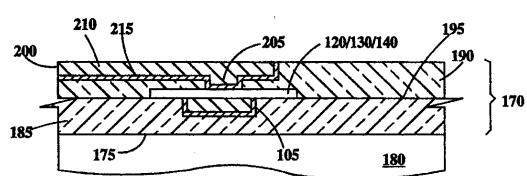

図2は、本発明によるMIMキャパシタを組み込む相互接続構造体の平面図であり、図3は、図2の線1C-1Cを通る断面図である。図2及び図3は、ダマシン配線レベルの集積回路デバイスに本発明のMIMキャパシタを統合する例示的なものである。例示的な層間誘電体(ILD)スタック170が、半導体基板180の上面175上に形成される。ILDスタック170は、基板180の上面175上に形成された第1のILD185と、第1のILD185の上面195上に形成された第2のILD190とを含む。下部電極105が、第1のILD185内に形成される。下部電極105は、MIMへの電気配線接続としても働く。導電性拡散障壁120、誘電体130、及び上部電極140が、第2のILD190内に形成される。ビア205を通して、MIMキャパシタの上部プレート140に電気的に接続させるための導体200も、第2のILD195内に形成される。導体200及びビア205は、銅コア210及び導電性ライナ215を含む。

#### 【0012】

2つのILDレベルが図3に示されているが、集積回路デバイスにおいて、如何なる数のILDレベルを用いることもでき、いずれの2つの隣接するILDレベル内にMIMキャパシタを物理的に配置することができ、下部電極は、2つのILDレベルの下部内にあり、MIM誘電体及び上部電極は、該2つのILDレベルの上部にある。導電性拡散障壁は、上部ILDレベル又は下部ILDレベルのいずれか、或いはその両方内に配置することができる。ILD材料の例は、テトラエトキシシラン(TEOS)、フッ素化酸化シリコン・ガラス(FSG)、及び他の化学気相成長(CVD)酸化物のような付着された酸化物を含む。

10

20

30

40

50

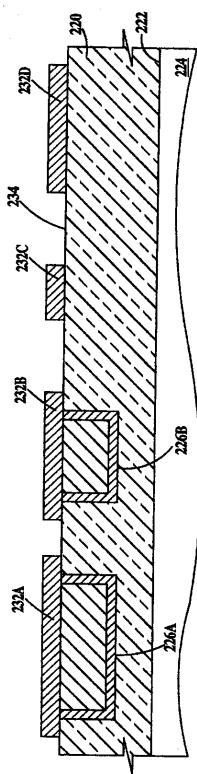

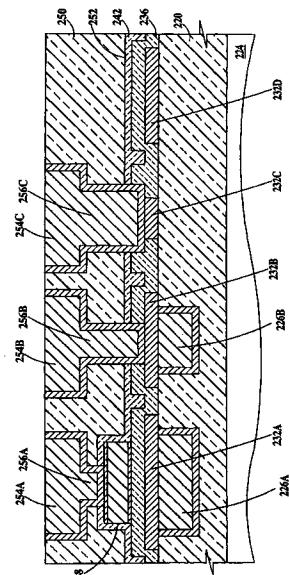

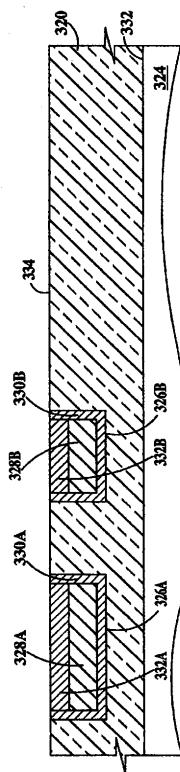

## 【0013】

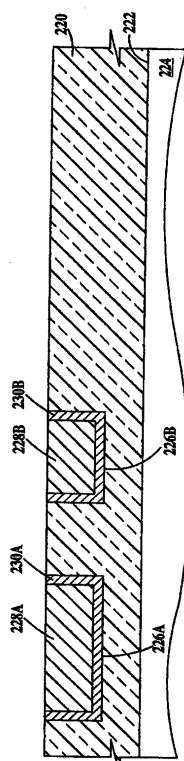

図4乃至図9は、本発明の第1の実施形態によるMIMキャパシタの製造を示す断面図である。図4において、ILD220が、半導体基板224の上面222上に形成される。下部電極226A及び導体226Bが、ILD220内に形成される。下部電極226Aは、銅コア導体228A及び導電性ライナ230Aを含む。導体226Bは、銅コア導体228B及び導電性ライナ230Bを含む。導電性ライナ及びILD材料については、上に説明された。下部電極226A及び導体226Bは、ダマシン法によって形成される。ダマシン法において、ILDの上に適用されるマスク層を光リソグラフィによりパターン加工し、ILDの反応性イオン・エッチング(RIE)を行い、マスク層を取り除き、導電性ライナを付着させ、銅シード層の付着物を付着させ、銅めっきしてトレンチを充填し、化学機械研磨(CMP)プロセスを行い、銅、導電性ライナ、及びILDの上面を同一平面にすることによって、トレンチが形成される。下部電極226Aは、MIMキャパシタの下部電極になり、導体226Bは、一般的な相互接続導体である。10

## 【0014】

図5において、導電性拡散障壁層が付着され、光リソグラフィによりパターン加工され、RIEプロセスが行われ、ILD220の上面234上に、導電性拡散障壁232A及び232B、抵抗体232C、並びに位置合わせマーク232Dを形成する。導電性拡散障壁232A及び232Bは、それぞれ第1の導体226A及び第2の導体226Bと重なることに留意されたい。導電性拡散障壁の材料及び厚さについては、上に説明された。20

## 【0015】

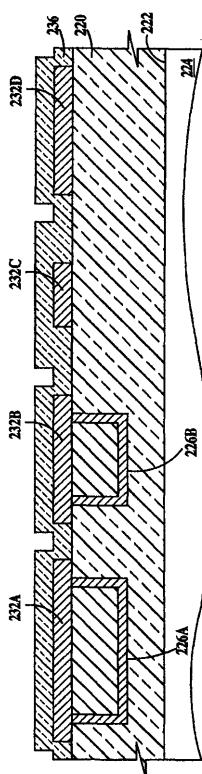

図6において、プランケットMIM誘電体層236が付着される。MIM誘電体の材料及び厚さについては、上に説明された。

## 【0016】

図7において、導体が付着され、光リソグラフィによりパターン加工され、RIEエッチングされ、MIM誘電体層236の上面240上に上部電極238を形成する。上部電極238が、導電性拡散障壁232A及び下部電極226Aの上に位置合わせされる。上部電極238は、導電性拡散障壁232Aと消極的に重なる(すなわち、該導電性拡散障壁232Aより小さい)。上部電極の材料及び厚さについては、上に説明された。

## 【0017】

図8において、任意のRIE停止層242が、MIM誘電体層236の上面240上、並びに上部電極238の上面246及び側壁248上に付着される。一例において、RIE停止層242は、約5nmから50nmまでの厚さを有し、Si<sub>3</sub>N<sub>4</sub>を含む。30

## 【0018】

図9において、第2のILD層250が、RIE停止層242の上面252上に付着される。RIE停止層242を通して、上部電極238、導体226B、及び抵抗体232Cと電気的に接触するように、それぞれ一体のビア256Aを有する導体254A、一体のビア256Bを有する導体254B、及び一体のビア256Cを有する導体254Cが形成される。導体254A、254B、及び254Cは、デュアル・ダマシン法によって形成される。デュアル・ダマシン法においては、ILDの上に適用される第1のマスク層を光リソグラフィによりパターン加工し、ILDのRIEを行い、ILD内にトレンチをエッチングし、第1のマスク層を取り除き、ILD及びトレンチの上に適用される第2のマスク層を光リソグラフィによりパターン加工し、ILDのRIEを行い、トレンチの下部内にビアをエッチングし、第2のマスク層を取り除き、導電性ライナを付着させ、銅シード層の付着物を付着させ、銅めっきしてトレンチを充填し、CMPプロセスを行い、銅、導電性ライナ、及びILDの上面を同一平面にすることによって、ILD内に導体が形成される。40

## 【0019】

2つのILDレベルが図9に示されているが、集積回路デバイスにおいて、如何なる数のILDレベルを用いることもでき、いずれの2つの隣接するILDレベル内にMIMキャパシタを物理的に配置することができ、下部電極は、2つのILDレベルの下部内にあ50

り、導電性拡散障壁、MIM誘電体、及び上部電極は、該2つのILDレベルの上部内にある。

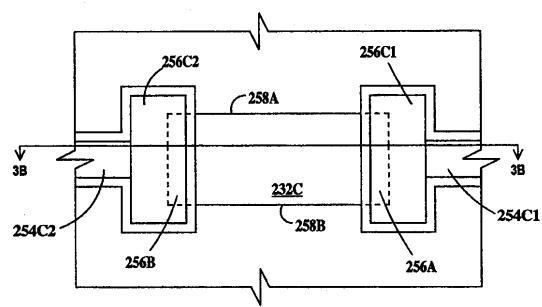

#### 【0020】

図10は、本発明による抵抗体232Cへのコンタクトの平面図であり、図11は、図10の線3B-3Bを通る断面図である。第1の導体254C1は、抵抗体232Cの第1端部256Aと電気的に接触し、第2の導体254C2は、該抵抗体の第2端部256Bと電気的に接触する。ビア256C1及び256C2は、それぞれ端部256A及び256B、並びに抵抗体232Cの両端部に隣接する側部258A及び258Bの一部と重なる。

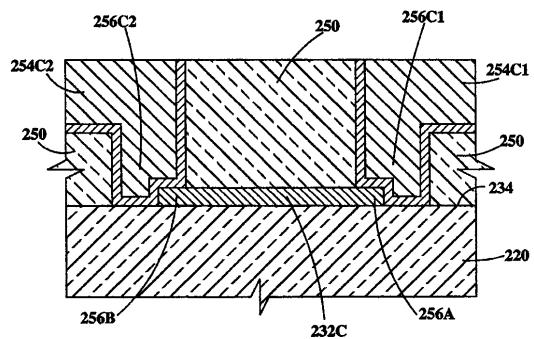

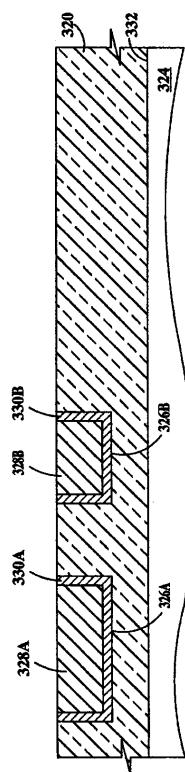

#### 【0021】

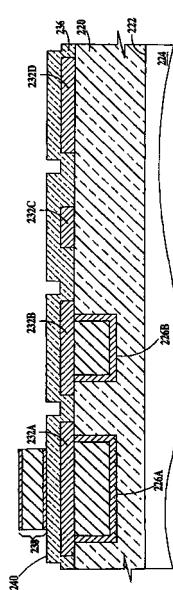

図12乃至図16は、本発明の第2の実施形態によるMIMキャパシタの製造を示す断面図である。図12において、ILD320が、半導体基板324の上面332上に形成される。下部電極326A及び導体326Bが、ILD320内に形成される。下部電極326Aは、銅コア導体328A及び導電性ライナ330Aを含む。導体326Bは、銅コア導体328B及び導電性ライナ330Bを含む。導電性ライナ及びILDの材料については、上に説明された。上述のように、下部電極326A及び導体326Bは、ダマシン法によって形成される。下部電極326Aは、MIMキャパシタの下部電極になり、導体326Bは、一般的な相互接続導体である。

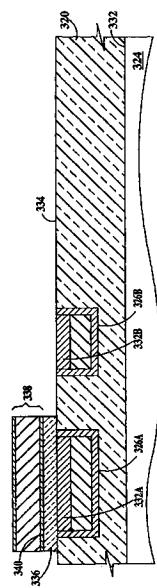

#### 【0022】

図13において、乾式プロセス又はRIEプロセスによって、コア導体328A及び328Bが凹まされる。ILD320上に、コア・エッティング・プロセスによって形成された凹部を充填するのに十分な厚さの導電性拡散障壁層が付着され、CMPを行い、凹まれた導電性拡散障壁332A及び332Bを形成し、該導電性拡散障壁をILD320の上面334と同一平面にする。拡散障壁の材料については、上に説明された。

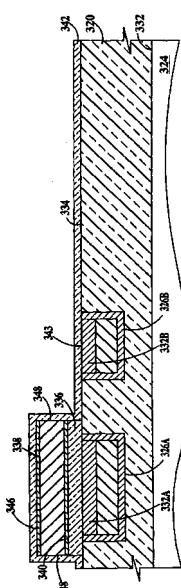

#### 【0023】

図14において、MIM誘電体336及び上部電極338（該MIM誘電体の上面上の）が、MIM誘電体層をILD320の上面334上、及び、導電性拡散障壁326A及び326Bの上に付着させ、導電性層を該MIM誘電体層の上面の上に付着させ、該導電性層の上に適用されるマスク層を光リソグラフィによりパターン加工し、該MIM誘電体336及び上部電極338の範囲を画定し、該MIM誘電体層及び該導電性層のRIEを行い、マスク層を取り除くことによって形成される。上部電極338が、凹まれた導電性拡散障壁332A及び下部電極326Aの上に位置合わせされる。上部電極338は、凹まれた導電性拡散障壁332Aと積極的に重なる（すなわち、該導電性拡散障壁332Aより大きい）。導電性拡散障壁の材料及び厚さ、MIM誘電体の材料及び厚さ、並びに上部電極の材料及び厚さについては、上に説明された。

#### 【0024】

図15において、任意のRIE停止層342が、上部電極338の上面346及び側壁338、ILD320の露出された上面334、並びに凹まれた導電性拡散障壁332Bの上面343上に付着される。一例において、RIE停止層342は、約5nmから50nmまでの厚さを有し、Si<sub>3</sub>N<sub>4</sub>を含む。

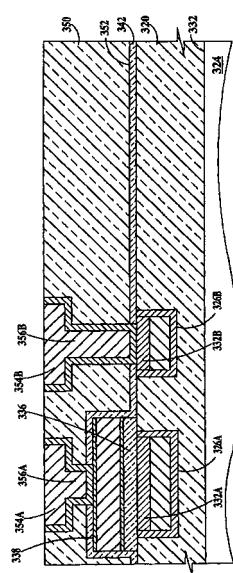

#### 【0025】

図16において、第2のILD層350が、RIE停止層342の上面352上に付着される。RIE停止層342を通して、上部電極338及び凹まれた導電性拡散障壁332Bと電気的に接触するように、それぞれ一体のビア356Aを有する導体354A及び一体のビア356Bを有する導体354Bが形成される。上述のように、デュアル・ダマシン法によって、導体354A及び354Bが形成される。

#### 【0026】

2つのILDレベルが図16に示されているが、集積回路デバイスにおいて、如何なる数のILDレベルを用いることもでき、いずれの2つの隣接するILDレベル内にMIMキャパシタを物理的に配置することができ、下部電極は、2つのILDレベルの下部内に

あり、導電性拡散障壁、MIM誘電体、及び上部電極は、該2つのILDレベルの上部内にある。

#### 【0027】

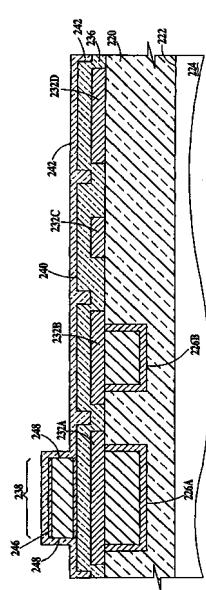

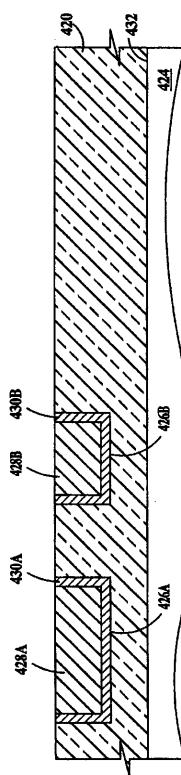

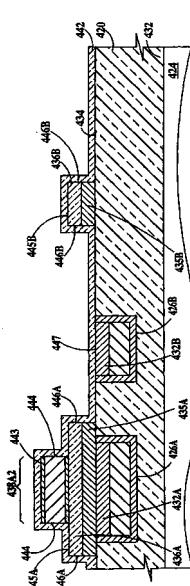

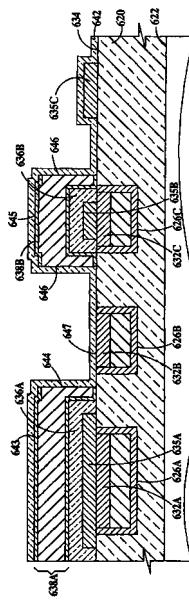

図17乃至図22は、本発明の第3の実施形態によるMIMキャパシタの製造を示す断面図である。図17において、ILD420が、半導体基板424の上面432上に形成される。下部電極426A及び導体426Bが、ILD420内に形成される。下部電極426Aは、銅コア導体428A及び導電性ライナ430Aを含む。導体426Bは、銅コア導体428B及び導電性ライナ430Bを含む。導電性ライナ及びILDの材料については、上に説明された。上述のように、下部電極426A及び導体426Bは、ダマシン法によって形成される。下部電極426Aは、MIMキャパシタの下部電極になり、導体426Bは、一般的な相互接続導体である。

10

#### 【0028】

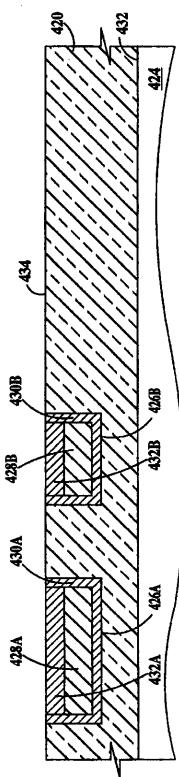

図18において、乾式プロセス又はRIEプロセスによって、コア導体428A及び428Bが凹まされる。ILD420上に、エッチング・プロセスによって形成された凹部を充填するのに十分な厚さの第1の導電性拡散障壁層が付着され、CMPプロセスを行い、凹まされた導電性拡散障壁432A及び432Bを形成し、該凹まされた導電性拡散障壁をILD420の上面434と同一平面にする。導電性拡散障壁の材料及び厚さについては、上に説明された。

#### 【0029】

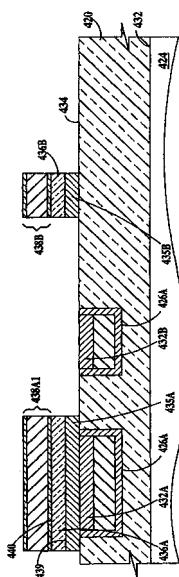

図19において、上部導電性拡散障壁435A、抵抗体435B、MIM誘電体436A、上部電極438A1（該MIM誘電体の上面440上の）、及びキャップ438Bが、次のように形成される。すなわち、第1に、第2の導電性拡散障壁層が、ILD420の上面434上、及び、凹まされた導電性拡散障壁432A及び432Bの上に付着される。第2に、MIM誘電体層が第2の導電性拡散障壁層の上面に付着され、導電性層が該第2の導電性拡散障壁層の上面に付着される。第3に、導電性層の上に適用されるマスク層が、光リソグラフィによりパターン加工され、MIM誘電体436Aの範囲、上部導電性拡散障壁435A及び抵抗体435Bの範囲、上部電極438A1の初期範囲、及びキャップ438Bの範囲を画定する。第4に、MIM誘電体層、第2の導電性拡散障壁層、及び導電性層のRIEが行われ、マスク層が取り除かれる。導電性拡散障壁の材料及び厚さについては、上に説明された。

20

30

#### 【0030】

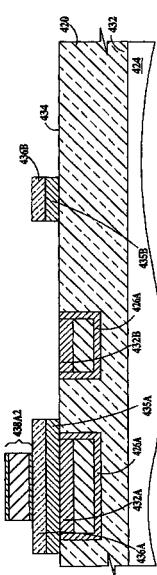

図20において、適用されるマスク層が光リソグラフィによりパターン加工され、RIEが行われ、上部電極438A2の最終範囲を画定し、キャップ438B（図19を参照されたい）をMIM誘電体436Bの上から取り除く。次に、マスク層が取り除かれる。上部電極438A2が、凹まされた導電性拡散障壁432A、上部導電性拡散障壁435A、及び下部電極426Aの上に位置合わせされる。上部電極438A2は、上部導電性拡散障壁435Aと消極的に重なる（すなわち、該上部導電性拡散障壁435Aより小さい）。上部導電性拡散障壁435Aは、凹まされた導電性拡散障壁432Aと積極的に重なる（すなわち、該凹まされた導電性拡散障壁432Aより大きい）。MIM誘電体の材料及び厚さ、並びに上部電極の材料及び厚さについては、上に説明された。

40

#### 【0031】

図21において、任意のRIE停止層442が、上部電極438A2の上面443及び側壁444、MIM誘電体436A / 上部導電性拡散障壁435Aの上面445A及び側壁446A、MIM誘電体436B / 抵抗体435Bの上面445B及び側壁446B、ILD420の露出された上面434、並びに凹まされた導電性拡散障壁432Bの上面447上に付着される。一例において、RIE停止層442は、約5nmから50nmまでの厚さを有し、Si<sub>3</sub>N<sub>4</sub>を含む。

#### 【0032】

図22において、第2のILD層450が、RIE停止層442の上面452上に付着される。RIE停止層442を通して、上部電極438A2、凹まされた導電性拡散障壁

50

432B、及び抵抗体435Bと電気的に接触するように、それぞれ一体のビア456Aを有する導体454A、一体のビア456Bを有する導体454B、及び一体のビア456Cを有する導体454Cが形成される。上述のように、デュアル・ダマシン法によって、導体454A及び454Bが形成される。2つのILDレベルが図22に示されているが、集積回路デバイスにおいて、如何なる数のILDレベルを用いることもでき、いずれの2つの隣接するILDレベル内にMIMキャパシタを物理的に配置することができ、下部電極は、2つのILDレベルの下部内にあり、導電性拡散障壁、MIM誘電体、及び上部電極は、該2つのILDレベルの上部内にある。

### 【0033】

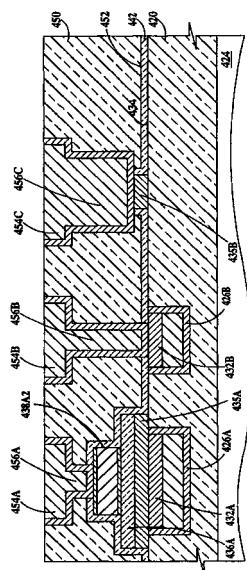

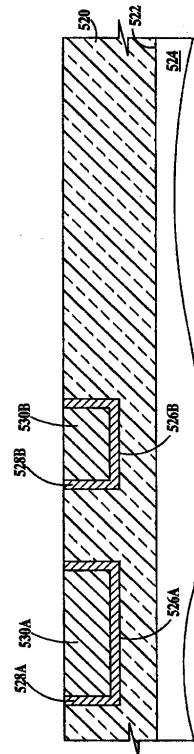

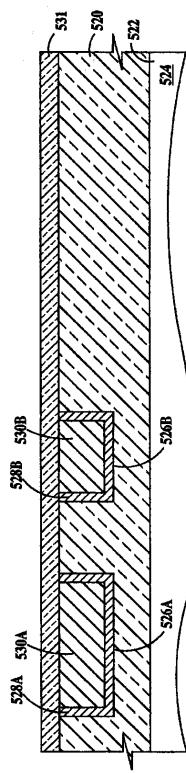

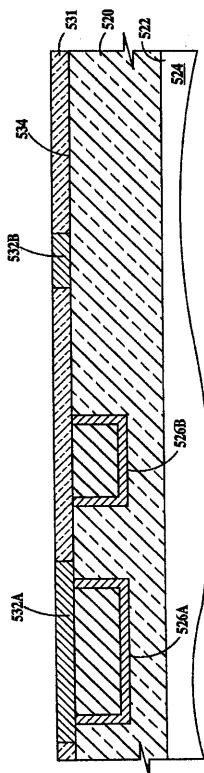

図23乃至図28は、本発明の第4の実施形態によるMIMキャパシタの製造を示す断面図である。図23において、ILD520が、半導体基板524の上面522上に形成される。下部電極526A及び導体526Bが、ILD520内に形成される。下部電極526Aは、銅コア導体528A及び導電性ライナ530Aを含む。導体526Bは、銅コア導体528B及び導電性ライナ530Bを含む。導電性ライナ及びILDの材料については、上に説明された。上述のように、ダマシン法によって、下部電極526A及び導体526Bが形成される。下部電極526Aは、MIMキャパシタの下部電極になり、導体526Bは、一般的な相互接続導体である。

### 【0034】

図24において、付着によって、ILD520、下部電極526A、及び導体526Bの上部に、誘電体拡散障壁層531が形成される。誘電体拡散障壁層531についての適切な材料の例は、 $\text{Si}_3\text{N}_4$ 、 $\text{SiC}$ 、 $\text{Si}_3\text{N}_4$ の上の $\text{SiO}_2$ 、及び $\text{Si}_3\text{N}_4$ の上のFSGを含み、約5nmから50nmまでの厚さを有する。

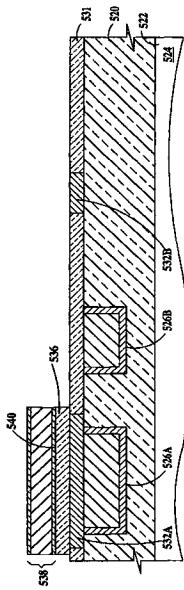

### 【0035】

図25において、上述のように、ダマシン法によって、導電性拡散障壁532Aが、下部電極526Aの上に形成され、(かつILD520と重なっており)、抵抗体532Bが、ILD520の上面534上に形成される。拡散障壁の材料及び厚さについては、上に説明された。

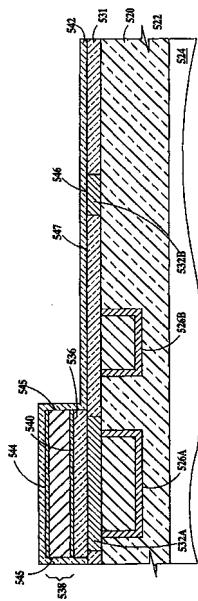

### 【0036】

図26において、最初にMIM誘電体層が、次に導電性層が付着され、光リソグラフィによりパターン加工され、RIEエッチングされ、上部電極538をMIM誘電体536の上面540上に形成する。上部電極538は、導電性拡散障壁532A及び下部電極526Aの上に位置合わせされる。上部電極538は、導電性拡散障壁532Aと積極的に重なる(すなわち、該導電性拡散障壁532Aより大きい)。導電性拡散障壁532Aは、下部電極526Aと積極的に重なる(すなわち、該下部電極526Aより大きい)。MIM誘電体の材料及び厚さ、並びに上部電極の材料及び厚さについては、上に説明された。

### 【0037】

図27において、任意のRIE停止層542が、上部電極538の上面544、上部電極538/MIM誘電体536の側壁545、抵抗体532Bの上面546、及び誘電体拡散障壁531の上面547上に付着される。一例において、RIE停止層542は、約5nmから50nmまでの厚さを有し、 $\text{Si}_3\text{N}_4$ を含む。

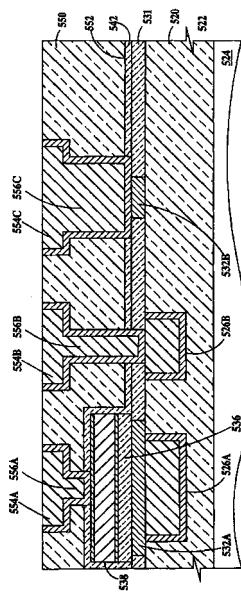

### 【0038】

図28において、第2のILD層550が、RIE停止層542の上面552上に付着される。RIE停止層542を通して、上部電極538、導体526B、及び抵抗体532Bと電気的に接触するように、それぞれ一体のビア556Aを有する導体554A、一体のビア556Bを有する導体554B、及び一体のビア556Cを有する導体554Cが形成される。上述のように、デュアル・ダマシン法によって、導体554A、554B、及び554Cが形成される。

### 【0039】

2つのILDレベルが図28に示されているが、集積回路デバイスにおいて、如何なる

10

20

30

40

50

数のILDレベルを用いることもでき、いずれの2つの隣接するILDレベル内にMIMキャパシタを物理的に配置することができ、下部電極は、2つのILDレベルの下部内にあり、導電性拡散障壁、MIM誘電体、及び上部電極は、該2つのILDレベルの上部内にある。

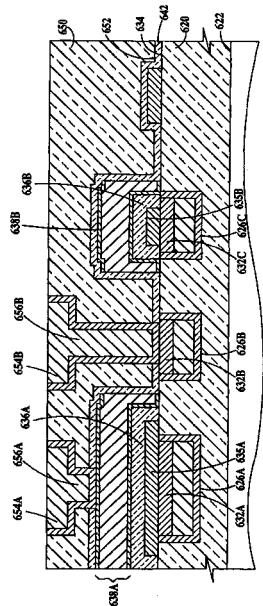

#### 【0040】

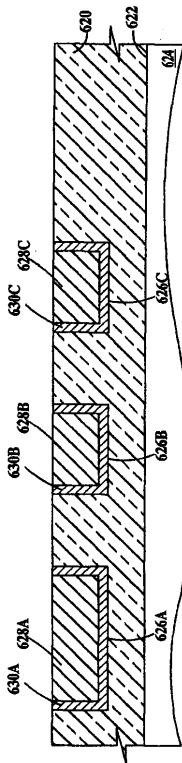

図29乃至図34は、本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。図29において、ILD620が、半導体基板624の上面622上に形成される。下部電極626A、導体626B、及び抵抗体コンタクト626Cが、ILD620内に形成される。下部電極626Aは、銅コア導体628A及び導電性ライナ630Aを含む。導体626Bは、銅コア導体628B及び導電性ライナ630Bを含む。抵抗体コンタクト626Cは、銅コア導体628C及び導電性ライナ630Cを含む。10導電性ライナ及びILDの材料については、上に説明された。上述のように、ダマシン法によって、下部電極626A、導体626B、及び抵抗体コンタクト626Cが形成される。下部電極626Aは、MIMの下部電極になり、導体626Bは、一般的な相互接続導体である。

#### 【0041】

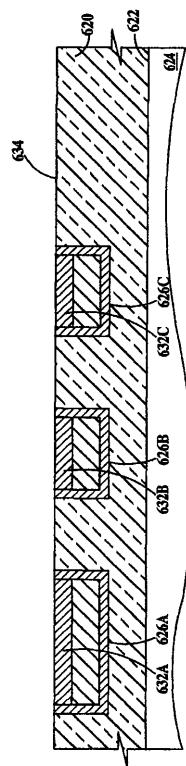

図30において、乾式プロセス又はRIEプロセスによって、コア導体628A、628B、及び628Cが凹まされ、ILD620上に、エッティング・プロセスによって形成された凹部を充填するのに十分な厚さの第1の導電性拡散障壁層が付着され、CMPプロセスを行い、凹まされた導電性拡散障壁632A、632B、及び632Cを形成し、該凹まされた導電性拡散障壁をILD620の上面634と同一平面にする。導電性拡散障壁の材料及び厚さについては、上に説明された。20

#### 【0042】

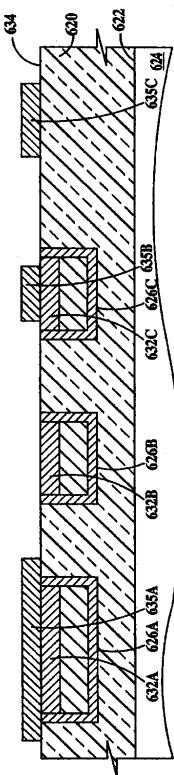

図31において、導電性拡散障壁層をILD620の上面634上に付着させ、該導電性拡散障壁層に適用されるマスク層を光リソグラフィによりパターン加工し、RIEプロセスを行い、該マスク層を取り除くことによって、上部導電性拡散障壁635A、抵抗体635B、及び位置合わせマーク635Cが形成される。導電性拡散障壁の材料及び厚さについては、上に説明された。

#### 【0043】

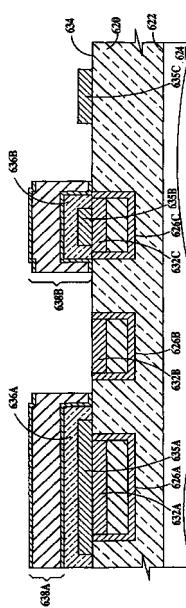

図32において、上部導電性拡散障壁635Aを覆うMIM誘電体636A、MIM誘電体636Aを覆う上部電極638A、抵抗体635Bを覆う誘電体キャップ636B、誘電体キャップ636Bを覆う導電性キャップ638Bが、次のように形成される。すなわち、第1に、MIM誘電体層が、導電性拡散障壁635A、抵抗体635B、位置合わせマーク635C、及びILD620の露出された上面634の上に付着される。第2に、マスク層がMIM誘電体層の上に適用され、光リソグラフィによりパターン加工され、MIM誘電体635A及び636Bの範囲を画定し、MIM誘電体層のRIEが行われ、マスク層が取り除かれる。第3に、導電性層が、MIM誘電体636A及び636B、位置合わせマーク635C、並びにILD620の露出された上面634の上に付着される。第4に、マスク層が導電性層の上に適用され、上部電極638A及び導電性キャップ636Bの範囲を画定し、該導電性層のRIEが行われ、マスク層が取り除かれる。上部電極638は、MIM誘電体636Aの上に位置合わせされ、MIM誘電体は、上部導電性拡散障壁635A及び下部電極626Aの上に位置合わせされる。上部電極638Aは、MIM誘電体636Aと積極的に重なり（すなわち、該MIM誘電体636Aより大きい）、MIM誘電体636Aは、上部導電性拡散障壁635Aと積極的に重なる（すなわち、該上部導電性拡散障壁635Aより大きい）。MIM誘電体の材料及び厚さ、並びに上部電極の材料及び厚さについては、上に説明された。3040

#### 【0044】

図33において、任意のRIE停止層642が、上部電極638Aの上面643及び側壁644、導電性キャップ636Bの上面645及び側壁646、ILD620の露出された上面634、凹まされた導電性拡散障壁632Bの上面647上、並びに位置合わせ

マーク 635C の上に付着される。一例において、RIE 停止層 642 は、約 5 nm から 50 nm までの厚さを有し、Si<sub>3</sub>N<sub>4</sub> を含む。

#### 【0045】

図 34において、第 2 の ILD 層 650 が、RIE 停止層 642 の上面 652 上に付着される。RIE 停止層 642 を通して、上部電極 638A 及び凹まされた導電性拡散障壁 632B と電気的に接触するように、それぞれ一体のビア 656A を有する導体 654A 及び一体のビア 656B を有する導体 654B が形成される。上述のように、デュアル・ダマシン法によって、導体 654A 及び 654B が形成される。

#### 【0046】

2つのILD レベルが図 34 に示されているが、集積回路デバイスにおいて、如何なる数のILD レベルを用いてもよく、いずれの 2 つの隣接する ILD レベル内に MIM キャパシタを物理的に配置することができ、下部電極は、2 つの ILD レベルの下部内にあり、導電性拡散障壁、MIM 誘電体、及び上部電極は、該 2 つの ILD レベルの上部内にある。

#### 【0047】

このように、本発明は、銅相互接続技術と両立性があり、抵抗体及び位置合わせマーク構造体とも両立性がある MIM 構造体及びその製造方法を提供するものである。

#### 【0048】

本発明の理解のために、本発明の実施形態の説明が上に与えられる。本発明は、ここに説明される特定の実施形態に制限されるものでなく、本発明の範囲から逸脱することなく、ここで当業者には明らかになるような種々の修正、再構成、及び置換が可能であることが理解されるであろう。したがって、上記の特許請求の範囲は、本発明の真の精神及び範囲内に含まれるような、こうした全ての修正及び変更を網羅することが意図される。

#### 【図面の簡単な説明】

#### 【0049】

【図 1】本発明による例示的な MIM キャパシタの断面図である。

【図 2】本発明による MIM キャパシタを組み込む相互接続構造体の平面図である。

【図 3】図 2 の線 1C - 1C を通る断面図である。

【図 4】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 5】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 6】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 7】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 8】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 9】本発明の第 1 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 10】本発明による抵抗体へのコントクトの平面図である。

【図 11】図 10 の線 3B - 3B を通る断面図である。

【図 12】本発明の第 2 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 13】本発明の第 2 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 14】本発明の第 2 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 15】本発明の第 2 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 16】本発明の第 2 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 17】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 18】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 19】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 20】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 21】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 22】本発明の第 3 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 23】本発明の第 4 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 24】本発明の第 4 の実施形態による MIM キャパシタの製造を示す断面図である。

【図 25】本発明の第 4 の実施形態による MIM キャパシタの製造を示す断面図である。

10

20

30

40

50

- 【図26】本発明の第4の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図27】本発明の第4の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図28】本発明の第4の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図29】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図30】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図31】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図32】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図33】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

- 【図34】本発明の第5の実施形態によるMIMキャパシタの製造を示す断面図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 クールバウフ、ダグラス、ディー

アメリカ合衆国 05452 バーモント州 エセックス・ジャンクション セージ・サークル

21

(72)発明者 エーシュン、エベンザー、イー

アメリカ合衆国 05452 バーモント州 エセックス・ジャンクション パール・ストリート

96 #5

(72)発明者 ガンビーノ、ジェフリー、ピー

アメリカ合衆国 05494 バーモント州 ウエストフォードハントレイ・ロード 98

(72)発明者 ホー、チョン、シャン

アメリカ合衆国 05452 バーモント州 エセックス・ジャンクション タマラック・ドライブ

25

(72)発明者 ラマチャンドラン、ヴェーダ

アメリカ合衆国 10562 ニューヨーク州 オシニング スプリング・ストリート 80 #

3A

審査官 大嶋 洋一

(56)参考文献 特開2003-060081(JP, A)

特開2003-051501(JP, A)

特表2002-026018(JP, A)

特開2001-313372(JP, A)

特開2001-308280(JP, A)

特開2001-237375(JP, A)

特開2000-332203(JP, A)

特開平07-307338(JP, A)

国際公開第2003/021661(WO, A1)

米国特許第06583491(US, B1)

米国特許第06338999(US, B1)

米国特許出願公開第2003/0072899(US, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04