(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2023-161435

(P2023-161435A)

(43)公開日 令和5年11月7日(2023.11.7)

## (51)国際特許分類

G 09 F 9/30 (2006.01)

H 10 K 50/10 (2023.01)

H 10 K 59/10 (2023.01)

H 05 B 33/02 (2006.01)

F I

G 09 F 9/30

G 09 F 9/30

H 05 B 33/14

H 01 L 27/32

H 05 B 33/02

テーマコード(参考)

3 K 1 0 7

5 C 0 9 4

A

審査請求 未請求 請求項の数 7 O L (全25頁)

(21)出願番号

特願2022-71830(P2022-71830)

(22)出願日

令和4年4月25日(2022.4.25)

(71)出願人

000002369

セイコーホーム株式会社

東京都新宿区新宿四丁目1番6号

(74)代理人

100149548

弁理士 松沼 泰史

(74)代理人

100140774

弁理士 大浪 一徳

(74)代理人

100114937

弁理士 松本 裕幸

(74)代理人

100196058

弁理士 佐藤 彰雄

(72)発明者

窪田 岳彦

長野県諏訪市大和3丁目3番5号 セイ

コーホーム株式会社内

Fターム(参考) 3K107 AA01 BB01 CC31 DD14

最終頁に続く

## (54)【発明の名称】 電気光学装置及び画像表示装置

## (57)【要約】

【課題】有機ELパネルの微細化に伴うクロストーク及び画像のちらつきを低減する。

【解決手段】本発明の電気光学装置は、第1電極と発光層と第2電極とを含む発光素子と、前記発光素子に対応して設けられる駆動トランジスターと、前記駆動トランジスターのゲート電極と電気的に接続され、前記ゲート電極と前記発光素子の前記第1電極との間の層に設けられる中継電極と、前記中継電極と同一層に設けられ、平面視において第1の方向に延在し、前記発光素子の前記第1電極と電気的に接続される電源配線と、平面視において前記中継電極と前記電源配線との間に設けられ、定電位が供給される導電部材と、を備える。

【選択図】図5

10

20

**【特許請求の範囲】****【請求項 1】**

第1電極と発光層と第2電極とを含む発光素子と、

前記発光素子に対応して設けられる駆動トランジスターと、

前記駆動トランジスターのゲート電極と電気的に接続され、前記ゲート電極と前記発光素子の前記第1電極との間の層に設けられる中継電極と、

前記中継電極と同一層に設けられ、平面視において第1の方向に延在し、前記発光素子の前記第1電極と電気的に接続される電源配線と、

平面視において前記中継電極と前記電源配線との間に設けられ、定電位が供給される導電部材と、

を備える、

電気光学装置。

**【請求項 2】**

半導体基板に不純物を含む拡散領域を含み、

前記導電部材は、前記拡散領域に電気的に接続されている、

請求項1に記載の電気光学装置。

**【請求項 3】**

前記中継電極は、平面視で前記導電部材によって囲まれている、

請求項2に記載の電気光学装置。

**【請求項 4】**

前記中継電極は、平面視で絶縁層を介して前記導電部材と隣り合って設けられている、

請求項3に記載の電気光学装置。

10

20

**【請求項 5】**

前記導電部材の少なくとも一部は、平面視で前記ゲート電極と重なっている、

請求項1又は2に記載の電気光学装置。

**【請求項 6】**

前記発光素子は有機発光ダイオードである、

請求項1から4の何れか一項に記載の電気光学装置。

**【請求項 7】**

請求項1から4の何れか一項に記載の電気光学装置と、

前記電気光学装置から射出された画像光を表示する光学系と、

を備える、

画像表示装置。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電気光学装置及び画像表示装置に関する。

**【背景技術】****【0002】**

近年、有機発光ダイオード(Organic Light Emitting Diode; OLED)を用いて画像を表示する有機EL(Electro-Luminescence)パネル(電気光学装置)が開発され、ヘッドマウントディスプレイやプロジェクターを含む画像表示装置への有機ELパネルの適用が検討されている。有機ELパネルは画像生成領域を有し、画像生成領域には画像を生成するための複数の画素に対応する複数の画素回路がマトリクス状に設けられている。また、画像生成領域には複数の画素回路を駆動するための複数の走査線とこれらの走査線に直交する複数のデータ線が設けられ、走査線とデータ線との交差領域に画素回路が構成されている。

40

**【0003】**

例えば、特許文献1には、画素回路の駆動トランジスターのゲート電極と電気的に接続された中継ノード(中継電極)と、OLED(発光素子)の陽極側の回路に設けられた給

50

電線（電源配線）とを備える電気光学装置が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2013-213979号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述の特許文献1に開示されている電気光学装置では、パネルの微細化が進むと、画素回路のトランジスターのゲート電極と電気的に接続される中継ノードとOLEDの陽極側の給電線との間隔が狭くなり、中継モードと給電線との間で寄生容量が発生する。このような状況において、画素回路に供給される制御信号のレベルの切り替えによってトランジスターのゲートへの電位、すなわち中継ノードの電位が変化すると、中継ノードと給電線との間での寄生容量の影響によって電気配線に流れる電流値が変化し、クロストークの要因となる。その結果、電気光学装置から出力される画像にちらつきが目立つ虞があった。

10

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本発明の一つの態様の電気光学装置は、第1電極と発光層と第2電極とを含む発光素子と、前記発光素子に対応して設けられる駆動トランジスターと、前記駆動トランジスターのゲート電極と電気的に接続され、前記ゲート電極と前記発光素子の前記第1電極との間に層に設けられる中継電極と、前記中継電極と同一層に設けられ、平面視において第1の方向に延在し、前記発光素子の前記第1電極と電気的に接続される電源配線と、平面視において前記中継電極と前記電源配線との間に設けられ、定電位が供給される導電部材と、を備える。

20

【図面の簡単な説明】

【0007】

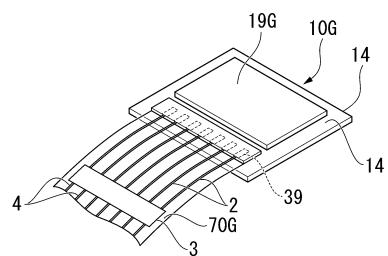

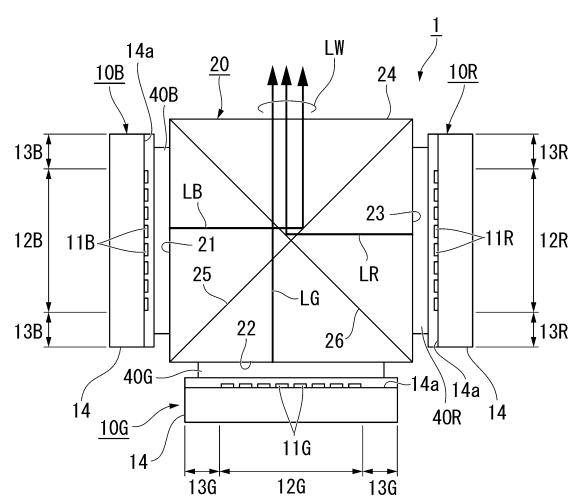

【図1】第1実施形態の電気光学装置の構成を示す斜視図である。

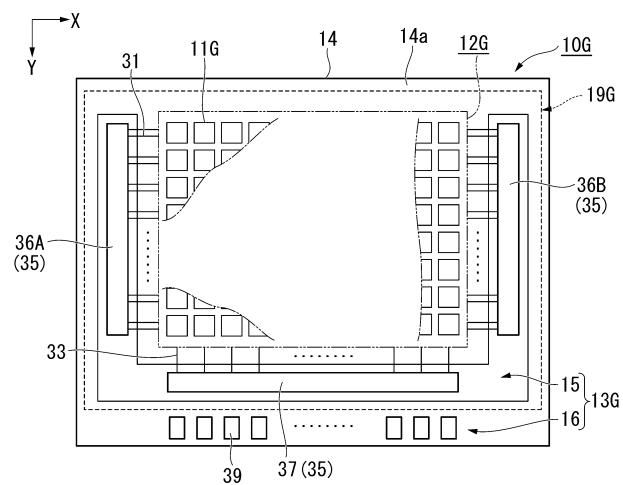

【図2】図1の電気光学装置の構成を示す概略図である。

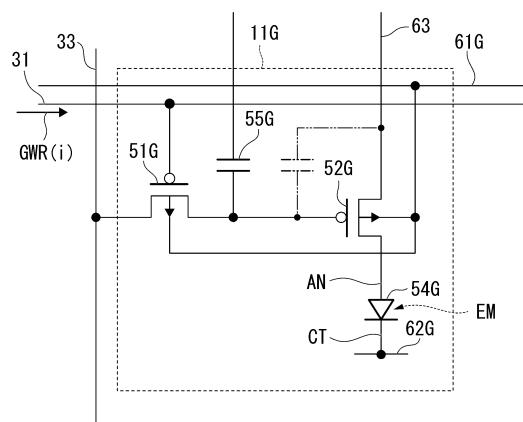

【図3】図1の電気光学装置の各々の画素が有する画素回路の等価回路図である。

30

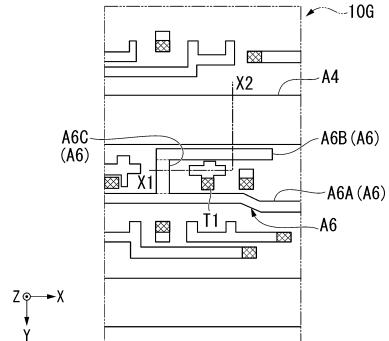

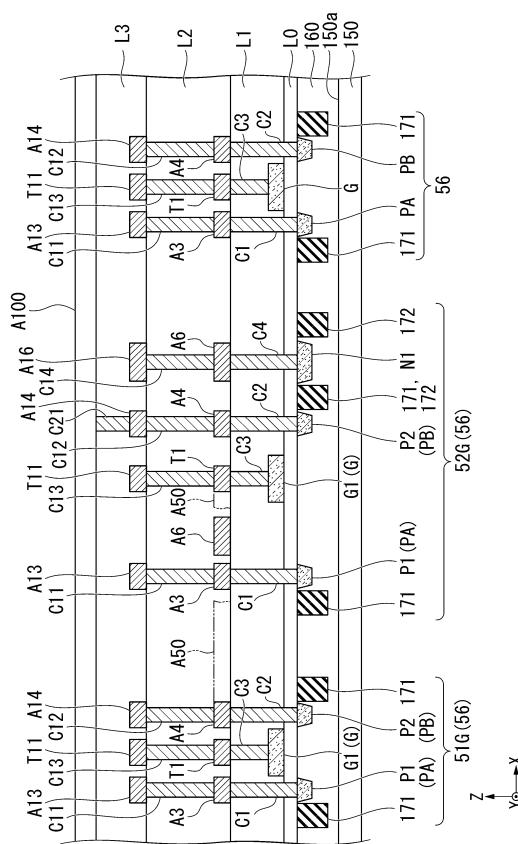

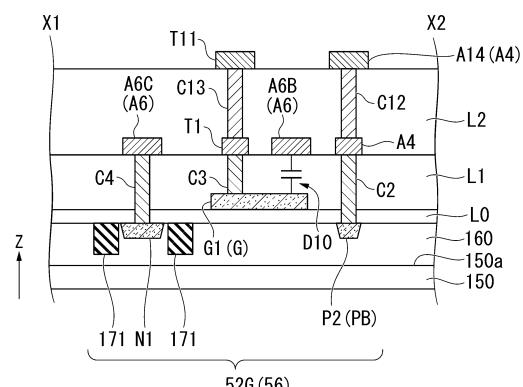

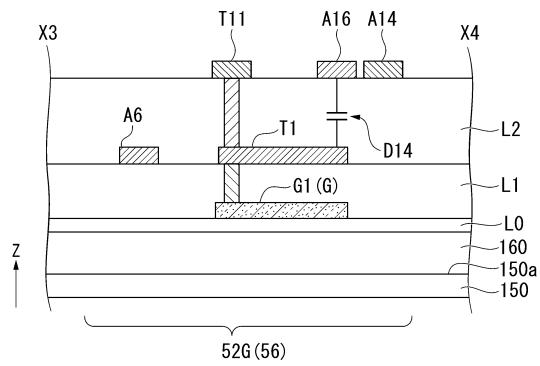

【図4】図1の電気光学装置の画素回路の基本構成を示す断面図である。

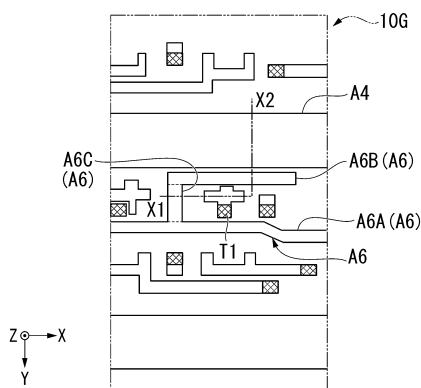

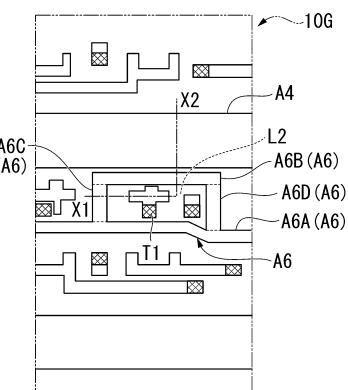

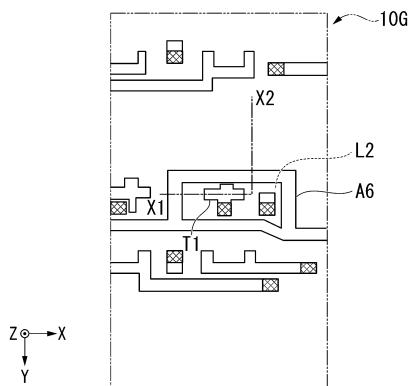

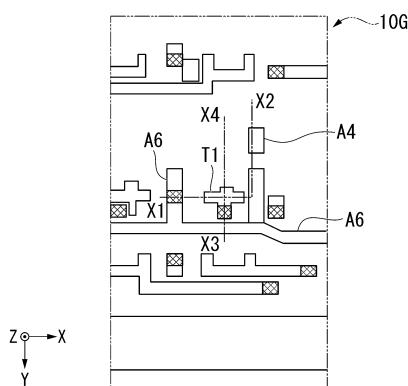

【図5】図1の電気光学装置の画素回路の平面図である。

【図6】図5の画素回路の平面図である。

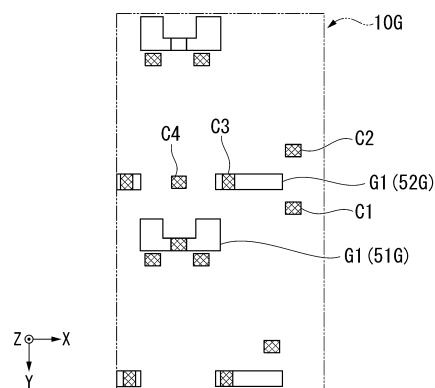

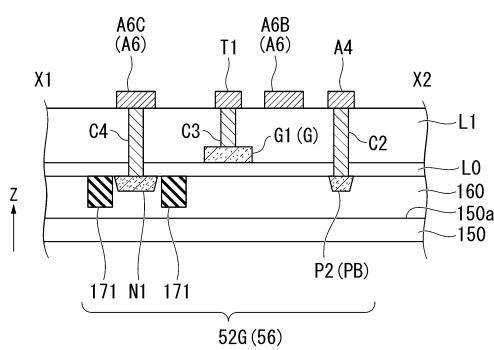

【図7】図5の画素回路の断面図である。

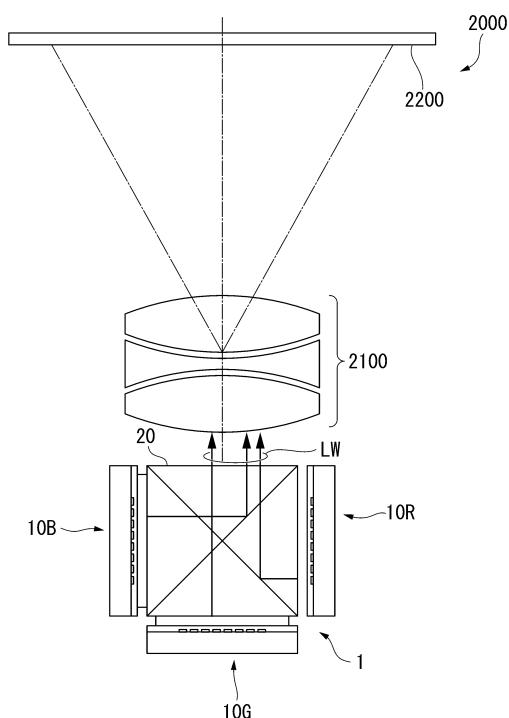

【図8】図1の電気光学装置を備えた光学装置の構成を示す概略図である。

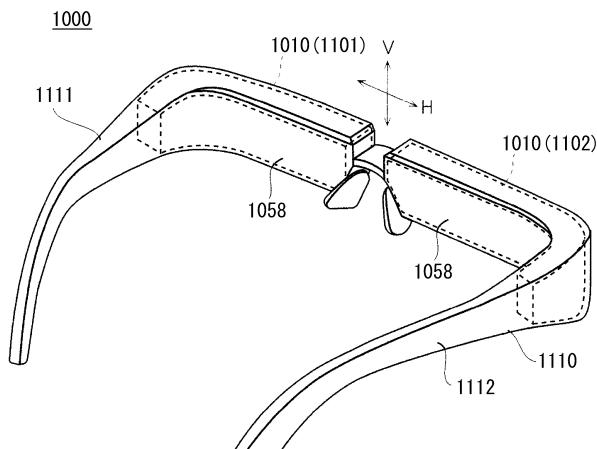

【図9】図1の電気光学装置を備えた画像表示装置の構成を示す概略図である。

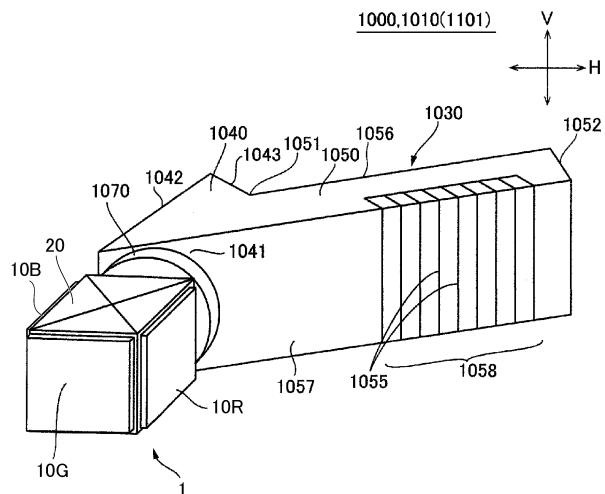

【図10】図9に示す画像表示装置の光学系の構成を示す斜視図である。

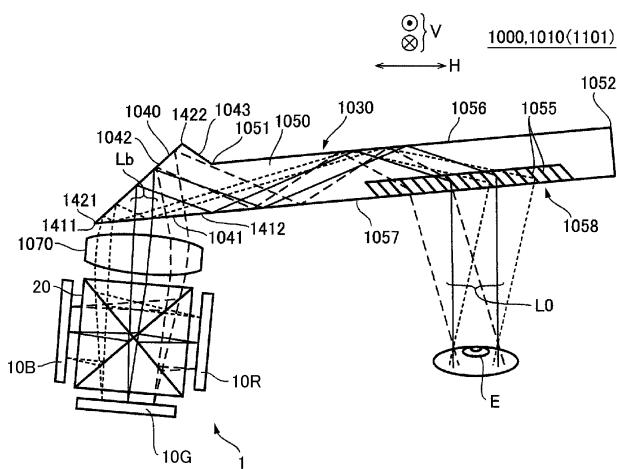

【図11】図10に示す光学系の光路図である。

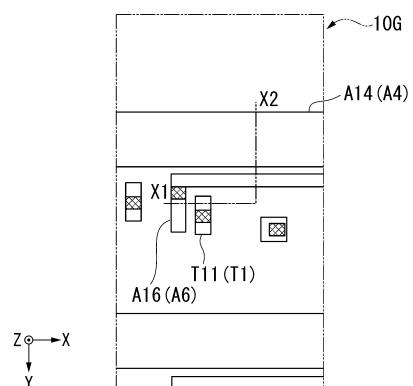

【図12】第2実施形態の電気光学装置の画素回路のレイアウトを説明するための概略図である。

【図13】第3実施形態の電気光学装置の画素回路のレイアウトを説明するための概略図である。

【図14】図13の電気光学装置の画素回路のレイアウトを説明するための概略図である。

【図15】図13の電気光学装置の画素回路のレイアウトを説明するための概略図である。

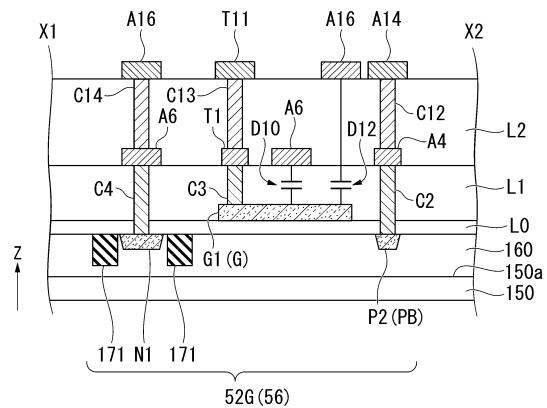

【図16】図13の電気光学装置の画素回路の断面図である。

【図17】第3実施形態の変形例の電気光学装置の画素回路のレイアウトを説明するための概略図である。

【図18】図17の電気光学装置の画素回路のレイアウトを説明するための概略図である。

40

50

【図19】図17の電気光学装置の画素回路の断面図である。

【図20】図17の電気光学装置の画素回路の断面図である。

【図21】図1の電気光学装置を備えた他の画像表示装置の構成を示す概略図である。

【発明を実施するための形態】

【0008】

[第1実施形態]

以下、本発明の第1実施形態について、図1～図11を用いて説明する。以下の各図面では、各構成要素を見やすくするため、構成要素によって寸法の縮尺を変えている場合がある。

【0009】

(電気光学装置)

図1は、第1実施形態の電気光学装置10Gの構成を示す斜視図である。電気光学装置10Gは、後述する発光素子54Gとして例えばOLEDが用いられた装置である。図1に示すように、電気光学装置10Gは、基板14と、画素生成部19Gと、複数の実装端子39と、を備える。画素生成部19G及び複数の実装端子39は、基板14の表面14aに設けられている。複数の実装端子39は、画素生成部19Gが占める矩形状の領域の一辺に沿って互いに間隔をあけて配置されている。複数の実装端子39に、フレキシブルフラットケーブル70Gの一方のコネクタ部が接続されている。フレキシブルフラットケーブル70Gの他方のコネクタ部は、不図示の制御基板と接続されている。

【0010】

フレキシブルフラットケーブル70Gに、複数の配線2,4と、制御回路3が設けられている。複数の配線2の各々の一方の端は、複数の実装端子39に接続されている。複数の配線2の各々の他方の端は、制御回路3に接続されている。制御回路3は、後述するよう発光素子54Gの輝度に対応した電位を示す画像信号を生成し、複数の配線2を介して実装端子39に供給する。複数の配線4の各々の一方の端は、制御回路3に接続されている。複数の配線4の各々の他方の端は、不図示の上位回路に接続されている。

【0011】

図2は、電気光学装置10Gの構成を示す平面図である。図2において、電気光学装置10Gの基板14の表面14aの水平方向をX方向とし、表面14aのX方向に直交する垂直方向をY方向とする。図2に示すように、基板14の表面14aに、画素生成部19Gが設けられている。表面14aは、画素領域12Gと、非画素領域13Gと、を含む。画素領域12Gには、複数の画素11GがX方向及びY方向に沿ってマトリクス状に配置され、X方向及びY方向に直交する方向から見たときに矩形状の領域である。画素領域12Gには、X方向と平行に延在する複数の走査線31と、Y方向と平行に延在する複数のデータ線33が設けられている。画素11Gは、複数の走査線31と複数のデータ線33とが交差する領域の各々に対応して構成されている。画素11Gが有する画素回路については、後に説明する。

【0012】

非画素領域13Gは、周辺領域15と、実装領域16と、を含む。周辺領域15は、X方向及びY方向に直交する方向から見たときに画素領域12Gを囲む矩形枠状の領域である。周辺領域15には、複数の画素11Gを駆動する駆動回路35が設けられている。駆動回路35は、走査線駆動回路36A,36Bと、データ線駆動回路37と、を備える。電気光学装置10Gでは前述のように駆動回路35が基板14の表面14aに形成されているため、電気光学装置10Gはトランジスターを備えた能動素子で構成される回路内蔵型の装置である。

【0013】

実装領域16は、周辺領域15に設けられたデータ線駆動回路37に対してY方向で画素領域12Gの反対側に設けられた領域、すなわち周辺領域15の外側に設けられた領域である。実装領域16には、複数の実装端子39が設けられている。実装端子39には、少なくとも電気光学装置10Gの複数の画素11Gを駆動するのに必要な映像信号及び電

10

20

30

40

50

源電圧が入力される。

#### 【 0 0 1 4 】

図3は、画素11Gが有する画素回路の等価回路図である。複数の画素11Gが有する画素回路の構成は互いに共通しているため、ここではi行目j列目の画素11Gが有する画素回路を例に挙げて説明する。iは、画素11Gが配置される行の番号を表し、1以上m以下の整数である。jは、画素11Gが配置される列の番号を表し、1以上n以下の整数である。画素11Gの画素回路は、選択トランジスター51Gと、駆動トランジスター52Gと、発光素子54Gと、保持容量55Gと、を有する。選択トランジスター51G及び駆動トランジスター52Gの各々は、例えばPチャネル型の金属酸化膜半導体電界効果トランジスター(Metal-oxide-semiconductor Field-effect Transistor; MOS-FET)である。

10

#### 【 0 0 1 5 】

選択トランジスター51Gのゲート電極は、i行目の走査線31と電気的に接続されている。選択トランジスター51Gのソース／ドレイン領域のうちの一方の領域は、j列目のデータ線33と電気的に接続されている。選択トランジスター51Gのソース／ドレイン領域のうちの他方の領域は、駆動トランジスター52Gのゲート電極、及び保持容量55Gの一方の電極と電気的に接続されている。選択トランジスター51Gのバックゲートは、電源電位が印加される電源配線61Gと電気的に接続されている。

#### 【 0 0 1 6 】

駆動トランジスター52Gのゲート電極は、選択トランジスター51Gのソース／ドレイン領域のうちの前述の他方の領域、及び保持容量55Gの一方の電極と電気的に接続されている。駆動トランジスター52Gのソース／ドレイン領域のうちの一方の領域は、電源配線61Gとは別の電源配線63と電気的に接続されている。駆動トランジスター52Gのソース／ドレイン領域のうちの他方の領域は、発光素子54Gの一方の電極、すなわちアノードANと電気的に接続されている。駆動トランジスター52Gのバックゲートは、電源配線61Gと電気的に接続されている。

20

#### 【 0 0 1 7 】

発光素子54Gは、緑色光を射出する発光素子である。発光素子54Gの発光層EMは、アノードと発光素子54Gの他方の電極、すなわちカソードCTとによって挟持され、例えばOLED、又はマイクロLED( $\mu$ LED)である。発光素子54Gの一方の電極は、駆動トランジスター52Gのソース／ドレイン領域のうちの前述の他方の領域と電気的に接続されている。発光素子54Gの他方の電極は、電源電位が印加される電源配線62Gと電気的に接続されている。

30

#### 【 0 0 1 8 】

保持容量55Gは、駆動トランジスター52Gのゲート電極と駆動トランジスター52Gのソース／ドレイン領域のうちの前述の一方の領域との間の電圧を保持するためのコンデンサである。保持容量55Gの一方の電極は、選択トランジスター51Gのソース／ドレイン領域のうちの前述の他方の領域、及び駆動トランジスター52Gのゲート電極と電気的に接続されている。保持容量55Gの他方の電極は、電源配線61Gとは別の不図示の電源配線と電気的に接続されている。なお、保持容量55Gとして、駆動トランジスター52Gのゲート電極に寄生する容量が用いられてもよく、Si基板において互いに異なる導電層で絶縁層を挟持することによって形成される容量が用いられてもよい。

40

#### 【 0 0 1 9 】

上述のように構成された画素11Gの画素回路において、i行目の走査線31に供給される走査信号GWR(i)がハイ(High:H)レベルのとき、選択トランジスター51GはOFF状態である。一方、走査信号GWR(i)がロー(Low:L)レベルのとき、選択トランジスター51GはON状態となる。選択トランジスター51GがON状態にあるとき、データ線33の電位と保持容量55Gの他方の電極の電位との電位差Vd1に応じて保持容量55Gに電流が流れることによって、保持容量55Gの電極間の電圧が電位差Vd1となるまで保持容量55Gは充電される。

50

## 【0020】

駆動トランジスター52Gのゲート電位が駆動トランジスター52Gの閾値電圧を越えると、駆動トランジスター52G及び発光素子54Gを介して、電源配線63から電源配線62Gへ向かって駆動電流が流れる。駆動電流の値は、駆動トランジスター52Gのゲート電位によって制御される。駆動トランジスター52Gのゲート電極と電源配線63に電気的に接続されている駆動トランジスター52Gのソース／ドレイン領域のうちの前述の一方の領域との間の電圧は、保持容量55Gによって保持される電圧、すなわち保持容量55Gの電極間の電圧と等しい。したがって、駆動電流は、保持容量55Gによって保持される電圧に応じた電流値を有する。また、駆動電流が発光素子54Gに流れることによって、発光素子54Gは、駆動電流に応じた強度を有する緑色光を射出する。

10

## 【0021】

図4は、図3に示す画素回路の底部の基本構成を示す断面図である。図4以降の各図面において、X方向及びY方向に直交し、画素回路の厚み方向と平行であって鉛直方向とは逆向きの方向をZ方向とする。図4を参照した説明における平面視、及び後述する特許請求の範囲における平面視とは、X方向及びY方向に直交する方向、すなわちZ方向に沿って観察することを意味し、半導体基板150の表面150aに直交する方向に沿って半導体基板150よりも上方から表面150aする。以下では、各構成要素のZ方向の前側の面を表面と称し、各構成要素のZ方向の後側の面を底面と称する。

## 【0022】

図4に示すように、画素11Gが有する画素回路の各構成要素は、Si基板からなるP型の半導体基板150の上、すなわち半導体基板150の表面150aよりもZ方向の前方に形成されている。半導体基板150において表面150aを含む上側の領域、すなわち半導体基板150のうちのZ方向の前側の領域には、表面150aの全域にわたって、N型ウェル160が形成されている。N型ウェル160には、N型の不純物ドーパントが適切な濃度で注入されている。各型の不純物ドーパントの適切な濃度とは、半導体基板150の特性を考慮したときに、半導体基板150に対して不純物ドーパントを含む領域の電気的特性及び所望の作用が安定して保持され得る濃度を意味する。

20

## 【0023】

N型ウェル160において半導体基板150の表面150aを含む上側の領域に、1つの画素11Gの画素回路につき、複数のP型拡散領域Pjと1つ以上のN型拡散領域Nkが形成されている。j, kの各々は、任意の自然数である。画素11Gの画素回路につき、図4に例示する基本構造では、N型ウェル160に例えば6つのP型拡散領域P1～P6と1つのN型拡散領域N1が形成されている。P型拡散領域Pjは、N型ウェル160の所定の領域の表面150aにP型の不純物ドーパントが適切な濃度で注入されることによって、形成されている。すなわち、P型拡散領域Pjは、P型の不純物ドーパントを含む。N型拡散領域Nkは、平面視でN型ウェル160においてP型拡散領域Pjが形成されている領域とは異なる所定の領域の表面150aにN型の不純物ドーパントが適切な濃度で注入されることによって、形成されている。すなわち、N型拡散領域Nkは、N型の不純物ドーパントを周囲のN型ウェル160よりも多く含む。

30

## 【0024】

P型拡散領域Pjは、選択トランジスター51G及び駆動トランジスター52Gを含むトランジスター56のソース領域又はドレイン領域として作用する。N型ウェル160において1つのトランジスター56に用いられるP型拡散領域PA, PBを平面視で囲む枠状にSTI(Shallow Trench Isolation)171が設けられている。STI171が設けられることによって、平面視で互いに隣り合うトランジスター56の間でのリーク電流が低減され、耐圧が確保されている。

40

## 【0025】

トランジスター56は、少なくともゲート電極層Gと、P型拡散領域PA, PBを有し、Pチャネル型のMOS-FETである。P型拡散領域PAは、トランジスター56のソース／ドレイン領域のうちの一方の領域として作用する。P型拡散領域PBは、トランジ

50

スター 5 6 のソース / ドレイン領域のうちの他方の領域として作用する。

#### 【 0 0 2 6 】

トランジスター 5 6 のうち、駆動トランジスター 5 2 G は、ゲート電極層 G 1 と、P 型拡散領域 P 1 , P 2 と、N 型拡散領域 N 1 と、を有する。P 型拡散領域 P 1 は、駆動トランジスター 5 2 G のソース / ドレイン領域のうちの一方の領域として作用する。P 型拡散領域 P 2 は、駆動トランジスター 5 2 G のソース / ドレイン領域のうちの他方の領域として作用する。N 型拡散領域 N 1 は、トランジスター 5 6 のボディ電源として作用する。

#### 【 0 0 2 7 】

N 型ウェル 1 6 0 において駆動トランジスター 5 2 G に用いられる N 型拡散領域 N 1 を平面視で囲む枠状に S T I 1 7 2 が設けられている。図 4 には、P 型拡散領域 P A , P B を平面視で囲む S T I 1 7 1 のうち、X 方向において P 型拡散領域 P A , P B を挟んで配置されている S T I 1 7 1 が示され、N 型拡散領域 N 1 を平面視で囲む S T I 1 7 2 のうち、X 方向において N 型拡散領域 N 1 を挟んで配置されている S T I 1 7 2 が示されている。S T I 1 7 2 の一部分は、P 型拡散領域 P 1 , P 2 を囲む S T I 1 7 1 と共にされている。

10

#### 【 0 0 2 8 】

駆動トランジスター 5 2 G の N 型拡散領域 N 1 の電位は、ソース領域に印加される高電位の電位と同等に設定及び供給される。

#### 【 0 0 2 9 】

N 型ウェル 1 6 0 、P 型拡散領域 P j 及び N 型拡散領域 N k の表面、すなわち半導体基板 1 5 0 の表面 1 5 0 a には、ゲート絶縁層 L 0 が形成されている。ゲート絶縁層 L 0 は、例えば酸化シリコン ( S i O 2 ) で形成されている。平面視で P 型拡散領域 P A , P 1 と P 型拡散領域 P B , P 2 との間のゲート絶縁層 L 0 の表面には、例えばパターニングによってトランジスター 5 6 のゲート電極層 G 、或いは駆動トランジスターのゲート電極層 G 1 が形成されている。ゲート電極層 G , G 1 は、例えば多結晶シリコン ( P o l y - S i ) によって形成されている。ゲート電極層 G , G 1 及びゲート絶縁層 L 0 を覆う層間絶縁層 L 1 が設けられている。

20

#### 【 0 0 3 0 】

平面視で P 型拡散領域 P j の各々が形成されている領域の少なくとも一部の領域に、層間絶縁層 L 1 の表面から層間絶縁層 L 1 及びゲート絶縁層 L 0 を Z 方向に貫通して P 型拡散領域 P j の各々に到達するコンタクトホールが形成されている。また、平面視でゲート電極層 G , G 1 が形成されている領域の少なくとも一部の領域に、層間絶縁層 L 1 の表面から層間絶縁層 L 1 を Z 方向に貫通してゲート電極層 G , G 1 に到達するコンタクトホールが形成されている。さらに、平面視で N 型拡散領域 N k の各々が形成されている領域の少なくとも一部の領域に、層間絶縁層 L 1 の表面から層間絶縁層 L 1 及びゲート絶縁層 L 0 を Z 方向に貫通して N 型拡散領域 N k の各々に到達するコンタクトホールが形成されている。

30

#### 【 0 0 3 1 】

各々のコンタクトホールに導電材料が埋設されることによって、コンタクトプラグ C 1 ~ C 4 が形成されている。前述の導電材料は、例えばタンクスチタン ( W ) である。但し、前述の導電材料が走査線 3 1 、データ線 3 3 や電源配線 6 1 G 、或いは各電極層を構成する導電材料と同じであり、トランジスター 5 6 の形成工程でコンタクトホールが走査線 3 1 、データ線 3 3 や電源配線 6 1 G を構成する導電材料で埋められてもよい。コンタクトプラグ C 1 の一方の端、すなわち Z 方向の後側の端は、P 型拡散領域 P A , P 1 に電気的に接続されている。コンタクトプラグ C 2 の一方の端は、P 型拡散領域 P B , P 2 に電気的に接続されている。コンタクトプラグ C 3 の一方の端は、ゲート電極層 G , G 1 に電気的に接続されている。駆動トランジスター 5 2 G のコンタクトプラグ C 4 の一方の端は、N 型拡散領域 N 1 に電気的に接続されている。コンタクトプラグ C 1 ~ C 4 の各々の他方の端の端面は、層間絶縁層 L 1 の表面と同一である。

40

#### 【 0 0 3 2 】

10

20

30

40

50

コンタクトプラグ C 1 の前述の他方の端面を含む層間絶縁層 L 1 の表面の所定の領域には、例えばパターニングによって電極層 A 3 が形成されている。電極層 A 3 は、トランジスター 5 6 のソース／ドレイン領域のうちの P 型拡散領域 P A , P 1 が作用する一方の領域を構成する電極層の一部分をなす部材、又は前述の一方の領域を構成する電極層と電気的に接続されている部材である。コンタクトプラグ C 2 の前述の他方の端面を含む層間絶縁層 L 1 の表面の所定の領域には、例えばパターニングによって電極層 A 4 が形成されている。電極層 A 4 は、トランジスター 5 6 のソース／ドレイン領域のうちの P 型拡散領域 P B , P 2 が作用する他方の領域を構成する電極層の一部分をなす部材、又は前述の他方の領域を構成する電極層と電気的に接続されている部材である。

## 【 0 0 3 3 】

10

コンタクトプラグ C 3 の前述の他方の端面を含む層間絶縁層 L 1 の表面の所定の領域には、例えばパターニングによって中継層 T 1 が形成されている。中継層 T 1 は、各々のトランジスター 5 6 のゲート電極層 G と電気的に接続された中継部材（中継電極）である。駆動トランジスター 5 2 G のコンタクトプラグ C 4 の前述の他方の端面を含む層間絶縁層 L 1 の表面の所定の領域には、例えばパターニングによって電極層 A 6 が形成されている。電極層 A 6 は、トランジスター 5 6 の電源配線 6 1 G と電気的に接続されている部材である。

## 【 0 0 3 4 】

20

例えば、図 3 に示す画像回路において、選択トランジスター 5 1 G のソース領域が j 列目のデータ線 3 3 と電気的に接続され、選択トランジスター 5 1 G のドレイン領域が駆動トランジスター 5 2 G のゲート電極、及び保持容量 5 5 G の一方の電極と電気的に接続されていると想定する。また、駆動トランジスター 5 2 G のドレイン領域が発光素子 5 4 G のアノード A N と電気的に接続され、駆動トランジスター 5 2 G のソース領域が電源配線 6 3 と電気的に接続されていると想定する。

## 【 0 0 3 5 】

30

上述の想定において、図 4 に示す画像回路の選択トランジスター 5 1 G の基本構成の P 型拡散領域 P 1 がソース領域として作用し、P 型拡散領域 P 2 がドレイン領域として作用すると想定する。その場合、選択トランジスター 5 1 G と電気的に接続された電極層 A 3 , A 1 3 は、データ線 3 3 を構成する導電層の一部であるか、データ線 3 3 を構成する導電層と電気的に接続され、例えば電極層 A 3 , A 1 3 とデータ線 3 3 を構成する導電層との間で X 方向及び Y 方向に平行な面に沿って延在する不図示の導電部材又は Z 方向に沿って延在する不図示のコンタクトプラグによってデータ線 3 3 を構成する導電層と電気的に接続されている。電極層 A 4 , A 1 4 は、一点鎖線で示すように中継層 T 1 , T 1 1 と電気的に接続され、例えば電極層 A 4 , A 1 4 と中継層 T 1 , T 1 1 との間で X 方向及び Y 方向に平行な面に沿って延在する不図示の導電部材や Z 方向に沿って延在する不図示のコンタクトプラグによって中継層 T 1 , T 1 1 と電気的に接続されていてもよい。電極層 A 4 , A 1 4 と中継層 T 1 , T 1 1 との間の導電部材からなる電極層 A 5 0 や不図示のコンタクトプラグは、保持容量 5 5 G の一方の電極を構成する導電層と電気的に接続されている。

## 【 0 0 3 6 】

40

中継層 T 1 , T 1 1 は、走査線 3 1 を構成する導電層の一部であるか、走査線 3 1 を構成する導電層と電気的に接続されている。

## 【 0 0 3 7 】

また、上述のように図 4 に示す画像回路の駆動トランジスター 5 2 G 基本構成の P 型拡散領域 P 1 がドレイン領域として作用し、P 型拡散領域 P 2 がソース領域として作用するという想定では、電極層 A 3 , A 1 3 は、電源配線 6 3 を構成する導電層の一部であるか、電源配線 6 3 を構成する導電層と電気的に接続される。電極層 A 4 , A 1 4 は、発光素子 5 4 G の一方の電極すなわちアノード A N を構成する電極に電気的に接続され、具体的には後述する電極層 A 1 0 0 と電気的に接続されている。

## 【 0 0 3 8 】

50

中継層 T 1 , T 1 1 は、前述のように電極層 A 4 , A 1 4 と電気的に接続されている。電極層 A 6 , A 1 6 は、電源配線 6 3 を構成する導電層の一部であるか、電源配線 6 3 を構成する導電層と電気的に接続されている。

#### 【 0 0 3 9 】

図 4 に示す画素 1 1 G の画素回路の基本構造では、電極層 A 3 , A 4 , A 6 、中継層 T 1 及び層間絶縁層 L 1 を覆う層間絶縁層 L 2 が設けられている。層間絶縁層 L 2 の表面に、電極層 A 3 と電気的に接続された電極層 A 1 3 と、電極層 A 4 と電気的に接続された電極層 A 1 4 と、電極層 A 6 と電気的に接続された電極層 A 1 6 と、中継層 T 1 と電気的に接続された中継層 T 1 1 が設けられている。例えば、電極層 A 3 , A 1 3 は、コンタクトプラグ C 1 1 によって連結されている。コンタクトプラグ C 1 1 は、層間絶縁層 L 2 に形成されて電極層 A 3 , A 1 3 同士の間を貫通するコンタクトホールに導電材料が埋設されることによって形成可能である。同様に、電極層 A 4 , A 1 4 は、コンタクトプラグ C 1 2 によって連結されている。コンタクトプラグ C 1 2 は、層間絶縁層 L 2 に形成されて電極層 A 4 , A 1 4 同士の間を貫通するコンタクトホールに導電材料が埋設されることによって形成可能である。中継層 T 1 , T 1 1 は、コンタクトプラグ C 1 3 によって連結されている。コンタクトプラグ C 1 3 は、層間絶縁層 L 2 に形成されて中継層 T 1 , T 1 1 同士の間を貫通するコンタクトホールに導電材料が埋設されることによって形成可能である。駆動トランジスター 5 2 G の電極層 A 6 , A 1 6 は、コンタクトプラグ C 1 4 によって連結されている。コンタクトプラグ C 1 4 は、層間絶縁層 L 2 に形成されて電極層 A 6 , A 1 6 同士の間を貫通するコンタクトホールに導電材料が埋設されることによって形成可能である。10 20

#### 【 0 0 4 0 】

図 4 に示す画素 1 1 G の画素回路の基本構造では、電極層 A 1 3 , A 1 4 , A 1 6 、中継層 T 1 1 及び層間絶縁層 L 2 を覆う層間絶縁層 L 3 が設けられている。層間絶縁層 L 3 の表面に、電極層 A 1 4 と電気的に接続された電極層 A 1 0 0 が設けられている。電極層 A 1 0 0 の平面視での大きさは、1つの画素 1 1 G に対応している。例えば、電極層 A 1 4 , A 1 0 0 は、コンタクトプラグ C 2 1 によって連結されている。電極層 A 1 0 0 は、発光素子 5 4 G の一方の電極すなわちアノード A N を構成する電極層である、又は発光素子 5 4 G のアノード A N と電気的に接続されている電極層である。30

#### 【 0 0 4 1 】

電極層 A 3 , A 4 , A 6 , A 1 3 , A 1 4 , A 1 6 、及び中継層 T 1 , T 1 1 の各々は、例えば銅 ( Cu ) を含む金属で形成されている。層間絶縁層 L 1 ~ L 3 の各々は、例えば SiO<sub>2</sub> で形成されている。40

#### 【 0 0 4 2 】

図 4 に示す画素 1 1 G の画素回路では、電極層 A 1 0 0 が最表層の構成要素である。但し、電極層 A 1 0 0 よりも上層に、すなわち電極層 A 1 0 0 よりも Z 方向の前方に不図示の層間絶縁層、絶縁層、半導体層及び導電層が設けられていてもよい。画素 1 1 G の画素回路の層状構造は、電気光学装置 1 0 G に求められる光学的性能、電気的性能をふまえて適宜設計される。例えば、電極層 A 1 3 , A 1 6 、中継層 T 1 1 、コンタクトプラグ C 1 1 , C 1 3 , C 1 4 のうちの少なくとも 1 つ以上の構成要素は適宜省略されてもよい。40

#### 【 0 0 4 3 】

第 1 実施形態の電気光学装置 1 0 G の画素 1 1 G の画素回路では、P 型拡散領域 P B , P 2 が駆動トランジスター 5 2 G のソース領域として作用する場合、層間絶縁層 L 1 の表面の平面視で電極層 A 4 と中継層 T 1 との間に電極層 A 6 が延在している。画素 1 1 G の画素回路における各構成要素の平面視でのレイアウトは、上述の電気光学装置 1 0 G に求められる光学的性能、電気的性能をふまえた層状構造と併せて、電気光学装置 1 0 G の形状や大きさに関する制約も考慮して、適宜設計される。

#### 【 0 0 4 4 】

図 5 は、適宜設計された第 1 実施形態の画素 1 1 G の画素回路の層間絶縁層 L 1 の表面での平面視のレイアウトを示す概略図である。図 6 は、適宜設計された第 1 実施形態の画50

素 1 1 G の画素回路のゲート絶縁層 L 0 の表面での平面視のレイアウトを示す概略図である。図 7 は、図 5 及び図 6 に示すレイアウトで形成された画素回路の構成を示す図であり、図 5 に示す X 1 - X 2 線で矢視した場合の断面図である。なお、図 7 では、電極層 A 4 , A 6 及び中継層 T 1 よりも上層、すなわち電極層 A 4 , A 6 及び中継層 T 1 よりも Z 方向の前方の構成は、省略されている。

#### 【 0 0 4 5 】

図 5 に示す中継層 T 1 は、図 3 に示す等価回路図の駆動トランジスター 5 2 G のゲート電極層 G 1 と電気的に接続される導電層である。図 6 に示す G 1 ( 5 1 G ) は選択トランジスター 5 1 G のゲート電極層 G 1 を表し、同図の G 1 ( 5 2 G ) は駆動トランジスター 5 2 G のゲート電極層 G 1 を表す。図 6 に示すコンタクトプラグ C 1 は、中継層 T 1 よりも Y 方向の前方に形成され、不図示のアノード A N と電気的に接続される。図 6 に示すコンタクトプラグ C 2 は、図 5 に示すように中継層 T 1 よりも Y 方向の後方に形成された電極層 A 4 に電気的に接続されている。図 6 に示すコンタクトプラグ C 3 は、図 5 に示す中継層 T 1 に電気的に接続されている。図 6 に示すコンタクトプラグ C 4 は、図 5 に示す電極層 A 6 のうち、電極層 A 6 C に電気的に接続されている。電極層 A 6 C は、電極層 A 6 A と中継層 T 1 よりも Y 方向の後方に形成され、X 方向に沿って延在する電極層 A 6 B とを連結し、Y 方向に沿って延びている。

#### 【 0 0 4 6 】

図 5 及び図 7 に示すように、第 1 実施形態の電気光学装置 1 0 G の画素 1 1 G の画素回路では、平面視及び断面視でのゲート絶縁層 L 0 の表面の Y 方向で駆動トランジスター 5 2 G の電極層 A 4 と中継層 T 1 との間に電極層 A 6 B が配置されている。この場合、電極層 A 4 は、ソース領域として作用する P 型拡散領域 P 2 , P B と電気的に接続され、具体的にはコンタクトプラグ C 2 を介して P 型拡散領域 P 2 , P B に電気的に接続されている。中継層 T 1 は、ゲート電極層 G 1 , G と電気的に接続され、具体的にはコンタクトプラグ C 3 を介してゲート電極層 G 1 , G と電気的に接続される。第 1 実施形態の電気光学装置 1 0 G の画素 1 1 G の画素回路では、駆動トランジスター 5 2 G に少なくとも必要とされる電極層 A 6 A 、すなわちコンタクトプラグ C 4 を介して N 型拡散領域 N 1 と電気的に接続されている電極層 A 6 から、新たに電極層 A 6 C , A 6 B が延出して形成されることによって、Y 方向で電極層 A 4 と中継層 T 1 との間に電極層 A 6 B が設けられている。

#### 【 0 0 4 7 】

電極層 A 6 を構成する電極層 A 6 A , A 6 B , A 6 C の各々は半導体基板 1 5 0 に形成された N 型拡散領域 N 1 , N k と電気的に接続されているため、電極層 A 6 A , A 6 B , A 6 C の各々の抵抗は電源配線 6 1 G よりも低く、電極層 A 6 A , A 6 B , A 6 C の各々の電位は電源配線 6 1 G よりも安定している。上述のように電極層 A 4 と中継層 T 1 との間に電極層 A 6 B が層間絶縁層 L 1 の表面で互いに同層に設けられているため、駆動トランジスター 5 2 G のゲート電極層 G 1 , G と電源配線 6 1 G との間が安定的にシールドされている。

#### 【 0 0 4 8 】

次に、図 4 から図 7 に例示した第 1 実施形態の電気光学装置 1 0 G の画素回路の基本構造の製造方法を簡単に説明する。図示していないが、半導体基板 1 5 0 を構成する P 型の S i 基板の表面を含む Z 方向の前側の部分に、半導体基板 1 5 0 の表面 1 5 0 a の全体に亘って、例えば Z 方向の前方からイオン化した N 型の不純物ドーパントを注入し、N 型ウェル 1 6 0 を形成する。続いて、平面視において N 型ウェル 1 6 0 の領域内の互いに異なる小領域であってトランジスター 5 6 のソース領域又はドレイン領域とする小領域に、例えば Z 方向の前方からイオン化した P 型の不純物ドーパントを注入し、P 型拡散領域 P j を形成する。続いて、平面視において N 型ウェル 1 6 0 の領域内の平面視で P 型拡散領域 P j とは異なる小領域であってトランジスター 5 6 の電源配線 6 1 G とする小領域に、例えば Z 方向の前方からイオン化した N 型の不純物ドーパントを注入し、N 型拡散領域 N k を形成する。続いて、平面視において N 型ウェル 1 6 0 の領域内のソース領域及びドレイン領域を構成する P 型拡散領域 P j を囲むように枠状に N 型ウェル 1 6 0 を削除すること

10

20

30

40

50

によって、ソース領域及びドレイン領域を構成するP型拡散領域Pjを囲む溝を形成する。当該溝を埋めて半導体基板150の表面150aよりもZ方向の前方に至るまでSTI171を構成する絶縁材料を例えばプラズマ化学的気相成長(Chemical Vap or Deposition; CVD)法によって形成する。その後、例えばCMP(Chemical Mechanical Polisher)装置を用いて半導体基板150の表面150aすなわちN型ウェル160の表面が露出されるまで、絶縁材料からなる堆積層の上部を除去する。絶縁材料として、例えばSiO<sub>2</sub>を用いることができる。

#### 【0049】

続いて、半導体基板150の表面150aに、例えば熱酸化法又はスパッタ装置を用いる成膜法によってSiO<sub>2</sub>からなるゲート絶縁層L0を形成する。続いて、ゲート絶縁層L0の表面に、例えばCVD法によって層間絶縁層L1を構成する絶縁材料をゲート電極層Gと同等の厚みで堆積する。必要に応じて、絶縁材料からなる絶縁層の表面を平坦化する。続いて、平面視でゲート電極層Gとする小領域の絶縁層を除去し、穴を形成する。穴の内部に、ゲート電極層Gを構成する材料として例えばPoly-Siを成長させ、穴にゲート電極層Gを形成する。必要に応じて、ゲート電極層Gの表面を周囲の絶縁層の表面と面一になるように平坦化してもよい。

#### 【0050】

続いて、ゲート電極層G及び平面視で周囲の絶縁層の表面に、例えば原子層堆積(Atomic Layer Deposition; ALD)法によって絶縁材料を形成し、層間絶縁層L1を形成する。その後、層間絶縁層L1において平面視でP型拡散領域Pj、N型拡散領域Nkの各々と重なる領域に、例えばパターニング及び反応性イオンエッチング(Reactive Ion Etching; RIE)によって層間絶縁層L1及びゲート絶縁層L0をP型拡散領域Pj、N型拡散領域Nkの各々の表面まで貫通するコンタクトホールを形成する。また、層間絶縁層L1において平面視でゲート電極層Gと重なる領域に、例えばパターニング及び反応性イオンエッチング(Reactive Ion Etching; RIE)法によって層間絶縁層L1をゲート電極層Gの表面まで貫通するコンタクトホールを形成する。続いて、各々のコンタクトホールに内部に導電材料を埋設し、コンタクトプラグC1～C4を形成する。必要に応じて、コンタクトプラグC1～C4の表面を層間絶縁層L1の表面と面一になるように平坦化してもよい。

#### 【0051】

続いて、コンタクトプラグC1～C4の表面及び層間絶縁層L1の表面に、電極層A3、A4、A6及び中継層T1の各々を構成する導電材料を形成する。その後、パターニング及びRIE法を用いて導電材料からなる導電層のうち、平面視で電極層A3、A4、A6及び中継層T1の各々とする領域の導電層を残し、これらの領域以外の導電層を削除することによって、層間絶縁層L1の表面に電極層A3、A4、A6及び中継層T1の各々を形成する。本工程で用いる電極層A3、A4、A6及び中継層T1の各々のマスクパターンでは、平面視で、すなわちマスク基板の表面に平行な所定の方向において、電極層A4の領域と中継層T1の領域との間に電極層A6の領域が配置されている。所定の方向は、図4や図7に例示したようにトランジスター56のソース領域として作用するP型拡散領域Pjと電気的に接続される電極層A4と同じトランジスター56のゲート電極層Gと電気的に接続される中継層T1とが互いに間隔をあけて配置される方向を表す。すなわち、層間絶縁層L1の表面に電極層A3、A4、A6及び中継層T1の各々を形成する際には、平面視で図5に示すレイアウトと一致したパターンを有するマスクを用いる。

#### 【0052】

続いて、層間絶縁層L1、電極層A3、A4、A6及び中継層T1の各々を覆うように、例えばALD法を用いて絶縁材料からなる層間絶縁層L2を形成する。層間絶縁層L2において平面視で電極層A3、A4、A6及び中継層T1の各々と重なる領域に、例えばパターニング及び反応性イオンエッチング(Reactive Ion Etching; RIE)法によって層間絶縁層L2を電極層A3、A4、A6及び中継層T1の各々の表面まで貫通するコンタクトホールを形成する。続いて、各々のコンタクトホールの内部

10

20

30

40

50

に導電材料を埋設し、コンタクトプラグ C 1 1 ~ C 1 4 を形成する。必要に応じて、コンタクトプラグ C 1 1 ~ C 1 4 の表面を層間絶縁層 L 2 の表面と面一になるように平坦化してもよい。

#### 【 0 0 5 3 】

続いて、コンタクトプラグ C 1 1 ~ C 1 4 の表面及び層間絶縁層 L 2 の表面に、電極層 A 1 3 , A 1 4 , A 1 6 及び中継層 T 1 1 の各々を構成する導電材料を形成する。その後、パターニング及び R I E 法を用いて導電材料からなる導電層のうち、平面視で電極層 A 1 3 , A 1 4 , A 1 6 及び中継層 T 1 1 の各々とする領域の導電層を残し、これらの領域以外の導電層を削除することによって、層間絶縁層 L 2 の表面に電極層 A 1 3 , A 1 4 , A 1 6 及び中継層 T 1 1 の各々を形成する。

10

#### 【 0 0 5 4 】

続いて、層間絶縁層 L 2 、電極層 A 1 3 , A 1 4 , A 1 6 及び中継層 T 1 1 の各々を覆うように、例えば A L D 法を用いて絶縁材料からなる層間絶縁層 L 3 を形成する。層間絶縁層 L 3 において平面視で駆動トランジスター 5 2 G の電極層 A 1 6 と重なる領域に、例えばパターニング及び R I E 法によって層間絶縁層 L 3 を電極層 A 1 6 の表面まで貫通するコンタクトホールを形成する。続いて、コンタクトホールに内部に導電材料を埋設し、コンタクトプラグ C 2 1 を形成する。必要に応じて、コンタクトプラグ C 2 1 の表面を層間絶縁層 L 3 の表面と面一になるように平坦化してもよい。続いて、コンタクトプラグ C 2 1 の表面及び層間絶縁層 L 3 の表面に、電極層 A 1 0 0 を構成する導電材料を形成する。

20

#### 【 0 0 5 5 】

上述の工程を経て、第 1 実施形態の電気光学装置 1 0 G の画素回路を製造することができる。なお、必要に応じて、電極層 A 1 0 0 の表面に、層間絶縁層 L 2 、コンタクトプラグ C 1 1 ~ C 1 4 、及び電極層 A 1 3 , A 1 4 , A 1 6 及び中継層 T 1 1 の各々と同様の工程を経て、これらの構成要素を Z 方向に積層してもよい。

#### 【 0 0 5 6 】

##### ( 画像表示装置 )

次に、第 1 実施形態の電気光学装置 1 0 G を備える画像表示装置について説明する。図 8 は、第 1 実施形態の電気光学装置 1 0 G を備える光学装置 1 の構成を示す概略図である。図 8 に示すように、光学装置 1 は、電気光学装置 1 0 G , 1 0 B , 1 0 R と、ダイクロイックプリズム 2 0 と、を備える。電気光学装置 1 0 G は、緑色の画像光 L G をダイクロイックプリズム 2 0 に射出する自発光型の電気光学装置である。電気光学装置 1 0 B は、上述で説明した電気光学装置 1 0 G と同様の構成を備え、青色の画像光 L B をダイクロイックプリズム 2 0 に射出する自発光型の電気光学装置である。電気光学装置 1 0 R は、電気光学装置 1 0 G と同様の構成を備え、赤色の画像光 L R をダイクロイックプリズム 2 0 に射出する自発光型の電気光学装置である。電気光学装置 1 0 G , 1 0 B , 1 0 R の各々は、有機 E L パネルである。

30

#### 【 0 0 5 7 】

画像光 L G が有する緑色の波長域は、例えば 4 9 5 n m から 5 7 0 n m までの波長域を含む。電気光学装置 1 0 G の複数の画素 1 1 G は、緑色光を射出する。電気光学装置 1 0 G から射出される画像光 L G は、複数の画素 1 1 G の各々から射出される緑色光で構成されている。

40

#### 【 0 0 5 8 】

電気光学装置 1 0 G の基板 1 4 の表面 1 4 a は、ダイクロイックプリズム 2 0 の緑色光の入射面 2 2 に対向し、透光性を有する接着剤層 4 0 G を介して入射面 2 2 に貼り合わされている。言い換えれば、電気光学装置 1 0 G は、画像光 L G が入射面 2 2 に対して垂直に入射されるように配置されている。

#### 【 0 0 5 9 】

電気光学装置 1 0 B は、発光素子として O L E D 又は  $\mu$  L E D が用いられた装置であり、複数の画素 1 1 B を含む画素領域 1 2 B と、非画素領域 1 3 B と、を備える。画像光 L

50

B が有する青色の波長域は、例えば 450 nm から 490 nm までの波長域を含む。電気光学装置 10B の複数の画素 11B は、青色光を射出する。電気光学装置 10B から射出される画像光 LB は、複数の画素 11B の各々から射出される青色光で構成されている。

#### 【0060】

電気光学装置 10B の基板 14 の表面 14a は、ダイクロイックプリズム 20 の青色光の入射面 21 に対向し、透光性を有する接着剤層 40B を介して入射面 21 に貼り合わされている。言い換えれば、電気光学装置 10B は、画像光 LB が入射面 21 に対して垂直に入射されるように配置されている。

#### 【0061】

電気光学装置 10R は、発光素子として OLED 又は μLED が用いられた装置であり、複数の画素 11R を含む画素領域 12R と、非画素領域 13R と、を備える。画像光 LR が有する赤色の波長域は、例えば 610 nm から 680 nm までの波長域を含む。電気光学装置 10R の複数の画素 11R は、赤色光を射出する。電気光学装置 10R から射出される画像光 LR は、複数の画素 11R の各々から射出される赤色光で構成されている。

#### 【0062】

電気光学装置 10R の基板 14 の表面 14a は、ダイクロイックプリズム 20 の赤色光の入射面 23 に対向し、透光性を有する接着剤層 40R を介して入射面 23 に貼り合わされている。言い換えれば、電気光学装置 10R は、画像光 LR が入射面 23 に対して垂直に入射されるように配置されている。

#### 【0063】

画像光 LG, LB, LR の各々は、偏光特性を有さず、特定の振動方向を有さない無偏光の光である。なお、無偏向の光、すなわち偏光特性を有していない光は、完全に無偏光の状態ではなく、ある程度の偏光成分は含まれているが、例えばダイクロイックミラーを含む光学部品に対して光学性能には積極的に影響を及ぼさないとみなされる範囲の偏光度を有する光である。

#### 【0064】

ダイクロイックプリズム 20 は、四角柱状の形状をなす透光性部材から構成されている。また、四角柱状の透光性部材は、4 個の三角柱状の透光性部材が組み合わされて構成されている。ダイクロイックプリズム 20 は、入射面 21, 22, 23 と、射出面 24 と、を有する。ダイクロイックプリズム 20 は、さらに偏光分離特性を有さない第 1 のダイクロイックミラー 25 と、偏光分離特性を有さない第 2 のダイクロイックミラー 26 と、を有する。第 1 のダイクロイックミラー 25 と第 2 のダイクロイックミラー 26 とは、互いに 90° の角度で交差している。第 1 のダイクロイックミラー 25 は、入射面 21 を介して入射される画像光 LB を射出面 24 に向けて反射し、入射面 22 を介して入射される画像光 LG を射出面 24 に向けて透過する。第 2 のダイクロイックミラー 26 は、入射面 23 を介して入射される画像光 LR を射出面 24 に向けて反射し、入射面 22 を介して入射される画像光 LG を射出面 24 に向けて透過する。第 1 のダイクロイックミラー 25 及び第 2 のダイクロイックミラー 26 の特性によって、画像光 LG, LB, LR が互いに合成されて生成された合成画像光 LW が射出面 24 から射出される。

#### 【0065】

図 9 は、第 1 実施形態の画像表示装置であるヘッドマウントディスプレイ（画像表示装置）1000 の構成を示す概略図である。ヘッドマウントディスプレイ 1000 は、シースルー型のアイグラスディスプレイとして構成され、テンブル 1111, 1112 を左右に備えたフレーム 1110 を有する。虚像表示部 1010 は、フレーム 1110 に支持され、虚像表示部 1010 から射出された画像を不図示の使用者に虚像として認識させる。

#### 【0066】

ヘッドマウントディスプレイ 1000 は、虚像表示部 1010 として、左眼用表示部 1101 と、右眼用表示部 1102 と、を備える。左眼用表示部 1101 と右眼用表示部 1102 とは、同一の構成を有し、左右対称に配置されている。図 10 は、虚像表示部 1010 の光学系の構成を示す斜視図である。図 11 は、図 10 に示す光学系の光路を示す概

10

20

30

40

50

略図であり、導光部 1050 の表面に直交する方向から見たときの図である。図 10 及び図 11 に示すように、左眼用表示部 1101 は、光学装置 1 と、光学装置 1 から射出された合成画像光 LW を射出部 1058 に導く導光系 1030 と、を備える。光学装置 1 と導光系 1030との間に、投写レンズ系 1070 が配置されている。光学装置 1 から射出された合成画像光 LW は、投写レンズ系 1070 を介して導光系 1030 に入射する。投写レンズ系 1070 は、正のパワーを有する 1 つのコリメートレンズによって構成されている。

#### 【0067】

導光系 1030 は、合成画像光 LW が入射する透光性の入射部 1040 と、一方の端 1051 が入射部 1040 に接続された透光性の導光部 1050 と、を備える。入射部 1040 と導光部 1050 とは、互いに一体の透光性部材で構成されている。10

#### 【0068】

入射面 1041 には反射膜が形成されていないが、入射面 1041 は、光透過性及び光反射性を備え、臨界角以上の入射角で入射した光を全反射する。反射面 1042 は、入射面 1041 と対向している。反射面 1042 の一方の端 1422 は、反射面 1042 の他方の端 1421 よりも入射面 1041 から離間している。すなわち、入射部 1040 は、略三角形状の形状を有している。反射面 1042 は、平面、非球面、または自由曲面等からなる。反射面 1042 は、アルミニウム、銀、マグネシウム、クロム等を主成分とする反射性の金属層が形成された構成を有する。20

#### 【0069】

導光部 1050 は、一方の端 1051 から他方の端 1052 に向かって延在する第 1 面 1056 と、第 1 面 1056 に平行に対向して端 1051 から端 1052 に向かって延在する第 2 面 1057 と、第 2 面 1057 の入射部 1040 から離間する部分に設けられた射出部 1058 と、を備える。第 1 面 1056 と入射部 1040 の反射面 1042 とは、斜面 1043 を介して連続している。第 1 面 1056 と第 2 面 1057 との間隔は、入射部 1040 の厚みよりも小さい。第 1 面 1056 及び第 2 面 1057 は、導光部 1050 と外界の空気との屈折率差に基づいて、臨界角以上の入射角で入射した光を全反射する。そのため、第 1 面 1056 及び第 2 面 1057 には反射膜が形成されていない。30

#### 【0070】

射出部 1058 は、導光部 1050 の厚さ方向の第 2 面 1057 側の一部に構成されている。射出部 1058 では、第 2 面 1057 に対して直交する方向に対して傾斜する複数の部分反射面 1055 が互いに平行に配置されている。射出部 1058 は、第 2 面 1057 のうち、複数の部分反射面 1055 に重なる部分であり、導光部 1050 の延在方向において所定の幅を有する。複数の部分反射面 1055 の各々は、誘電体多層膜から構成されている。また、複数の部分反射面 1055 のうちの少なくとも 1 つは、誘電体多層膜と、アルミニウム、銀、マグネシウム、クロムの何れか一種類以上を主成分とする反射性の金属層との複合層であってもよい。部分反射面 1055 が金属層を含んでいる場合、部分反射面 1055 の反射率を高める効果、或いは、部分反射面 1055 の透過率及び反射率の入射角依存性や偏光依存性を適正化することができる。なお、射出部 1058 には、回折格子やホログラムを含む光学素子が設けられてもよい。40

#### 【0071】

上述の構成を備えるヘッドマウントディスプレイ 1000 において、入射部 1040 から入射した平行光からなる合成画像光 LW は、入射面 1041 で屈折し、反射面 1042 に向かって伝搬する。合成画像光 LW は、反射面 1042 で反射され、再び入射面 1041 に向かって伝搬する。その際、合成画像光 LW が入射面 1041 に臨界角以上の入射角で入射するため、合成画像光 LW は、入射面 1041 で導光部 1050 に向けて反射され、導光部 1050 に向かって伝搬する。なお、入射部 1040 では、入射面 1041 及び反射面 1042 が自由曲面によって構成され、非平行光である合成画像光 LW が入射面 1041 に入射した後、反射面 1042 と入射面 1041 との間で反射する間に平行光に変換されてもよい。50

## 【 0 0 7 2 】

導光部 1050 では、合成画像光 LW が第 1 面 1056 と第 2 面 1057 の間で反射して進行する。部分反射面 1055 に入射した合成画像光 LW の一部は、部分反射面 1055 で反射して射出部 1058 から観察者の眼 E に向けて射出される。また、部分反射面 1055 に入射した合成画像光 LW の残りの少なくとも一部は、部分反射面 1055 を透過し、隣り合う次の部分反射面 1055 に入射する。そのため、複数の部分反射面 1055 の各々において反射した合成画像光 LW は、射出部 1058 から観察者の眼 E に向けて射出される。このことによって、観察者は、虚像を認識することができる。その際に、外界から導光部 1050 に入射した光は、導光部 1050 に入射した後、部分反射面 1055 を透過して観察者の眼 E に到達する。このため、観察者は、光学装置 1 から射出されたカラー画像を視認し、外界の景色を所謂シースルーで視認することができる。

10

## 【 0 0 7 3 】

以上説明した第 1 実施形態の電気光学装置 10G は、発光素子 54G と、駆動トランジスター 52G と、中継層（中継電極）T1 と、電極層 A4 と、電極層（導電部材）A6 と、を備える。発光素子 54G は、アノード（第 1 電極）AN と、発光層 EM と、カソード（第 2 電極）と、を含む。駆動トランジスター 52G は、発光素子 54G に対応して設けられている。中継層 T1 は、駆動トランジスター 52G のゲート電極層（ゲート電極）G, G1 と電気的に接続されている。中継層 T1 は、半導体基板 150 の厚み方向と平行な Z 方向において、ゲート電極層 G, G1 と発光素子 54G のアノード AN との間の層間絶縁層（層）L1 に設けられている。電極層 A4 は、中継層 T1 と同層で層間絶縁層 L1 に、すなわち中継層 T1 と同一層に設けられ、電気光学装置 10G の平面視において平面視において例えば X 方向（第 1 の方向）に延在し、発光素子 54G のアノード AN 側の電極層（第 1 電極側）A100 と電気的に接続されている。電極層 A6 は、平面視において中継層 T1 と電極層 A4 との間に設けられている。電極層 A6 には、定電位が供給される。

20

## 【 0 0 7 4 】

第 1 実施形態の電気光学装置 10G の構成において、仮に層間絶縁層 L1 の表面で中継層 T1 と電極層 A4 との間に電極層 A6 すなわち電極層 A6B が介在しない場合、図 3 に例示された選択トランジスター 51G のソース / ドレイン領域のうちの保持容量 55G に電気的に接続されている領域から駆動トランジスター 52G のゲートへの入力と駆動トランジスター 52G のソース / ドレイン領域のうちの電源配線 63 に電気的に接続されている方の領域からの出力との間に、二点鎖線で示す寄生容量が発生する。電極層 A4 の電圧変化は、前述の寄生容量を介して駆動トランジスター 52G のゲート電極 G, G1 と電気的に接続されている中継層 T1 に伝わり、クロストークや画像のちらつきが発生する。第 1 実施形態の電気光学装置 10G では、電極層 A6 の各々の抵抗は電源配線 63 よりも低く、電極層 A6 の各々の電位は電源配線 63 よりも安定している。第 1 実施形態の電気光学装置 10G によれば、平面視で中継層 T1 と電極層 A4 との間に電極層 A6 が設けられているため、駆動トランジスター 52G のゲート電極層 G1 と電気的に接続されている中継層 T1 と電極層 A4 との間を良好にシールドし、中継層 T1 と電極層 A4 との間に從来の電気光学装置で発生していた寄生容量の発生を防止することができる。したがって、第 1 実施形態の電気光学装置 10G におけるクロストークを低減し、画像のちらつきを抑えることができる。

30

## 【 0 0 7 5 】

また、第 1 実施形態の電気光学装置 10G は、半導体基板 150 の N 型ウェル 160 に、P 型の不純物ドーパントを含む P 型拡散領域（拡散領域）Pj と、N 型の不純物ドーパントを含む N 型拡散領域（拡散領域）Nk と、を含む。すなわち、半導体基板 150 には、P 型拡散領域 Pj 及び N 型拡散領域 Nk からなる複数の拡散領域が設けられている。電極層（導電部材）A6 は、複数の拡散領域のうちの N 型拡散領域 N1 と電気的に接続され、例えばコンタクトプラグ C4 によって N 型拡散領域 N1 と電気的に接続されている。第 1 実施形態の電気光学装置 10G によれば、電極層 A6 が半導体基板 150 に比べて強い導電性を有する N 型拡散領域 N1 と電気的に接続されているため、電極層 A6 の電位を安

40

50

定させ、中継層 T 1 と電極層 A 4 との間のシールド効果を高めることができる。したがって、第 1 実施形態の電気光学装置 10 G におけるクロストークを低減し、画像のちらつきをさらに抑えることができる。

#### 【 0 0 7 6 】

また、第 1 実施形態の電気光学装置 10 G では、発光素子 54 G は例えば OLED (有機発光ダイオード) であるため、電極層 A 6 をボディ電源と電気的に接続された端子として用いることができる。

#### 【 0 0 7 7 】

また、第 1 実施形態のヘッドマウントディスプレイ 1000 は、上述の電気光学装置 10 G と、電気光学装置 10 G と同様の構成を備える電気光学装置 10 B, 10 R と、電気光学装置 10 G, 10 B, 10 R の各々から射出された画像光 L G, L B, L R を表示するための光学装置 (光学系) 1、投写レンズ系 (光学系) 1070 及び導光系 (光学系) 1030 を備える。第 1 実施形態のヘッドマウントディスプレイ 1000 によれば、画像光 L G, L B, L R を表示する光学系によって表示された観察対象の画像のクロストークやちらつきを抑えることができる。10

#### 【 0 0 7 8 】

##### [ 第 2 実施形態 ]

次いで、本発明の第 2 実施形態について、図 12 を用いて説明する。

なお、第 2 実施形態以降の各実施形態において、上位の実施形態と共に通する構成には、当該構成と同じ符号を付し、その説明を省略する。第 2 実施形態以降の各実施形態では、上位の実施形態とは異なる構成や内容について主に説明する。また、第 2 実施形態以降の各実施形態の電気光学装置を備えた光学装置及び画像表示装置は、第 1 実施形態で説明した光学装置 1 及びヘッドマウントディスプレイ 1000 の各々における電気光学装置 10 G, 10 B, 10 R を各実施形態の電気光学装置に置き換えたものである。20

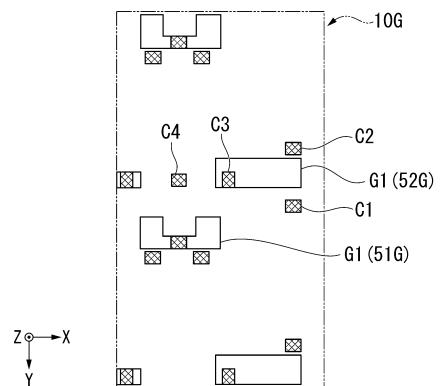

#### 【 0 0 7 9 】

第 2 実施形態の電気光学装置 10 G の画素 11 G の画素回路は、第 1 実施形態の画素 11 G の画素回路と同様の構成を備える。図 12 は、第 2 実施形態の画素 11 G の画素回路の層間絶縁層 L 1 の表面での平面視のレイアウトを示す概略図である。第 2 実施形態の画素 11 G の画素回路のゲート絶縁層 L 0 の表面での平面視のレイアウト、及び図 5 に示す X 1 - X 2 線で矢視した場合の断面は、第 1 実施形態と同様である。30

#### 【 0 0 8 0 】

図 12 に示すように、第 2 実施形態の電気光学装置 10 G の画素 11 G の画素回路では、電極層 A 6 は、電極層 A 6 A, A 6 B, A 6 C に加えて電極層 A 6 D を備える。電極層 A 6 D は、平面視で電極層 A 6 B において電極層 A 6 C と電気的に接続されている一方の端とは反対側の他方の端と電極層 A 6 A とを連結し、V 方向に沿って延在している。すなわち、中継層 T 1 は、電極層 A 6 A ~ A 6 D からなる電極層 A 6 によって囲まれた領域に配置されている。また、第 2 実施形態の電気光学装置 10 G の画素 11 G の画素回路では、第 1 実施形態と同様に、電極層 A 4 は、中継層 T 1 と同じく層間絶縁層 L 1 の表面に設けられ、中継層 T 1 と同層に設けられている。30

#### 【 0 0 8 1 】

第 2 実施形態の電気光学装置 10 G の製造方法は、第 1 実施形態の電気光学装置 10 G の製造方法と同様である。但し、層間絶縁層 L 1 の表面に電極層 A 3, A 4, A 6 及び中継層 T 1 の各々を形成する際には、平面視で図 12 に示すレイアウトと一致したパターンを有するマスクを用いる。40

#### 【 0 0 8 2 】

上述説明した第 2 実施形態の電気光学装置 10 G は、第 1 実施形態の電気光学装置 10 G と同様の構成を備えるため、第 1 実施形態の電気光学装置 10 G と同様の作用効果を奏する。また、第 2 実施形態の電気光学装置 10 G では、中継層 (中継電極) T 1 は、平面視で電極層 (導電部材) A 6 によって囲まれている。中継層 (中継電極) T 1 は、平面視で層間絶縁層 (絶縁層) L 2 を介して電極層 (導電部材) A 6 と隣り合い、層間絶縁層 L 50

2を介して電極層A6に囲まれて配置されている。第2実施形態の電気光学装置10Gによれば、平面視で中継層T1の周囲の全方位で想定外の寄生容量の発生を防止し、中継層T1と電極層A4との間に留まらずに中継層T1に対するシールド効果を高めることができる。したがって、第1実施形態の電気光学装置10Gにおけるクロストークを低減し、画像のちらつきをさらに抑えることができる。

### 【0083】

#### [第3実施形態]

次いで、本発明の第3実施形態について、図13から図20を用いて説明する。

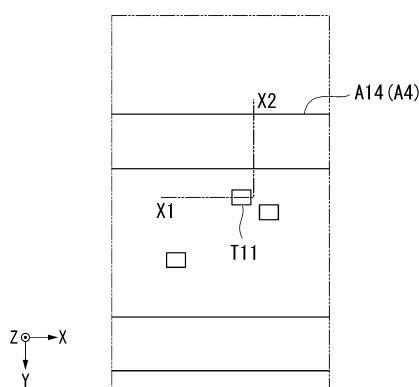

### 【0084】

第3実施形態の電気光学装置10Gの画素11Gの画素回路は、第1実施形態の画素11Gの画素回路と同様の構成を備える。図13は、第3実施形態の画素11Gの画素回路の層間絶縁層L1の表面での平面視のレイアウトを示す概略図である。図14は、第3実施形態の画素11Gの画素回路のゲート絶縁層L0の表面での平面視のレイアウトを示す概略図である。図15は、第3実施形態の画素11Gの画素回路の層間絶縁層L2の表面での平面視のレイアウトを示す概略図である。図16は、図13から図15に示すレイアウトで形成された画素回路の構成を示す図であり、図13及び図15に示すX1-X2線で矢視した場合の断面図である。図16では、電極層A14よりも上層すなわちZ方向の前方の構成は省略されているが、電極層A14は発光素子54GのアノードANの電極層A100と電気的に接続されている。

10

### 【0085】

図13から図16に示すように、第3実施形態の電気光学装置10Gの画素11Gの画素回路では、第2実施形態で説明した構成及び配置において、最上の電極層A14は、例えば層間絶縁層L2の表面に設けられ、中継層T1とは異なる層に設けられている。また、第3実施形態の電気光学装置10Gの画素11Gの画素回路では、平面視で駆動トランジスター52Gの電極層A6の少なくとも一部がゲート電極層G1と重なっている。具体的には、ゲート絶縁層L0の表面でゲート電極層G1の電極層A4に近い方の端部が平面視で中継層T1よりも電極層A4に近づく方向に延出している。

20

### 【0086】

第3実施形態の電気光学装置10Gの製造方法は、第1実施形態の電気光学装置10Gの製造方法と概ね同様である。但し、層間絶縁層L1の表面に電極層A3,A6及び中継層T1の各々を形成する際には、平面視で図13に示すレイアウトと一致したパターンを有するマスクを用いる。層間絶縁層L1の表面に電極層A3,A6及び中継層T1の各々を形成する工程で用いるマスクでの電極層A6のパターンは平面視でゲート電極層G1を形成するための層間絶縁層L1の穴が形成された領域の少なくとも一部と重なる。

30

### 【0087】

上述説明した第3実施形態の電気光学装置10Gは、第2実施形態の電気光学装置10Gと同様の構成を備えるため、第2実施形態の電気光学装置10Gと同様の作用効果を奏する。図16に例示したように、電極層A14と中継層T1とが互いに同層に設けられていなくても、平面視で電極層A14と中継層T1との間に電極層A6が設けられることによって、電極層A14と中継層T1とのシールド効果は作用する。また、第3実施形態の電気光学装置10Gでは、電極層(導電部材)A6の少なくとも一部は、平面視でゲート電極層(ゲート電極)G1と重なっている。第3実施形態の電気光学装置10Gによれば、図16に示すように、平面視で電極層A6とゲート電極層G1とが互いに重なっている領域の間に保持容量D10を構成し、保持容量D10を画素容量として用いることができる。

40

### 【0088】

図17から図20の各々は、第3実施形態の電気光学装置10Gの画素11Gの画素回路の変形例の構成を示す概略図である。図17は、第3実施形態の変形例の画素11Gの画素回路における層間絶縁層L1の表面での平面視のレイアウトを示す概略図である。第3実施形態の変形例の画素11Gの画素回路におけるゲート絶縁層L0の表面での平面視

50

のレイアウトは、第3実施形態と同様である。図18は、第3実施形態の変形例の画素11Gの画素回路における層間絶縁層L2の表面での平面視のレイアウトを示す概略図である。図19は、図14、図17及び図18に示すレイアウトで形成された画素回路の構成を示す図であり、図17及び図18に示すX1-X2線で矢視した場合の断面図である。図20は、図14、図17及び図18に示すレイアウトで形成された画素回路の構成を示す図であり、図17に示すX3-X4線で矢視した場合の断面図である。図19及び図20では、電極層A14よりも上層すなわちZ方向の前方の構成は省略されているが、電極層A14は発光素子54GのアノードANの電極層A100と電気的に接続されている。

#### 【0089】

第3実施形態の変形例の電気光学装置10Gの画素11Gの画素回路では、図17から図19に示すように、例えば平面視で中継層T1と電極層A4,A14との間に、電極層A6,A16が設けられている。前述のように、中継層T1と電極層A4,A6の各々は、層間絶縁層L1の表面上に設けられている。また、電極層A14,A16の各々は、層間絶縁層L2の表面上に設けられている。さらに、ゲート電極層G1は、平面視で中継層T1及び電極層A6,A16と重なっている。このようなレイアウトによって、電極層A6とゲート電極層G1との間に、保持容量D10が構成される。また、電極層A16とゲート電極層G1との間に、保持容量D12が構成される。

#### 【0090】

図17、図18及び図20に示すように、例えば平面視で中継層T11と電極層A14との間に、電極層A16が設けられている。この抽出領域では、層間絶縁層L1の表面上のゲート電極層G1に加えて層間絶縁層L2の表面上の中継層T1が電極層A16と平面視で重なる位置まで延在している。このようなレイアウトでは、電極層A16とゲート電極層G1と電気的に同等な中継層T1との間に、保持容量D14が構成される。

#### 【0091】

上述説明した第3実施形態の変形例の電気光学装置10Gによれば、第3実施形態の電気光学装置10Gと同様に、平面視で電極層A6,A16とゲート電極層G1とが互いに重なっている領域の間に保持容量D10,D12,D14を構成し、保持容量D10,D12,D14を画素容量として用いることができる。

#### 【0092】

以上、本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。また、複数の実施形態の構成要素は適宜組み合わせ可能である。上述の各実施形態については、特筆すべき作用効果を説明しているが、詳細を説明していなくても、自身の光源装置が備える構成が当てはまる他の実施形態の作用効果が得られる。

#### 【0093】

例えば、第1実施形態から第3実施形態の電気光学装置の画素の画素回路について各図面を参照して説明した電極層、中継層、ゲート電極層の相対的なレイアウトは本発明に含まれる一例である。後述する特許請求の範囲の範囲内でレイアウトは適宜変更可能であり、例えば第3実施形態の変形例で説明したように電極層、中継層、ゲート電極層の各々を形成するZ方向の位置、すなわち電極層、中継層、ゲート電極層の各々を形成する絶縁層の選択、及び平面視での電極層、中継層、ゲート電極層の各々の形状との組み合わせによって、電極層、中継層、ゲート電極層の相対的なレイアウトは自在に設計され、レイアウトの種類及び数は特に限定されない。

#### 【0094】

また、本発明に係る電気光学装置を備えた画像表示装置としてヘッドマウントディスプレイについて説明したが、本発明に係る画像表示装置は、ヘッドマウントディスプレイに限定されず、例えばプロジェクター、電子ビューファインダー(Electronic View Finder; EVF)、携帯可能な情報端末、タブレット機器や腕時計であつてもよい。

10

20

30

40

50

## 【0095】

図21は、上述の電気光学装置10G, 10B, 10Rを備えたプロジェクター200の構成を示す概略図である。例えば、図21に示すように、プロジェクター200は、上述の光学装置1と、光学装置1から射出された合成画像光LWをスクリーン2200に拡大して投射する投射光学系(光学系)2100と、を備える。プロジェクター200によれば、スクリーン2200に投射される合成画像光LWのホワイトバランスの最適化を図り、電気光学装置10Rと比較して電気光学装置10G, 10Bの各々の消費電力を低減することができる。

## 【0096】

本発明の態様の電気光学装置は、以下の構成を有していてもよい。

10

[1] 本発明の一つの態様の電気光学装置は、第1電極と発光層と第2電極とを含む発光素子と、発光素子に対応して設けられる駆動トランジスターと、駆動トランジスターのゲート電極と電気的に接続され、ゲート電極と発光素子の第1電極との間の層に設けられる中継電極と、中継電極と同一層に設けられ、平面視において第1の方向に延在し、発光素子の第1電極と電気的に接続される電源配線と、平面視において中継電極と電源配線との間に設けられ、定電位が供給される導電部材と、を備える。

## 【0097】

[2] 上述[1]に記載の電気光学装置において、半導体基板に不純物を含む拡散領域を含み、導電部材は、拡散領域に電気的に接続されていてもよい。

20

## 【0098】

[3] 上述[2]に記載の電気光学装置において、中継電極は、平面視で導電部材によって囲まれていてもよい。

## 【0099】

[4] 上述[3]に記載の電気光学装置において、平面視で絶縁層を介して導電部材と隣り合って設けられていてもよい。

## 【0100】

[5] 上述[1]又は[2]に記載の電気光学装置において、導電部材の少なくとも一部は、平面視でゲート電極と重なっていてもよい。

## 【0101】

[6] 上述[1]から[5]の何れかに記載の電気光学装置において、発光素子は有機発光ダイオードであってもよい。

30

## 【0102】

[7] 本発明の一つの態様の画像表示装置は、上述[1]から[6]の何れかに記載の電気光学装置と、電気光学装置から射出された画像光を表示する光学系と、を備える。

## 【符号の説明】

## 【0103】

54G…発光素子、150…半導体基板、1000…ヘッドマウントディスプレイ(画像表示装置)、2000…プロジェクター(画像表示装置)、A4…電極層(電源配線)、A6…電極層(導電部材)、AN…アノード(第1電極)、CT…カソード(第2電極)、EM…発光層、G, G1…ゲート電極層(ゲート電極)、L0…ゲート絶縁層(第1層)、L1…層間絶縁層(第3層)、L3…層間絶縁層(第2層)、N1, Nk…N型拡散領域(拡散領域)、P1~P6, Pj…P型拡散領域(拡散領域)、T1, T11…中継層(中継電極)

40

50

【図面】

【図1】

【図2】

10

20

30

40

【図3】

【図4】

50

【図5】

【図6】

10

20

30

40

50

【図7】

【図8】

10

20

30

40

50

【図9】

【 図 1 0 】

【 図 1 1 】

【図12】

10

20

30

40

50

【図13】

【図14】

10

【図15】

【図16】

20

【図17】

【図18】

30

40

50

【図19】

【図20】

10

20

30

40

50

【図21】

---

フロントページの続き

F ターム (参考) DD39 DD93 EE03 EE21

5C094 AA09 BA03 BA27 CA19 DA13 EB05 ED05 HA03 HA08