(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5977947号

(P5977947)

(45) 発行日 平成28年8月24日(2016.8.24)

(24) 登録日 平成28年7月29日(2016.7.29)

(51) Int.Cl.

F 1

|            |           |            |           |             |           |            |           |             |           |

|------------|-----------|------------|-----------|-------------|-----------|------------|-----------|-------------|-----------|

| HO1L 21/02 | (2006.01) | HO1L 27/12 | (2006.01) | HO1L 21/265 | (2006.01) | HO1L 21/20 | (2006.01) | HO1L 21/336 | (2006.01) |

|            |           |            |           |             |           |            |           |             |           |

|            |           |            |           |             |           |            |           |             |           |

|            |           |             |           |            |           |            |      |

|------------|-----------|-------------|-----------|------------|-----------|------------|------|

| HO1L 27/12 | (2006.01) | HO1L 21/265 | (2006.01) | HO1L 21/20 | (2006.01) | HO1L 29/78 | 627D |

|            |           |             |           |            |           |            |      |

|            |           |             |           |            |           |            |      |

請求項の数 2 (全 21 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2012-1723 (P2012-1723)      |

| (22) 出願日     | 平成24年1月9日(2012.1.9)           |

| (65) 公開番号    | 特開2012-160713 (P2012-160713A) |

| (43) 公開日     | 平成24年8月23日(2012.8.23)         |

| 審査請求日        | 平成27年1月7日(2015.1.7)           |

| (31) 優先権主張番号 | 特願2011-5490 (P2011-5490)      |

| (32) 優先日     | 平成23年1月14日(2011.1.14)         |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 肥塚 純一<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 右田 勝則                                          |

最終頁に続く

(54) 【発明の名称】 SOI 基板の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板中に炭素及び水素を含むクラスタイオンを照射し、前記炭素及び水素を含むクラスタイオンが照射された半導体基板中に、水素イオンを照射して、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させて、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成することを特徴とする SOI 基板の作製方法。

## 【請求項 2】

半導体基板中に炭素及び水素を含むクラスタイオンを照射し、前記炭素及び水素を含むクラスタイオンが照射された半導体基板中に、水素イオンを照射して、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させて、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成し、前記半導体層にレーザ光を照射することを特徴とする SOI 基板の作製方法。

## 【発明の詳細な説明】

**【技術分野】****【0001】**

開示される発明の一態様は、S O I 基板の作製方法に関する。

**【背景技術】****【0002】**

近年、バルク状のシリコンウェハに代わり、絶縁表面に薄い単結晶半導体層が存在するS O I (Silicon on Insulator) 基板を使った集積回路が開発されている。S O I 基板を使うことで、トランジスタのドレインと基板間における寄生容量が低減されるため、S O I 基板は半導体集積回路の性能を向上させるものとして注目されている。

10

**【0003】**

S O I 基板を製造する方法の1つに、水素イオン注入剥離法が知られている（例えば、特許文献1参照）。水素イオン注入剥離法によるS O I 基板の作製方法の概要を以下に説明する。まず、シリコンウェハにイオン注入法を用いて水素イオンを注入することによって表面から所定の深さに微小気泡層を形成する。次に、酸化シリコン膜を介して、水素イオンを注入したシリコンウェハを別のシリコンウェハに接合させる。その後、熱処理を行うことにより、微小気泡層が劈開面となり、水素イオンが注入されたシリコンウェハの一部が微小気泡層を境に薄膜状に分離し、接合させた別のシリコンウェハ上に単結晶シリコン膜を形成することができる。

**【0004】**

また、このような水素イオン注入剥離法を用いて単結晶シリコン層をガラスからなるベース基板上に形成する方法が提案されている（例えば、特許文献2参照）。ガラス基板はシリコンウェハよりも大面積化が可能であり且つ安価な基板であるため、ガラス基板をベース基板として用いることにより、大面積で安価なS O I 基板を作製することが可能となる。

20

**【0005】**

単結晶半導体基板に加速した水素イオンを照射して、特定の深さに水素イオンを注入、またはドーピングして脆化領域を形成する。次いで加熱処理して当該脆化領域が含む水素を気体化し、さらに水素を膨張せしめて、劈開面を当該脆化領域に形成する。

**【先行技術文献】**

30

**【特許文献】****【0006】**

【特許文献1】特開2000-124092号公報

【特許文献2】特開2002-170942号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

しかしながら、照射された水素イオンが全て分離に寄与するわけではない。照射された水素イオンは、照射中又は分離のための熱処理中にシリコンウェハ中に拡散してしまい、一部はシリコンウェハから脱離してしまう。そのため、分離に必要な水素イオンの量よりも多くの量の水素イオンを照射しなければならなかった。

40

**【0008】**

またシリコンウェハ中に照射された水素イオンが拡散すると、水素イオンの濃度分布が不均一となる。シリコンウェハ中の水素イオンの濃度分布が不均一となると、シリコンウェハからベース基板上に分離した半導体層の表面の凹凸が大きくなるという問題が生じる。

**【0009】**

またベース基板上に分離した半導体層の結晶性を回復するために、レーザ照射等の熱処理を行った場合、多量の水素イオンが照射された半導体層は、熱処理を行っても欠陥や転位等が残留してしまい、十分に結晶性が回復しない恐れがある。結晶性が回復しない半導体層を用いて半導体装置を作製すると、当該半導体装置の特性が悪化する恐れがある。

50

**【 0 0 1 0 】**

さらに上述のように、ベース基板上に分離した半導体層の表面の凹凸が大きい場合に、レーザ照射等の熱処理を行うと、半導体層の表面に孔が生じる恐れがある。

**【 0 0 1 1 】**

以上を鑑みて、開示される発明の一様態では、単結晶半導体基板に照射した水素イオンの単結晶半導体基板からの脱離を抑制することを課題の一とする。

**【 0 0 1 2 】**

また開示される発明の一様態では、結晶性のよい半導体層を有するSOI基板を得ることを課題の一とする。

**【 0 0 1 3 】**

また開示される発明の一様態では、表面の凹凸が少ない半導体層を有するSOI基板を得ることを課題の一とする。

**【課題を解決するための手段】****【 0 0 1 4 】**

開示される発明の一様態では、水素イオンの拡散を抑制する炭素イオンを照射することにより、単結晶半導体基板に注入された水素イオンの脱離を抑制する。

**【 0 0 1 5 】**

結晶性珪素中の水素拡散は、イオン注入等で導入される過剰な格子間珪素と結合することで加速する。一方、炭素は、このような格子間珪素と容易に結合する。炭素がこのような格子間珪素と結合するため、水素の拡散を抑制することができる。

20

**【 0 0 1 6 】**

開示される発明の一様態は、半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製方法に関する。

**【 0 0 1 7 】**

開示される発明の一様態において、当該半導体基板中の当該炭素濃度の極大値と当該水素濃度の極大値が同じ深度、又は、当該炭素濃度の極大値が当該水素濃度の極大値よりもより浅い深度に位置することを特徴とする。

30

**【 0 0 1 8 】**

開示される発明の一様態において、当該半導体基板上に絶縁層を形成し、当該絶縁層が形成された半導体基板中に、当該炭素イオンを照射することを特徴とする。

**【 0 0 1 9 】**

開示される発明の一様態において、当該炭素イオンが照射された半導体基板上に、絶縁層を形成することを特徴とする。

**【 0 0 2 0 】**

開示される発明の一様態は、半導体基板中に、炭素及び水素を含むクラスタイオンを照射して、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製方法に関する。

40

**【 0 0 2 1 】**

開示される発明の一様態において、当該半導体基板中の当該炭素濃度の極大値と当該水素濃度の極大値が同じ深度、又は、当該炭素濃度の極大値が当該水素濃度の極大値よりもより浅い深度に位置することを特徴とする。

**【 0 0 2 2 】**

開示される発明の一様態において、当該炭素及び水素を含むクラスタイオンの照射後に、

50

当該半導体基板中に水素イオンを照射することを特徴とする。

【0023】

開示される発明の一様態において、当該半導体基板上に絶縁層を形成し、当該絶縁層が形成された半導体基板中に、当該炭素と水素を含むクラスタイオンを照射することを特徴とする。

【0024】

開示される発明の一様態において、当該炭素と水素を含むクラスタイオンが照射された半導体基板上に、絶縁層を形成することを特徴とする。

【0025】

一般に、「SOI基板」は絶縁表面上にシリコン層が設けられた構成の半導体基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の半導体基板をも含む概念として用いる。つまり、「SOI基板」が有する半導体層は、シリコン層に限定されない。また、本明細書等において、半導体基板は、半導体材料のみからなる基板を指すに留まらず、半導体材料を含む基板全般を示すものとする。つまり、本明細書等においては「SOI基板」も広く半導体基板に含まれる。

10

【0026】

なお、本明細書等において単結晶とは、ある結晶軸に注目した場合、その結晶軸の方向が試料のどの部分においても同様の方向を向いているものをいう。つまり、結晶欠陥やダングリングボンドなどを含んでいても、上記のように結晶軸の方向が揃っているものは単結晶として扱う。

20

【0027】

また、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、表示装置や、集積回路は半導体装置に含まれる。また、本明細書等において表示装置とは、発光表示装置や液晶表示装置、電気泳動素子を用いた表示装置を含む。発光表示装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(ELectro Luminescence)、有機EL等がある。

【0028】

なお、第1、第2、又は第3として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

30

【発明の効果】

【0029】

開示される発明の一様態により、単結晶半導体基板に照射した水素イオンの単結晶半導体基板からの脱離を抑制することができる。

【0030】

また開示される発明の一様態により、結晶性のよい半導体層を有するSOI基板を得ることができる。

【0031】

また開示される発明の一様態により、表面の凹凸が少ない半導体層を有するSOI基板を得ることができる。

40

【図面の簡単な説明】

【0032】

【図1】SOI基板の作製工程を示す断面図。

【図2】SOI基板の作製工程を示す断面図。

【図3】SOI基板の作製工程を示す断面図。

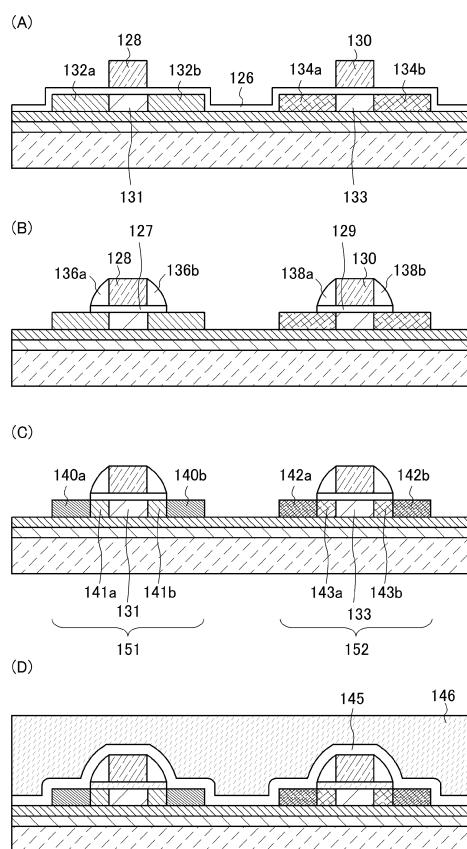

【図4】半導体装置の作製工程を示す断面図。

【図5】半導体装置の作製工程を示す断面図。

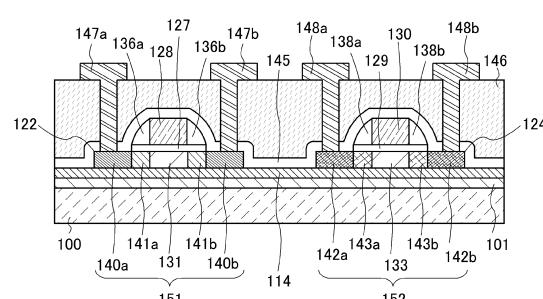

【図6】半導体装置の作製工程を示す断面図。

【発明を実施するための形態】

50

## 【0033】

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することが可能であり、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

## 【0034】

## [実施の形態1]

まずボンド基板として半導体基板110を用意する。半導体基板110としては、多結晶半導体基板または単結晶半導体基板を用いることができる。半導体基板110としては、例えば、多結晶または単結晶のシリコン基板やゲルマニウム基板、シリコンゲルマニウム基板、炭化シリコン基板などの第14族元素でなる半導体基板、またヒ化ガリウム（ガリウムヒ素ともいう）やリン化インジウム（インジウムリンともいう）等の化合物半導体基板が挙げられる。シリコン基板としては、直径5インチ（125mm）、直径6インチ（150mm）、直径8インチ（200mm）、直径12インチ（300mm）サイズの円形のものが代表的である。なお、形状は円形に限らず矩形状等に加工したシリコン基板を用いることも可能である。なお、特段の断りが無い限り、矩形には正方形が含まれることとする。以下の説明では、半導体基板110として、矩形状に加工された単結晶シリコン基板（シリコンウェハ）を用いる場合について示す。

10

## 【0035】

また一方で、ベース基板100を用意する。ベース基板100には、液晶表示装置などに使用されている透光性を有するガラス基板を用いることができる。ガラス基板としては、歪み点が600以上であるものを用いることが好ましい。また、ガラス基板は無アルカリガラス基板であることが好ましい。無アルカリガラス基板には、例えば、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。ベース基板100として大面積化が可能で安価なガラス基板を用いることにより、シリコン基板を用いる場合と比較して低コスト化を図ることができる。

20

## 【0036】

また、ベース基板100として、セラミック基板、石英基板やサファイア基板などの絶縁体でなる基板、シリコンなどの半導体基板、金属やステンレスなどの導電体でなる基板などを用いることもできる。他にも、ベース基板100として、作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。以下の説明では、ベース基板100として、矩形状に加工されたガラス基板を用いる場合について示す。

30

## 【0037】

なおベース基板100上には、絶縁層101を形成する。絶縁層101の形成方法は特に限定されないが、例えば、スパッタリング法、プラズマCVD法などを用いることができる。絶縁層101は、貼り合わせに係る表面を有する層であるから、その表面が、高い平坦性を有するように形成されることが好ましい。絶縁層101は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウムなどから選ばれた一または複数の材料を用いて形成することができる。例えば、酸化シリコンを用いて絶縁層101を形成する場合には、有機シランガスを用いて化学気相成長法により形成することで極めて平坦性に優れた絶縁層101を得ることができる。なお、本実施の形態においては絶縁層101を単層構造としているが、積層構造としても良い。また貼り合わせに際して特に問題がない場合など、絶縁層101を設ける必要がない場合には、絶縁層101を設けない構成としてもよい。

40

## 【0038】

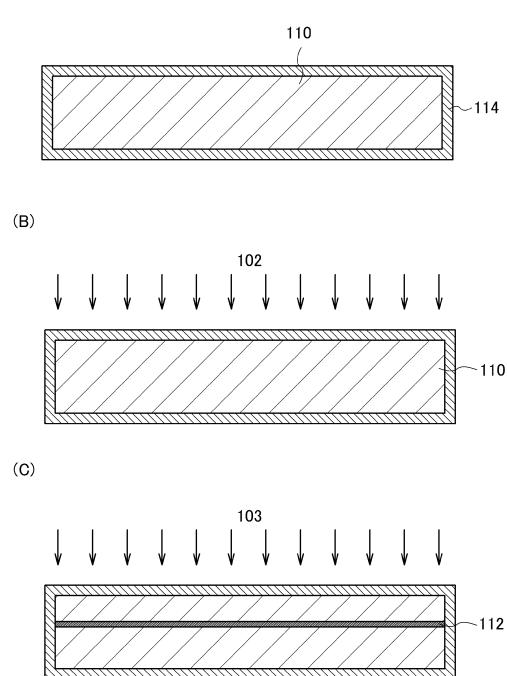

次に、半導体基板110に絶縁層114を形成する（図2（A）参照）。

## 【0039】

50

絶縁層 114 は、例えば、酸化シリコン層、酸化窒化シリコン層、窒化シリコン層、窒化酸化シリコン層等の単層、又はこれらを積層させた層を用いることができる。これらの層は、CVD法又はスパッタリング法等を用いて形成することができる。また、CVD法を用いて絶縁層 114 を形成する場合には、テトラエチルオルソシリケート（略称；TEOS：化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ）等の有機シランを用いて作製される酸化シリコン層を絶縁層 114 に用いることが生産性の点から好ましい。

#### 【0040】

なお、酸化窒化シリコン層とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）、及び水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 15 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒化酸化シリコン層とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 50 原子%、Si が 25 ~ 35 原子%、水素が 15 ~ 25 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

#### 【0041】

また、絶縁層 114 は、半導体基板 110 に熱酸化処理を行うことにより形成してもよい。この場合、熱酸化処理は、ハロゲンを添加した酸化性雰囲気中で熱処理を行うことが好ましい。このような熱酸化処理の一例としては、酸素に対し塩化水素（HCl）を 0.5 ~ 10 体積%（好ましくは 3 体積%）の割合で含む雰囲気中で、900 ~ 1150 の温度（たとえば 950 ）で熱酸化処理を行うと良い。処理時間は 0.1 ~ 6 時間、好ましくは 0.5 ~ 1 時間とすれば良い。形成される酸化層の厚さとしては、10 nm ~ 100 nm（好ましくは 50 nm ~ 200 nm）、例えば 100 nm の厚さとする。

#### 【0042】

本実施の形態では、半導体基板 110 に塩化水素（HCl）を含む雰囲気中で熱酸化処理を行うことにより、絶縁層 114（ここでは、酸化シリコン層）を形成する。従って、絶縁層 114 は、塩素原子を含有した層となる。

#### 【0043】

なお本実施の形態では、半導体基板 110 の全面に絶縁層 114 を形成しているが、ベース基板 100 と貼り合わせる面（すなわち後述の工程で、炭素イオン 102 や水素イオン 103 が照射される面）上のみに絶縁層 114 を形成してもよい。さらに貼り合わせに際して特に問題がない場合など、絶縁層 114 を設ける必要がない場合には、絶縁層 114 を設けない構成としてもよい。

#### 【0044】

次に、絶縁層 114 が形成された半導体基板 110 に炭素イオン 102 を照射する（図 2 (B) 参照）。

#### 【0045】

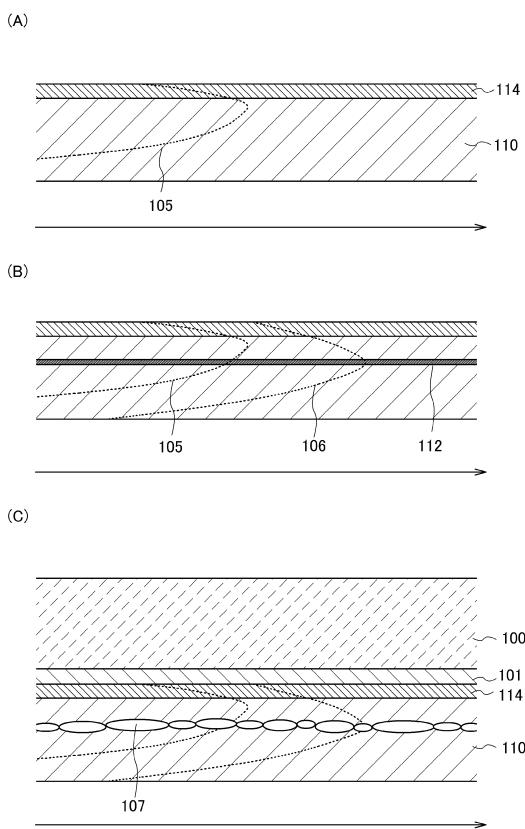

また、半導体基板 110 中の炭素の濃度分布を図 1 (A) に示す。図 1 (A) 中曲線 105 に示される半導体基板 110 中の炭素濃度は、所定の深度に極大値を有する。なお図 1 (A) ~ 図 1 (C) の矢印は、炭素濃度及び水素濃度の大小を示す。炭素濃度及び水素濃度は、図 1 (A) ~ 図 1 (C) の矢印の方向に増大する。

#### 【0046】

炭素イオン 102 を半導体基板 110 に添加する際には、イオン注入装置またはイオンドーピング装置を用いることができる。イオン注入装置は、ソースガスを励起してイオン種を生成し、生成されたイオン種を質量分離して、所定の質量を有するイオン種を被処理物に照射する。イオンドーピング装置は、プロセスガスを励起してイオン種を生成し、生成されたイオン種を質量分離せずに被処理物に照射する。

10

20

30

40

50

## 【0047】

イオンドーピング装置を用いる場合の炭素イオンの照射工程は、例えば、以下の条件で行うことができる。

## 【0048】

加速電圧が、10 keV以上100 keV以下、例えば90 keVである。

## 【0049】

ドーザ量が、 $1 \times 10^{14}$  ions/cm<sup>2</sup>以上 $2 \times 10^{16}$  ions/cm<sup>2</sup>以下、例えば $1 \times 10^{15}$  ions/cm<sup>2</sup>である。

## 【0050】

イオンドーピング装置を用いる場合、ソースガスとして炭素を含むガスを用いる。該炭素を含むガスを用いることによりイオン種としてC<sup>+</sup>を生成することができる。また、炭素イオン102の照射を複数回に分けて行ってもよい。

10

## 【0051】

なお本実施の形態では、炭素イオン102の照射を絶縁層114形成後に行うがこれに限定されない。半導体基板110への炭素イオン102の照射は、絶縁層114の形成前に行ってもよい。ただし、絶縁層114として、半導体基板110に熱酸化処理を行うことにより熱酸化膜を形成する場合、炭素イオン102の照射は当該熱酸化膜形成後に行う。なぜなら、炭素イオン102照射後に熱酸化処理を行うと、半導体基板110中の炭素は熱酸化処理により拡散してしまうからである。

20

## 【0052】

次に、絶縁層114が形成された半導体基板110に水素イオン103を照射する。これにより、半導体基板110中に脆化領域112を形成する(図2(C)参照)。例えば、加速された水素イオン103でなるイオンビームを照射して、半導体基板110の表面から所定の深さの領域に脆化領域112を形成する。脆化領域112が形成される深さは、イオンビームの加速エネルギー やイオンビームの入射角によって制御される。つまり、脆化領域112は、水素イオン103の平均侵入深さと同程度の深さの領域に形成されることになる。ここで、脆化領域112が形成される深さは、半導体基板110の表面から均一であることが望ましい。

## 【0053】

上述の脆化領域112が形成される深さにより、半導体基板110から分離される半導体層の厚さが決定される。脆化領域112が形成される深さは、半導体基板110の表面から50 nm以上1 μm以下であり、好ましくは50 nm以上300 nm以下である。

30

## 【0054】

また、半導体基板110中の水素の濃度分布を図1(B)に示す。図1(B)中曲線106に示される半導体基板110中の炭素濃度は、所定の深度に極大値を有する。なお炭素濃度の極大値と水素濃度の極大値について、炭素濃度の極大値と水素濃度の極大値を同じ深度に位置させる、または炭素濃度の極大値を水素濃度の極大値よりも浅い深度に位置させる(すなわち半導体基板110の表面により近づける)ことが望ましい。炭素濃度の極大値を水素濃度の極大値よりも浅い深度に位置していると、水素イオンが半導体基板110の表面側に拡散するのを抑制することができるので好適である。

40

## 【0055】

水素イオン103を半導体基板110に照射する際には、イオン注入装置またはイオンドーピング装置を用いることができる。イオン注入装置は、ソースガスを励起してイオン種を生成し、生成されたイオン種を質量分離して、所定の質量を有するイオン種を被処理物に照射する。イオンドーピング装置は、プロセスガスを励起してイオン種を生成し、生成されたイオン種を質量分離せずに被処理物に照射する。

## 【0056】

イオンドーピング装置を用いる場合の脆化領域112の形成工程は、例えば、以下の条件で行うことができる。

## 【0057】

50

加速電圧が、10 keV以上100 keV以下、例えば50 keVである。

【0058】

ドーズ量が、 $5 \times 10^{15}$  ions / cm<sup>2</sup>以上 $4 \times 10^{16}$  ions / cm<sup>2</sup>以下、例えば $1 \times 10^{16}$  ions / cm<sup>2</sup>である。

【0059】

先の工程で半導体基板110中に炭素が添加されているので、添加された水素は半導体基板110中から脱離しない。そのため、炭素を添加しない場合に比べて、水素イオン103のドーズ量を低減させることができる。

【0060】

ビーム電流密度が、 $2 \mu\text{A} / \text{cm}^2$ 以上(好ましくは $5 \mu\text{A} / \text{cm}^2$ 以上、より好ましくは $10 \mu\text{A} / \text{cm}^2$ 以上)である。

【0061】

イオンドーピング装置を用いる場合、ソースガスとして水素を含むガスを用いる。該水素を含むガスを用いることによりイオン種としてH<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>を生成することができる。水素を含むガスをソースガスとして用いる場合には、H<sub>3</sub><sup>+</sup>を多く照射することが好ましい。具体的には、イオンビームに、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>の総量に対してH<sub>3</sub><sup>+</sup>が70%以上含まれるようにすることが好ましい。また、H<sub>3</sub><sup>+</sup>イオンの割合を80%以上とすることがより好ましい。このようにH<sub>3</sub><sup>+</sup>の割合を高めておくことで、脆化領域112に $1 \times 10^{21}$  atoms / cm<sup>3</sup>以上の濃度で水素を含ませることが可能である。これにより、脆化領域112における分離が容易になる。また、H<sub>3</sub><sup>+</sup>を多く照射することで、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>を照射する場合より短時間で脆化領域112を形成することができる。また、H<sub>3</sub><sup>+</sup>を用いることで、水素イオン103の平均侵入深さを浅くすることができるため、脆化領域112を浅い領域に形成することができる。

【0062】

イオン注入装置を用いる場合には、質量分離により、H<sub>3</sub><sup>+</sup>が照射されるようにすることが好ましい。もちろん、H<sup>+</sup>やH<sub>2</sub><sup>+</sup>を照射してもよい。ただし、イオン注入装置を用いる場合には、イオン種を選択して照射するため、イオンドーピング装置を用いる場合と比較して、イオン照射の効率が低下する場合がある。

【0063】

また、水素イオン103の照射を複数回に分けて行うことで、脆化領域112を形成することもできる。この場合、ソースガスを異ならせてイオン照射を行っても良いし、同じソースガスを用いてもよい。例えば、ソースガスとして希ガスを用いてイオン照射を行った後、水素を含むガスをソースガスとして用いてイオン照射を行うことができる。また、始めにハロゲンガスまたはハロゲン化合物ガスを用いてイオン照射を行い、次に、水素を含むガスを用いてイオン照射を行うこともできる。

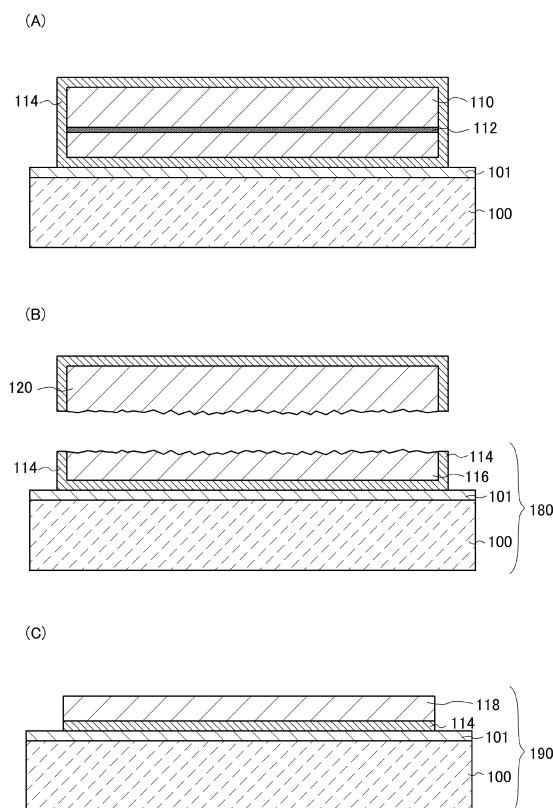

【0064】

次に、ベース基板100と半導体基板110とを貼り合わせる(図3(A)参照)。具体的には、ベース基板100の表面と半導体基板110の表面とを対向させて、ベース基板100に形成された絶縁層101と、半導体基板110に形成された絶縁層114とを貼り合わせる。

【0065】

なお、ベース基板100と半導体基板110とを貼り合わせる前に、半導体基板110上に形成された絶縁層114及びベース基板100上の絶縁層101の少なくとも一方に表面処理を行うことが好ましい。表面処理を行うことで、半導体基板110とベース基板100の接合界面での接合強度を向上させることができる。さらに、表面処理を行うことで、基板上に存在するパーティクル(ゴミ、とも記す)を低減することができるため、パーティクル等に起因する貼り合わせ不良を低減することができる。なお、ベース基板100上に絶縁層101を設けない場合は、ベース基板100表面に表面処理を行うことが好ましい。また、半導体基板110上に絶縁層114を設けない場合は、半導体基板110表面に表面処理を行うことが好ましい。

10

20

30

40

50

## 【0066】

表面処理としては、ウェット処理、ドライ処理、またはウェット処理及びドライ処理の組み合わせが挙げられる。また、異なるウェット処理を組み合わせる、または異なるドライ処理を組み合わせて行うことができる。

## 【0067】

ベース基板100と半導体基板110を貼り合わせる場合は、ベース基板100又は半導体基板110、あるいはその両方を加熱すると、ベース基板100と半導体基板110の貼り合わせの界面に起因する不良を抑制することができる。ベース基板100を加熱する場合は、ベース基板100の加熱温度は、50以上100以下、好ましくは55以上95以下とする。加熱時間については特に限定されず、ベース基板100が所望の温度になるよう適切な条件を設定すればよい。例えば、180秒間加熱することができる。10

## 【0068】

次に、所望の温度に加熱されたベース基板100を押圧することで、ベース基板100の端部と、半導体基板110の端部とを接触させる。また、ピンなどを用いてベース基板100または半導体基板110の一点、たとえばベース基板100の中央を押圧することで、ベース基板100と半導体基板110とを接触させてもよい。接触させた部分からベース基板100と半導体基板110との貼り合わせが開始され、貼り合わせは、その開始地点から同心円を描くように進行する。例えば、ベース基板100と半導体基板110の角部の一から貼り合わせを開始させる場合、貼り合わせは、該角部の対角に位置する角部に向かって同心円状に進行し、全面に及ぶ。20

## 【0069】

次に、半導体基板110とベース基板100とを貼り合わせた後に、貼り合わされたベース基板100及び半導体基板110に対して熱処理を施して、貼り合わせを強固なものとすることが好ましい。この際の加熱温度は、脆化領域112における分離が進行しない温度とする必要がある。例えば、400未満、好ましくは300以下とする。熱処理時間については特に限定されず、処理時間と貼り合わせ強度との関係から適切な条件を設定すればよい。熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA(瞬間熱アニール、Rapid Thermal Annealing)装置などを用いることができる。また、マイクロ波などを照射して、該領域のみを局所的に加熱することもできる。貼り合わせ強度に問題がない場合には、上記熱処理は省略すれば良い。本実施の形態においては200、2時間の熱処理を施す。30

## 【0070】

次に、再度熱処理を行うことにより、半導体基板110を、脆化領域112において、半導体層116と半導体基板120とに分離する(図3(B)参照)。これにより、ベース基板100上に絶縁層114を介して半導体層116が設けられたSOI基板180が得られる。

## 【0071】

熱処理を行うことで、温度上昇によって脆化領域112に形成されている微小な孔には、添加された水素原子が析出し、微小な孔の内部の圧力が上昇する。圧力の上昇により、脆化領域112の微小な孔に体積変化が起こり、水素の微小気泡107が成長する(図1(C)参照)。40

## 【0072】

本実施の形態では、半導体基板110中に炭素イオン102が照射されているため、水素の拡散が抑制される。そのため水素のドーズ量が少ない場合でも、効果的に水素の微小気泡107を成長させることができる。

## 【0073】

成長した微小気泡107は微小気泡層を形成し、当該微小気泡層を境に半導体基板110の一部が半導体基板110から分離する。絶縁層114はベース基板100に接合しているので、ベース基板100上には絶縁層114を介して半導体基板110から分離された半導体層116が形成される。また、ここでの熱処理の温度は、ベース基板100の歪み50

点を越えない温度とする。例えば、ベース基板 100 としてガラス基板を用いる場合には、熱処理の温度は 400 以上 750 以下とすることが好ましい。ただし、ガラス基板の耐熱性が許るのであればこの限りではない。この熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA (瞬間熱アニール、Rapid Thermal Anneal) 装置、マイクロ波加熱装置などを用いることができる。本実施の形態においては 600 、2 時間の熱処理を施す。

【0074】

なお半導体基板 110 中に添加された炭素は、水素が深さ方向 (半導体基板 110 の表面と垂直な方向) に拡散することも抑制する。そのため、半導体基板 110 中に炭素を添加すると深さ方向に対する、微小気泡層の幅が小さくなる。これにより、当該微小気泡層を境に半導体基板 110 の一部が半導体基板 110 から分離した場合、当該半導体基板 110 の一部 (半導体層) の表面凹凸を低減させることができる。

【0075】

なお、上述したベース基板 100 と半導体基板 110 との接合強度を増加させるための熱処理を行わず、ベース基板 100 と絶縁層 114 との接合強度の増加の熱処理工程と、脆化領域 112 における分離の熱処理工程を同時に行ってもよい。

【0076】

また必要であれば、次に SOI 基板 180 の半導体層 116 に平坦化処理を行う。半導体層 116 の表面に分離工程やイオン照射工程などに起因する凹凸や欠陥が生じた場合であっても、SOI 基板 180 に対して平坦化処理を行うことにより、半導体層 116 の表面を平坦化することができる。

【0077】

平坦化処理は、化学機械研磨 (CMP) 、エッティング処理、レーザ光の照射等により行うことができる。ここでは、半導体層 116 にレーザ光を照射することで、半導体層 116 の再結晶化と表面の平坦化を行う。

【0078】

本実施の形態では、上述のように当該半導体基板 110 の一部 (半導体層) の表面凹凸を低減させることができるので、半導体層 116 にレーザ光を照射しても半導体層の表面に孔が生じる恐れはない。

【0079】

レーザ光を半導体層 116 の上面側から照射することで、半導体層 116 の上面を溶融させる。溶融した後、半導体層 116 が冷却、固化することで、その上面の平坦性が向上した半導体層 118 が得られる。レーザ光を用いることにより、ベース基板 100 が直接加熱されないため、当該ベース基板 100 の温度上昇を抑えることができる。このため、ガラス基板のような耐熱性の低い基板をベース基板 100 に用いることが可能である。

【0080】

なお、レーザ光の照射による半導体層 116 の溶融は、部分溶融とすることが好ましい。完全溶融させた場合には、液相となった後の無秩序な核発生により微結晶化し、結晶性が低下する可能性が高いためである。一方で、部分溶融させることにより、溶融されていない固相部分から結晶成長が進行する。これにより、半導体層 116 の欠陥を減少させることができる。ここで、完全溶融とは、半導体層 116 が下部界面付近まで溶融されて、液体状態になることをいう。他方、部分溶融とは、この場合、半導体層 116 の上部は溶融して液相となるが、下部は溶融せずに固相のままであることをいう。

【0081】

本実施の形態により、水素イオン 103 のドーズ量を低減させることができるために、半導体層 116 中の水素濃度も小さい。そのため、半導体層 116 へのレーザ光の照射により、結晶性のよい半導体層 118 を得ることができる。

【0082】

上記レーザ光の照射には、パルス発振レーザを用いることが好ましい。これは、瞬間に高エネルギーのパルスレーザ光を発振することができ、溶融状態を作り出すことが容易と

10

20

30

40

50

なるためである。発振周波数は、1 H z 以上 1 0 M H z 以下程度とすることが好ましい。

【 0 0 8 3 】

上述のようにレーザ光を照射した後には、半導体層 1 1 8 の厚さを小さくする薄膜化工程を行っても良い。半導体層 1 1 8 の薄膜化には、ドライエッチングまたはウエットエッチングの一方、または双方を組み合わせたエッチング処理（エッチバック処理）を適用すればよい。例えば、半導体層 1 1 8 がシリコン材料からなる層である場合、ドライエッチングとして  $S F_6$  と  $O_2$  をプロセスガスに用いて、半導体層 1 1 8 を薄くすることができる。

【 0 0 8 4 】

なお、平坦化処理は S O I 基板 1 8 0 に限らず分離後の半導体基板 1 2 0 に対して行ってもよい。分離後の半導体基板 1 2 0 の表面を平坦にすることによって、当該半導体基板 1 2 0 を S O I 基板の作製工程において再度利用することが可能となる。

10

【 0 0 8 5 】

以上の工程により、ベース基板 1 0 0 上に、絶縁層 1 1 4 を介して半導体層 1 1 8 が設けられた S O I 基板 1 9 0 を作製することができる（図 3 ( C ) 参照）。

【 0 0 8 6 】

なお、本実施の形態では、半導体層 1 1 6 にレーザ光を照射した後に、エッチング処理を行う場合について説明したが、開示される発明の一態様はこれに限定されず、レーザ光を照射する前にエッチング処理を行ってもよいし、レーザ光の照射前後にエッチング処理を行ってもよい。

20

【 0 0 8 7 】

なお、本実施の形態においては、レーザ光を用いて欠陥の低減、及び、平坦性の向上を実現しているが、本発明の一態様はこれに限定されない。熱処理など、他の方法を用いて欠陥の低減、平坦性の向上を実現しても良い。熱処理により、欠陥の低減、平坦性を向上させる場合であっても、貼り合わせ前にベース基板 1 0 0 と半導体基板 1 1 0 との少なくとも一方に加熱処理を行うことにより、余剰水分に起因する貼り合わせ不良を低減することは有効である。また、欠陥低減処理が不要であれば、エッチング処理などの平坦性向上処理のみを適用しても良い。

【 0 0 8 8 】

以上のようにして、本実施の形態により、照射された水素イオン 1 0 3 の半導体基板 1 1 0 からの脱離を抑制することができる。

30

【 0 0 8 9 】

また半導体基板 1 1 0 からの水素イオンの脱離を抑制することができる、照射する水素イオン 1 0 3 のドーズ量を低減させることができる。

【 0 0 9 0 】

また本実施の形態により、結晶性のよい半導体層 1 1 8 を有する S O I 基板 1 9 0 を得ることができる。

【 0 0 9 1 】

また本実施の形態により、表面の凹凸が少ない半導体層 1 1 8 を有する S O I 基板 1 9 0 を得ることができる。

40

【 0 0 9 2 】

[ 実施の形態 2 ]

本実施の形態では、実施の形態 1 とは異なる S O I 基板の作製方法について述べる。なお本実施の形態では、実施の形態 1 と異なるものについてのみ説明する。本実施の形態で説明しないものについては、実施の形態 1 と同様である。

【 0 0 9 3 】

本実施の形態では、実施の形態 1 で述べた炭素イオン 1 0 2 に代えて、炭素及び水素を含むクラスタイオン ( $C_x H_y^+$ ) を照射する。炭素及び水素を含むクラスタイオン ( $C_x H_y^+$ ) を用いた場合は、炭素と同時に水素を添加することができるため、更に効果的に水素の微小気泡 1 0 7 を形成することができる。

50

## 【0094】

上記の炭素及び水素を含むクラスタイオンを半導体基板110に照射する場合には、例えば、ドーズ量 $1 \times 10^{15}$  ions / cm<sup>2</sup>で行えばよい。また、加速電圧は、上記xの値によって変化し、例えばxが1の場合50keV以上100keV以下、xが2の場合100keV以上200keV以下、xが10の場合500keV以上1000keV以下で行えばよい。

## 【0095】

また炭素及び水素を含むクラスタイオンを半導体基板110に照射する場合、当該クラスタイオンを照射することで、脆化領域を形成するのに十分は水素を添加できるのであれば、その後の水素イオン照射は必ずしも行う必要はない。

10

## 【0096】

また炭素及び水素を含むクラスタイオン照射後に、水素イオンを照射する場合は、水素イオンのドーズ量を実施の形態1に比較して更に低減させることが可能である。本実施の形態では、水素イオンは、例えば加速電圧50keV、ドーズ量 $5 \times 10^{15}$  ions / cm<sup>2</sup>で照射することができる。

## 【0097】

なお、本実施の形態においても実施の形態1と同様に、半導体基板110への炭素及び水素を含むクラスタイオンの照射を、絶縁層114の形成前又は形成後いずれかに行ってよい。ただし、絶縁層114として、半導体基板110に熱酸化処理を行うことにより熱酸化膜を形成する場合、炭素及び水素を含むクラスタイオンの照射は当該熱酸化膜形成後に行う。なぜなら、炭素及び水素を含むクラスタイオン照射後に熱酸化処理を行うと、半導体基板110中の炭素及び水素は熱酸化処理により拡散してしまうからである。

20

## 【0098】

以上のようにして、本実施の形態により、炭素及び水素を含むクラスタイオンの照射によって添加された水素、又は照射された水素イオンが半導体基板110から脱離することを抑制することができる。

## 【0099】

また本実施の形態により、結晶性のよい半導体層118を有するSOI基板190を得ることができる。

30

## 【0100】

また本実施の形態により、表面の凹凸が少ない半導体層118を有するSOI基板190を得ることができる。

## 【0101】

## [実施の形態3]

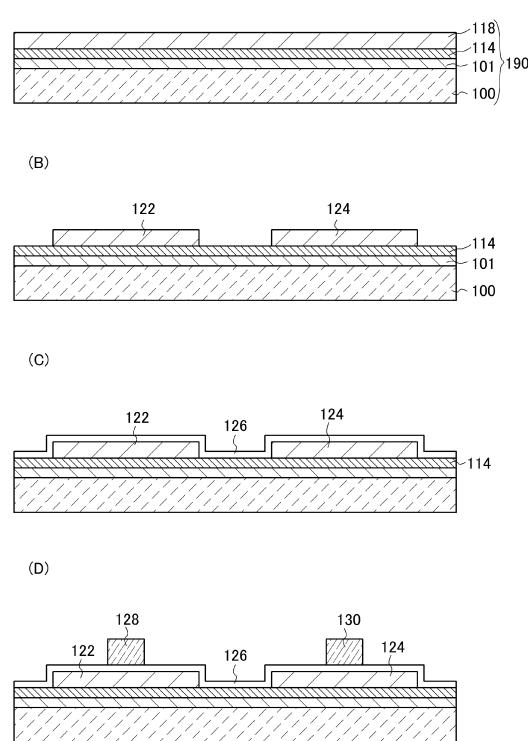

図4(A)は、実施の形態1又は実施の形態2に示す方法で作製したSOI基板(図3(C)参照)の一部を示す断面図である。

## 【0102】

半導体層118には、薄膜トランジスタ(Thin Film Transistor: TFT)のしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型不純物や、リン、砒素などのn型不純物を添加しても良い。不純物を添加する領域、及び添加する不純物の種類は、適宜変更することができる。例えば、nチャネル型TFTの形成領域にp型不純物を添加し、pチャネル型TFTの形成領域にn型不純物を添加する。上述の不純物を添加する際には、ドーズ量が $1 \times 10^{11}$  ions / cm<sup>2</sup>以上 $1 \times 10^{14}$  ions / cm<sup>2</sup>以下程度となるよう行えばよい。

40

## 【0103】

その後、半導体層118を島状に分離して、半導体層122及び半導体層124を形成する(図4(B)参照)。

## 【0104】

次に、半導体層122と半導体層124を覆うように、絶縁膜126を形成する(図4(C)参照)。ここでは、プラズマCVD法を用いて、酸化シリコン膜を単層で形成するこ

50

ととする。酸化シリコン以外にも、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等を含む膜を、単層構造または積層構造で形成することにより絶縁膜 126 としても良い。

【0105】

プラズマ CVD 法以外の作製方法としては、スパッタリング法や、高密度プラズマ処理による酸化または窒化による方法が挙げられる。高密度プラズマ処理は、例えば、ヘリウム、アルゴン、クリプトン、キセノンなどの希ガスと、酸素、酸化窒素、アンモニア、窒素、水素などガスの混合ガスを用いて行う。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル (OH ラジカルを含む場合もある) や窒素ラジカル (NH ラジカルを含む場合もある) によって、半導体層の表面を酸化または窒化することにより、1 nm 以上 20 nm 以下、望ましくは 2 nm 以上 10 nm 以下の絶縁膜を半導体層に接するように形成する。

10

【0106】

上述した高密度プラズマ処理による半導体層 122 及び半導体層 124 の酸化または窒化は固相反応であるため、絶縁膜 126 と半導体層 122 及び絶縁膜 126 と半導体層 124 の界面準位密度をきわめて低くすることができる。また、高密度プラズマ処理により半導体層 122 及び半導体層 124 を直接酸化または窒化することで、形成される絶縁膜 126 の厚さのバラツキを抑えることができる。また、半導体層 122 及び半導体層 124 が単結晶であるため、高密度プラズマ処理を用いて半導体層 122 及び半導体層 124 の表面を固相反応で酸化させる場合であっても、均一性が良く、界面準位密度の低い絶縁膜 126 を形成することができる。このように、高密度プラズマ処理により形成された絶縁膜 126 をトランジスタのゲート絶縁膜の一部または全部に用いることで、特性のバラツキを抑制することができる。

20

【0107】

または、半導体層 122 と半導体層 124 を熱酸化させることで、ゲート絶縁膜を形成するようにしても良い。このように、熱酸化を用いる場合には、ある程度の耐熱性を有するガラス基板を用いることが必要である。

【0108】

なお、水素を含む絶縁膜 126 を形成し、その後、350 以上 450 以下の温度による加熱処理を行うことで、絶縁膜 126 中に含まれる水素を半導体層 122 及び半導体層 124 中に拡散させるようにしても良い。この場合、絶縁膜 126 として、プラズマ CVD 法を用いた窒化シリコンまたは窒化酸化シリコンを用いることができる。なお、プロセス温度は 350 以下とすると良い。このように、半導体層 122 及び半導体層 124 に水素を供給することで、半導体層 122 中、半導体層 124 中、ゲート絶縁膜となる絶縁膜 126 と半導体層 122 の界面、及びゲート絶縁膜となる絶縁膜 126 と半導体層 124 の界面における欠陥を効果的に低減することができる。

30

【0109】

次に、絶縁膜 126 上に導電膜を形成した後、該導電膜を所定の形状に加工 (パターニング) することで、半導体層 122 の上方にゲート電極 128 を、半導体層 124 の上方にゲート電極 130 を形成する (図 4 (D) 参照)。導電膜の形成には CVD 法、スパッタリング法等を用いることができる。導電膜は、タンタル (Ta)、タンゲステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ニオブ (Nb) 等の材料を用いて形成することができる。また、上記金属を主成分とする合金材料を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体に導電性を付与する不純物元素をドーピングした多結晶シリコンなど、半導体材料を用いて形成しても良い。

40

【0110】

本実施の形態ではゲート電極 128 及びゲート電極 130 を単層の導電膜で形成しているが、開示する発明の一態様に係る半導体装置は該構成に限定されない。ゲート電極 128

50

及びゲート電極 130 は積層された複数の導電膜で形成されていても良い。2層構造とする場合には、例えば、モリブデン膜、チタン膜、窒化チタン膜等を下層に用い、上層にはアルミニウム膜などを用いればよい。3層構造の場合には、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造や、チタン膜とアルミニウム膜とチタン膜の積層構造などを採用するとよい。

【0111】

なお、ゲート電極 128 及びゲート電極 130 を形成する際に用いるマスクは、酸化シリコンや窒化酸化シリコン等の材料を用いて形成してもよい。この場合、酸化シリコン膜や窒化酸化シリコン膜等をパターニングしてマスクを形成する工程が加わるが、これらの材料を用いたマスクでは、レジスト材料を用いたマスクと比較してエッチング時における膜減りが少ないため、より正確な形状のゲート電極 128 及びゲート電極 130 を形成することができる。また、マスクを用いずに、液滴吐出法を用いて選択的にゲート電極 128 及びゲート電極 130 を形成しても良い。ここで、液滴吐出法とは、所定の組成物を含む液滴を吐出または噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

10

【0112】

また、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) エッチング法を用い、エッチング条件 (コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等) を適宜調節し、所望のテーパ形状を有するようにゲート電極 128 及びゲート電極 130 を形成することもできる。また、テーパ形状は、マスクの形状によって制御することもできる。なお、エッチング用ガスとしては、塩素、塩化硼素、塩化珪素、四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄、弗化窒素などのフッ素系ガス、または酸素などを適宜用いることができる。

20

【0113】

次に、ゲート電極 128 及びゲート電極 130 をマスクとして、一導電型を付与する不純物元素を半導体層 122 及び半導体層 124 それぞれに添加する (図 5 (A) 参照)。本実施の形態では、半導体層 122 に n 型を付与する不純物元素 (例えばリンまたはヒ素) を、半導体層 124 に p 型を付与する不純物元素 (例えばホウ素) を添加する。なお、n 型を付与する不純物元素を半導体層 122 に添加する際には、p 型の不純物が添加される半導体層 124 はマスク等で覆い、n 型を付与する不純物元素の添加が選択的に行われるようになる。また、p 型を付与する不純物元素を半導体層 124 に添加する際には、n 型の不純物が添加される半導体層 122 はマスク等で覆い、p 型を付与する不純物元素の添加が選択的に行われるようになる。または、半導体層 122 及び半導体層 124 に、p 型を付与する不純物元素または n 型を付与する不純物元素の一方を添加した後、一方の半導体層のみに、より高い濃度で p 型を付与する不純物元素または n 型を付与する不純物元素の他方を添加するようにしても良い。上記不純物の添加により、半導体層 122 に不純物領域 132a 及び不純物領域 132b、並びに半導体層 124 に不純物領域 134a 及び不純物領域 134b が形成される。また不純物領域 132a 及び不純物領域 132b との間にチャネル形成領域 131、並びに不純物領域 134a 及び不純物領域 134b との間にチャネル形成領域 133 が形成される。

30

【0114】

次に、ゲート電極 128 の側面にサイドウォール 136a 及びサイドウォール 136b を、ゲート電極 130 の側面にサイドウォール 138a 及びサイドウォール 138b を形成する (図 5 (B) 参照)。サイドウォール 136a 及びサイドウォール 136b、並びにサイドウォール 138a 及びサイドウォール 138b は、例えば、絶縁膜 126、ゲート電極 128、及びゲート電極 130 を覆うように新たに絶縁膜を形成し、異方性エッチングにより該絶縁膜を部分的にエッチングすることで形成することができる。なお、ゲート電極 128、サイドウォール 136a、及びサイドウォール 136b をマスクとし、上記の異方性エッチングにより、絶縁膜 126 を部分的にエッチングし、ゲート絶縁膜 127 を形成する。同様にゲート電極 130、サイドウォール 138a、及びサイドウォール 1

40

50

38bをマスクとし、上記の異方性エッティングにより、絶縁膜126を部分的にエッティングし、ゲート絶縁膜129を形成する。

【0115】

サイドウォール136a及びサイドウォール136b、並びにサイドウォール138a及びサイドウォール138bを形成するための絶縁膜としては、プラズマCVD法やスパッタリング法等を用いて、シリコン、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、有機材料などを含む膜を、単層構造または積層構造で形成すれば良い。本実施の形態では、膜厚100nmの酸化シリコン膜をプラズマCVD法によって形成する。また、エッティングガスとしては、CHF<sub>3</sub>とヘリウムの混合ガスを用いることができる。なお、サイドウォール136a及びサイドウォール136b、並びにサイドウォール138a及びサイドウォール138bを形成する工程は、これらに限定されるものではない。

10

【0116】

次に、ゲート絶縁膜127、ゲート電極128、サイドウォール136a、及びサイドウォール136bをマスクとして、半導体層122に一導電型を付与する不純物元素を添加する。同様に、ゲート絶縁膜129、ゲート電極130、サイドウォール138a、及びサイドウォール138bをマスクとして、半導体層124に一導電型を付与する不純物元素を添加する。

【0117】

なお、半導体層122及び半導体層124のそれぞれには、それぞれ先の工程で添加した不純物元素と同じ導電型の不純物元素をより高い濃度で添加する。ここで、n型を付与する不純物元素を半導体層122に添加する際には、p型の不純物が添加される半導体層124はマスク等で覆い、n型を付与する不純物元素の添加が選択的に行われるようとする。また、p型を付与する不純物元素を半導体層124に添加する際には、n型の不純物が添加される半導体層122はマスク等で覆い、p型を付与する不純物元素の添加が選択的に行われるようとする。

20

【0118】

上記不純物元素の添加により、半導体層122に、一対の高濃度不純物領域140a及び高濃度不純物領域140bと、一対の低濃度不純物領域141a及び低濃度不純物領域141bと、チャネル形成領域131とが形成される。また、上記不純物元素の添加により、半導体層124に、一対の高濃度不純物領域142a及び高濃度不純物領域142bと、一対の低濃度不純物領域143a及び低濃度不純物領域143bと、チャネル形成領域133とが形成される。一対の高濃度不純物領域140a及び高濃度不純物領域140b、並びに一対の高濃度不純物領域142a及び高濃度不純物領域142bは、それぞれソース領域またはドレイン領域として機能し、低濃度不純物領域141a及び低濃度不純物領域141b、並びに低濃度不純物領域143a及び低濃度不純物領域143bは、LDD(Lightly Doped Drain)領域として機能する。

30

【0119】

なお、半導体層122上に形成されたサイドウォール136a及びサイドウォール136bと、半導体層124上に形成されたサイドウォール138a及びサイドウォール138bは、キャリアが移動する方向(いわゆるチャネル長に平行な方向)の長さが同じになるように形成しても良いが、異なるように形成しても良い。例えば、pチャネル型トランジスタ152となる半導体層124上のサイドウォール138a及びサイドウォール138bは、nチャネル型トランジスタ151となる半導体層122上のサイドウォール136a及びサイドウォール136bよりも、キャリアが移動する方向の長さが長くなるように形成すると良い。pチャネル型トランジスタ152において、サイドウォール138a及びサイドウォール138bの長さをより長くすることで、ホウ素の拡散による短チャネル効果を抑制することができるため、ソース領域及びドレイン領域に高濃度のホウ素を添加することが可能となる。これにより、ソース領域及びドレイン領域を十分に低抵抗化することができる。

40

50

## 【0120】

ソース領域及びドレイン領域をさらに低抵抗化するために、半導体層122及び半導体層124の一部をシリサイド化したシリサイド領域を形成しても良い。シリサイド化は、半導体層に金属を接触させ、加熱処理（例えば、G R T A法、L R T A法等）により、半導体層中の珪素と金属とを反応させて行う。シリサイド領域としては、コバルトシリサイドまたはニッケルシリサイドを形成すれば良い。半導体層122や半導体層124が薄い場合には、半導体層122及び半導体層124それぞれの底部までシリサイド反応を進めても良い。シリサイド化に用いることができる金属材料としては、チタン（T i）、ニッケル（N i）、タングステン（W）、モリブデン（M o）、コバルト（C o）、ジルコニウム（Z r）、ハフニウム（H f）、タンタル（T a）、バナジウム（V）、ネオジム（N d）、クロム（C r）、白金（P t）、パラジウム（P d）等が挙げられる。また、レーザ光の照射などによってもシリサイド領域を形成することができる。

10

## 【0121】

上述の工程により、nチャネル型トランジスタ151及びpチャネル型トランジスタ152が形成される。なお、図5（C）に示す段階では、ソース電極またはドレイン電極として機能する導電膜は形成されていないが、これらのソース電極またはドレイン電極として機能する導電膜を含めてトランジスタと呼ぶこともある。

## 【0122】

次に、nチャネル型トランジスタ151及びpチャネル型トランジスタ152を覆うように絶縁膜145を形成する。絶縁膜145は必ずしも設ける必要はないが、絶縁膜145を形成することで、アルカリ金属やアルカリ土類金属などの不純物がnチャネル型トランジスタ151及びpチャネル型トランジスタ152に侵入することを防止できる。具体的には、絶縁膜145を、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム、酸化アルミニウムなどの材料を用いて形成するのが望ましい。本実施の形態では、膜厚600nm程度の窒化酸化シリコン膜を、絶縁膜145として用いる。この場合、上述の水素化の工程は、該窒化酸化シリコン膜形成後に行っても良い。なお、本実施の形態においては、絶縁膜145を単層構造としているが、積層構造としても良いことはいうまでもない。例えば、2層構造とする場合には、酸化窒化シリコン膜と窒化酸化シリコン膜との積層構造とすることができる。

20

## 【0123】

次に、nチャネル型トランジスタ151及びpチャネル型トランジスタ152を覆うように、絶縁膜145上に絶縁膜146を形成する（図5（D）参照）。絶縁膜146は、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いて形成するとよい。また、上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、PSG（リンガラス）、BPSG（リンボロンガラス）、アルミナ等を用いることもできる。ここで、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は、置換基に水素の他、フッ素、アルキル基、芳香族炭化水素から選ばれる一を有していても良い。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜146を形成しても良い。

30

## 【0124】

絶縁膜146の形成には、その材料に応じて、CVD法、スパッタ法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法等）、印刷法（スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

## 【0125】

次に、半導体層122の一部と半導体層124の一部が露出するように絶縁膜145及び絶縁膜146にコンタクトホールを形成する。そして、該コンタクトホールを介して半導体層122に接する導電膜147a及び導電膜147bと、半導体層124に接する導電

40

膜 148a 及び導電膜 148b を形成する(図6参照)。導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b は、トランジスタのソース電極又はドレイン電極として機能する。なお、本実施の形態においては、コンタクトホール開口時のエッチングに用いるガスとして  $\text{CHF}_3$  と  $\text{He}$  の混合ガスを用いたが、これに限定されるものではない。

#### 【0126】

導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b は、CVD 法やスパッタリング法等により形成することができる。材料としては、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、珪素(Si)等を用いることができる。また、上記材料を主成分とする合金を用いても良いし、上記材料を含む化合物を用いても良い。また、導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b は、単層構造としても良いし、積層構造としても良い。

#### 【0127】

アルミニウムを主成分とする合金の例としては、アルミニウムを主成分として、ニッケルを含むものを挙げることができる。また、アルミニウムを主成分とし、ニッケルと、炭素または珪素の一方または両方を含むものを挙げることができる。アルミニウムやアルミニウムシリコン(A1-Si)は抵抗値が低く、安価であるため、導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b を形成する材料として適している。特に、アルミニウムシリコンは、パターニング(成膜及びエッチングを含む工程)の際のレジストベークによるヒロックの発生を抑制することができるため好ましい。また、珪素の代わりに、アルミニウムに 0.5% 程度の銅(Cu)を混入させた材料を用いても良い。

#### 【0128】

導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b を積層構造とする場合には、例えば、バリア膜とアルミニウムシリコン膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン膜と窒化チタン膜とバリア膜の積層構造などを採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、モリブデンの窒化物、タンタル、タンタルの窒化物などを用いて形成された膜である。バリア膜の間にアルミニウムシリコン膜を挟むように導電膜を形成すると、アルミニウムやアルミニウムシリコンのヒロックの発生をより一層防止することができる。また、還元性の高い元素であるチタンを用いてバリア膜を形成すると、半導体層 122 と半導体層 124 上に薄い酸化膜が形成されていたとしても、バリア膜に含まれるチタンが該酸化膜を還元し、導電膜 147a 及び導電膜 147b と半導体層 122 とのコンタクト、導電膜 148a 及び導電膜 148b と半導体層 124 とのコンタクトを良好なものとすることができる。また、バリア膜を複数積層するようにして用いても良い。その場合、例えば、導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b を、下層からチタン、窒化チタン、アルミニウムシリコン、チタン、窒化チタンのように、5 層構造またはそれ以上の積層構造とすることもできる。

#### 【0129】

また、導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b として、 $\text{WF}_6$  ガスと  $\text{SiH}_4$  ガスから化学気相成長法で形成したタンゲステンシリサイドを用いても良い。また、 $\text{WF}_6$  を水素還元して形成したタンゲステンを、導電膜 147a、導電膜 147b、導電膜 148a、及び導電膜 148b として用いても良い。

#### 【0130】

なお、導電膜 147a 及び導電膜 147b はそれぞれ、n チャネル型トランジスタ 151 の高濃度不純物領域 140a 及び高濃度不純物領域 140b に接続されている。導電膜 148a 及び導電膜 148b はそれぞれ、p チャネル型トランジスタ 152 の高濃度不純物領域 142a 及び高濃度不純物領域 142b に接続されている。

#### 【0131】

10

20

30

40

50

なお、本実施の形態においては、nチャネル型トランジスタ151は、ゲート電極128を1つ有しており、pチャネル型トランジスタ152は、ゲート電極130を1つ有しているが、開示する発明の一態様は該構成に限定されない。トランジスタは、ゲート電極として機能する電極を複数有し、なおかつ該複数の電極が電気的に接続されているマルチゲート構造を有していても良い。

## 【0132】

なお、本実施の形態で示した構成は、他の実施の形態で示す構成と適宜組み合わせて用いることができる。

## 【0133】

本実施の形態により、照射された水素イオンの半導体基板からの脱離を抑制することができ、照射する水素イオンのドーズ量を低減させることができるので、トランジスタの作製コストを抑制することができる。

10

## 【0134】

また本実施の形態により、結晶性がよく、表面の凹凸が少ない半導体層を有するSOI基板を得ることができるので、特性の向上したトランジスタを得ることができる。

## 【符号の説明】

## 【0135】

|      |          |    |

|------|----------|----|

| 100  | ベース基板    | 20 |

| 101  | 絶縁層      |    |

| 102  | 炭素イオン    |    |

| 103  | 水素イオン    |    |

| 105  | 曲線       |    |

| 106  | 曲線       |    |

| 107  | 微小気泡     |    |

| 110  | 半導体基板    |    |

| 112  | 脆化領域     |    |

| 114  | 絶縁層      |    |

| 116  | 半導体層     |    |

| 118  | 半導体層     |    |

| 120  | 半導体基板    | 30 |

| 122  | 半導体層     |    |

| 124  | 半導体層     |    |

| 126  | 絶縁膜      |    |

| 127  | ゲート絶縁膜   |    |

| 128  | ゲート電極    |    |

| 129  | ゲート絶縁膜   |    |

| 130  | ゲート電極    |    |

| 131  | チャネル形成領域 |    |

| 132a | 不純物領域    | 40 |

| 132b | 不純物領域    |    |

| 133  | チャネル形成領域 |    |

| 134a | 不純物領域    |    |

| 134b | 不純物領域    |    |

| 136a | サイドウォール  |    |

| 136b | サイドウォール  |    |

| 138a | サイドウォール  |    |

| 138b | サイドウォール  |    |

| 140a | 高濃度不純物領域 |    |

| 140b | 高濃度不純物領域 |    |

| 141a | 低濃度不純物領域 | 50 |

|         |               |    |

|---------|---------------|----|

| 1 4 1 b | 低濃度不純物領域      |    |

| 1 4 2 a | 高濃度不純物領域      |    |

| 1 4 2 b | 高濃度不純物領域      |    |

| 1 4 3 a | 低濃度不純物領域      |    |

| 1 4 3 b | 低濃度不純物領域      |    |

| 1 4 5   | 絶縁膜           |    |

| 1 4 6   | 絶縁膜           |    |

| 1 4 7 a | 導電膜           |    |

| 1 4 7 b | 導電膜           |    |

| 1 4 8 a | 導電膜           | 10 |

| 1 4 8 b | 導電膜           |    |

| 1 5 1   | n チャネル型トランジスタ |    |

| 1 5 2   | p チャネル型トランジスタ |    |

| 1 8 0   | S O I 基板      |    |

| 1 9 0   | S O I 基板      |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/786 (2006.01)

(56)参考文献 特開2000-124092 (JP, A)

特開2002-170942 (JP, A)

特表2003-524876 (JP, A)

特開2004-039735 (JP, A)

特開2011-151318 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/02

H 01 L 21/20

H 01 L 21/265

H 01 L 21/336

H 01 L 27/12

H 01 L 29/786