(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3992976号

(P3992976)

(45) 発行日 平成19年10月17日(2007.10.17)

(24) 登録日 平成19年8月3日(2007.8.3)

(51) Int.C1.

F 1

|             |           |                 |

|-------------|-----------|-----------------|

| HO1L 21/20  | (2006.01) | HO1L 21/20      |

| GO2F 1/1368 | (2006.01) | GO2F 1/1368     |

| HO1L 21/268 | (2006.01) | HO1L 21/268 J   |

| HO1L 21/336 | (2006.01) | HO1L 29/78 627G |

| HO1L 29/786 | (2006.01) |                 |

請求項の数 13 (全 36 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2001-390714 (P2001-390714)  |

| (22) 出願日  | 平成13年12月21日 (2001.12.21)      |

| (65) 公開番号 | 特開2003-197521 (P2003-197521A) |

| (43) 公開日  | 平成15年7月11日 (2003.7.11)        |

| 審査請求日     | 平成16年12月21日 (2004.12.21)      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (74) 代理人  | 100116159<br>弁理士 玉城 信一                         |

| (72) 発明者  | 小久保 千穂<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (72) 発明者  | 志賀 愛子<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 棚田 好文<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

カレントミラー回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸

端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先

の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1

の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走

査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2

の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記カレントミラー回路が有する全ての薄膜

トランジスタを形成することを特徴とする半導体装置の作製方法。

## 【請求項2】

差動增幅回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸

端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先

10

20

の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記差動增幅回路が有する全ての薄膜トランジスタを形成することを特徴とする半導体装置の作製方法。

【請求項3】

オペアンプ回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

10

前記非晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記オペアンプ回路が有する全ての薄膜トランジスタを形成することを特徴とする半導体装置の作製方法。

20

【請求項4】

カレントミラー回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層上に金属含有層を形成し、加熱処理することにより結晶質半導体層を形成し、

前記結晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

30

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記カレントミラー回路が有する全ての薄膜トランジスタを形成することを特徴とする半導体装置の作製方法。

【請求項5】

差動增幅回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層上に金属含有層を形成し、加熱処理することにより結晶質半導体層を形成し、

40

前記結晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記差動增幅回路が有する全ての薄膜トランジスタを形成することを特徴とする半導体装置の作製方法。

50

## 【請求項 6】

オペアンプ回路を有する半導体装置の作製方法であって、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層上に金属含有層を形成し、加熱処理することにより結晶質半導体層を形成し、

前記結晶質半導体層をパターニングすることによって、一辺に先の尖った同じ形状の凸端部を複数有する形状の第1の島状半導体層を形成し、

矩形状に集光したレーザ光を、前記第1の島状半導体層の複数の前記凸端部の尖った先の部分と最初に、かつ同時に接するように前記基板に対して相対的に走査しつつ前記第1の島状半導体層に照射することによって、前記第1の島状半導体層を結晶化し、

前記結晶化した第1の島状半導体層のうち、前記凸端部と凸端部間の前記レーザ光の走査方向に形成される結晶性が芳しくない領域以外の領域をパターニングして、複数の第2の島状半導体層を形成し、

前記複数の第2の島状半導体層を用いて、前記オペアンプ回路が有する全ての薄膜トランジスタを形成することを特徴とする半導体装置の作製方法。

## 【請求項 7】

請求項1乃至請求項6のいずれか一において、前記薄膜トランジスタは、そのチャネル形成領域における電荷の移動方向がレーザ光のスポットの走査方向と平行、又はそれに準ずる方向に揃うように配置されていることを特徴とする半導体装置の作製方法。

## 【請求項 8】

請求項1乃至請求項6のいずれか一において、前記レーザ光は、連続発振の固体レーザ、気体レーザ、あるいは金属レーザから発振されることを特徴とする半導体装置の作製方法。

## 【請求項 9】

請求項1乃至請求項6のいずれか一において、前記レーザ光は、連続発振のYAGレーザ、 $YVO_4$ レーザ、YLFレーザ、 $YAlO_3$ レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、あるいはTi:サファイアレーザから発振されることを特徴とする半導体装置の作製方法。

## 【請求項 10】

請求項1乃至請求項6のいずれか一において、前記レーザ光は、連続発振のエキシマレーザ、Arレーザ、Krレーザ、あるいは $CO_2$ レーザから発振されることを特徴とする半導体装置の作製方法。

## 【請求項 11】

請求項1乃至請求項6のいずれか一において、前記レーザ光は、連続発振のヘリウムカドミウムレーザ、銅蒸気レーザ、あるいは金蒸気レーザから発振されることを特徴とする半導体装置の作製方法。

## 【請求項 12】

請求項1乃至請求項3のいずれか一において、前記非晶質半導体層をパターニングすることによって前記第1の島状半導体層及びマーカーを形成することを特徴とする半導体装置の作製方法。

## 【請求項 13】

請求項4乃至請求項6のいずれか一において、前記結晶質半導体層をパターニングすることによって前記第1の島状半導体層及びマーカーを形成することを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、半導体装置の作製方法および、当該作製方法によって作製された半導体装置に関する。なお、ここでいう半導体装置とは、液晶表示装置、発光装置等の電気光学装置および、これらを表示部として用いた電子機器も含まれるものとする。

10

20

30

40

50

## 【0002】

## 【従来の技術】

近年、絶縁体上、特にガラス基板上に形成された非晶質半導体層を結晶化させ、結晶質半導体層を得、当該結晶質半導体層を活性層とした薄膜トランジスタ(以下、TFTと表記)を形成する技術が広く用いられており、その電気的特性も著しく向上してきている。

## 【0003】

よって、当初はIC等を用いて、外付けで実装されていた様々な信号処理回路を、TFTを用いて形成することが可能となり、基板上に画素部と駆動回路とを一体形成した表示装置が実現した。これらは部品点数の減少により、小型・軽量であり、さらに製造コストの大幅な削減を可能とし、最近では広く研究、開発が進んでいる。

10

## 【0004】

## 【発明が解決しようとする課題】

現在実用されているTFTとしては、代表的には、前記非晶質半導体層を活性層として形成されるアモルファスシリコンTFT(以下、a-Si TFTと表記)と、前記結晶質半導体層を活性層として形成されるポリシリコンTFT(以下、P-Si TFTと表記)が挙げられる。P-Si TFTは、a-Si TFTに比べてはるかに高い電界効果移動度が得られる等、様々な点で優れており、前記表示装置の駆動回路を形成するためのTFTとして十分に良好な性能を有する。

## 【0005】

しかし、ICチップ等に用いられているトランジスタは単結晶シリコン上に形成されているため、さらに良好な電気的特性を有し、またその特性が均一に得られるのに対し、P-Si TFTは、半導体層が多数の結晶粒が集まって形成されている。それぞれの結晶状態は良好であるが、結晶粒同士の境界(粒界)においては配向が異なっているなどの理由で、電気的特性に大きく劣る。P-Si TFTにおいてはこの粒界が活性層中に多く含まれ、さらに粒界の数や隣接した結晶粒同士の配向の違いにより、その電気的特性に差が生ずる場合がある。つまり、同サイズのTFTを作製し、かつ各電極に同様な電圧を印加した場合にも、電流値等がばらつく場合がある。

20

## 【0006】

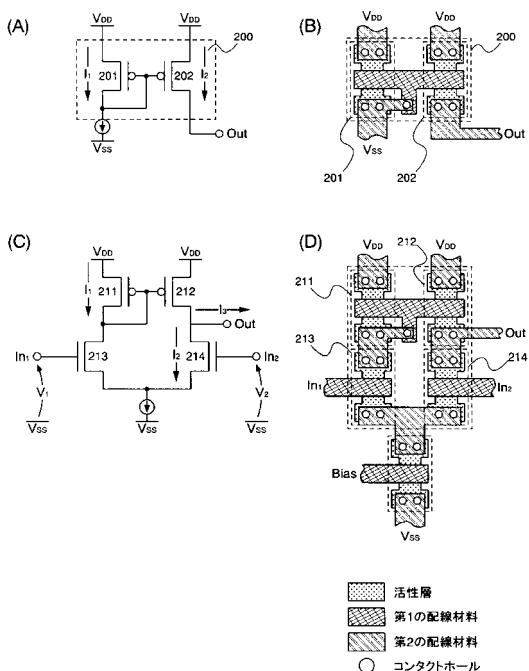

トランジスタを用いて形成される代表的な回路として、オペアンプや差動增幅回路等がある。これらの回路は、カレントミラー回路を有している。カレントミラー回路とは、2つのトランジスタを用いて、図2(A)に示すような構成をしており、トランジスタ201を流れるドレイン電流 $I_1$ と、トランジスタ202を流れるドレイン電流 $I_2$ とが等しくなる特徴を有する。

30

## 【0007】

例えば、このカレントミラー回路においては、トランジスタ201と、トランジスタ202との特性が等しいことが動作の前提となっている。つまり双方の電気的特性にばらつきがある場合、 $I_1 = I_2$ とは必ずしもならないため、回路として機能しない。よって通常カレントミラー回路を構成するトランジスタは、そのチャネル長、チャネル幅等が等しいものを用いて構成される。実際の基板上でのレイアウト例を図2(B)に示す。

## 【0008】

40

また、このカレントミラー回路を能動負荷として用いた差動增幅回路の構成を図2(C)に示す。この回路は、入力端( $I_{n1}$ 、 $I_{n2}$ )にそれぞれ異なる電位が与えられたとき、前述のカレントミラー回路によって $I_1 = I_2 + I_3$ となることを利用し、出力端( $O_{ut}$ )より、 $I_{n1}$ 、 $I_{n2}$ に入力された信号の電位差を増幅した波形を取り出すことが出来る回路である。この回路もまた、TFT211～214の電気的特性が等しいことが前提となっている。

## 【0009】

しかし、実際にはP-Si TFTにおいてその電気的特性にばらつきがある以上、素子のサイズを等しくしてもばらつきは抑えられないため、前述のような回路を作製するのには向かないことになる。

50

## 【0010】

ところで、非晶質半導体層を結晶化する方法の1つとして、C W(Continuous Wave:連続発振)レーザを一方向に走査させながら半導体層に照射することで、走査方向に繋がって結晶を成長させ、その方向に長く伸びた単結晶を形成する技術がある。この方法を用いれば、少なくともTFTのチャネル方向には結晶粒界のほとんどないものが得られると考えられている。さらに各結晶粒は、単結晶に近い組成となるため、電気的特性、均一性に優れている。

## 【0011】

反面、C Wレーザを半導体層に照射する工程において、基板上に成膜した半導体層のはがれ(ピーリング)が生ずる場合がある。基板上の一部でピーリングが生じた場合、可能であれば半導体層を除去し、ふたたび半導体層の形成を行って工程を継続すれば良いが、工程增加による損失は避けられない。また、基板サイズの大型化に伴って、一度に多くのデバイスの作製が可能となっているため、基板1枚の損失によって複数のデバイスの損失につながることになる。

10

## 【0012】

本発明は、前述の問題を鑑みて、P-Si TFTを用いて、前述のカレントミラー回路をはじめとした、高い素子整合性を必要とする回路を効率良く形成するための方法を提供することを課題とする。

## 【0013】

20

## 【課題を解決するための手段】

本発明においては、基板上に半導体層を形成した後、第1の島状半導体層をパターニングにより形成し、当該第1の島状半導体層を、レーザ照射によって結晶化、もしくは結晶性を高め、その後、第2の島状半導体層をパターニングにより形成する。当該第2の島状半導体層が、後にTFTの活性層となる。

## 【0014】

30

第1の島状半導体層より、単数もしくは複数の第2の島状半導体層が形成される。本発明においては特に、高い整合性を求められるTFT、具体的には1つのカレントミラー回路や1つの差動增幅回路、あるいは1つのオペアンプ回路等を構成するすべてのTFTの活性層となる第2の島状半導体層が、1つの第1の島状半導体層から形成されることを特徴としている。ここで、一般的に半導体回路において、特に高い整合性が求められるTFTを全て含む1つの回路もしくはそれに準ずる構成部分を単位回路と定義する。ただし、単位回路の中に、特に整合性を求められないTFTが含まれていても良い。すなわち、1つの第1の島状半導体層より、1つの単位回路を構成する全てのTFTの活性層が形成される。

## 【0015】

40

さらに、第1の島状半導体層にレーザ照射を行う際、レーザ光スポットが第1の島状半導体層の端部に達したときに、レーザ光スポットと第1の島状半導体層とが、基板表面もしくは裏面から見て1点で接するように、レーザ光の走査方向もしくは第1の島状半導体層の形状を決定している。例えば、レーザ光を走査していく、レーザ光スポットが、第1の島状半導体層の頂点のうち1点と最初に接するような経路で走査する。あるいは、あらかじめ走査方向が決定している場合、レーザ光スポットが、第1の島状半導体層の頂点のうち1点と最初に接するように第1の島状半導体層の形状を決定する。第1の島状半導体層の外周の一部あるいは全てが曲線である場合にも同様に、レーザ光スポットと第1の島状半導体層の端部が、ある1点の接点で最初に接するように、レーザ光の走査方向や第1の島状半導体層の形状を決定する。このようにすると、レーザ光スポットが最初に接した1点から、(100)配向面を有する結晶化が進行し、やがて当該第1の島状半導体層へのレーザ照射が終了すると、当該第1の島状半導体層において、(100)配向面の比率を高くすることが出来る。

## 【0016】

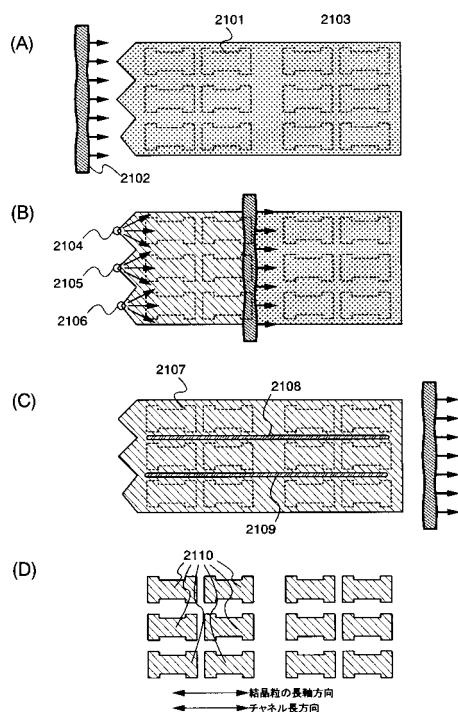

また、図21(A)に示すように、レーザ光スポットが、一辺に凸端部を三個有する形

50

状の第1の島状半導体層の頂点のうち1点と最初に接するようにしても良い。図21(A)の場合、レーザ光スポットが矢印の方向へ移動し、第1の島状半導体層2101の頂点2104、2105、2106と接する。その後、図21(B)に矢印で示す方向へと結晶化が進行し、図21(C)に示すように、結晶化した第1の半導体層2107を得る。

【0017】

このとき、図21(C)にて2108、2109で示す領域は結晶性が芳しくないため、この領域には第2の島状半導体層が形成されないようにするのが望ましい。以後、パターニングによって図21(D)に示すように、第2の島状半導体層2110を得る。

【0018】

このようにして結晶化された第1の島状半導体層より形成される単数もしくは複数の第2の島状半導体層を活性層として用いたTFTは、その特性を通常よりも均一化することが可能となるため、前記カレントミラー回路や差動増幅回路、あるいはオペアンプ回路といった単位回路含む半導体回路を、TFTを用いて基板上に構成することが可能となる。

10

【0019】

本発明の構成を以下に記す。

【0020】

本発明の半導体装置の作製方法は、

基板上に非晶質半導体層を形成する工程と、

前記非晶質半導体層を所望の形状にパターニングして、第1の島状半導体層とマーカーを形成する工程と、

20

前記第1の島状半導体層を含む領域に、楕円状あるいは矩形状に集光されたレーザ光を、前記基板に対して相対的に走査しつつ照射し、前記第1の島状半導体層を結晶化する工程と、

前記結晶化された第1の島状半導体層を所望の形状にパターニングして、第2の島状半導体層を形成する工程と、

前記第2の島状半導体層を活性層とした薄膜トランジスタを形成し、前記薄膜トランジスタを用いて回路を構成する半導体装置の作製方法であって、

前記半導体装置に含まれる単位回路が有する全ての薄膜トランジスタの活性層は、前記結晶化された第1の島状半導体層のうちいずれか1つから形成されることを特徴としている。

30

【0021】

本発明の半導体装置の作製方法は、

基板上に非晶質半導体層を形成する工程と、

前記非晶質半導体層上に金属含有層を形成し、熱処理により第1の結晶質半導体層を得る工程と、

前記第1の結晶質半導体層を所望の形状にパターニングして、第1の島状半導体層とマーカーを形成する工程と、

前記第1の島状半導体層を含む領域に、楕円状あるいは矩形状に集光されたレーザ光を、前記基板に対して相対的に走査しつつ照射し、第2の結晶質半導体層でなる第1の島状半導体層を得る工程と、

40

前記第2の結晶質半導体層でなる第1の島状半導体層を所望の形状にパターニングして、第2の島状半導体層を形成する工程と、

前記第2の島状半導体層を活性層とした薄膜トランジスタを形成し、前記薄膜トランジスタを用いて回路を構成する半導体装置の作製方法であって、

前記半導体装置に含まれる単位回路が有する全ての薄膜トランジスタの活性層となる前記第2の島状半導体層は、前記第2の結晶質半導体層でなる第1の島状半導体層のうちいずれか1つから形成されることを特徴としている。

【0022】

本発明の半導体装置の作製方法においては、

前記薄膜トランジスタは、そのチャネル形成領域における電荷の移動方向が全て平行もし

50

くはそれに準ずる方向に揃うように配置されていることを特徴としている。

【0023】

本発明の半導体装置の作製方法においては、

前記単位回路は、電流源、カレントミラー回路、差動増幅回路、オペアンプ回路のうちいずれか1つであることを特徴としている。

【0024】

本発明の半導体装置の作製方法においては、

前記レーザ光は、連続発振の固体レーザ、気体レーザ、あるいは金属レーザから発振されたものであることを特徴としている。

【0025】

10

本発明の半導体装置の作製方法においては、

前記レーザ光は、連続発振のYAGレーザ、YVO4レーザ、YLFレーザ、YAlO3レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザから選ばれた1種から発振されたものであることを特徴としている。

【0026】

本発明の半導体装置の作製方法においては、

前記レーザ光は、連続発振のエキシマレーザ、Arレーザ、Krレーザ、CO2レーザから選ばれた1種から発振されたものであることを特徴としている。

【0027】

20

本発明の半導体装置の作製方法においては、

前記レーザ光は、連続発振のヘリウムカドミウムレーザ、銅蒸気レーザ、金蒸気レーザから選ばれた1種から発振されたものであることを特徴としている。

【0028】

本発明の半導体装置は、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層を所望の形状にパターニングして、第1の島状半導体層とマーカーを形成し、

前記第1の島状半導体層を含む領域に、楕円状あるいは矩形状に集光されたレーザ光を、前記基板に対して相対的に走査しつつ照射し、前記第1の島状半導体層を結晶化し、

前記結晶化された第1の島状半導体層を所望の形状にパターニングして、第2の島状半導体層を形成し、

30

前記第2の島状半導体層を活性層とした薄膜トランジスタを形成し、前記薄膜トランジスタを用いて回路が構成された半導体装置であって、

前記半導体装置に含まれる単位回路が有する全ての薄膜トランジスタの活性層となる前記第2の島状半導体層は、前記結晶化された第1の島状半導体層のうちいずれか1つから形成されることを特徴としている。

【0029】

本発明の半導体装置は、

基板上に非晶質半導体層を形成し、

前記非晶質半導体層上に金属含有層を形成し、熱処理により第1の結晶質半導体層を得、前記第1の結晶質半導体層を所望の形状にパターニングして、第1の島状半導体層とマーカーを形成し、

40

前記第1の島状半導体層を含む領域に、楕円状あるいは矩形状に集光されたレーザ光を、前記基板に対して相対的に走査しつつ照射し、第2の結晶質半導体層でなる第1の島状半導体層を得、

前記第2の結晶質半導体層でなる第1の島状半導体層を所望の形状にパターニングして、第2の島状半導体層を形成し、

前記第2の島状半導体層を活性層とした薄膜トランジスタを形成し、前記薄膜トランジスタを用いて回路が構成された半導体装置であって、

前記半導体装置に含まれる単位回路が有する全ての薄膜トランジスタの活性層となる前記

50

第2の島状半導体層は、前記第2の結晶質半導体層でなる第1の島状半導体層のうちいずれか1つから形成されることを特徴としている。

【0030】

本発明の半導体装置は、

複数の薄膜トランジスタを用いて構成した回路を有する半導体装置において、

前記半導体装置は、単数もしくは複数の単位回路を有し、

前記単位回路が有する全ての薄膜トランジスタの活性層となる前記第2の島状半導体層は、1つの第1の島状半導体層を所望の形状にパターニングすることによって同時に形成されることを特徴としている。

【0031】

10

本発明の半導体装置は、

複数の薄膜トランジスタを用いて構成した回路を有する半導体装置において、

前記半導体装置は、単数もしくは複数の単位回路を有し、

前記単位回路が有する全ての薄膜トランジスタの活性層となる前記第2の島状半導体層は、1つの第1の島状半導体層を所望の形状にパターニングすることによって同時に形成され、

前記単位回路が有する全ての薄膜トランジスタは、そのチャネル形成領域における電荷の移動方向が全て平行もしくはそれに準ずる方向に揃えて配置されていることを特徴としている。

【0032】

20

本発明の半導体装置は、

複数の薄膜トランジスタを用いて構成した回路を有する半導体装置において、

前記半導体装置は、単数もしくは複数の単位回路を有し、

前記単位回路が有する全ての薄膜トランジスタの活性層となる前記第2の島状半導体層は、1つの第1の島状半導体層を所望の形状にパターニングすることによって同時に形成され、

前記単位回路が有する全ての薄膜トランジスタは、そのチャネル形成領域における電荷の移動方向が、前記第1の島状半導体層を結晶化する際に照射されるレーザ光の走査方向と平行もしくはそれに準ずる方向に揃うように配置されていることを特徴としている。

【0033】

30

本発明の半導体装置は、

前記単位回路は、電流源、カレントミラー回路、差動増幅回路、オペアンプ回路のうちいずれか1つであることを特徴としている。

【0034】

【発明の実施の形態】

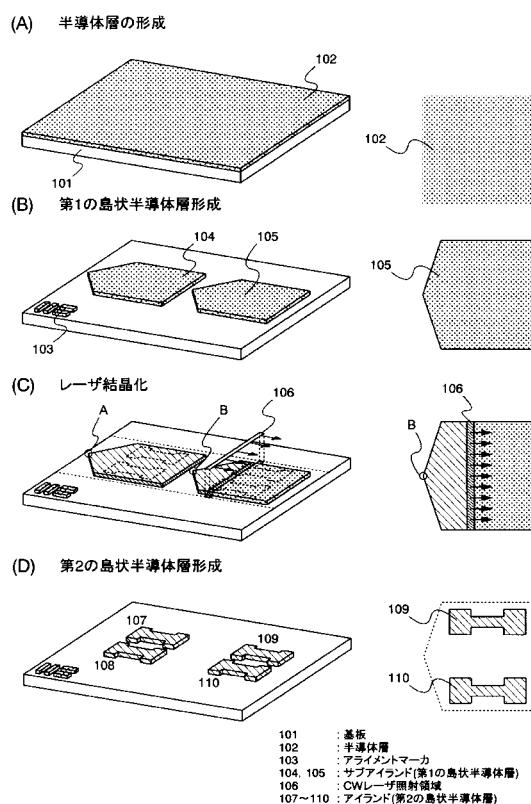

本発明の一実施形態を、図1に沿って説明する。

【0035】

基板101上に、半導体層102を形成する(図1(A))。なお、基板101としては、半導体装置の作製を通じての処理温度に耐えうる材質のものであれば良く、例えば石英基板、シリコン基板、バリウムホウケイ酸ガラスあるいはアルミニノホウケイ酸ガラス等の無アルカリガラス基板、金属基板の表面に絶縁膜を形成した基板等を用いることが出来る。また、処理温度に耐えうる程度の耐熱性を有するプラスチック基板であっても良い。

40

【0036】

なお、基板101と半導体層102との間に、基板101に含まれるアルカリ金属等の不純物による半導体層102の汚染を防ぐための下地膜を、絶縁膜等によって形成しても良い。

【0037】

また、半導体層102は、公知の技術(スパッタ法、LPCVD法、プラズマCVD法等)を用いて成膜すれば良い。また、半導体層102は、非晶質半導体層であっても良いし、微結晶半導体層、多結晶半導体層であっても良い。

50

## 【0038】

続いて、半導体層102をパターニングして、アライメントマーカー103と、五角形状の第1の島状半導体層104、105とを形成する(図1(B))。ここで、アライメントマーカー103、第1の島状半導体層104、105の形状については、図1(B)に示すものに限定しない。

## 【0039】

続いて、図1(C)に示すように、アライメントマーカー103を元に、レーザ照射位置を決定し、第1の島状半導体層104、105にレーザ光106を照射することによって、第1の島状半導体層を形成する半導体層を結晶化する。ここで、第1の島状半導体層を形成する半導体層があらかじめある程度結晶化が進んでいる場合、このレーザ照射工程により、その結晶性がより高められる。ここでは、レーザ光はスリット(図示せず)によってエネルギー密度が低い領域を遮蔽し、半導体層に当たらないようにしている。エネルギー密度の低いレーザ光が半導体層に照射されて結晶化すると、その結晶粒は0.1[μm]程度もしくはそれ以下の微結晶粒となってしまい、そのような結晶性半導体層では優れた電気的特性が得られないためである。

## 【0040】

エネルギー密度が十分か否かは、半導体層において、所望の結晶粒が得られるか否かで判断され、設計者が適宜判断すれば良い。よって、設計者にとって結晶性が十分でないと判断される場合、そのときのエネルギー密度は低いと判断される。

## 【0041】

レーザ光のエネルギー密度は、スリットを介して得られたレーザ光スポットの端部近傍において低くなっているため、照射端部近傍においては結晶粒が小さく、結晶の粒界に沿って突起した部分(リッジ)が出現する。そのため、レーザ光スポットの軌跡(図1(C)に点線で表記)と、第1の島状半導体層104、105が重ならないようにする。最低限、第1の島状半導体層104、105より、後に形成される第2の島状半導体層の領域(図1(C)、第1の島状半導体層104、105中に点線で表記)が、前記レーザ光スポットの軌跡と重ならないようにする。

## 【0042】

なお、第1の島状半導体層にレーザ照射を行う際、レーザ光スポットが第1の島状半導体層の端部に達したときに、レーザ光スポットと第1の島状半導体層とが、基板表面もしくは裏面から見て1点で接するように、レーザ光の走査方向もしくは第1の島状半導体層の形状を決定している。図1(C)において、第1の島状半導体層104、105は、それぞれA点、B点でレーザ光スポットと接する。

## 【0043】

このように、1つの接点よりレーザ光の照射が開始され、結晶化されると、当該接点を含めた近傍より(100)配向面を有する結晶が成長していく。よって最終的に、第1の島状半導体層内では(100)配向面の率が高くなる。すなわち、各結晶粒が等しい配向面を有するため、粒界近傍での電子もしくはホールの移動がスムーズに行われ、よってこのような結晶性半導体層は、大変良好な電界効果移動度を有する。

## 【0044】

本発明では、半導体層に照射するレーザとして、公知のレーザを用いることが出来る。レーザは、パルス発振または連続発振の気体レーザもしくは固体レーザを用いることが出来る。気体レーザとして、エキシマレーザ、Arレーザ、Krレーザ等があり、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YALO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザ等が挙げられる。また、固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、NiまたはTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YALO<sub>3</sub>等の結晶を用いたレーザが適用される。当該レーザの基本波はドーピングする材料によって異なり、1[μm]前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得られる。

10

20

30

40

50

## 【0045】

さらに、固体レーザより発せられた赤外レーザ光を非線形光学素子でグリーンレーザ光に変換後、さらに別の非線形光学素子によって得られる紫外レーザ光を用いることが出来る。

## 【0046】

なお、マーカー103には、必ずしもレーザ照射を行う必要はない。

## 【0047】

続いて、図1(D)に示すように、結晶化された第1の島状半導体層104、105をパターニングすることによって、所望の形状の第2の島状半導体層107～110を形成する。ここで、第2の島状半導体層107～110は、第1の島状半導体層の端部近傍を避け、良好な結晶性が得られている第1の島状半導体層中心近傍の領域を用いているのが望ましい。なお、マーカー103は、後の工程(ゲート電極形成、配線形成等)にて用いるマスクのアライメントに用いるために残しておいても良い。

10

## 【0048】

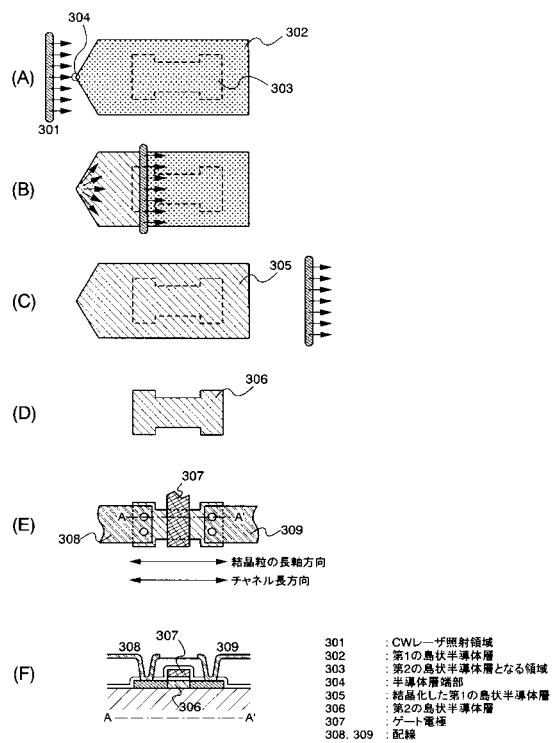

ここまで工程を簡単に図示したものを図3(A)～(D)に示す。以後、ゲート電極307、ソース・ドレイン配線308、309がそれぞれ形成され、TFTとなる。図3(E)において、A-A'における断面図を図3(F)に示す。なおここでは簡単のため、第1の島状半導体層302より、第2の島状半導体層306ただ1つが形成されているが、実際には回路の構成において整合性が求められる複数のTFTの活性層となる複数の第2の島状半導体層が形成され、同様の工程に従ってそれぞれTFTとなる。

20

## 【0049】

1つの第1の島状半導体層より形成される第2の島状半導体層107、108および、109、110は、互いに均一な結晶性を有するため、第2の島状半導体層107、108をそれぞれ活性層としたTFT、あるいは第2の島状半導体層109、110をそれぞれ活性層としたTFTは、その電気的特性が均一となる。よってこれらのTFTを用いて前述のカレントミラー回路のような、構成素子に高い整合性が要求される回路の作製に適したものとなる。

## 【0050】

なおここでは、第1の島状半導体層104、105から、それぞれ2つの第2の島状半導体層が形成されているが、特に1つの第1の島状半導体層より形成される第2の島状半導体層の数は限定しない。ある回路を構成するのに必要なTFTのうち、整合性が要求されるTFTの活性層となる第2の島状半導体層が1つの第1の島状半導体層から形成されれば良い。

30

## 【0051】

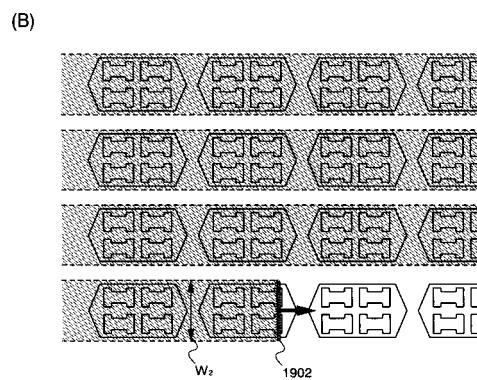

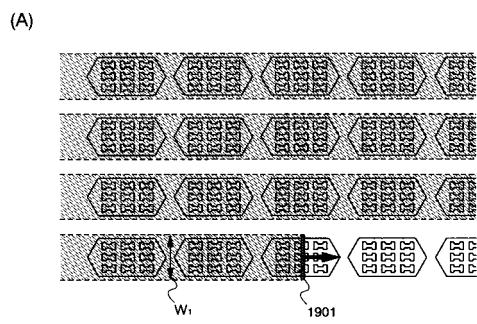

なお、ビームスポットの幅は、第1の島状半導体層または第2の島状半導体層のサイズによって適宜変えることができる。例えば、電流を比較的多く流すことが望まれる駆動回路のTFTは、チャネル幅が大きく、よって第2の島状半導体層のサイズも画素部に比べて大きい傾向にある。図19に、2通りのサイズの六角形状の第1の島状半導体層に、スリットの幅を変えてレーザ光を走査する場合について示す。図19(A)に、走査方向と垂直な方向における第1の島状半導体層の長さが短い場合を、図19(B)に走査方向と垂直な方向における第1の島状半導体層の長さが長い場合の、レーザ光の走査する部分と、第1の島状半導体層との関係を示す。

40

## 【0052】

図19(A)におけるスポット1901の幅をW1、図19(B)におけるスポット1902の幅をW2とすると、W1 < W2となる。もちろん、スポットの幅はこれに限られず、第1の島状半導体層間の走査方向と垂直な方向における間隔に余裕がある場合は、自由にその幅を設定することができる。

## 【0053】

なお本発明では、図19(A)(B)に示すように、レーザ光を基板全面に照射するのではなく、第1の島状半導体層の部分を最低限結晶化できるようにスポットを走査する。基

50

板全面を照射するのではなく、第1の島状半導体層が結晶化できるように必要最低限の部分にレーザ光が照射されるので、1枚の基板にかかる処理時間を抑えることができ、基板処理の効率を高めることができる。

#### 【0054】

##### 【実施例】

以下に、本発明の実施例について記載する。

#### 【0055】

##### [実施例1]

本実施例においては、CWレーザを用いたレーザ結晶化工程の一例について述べる。

#### 【0056】

本方法に適当なCWレーザとしては、波長が550[nm]以下で出力安定性の著しく高いものが望ましい。例えば、YVO<sub>4</sub>レーザの第2高調波や、YAGレーザの第2高調波、YLFレーザの第2高調波、ガラスレーザの第2高調波、YAlO<sub>3</sub>レーザの第2高調波、Arレーザ等が該当する。あるいは、前記レーザのさらなる高次高調波を用いても良い。あるいは、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザ、連続発振のエキシマレーザ、Krレーザ、CO<sub>2</sub>レーザ、連続発振のヘリウムカドミウムレーザ、銅蒸気レーザ、金蒸気レーザ等のレーザを使用しても良い。さらに、これらのレーザを複数、あるいは複数種用いることも可能である。

#### 【0057】

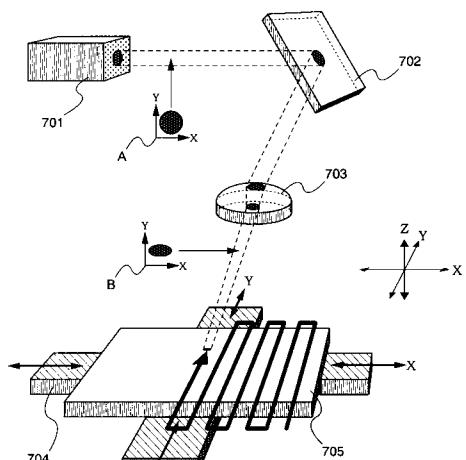

図7は、CWレーザ結晶化を行うための装置を模式的に表したものであり、レーザ発振器701、ミラー702、凸レンズ703、X-Yステージ704等からなる。ここで用いるレーザは、出力10[W]で連続発振のYVO<sub>4</sub>レーザである。レーザ発振器701には、非線形光学素子が内蔵されており、射出口より第2高調波が射出される。

#### 【0058】

レーザ発振器701から射出されたレーザビームは、図7中、Aで示すように円形状をしている。前記レーザビームは水平方向に射出され、ミラー702によって鉛直方向から20°前後の方向に偏向される。その後、水平方向に配置された凸レンズ703により集光される。X-Yステージ704に基板705を固定し、基板上に形成された半導体層上の照射面を、凸レンズ703の焦点に合わせる。このとき、照射面が凸レンズ703と平行になるように配置する。すなわち基板705は水平配置される。凸レンズ703には、20°前後の角度でレーザビームが入射するため、凸レンズの非点収差によって、照射面でのレーザビーム光の形状は橢円形状となる。照射面におけるビーム形状は、凸レンズ703への入射角度によって決定するため、凸レンズに対し、鉛直方向により大きな角度を持ってレーザビームを入射させることによって、さらにアスペクト比の大きい橢円とすることが出来るが、反面、焦点深度が浅くなるために均一な照射が困難となることから、偏向角度は20°前後が妥当であるとしている。

#### 【0059】

基板全面の半導体層を結晶化するためには、適当な照射ピッチで橢円ビームをその長径方向にずらしながら基板上を走査させることを繰り返す必要がある。この動作は、レーザ発振器701、ミラー702、凸レンズ703からなるレーザ出力部分を固定し、X-Yステージ704を用いて、基板上を橢円ビームが走査するように基板を移動させて行う。照射対象である基板のサイズが、図7においてX方向600[mm]、Y方向720[mm]であるとし、橢円ビームの長軸長さが200[μm]であるとき、図7に示す方向で走査すると、3000回(1500往復)の走査によって、基板全面にレーザ照射を行うことが出来る。

#### 【0060】

また、後の実施例で詳しく説明するが、レーザ発振器を複数台用い、橢円ビームを長軸方向に複数並べて平行に走査することにより、走査回数を減らし、処理時間を短縮することも可能である。こうすることにより、単体レーザ光の両端部における、エネルギー密度の低い部分が隣接間で互いに重なり合い、エネルギー密度を高くすることが出来る。よって、有効照射領域を広く、かつ1回の照射領域における有効照射領域の割合を大きくするこ

10

20

30

40

50

とが出来、回路レイアウトの際の制約をより小さくすることも出来る。

【0061】

なお、本実施例は他の実施例と組み合わせて実施することが可能である。

【0062】

[実施例2]

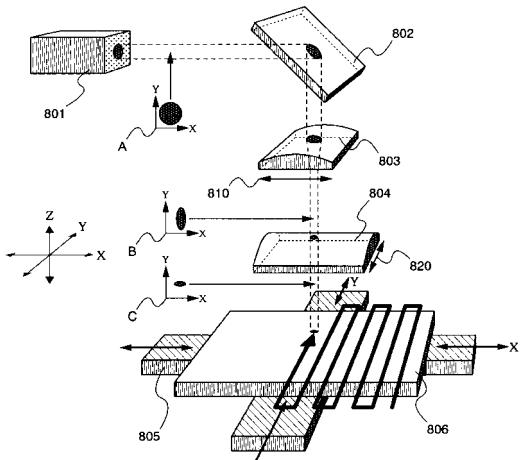

本実施例においては、実施例1とは異なる光学系を用いてレーザビームの偏光を行う例について、図8に沿って説明する。

【0063】

レーザ発振器801から射出されたレーザビームは、図8中、Aで示すように円形状をしている。前記レーザビームは水平方向に射出され、ミラー802によって鉛直方向に偏向される。その後、第1のシリンドリカルレンズ803によってX方向に集光される。このときのビーム形状は、図8中、Bで示すように、円形状がX方向に集光されて、Y方向を長軸とする橢円形状となる。続いて、第2のシリンドリカルレンズ804によってY方向に集光される。このときのビーム形状は、図8中、Cで示すように、さらにY方向に集光されて、X方向を長軸とする橢円形状となる。このような光学系を用いると、実施例2で示したよりもさらにアスペクト比の大きい橢円形状のビームを得ることが出来る。その後、X-Yステージ805に固定された基板806に照射される。基板上のレーザビームの走査については、実施例3と同様にして行えばよい。

【0064】

また、レーザ発振器を複数台用い、橢円ビームを図9に示すように長軸方向に複数並べて平行に走査することにより、走査回数を減らし、処理時間を短縮することも可能である。こうすることにより、単体レーザ光の両端部における、エネルギー密度の低い部分が隣接間で互いに重なり合い、エネルギー密度を高めることが出来る。よって、有効照射領域を広くすることが出来、より回路レイアウトに制約を与えないようにすることも出来る。

【0065】

なお、本実施例は他の実施例と組み合わせて実施することが可能である。

【0066】

[実施例3]

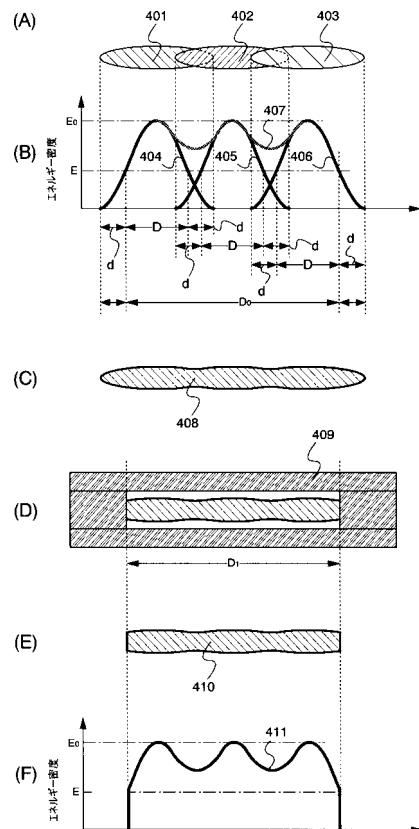

CWレーザによって、実施形態に示した工程に従って半導体層を結晶化する場合、単体のレーザ発振器より発振されるレーザ光の、被照射面における形状は、橢円形状もしくは矩形状である。また、照射面でのエネルギー密度を高めるためにレーザ光をスポット状に絞り込んでいるため、その照射範囲は図6(A)に示すようになる。

【0067】

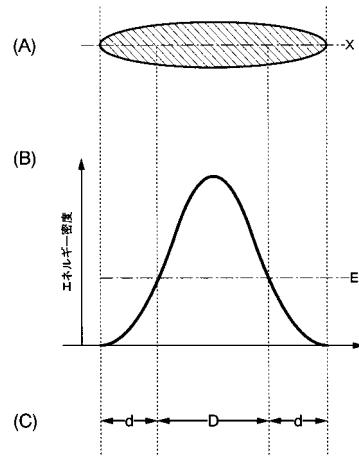

スポット状に絞り込んだレーザ光の中では、さらにエネルギー密度に分布がある。図6(A)において、長軸方向、X断面すなわち橢円の長軸方向におけるエネルギー分布を図6(B)に示す。

【0068】

図6(B)に示すように、レーザ光スポットの中では、中心部から端部に向かって徐々にエネルギー密度が減少する分布を有する。ここで、Eと示しているのは、半導体層を良好に結晶化するために最低限必要なエネルギー密度とする。すると、図6(C)において、Dで示した範囲のレーザ光が照射された半導体層は良好に結晶化し、優れた電気的特性を有する。反面、dで示した範囲のレーザ光が照射された半導体層は、レーザ光のエネルギー密度が十分でないために溶融が十分でなく、微結晶化する。このような領域においては十分な電気的特性が得られないため、活性層として用いるには適さない。

【0069】

本発明のように、複数のTFTを1つの第1の島状半導体層をパターニングして得られる半導体層を用いて作製するには、Dで示した範囲がより広いことが望ましい。しかしレーザ光スポット径を大きくするには限度があるため、その限られた幅で回路を構成しようとすると、素子のレイアウトが困難になる。結果として配線等の引き回しが長くなり、非効率な回路レイアウトとなってしまう。

10

20

30

40

50

## 【0070】

そこで本実施例においては、複数のレーザ発振器から出力されるレーザ光を用いて、効率的なレーザ照射を行う方法の一例について説明する。

## 【0071】

図4(A)を参照する。401～403は、それぞれ異なる3台のレーザ発振器より出力されたレーザ光を、光学系を用いてスポット状に集光したものである。各レーザ光スポット401～403は、各楕円の長軸が直線上に並び、かつ互いのレーザ光スポットの一部が重なることによって合成され、1つのレーザ光スポットとなっている。

## 【0072】

図4(B)に、各レーザ光スポット401～403の、長軸方向のエネルギー密度分布を404～406で示す。各スポットのエネルギー密度は等しく、そのピーク値は $E_0$ で表される。合成されたレーザ光スポットにおいては、重なり合う領域のエネルギー密度は加算され、図4(B)に407で示したようなエネルギー密度分布となる。

## 【0073】

このとき、隣接したスポット404、405が重なり合う領域と、405、406が重なり合う領域においては、2つのスポットのエネルギー密度が加算され、半導体層を良好に結晶化させるのに十分なエネルギー密度を有する。よって、合成後のスポット形状は、図4(C)に408で示す形状となり、この中で半導体層を良好に結晶化させることの出来る範囲は $D_0$ となる。

## 【0074】

なお、隣接したスポットの重なり合う領域におけるエネルギー密度の和は、単体スポットのピーク値 $E_0$ に等しくなるのが理想であるが、 $D_0$ の範囲で半導体層を良好に、かつ均一に結晶化できる範囲の値となるように、適宜スポットの重なり幅を設定すれば良い。

## 【0075】

図4(A)(C)からわかるように、複数のレーザ光スポットを重ね合わせてエネルギー密度の低い部分を互いに補うようにすることで、より広い幅でのレーザ照射が可能となる。

## 【0076】

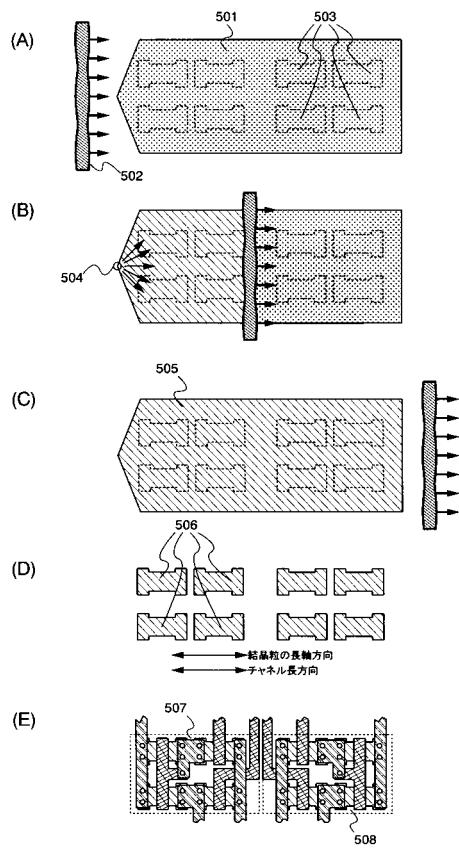

結果、図5(A)～(C)に示すように、複数の第2の島状半導体層が形成される、幅の大きい第1の島状半導体層501を結晶化する場合、合成レーザ光スポット502を用いて、ただ1回の走査で完了することが出来る。よって第1の島状半導体層501は、図5(B)にて504で示す1点が最初にレーザ光スポットと接触して結晶化を開始し、(100)配向面を有する結晶が成長する。得られた第1の島状半導体層505の結晶状態は(100)配向面の率の高が高く、良好なものとなる。

## 【0077】

さらに、図5(D)に示すように、パターニングによって第2の島状半導体層506が形成される。このとき、TFTのチャネル長方向、すなわち電荷の移動方向が、結晶粒の長軸方向、すなわちレーザ光スポットの走査方向と平行あるいはそれに準ずる方向となるようにレイアウトすることによって、TFTのチャネル形成領域における電荷の移動が、結晶粒界に妨げられるのを少なくすることが出来る。

## 【0078】

以後、図5(E)に示すように、ゲート電極、配線等が形成され、回路が完成する。ここでは、2つの作動增幅回路507、508が形成されている。

## 【0079】

図4に戻る。合成レーザ光スポットの使用は、単に広い領域の走査を可能とするだけでなく、効率面でも有利である。単独のレーザ光を用いた場合の照射領域の幅は $(D + 2d)$ であり、図4(C)に示したような合成レーザ光スポットを用いた場合の照射領域の幅は $(D_0 + 2d)$ である。レーザ光スポット1走査幅あたり、良好な結晶化が行える幅の比は、前者は $(D / (D + 2d))$ であり、後者は $(D_0 / (D_0 + 2d))$ となる。 $D < D_0$ であるから、より効率良く、良好な結晶化を行うことが出来るといえる。

## 【0080】

10

20

30

40

50

また、合成レーザ光スポットにおいて、長軸方向の両端に位置する、エネルギー密度の低い領域を、図4(D)に示すように、スリット409を用いて遮蔽し、半導体層に当たらないようにするより望ましい。このとき、半導体層表面でのスポット形状は、図4(E)に示すようになり、長軸方向に $D_1$ ( $< D_0$ )の幅を有する、矩形に近い形状となる。

#### 【0081】

このような形状で半導体層に照射されるレーザ光スポットにおいては、そのスポットにおいて、エネルギー密度の低い領域が存在しない。もしくは存在しても、スリットを用いていない場合と比較してはるかに幅が小さいので、レーザ光スポットの照射端部が第1の島状半導体層上を走査しないようにスポット位置を制御するのがより容易になる。よって、レーザ光の走査経路および、第1の島状半導体層または第2の島状半導体層のレイアウト10時の制約を小さくすることが出来る。

#### 【0082】

さらに、スリットを用いることで、レーザ発振器の出力を止めることなく、エネルギー密度を一定に保ったままでレーザ光スポットの幅を変更することが出来るため、レーザ光スポットの照射端部が第2の島状半導体層もしくはそのチャネル形成領域を走査するのを防ぐことが出来る。また、基板上の不必要的領域にもレーザ光を照射して、基板にダメージが与えられるのを防ぐ効果も期待できる。

#### 【0083】

##### [実施例4]

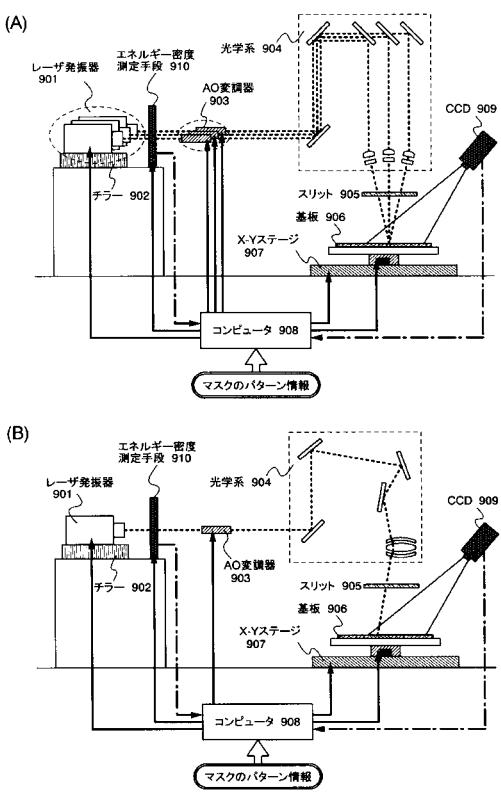

本発明において用いられるレーザ照射装置の制御系を含めた構成について、図9(A)を用いて説明する。901はレーザ発振器である。図9(A)では3つのレーザ発振器を用いて20いるが、レーザ照射装置が有するレーザ発振器はこの数に限定されない。

#### 【0084】

図9(A)のレーザ照射装置は、中央演算処理装置及びメモリ等の記憶手段を兼ね備えたコンピュータ908を有している。コンピュータ908は、レーザ発振器901の発振を制御し、なおかつレーザ光スポットがマスクのパターン情報に従って定められる領域を覆うように、基板106へのレーザ光スポットの照射位置を制御すべく、基板を所定の位置に移動させることができる。

#### 【0085】

なお、レーザ発振器901は、チラー902を用いてその温度を一定に保つようにしても良い。チラー902は必ずしも設ける必要はないが、レーザ発振器901の温度を一定に保つことで、出力されるレーザ光のエネルギーが温度によってばらつくのを抑えることができる。

#### 【0086】

また904は光学系であり、レーザ発振器901から出力された光路を変更したり、そのレーザ光スポットの形状を加工したりして、レーザ光を集光することができる。さらに、図9(A)のレーザ照射装置では、光学系904によって、複数のレーザ発振器901から出力されたレーザ光スポットを互いに一部を重ね合わせることで、合成することができる。

#### 【0087】

なお、レーザ光を一次的に完全に遮蔽することができるAO変調器903を、被処理物である基板906とレーザ発振器901との間の光路に設けても良い。また、AO変調器903の代わりに、テニュエイター(光量調整フィルタ)を設けて、レーザ光のエネルギー密度を調整するようにしても良い。

#### 【0088】

また、被処理物である基板906とレーザ発振器901との間の光路に、レーザ発振器901から出力されたレーザ光のエネルギー密度を測定する手段(エネルギー密度測定手段)910を設け、測定したエネルギー密度の経時変化をコンピュータ908において監視するようにしても良い。この場合、レーザ光のエネルギー密度の減衰を補うように、レーザ発振器901からの出力を高めるようにしても良い。

10

20

30

40

50

**【 0 0 8 9 】**

合成されたレーザ光スポットは、スリット 905 を介して被処理物である基板 906 に照射される。スリット 905 は、レーザ光を遮ることが可能であり、なおかつレーザ光によって変形または損傷しないような材質で形成するのが望ましい。そして、スリット 905 はスリットの幅が可変であり、当該スリットの幅によってレーザ光スポットの幅を変更することができる。

**【 0 0 9 0 】**

なお、スリット 905 を介さない場合の、レーザ発振器 901 から発振されるレーザ光の基板 906 におけるレーザ光スポットの形状は、レーザの種類によって異なり、また光学系により成形することもできる。

10

**【 0 0 9 1 】**

基板 906 は X-Y ステージ 907 上に載置されている。図 9(A)では、X-Y ステージ 907 は、コンピュータによって制御され、被処理物すなわち基板 906 を移動することによってレーザ光スポットの照射位置を制御している。

**【 0 0 9 2 】**

さらに本発明では、コンピュータ 908 によって、スリット 905 の幅を制御し、マスクのパターン情報に従ってレーザ光スポットの幅を変更することができる。

**【 0 0 9 3 】**

さらに図 9(A)のレーザ照射装置は、被処理物の温度を調節する手段を備えていても良い。また、レーザ光は指向性およびエネルギー密度の高い光であるため、ダンパーを設けて、反射光が不適切な箇所に照射されるのを防ぐようにしても良い。ダンパーは、反射光を吸収させる性質を有していることが望ましく、ダンパー内に冷却水を循環させておき、反射光の吸収により隔壁の温度が上昇するのを防ぐようにしても良い。また、X-Y ステージ 907 に基板 906 を加熱するための手段(基板加熱手段)を設けるようにしても良い。

20

**【 0 0 9 4 】**

なお、アライメントマーカーをレーザで形成する場合、マーカー用のレーザ発振器を設けるようにしても良い。この場合、マーカー用のレーザ発振器の発振を、コンピュータ 908 において制御するようにしても良い。さらにマーカー用のレーザ発振器を設ける場合、マーカー用のレーザ発振器から出力されたレーザ光を集光するための光学系を別途設ける。なおマーカーを形成する際に用いるレーザは、代表的には YAG レーザ、CO<sub>2</sub> レーザ等が挙げられるが、もちろんこの他のレーザを用いて形成することは可能である。

30

**【 0 0 9 5 】**

またマーカーを用いた位置合わせのために、CCD カメラ 909 を 1 台、場合によっては数台設けるようにしても良い。

**【 0 0 9 6 】**

なお、マーカーを設けずに、CCD カメラ 909 によって第 1 の島状半導体層のパターンを認識し、位置合わせを行うようにしても良い。この場合、コンピュータ 908 に入力されたマスクによる第 1 の島状半導体層のパターン情報と、CCD カメラ 909 において収集された実際の第 1 の島状半導体層のパターン情報を照らし合わせて、基板の位置情報を把握することができる。この場合マーカーを別途設ける必要がない。

40

**【 0 0 9 7 】**

なお、図 9(A)では、レーザ発振器を複数台設けたレーザ照射装置の構成について示したが、レーザ発振器は 1 台であってもよい。図 9(B)に、レーザ発振器を 1 台用いたレーザ照射装置の構成を示す。図 9(B)において、901 はレーザ発振器、902 はチラーである。また 910 はエネルギー密度測定装置、903 は AO 变調器、904 は光学系、905 はスリット、909 は CCD カメラである。基板 906 は X-Y ステージ 907 上に設置され、レーザ光スポットの基板 906 への照射位置が制御されている。そして図 9(A)に示したものと同様に、コンピュータ 908 によって、レーザ照射装置が有する各手段の動作が制御されている。図 9(A)と異なるのはレーザ発振器が 1 つであることである。したがって、光学系 904 もまた図 9(A)の場合と異なり、1 つのレーザ光を集光する機能

50

を有していれば良い。

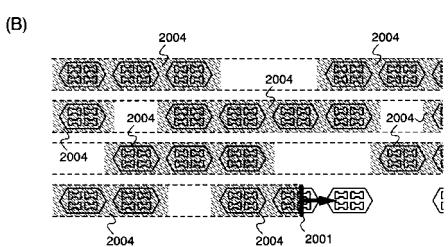

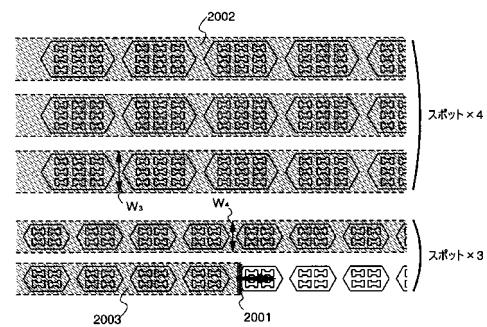

【0098】

図20(A)に、レーザ光を1回照射する場合の、半導体膜のパターニングのマスクの形状と、レーザ光スポット2001の幅の関係を一例として示す。2002と2003は、レーザ光が照射された部分を示している。なお2002は、4つのレーザ発振装置から出力されたレーザ光を重ね合わせて合成することで得られる幅W3のビームスポットを走査した部分、2003は、3つのレーザ発振装置から出力されたレーザ光を重ね合わせて合成することで得られる幅W4のビームスポットを走査した部分である。走査幅は、スリットによって制御しても良いし、一部のレーザ光の出力を停止、もしくはAO変調器を用いて遮蔽しても良い。

10

【0099】

なお本実施例のように、AO変調器を用いることで、全てのレーザ発振装置の出力を止めずにレーザ光スポット2001の幅を自在に変えることができ、レーザ発振装置の出力を止めることで出力が不安定になるのを避けることができる。

【0100】

上記構成により、レーザ光の軌跡の幅を変えることができるので、図20(A)に示すように部分的に第1の島状半導体層の幅が異なっていても、レーザ光の軌跡のエッジが、パターニングによって得られる半導体と重なるのを防ぐことができる。また、また不必要な部分にレーザ光を照射することで基板に与えられるダメージをさらに軽減することができる。

20

【0101】

次に、レーザ光照射の途中で、AO変調器によりレーザ光を遮り、所定の部分にのみレーザ光を照射する例について説明する。なおオーバー光を遮蔽しているが、本発明はこれに限定されず、レーザ光を遮蔽できればどのような手段を用いても良い。

【0102】

本発明では、コンピュータにおいて、入力されたマスクの情報に基づきレーザ光を走査する部分を把握する。さらに本実施例では、走査するべき部分のみにレーザ光が照射されるようにAO変調器を用いてレーザ光を遮る。このときAO変調器は、レーザ光を遮ることが可能であり、なおかつレーザ光によって変形または損傷しないような材質で形成するのが望ましい。

30

【0103】

図20(B)に、半導体膜のパターニングのマスクの形状と、レーザ光が照射される部分の関係を一例として示す。2001は、レーザ光スポットを示しており、2004は、レーザ光が照射された部分を示している。図20(B)に示すとおり、第1の島状半導体層が形成されていない部分を走査するときには、AO変調器によってレーザ光が遮蔽され、基板上に照射されていない。本実施例では結晶化させる必要のない部分にはレーザ光を照射しないか、照射されてもそのエネルギー密度が低くなるようにすることができる。したがって、不必要な部分にレーザ光を照射することで基板に与えられるダメージをさらに軽減することができる。

【0104】

40

[実施例5]

本実施例においては、本発明の半導体装置の作製方法における工程フローについて説明する。

【0105】

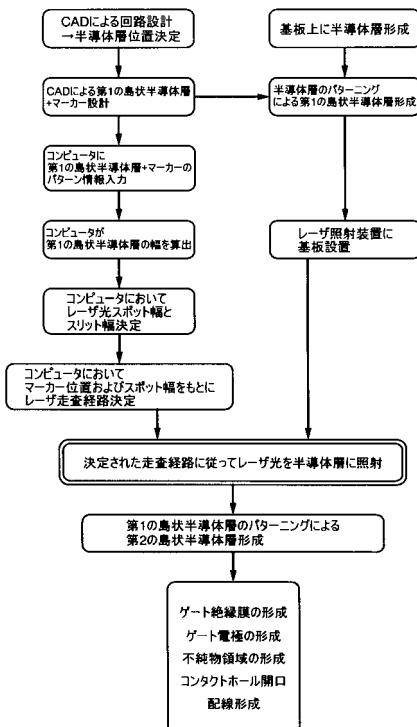

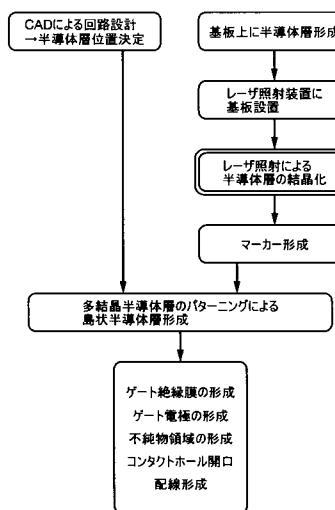

図10に、工程フローを示す。まずCADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

50

## 【0106】

また、このとき第1の島状半導体層と共にマーカーが形成されるように、第1の島状半導体層のマスクを設計するようにしても良い。

## 【0107】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、走査方向に対して垂直方向における、各第1の島状半導体層の幅を算出する。そして、各第1の島状半導体層の幅をもとに、走査方向に対して垂直方向におけるスリットの幅を設定する。

## 【0108】

そして、スリットの幅をもとに、マーカーの位置を基準として、レーザ光の走査経路を定める。

## 【0109】

一方、半導体層基板上に成膜し、第1の島状半導体層のマスクを用いて当該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

## 【0110】

そしてマーカーを基準にして、定められた走査経路にしたがってレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

## 【0111】

そして、レーザ光を照射した後、レーザ光照射により結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

## 【0112】

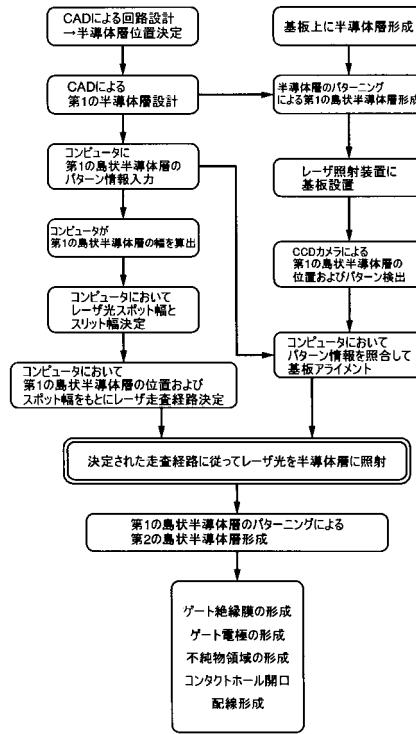

次に、アライメントマーカーを形成することなく、CCDカメラによって基板とマスクのアライメントを行う例について説明する。

## 【0113】

図11に、工程フローを示す。まず図10の場合と同様に、CADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

## 【0114】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、走査方向に対して垂直方向における、各第1の島状半導体層の幅を算出する。そして、各第1の島状半導体層の幅をもとに、走査方向に対して垂直方向におけるスリットの幅を設定する。

## 【0115】

一方、半導体層を基板上に成膜し、第1の島状半導体層のマスクを用いて当該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

## 【0116】

そして、ステージに設置された基板上の第1の島状半導体層のパターン情報を、CCDカメラにより検出し、コンピュータに情報として入力する。コンピュータではCADによっ

10

20

30

40

50

て設計された第1の島状半導体層のパターン情報と、CCDカメラによって得られる、実際に基板上に形成された第1の島状半導体層のパターン情報を照らし合わせ、基板とマスクとの位置合わせを行う。

【0117】

また該スリットの幅と、CCDカメラによる第1の島状半導体層の位置情報をもとに、レーザ光の走査経路を決定する。

【0118】

そして、定められた走査経路にしたがってレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0119】

次に、レーザ光を照射した後、結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

【0120】

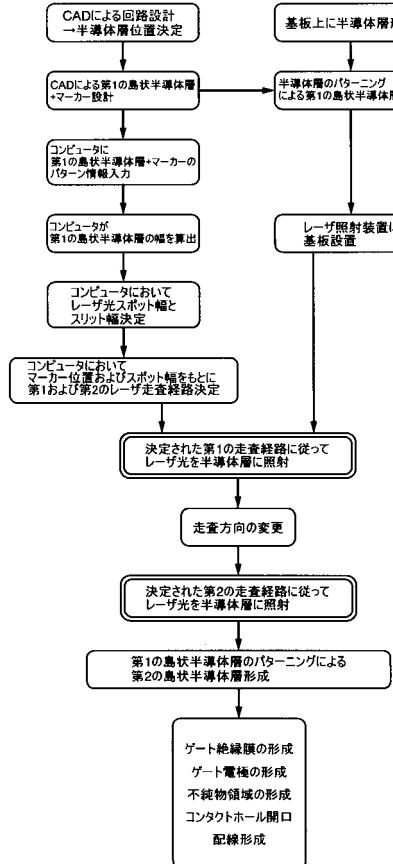

次に、レーザ光の照射を複数回行う例について説明する。ここでは、例として1度レーザ照射を行った後、方向を変えて2度目のレーザ照射を行う工程を挙げる。

【0121】

図12に、工程フローを示す。まずCADを用いて半導体装置の回路設計を行う。回路レイアウト、すなわちTFTの配置が決定すると、第2の島状半導体層の形成場所も決定する。このとき、1つの第1の島状半導体層に含まれる第2の島状半導体層は、チャネル形成領域における電荷の移動方向を、レーザ光の走査方向と平行もしくはそれに準ずる方向に揃えるようにすることが望ましいが、用途に応じて意図的に方向を揃えない様にしても良い。

【0122】

そして、設計された第1の島状半導体層のマスクの形状に関する情報(パターン情報)を、レーザ照射装置が有するコンピュータに入力する。コンピュータでは、入力された第1の島状半導体層のパターン情報に基づき、2つの各走査方向それぞれに対して垂直方向における、各第1の島状半導体層の幅を2通り算出する。そして、各第1の島状半導体層の幅をもとに、2つの各走査方向に対して垂直方向におけるスリットの幅をそれぞれ算出する。

【0123】

そして、2つの各走査方向において、それぞれ定められたスリットの幅をもとに、マーカーの位置を基準として、レーザ光の走査経路を定める。

【0124】

一方、半導体層を基板上に成膜し、第1の島状半導体層のマスクを用いて該半導体層をパターニングし、第1の島状半導体層を形成する。そして第1の島状半導体層が形成された基板を、レーザ照射装置のステージに設置する。

【0125】

そしてマーカーを基準にして、定められた2つの走査経路のうち、第1の走査経路にしたがって第1のレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0126】

そして、走査方向を変え、第2の走査経路にしたがって、第2のレーザ光を照射し、第1の島状半導体層を狙って結晶化する。

【0127】

なお、1回目のレーザ光の走査方向と2回目のレーザ光の走査方向の角度は、予めメモリ等に記憶しておいても良いし、手動でその都度入力するようにしても良い。

10

20

30

40

50

## 【0128】

なお図12では、同じ第1の島状半導体層に2回レーザー光を照射する例について示したが、AO変調器等を用いることで、場所指定して走査方向を変えることも可能である。例えば信号線駆動回路における走査方向と画素部及び走査線駆動回路における走査方向とを異ならせ、AO変調器を用いて信号線駆動回路となる部分においてレーザ光を照射する場合は、AO変調器を用いて画素部及び走査線駆動回路となる部分においてレーザ光が照射されないようにし、画素部及び走査線駆動回路となる部分においてレーザ光を照射する場合は、AO変調器を用いて信号線駆動回路となる部分においてレーザ光が照射されないようにすることができる。そしてこの場合、コンピュータにおいてAO変調器を位置制御手段と同期させるようにする。

10

## 【0129】

なお、レーザ光を照射した後、結晶性が高められた第1の島状半導体層をパターニングし、第2の島状半導体層を形成する。以下、第2の島状半導体層からTFTを作製する工程が行われる。TFTの具体的な作製工程はTFTの形状によって異なるが、代表的にはゲート絶縁膜を成膜し、第2の島状半導体層に不純物領域を形成する。そして、ゲート絶縁膜及びゲート電極を覆うように層間絶縁膜を形成し、当該層間絶縁膜にコンタクトホールを開口し、不純物領域の一部を露出させる。そして当該コンタクトホールを介して不純物領域に接するように層間絶縁膜上に配線を形成する。

## 【0130】

比較対象のために、図13に従来の半導体装置の工程フローを示す。図13に示すように、CADによる半導体装置のマスク設計が行われる。一方で、基板に非晶質半導体層を成膜し、当該非晶質半導体層が成膜された基板をレーザ照射装置に設置する。そして、非晶質半導体層全面にレーザ光が照射されるように走査し、非晶質半導体層を結晶化させる。そして、結晶化により得られた多結晶半導体層にアライメントマーカーを形成し、当該アライメントマーカーを基準として多結晶半導体層をパターニングして第2の島状半導体層を形成する。そして当該第2の島状半導体層を用いてTFTを作製する。

20

## 【0131】

このように本発明では、図13に示すような従来の場合とは異なり、アライメントマーカーをレーザ光を用いて非晶質半導体層を結晶化させる前に形成する。そして、半導体層のパターニングのマスクの情報に従って、レーザ光を走査させる。

30

## 【0132】

上記構成により、基板上の半導体層のうち、パターニングにより除去される部分にレーザ光を照射する時間を省くことができるので、レーザ光照射にかかる時間を短縮化することができ、なおかつ基板の処理速度を向上させることができる。

## 【0133】

なお、レーザ光による結晶化工程の前に、触媒を用いて半導体層を結晶化させる工程を含んでいても良い。触媒元素を用いる場合、特開平7-130652号公報、特開平8-78329号公報で開示された技術を用いることが望ましい。

## 【0134】

触媒を用いて半導体層を結晶化させる工程を含んでいる場合、非晶質半導体層を成膜後にNiを用いて結晶化させる工程(NiSPC)を含んでいる。例えば特開平7-130652号公報に開示されている技術を用いる場合、重量換算で10[ppm]のニッケルを含む酢酸ニッケル塩溶液を非晶質半導体層に塗布してニッケル含有層を形成し、500、1時間の脱水素工程の後、500~650[ ]で4~12時間、例えば550[ ]、8時間の熱処理を行い結晶化する。尚、使用可能な触媒元素は、ニッケル(Ni)の以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素を用いても良い。

40

## 【0135】

そして、レーザ光照射により、NiSPCにより結晶化された半導体層の結晶性をさらに高める。レーザ光照射により得られた多結晶半導体層は触媒元素を含んでおり、レーザ光

50

照射後にその触媒元素を結晶質半導体層から除去する工程(ゲッタリング)を行う。ゲッタリングは特開平10-135468号公報または特開平10-135469号公報等に記載された技術を用いることができる。

【0136】

具体的には、レーザ照射後に得られる多結晶半導体層の一部にリンを添加し、窒素雰囲気中で550～800[ ]、5～24時間、例えば600[ ]、12時間の熱処理を行う。すると多結晶半導体層のリンが添加された領域がゲッタリングサイトとして働き、多結晶半導体層中に存在するリンを、当該ゲッタリングサイトに偏析させることができる。その後、多結晶半導体層のリンが添加された領域をパーニングにより除去することで、触媒元素の濃度を $1 \times 10^{17}$ atms/cm<sup>3</sup>以下好ましくは $1 \times 10^{16}$ atms/cm<sup>3</sup>程度にまで低減された第2の島状半導体層を得ることができる。

10

【0137】

[実施例6]

本実施例においては、基板上の回路配置とCWレーザ照射方向等について数例を挙げて説明する。

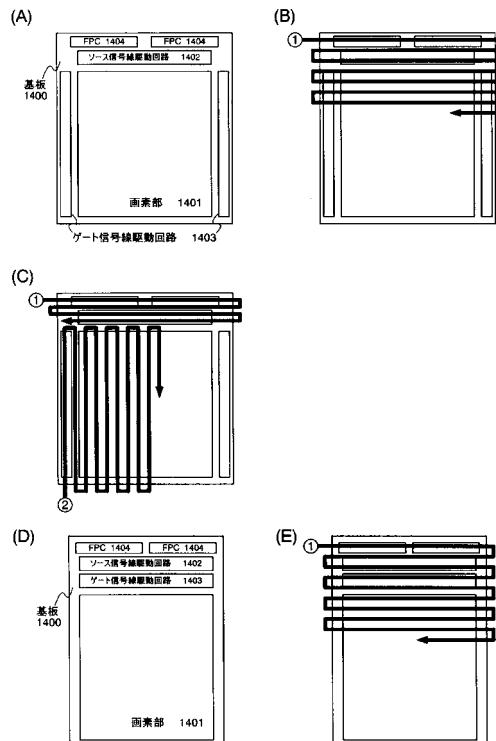

【0138】

表示装置の構成例としては、図14(A)に示すように、基板1400の中央部に画素部1401を有し、画素部1401の上側もしくは下側に、ソース信号線駆動回路1402を有し、画素部1401の左右いずれかもしくは両側に、ゲート信号線駆動回路1403を有する構成が一般的といえる。各駆動回路を動作させるための信号および電源は、基板外部よりフレキシブルプリント基板(Flexible Print Circuit: FPC)1404を介して入力される。

20

【0139】

図14(A)に示すように、ソース信号線駆動回路1402は、画素の列方向に延びて配置されており、ゲート信号線駆動回路1403は、画素の行方向に延びて配置されているため、実施形態に示したようにCWレーザ照射を行うと、図14(B)に示すように、ソース信号線駆動回路の配置方向に方向を合わせた場合、ゲート信号線駆動回路の配置方向に、CWレーザの照射方向が合致しないことになる。しかし、一般的に高速駆動が要求されるソース信号線駆動回路に対し、ゲート信号線駆動回路は、その駆動周波数はおよそ数百分の1で良く、仮にゲート信号線駆動回路を構成するTFTの活性層に微結晶半導体層である部分が含まれていたとしても、回路の動作に関しては問題ないといえる。

30

【0140】

ここで、図14(C)に示すように、走査方向を途中で切り替える方法を用いても良い。つまり、第1に、ソース信号線駆動回路に合わせて、第1のレーザ走査を行い、続いて、基板を固定しているステージを90°回転させる等によって、レーザの走査方向を変更し、今度はゲート信号線駆動回路と画素部とに合わせて、第2のCWレーザ照射を行っても良い。

【0141】

また、図14(D)に示すように、特願2001-241463号に記載の技術によって、ソース信号線駆動回路1402と、ゲート信号線駆動回路1403とを、画素部の1辺側、もしくは対向する2辺の側に平行配置することにより、図14(E)に示すように、1度のCWレーザ照射によって結晶化し、かつ画素部、駆動回路における半導体層を、1方向のみのレーザ光照射によって構成することが可能となる。

40

【0142】

本実施例にて示した方法はあくまでも一例であり、例えば高速駆動が要求される駆動回路部のみをレーザ照射によって結晶化し、画素部等、比較的高速駆動が必要でない部分においては、従来の結晶化方法を用いて作製しても良い。なお、本実施例は他の実施例と組み合わせて実施することが可能である。

【0143】

[実施例7]

50

本実施例では、アクティブマトリクス基板の作製方法について図15、16を用いて説明する。本明細書ではC M O S回路を有する駆動回路と、画素部とを同一基板上に形成された基板を、便宜上アクティブマトリクス基板と呼ぶ。

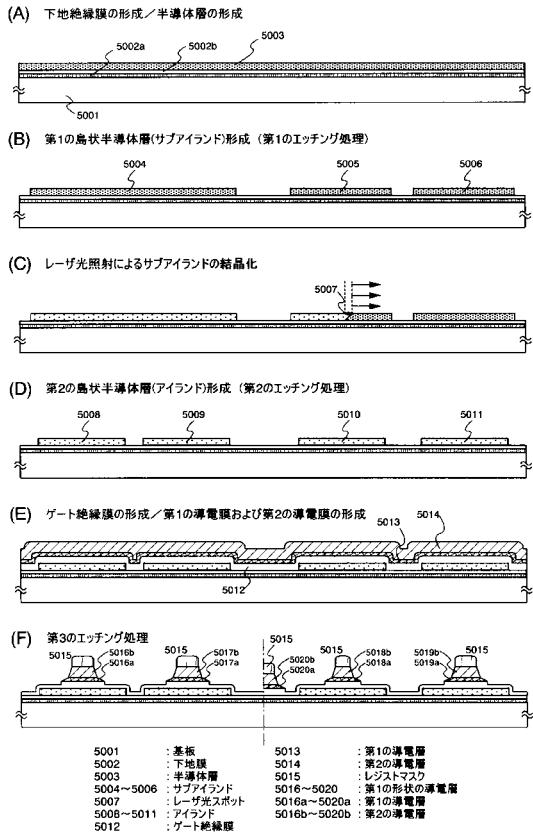

#### 【0144】

まず、本実施例ではバリウムホウケイ酸ガラス、またはアルミニウムホウケイ酸ガラスなどのガラスからなる基板5001を用いる。なお、基板5001としては、石英基板やシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。

#### 【0145】

次いで、基板5001上に酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの絶縁膜から成る下地膜5002を公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により形成する。本実施例では下地膜5002として下地膜5002a、5002bの2層の下地膜を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。

#### 【0146】

次いで、下地膜5002上に、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により25～80[nm](好ましくは30～60[nm])の厚さで半導体層5003を形成する。なお、この半導体層は、非晶質半導体層であっても良いし、微結晶半導体層、あるいは結晶性半導体層であっても良い。また、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体層を用いても良い(図15(A))。

#### 【0147】

次に、半導体層5003をパターニングし、フッ化ハロゲン、例えば、ClF、ClF<sub>3</sub>、BrF、BrF<sub>3</sub>、IF、IF<sub>3</sub>等を含む雰囲気で異方性ドライエッティング法によりエッティング(第1のエッティング処理)することで、第1の島状半導体層5004～5006を形成する(図15(B))。

#### 【0148】

次に、第1の島状半導体層5004～5006をレーザ結晶化法により結晶化させる。半導体層が微結晶半導体層、あるいは結晶性半導体層の場合、この工程によってその結晶性がさらに高められる。レーザ結晶化法は、本発明の実施形態や実施例1～6に記載されたレーザ照射方法を用いて行う。具体的には、レーザ照射装置のコンピュータに入力されたマスクの情報に従って、第1の島状半導体層5004～5006に選択的にレーザ光を照射する。もちろん、レーザ結晶化法だけでなく、他の公知の結晶化法(RTAやファーネスアニール炉を用いた熱結晶化法、結晶化を助長する金属元素を用いた熱結晶化法等)と組み合わせて行ってもよい。

#### 【0149】

半導体層の結晶化に際しては、連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波を用いることで、大粒径の結晶を得ることができる。代表的には、Nd:YVO<sub>4</sub>レーザ(基本波1064[nm])の第2高調波(532[nm])や第3高調波(355[nm])を用いるのが望ましい。具体的には、出力10[W]の連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または機能形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01～100[MW/cm<sup>2</sup>]程度(好ましくは0.1～10[MW/cm<sup>2</sup>])が必要である。そして、10～2000[cm/s]程度の速度でレーザ光に対して相対的に半導体層が形成された基板5001を移動させて照射する。

#### 【0150】

なおレーザ照射は、パルス発振または連続発振の気体レーザもしくは固体レーザを用いることができる。気体レーザとして、エキシマレーザ、Arレーザー、Krレーザーなどがあり、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザー、YLFレーザ、YAlO<sub>3</sub>レーザー、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレ

10

20

30

40

50

ーザなどが挙げられる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザ等も使用可能である。当該レーザの基本波はドーピングする材料によって異なり、1 [μm]前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。

【 0 1 5 1 】

上述したレーザ結晶化によって、第1の島状半導体層5004～5006にレーザ光が照射され、結晶性が高められる(図15(C))。

【 0 1 5 2 】

次に、結晶性が高められた第1の島状半導体層5004～5006を所望の形状にパターンング(第2のエッチング処理)して、第2の島状半導体層5008～5011を形成する(図15(D))。

【 0 1 5 3 】

また、第2の島状半導体層5008～5011を形成した後、TFTのしきい値を制御するためには微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

【 0 1 5 4 】

次いで、第2の島状半導体層5008～5011を覆うゲート絶縁膜5012を形成する。ゲート絶縁膜5012はプラズマCVD法またはスパッタ法を用い、厚さを40～150[nm]として珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により110[nm]の厚さで酸化窒化珪素膜(組成比Si = 32[%]、O = 59[%]、N = 7[%]、H = 2[%])で形成した。勿論、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【 0 1 5 5 】

また、酸化珪素膜を用いる場合には、プラズマ CVD 法で TEOS (Tetraethyl Orthosilicate) と  $O_2$  を混合し、反応圧力 40 [Pa]、基板温度 300 ~ 400 [°C] とし、高周波 (13.56 [MHz]) 電力密度 0.5 ~ 0.8 [W/cm<sup>2</sup>] で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後 400 ~ 500 [°C] の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【 0 1 5 6 】

次いで、ゲート絶縁膜 5012 上に膜厚 20 ~ 100 [nm] の第 1 の導電層 5013 と、膜厚 100 ~ 400 [nm] の第 2 の導電層 5014 とを積層形成する。本実施例では、膜厚 30 [nm] の TaN 膜からなる第 1 の導電層 5013 と、膜厚 370 [nm] の W 膜からなる第 2 の導電層 5014 を積層形成した。TaN 膜はスパッタ法で形成し、Ta のターゲットを用い、窒素を含む雰囲気内でスパッタする。また、W 膜は、W のターゲットを用いたスパッタ法で形成した。その他に 6 フッ化タンゲステン (WF<sub>6</sub>) を用いる熱 CVD 法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W 膜の抵抗率は 20 [μ cm] 以下にすることが望ましい。W 膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W 膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度の W (純度 99.999 [%]) のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮して W 膜を形成することにより、抵抗率 9 ~ 20 [μ cm] を実現することができる。

【 0 1 5 7 】

a N)で形成し、第2の導電層をWとする組み合わせ、第1の導電層を窒化タンタル(T a N)膜で形成し、第2の導電層をA 1膜とする組み合わせ、第1の導電層を窒化タンタル(T a N)膜で形成し、第2の導電層をC u膜とする組み合わせとしてもよい。

#### 【0158】

また、2層構造に限定されず、例えば、タングステン膜、アルミニウムとシリコンの合金(A 1 - S i)膜、窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、タングステンに代えて窒化タングステンを用いてもよいし、アルミニウムとシリコンの合金(A 1 - S i)膜に代えてアルミニウムとチタンの合金膜(A 1 - T i)を用いてもよいし、窒化チタン膜に代えてチタン膜を用いてもよい。

#### 【0159】

なお、導電層の材料によって、適宜最適なエッティングの方法や、エッチャントの種類を選択することが重要である(図15(E))。

#### 【0160】

次に、フォトリソグラフィ法を用いてレジストからなるマスク5015を形成し、電極及び配線を形成するための第3のエッティング処理を行う。第3のエッティング処理では第1及び第2のエッティング条件で行う。(図15(F))本実施例では第1のエッティング条件として、I C P (Inductively Coupled Plasma: 誘導結合型プラズマ)エッティング法を用い、エッティング用ガスにC F<sub>4</sub>とC l<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25:25:10 [sccm]とし、1 [Pa]の圧力でコイル型の電極に500 [W]のR F (13.56 [MHz])電力を投入してプラズマを生成してエッティングを行う。基板側(試料ステージ)にも150 [W]のR F (13.56 [MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッティング条件によりW膜をエッティングして第1の導電層の端部をテーパー形状とする。

#### 【0161】

この後、レジストからなるマスク5015を除去せずに第2のエッティング条件に変え、エッティング用ガスにC F<sub>4</sub>とC l<sub>2</sub>とを用い、それぞれのガス流量比を30:30 [sccm]とし、1 [Pa]の圧力でコイル型の電極に500 [W]のR F (13.56 [MHz])電力を投入してプラズマを生成して約30秒程度のエッティングを行った。基板側(試料ステージ)にも20 [W]のR F (13.56 [MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。C F<sub>4</sub>とC l<sub>2</sub>を混合した第2のエッティング条件ではW膜及びT a N膜とも同程度にエッティングされる。なお、ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10~20 [%]程度の割合でエッティング時間を増加させると良い。

#### 【0162】

上記第3のエッティング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15~45°となる。こうして、第3のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5016~5020(第1の導電層5016a~5020aと第2の導電層5016b~5016b)を形成する。ゲート絶縁膜5012においては、第1の形状の導電層5016~5020で覆われない領域は20~50 [nm]程度エッティングされ、薄くなった領域が形成される。

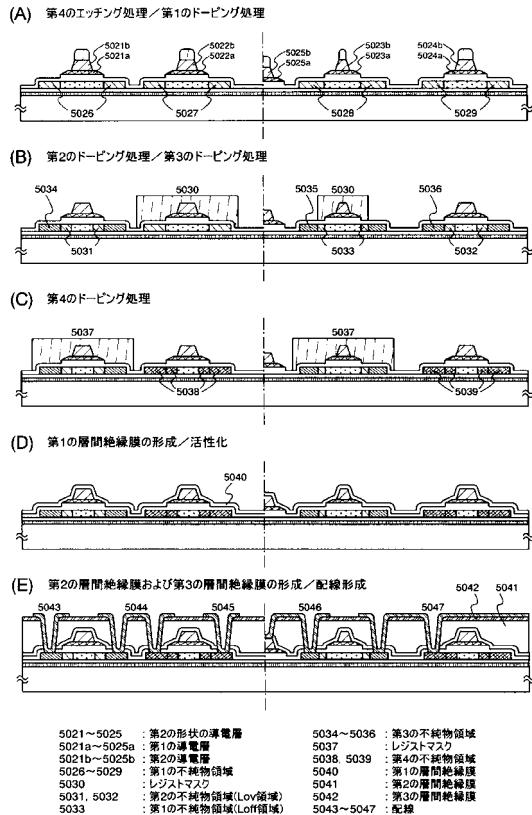

#### 【0163】

次いで、レジストからなるマスク5015を除去せずに第4のエッティング処理を行う(図16(A))。ここでは、エッティングガスにC F<sub>4</sub>とC l<sub>2</sub>とO<sub>2</sub>とを用い、W膜を選択的にエッティングする。この時、第4のエッティング処理により第2の導電層5021b~5025bを形成する。一方、第1の導電層5016a~5020aは、ほとんどエッティングされず、第2の形状の導電層5021~5025を形成する。

#### 【0164】

そして、レジストからなるマスク5015を除去せずに第1のドーピング処理を行い、第2の島状半導体層にn型を付与する不純物元素を低濃度に添加する。ドーピング処理はイ

10

20

30

40

50

オンドープ法、若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーザ量を  $1 \times 10^{13} \sim 5 \times 10^{14} [\text{cm}^2]$  とし、加速電圧を  $40 \sim 80 [\text{keV}]$  として行う。本実施例ではドーザ量を  $1.5 \times 10^{13} [\text{cm}^2]$  とし、加速電圧を  $60 [\text{keV}]$  として行う。n型を付与する不純物元素として 15 族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、導電層 5021 ~ 5025 が n型を付与する不純物元素に対するマスクとなり、自己整合的に不純物領域 5026 ~ 5029 が形成される。不純物領域 5026 ~ 5029 には  $1 \times 10^{18} \sim 1 \times 10^{20} [\text{cm}^3]$  の濃度範囲で n型を付与する不純物元素を添加する。

#### 【0165】

次に、レジストからなるマスク 5015 を除去した後、新たにレジストからなるマスク 5030 を形成して第1のドーピング処理よりも高い加速電圧で第2のドーピング処理を行う。イオンドープ法の条件はドーザ量を  $1 \times 10^{13} \sim 1 \times 10^{15} [\text{cm}^2]$  とし、加速電圧を  $60 \sim 120 [\text{keV}]$  として行う。ドーピング処理は第2の導電層 5021b ~ 5025b を不純物元素に対するマスクとして用い、第1の導電層のテーパー部の下方の第2の島状半導体層に不純物元素が添加されるようにドーピングする。続いて、第2のドーピング処理より加速電圧を下げる第3のドーピング処理を行って図 16(B)の状態を得る。イオンドープ法の条件はドーザ量を  $1 \times 10^{15} \sim 1 \times 10^{17} [\text{cm}^2]$  とし、加速電圧を  $50 \sim 100 [\text{keV}]$  として行う。第2のドーピング処理および第3のドーピング処理により、第1の導電層と重なる低濃度不純物領域 5031、5032 には  $1 \times 10^{18} \sim 5 \times 10^{19} [\text{cm}^3]$  の濃度範囲で n型を付与する不純物元素を添加され、高濃度不純物領域 5034 ~ 5036 には  $1 \times 10^{19} \sim 5 \times 10^{21} [\text{cm}^3]$  の濃度範囲で n型を付与する不純物元素が添加される。

#### 【0166】

もちろん、適当な加速電圧にすることで、第2のドーピング処理および第3のドーピング処理は1回のドーピング処理で、低濃度不純物領域および高濃度不純物領域を形成することも可能である。

#### 【0167】

次いで、レジストからなるマスク 5030 を除去した後、新たにレジストからなるマスク 5037 を形成して第4のドーピング処理を行う。この第4のドーピング処理により、pチャネル型 TFT の活性層となる第2の島状半導体層に前記一導電型とは逆の導電型を付与する不純物元素が添加された不純物領域 5038、5039 を形成する。第2の導電層 5021a ~ 5025a を不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に不純物領域を形成する。本実施例では、不純物領域 5038、5039 はジボラン( $\text{B}_2\text{H}_6$ )を用いたイオンドープ法で形成する(図 16(C))。この第4のドーピング処理の際には、nチャネル型 TFT を形成する第2の島状半導体層はレジストからなるマスク 5037 で覆われている。第1乃至3のドーピング処理によって、不純物領域 5038、5039 にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においても p型を付与する不純物元素の濃度を  $1 \times 10^{19} \sim 5 \times 10^{21} [\text{cm}^3]$  となるようにドーピング処理することにより、pチャネル型 TFT のソース領域およびドレイン領域として機能するために何ら問題は生じない。

#### 【0168】

以上までの工程で、それぞれの第2の島状半導体層に不純物領域が形成される。

#### 【0169】

次いで、レジストからなるマスク 5037 を除去して第1の層間絶縁膜 5040 を形成する。この第1の層間絶縁膜 5040 としては、プラズマ CVD 法またはスパッタ法を用い、厚さを  $100 \sim 200 [\text{nm}]$  として珪素を含む絶縁膜で形成する。本実施例では、プラズマ CVD 法により膜厚  $150 [\text{nm}]$  の酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜 5040 は酸化窒化珪素膜に限定されるものなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

#### 【0170】

10

20

30

40

50

次いで、第2の島状半導体層に添加された不純物を活性化する処理を行う(図16(D))。活性化処理としては、レーザアニール法を用いる。レーザアニール法を用いる場合、結晶化の際に用いたレーザを使用することが可能である。活性化の場合は、移動速度は結晶化と同じにし、0.01~100 [MW/cm<sup>2</sup>]程度(好ましくは0.01~10 [MW/cm<sup>2</sup>])のエネルギー密度が必要となる。また結晶化の際には連続発振のレーザを用い、活性化の際にはパルス発振のレーザを用いるようにしても良い。

#### 【0171】

また、第1の層間絶縁膜を形成する前に活性化処理を行っても良い。

#### 【0172】

そして、加熱処理(300~550 [ ]で1~12時間の熱処理)を行うと水素化を行うことができる。この工程は第1の層間絶縁膜5040に含まれる水素により第2の島状半導体層のダンギングボンドを終端する工程である。第1の層間絶縁膜の存在に関係なく第2の島状半導体層を水素化することができる。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)や、3~100 [%]の水素を含む雰囲気中で、300~650 [ ]で1~12時間の加熱処理を行っても良い。

10

#### 【0173】

次いで、第1の層間絶縁膜5040上に無機絶縁膜材料または有機絶縁物材料から成る第2の層間絶縁膜5041を形成する。本実施例では、膜厚1.6 [μm]のアクリル樹脂膜を形成した。次に、第2の層間絶縁膜5041を形成した後、第2の層間絶縁膜5041に接するように、第3の層間絶縁膜5042を形成する。

20

#### 【0174】

そして、配線5043~5047を形成する。なお、これらの配線は、膜厚50 [nm]のTi膜と、膜厚500 [nm]の合金膜(A1とTiとの合金膜)との積層膜をパターニングして形成する。もちろん、二層構造に限らず、単層構造でもよいし、三層以上の積層構造にしてもよい。また、配線の材料としては、A1とTiに限らない。例えば、TaN膜上にA1やCuを形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成してもよい。(図16(E))

#### 【0175】

以上の様にして、nチャネル型TFTとpチャネル型TFTからなるCMOS回路を有する駆動回路と、画素TFTと保持容量とを有する画素部を同一基板上に形成することができる。こうして、アクティブマトリクス基板が完成する。

30

#### 【0176】

なお、本実施例は他の実施例と組み合わせて実施することが可能である。

#### 【0177】

##### [実施例8]

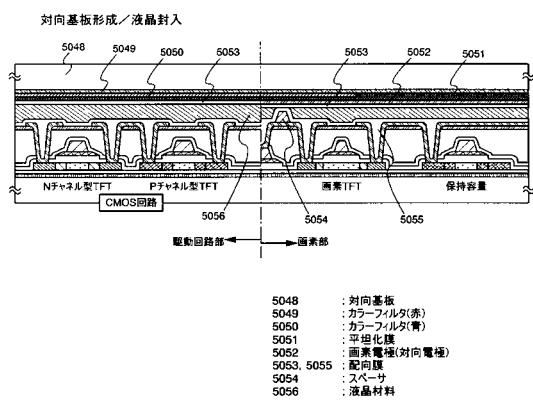

本実施例では、実施例7で作製したアクティブマトリクス基板から、反射型液晶表示装置を作製する工程を以下に説明する。説明には図16、17を用いる。

#### 【0178】

まず、実施例5に従い、図16(E)の状態のアクティブマトリクス基板を得た後、当該アクティブマトリクス基板上、少なくとも配線(画素電極)5047上に配向膜5055を形成しラビング処理を行う。なお、本実施例では配向膜5055を形成する前に、アクリル樹脂膜等の有機樹脂膜をパターニングすることによって基板間隔を保持するための柱状のスペーサ5054を所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

40

#### 【0179】

次いで、対向基板5048を用意する。対向基板5048上に着色層(カラーフィルタ)5049、5050(ここでは2色のカラーフィルタのみを図示しているが、実際にはR、G、Bの3色を用いて良い。)および平坦化膜5051を形成する。ここでは、赤色のカラーフィルタ5049と青色のカラーフィルタ5050とを重ねて、遮光部を形成する。また、赤色の着色層と緑色の着色層とを一部重ねて、遮光部を形成してもよい。同様に

50

、隣接した画素間の隙間をカラーフィルタの積層によって遮光する。このようにして、遮光膜の形成工程を省略した。

【0180】

次いで、平坦化膜5051を形成し、当該平坦化膜5051上に透明導電膜からなる対向電極5052を少なくとも画素部に形成し、対向基板の全面に配向膜5053を形成し、ラビング処理を施した。

【0181】

そして、アクティブマトリクス基板と対向基板とをシール材(図示せず)で貼り合わせる。シール材にはフィラーが混入されており、このフィラーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料5056を注入し、封止剤(図示せず)によって完全に封止する。液晶材料5056には公知の液晶材料を用いれば良い。このようにして図17に示す反射型液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、対向基板のみに偏光板(図示せず)を貼りつけた。そして、公知の技術を用いてフレキシブルプリント基板(Flexible Print Circuit: FPC)を貼りつけた。

【0182】

以上のようにして作製される液晶表示装置はエネルギー分布が周期的または一様なレーザ光が照射され、大粒径の結晶粒が形成された半導体膜を用いて作製されたTFTを有しており、前記液晶表示装置の動作特性や信頼性を十分なものとなり得る。そして、このような液晶表示装置は各種電子機器の表示部として用いることができる。

【0183】

なお、本実施例は他の実施例と組み合わせて実施することが可能である。

【0184】

[実施例9]

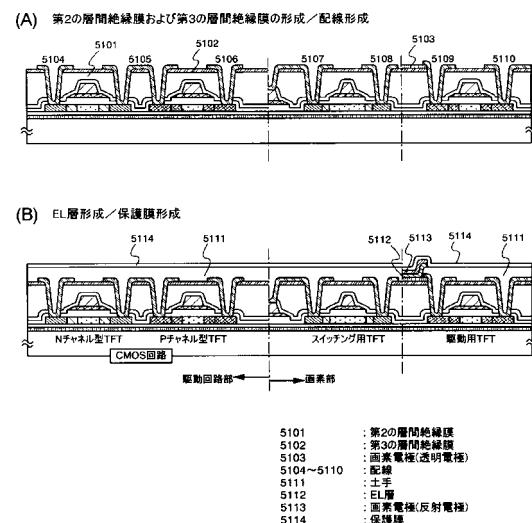

本実施例では、実施例7に示したアクティブマトリクス基板の作製方法を用いて作製されたアクティブマトリクス基板を用いて、発光装置を作製する例を以下に説明する。発光装置とは、基板上に形成された発光素子を、当該基板とカバー材の間に封入した表示用パネルおよび該表示用パネルにTFT等を実装した表示用モジュールを総称したものである。なお、発光素子は、電場を加えることで発生するルミネッセンス(Electro Luminescence)が得られる有機化合物を含む層(発光層)と陽極層と、陰極層とを有する。また、有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)があり、これらのうちどちらか、あるいは両方の発光を含む。

【0185】

なお、本明細書中では、発光素子において陽極と陰極の間に形成された全ての層をEL層と定義する。EL層には具体的に、発光層、正孔注入層、電子注入層、正孔輸送層、電子輸送層等が含まれる。基本的に発光素子は、陽極層、発光層、陰極層が順に積層された構造を有しており、この構造に加えて、陽極層、正孔注入層、発光層、陰極層や、陽極層、正孔注入層、発光層、電子輸送層、陰極層等の順に積層した構造を有していることもある。

【0186】

実施例7に従って第3の層間絶縁膜5102まで形成した後、発光素子の陽極となる画素電極を、透明導電膜からなる材料にて形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したもの用いても良い。

【0187】

第3の層間絶縁膜5102は、発光装置の場合、第2の層間絶縁膜5101に含まれる水分が有機発光層に入るのを防ぐのに効果的である。第2の層間絶縁膜5101が有機樹脂材料を有している場合、有機樹脂材料は水分を多く含むため、第3の層間絶縁膜5102

10

20

30

40

50

を設けることは特に有効である。また、本実施例においては、樹脂からなる第2の層間絶縁膜5101を用いてTFTによる段差を平坦化することは非常に重要である。後に形成される発光層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、発光層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

## 【0188】

駆動回路が有するnチャネル型TFT、pチャネル型TFTは実施例5の作製方法を用いて形成される。なお、本実施例ではシングルゲート構造としているが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

## 【0189】

次に、図18(B)に示すように、第3の層間絶縁膜5102を覆うように黒色染料、カーボンまたは黒色の顔料などを分散した樹脂膜を成膜し、発光素子となる部分に開口部を形成することで、遮蔽膜(図示せず)を成膜する。なお樹脂として、代表的にはポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)等が挙げられるが、上記材料に限定されない。また有機樹脂の他に、遮蔽膜の材料として例えば、珪素、酸化珪素、酸化窒化珪素などに黒色染料、カーボンまたは黒色の顔料を混入したものを用いることも可能である。遮蔽膜は、配線5104～5110において反射した外光が、観察者の目に入るのを防ぐ効果がある。その後、各不純物領域に達するコンタクトホールを開口し、配線5104～5110を形成する。

## 【0190】

続いて、樹脂材料でなる土手5111を形成する。土手5111は1～2[μm]厚のアクリル膜またはポリイミド膜をパターニングして画素電極5103の一部を露出させるように形成する。

## 【0191】

画素電極5103の上にはEL層5112が形成される。なお、図18(B)では一画素しか図示していないが、本実施例ではR(赤)、G(緑)、B(青)の各色に対応したEL層を作り分けている。また、本実施例では蒸着法により低分子系有機発光材料を形成している。具体的には、正孔注入層として20[nm]厚の銅フタロシアニン(CuPc)膜を設け、その上に発光層として70[nm]厚のトリス-8-キノリノラトアルミニウム錯体(A1q<sub>3</sub>)膜を設けた積層構造としている。A1q<sub>3</sub>にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで発光色を制御することができる。

## 【0192】

但し、以上の例は発光層として用いることのできる有機発光材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせて発光層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。例えば、本実施例では低分子系有機発光材料を発光層として用いる例を示したが、中分子系有機発光材料や高分子系有機発光材料を用いても良い。なお、ここでいう中分子系有機発光材料とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが10[μm]以下の有機発光材料を指す。また、高分子系有機発光材料を用いる例として、正孔注入層として20[nm]のポリチオフェン(PEDOT)膜をスピニ塗布法により設け、その上に発光層として100[nm]程度のパラフェニレンビニレン(PPV)膜を設けた積層構造としても良い。なお、PPVの共役系高分子を用いると、赤色から青色まで発光波長を選択できる。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機発光材料や無機材料は公知の材料を用いることができる。

## 【0193】

次に、EL層5112の上には、陰極として画素電極5113が設けられる。本実施例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはこれらの元素を添加した導電膜を用いれ

10

20

30

40

50

ば良い。

【0194】

この画素電極 5113 まで形成された時点で発光素子が完成する。なお、ここでいう発光素子とは、画素電極（陽極）5103、EL層5112、および陰極5113で形成された素子を指す。

【0195】

また、発光素子を完全に覆うようにして保護膜5114を設けても良い。保護膜5114としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、当該絶縁膜を単層もしくは組み合わせた積層で用いる。

【0196】

この際、カバレッジの良い膜を保護膜5114として用いることが好ましく、炭素膜、特にDLC（ダイヤモンドライクカーボン）膜を用いることは有効である。DLC膜は室温から100[ ]以下の温度範囲で成膜可能であるため、耐熱性の低い発光層5112の上方にも容易に成膜することができる。また、DLC膜は酸素に対するプロッキング効果が高く、発光層5112の酸化を抑制することが可能である。そのため、この後に続く封止工程を行う間に発光層5112が酸化するといった問題を防止できる。

【0197】

本実施例では、発光層5112は全てバリア性の高い炭素膜、窒化珪素、窒化酸化珪素、窒化アルミニウムもしくは窒化酸化アルミニウム等の無機絶縁膜で覆われているため、水分や酸素等が発光層に入りて発光層が劣化するのをより効果的に防ぐことができる。

【0198】

また、第3の層間絶縁膜5102、保護膜5114を、シリコンをターゲットとしたスパッタリング法により作製される窒化珪素膜を用いることで、より発光層への不純物の侵入を防ぐことができる。成膜条件は適宜選択すれば良いが、特に好ましくはスパッタガスには窒素（N<sub>2</sub>）又は窒素とアルゴンの混合ガスを用い、高周波電力を印加してスパッタリングを行う。基板温度は室温の状態とし、加熱手段を用いなくても良い。既に有機絶縁膜や有機化合物層を形成した後は、基板を加熱せずに成膜することが望ましい。但し、吸着又は吸蔵している水分を十分除去するために、真空中で数分～数時間、50～100[ ]程度で加熱して脱水処理することは好ましい。

【0199】

室温でシリコンをターゲットとし、13.56[MHz]の高周波電力を印加し、窒素ガスのみ用いたスパッタリング法で形成された窒化珪素膜は、その赤外吸収スペクトルにおいてN-H結合とSi-H結合の吸収ピークが観測されず、またSi-Oの吸収ピークも観測されていないことが特徴的であり、膜中に酸素濃度及び水素濃度は1[原子%]以下であることがわかっている。このことからも、より効果的に酸素や水分などの不純物の侵入を防ぐことができるのがわかる。

【0200】

こうして図18（B）に示すような構造の発光装置が完成する。なお、土手5111を形成した後、保護膜5114を形成するまでの工程を、大気解放せずに連続的に処理することは有効である。

【0201】

なお本実施例では遮蔽膜を第3の層間絶縁膜5102と土手5111との間に形成したが、本発明はこの構成に限定されない。配線5104～5110において反射した外光が、観察者の目に入るのを防ぐことができる位置に設けることが肝要である。例えば、本実施例のように発光素子から発せられる光が基板側に向かう構成である場合、第1の層間絶縁膜と第2の層間絶縁膜5101との間に遮蔽膜を設けるようにしても良い。そしてこの場合においても、遮蔽膜は発光素子からの光が通過できるように開口部を有する。

【0202】

さらに、実施例7において説明したように、ゲート電極に絶縁膜を介して重なる不純物領域を設けることによりホットキャリア効果に起因する劣化に強いnチャネル型TFTを形

10

20

30

40

50

成することができる。そのため、信頼性の高い発光装置を実現できる。

【0203】

また、本実施例では画素部と駆動回路の構成のみ示しているが、本実施例の製造工程に従えば、その他にも信号分割回路、D/Aコンバータ、オペアンプ、補正回路などの論理回路を同一の絶縁体上に形成可能であり、さらにはメモリやマイクロプロセッサをも形成しうる。

【0204】

以上のようにして作製される発光装置はエネルギー分布が周期的または一様なレーザ光が照射され、大粒径の結晶粒が形成された半導体膜を用いて作製されたTFTを有しており、前記発光装置の動作特性や信頼性を十分なものとなり得る。そして、このような発光装置は各種電子機器の表示部として用いることができる。

【0205】

なお、本実施例では、発光素子から発せられる光がTFT側に向かっているが、発光素子がTFTとは反対側に向かっていても良い。この場合、土手5111に黒色染料、カーボンまたは黒色の顔料を混入した樹脂を用いることができる。この場合、画素電極5103には反射性に優れた材料を用い、画素電極5113には透明導電膜を用いる。

【0206】

なお、本実施例は実施例1～実施例6のいずれか一と組み合わせて実施することが可能である。

【発明の効果】

本発明によると、1つの第1の島状半導体層より形成される单数もしくは複数の第2の島状半導体層を活性層として用いたTFTは、その特性を通常よりも均一化することが可能となるため、前記カレントミラー回路や差動増幅回路、あるいはオペアンプ回路といった、素子同士の整合性が求められる回路を、TFTを用いて基板上に構成することが可能となる。結果、従来は外付けIC等によって実装されていた回路を、画素部を含む基板上に同時形成することが可能となり、製造コスト削減、装置の軽量、小型化に寄与する。

【図面の簡単な説明】

【図1】 本発明の一実施形態を説明する図。

【図2】 回路を構成するTFTに特に整合性が求められる回路の例（カレントミラー回路、差動増幅回路）を示す図。

【図3】 第1の島状半導体層からTFT形成までの工程と、TFTの断面を示す図。

【図4】 複数のレーザ光スポットから、合成レーザ光スポットを生成する図。

【図5】 合成レーザ光スポットによって結晶化される第1の島状半導体層と、当該第1の島状半導体層から形成された第2の島状半導体層を用いたTFTによって回路を構成する例を示す図。

【図6】 レーザ光スポットとそのエネルギー密度分布を説明する図。

【図7】 レーザ光照射工程の概略図。

【図8】 レーザ光照射工程の概略図。

【図9】 制御系を含むレーザ照射装置の概略図。

【図10】 半導体層へのレーザ照射による結晶化を含む工程フローの一例を説明する図。

【図11】 半導体層へのレーザ照射による結晶化を含む工程フローの一例を説明する図。

【図12】 半導体層へのレーザ照射による結晶化を含む工程フローの一例を説明する図。

【図13】 半導体層へのレーザ照射による結晶化を含む工程フローの一例を説明する図。

【図14】 基板上でのレーザ光走査方向の例を説明する図。

【図15】 半導体装置の作製工程を説明する図。

【図16】 半導体装置の作製工程を説明する図。

10

20

30

40

50

- 【図17】 液晶表示装置の作製工程を説明する図。

- 【図18】 発光装置の作製工程を説明する図。

- 【図19】 基板照射中のレーザ光の照射幅の変更について説明する図。

- 【図20】 基板照射中のレーザ光の照射幅の変更および遮蔽について説明する図。

- 【図21】 合成レーザ光スポットによって、複数の点から結晶化が進行する場合の第1の島状半導体層を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

701:レーザ発振器

702:ミラー

703:凸レンズ

704:X-Yステージ

705:基板

【図8】

801:レーザ発振器

802:ミラー

803:第1のシリンドリカルレンズ

804:第2のシリンドリカルレンズ

805:X-Yステージ

806:基板

【図9】

—: コンピュータ908が送出する制御信号

—: コンピュータ908に入力される検出信号

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 萩原 周治

(56)参考文献 特開2001-291666(JP,A)

特開昭59-046021(JP,A)

特開平07-335906(JP,A)

特開平07-130652(JP,A)

特開平08-078329(JP,A)

特開平10-135468(JP,A)

特開平10-135469(JP,A)

特開2000-174282(JP,A)

特開2000-150377(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

G02F 1/1343-1/1345

G02F 1/135-1/1368

H01L 21/26-21/268

H01L 21/322-21/326

H01L 21/336

H01L 29/786