(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-502626

(P2006-502626A)

(43) 公表日 平成18年1月19日(2006.1.19)

|                     |           |             |

|---------------------|-----------|-------------|

| (51) Int.CI.        | F 1       | テーマコード (参考) |

| HO3M 1/50 (2006.01) | HO3M 1/50 | 5 J 001     |

| HO3K 5/05 (2006.01) | HO3K 5/05 | 5 J 022     |

| HO3K 7/08 (2006.01) | HO3K 7/08 | A           |

審査請求 未請求 予備審査請求 未請求 (全 14 頁)

|               |                              |          |                                                                                                                             |

|---------------|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2004-542048 (P2004-542048) | (71) 出願人 | 500575824<br>ハネウェル・インターナショナル・インコ<br>ーポレーテッド<br>アメリカ合衆国・07962-2245・<br>ニュージャージー・モーリスタウン・ピー<br>オー・ボックス・2245・コロンビア・<br>ロード・101 |

| (86) (22) 出願日 | 平成15年10月2日 (2003.10.2)       | (74) 代理人 | 100089705<br>弁理士 社本 一夫                                                                                                      |

| (85) 翻訳文提出日   | 平成17年4月20日 (2005.4.20)       | (74) 代理人 | 100076691<br>弁理士 増井 忠式                                                                                                      |

| (86) 國際出願番号   | PCT/US2003/031242            | (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                                                       |

| (87) 國際公開番号   | W02004/032330                | (74) 代理人 | 100080137<br>弁理士 千葉 昭男                                                                                                      |

| (87) 國際公開日    | 平成16年4月15日 (2004.4.15)       |          |                                                                                                                             |

| (31) 優先権主張番号  | 10/263,931                   |          |                                                                                                                             |

| (32) 優先日      | 平成14年10月2日 (2002.10.2)       |          |                                                                                                                             |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                             |

最終頁に続く

(54) 【発明の名称】パルス幅変調アナログデジタル変換

## (57) 【要約】

アナログ信号を精度良く確実に変換するためにパルス幅変調を使用するアナログデジタル変換方法及び装置が提供される。この方法及び装置によれば、最も厳しい環境における要求を満たすアナログデジタル変換器(ADC)が実現可能である。さらに、多くの用途で求められる高精度を満たすADCが実現可能である。この方法及び装置に係るADCは、受け取ったアナログ入力をアナログ信号入力に応じたデューティサイクルのパルス幅変調信号に変換する。パルス幅変調信号はデューティサイクル機構に送られてパルス幅変調信号のデューティサイクルが決定される。決定されたデューティサイクルにより、アナログ信号に比例したデジタル値が生成される。この好適な方法及び装置により、広範囲の環境で使用可能な正確且つ高信頼性のADCが得られる。

**【特許請求の範囲】****【請求項 1】**

a ) アナログ信号を受け取り、前記アナログ信号に応じたデューティサイクルを有するパルス幅変調信号を出力するパルス幅変調器と、

b ) 前記パルス幅変調信号を受け取り、前記パルス幅変調信号のデューティサイクルに基づいて前記アナログ信号に比例したデジタル値を決定するデューティサイクル機構と、を備えるアナログデジタル変換器。

**【請求項 2】**

前記パルス幅変調器は、入力及び出力を有するコンパレータと、第1の入力、第2の入力、及び出力を有する演算增幅器を備え、前記演算增幅器の出力は前記コンパレータの入力に接続され、前記コンパレータの出力は前記演算增幅器の第1の入力にフィードバックされる、請求項1に記載のアナログデジタル変換器。10

**【請求項 3】**

前記コンパレータはフリップフロップを備える、請求項2に記載のアナログデジタル変換器。

**【請求項 4】**

前記コンパレータはインバータを備える、請求項2に記載のアナログデジタル変換器。

**【請求項 5】**

前記コンパレータの出力は第1のインバータを介して前記演算增幅器入力にフィードバックされる、請求項2に記載のアナログデジタル変換器。20

**【請求項 6】**

さらに前記コンパレータの出力はフィードバック経路により前記コンパレータの入力にもフィードバックされる、請求項2に記載のアナログデジタル変換器。

**【請求項 7】**

さらに、前記演算增幅器の出力と前記コンパレータの入力間に接続される第1の抵抗と、前記フィードバック経路内において前記コンパレータの出力と前記コンパレータの入力間に接続される第2の抵抗を備え、前記第1及び第2の抵抗は前記コンパレータの出力にヒステリシスを与えるように選択される、請求項6に記載のアナログデジタル変換器。

**【請求項 8】**

前記デューティサイクル機構は、前記パルス幅変調信号のアクティブな部分をカウントするアクティブカウンタを備える、請求項1に記載のアナログデジタル変換器。30

**【請求項 9】**

さらに前記デューティサイクル機構は、前記パルス幅変調信号の1以上の周期をカウントする周期カウンタを備える、請求項8に記載のアナログデジタル変換器。

**【請求項 10】**

前記デューティサイクル機構は前記アクティブカウンタをラッチするラッチを備える、請求項8に記載のアナログデジタル変換器。

**【請求項 11】**

前記デューティサイクル機構はFPGAで構成される、請求項1に記載のアナログデジタル変換器。40

**【請求項 12】**

a ) パルス幅変調器と、

該パルス幅変調器は、

i ) 第1の入力、第2の入力、及び出力を有し、第1の入力でアナログ信号を受け取る演算增幅器と、

ii ) コンパレータ入力及びコンパレータ出力を有し、コンパレータ入力で前記演算增幅器の出力を受け取り、コンパレータ出力は前記演算增幅器の第1の入力に接続され、コンパレータ出力は前記演算增幅器の出力に応じて遷移し、遷移したコンパレータ出力は前記演算增幅器の第1の入力にフィードバックされてコンパレータ出力に第2の遷移を生じさせ、第1及び第2の遷移により前記アナログ信号に応じたデューティサイクルを有する

50

パルス幅変調信号が生成されるようにしたコンパレータと、を含み、

b) 前記パルス幅変調信号を受け取り、前記パルス幅変調信号のデューティサイクルから前記アナログ信号に比例したデジタル値を決定するデューティサイクル機構と、備えるアナログデジタル変換器。

【請求項 1 3】

前記コンパレータはフリップフロップを備える、請求項 1 2 に記載のアナログデジタル変換器。

【請求項 1 4】

さらに当該アナログデジタル変換器は、前記演算増幅器の出力と前記コンパレータ入力間に接続される第 1 の抵抗を備え、前記コンパレータ出力は第 2 の抵抗を介して前記コンパレータ入力にフィードバックされ、前記第 1 及び第 2 の抵抗により前記コンパレータにヒステリシスを作成する、請求項 1 3 に記載のアナログデジタル変換器。

【請求項 1 5】

前記コンパレータはインバータを備える、請求項 1 2 に記載のアナログデジタル変換器。

【請求項 1 6】

さらに、前記コンパレータ出力と前記第 1 の入力間にインバータ及び抵抗を備える、請求項 1 2 に記載のアナログデジタル変換器。

【請求項 1 7】

a) 電圧のアナログ入力信号を受け取るステップと、

b) 前記アナログ入力信号を、前記アナログ信号の電圧に応じたデューティサイクルを有するパルス幅変調信号に変換するステップと、

c) 前記パルス幅変調信号のデューティサイクルを決定するステップと、

d) 前記デューティサイクルから前記アナログ信号の電圧に比例したデジタル値を出力するステップと、

を備える方法。

【請求項 1 8】

前記デューティサイクルを決定するステップは、前記パルス幅変調信号がイネーブルになる部分の時間をカウントするとともに前記パルス幅変調信号の周期をカウントする、請求項 1 7 に記載の方法。

【請求項 1 9】

さらに前記デューティサイクルを決定するステップは、前記カウントされた前記パルス幅変調信号がイネーブルになる部分の時間と前記カウントされた前記パルス幅変調信号の周期の比を算出する、請求項 1 8 に記載の方法。

【請求項 2 0】

前記パルス幅変調ステップは、出力を遷移し、遷移した出力をフィードバックして第 2 の遷移を生じさせ、第 1 及び第 2 の遷移により前記アナログ信号の電圧に応じたデューティサイクルを有するパルス幅変調信号を生成する、請求項 1 7 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は概して電子システムに関し、詳細にはアナログデジタル変換技術に関する。

【背景技術】

【0 0 0 2】

現代の暮らしは電子システムに益々依存するようになっている。電子機器は非常に洗練された装置へと変貌を遂げ、様々な用途で利用されている。電子機器が日常生活に不可欠なものとなっていくなかで、電子機器の信頼性や正確さに対する要求は高まり続けている。

【0 0 0 3】

10

20

30

40

50

信頼性や精度が重要な条件になる電子部品の一種としてアナログデジタル変換器(ADC)がある。ADCはアナログ信号を受け取り、受け取ったアナログ信号を何らかの方法でそれに比例するデジタル値に変換する装置である。デジタル計算装置が益々一般化するなかで、高精度、高信頼性ADC装置に対するニーズは増加している。

#### 【0004】

既存のADC装置は回路が複雑化し、アプリケーションの要求する堅牢さと精度を備えていない。例えば、宇宙飛行体における用途において、宇宙の使用で増加する放射線に十分な精度をもつADC装置は入手困難である。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

したがって、求められているものは、アナログ信号からデジタル信号への変換において、現代のシステムが要求する高信頼性、高精度の条件を満たすように改良した装置及び方法である。

#### 【課題を解決するための手段】

#### 【0006】

本発明は、アナログ信号を精度よく確実に変換するためにパルス幅変調を使用するアナログデジタル変換方法及び装置を提供する。このアナログデジタル変換方法及び装置は、最も厳しい環境の要求を満たすアナログデジタル変換器(ADC)で実現することができる。さらに、様々な用途で求められる高精度を満たすADCを実現することができる。

#### 【0007】

このアナログデジタル変換方法及び装置に係るADCは、受け取ったアナログ入力をアナログ入力に応じたデューティサイクルのパルス幅変調信号に変換する。パルス幅変調信号はデューティサイクル機構に送られてパルス幅変調信号のデューティサイクルが決定される。決定されたデューティサイクルに基づいて、アナログ入力に比例したデジタル値が生成される。このような方法及び装置により、広範囲の環境で使用可能な正確で信頼性のあるADCが得られる。

#### 【0008】

本発明の前記及び他の目的、特徴及び効果は、添付図面に示されるような発明を実施するための最良の形態に関する以下の説明から明らかになろう。

#### 【発明を実施するための最良の形態】

#### 【0009】

以下、添付図面を参照して本発明の好適な実施形態について説明する。図面中、同様な要素には同様な参照符号が付されている。

本発明は、アナログ信号を精度良く確実に変換するためにパルス幅変調を使用するアナログデジタル変換方法及び装置を提供する。この方法及び装置は、最も厳しい環境の要求に適合できるアナログデジタル変換器(ADC)を実現可能である。さらに、多くの用途で必要とされる高精度を与えるADCを実現可能である。

#### 【0010】

この方法及び装置は、受け取ったアナログ入力をアナログ入力に応じたデューティサイクルのパルス幅変調信号に変換するADCを提供する。パルス幅変調信号はデューティサイクル機構に送られてパルス幅変調信号のデューティサイクルが決定される。決定されたデューティサイクルから、アナログ入力に比例したデジタル値が生成される。この好適な方法及び装置により、広範囲の環境で使用可能な正確で信頼性のあるADCが得られる。

#### 【0011】

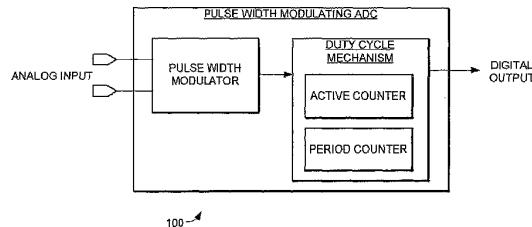

図1に、好適な実施形態のパルス幅変調ADC100の概略図を示す。パルス幅変調ADC100はアナログ入力を受けるとそれをパルス幅変調器に渡す。パルス幅変調器はアナログ入力をそれに応じたパルス幅変調信号に変換する。パルス幅変調信号はデューティサイクル機構に送られ、デューティサイクル機構はパルス幅変調信号のデューティサイクルを決定し、アナログ入力信号に比例したデジタル値を出力する。図示の実施形態におい

10

20

30

40

50

て、デューティサイクル機構はアクティブカウンタと周期カウンタを備える。アクティブカウンタはパルス幅変調信号がイネーブルなる部分の時間を測定する。周期カウンタはパルス幅変調信号の周期を決定する。パルス幅変調信号のデューティサイクルはイネーブル時間と周期時間の比によって決定される。デューティサイクル機構は、決定されたデューティサイクルに基づいて、原アナログ入力信号に比例したデジタル出力を発生する。

#### 【0012】

図2にパルス幅変調器200の概略図を示す。パルス幅変調器200はパルス幅変調ADC100に使用可能な種類の変調器の例である。パルス幅変調器200はアナログ入力信号を受け取り、アナログ入力信号に応じたパルス幅を有するパルス幅変調信号を出力する。パルス幅変調器200は、演算増幅器201、フリップフロップ203、インバータ205、コンデンサ211、213、及び抵抗221、223、225、227、229、231、233、235を備える。さらにパルス幅変調器200は、オフセット入力、試験入力、及びクロック入力を受け取る。第1のフィードバック経路として、フリップフロップ203の出力はインバータ205及び抵抗221を介して演算増幅器201の入力にフィードバックされる。第2のフィードバック経路として、フリップフロップ203の出力は抵抗235を介してフリップフロップ203のD入力にフィードバックされる。数値例として、コンデンサ211、213は220ピコファラド、抵抗221、225、227、231は500キロオーム、抵抗223、229は250キロオーム、抵抗235は50キロオーム、抵抗233は10キロオームであってよい。

10

#### 【0013】

アナログ入力はデジタル値に変換すべきアナログ信号を受け取る。アナログ入力は、コモンモード電圧との差分信号からなる入力信号を受け取るように構成されてよく、あるいは、他入力をグランドとしたシングルエンド入力信号を受け取るようにしてもよい。

20

#### 【0014】

オフセット入力から演算増幅器入力にオフセット電圧が加えられる。全入力電圧をゼロボルトにならないようにオフセット電圧が与えられる、さもなければ無数のまたは一定デューティサイクルの出力に潜在的になるであろう。オフセット電圧入力の値は、アナログ入力に入力される電圧範囲に依存する。例えば、アナログ入力が0.0から4.5Vの電圧で受け取られる場合、適切なオフセット電圧は150mVである。また、アナログ入力に負の電圧入力を受ける場合、オフセットはアナログ入力が正の範囲に移行するのに十分であるように一般に選ばれる。

30

#### 【0015】

試験入力からパルス幅変調器200に試験信号が入力され、この試験信号はパルス幅変調ADC200が正常に動作しているかを決定するために使用される。通常動作中、試験信号は実質的にゼロボルトでディスイネーブルされ、ADCは通常に動作する。試験中、試験信号はイネーブルされ、制限された方法でADCの出力を変化させる。この変化監視されてADCが正常に動作しているかを決定する。デジタル出力が正常に変化しなければ、ADCは正常に動作していないと知らされる。試験信号は制御されたデューティサイクルを有するパルス列信号であるのが好ましい。パルス幅変調器200出力を異なるデューティサイクルを有する異なる試験信号で評価することにより、パルス幅変調器200の動作を十分に評価できる。フリップフロップ203と同一のクロック入力で動作するカウンタにより適切な試験信号を生成し、インバータ205と同種のインバータを使用してこの試験信号を試験入力に入力できる。試験信号はDC電圧レベル信号であってもよく、その場合、通常動作中は、ディスイネーブルされて実質的にゼロボルトになり、試験中は、イネーブルされて出力デューティサイクルを既知の変化を与える。

40

#### 【0016】

クロック入力からは、フリップフロップ203の出力とフィードバックのタイミングを制御するクロック信号が与えられる。クロックレートはパルス幅変調器100に要求される分解能に依存し、一般にクロックレートが高いほど分解能も高くなる。一実施例において、クロック入力は32MHzクロックである。

50

## 【0017】

パルス幅変調器200はフリップフロップ203をコンパレータとして用い、これによる非線形フィードバックによりパルス幅変調信号を生成する。後で詳述するように、例えば論理インバータのような他のコンパレータ装置を用いてもよい。一般に、コンパレータ出力は演算増幅器出力に応じて遷移する。この遷移出力は演算増幅器201の入力にフィードバックされ、これにより第2の遷移がコンパレータ出力に発生する。コンパレータ出力に第1と第2の遷移が発生することにより、アナログ信号に応じたデューティサイクルを有するパルス幅変調信号が発生することになる。

## 【0018】

図1の実施形態において、コンパレータはフリップフロップ203で構成される。演算増幅器201はアナログ信号を受け取り、信号をフリップフロップ203のD入力に出力する。フリップフロップ203出力遷移状態は、演算増幅器201出力によりD入力が閾値電圧を交差した後のクロックのエッジで示す。反転出力Qバーはインバータ205と抵抗221を介してフィードバックされる。インバータ205は基準電圧VREFで電力がオフし、入力電圧に応じてゼロ電圧または基準電圧になる精密振幅フィードバックを与える。出力Qは抵抗235を介してフィードバックされ、フリップフロップ203のスイッチング動作にヒステリシスを与える。

## 【0019】

パルス幅変調器200はESD保護用に入力コンデンサ241を備える。入力抵抗225と227は高入力インピーダンスを与え、PWM信号のデューティサイクルは、フィードバック抵抗221に対する抵抗225、227の比に反比例する。抵抗223、229、231は、抵抗225、227、221と結合して、前記数値例のような適切な数値を取る場合、アナログ入力信号の同相モード成分を除去する。コンデンサ211、213により、演算増幅器201の出力に発生する「のこぎり」波形は演算増幅器のスルーレート以下に抑えられる。

## 【0020】

フリップフロップ203の入力での抵抗233、235はヒステリシスのレベルを設定するものである。さらに抵抗233、235は、コンデンサ213、抵抗221と共に、PWM信号の周波数を制御する。特に、フリップフロップ203のQ出力から抵抗235を通るフィードバック経路は制御されたヒステリシスを与え、高周波信号を制限する。演算増幅器201の出力がローレベルで、その結果フリップフロップ203のQ出力がローレベルになるとき、入力抵抗233、235は電圧分割器になるため、フリップフロップ入力の論理ハイは検知される前に演算増幅器201の出力はレベルVHに立ち上がらなければならない。ここに、 $VH = (R1 + R2) * VTH / R2$ である（ここに、R1は抵抗233の抵抗値、R2は抵抗235の抵抗値、VTHはD入力の閾値電圧である）。演算増幅器201の出力がこの値を超えると、次のクロックの立上りエッジで出力Q、Qバーの状態が変化し、Qは論理ハイに、Qバーは論理ローになる。抵抗235を通る正フィードバックによりD入力は引き上げられる一方、Qバーからインバータ205を通る主フィードバックにより演算増幅器201の出力は下降する。演算増幅器201の出力変化率はコンデンサ213により制御される。演算増幅器201の出力が下降していくにつれ、D入力電圧は、抵抗235がVREFに引き上げられるため、演算増幅器201の出力電圧より高くなる。そして抵抗235により演算増幅器201の出力は強制的にレベルVLに下降していく。ここに、 $VL = (R2 - R1) * VTH / R2$ である。演算増幅器201の出力がこの値より低くなると、次のクロックの立上りエッジでフリップフロップ203の出力は変化し、Q出力はローになる。このとき、抵抗235の正フィードバックによりD入力は引き下げられる。このように、抵抗233、235によりヒステリシスが与えられて、コンデンサ213、抵抗221とともにPWM信号の周波数が制御されるとともに、D入力電圧は全時間に閾値レベルにないことを確かにする。

## 【0021】

さらに抵抗233は、電源投入により演算増幅器203が最初に飽和する際に、演算増

10

20

30

40

50

幅器 203 の出力電流を制限する。

アナログから PWMへの変換を説明するため、インバータ 205 の出力が論理ハイ V R E F である場合を考えてみる。この条件下では、抵抗 221 を通る過大なフィードバックにより演算增幅器 201 の出力はローに駆動される。フリップフロップ 203 の D 入力電圧が閾値より小さくなると、次のクロックサイクルで Q バー出力はハイになる。このハイの信号はインバータ 205、抵抗 221 を経由して演算增幅器 201 の負入力にフィードバックされる。負入力に与えられる負信号により演算增幅器 201 の出力はハイになる。フリップフロップ 203 の D 入力電圧が閾値より高くなると、次のクロックサイクルで Q バー出力はローになる。このようなプロセスが繰り返される結果、アナログ入力に比例したデューティサイクルを有する出力信号が Q バーから発生する。演算增幅器 201 の出力からフリップフロップ 203 を経由したフィードバックにより、インバータ 205 出力の平均電圧はアナログ入力電圧に比例することになる。したがって、PWM 信号のデューティサイクルはインバータ 205 出力の平均電圧に比例する。

#### 【 0022 】

明らかなように、多くの様々な変更をパルス幅変調器 100 に施すことが可能である。例えば、フリップフロップ 403 の Q バー出力の代わりに Q 出力を演算增幅器 201 にフィードバックすればインバータ 205 の必要性は不要になる。この実施例の場合、利点として構成が簡単になる反面、精度が若干低下する可能性が高い。また、ケースによっては、Q バー出力の代わりに Q 出力を PWM 信号として使用するのが望ましい場合もある。どちらを選択するかは、主として、デューティサイクル機構側で余分の反転が必要になるかどうかに依存する。

#### 【 0023 】

上述したように、パルス幅変調器 200 は、フリップフロップ 203 以外のコンパレータでも実現可能である。例えば、図 3 に示す第 2 のパルス幅変調器 300 では、コンパレータとしてインバータ 301 を使用している。この実施形態は、装置が簡単になる反面、PWM 信号の周波数と繰返し精度を制御するヒステリシスの精度と繰返し精度については概ね劣ることになる。

#### 【 0024 】

図 4 にデューティサイクル機構 400 の概略図を示す。デューティサイクル機構 400 は、図 1 のパルス幅変調 ADC で使用可能な種類の機構の一例である。後で詳述するように、他のデバイス、例えばプログラム FPGA デバイスなどを用いてデューティサイクル機構を実現することができる。デューティサイクル機構 400 はパルス幅変調信号のデューティサイクルを決定し、2 つのデジタル値を出力する。一方のデジタル値は PWM 信号の周期に比例し、他方のデジタル値は PWM 信号がアクティブになる時間に比例する。図示の実施形態において、PWM 信号は論理ローのとき「アクティブ」である。他の実施形態では、PWM 信号は論理ハイのとき「アクティブ」になってよい。2 つのデジタル値の比はアナログ入力信号に比例する。図示の実施形態において、デューティサイクル機構は反転マルチプレクサ (MUX) スイッチ 401、フリップフロップ 403、AND ゲート 405、407、アクティブカウンタ 411、周期カウンタ 413、アクティブラッチ 415、周期ラッチ 417、及び比算出器 419 を備える。

#### 【 0025 】

リセット入力によりデューティサイクル機構は開始時または他の適当なタイミングでリセットされ、PWM からデジタルへの変換の演算結果はその時点でクリアされる。図示の実施形態の場合、リセット入力が論理ローのときデューティサイクル機構はクリアされ、論理ハイのとき PWM からデジタルへの変換が行われる通常状態になる。

#### 【 0026 】

反転マルチプレクサスイッチ 401 により異なる PWM 入力信号をデューティサイクル機構 400 に送り込むことが可能になる。すなわち、単一のデューティサイクル機構 400 は複数のパルス幅変調器からの PWM 入力信号に結合し、受け取る。反転マルチプレクサスイッチ 401 は複数の PWM 入力信号（図 4 に図示せず）のなかから 1 つを選択し、

10

20

30

40

50

それがデューティサイクル機構に渡されてデジタル値に変換される。

#### 【0027】

選択された PWM 入力信号は反転マルチプレクサスイッチ 401 から出力されてフリップフロップ 403 と AND ゲート 407 に送られる。フリップフロップ 403 の Q バー出力は論理ハイ時に周期カウンタ 413 をイネーブルする。AND ゲート 407 は、PWM 入力がローで、周期カウンタ 413 がイネーブルされているときにアクティブカウンタ 411 をイネーブルする。リセット入力あるいはフリップフロップ 403 の Q バー出力がローになると AND ゲート 405 の出力はローになって、アクティブカウンタと周期カウンタの双方がクリアされる。説明の便宜上、カウンタがクリアされている状態から始めると、フリップフロップ 403 の D 入力にフィードバックされる周期カウンタ 413 の出力は論理ローである。フリップフロップ 403 の D 入力が論理ローになると、フリップフロップ 403 に入力される反転 PWM 信号の次の立上りエッジでフリップフロップ 403 の Q バー出力は論理ハイになり、これにより、周期カウンタ 413 は、リセット入力が論理ハイであれば、すなわちリセット状態でなければイネーブルされてカウント動作する。周期カウンタ 413 はクロック入力パルスをカウントし、所定のカウント値に達すると、フリップフロップ 403 の D 入力にフィードバックされる出力が論理ハイに切り替わる。反転 PWM 入力の次の立上りエッジでフリップフロップ 403 の Q バー出力は論理ローに変化して、アクティブカウンタと周期カウンタの双方をディスイネーブルする。同時に、フリップフロップ 403 の Q 出力は論理ハイになって、アクティブラッチ 415 と周期ラッチ 417 の出力をそれぞれの入力の論理値にラッチする。周期カウンタ 413 の出力に続き周期ラッチ 417 の出力は、周期カウンタ 413 のイネーブル期間中に発生したクロック入力パルスの個数になる。フリップフロップ 403 の D 入力へのフィードバックにより、カウント動作は反転 PWM 入力の立上りエッジから開始して、所定の個数のクロック入力パルスのカウント終了後、次の反転 PWM 入力の立上りエッジになるまでカウント動作は継続するので、PWM 信号の全期間についてカウント動作が行われる。アクティブカウンタ 407 の出力に続きアクティブラッチ 415 の出力は、反転 PWM 入力が論理ハイでかつ周期カウンタがイネーブルされている期間中に発生したクロック入力パルスの個数になる。アクティブラッチ 415 の出力と周期ラッチ 417 の出力は比算出器 419 に送られる。比算出器 419 は、アクティブラッチ 415 出力のデジタル値と周期ラッチ 417 出力のデジタル値の比を求める。この比は PWM 入力信号のデューティサイクルであり、アナログ入力信号に比例するものである。また、フリップフロップ 403 の Q バー出力が論理ローになると、AND ゲート 405 出力が論理ローに切り替わり、アクティブカウンタと周期カウンタは共にクリアされる。両カウンタはクリア状態になり、反転マルチプレクサ 401 出力の次の立上りエッジからカウント動作を再開する。

#### 【0028】

クロック入力から、アクティブカウンタ 411 と周期カウンタ 413 のカウントするパルス列が与えられる。すなわち、アクティブカウンタ 411 は PWM 信号がアクティブである期間中に発生したクロックサイクル数をカウントする。同様に、周期カウンタ 413 は PWM 信号の 1 以上の周期で発生したクロックサイクル数をカウントする。カウント結果はアクティブラッチ 415 と周期ラッチ 417 にラッチされる。ラッチ値は除算されて PWM のデューティサイクルが求められ、アナログ入力に比例するデジタル値として出力される。

#### 【0029】

アクティブカウンタ 411 と周期カウンタ 413 は、任意の適当なカウンティングデバイスで実現可能である。例えば、両者はディスクリートなカウンタの列で実現可能である。例えば、直列構成の 4 個の 4 ビットカウンタにより  $2^{15}$  分解能が得られる。アクティブラッチ 415 と周期ラッチ 417 も同様にラッチの列で実現可能である。8 ビットラッチのデバイス 2 個で各カウンタの 16 ビット出力をラッチできる。この実施例において、アクティブカウンタ 411 とアクティブラッチ 415 は PWM 信号のアクティブ期間をカウントし、保持する能力を有する。同様に、周期カウンタ 413 と周期ラッチ 417 は 2

10

20

30

40

50

<sup>1 5</sup> の分解能で P W M 信号の周期をカウントし、保持する能力を有する。このような高分解能の値の比により、正確な P W M のデューティサイクルの決定が与えられる結果、アナログ入力信号に対する正確なアナログデジタル変換が行われることになる。

#### 【 0 0 3 0 】

比算出器 4 1 9 は任意の適当な演算デバイスで実現可能である。例えば、F P G A を用いたハードウェアで実現可能である。あるいは、マイクロプロセッサまたは他の計算装置を含むシステムの一部としてパルス幅変調A D C を使用するような場合、ソフトウェアで比算出を実現可能である。また、アクティブラッチ 4 1 5 出力および周期ラッチ 4 1 7 出力はアナログ入力信号電圧を表すデジタル値としてそれ自体使用可能なので、実施形態によっては、比算出器 4 1 9 は不要になる。10

#### 【 0 0 3 1 】

上述したように、これはデューティサイクル機構を実現するための一実施形態にすぎない。他の実施形態として、標準化デバイス設計技法によるフィールドプログラマブルゲートアレー(F P G A)を使用してデューティサイクル機構を実現することができる。このような実施形態の場合、比算出器 4 1 9 を実現するのに用いた F P G A でデューティサイクル機構の残部を、同時に実現することができる。

#### 【 0 0 3 2 】

このように本発明によれば、アナログ信号を精度良く確実に変換するためにパルス幅変調を使用するアナログデジタル変換方法及び装置が提供される。このアナログデジタル変換方法及び装置は、最も厳しい環境における要求を満たすアナログデジタル変換器(A D C)を実現可能である。さらに、多くの用途で求められる高精度を満たすA D C を実現可能である。20

#### 【 0 0 3 3 】

以上、本発明及びその特定の応用を明らかにするとともに、それによって当業者が本発明を実施できるように実施形態について述べた。しかしながら、当業者には明らかなように、以上の記載及び実施形態は専ら例示を目的として提示されたものである。記載事項は包括的ではなく、本発明は開示した形態そのものに限定されないものである。したがって特許請求の範囲の趣旨から逸脱することなく、開示内容に照らして様々な変形、変更が可能である。

#### 【 図面の簡単な説明 】

#### 【 0 0 3 4 】

【 図 1 】好適な実施形態に基づいたパルス幅変調アナログデジタル変換器の概略図である。

【 図 2 】好適な実施形態に基づいたパルス幅変調器の概略図である。

【 図 3 】第 2 の実施形態に基づいたパルス幅変調器の概略図である。

【 図 4 】デューティサイクル機構の概略図である。

【図】

デジタル出力

パルス幅変調器/ADC

サイクルタイミング

アクチュエータ

カウンタ

周期カウンタ

パルス幅

変調器

100

```

graph TD

ADC[パルス幅変調器/ADC] --> Counter[サイクルタイミング

アクチュエータ

カウンタ]

Counter --> PWM[パルス幅

変調器]

PWM --> ADC

Counter --> DigitalOut[デジタル出力]

DigitalOut --> Timer[周期カウンタ]

Timer --> Counter

```

【図2】

This circuit diagram illustrates a PWM generation and control system. The input signal is fed into an operational amplifier (201) configured as a voltage-controlled voltage source. The output of this stage is connected to one input of a second operational amplifier (202), which also receives feedback from a resistor network (225, 227, 229, 231) and a diode (241-227). The output of 202 is compared against a reference voltage (VREF) from a third operational amplifier (203). The error signal is processed by a fourth operational amplifier (204) along with a feedback signal from a fifth operational amplifier (205). The final output is a PWM signal (PWM出力) and a clock signal (クロック出力).

【図3】

アダクティブ入力

オフセット入力

VREF

205

213

223

225

227

241

291

301

300

PWM出力

【図4】

The diagram illustrates the pulse width modulation (PWM) control mechanism. It features a central D flip-flop (403) with inputs PRE and C. The PRE input is connected to the output of a counter (413) via an inverter (405). The C input is controlled by a logic gate (407) which receives signals from two comparators (419 and 417) and the output of the flip-flop. The Q output of the flip-flop is connected to the clock input of the counter (413) via another inverter (406). The Q-bar output of the flip-flop is connected to the output of a switch (401). The switch (401) has three outputs: one goes to the PWM input, another to the digital output, and the third is labeled 'リセット' (Reset). The PWM input also feeds back into the counter (413). The digital output is labeled 'デジタル出力' (Digital Output).

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |                                                                                    |  |                              | PCT/US 03/31242       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|------------------------------|-----------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 H03M1/00 H03M1/14 H03F3/217 H02M7/5387 H04N9/29<br>G01R21/00 G01R21/127 G05F1/565 H03K7/08 H03M1/16<br>H03M1/40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                              |                                                                                    |  |                              |                       |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                              |                                                                                    |  |                              |                       |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H03M H03F H02M H04N G01R G05F H03K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                              |                                                                                    |  |                              |                       |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                              |                                                                                    |  |                              |                       |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data, PAJ, INSPEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                              |                                                                                    |  |                              |                       |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                              |                                                                                    |  |                              |                       |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages |  |                              | Relevant to claim No. |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 6 445 326 B1 (DONOVAN BRIAN T ET AL)<br>3 September 2002 (2002-09-03)<br>column 1, line 45 -column 3, line 3;<br>figure 3 |                                                                                    |  | 1,17                         |                       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | column 1, line 45 -column 3, line 3;<br>figure 3                                                                             |                                                                                    |  | 2-5,<br>8-13,15,<br>16,18-20 |                       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 4 504 793 A (YOKOYAMA KENJI)<br>12 March 1985 (1985-03-12)<br><br>column 3, line 38 -column 7, line 46;<br>figures 5,6    |                                                                                    |  | 2-5,<br>8-13,15,<br>16,18-20 |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                              |                                                                                    |  | -/-                          |                       |

| <input checked="" type="checkbox"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                              | Further documents are listed in the continuation of box C.                         |  |                              |                       |

| <input checked="" type="checkbox"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                              | Patent family members are listed in annex.                                         |  |                              |                       |

| * Special categories of cited documents :<br>'A' document defining the general state of the art which is not considered to be of particular relevance<br>'E' earlier document but published on or after the international filing date<br>'L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>'O' document referring to an oral disclosure, use, exhibition or other means<br>'P' document published prior to the international filing date but later than the priority date claimed                                                                               |                                                                                                                              |                                                                                    |  |                              |                       |

| 'T' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>'X' document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>'Y' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>'Z' document member of the same patent family |                                                                                                                              |                                                                                    |  |                              |                       |

| Date of the actual completion of the International search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                              | Date of mailing of the International search report                                 |  |                              |                       |

| 27 January 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                              | 05/02/2004                                                                         |  |                              |                       |

| Name and mailing address of the ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                              | Authorized officer                                                                 |  |                              |                       |

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL-2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.<br>Fax: (+31-70) 340-2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                              | Brosa Gonzalez, A                                                                  |  |                              |                       |

## INTERNATIONAL SEARCH REPORT

PCT/US 03/31242

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                      |                       |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category *                                           | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                   | Relevant to claim No. |

| X                                                    | PATENT ABSTRACTS OF JAPAN<br>vol. 007, no. 288 (E-218),<br>22 December 1983 (1983-12-22)<br>& JP 58 165420 A (NIPPON GAKKI SEIZO KK),<br>30 September 1983 (1983-09-30)<br>abstract; figure 3<br>--- | 6,7,14                |

| X                                                    | US 5 355 136 A (KATAGIRI TAKASHI)<br>11 October 1994 (1994-10-11)<br>column 1, line 59 -column 16, line 23<br>---                                                                                    | 1,17                  |

| X                                                    | PATENT ABSTRACTS OF JAPAN<br>vol. 1999, no. 13,<br>30 November 1999 (1999-11-30)<br>& JP 11 237290 A (FUJIKOKI CORP),<br>31 August 1999 (1999-08-31)<br>abstract<br>---                              | 1,17                  |

| A                                                    | EP 0 817 506 A (THOMSON CONSUMER<br>ELECTRONICS) 7 January 1998 (1998-01-07)<br>* the whole document *<br>---                                                                                        | 1-20                  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

PCT/US 03/31242

| Patent document cited in search report |    | Publication date |                      | Patent family member(s)                               | Publication date                                     |

|----------------------------------------|----|------------------|----------------------|-------------------------------------------------------|------------------------------------------------------|

| US 6445326                             | B1 | 03-09-2002       | AU<br>EP<br>WO       | 7138801 A<br>1314253 A1<br>0199283 A1                 | 02-01-2002<br>28-05-2003<br>27-12-2001               |

| US 4504793                             | A  | 12-03-1985       | JP                   | 1654156 C<br>3020090 B<br>5B130617 A                  | 13-04-1992<br>18-03-1991<br>04-08-1983               |

| JP 58165420                            | A  | 30-09-1983       |                      | NONE                                                  |                                                      |

| US 5355136                             | A  | 11-10-1994       | JP<br>JP<br>JP<br>DE | 5039038 U<br>5122968 A<br>5167450 A<br>4241702 A1     | 25-05-1993<br>18-05-1993<br>02-07-1993<br>01-07-1993 |

| JP 11237290                            | A  | 31-08-1999       |                      | NONE                                                  |                                                      |

| EP 0817506                             | A  | 07-01-1998       | US<br>CN<br>EP<br>JP | 5739638 A<br>1171701 A ,B<br>0817506 A2<br>10117360 A | 14-04-1998<br>28-01-1998<br>07-01-1998<br>06-05-1998 |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA, GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ, EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,M W,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100107696

弁理士 西山 文俊

(72)発明者 オット, ウィリアム・イー

アメリカ合衆国アリゾナ州85023, フェニックス, ノース・セブンス・アベニュー 1580

9

F ターム(参考) 5J001 BB05 BB14 BB21 DD09

5J022 AA07 AA11 BA01 CA04 CB01 CB04 CE02 CE05 CE08 CF01

CF02 CF03 CF08 CG01