(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5777302号

(P5777302)

(45) 発行日 平成27年9月9日(2015.9.9)

(24) 登録日 平成27年7月17日(2015.7.17)

(51) Int.Cl.

F 1

|             |             |                  |

|-------------|-------------|------------------|

| <b>H01G</b> | <b>4/12</b> | <b>(2006.01)</b> |

| <b>H01G</b> | <b>4/30</b> | <b>(2006.01)</b> |

| <b>H05K</b> | <b>3/46</b> | <b>(2006.01)</b> |

|        |      |         |

|--------|------|---------|

| HO 1 G | 4/12 | 3 6 4   |

| HO 1 G | 4/12 | 3 4 9   |

| HO 1 G | 4/30 | 3 0 1 F |

| HO 5 K | 3/46 | H       |

請求項の数 6 (全 17 頁)

(21) 出願番号

特願2010-164112 (P2010-164112)

(22) 出願日

平成22年7月21日 (2010.7.21)

(65) 公開番号

特開2012-28456 (P2012-28456A)

(43) 公開日

平成24年2月9日 (2012.2.9)

審査請求日

平成25年5月17日 (2013.5.17)

審判番号

不服2014-15368 (P2014-15368/J1)

審判請求日

平成26年8月5日 (2014.8.5)

(73) 特許権者 000006231

株式会社村田製作所

京都府長岡京市東神足1丁目10番1号

(74) 代理人 110001232

特許業務法人 宮▲崎▼・目次特許事務所

(72) 発明者 佐藤 浩司

京都府長岡京市東神足1丁目10番1号

株式会社村田製作所内

(72) 発明者 真田 幸雄

京都府長岡京市東神足1丁目10番1号

株式会社村田製作所内

(72) 発明者 西坂 康弘

京都府長岡京市東神足1丁目10番1号

株式会社村田製作所内

最終頁に続く

(54) 【発明の名称】セラミック電子部品の製造方法、セラミック電子部品及び配線基板

## (57) 【特許請求の範囲】

## 【請求項 1】

長さ方向及び幅方向に沿って延びており、互いに対向する第1及び第2の主面と、長さ方向及び厚み方向に沿って延びており、互いに対向する第1及び第2の側面と、幅方向及び厚み方向に沿って延びておあり、互いに対向する第1及び第2の端面とを有し、長さ寸法をL、幅寸法をW、厚み寸法をTとしたときに、 $T < W < L$ 、 $1 / 5 W \leq T \leq 1 / 2 W$ 、 $T = 0.3 \text{ mm}$ を満たす直方体状のセラミック素体と、

前記セラミック素体の内部において、少なくとも一部同士が厚み方向に対向するように形成されている第1及び第2の内部電極と、

前記第1の主面上の長さ方向の一方側端部に形成されており、前記第1の内部電極に電気的に接続されている第1の外部電極と、 10

前記第1の主面上の長さ方向の他方側端部に形成されており、前記第2の内部電極に電気的に接続されている第2の外部電極と、

前記第1の主面上の長さ方向の他方側端部に形成されており、前記第2の内部電極に電気的に接続されている第2の外部電極と、

を備えるセラミックコンデンサの製造方法であって、

重合度が1000～1500である有機バインダーを含むセラミックグリーンシートを用意する工程と、

前記セラミックグリーンシートの表面に、導電性ペーストを塗布することにより、前記第1または第2の内部電極形成用の第1の導電性ペースト層を形成する工程と、

前記セラミックグリーンシートを積層することにより、内部に前記第1の導電性ペースト層が形成されている生のセラミック積層体を形成する工程と、

前記生のセラミック積層体の表面に、導電性ペーストを塗布することにより前記第1及び第2の外部電極形成用の第2の導電性ペースト層を形成する工程と、

前記第2の導電性ペースト層が形成された前記生のセラミック積層体を焼成する工程と、

前記第2の導電性ペースト層が形成された前記生のセラミック積層体を、前記焼成の前にプレスするプレス工程と、

を備え、

前記プレス工程において、厚みが $0.05 \sim 0.15\text{ mm}$ の弾性体を介して、前記生のセラミック積層体を厚み方向にプレスする、セラミックコンデンサの製造方法。

#### 【請求項2】

10

前記焼成された第2の導電性ペースト層の上に、Cuめっきを施す工程をさらに備える、請求項1に記載のセラミックコンデンサの製造方法。

#### 【請求項3】

前記有機バインダーとして、重合度が $1000 \sim 1500$ のポリビニルブチラールを用いる、請求項1または2に記載のセラミックコンデンサの製造方法。

#### 【請求項4】

長さ方向及び幅方向に沿って延びてあり、互いに対向する第1及び第2の主面と、長さ方向及び厚み方向に沿って延びてあり、互いに対向する第1及び第2の側面と、幅方向及び厚み方向に沿って延びてあり、互いに対向する第1及び第2の端面とを有し、長さ寸法をL、幅寸法をW、厚み寸法をTとしたときに、 $T < W < L$ 、 $1/5W \leq T \leq 1/2W$ 、 $T = 0.3\text{ mm}$ を満たす直方体状のセラミック素体と、

20

前記セラミック素体の内部において、少なくとも一部同士が厚み方向に対向するように形成されている第1及び第2の内部電極と、

前記第1の主面上の長さ方向の一方側端部に形成されており、前記第1の内部電極に電気的に接続されている第1の外部電極と、

前記第1の主面上の長さ方向の他方側端部に形成されており、前記第2の内部電極に電気的に接続されている第2の外部電極と、

を備えるセラミックコンデンサであって、

前記第1の主面上の長さ方向の一方側端部に形成されており、前記第2の内部電極に電気的に接続されている第2の外部電極と、

を通過する平面と、前記第1の主面上のうちの前記平面と最も離れた部分との間の距離が $4.9\mu\text{m}$ 以下であり、かつ $0\mu\text{m}$ よりも大きく、

30

前記第1及び第2の外部電極のそれぞれの表面の表面粗さ(Ra)が $1.55\mu\text{m}$ 以下である、セラミックコンデンサ。

#### 【請求項5】

請求項4に記載のセラミックコンデンサと、

前記セラミックコンデンサが埋め込まれている配線基板本体と、

を備える、配線基板。

#### 【請求項6】

前記配線基板本体には、前記セラミックコンデンサの前記第1、第2の外部電極に向かって開口する貫通孔が形成されている、請求項5に記載の配線基板。

40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、セラミック電子部品の製造方法、セラミック電子部品及び配線基板に関する。特に、本発明は、配線基板に埋め込まれて好適に使用されるセラミック電子部品の製造方法、セラミック電子部品及びそれが埋め込まれたセラミック電子部品埋め込み型配線基板に関する。

##### 【背景技術】

##### 【0002】

50

近年、携帯電話機や携帯音楽プレイヤーなどの電子機器の小型化や薄型化に伴い、電子機器に搭載される配線基板の小型化が進んでいる。

### 【0003】

配線基板を小型化する方法としては、例えば、下記の特許文献1において、チップコンデンサを配線基板の内部に埋め込み、配線基板のチップコンデンサの上に位置する部分にレーザーにより貫通孔を形成し、貫通孔内部にめっきを施すことにより、チップコンデンサへの配線を構成する方法が提案されている。この方法によれば、配線基板の表面における部品の実装面積を小さくすることが可能となり、配線基板を小型化することができる。

### 【先行技術文献】

#### 【特許文献】

10

#### 【0004】

#### 【特許文献1】特開2001-352141号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、特許文献1に記載の方法でチップコンデンサを配線基板内に埋め込んだ場合に、チップコンデンサが埋め込まれた配線基板の特性がばらつく場合があるという問題がある。

#### 【0006】

本発明は、係る点に鑑みてなされたものであり、その目的は、配線基板に埋め込まれて使用された際にも特性のばらつきが少ないセラミック電子部品の製造方法を提供することにある。

20

#### 【課題を解決するための手段】

#### 【0007】

本発明に係るセラミックコンデンサの製造方法は、長さ方向及び幅方向に沿って延びており、互いに対向する第1及び第2の正面と、長さ方向及び厚み方向に沿って延びておらず、互いに対向する第1及び第2の側面と、幅方向及び厚み方向に沿って延びており、互いに対向する第1及び第2の端面とを有し、長さ寸法をL、幅寸法をW、厚み寸法をTとしたときに、 $T < W < L$ 、 $1 / 5 W \leq T \leq 1 / 2 W$ 、 $T = 0.3 \text{ mm}$ を満たす直方体状のセラミック素体と、セラミック素体の内部において、少なくとも一部同士が厚み方向に対向するように形成されている第1及び第2の内部電極と、第1の正面の長さ方向の一方側端部に形成されており、第1の内部電極に電気的に接続されている第1の外部電極と、第1の正面の長さ方向の他方側端部に形成されており、第2の内部電極に電気的に接続されている第2の外部電極とを備えるセラミックコンデンサの製造方法に関する。本発明に係るセラミックコンデンサの製造方法では、重合度が1000～1500である有機バインダーを含むセラミックグリーンシートを用意する。セラミックグリーンシートの表面に、導電性ペーストを塗布することにより、第1または第2の内部電極形成用の第1の導電性ペースト層を形成する。セラミックグリーンシートを積層することにより、内部に第1の導電性ペースト層が形成されている生のセラミック積層体を形成する。生のセラミック積層体の表面に、導電性ペーストを塗布することにより第1及び第2の外部電極形成用の第2の導電性ペースト層を形成する。第2の導電性ペースト層が形成された生のセラミック積層体を焼成する。生のセラミック積層体を、焼成の前にプレスする工程をさらに備えている。プレス工程において、厚みが0.05～0.15mmの弾性体を介して、生のセラミック積層体を厚み方向にプレスする。この場合、第1及び第2の外部電極の表面粗さを小さくできる。従って、第1及び第2の外部電極にレーザー光を照射したときの、レーザー光の第1及び第2の外部電極表面における乱反射を抑制することができる。

30

#### 【0009】

本発明に係るセラミックコンデンサの製造方法の他の特定の局面では、セラミックコンデンサの製造方法は、焼成された第2の導電性ペースト層の上に、Cuめっきを施す工程をさらに備えている。この場合、第1及び第2の外部電極のレーザー光に対する反射率を

40

50

高くすることができる。

**【0010】**

本発明に係るセラミックコンデンサの製造方法の別の特定の局面では、有機バインダーとして、重合度が1000～1500のポリビニルブチラールを用いる。

**【0011】**

本発明に係るセラミックコンデンサは、直方体状のセラミック素体と、第1及び第2の内部電極と、第1の外部電極と、第2の外部電極とを備えている。セラミック素体は、第1及び第2の正面と、第1及び第2の側面と、第1及び第2の端面とを有する。第1及び第2の正面は、長さ方向及び幅方向に沿って延びている。第1及び第2の正面は、互いに對向している。第1及び第2の側面は、長さ方向及び厚み方向に沿って延びている。第1及び第2の側面は、互いに對向している。第1及び第2の端面は、幅方向及び厚み方向に沿って延びている。第1及び第2の端面は、互いに對向している。セラミック素体は、長さ寸法をL、幅寸法をW、厚み寸法をTとしたときに、 $T < W < L$ 、 $1 / 5 W \leq T \leq 1 / 2 W$ 、 $T \geq 0.3\text{ mm}$ を満たす。第1及び第2の内部電極は、セラミック素体の内部において、少なくとも一部同士が厚み方向に對向するように形成されている。第1の外部電極は、第1の正面の長さ方向の一方側端部に形成されている。第1の外部電極は、第1の内部電極に電気的に接続されている。第2の外部電極は、第1の正面の長さ方向の他方側端部に形成されている。第2の外部電極は、第2の内部電極に電気的に接続されている。第1の正面の第1の外部電極の長さ方向の一方側の端部が位置している部分と、第1の正面の第2の外部電極の長さ方向の他方側の端部が位置している部分とを通過する平面と、第1の正面のうちの平面と最も離れた部分との間の距離が $4.9\text{ }\mu\text{m}$ 以下であり、かつ $0\text{ }\mu\text{m}$ よりも大きい。第1及び第2の外部電極のそれぞれの表面の表面粗さ(Ra)が $1.55\text{ }\mu\text{m}$ 以下である。この構成によれば、第1及び第2の外部電極の表面粗さを小さくできる。従って、第1及び第2の外部電極にレーザー光を照射したときの、レーザー光の第1及び第2の外部電極表面における乱反射を抑制することができる。

**【0013】**

なお、本発明において、表面粗さ(Ra)とは、JIS B 0601-1994で規定される算術平均粗さRaのことである。

**【0014】**

本発明に係る配線基板は、上記本発明に係るセラミックコンデンサと、セラミックコンデンサが埋め込まれている配線基板本体とを備えている。

**【0015】**

本発明に係る配線基板のある特定の局面では、配線基板本体には、セラミックコンデンサの第1、第2の外部電極に向かって開口する貫通孔が形成されている。

**【発明の効果】**

**【0016】**

本発明によれば、配線基板に埋め込まれて使用された際にも特性のはらつきが少ないセラミック電子部品の製造方法及びセラミック電子部品を提供することができる。

**【図面の簡単な説明】**

**【0017】**

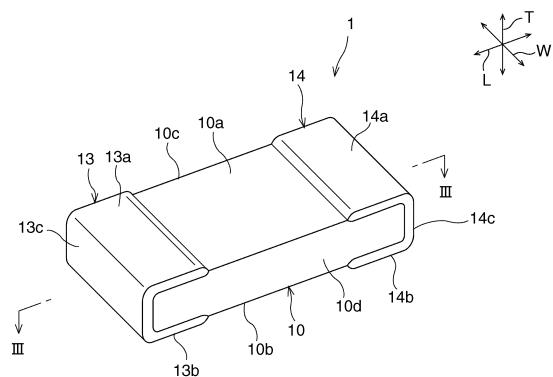

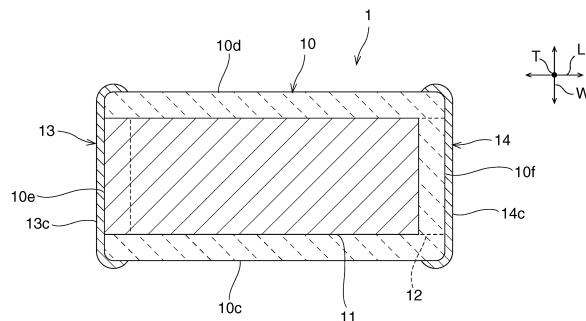

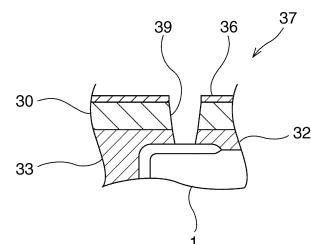

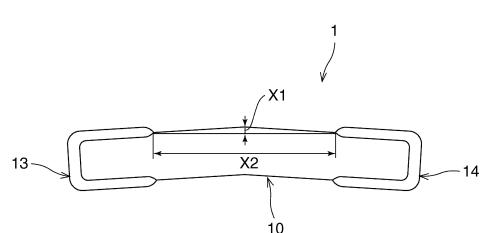

【図1】第1の実施形態に係るセラミック電子部品の略図的斜視図である。

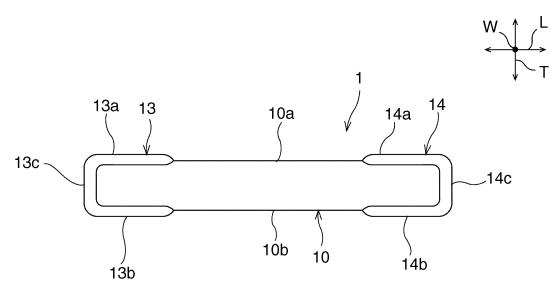

【図2】第1の実施形態に係るセラミック電子部品の略図的側面図である。

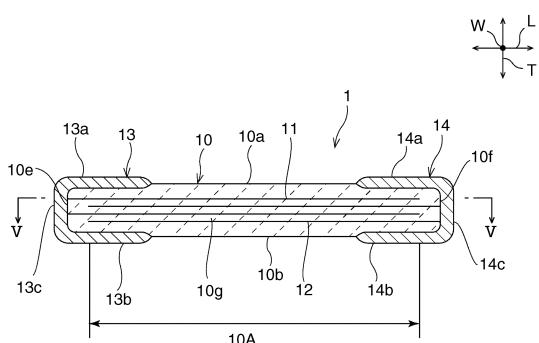

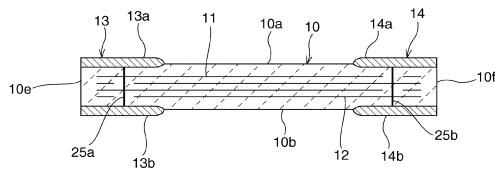

【図3】図1の線I—I-I-Iにおける略図的断面図である。

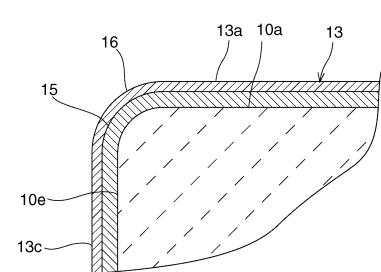

【図4】第1の実施形態に係るセラミック電子部品の一部分を拡大した略図的断面図である。

【図5】図3の線V—Vにおける略図的断面図である。

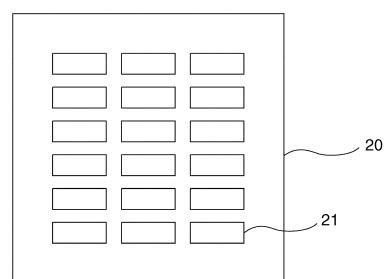

【図6】導電パターンが形成されたセラミックグリーンシートの略図的平面図である。

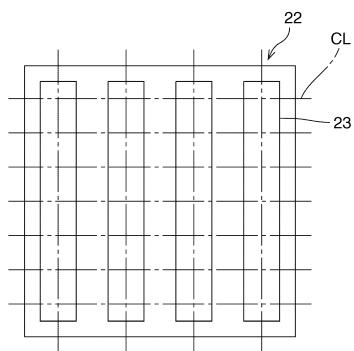

【図7】マザー積層体の略図的平面図である。

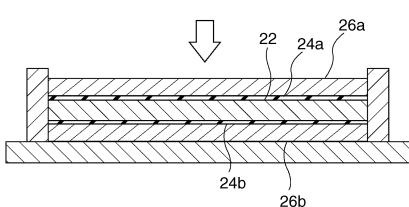

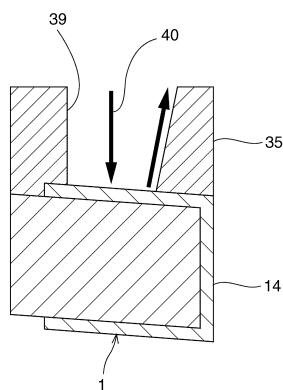

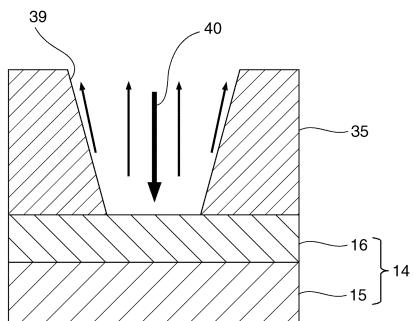

【図8】マザー積層体のプレス工程を説明するための略図的断面図である。

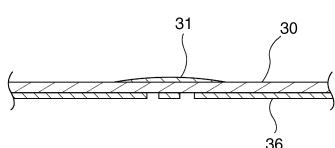

【図9】ベース基板に接着剤を塗布する工程を説明するための略図的断面図である。

10

20

30

40

50

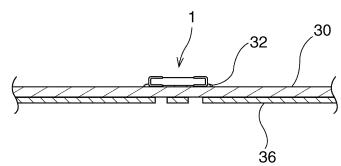

【図10】セラミック電子部品をベース基板に接着する工程を説明するための略図的断面図である。

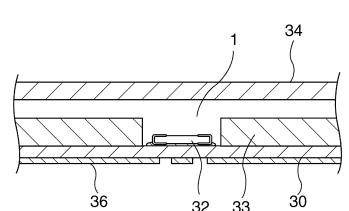

【図11】配線基板本体を形成する工程を説明するための略図的断面図である。

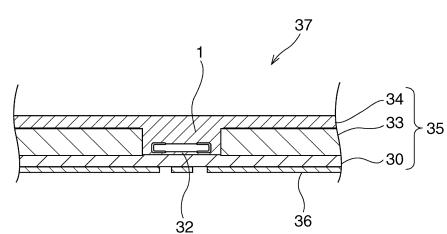

【図12】ピアホールを形成する工程を説明するための略図的断面図である。

【図13】配線基板の一部分の略図的拡大断面図である。

【図14】セラミック電子部品の反り量を説明するための模式図である。

【図15】セラミック素体が沿っている場合に、レーザー光によりピアホールを形成する工程を説明するための模式図である。

【図16】外部電極の表面の表面粗さが大きい場合に、レーザー光によりピアホールを形成する工程を説明するための模式図である。

【図17】第2の実施形態に係るセラミック電子部品の略図的断面図である。

【発明を実施するための形態】

【0018】

(第1の実施形態)

以下、本発明の好ましい実施形態について、図1に示すセラミック電子部品1を例に挙げて説明する。但し、セラミック電子部品1は、単なる例示である。本発明は、以下に示すセラミック電子部品1及びその製造方法に何ら限定されない。

【0019】

図1は、第1の実施形態に係るセラミック電子部品の略図的斜視図である。図2は、第1の実施形態に係るセラミック電子部品の略図的側面図である。図3は、図1の線I—I-I—Iにおける略図的断面図である。図4は、第1の実施形態に係るセラミック電子部品の一部分を拡大した略図的断面図である。図5は、図3の線V—Vにおける略図的断面図である。

【0020】

まず、図1～図5を参照しながら、セラミック電子部品1の構成について説明する。

【0021】

図1～図3に示すように、セラミック電子部品1は、セラミック素体10を備えている。セラミック素体10は、セラミック電子部品1の機能に応じた適宜のセラミック材料からなる。具体的には、セラミック電子部品1がコンデンサである場合は、セラミック素体10を誘電体セラミック材料により形成することができる。誘電体セラミック材料の具体例としては、例えば、BaTiO<sub>3</sub>、CaTiO<sub>3</sub>、SrTiO<sub>3</sub>、CaZrO<sub>3</sub>などが挙げられる。なお、セラミック素体10には、所望するセラミック電子部品1の特性に応じて、上記セラミック材料を主成分として、例えば、Mn化合物、Mg化合物、Si化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物、希土類化合物などの副成分を適宜添加してもよい。

【0022】

セラミック電子部品1がセラミック圧電素子である場合は、セラミック素体10を圧電セラミック材料により形成することができる。圧電セラミック材料の具体例としては、例えば、PZT(チタン酸ジルコン酸鉛)系セラミック材料などが挙げられる。

【0023】

セラミック電子部品1がサーミスタ素子である場合は、セラミック素体10を半導体セラミック材料により形成することができる。半導体セラミック材料の具体例としては、例えば、スピネル系セラミック材料などが挙げられる。

【0024】

セラミック電子部品1が、インダクタ素子である場合は、セラミック素体10を磁性体セラミック材料により形成することができる。磁性体セラミック材料の具体例としては、例えば、フェライトセラミック材料などが挙げられる。

【0025】

セラミック素体10は、直方体状に形成されている。図1～図3に示すように、セラミック素体10は、第1及び第2の正面10a、10bと、第1及び第2の側面10c、1

10

20

30

40

50

0 d と、第 1 及び第 2 の端面 10 e、10 f を有する。図 1 ~ 図 3 に示すように、第 1 及び第 2 の主面 10 a、10 b は、長さ方向 L 及び幅方向 W に沿って延びている。第 1 及び第 2 の主面 10 a、10 b は、互いに対向している。図 1 及び図 5 に示すように、第 1 及び第 2 の側面 10 c、10 d は、厚み方向 T 及び長さ方向 L に沿って延びている。第 1 及び第 2 の側面 10 c、10 d は、互いに対向している。図 3 及び図 5 に示すように、第 1 及び第 2 の端面 10 e、10 f は、厚み方向 T 及び幅方向 W に沿って延びている。第 1 及び第 2 の端面 10 e、10 f は、互いに対向している。

#### 【 0 0 2 6 】

なお、本明細書において、「直方体状」には、角部や稜線部が面取り状または R 面取り状である直方体が含まれるものとする。すなわち、「直方体状」の部材とは、第 1 及び第 2 の主面、第 1 及び第 2 の側面並びに第 1 及び第 2 の端面とを有する部材全般を意味する。また、主面、側面、端面の一部または全部に凹凸などが形成されていてもよい。すなわち、主面、側面及び端面のそれぞれが平坦である必要は必ずしもない。10

#### 【 0 0 2 7 】

セラミック素体 10 の寸法は、特に限定されないが、セラミック素体 10 の厚み寸法を H、長さ寸法を L、幅寸法を W としたときに、セラミック素体 10 は、 $T \leq W < L$ 、 $1 / 5 W \leq T \leq 1 / 2 W$ 、 $T \geq 0.3 \text{ mm}$  を満たす薄型のものであることが好ましい。具体的には、 $0.1 \text{ mm} \leq T \leq 0.3 \text{ mm}$ 、 $0.4 \text{ mm} \leq L \leq 1 \text{ mm}$ 、 $0.2 \text{ mm} \leq W \leq 0.5 \text{ mm}$  であることが好ましい。20

#### 【 0 0 2 8 】

セラミック層 10 g (図 3 を参照) の厚さは、特に限定されない。セラミック層 10 g の厚さは、例えば、 $0.5 \mu\text{m} \sim 10 \mu\text{m}$  程度とすることができます。20

#### 【 0 0 2 9 】

図 3 に示すように、セラミック素体 10 の内部には、略矩形状の複数の第 1 及び第 2 の内部電極 11, 12 が厚み方向 T に沿って等間隔に交互に配置されている。第 1 及び第 2 の内部電極 11, 12 のそれぞれは、第 1 及び第 2 の主面 10 a、10 b と平行である。20

#### 【 0 0 3 0 】

図 3 に示すように、第 1 の内部電極 11 は、長さ方向 L 及び幅方向 W に沿って延びるようにならって形成されている。第 1 の内部電極 11 は、セラミック素体 10 の第 1 の端面 10 e に露出しており、第 1 の端面 10 e から第 2 の端面 10 f 側に向かって延びている。第 1 の内部電極 11 は、第 2 の端面 10 f、第 1 及び第 2 の側面 10 c、10 d のそれぞれには至っていない。一方、第 2 の内部電極 12 も、長さ方向 L 及び幅方向 W に沿って延びるようにならって形成されている。第 2 の内部電極 12 は、図 3 に示すように、セラミック素体 10 の第 2 の端面 10 f に露出しており、第 2 の端面 10 f から第 1 の端面 10 e 側に向かって延びている。第 2 の内部電極 12 は、第 1 の端面 10 e、第 1 及び第 2 の側面 10 c、10 d のそれぞれには至っていない。第 1 及び第 2 の内部電極 11, 12 は、幅方向 W において同じ位置に形成されている。このため、第 1 の内部電極 11 と第 2 の内部電極 12 とは、セラミック素体 10 の長さ方向 L における中央部において、セラミック層 10 g を介して、互いに対向している。第 1 の内部電極 11 と第 2 の内部電極 12 とは、セラミック素体 10 の長さ方向 L における両端部においては、厚み方向 T に対向していない。40

#### 【 0 0 3 1 】

セラミック素体 10 のうち、第 1 及び第 2 の内部電極 11, 12 が互いに対向している部分が、コンデンサとしての機能を発現している有効部 10 A を構成している。

#### 【 0 0 3 2 】

なお、第 1 及び第 2 の内部電極 11, 12 の材質は、特に限定されない。第 1 及び第 2 の内部電極 11, 12 は、例えば、Ni、Cu, Ag, Pd, Au などの金属や、Ag-Pd 合金などの、これらの金属の一種以上を含む合金により形成することができる。

#### 【 0 0 3 3 】

第 1 及び第 2 の内部電極 11, 12 の厚さも、特に限定されない。第 1 及び第 2 の内部電極 11, 12 の厚さは、例えば、 $0.3 \mu\text{m} \sim 2 \mu\text{m}$  程度とすることができます。50

## 【0034】

図1～図3に示すように、セラミック素体10の表面の上には、第1及び第2の外部電極13, 14が形成されている。第1の外部電極13は、第1の内部電極11に電気的に接続されている。第1の外部電極13は、第1の正面10aの長さ方向Lの一方側端部の上に形成されている第1の部分13aと、第2の正面10bの上に形成されている第2の部分13bと、第1の端面10eの上に形成されている第3の部分13cとを備えている。本実施形態では、第1の外部電極13は、第1及び第2の側面10c、10dの端部に浅く回り込むように形成されている。具体的には、第1の外部電極13の第1及び第2の側面10c、10dにおける長さ方向Lに沿った長さは、第1の部分13aの長さ方向Lに沿った長さの半分よりも短い。そして、第1の外部電極13は、幅方向Wに沿って第1及び第2の側面10c、10dからほとんど突出していない。このようにすることで、セラミック電子部品1の幅方向W寸法を小さくすることができる。なお、第1の外部電極13は、第1及び第2の側面10c、10dに実質的に形成されないようにしてもよい。

## 【0035】

一方、第2の外部電極14は、第2の内部電極12に電気的に接続されている。第2の外部電極14は、第1の正面10aの長さ方向Lの他方側端部の上に形成されている第1の部分14aと、第2の正面10bの上に形成されている第2の部分14bと、第2の端面10fの上に形成されている第3の部分14cとを備えている。本実施形態では、第2の外部電極14は、第1及び第2の側面10c、10dの長さ方向Lの端部に浅く回り込むように形成されている。具体的には、第2の外部電極14の第1及び第2の側面10c、10dにおける長さ方向Lに沿った長さは、第1の部分14aの長さ方向Lに沿った長さの半分よりも短い。そして、第2の外部電極14は、幅方向Wに沿って第1及び第2の側面10c、10dからほとんど突出していない。このようにすることで、セラミック電子部品1の幅方向W寸法を小さくすることができる。なお、第2の外部電極14は、第1及び第2の側面10c、10dに実質的に形成されないようにしてもよい。

## 【0036】

本実施形態では、第1及び第2の外部電極13, 14の第1及び第2の部分13a、13b、14a、14bの一部は、有効部10Aと厚み方向Tに対向している。

## 【0037】

次に、図4を参照しながら、本実施形態における第1及び第2の外部電極13, 14の具体的構成について説明する。第1及び第2の外部電極13, 14は、第1及び第2の導電層15, 16の積層体により構成されている。第1の導電層15は、セラミック素体10の上に形成されている。第2の導電層16は、第1の導電層15の一部分の上に形成されている。このため、本実施形態では、第2の導電層16が第1及び第2の外部電極13, 14の最外層を構成している。

## 【0038】

第1の導電層15は、適宜の導電材料により形成することができる。第1の導電層15は、例えば、Ni、Cu, Ag, Pd, Auなどの金属や、Ag-Pd合金などの、これらの金属の一種以上を含む合金により形成することができる。第1の導電層15の厚みは、例えば、3μm～20μm程度とすることができる。

## 【0039】

第1の導電層15は、無機結合材を含んでいる。無機結合材は、セラミック素体10に対する密着強度を高めるための成分である。第1の導電層15がコファイアにより形成される場合は、無機結合材は、共材とも呼ばれ、例えば、セラミック素体10に含まれるセラミック材料と同種のセラミック材料であってもよい。無機結合材は、例えば、セラミック素体10に含まれるセラミック材料と主成分が同じセラミック材料であってもよい。また、第1の導電層15がポストファイアにより形成される場合は、無機結合材は、例えば、ガラス成分であってもよい。

## 【0040】

第1の導電層15における無機結合材の含有量は、例えば、40体積%～60体積%の

範囲内であることが好ましい。

**【0041】**

第2の導電層16は、例えば、Cu、Ni、Sn、Pb、Au、Ag、Pd、Al、BiおよびZnからなる群から選ばれる1種の金属または当該金属を含む合金を用いることが好ましい。

**【0042】**

なかでも、セラミック電子部品1を配線基板に埋め込む場合、めっき層の最外層を構成する金属としては、Cu、Au、Ag、およびAlからなる群から選ばれる1種の金属または当該金属を含む合金を用いることが好ましい。埋め込みの際には、第1及び第2の外部電極13、14を狙って、配線基板を貫通するレーザー光を照射することがあり、これらの金属はレーザー光を効率よく反射するためである。10

**【0043】**

第2の導電層16は、めっき膜により構成されていることが好ましく、厚みは、 $1 \mu m$  ~  $15 \mu m$ 程度であることが好ましい。

**【0044】**

また、第2の導電層16は、第1の導電層15を完全に被覆するように形成されていることが好ましい。

**【0045】**

更に、第2の導電層16と第1の導電層15との間に、例えば樹脂層などのさらなる導電層が設けられていてもよい。20

**【0046】**

なお、本実施形態では、第1及び第2の外部電極13、14の第1及び第2の部分13a、13b、14a、14bのそれぞれの一部は、第1及び第2の主面10a、10bのそれに埋め込まれている。このため、第1及び第2の主面10a、10bのそれぞれのうち、第1及び第2の部分13a、13b、14a、14bが上に位置している部分は、第1及び第2の部分13a、13b、14a、14bが上に位置していない部分よりも厚み方向において中央寄りに位置している。

**【0047】**

第1及び第2の外部電極13、14の第1及び第2の部分13a、13b、14a、14bのそれぞれの厚みを $t_0$ とし、第1及び第2の外部電極13、14の第1及び第2の部分13a、13b、14a、14bが、セラミック素体10に埋め込まれている部分の厚みを $t_1$ とすると、本実施形態では、 $t_1$ と $t_0$ とは、 $1 / 10 t_0 < t_1 < 2 / 5 \cdot t_0$ を満たしている。このため、セラミック電子部品の薄型化と高い信頼性との両立が図られている。30

**【0048】**

$t_1$ が $1 / 10 t_0$ 未満であると、第1及び第2の外部電極13、14の第1及び第2の部分13a、13b、14a、14bとセラミック素体10との密着性が低くなりすぎ、第1及び第2の部分13a、13b、14a、14bの剥離が生じやすくなり、信頼性が低くなる場合がある。また、 $t_1$ が $1 / 10 t_0$ 未満であると、第1及び第2の外部電極13、14の第1及び第2の部分13a、13b、14a、14bの埋め込まれていない部分の厚み $t_2$ が大きくなりすぎ、セラミック電子部品の薄型化を十分に図れない場合がある。40

**【0049】**

一方、 $t_1$ が $2 / 5 \cdot t_0$ よりも大きい場合は、セラミック電子部品の信頼性が低下してしまう場合がある。これは、第1及び第2の部分13a、13b、14a、14bがセラミック素体10に埋め込まれる際に第1及び第2の内部電極11、12に大きな応力が付与され、第1及び第2の内部電極11、12が損傷してしまい、所望の容量が得られなかったり、短絡が生じてしまったりする場合があるためであると考えられる。

**【0050】**

なお、本実施形態において、 $t_0$ は、例えば、 $10 \mu m$  ~  $50 \mu m$ 程度とすることがで50

きる。

#### 【0051】

次に、図6～図8を主として参照しながら、本実施形態のセラミック電子部品1の製造方法の一例について説明する。

#### 【0052】

まず、セラミック素体10を構成するためのセラミック材料と、有機バインダーとを含むセラミックグリーンシート20(図6を参照)を用意する。ここで、本実施形態では、有機バインダーの重合度は、1000～1500の範囲内とされている。好ましく用いられる有機バインダーの具体例としては、例えば、重合度が1000～1500の範囲内であるポリビニルブチラール(PVB)などが挙げられる。

10

#### 【0053】

次に、図6に示すように、そのセラミックグリーンシート20の上に、導電性ペーストを塗布することにより、第1または第2の内部電極11, 12形成用の第1の導電性ペースト層21を形成する。なお、導電パターンの塗布は、例えば、スクリーン印刷法などの各種印刷法により行うことができる。導電性ペーストは、導電性微粒子の他に、公知のバインダーや溶剤を含んでいてもよい。

#### 【0054】

次に、第1の導電性ペースト層21が形成されていないセラミックグリーンシート20と、第1の導電性ペースト層21が形成されているセラミックグリーンシート20とを長さ方向Lに沿って適宜ずらしながら積層し、静水圧プレスなどの手段で積層方向にプレスすることにより、図7に示すマザー積層体22を作製する。

20

#### 【0055】

次に、図7に示すように、マザー積層体22の上に、スクリーン印刷法などの適宜の印刷法により導電性ペーストを塗布することにより、第1及び第2の外部電極13, 14の第1の導電層15の第1及び第3の部分13a, 13bを構成している部分に対応した形状の第2の導電性ペースト層23を形成する。

#### 【0056】

次に、マザー積層体22を再び積層方向(厚み方向)にプレスする。このプレス工程によって、第2の導電性ペースト層23の一部が埋め込まれる。第2の導電性ペースト層23の埋め込み量は、例えば、プレス量、プレス圧や、プレス時にマザー積層体22に接触する部材の硬度や弾性率を調整することによって行うことができる。

30

#### 【0057】

具体的には、例えば、対向する金型とマザー積層体22の両主面の間に、ゴムなどの弾性体を介在させないでマザー積層体22をプレスした場合には、第2の導電性ペースト層23の埋め込み量が大きくなる。それに対して、図8に示すように、対向する金型26a、26bとマザー積層体22の両主面との間にゴムなどの弾性体24a、24bを接触させた状態でプレスを行った場合は、埋め込み量が相対的に小さくなる。そして、弾性体24a、24bの弾性率などを調整することによって埋め込み量を調整することができる。

#### 【0058】

また、このプレス工程によって、第2の導電性ペースト層23の表面の表面粗さを小さくすることができる。従って、第1及び第2の外部電極13, 14の表面の表面粗さを小さくすることができる。

40

#### 【0059】

次に、図7に示す仮想のカットラインCLに沿ってマザー積層体22をカッティングすることにより、マザー積層体22から複数の生のセラミック積層体を作製する。なお、マザー積層体22のカッティングは、ダイシングや押切により行うことができる。

#### 【0060】

生のセラミック積層体作成後、バレル研磨などにより、生のセラミック積層体の稜線部及び稜線部の面取りまたはR面取り及び表層の研磨を行うようにしてもよい。

#### 【0061】

50

その後、生のセラミック積層体の両端面に、例えば、ディップ法などにより、導電性ペーストを塗布する。これにより、セラミック積層体の両端面にも導電性ペースト層を形成する。

#### 【0062】

次に、生のセラミック積層体の焼成を行う。この焼成工程において、上記形成の導電性ペースト層が同時焼成される（コファイア）。なお、焼成温度は、使用するセラミック材料や導電性ペーストの種類により適宜設定することができる。焼成温度は、例えば、900 ~ 1300 程度とすることができる。

#### 【0063】

その後、必要に応じて、バレル研磨などの研磨を行う。

10

#### 【0064】

同時焼成された導電性ペースト層の上に、例えば、Cuめっきなどのめっきを施すことにより第2の導電層16を形成し、第1及び第2の外部電極13, 14を完成させる。

#### 【0065】

本実施形態のセラミック電子部品1は、配線基板に埋め込まれて好適に使用されるものである。次に、セラミック電子部品1が埋め込まれたセラミック電子部品埋込み型配線基板の製造方法について、主として図9～図13を参照しながら説明する。

#### 【0066】

まず、図9に示すように、ベース基板30の上に、接着剤31を塗布する。ベース基板30は、特に限定されない。ベース基板30は、例えば、ガラスエポキシ樹脂などの樹脂基板などにより形成することができる。また、ベース基板30の厚みも特に限定されず、例えば、25 μm ~ 50 μm程度とすることができます。接着剤31としては、例えば、エポキシ樹脂系接着剤を用いることができる。接着剤31は、例えば、熱硬化型の樹脂接着剤であってもよいし、光硬化型の樹脂接着剤であってもよい。

20

#### 【0067】

次に、接着剤31の上にセラミック電子部品1を配置し、接着剤31を硬化させ、図10に示すように、接着剤32を形成することにより、セラミック電子部品1をベース基板30に対して接着させる。

#### 【0068】

次に、図11に示すように、ベース基板30のセラミック電子部品1が配置されていない部分の上に、コア材33を配置する。そして、コア材33及びセラミック電子部品1の上に、半硬化状態の硬化型樹脂を含むシート34を押し当ててプレスし、その状態でシート34を本硬化させる。これにより、図12に示すように、ベース基板30、コア材33及びシート34からなる配線基板本体35内にセラミック電子部品1が埋め込まれてなる配線基板37を完成させることができる。なお、コア材33は、例えば、ガラスエポキシ樹脂など樹脂基板などにより形成することができる。

30

#### 【0069】

次に、ベース基板30の上に、パターニングされたCu層36の上から配線基板37にレーザー光線を照射する（コンフォーマルマスク法）。これにより、配線基板37に第1, 第2の外部電極13, 14に開口するビアホール39（図13を参照）が形成される。なお、通常は、レーザー光線のスポット径が100 μm程度であるため、第1の部分13a, 14aの長さ方向Lに沿った長さは、170 μm ~ 250 μm程度であることが好ましい。

40

#### 【0070】

その後、ビアホール39の側壁などに付着したスミアを除去するデスマニア処理を行う。具体的には、過マンガン酸カリウムなどの強アルカリで処理することによりスミアを除去した後に、酸リンスを施す。

#### 【0071】

なお、ビアホール39内に第1, 第2の外部電極13, 14に接続された導体を形成するために、無電解めっきなどのめっきをさらに行ってもよい。

50

**【0072】**

ところで、従来の角柱状であり、第1及び第2の内部電極が多数設けられているセラミック電子部品においては、セラミック電子部品が厚み方向Tに反りにくく、セラミック電子部品の反りは、それほど大きな問題にならなかった。しかしながら、本実施形態のように、 $T \leq W < L$ 、 $1 / 5 W \leq T \leq 1 / 2 W$ 、 $T = 0.3 \text{ mm}$ であるような、扁平形状の薄型セラミック電子部品では、セラミック素体10の厚み寸法Tが小さいため、セラミック素体10が厚み方向に反りやすいという問題が生じる。

**【0073】**

例えば、図14に示すように、セラミック素体10が厚み方向に反っている場合は、セラミック電子部品を埋め込んだ配線基板に対してレーザー光を照射してビアホールを形成する際に、図15に模式的に示すように、第1、第2の外部電極13、14によりレーザー光40が、入射方向と異なる方向に反射されてしまう。このため、所望の形状ではない形状のビアホール39が形成されてしまう。その結果、セラミック電子部品1が埋め込まれた配線基板37の電気的特性にばらつきが生じてしまう。

10

**【0074】**

それに対して、本実施形態では、セラミックグリーンシート20(図6を参照)が含んでいる有機バインダーの重合度が、1000~1500とされている。このため、下記の実験例によっても裏付けられるように、セラミック素体10の反り量を小さくすることができる。具体的には、第1の主面の第1の外部電極の長さ方向の一方側の端部が位置している部分と、第1の主面の第2の外部電極の長さ方向の他方側の端部が位置している部分とを通過する平面と、第1の主面のうちの平面と最も離れた部分との間の距離X1を4.9  $\mu\text{m}$ 以下とすることができる。これにより、セラミック素体10の反り量を好適に低減できる。従って、ビアホール39を高い形状精度で形成でき、配線基板37の電気的特性のばらつきを低減できる。

20

**【0075】**

また、本実施形態では、第2の導電性ペースト層23が形成されたマザーリード層22のプレス工程によって、第2の導電性ペースト層23の表面の表面粗さが小さくされる。その結果、第1及び第2の外部電極13、14の表面の表面粗さを小さくすることができる。具体的には、第1及び第2の外部電極13、14のそれぞれの表面の表面粗さ(Ra)を、1.55  $\mu\text{m}$ 以下とすることができる。従って、図16に示すように、レーザー光40の反射散乱を抑制することができる。その結果、ビアホール39の形状精度をより高めることができ、配線基板37の電気的特性のばらつきをより効果的に低減できる。

30

**【0076】**

以下、本発明を実施した好ましい形態の他の例について説明する。以下の説明において、上記第1の実施形態と実質的に同様の機能を有する部材を同じ符号で参照し、説明を省略する。

**【0077】****(第2の実施形態)**

図17は、第2の実施形態に係るセラミック電子部品の略図的断面図である。

**【0078】**

上記第1の実施形態では、第1及び第2の内部電極11、12を第1または第2の端面10e、10fに引き出すと共に、第1及び第2の端面10e、10fの上に、第1または第2の外部電極13、14を形成することにより、第1及び第2の内部電極11、12を第1または第2の外部電極13、14と電気的に接続する例について説明した。但し、本発明は、この構成に限定されない。

40

**【0079】**

例えば、図17に示すように、ビアホール電極25a、25bを形成し、第1及び第2の内部電極11、12を第1及び第2の主面10a、10bに引き出し、第1及び第2の主面10a、10bにおいて、第1及び第2の外部電極13、14と電気的に接続させてよい。この場合は、第1及び第2の外部電極13、14は、第1及び第2の主面10a

50

、10bの少なくとも一方に形成されていればよく、第1及び第2の側面10c、10dや第1及び第2の端面10e、10fの上には、第1及び第2の外部電極13，14は、必ずしも形成されていなくてもよい。

#### 【0080】

##### (実験例1～5)

下記の表1に示すようにバインダーの重合度を種々異ならせて、上記第1の実施形態のセラミック電子部品1と同様の構成を有する、セラミックコンデンサとしてのセラミック電子部品を、上記第1の実施形態に記載の製造方法で10000個ずつ作製し、配線基板に実装した。そして、実装に際して、マウント機の吸着ヘッドに吸着されなかったものの数量(吸着不良数量)をカウントした。また、マウント時に割れや欠けが発生したものの数量(割れ欠け数量)をカウントした。結果を下記の表1に示す。

10

#### 【0081】

また、第1の正面の形状をレーザー変位計をもちいて計測し、X1、X2を測定した。結果を下記の表1に示す。

#### 【0082】

なお、実験例1～5における詳細な条件は以下の通りである。

#### 【0083】

##### (実験例1～5の条件)

セラミック層の厚み(焼成後)：4 μm

20

バインダー：ポリビニルブチラール

セラミック材料：BaTiO<sub>3</sub>

内部電極の数量：23枚

設計容量：100pF

セラミック電子部品の寸法：長さ1mm、幅0.5mm、厚み0.14mm

第2の導電層：Cuめっき層2層の積層体(全体厚：7.5μm)

焼成最高温度：1200

焼成最高温度でのキープ時間：2時間

第2の導電性ペースト層形成後のマザー積層体のプレス圧：77.2MPa

コア材の厚み：0.15mm

30

ベース基板の厚み：25μm

ピアホールの長さ：25μm

ピアホール形成時に照射したレーザー光：CO<sub>2</sub>レーザー

レーザー光の照射条件：2mjで16μ秒間照射

#### 【0084】

##### 【表1】

| 実験例     | 1        | 2       | 3       | 4       | 5    |

|---------|----------|---------|---------|---------|------|

| 重合度     | 900      | 1000    | 1200    | 1500    | 1600 |

| X1(μm)  | 5.9      | 4.9     | 1.9     | 1.7     |      |

| 吸着不良(個) | 48/10000 | 0/10000 | 0/10000 | 0/10000 | 形成不能 |

| 割れ欠け(個) | 12/10000 | 0/10000 | 0/10000 | 0/10000 |      |

40

#### 【0085】

上記表1に示すように、X1が4.9μmより大きい実験例1では、吸着不良が発生したり、マウント時に割れや欠けが発生する場合があった。それに対して、X1が4.9μm以下である実験例2～5は、吸着不良が発生せず、また、マウント時に割れや欠けも発生しなかった。重合度が1600である実験例5では、ペーストが好適に形成できず、セラミック素体を形成できなかった。以上の結果より、樹脂バインダーの重合度を1000～1500とし、X1を4.9以下とすることが好ましいことが分かる。

#### 【0086】

##### (実験例6～10)

50

実験例 6 ~ 10 では、実験例 3 と同様の条件で、下記の表 2 に示すように、第 2 の導電性ペースト層形成後のマザー積層体のプレス圧を種々異ならせてセラミックコンデンサとしてのセラミック電子部品を各 30 個作製した。作製した各 30 個のセラミック電子部品のそれぞれについて、第 1 の外部電極の第 1 の部分の形状をレーザー変位計を用いて測定し、表面粗さ ( $R_a$ ) を計測した。結果を下記の表 2 に示す。

#### 【0087】

また、上記作製のセラミック電子部品を上記第 1 の実施形態に記載の方法で配線基板に実装した。その実装時において、第 1 の電極の第 1 の部分に対して、直径  $100 \mu m$  のレーザー光を照射し、ピアホールを形成した。そして、形成されたピアホールの直径をマイクロスコープを用いて測定し、反射レーザー光の直径とした。そして、反射レーザー光の直径を入射レーザー光の直径で除算することにより、反射散乱率を算出した。結果を下記の表 2 に示す。

#### 【0088】

#### 【表 2】

| 実験例           | 1    | 2    | 3    | 4    | 5    |

|---------------|------|------|------|------|------|

| 弾性体の厚み(mm)    | 0.05 | 0.10 | 0.10 | 0.15 | 0.20 |

| プレス圧(MPa)     | 77.2 | 77.2 | 71.5 | 77.2 | 77.2 |

| 表面粗さ( $R_a$ ) | 0.80 | 0.90 | 1.23 | 1.55 | 2.00 |

| 反射散乱率(%)      | 3    | 3    | 5    | 8    | 12   |

#### 【0089】

上記表 2 に示す結果から、第 1 , 第 2 の外部電極の第 1 の部分の表面の表面粗さ ( $R_a$ ) を  $1.55 \mu m$  以下とすることにより、反射散乱率を 10 % 以下にできることが分かる。

#### 【符号の説明】

#### 【0090】

- 1 ... セラミック電子部品

- 1 0 ... セラミック素体

- 1 0 A ... 有効部

- 1 0 a ... 第 1 の正面

- 1 0 b ... 第 2 の正面

- 1 0 c ... 第 1 の側面

- 1 0 d ... 第 2 の側面

- 1 0 e ... 第 1 の端面

- 1 0 f ... 第 2 の端面

- 1 0 g ... セラミック層

- 1 1 ... 第 1 の内部電極

- 1 2 ... 第 2 の内部電極

- 1 3 ... 第 1 の外部電極

- 1 3 a ... 第 1 の部分

- 1 3 b ... 第 2 の部分

- 1 3 c ... 第 3 の部分

- 1 4 ... 第 2 の外部電極

- 1 4 a ... 第 1 の部分

- 1 4 b ... 第 2 の部分

- 1 4 c ... 第 3 の部分

- 1 5 ... 第 1 の導電層

- 1 6 ... 第 2 の導電層

- 2 0 ... セラミックグリーンシート

- 2 1 ... 第 1 の導電性ペースト層

10

20

30

40

50

- 2 2 ... マザー積層体

2 3 ... 第2の導電性ペースト層

2 4 a、2 4 b ... 弹性体

2 5 a、2 5 b ... ピアホール電極

3 0 ... ベース基板

3 1 ... 接着剤

3 2 ... 接着剤

3 3 ... コア材

3 4 ... シート

3 5 ... 配線基板本体

3 6 ... Cu層

3 7 ... 配線基板

3 9 ... ピアホール

4 0 ... レーザー光

- 10

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

---

フロントページの続き

合議体

審判長 酒井 朋広

審判官 関谷 隆一

審判官 井上 信一

(56)参考文献 特開2010-141300(JP,A)

特開平10-106882(JP,A)

特開2006-83060(JP,A)

特許第4299833(JP,B2)

特開平10-270283(JP,A)

特開2010-129737(JP,A)

特開2003-37022(JP,A)

特開2002-100527(JP,A)

特開平6-112085(JP,A)

特開2004-289090(JP,A)

特開2003-77756(JP,A)