(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5428368号

(P5428368)

(45) 発行日 平成26年2月26日(2014.2.26)

(24) 登録日 平成25年12月13日(2013.12.13)

(51) Int.Cl.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>HO2J</b> | <b>1/00</b> | <b>(2006.01)</b> | HO2J | 1/00 | 309R |

| <b>HO2H</b> | <b>7/00</b> | <b>(2006.01)</b> | HO2H | 7/00 | L    |

| <b>HO2H</b> | <b>9/02</b> | <b>(2006.01)</b> | HO2H | 9/02 | D    |

請求項の数 5 (全 14 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-27581 (P2009-27581)    |

| (22) 出願日  | 平成21年2月9日 (2009.2.9)          |

| (65) 公開番号 | 特開2010-183805 (P2010-183805A) |

| (43) 公開日  | 平成22年8月19日 (2010.8.19)        |

| 審査請求日     | 平成24年1月26日 (2012.1.26)        |

|           |                                                   |

|-----------|---------------------------------------------------|

| (73) 特許権者 | 000006747<br>株式会社リコー<br>東京都大田区中馬込1丁目3番6号          |

| (74) 代理人  | 100089118<br>弁理士 酒井 宏明                            |

| (72) 発明者  | 岩田 晃和<br>愛知県名古屋市千種区内山二丁目14番2<br>9号 リコーエレメックス株式会社内 |

審査官 坂本 聰生

最終頁に続く

(54) 【発明の名称】 インターロックシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

電源と、前記電源からの電力を負荷に供給する給電ライン上に設けられ、ユーザの操作により前記給電ラインを開閉するインターロックスイッチと、

前記インターロックスイッチの開閉状態を検出する開閉状態検出回路と、

前記給電ライン上に設けられ、検出された前記インターロックスイッチの開閉状態に基づいて、前記電源から前記負荷への電力の供給／遮断をスイッチングにより切り替える給電用トランジスタと、前記給電ライン上に設けられ、前記給電用トランジスタをバイパスするように接続された抵抗素子とを含む給電スイッチング回路と、

前記給電ラインとグランドとの間に接続されたコンデンサと、

前記給電用トランジスタの前記負荷側の端子の電圧の状態と、前記開閉状態検出回路が検出した前記インターロックスイッチの開閉状態との論理積信号を出力する論理積回路と

、

を備え、

前記給電スイッチング回路は、

前記開閉状態検出回路が前記インターロックスイッチが開状態から閉状態に切り替ったことを検出したときには、前記給電ラインを、前記給電用トランジスタを含まず前記抵抗素子のみを通る経路に切り替え、このときに前記給電ラインに流れる突入電流によって前記コンデンサを充電して前記突入電流が前記負荷へ流れることを抑制し、前記インターロックスイッチが開状態から閉状態に切り替ったことを検出してから予め定められたディ

10

20

レイ時間が経過した後に、前記給電ラインを、前記給電用トランジスタを通る経路に切り替え、さらに、前記論理積回路が output した前記論理積信号に基づいて、前記電源から前記負荷への電力の供給 / 遮断を行い、

前記ディレイ時間は、前記論理積回路の内部で前記論理積信号を生成するために要する時間を含むことを特徴とするインターロックシステム。

#### 【請求項 2】

前記ディレイ時間は、検出した前記インターロックスイッチの開閉状態に基づいて、前記給電用トランジスタをオン状態とするための信号が入力されてから、前記給電用トランジスタが実際にオン状態となるまでのスイッチング遅延時間を含む請求項 1 に記載のインターロックシステム。 10

#### 【請求項 3】

前記給電スイッチング回路は、前記開閉状態検出回路が検出した前記インターロックスイッチの開閉状態に基づいてスイッチング動作を行い、このスイッチング動作により前記給電用トランジスタをスイッチングさせるトランジスタ回路を含み、

前記ディレイ時間は、前記トランジスタ回路のスイッチング動作に要するスイッチング時間を含む請求項 2 に記載のインターロックシステム。

#### 【請求項 4】

前記給電用トランジスタとして F E T を用いる請求項 1 ないし請求項 3 のいずれか 1 項に記載のインターロックシステム。

#### 【請求項 5】

前記トランジスタ回路としてデジタルトランジスタを用いる請求項 3 、または請求項 3 を引用する請求項 4 に記載のインターロックシステム。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、インターロックシステムに関し、特に記録媒体搬送装置および画像形成装置、さらに詳しくは、プリンタ、複写機、F A X、印刷機等及びそれらを複数搭載した複合機等に用いられる静電吸着方式の記録媒体搬送装置および該記録媒体搬送装置を搭載した小型の画像形成装置に備えられたインターロックシステムに関する。 30

##### 【背景技術】

##### 【0002】

プリンタ、ファクシミリ、複写装置等の画像形成装置として用いるインクジェット記録装置は、一般的には、インク滴を吐出する記録ヘッドを被記録媒体（用紙）の搬送方向に對して直交する方向にシリアルスキャンさせるとともに、被記録媒体を記録幅に応じて間歇的に搬送し、搬送と記録を交互に繰り返すことによって被記録媒体に画像を形成している。

##### 【0003】

このような画像形成装置において、ローラ間に掛け渡した搬送ベルトに被記録媒体全面を吸着させて搬送することで、被記録媒体のヘッドに対する平面度を確保し、形成画像の品質の向上を図るものが知られている（特許文献 1 ~ 3 参照）。 40

##### 【0004】

このような画像形成装置においては、従来より搬送ベルトの帯電からのオペレータ保護のために、インターロック回路が給電装置内に設けられている。このインターロック回路は、画像形成装置のドア開閉に連動して開閉動作するインターロックスイッチを含み、ドアが開いている場合には、インターロックスイッチが開状態となって高電圧を発生する駆動部や定着部への給電が中止され、オペレータにとって感電等の危険な状態が発生しないようにしている。

##### 【0005】

しかし、このようなインターロック回路においては、ドアを閉めたときに高圧生成部に搭載されているコンデンサに急峻な電流（突入電流）が流れ込むことにより、インターロ

10

20

30

40

50

ツクスイッチが溶着してしまう問題がある。

**【0006】**

そこで、突入電流を低減させる策として、インターロック回路と並列に突入電流対策素子を搭載した突入電流低減回路が広く知られている（特許文献4，5参照）。これら特許文献4，5に記載の技術は、インターロック回路に接続される負荷の電流容量が大きいため、リレーを用いたインターロック回路を採用している。すなわち、電源をスイッチングするリレーと並列にNTCサーミスタやPTCサーミスタを接続し、突入電流によるリレーの接点溶着を防止している。

**【先行技術文献】**

**【特許文献】**

10

**【0007】**

**【特許文献1】**特開2000-238925号公報

**【特許文献2】**特開2003-103857号公報

**【特許文献3】**特開2001-206574号公報

**【特許文献4】**特開2006-094580号公報

**【特許文献5】**特開2007-236103号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

20

特許文献4にあるような、リレーを用いた給電のスイッチング回路は、回路が複雑になり、必然的にコストアップにつながってしまう。また、特許文献4の技術では、給電スイッチング回路のオンタイミングが任意に設定できず、負荷への容量が変更になった際に給電のスイッチング回路のオンタイミングを変更することができないという問題もある。

**【0009】**

また、特許文献5では、NPNトランジスタを用いて給電スイッチング回路を構成しているが、消費電力や発熱の増大等に懸念が残る。

**【0010】**

30

上記問題点を背景として、本発明の課題は、接続される負荷への電流容量が小さく、かつ安全上給電をスイッチングする必要のある小型の記録装置及び搬送装置に搭載するインターロックスイッチシステムについて、回路を簡潔かつコストを増大させずに、またスイッチング回路の発熱等に対して問題のない、突入電流を適切に制御したインターロックスイッチシステムを提供することにある。

**【課題を解決するための手段及び発明の効果】**

**【0011】**

上記課題を解決するためのインターロックスイッチシステムは、電源と、電源からの電力を負荷に供給する給電ライン上に設けられ、ユーザの操作により給電ラインを開閉するインターロックスイッチと、インターロックスイッチの開閉状態を検出する開閉状態検出回路と、給電ライン上に設けられ、検出されたインターロックスイッチの開閉状態に基づいて、電源から負荷への電力の供給／遮断をスイッチングにより切り替える給電用トランジスタと、給電ライン上に設けられ、給電用トランジスタをバイパスするように接続された抵抗素子とを含む給電スイッチング回路と、給電ラインとグランドとの間に接続されたコンデンサと、を備え、

40

給電スイッチング回路は、

開閉状態検出回路が、インターロックスイッチが開状態から閉状態に切り替ったことを検出したときには、給電ラインを、給電用トランジスタを含まず抵抗素子のみを通る経路に切り替え、このときに給電ラインに流れる突入電流によってコンデンサを充電して突入電流が負荷へ流れることを抑制し、インターロックスイッチが開状態から閉状態に切り替ったことを検出してから予め定められたディレイ時間が経過した後に、給電ラインを、給電用トランジスタを通る経路に切り替えることを前提とする。

**【0012】**

50

上記構成によって、給電用トランジスタ、インターロックスイッチや負荷等に突入電流が流れることを抑制できるため、これらを構成する部品への影響（例えば、電気的ストレス）を抑えることができる。また、耐電流値の低い部品を使用することができるので、低成本で本発明の構成を実現できる。

#### 【0013】

また、本発明のインターロックスистемにおけるディレイ時間は、検出したインターロックスイッチの開閉状態に基づいて、給電用トランジスタをオン状態とするための信号が入力されてから、給電用トランジスタが実際にオン状態となるまでのスイッチング遅延時間を含むように構成される。

#### 【0014】

上記構成によって、突入電流が流れる時間が給電用トランジスタのスイッチング遅延時間と同じあるいは短いときには、給電用トランジスタ以外の部品は必要なく、簡易かつ低成本で本発明の構成を実現できる。

#### 【0015】

また、本発明のインターロックスистемにおける給電スイッチング回路は、開閉状態検出回路が検出したインターロックスイッチの開閉状態に基づいてスイッチング動作を行い、このスイッチング動作により給電用トランジスタをスイッチングさせるトランジスタ回路を含み、ディレイ時間は、トランジスタ回路のスイッチング動作に要するスイッチング時間を含むように構成される。

#### 【0016】

上記構成によって、突入電流が流れる時間が給電用トランジスタのスイッチング遅延時間よりも長いときには、トランジスタ回路のスイッチング時間をディレイ時間に含めることで、負荷等に突入電流が流れることを抑制できる。また、ディレイ時間の調整をトランジスタ回路のスイッチング時間によって行うこともでき、インターロックスистемに最適な給電用トランジスタを用いることができる。

#### 【0017】

また、本発明のインターロックスистемは、開閉状態検出回路が検出したインターロックスイッチの開閉状態を入力する開閉状態入力回路と、入力されたインターロックスイッチの開閉状態に基づいて、給電用トランジスタのスイッチングを制御する給電スイッチング制御信号を給電スイッチング回路に出力する制御信号出力回路と、を備え、

制御信号出力回路は、開閉状態検出回路がインターロックスイッチが開状態から閉状態に切り替ったことを検出したときには、給電用トランジスタをオフ状態のままとする給電スイッチング制御信号を出力して、給電スイッチング回路が給電スイッチング制御信号に基づいて、給電ラインを抵抗素子のみを通る経路に切り替え、

また、制御信号出力回路は、インターロックスイッチが開状態から閉状態に切り替ってからディレイ時間が経過した後に、給電用トランジスタをオン状態とする給電スイッチング制御信号を出力して、給電スイッチング回路が給電スイッチング制御信号に基づいて、給電ラインを給電用トランジスタを通る経路に切り替えるように構成される。

#### 【0018】

上記構成によって、給電用トランジスタのスイッチング遅延時間、あるいはトランジスタ回路のスイッチング時間によらず、別途設けられた、開閉状態入力回路および制御信号出力回路によって任意にディレイ時間を設定できるので、負荷等に突入電流が流れることをより確実に抑制できる。また、給電用トランジスタあるいはトランジスタ回路を、インターロックスистемに応じて最適なものとすることができます。

#### 【0019】

また、本発明のインターロックスystemは、給電用トランジスタの負荷側の端子の電圧の状態と、開閉状態検出回路が検出したインターロックスイッチの開閉状態との論理積信号を出力する論理積回路を備え、

給電スイッチング回路は、論理積回路が出力した論理積信号に基づいて、電源から負荷への電力の供給／遮断を行い、

10

20

30

40

50

ディレイ時間は、論理積回路内部で論理積信号を生成するために要する時間を含むように構成される。

【0020】

上記構成によって、より確実にインターロックスイッチの開閉状態を検出することができる。また、突入電流が流れる時間が給電用トランジスタのスイッチング遅延時間よりも長いときには、論理積回路内部で論理積信号を生成するために要する時間をディレイ時間に含めることで、負荷等に突入電流が流れることを抑制できる。

【0021】

また、本発明のインターロックスистемは、給電用トランジスタとしてFETを用いるように構成される。

10

【0022】

FETは、スイッチング素子として広く用いられていて、MOSFETのようにバイポーラトランジスタよりも大きな電流を流すことのできるものもある。上記構成によって、比較的簡易かつ安価に本発明の構成を実現できる。

【0023】

また、本発明のインターロックスистемは、トランジスタ回路としてデジタルトランジスタを用いるように構成される。

【0024】

デジタルトランジスタはトランジスタチップに抵抗を内蔵したものである。上記構成によって、回路基板におけるトランジスタ回路の占有面積を小さくでき、インターロックスystemの小型化に寄与することができる。

20

【図面の簡単な説明】

【0025】

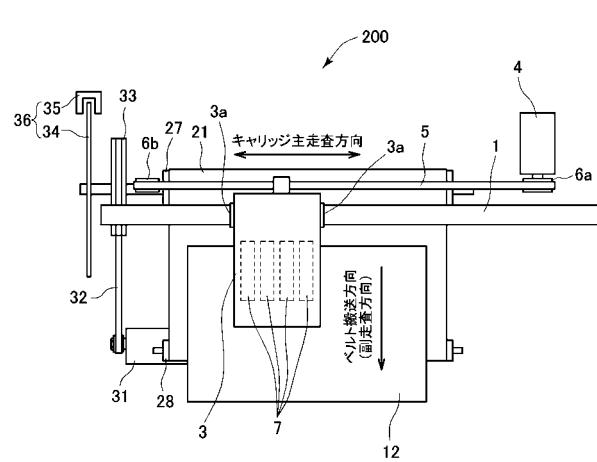

【図1】インターロックスystemが用いられるインクジェットプリンタにおける印刷基幹プロセスを示す図。

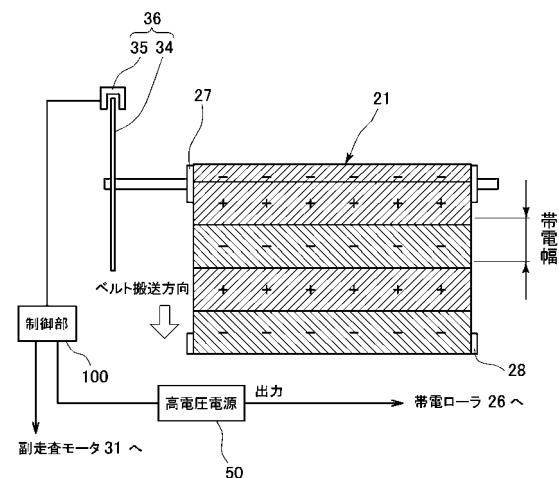

【図2】図1の搬送ベルト上での帯電の様子を表す模式図。

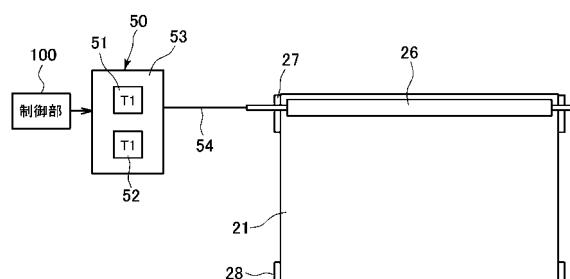

【図3】高電圧電源の構成の一例を示す図。

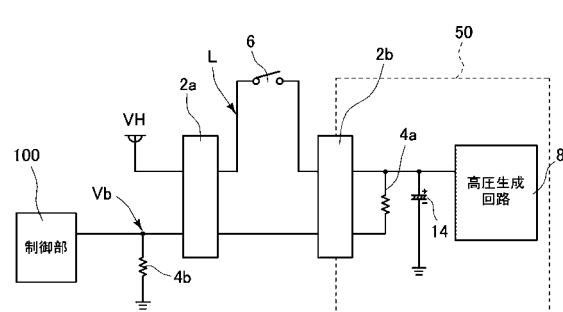

【図4】従来のインターロックスystemの構成を示す図。

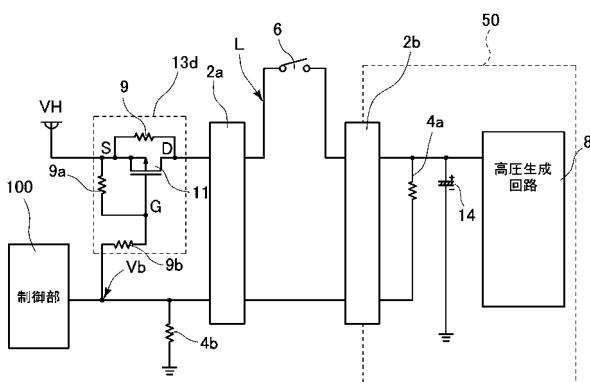

【図5】本発明のインターロックスystemの構成を示す図(実施例1)。

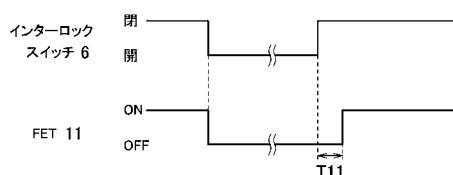

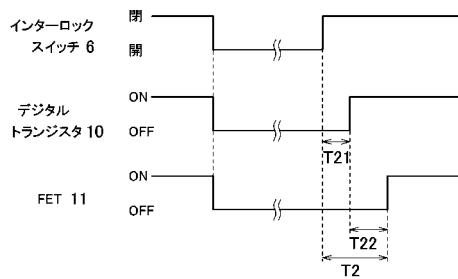

【図6】図5の構成におけるFETのオン/オフに係る信号のタイミングチャート(実施例1)。

30

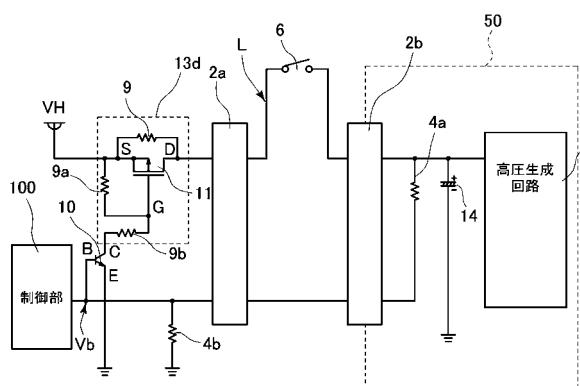

【図7】本発明のインターロックスystemの構成を示す図(実施例2)。

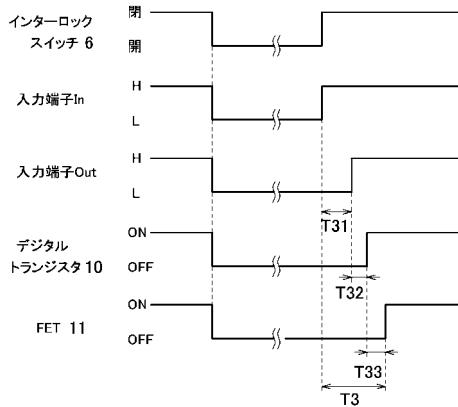

【図8】図7の構成におけるFETのオン/オフに係る信号のタイミングチャート(実施例2)。

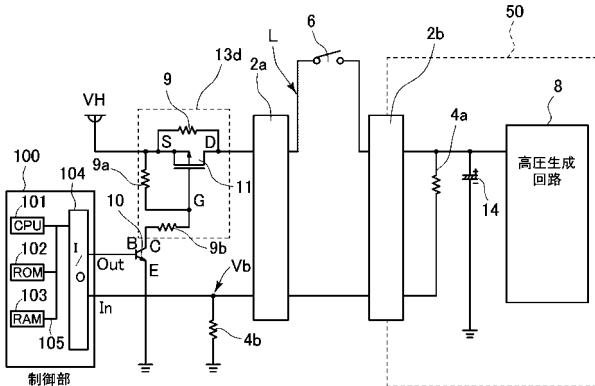

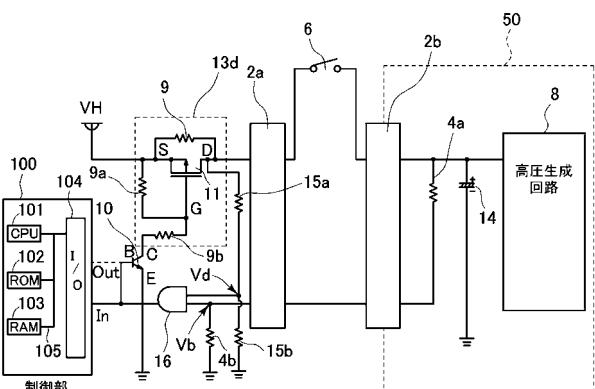

【図9】本発明のインターロックスystemの構成を示す図(実施例3)。

【図10】図9の構成におけるFETのオン/オフに係る信号のタイミングチャート(実施例3)。

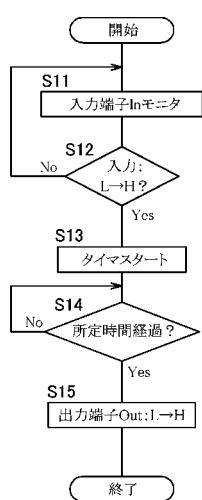

【図11】給電ライン開閉制御処理を説明するフロー図(実施例3)。

【図12】本発明のインターロックスystemの構成を示す図(実施例4)。

【図13】図12の構成におけるFETのオン/オフに係る信号のタイミングチャート(実施例4)。

40

【発明を実施するための形態】

【0026】

以下、本発明に係るインターロックスystemの実施形態を、本発明の好適な実施例として、小型のプリンタ、特にインクジェットプリンタを例に挙げて、図面を参照しつつ説明する。図1に、インクジェットプリンタ200における印刷基幹プロセスの説明図を示す。図2に、図1における搬送ベルト21上での帯電の様子を表す模式図を示す。

【0027】

図1に示すように、インクジェットプリンタ200では、図示しない左右の側板に横架したガイド部材であるガイドロッド1と、図示しないガイドステーとでキャリッジ3をキ

50

キャリッジ主走査方向に摺動自在に保持し、主走査モータ4で駆動プーリ6aと従動プーリ6b間に架け渡したタイミングベルト5を介して、キャリッジ主走査方向に移動走査する。なお、キャリッジ3とガイドロッド1との間にはガイドブッシュ（軸受）3a, 3aをそれぞれ介在させている。

#### 【0028】

このキャリッジ3には、例えばイエロー(Y), シアン(C), マゼンタ(M), ブラック(Bk)の各色のインク滴を吐出する4個のインクジェットヘッドからなる記録ヘッド7を複数のインク吐出口を主走査方向と交叉する方向に配列し、インク滴吐出方向を下方(印刷用紙12側)に向けて装着している。

#### 【0029】

記録ヘッド7を構成するインクジェットヘッドとしては、圧電素子などの圧電アクチュエータ、発熱抵抗体などの電気熱変換素子を用いて液体の膜沸騰による相変化を利用するサーマルアクチュエータ、温度変化による金属相変化を用いる形状記憶合金アクチュエータ、静電力を用いる静電アクチュエータなどをインクを吐出するためのエネルギー発生手段として備えたものなどを使用できる。なお、異なる色を吐出する複数のノズル列を備えた1または複数の液滴吐出ヘッドで記録ヘッドを構成することもできる。

#### 【0030】

搬送ベルト21は、無端または繋ぎ合わされた(これらを「無端状」という)ベルトであり、搬送ローラ27とテンションを与えたテンションローラ28との間に掛け渡され、副走査モータ31からタイミングベルト32およびタイミングローラ33を介して搬送ローラ27が回転されることで、ベルト搬送方向(副走査方向)に周回するように構成している。

#### 【0031】

このインクジェットプリンタ200における用紙搬送装置は、搬送ベルト21および搬送ローラ27、高電圧電源50などによって構成される。

#### 【0032】

図3のように、高電圧電源50は、2個のDCトランス(T1)51、52が1枚の基板53上に配設されており、制御部100からの制御信号に応じて、これらのDCトランス51、52によって生成した矩形波高電圧を、高圧ケーブル54を介して帯電ローラ26に印加する。

#### 【0033】

制御部100は、周知のCPU, ROM, RAMおよびその周辺回路を含むマイクロコンピュータとして構成され、CPUがROM等に記憶された制御プログラムを実行することで、インクジェットプリンタの各種機能を実現する。

#### 【0034】

図3のように、帯電ローラ26は、搬送ベルト21の表層に接触し、搬送ベルト21の回転に従動して回転するように配置されている。よって、図2のように、帯電ローラ26が1回転したときに搬送されたベルト21の長さ(つまり、円筒状の帯電ローラ26の断面を形成する円の円周の長さ)が帯電幅となる。また、搬送ローラ27はアースローラの役目も担っており、搬送ベルト22の中抵抗層と接触配置され、図示しない接地ラインを介して接地している。

#### 【0035】

また、搬送ローラ27の軸には、スリット円板34を取り付け、このスリット円板34のスリットを検知するセンサ35を設けて、これらのスリット円板34およびセンサ35によってエンコーダ36を構成している(図1, 図2参照)。

#### 【0036】

図4に、従来のインターロックシステムの構成を示す。電源VHと負荷である高電圧電源50とを結ぶ給電ラインLには、給電ラインLを開閉するためのインターロックスイッチ6と、インターロックスイッチ6を挟むようにコネクタ2a, 2bが設けられている。このインターロックスイッチ6は、インクジェットプリンタのドアあるいはカバーの開閉

10

20

30

40

50

に連動して開閉動作するものである。また、インターロックスイッチ 6 は、制御部 100 等が含まれる制御基板（図示せず）のコネクタ 2a と高電圧電源 50 側のコネクタ 2b を接続するハーネス上に組み込まれることが多い。

#### 【0037】

また、インターロックスイッチ 6 の開閉を検知することを目的とし、高電圧電源 50 へ給電された電圧を監視するための信号を生成するために、抵抗 4a と 4b とが配置されている。すなわち、インターロックスイッチ 6 が閉状態であるときには、抵抗 4b の電位 Vb は、抵抗 4a と 4b との分圧比による値となり、インターロックスイッチ 6 が開状態であるときには、抵抗 4b の電位 Vb は、0V となる。

#### 【0038】

また、インターロックスイッチ 6 は、安全規格の要求により、機械的に接点同士の沿面距離を必要とすることが多い。そこで、インクジェットプリンタ全体に通電されているときにドアを閉めると、インターロックスイッチ 6 が開閉状態となり、高電圧電源 50 上のコンデンサ 14 に対してインターロックスイッチ 6 を介して突発的な電流（突入電流）が流れ込む。この突入電流により、インターロックスイッチ 6 が接点の溶着を起こしたり、各基板上のコネクタ 2a ないし 2b の端子が溶着する等して、正常に高電圧が搬送ベルト 27 に供給されなくなってしまう。

10

#### 【実施例 1】

#### 【0039】

図 5 に、本発明のインターロックスистем の構成の一例を示す。本構成においては、図 4 の構成に加えて、給電ライン L の電源 VH とコネクタ 2a との間に、給電スイッチング回路 13d が設けられている。給電スイッチング回路 13d は、給電側にて、給電ライン L を電気的に遮断することのできる FET 11 を含んで構成される。FET 11 のソース端子 S が給電ライン L 上の電源 VH 側に接続され、ドレイン端子 D が給電ライン L 上の負荷すなわち高電圧電源 50 側に接続され、FET 11 のゲート端子 G は、静電気やサーボ電圧による破壊防止用のゲート保護抵抗 9b を介して、抵抗 4a, 4b の接続点に接続されている。つまり、FET 11 は、インターロックスイッチ 6 の開閉に応じて変化する抵抗 4b の電位 Vb に応じて、オン / オフの状態が切り替る。また、ゲート端子 G ~ ソース端子 S 間に接続された抵抗 9a は、FET 11 内部に溜まった電荷を放電させて、FET 11 の動作を確実にするためのものである。なお、抵抗 4a, 4b が本発明の開閉状態検出回路に相当する。また、FET 11 が本発明の給電用トランジスタに相当し、本実施例では MOSFET を用いている。

20

#### 【0040】

また、給電ライン L には、FET 11 をバイパスするように抵抗 9 が接続されている。また、高電圧電源 50 側の給電ライン L とグランドとの間には、コンデンサ 14 が接続されている。なお、抵抗 9 が本発明の抵抗素子に相当する。

30

#### 【0041】

また、高電圧電源 50 は、図 3 の DC トランジスタ 51, 52 が実装された基板 53 および高電圧を発生するために必要な他の回路を含んでいる。

40

#### 【0042】

図 6 に、図 5 の構成におけるインターロックスイッチ 6 と FET 11 との、動作の関係を表すタイミングチャートを示す。インターロックスイッチ 6 が閉開状態となったときには、ゲート端子 G（すなわち電位 Vb）への入力電圧がほぼ 0V となるので、FET 11 はオンオフ状態となる。

#### 【0043】

その後、インターロックスイッチ 6 が閉開状態となった直後には、FET 11 は直ちにオフオン状態とはならず、インターロックスイッチ 6 が閉開状態となってから時間 T11（詳細は後述）だけ遅れてオン状態となる。その間は、電源 VH からの電流（突入電流）は、抵抗 9 を流れてコンデンサ 14 に充電される。これにより、高電圧電源 50 へ流れる突入電流を抑制できるので、高電圧電源 50 を保護することができる。また、抵抗

50

9の値を調整して突入電流の一部を熱として消費させることで、インターロックスイッチ6の溶着を防ぐこともできる。そして、時間T11が経過した後にFET11がオン状態となって、電源VHからの電流（定格電流）は、抵抗9ではなくFET11を流れ、コンデンサ14への充電が終わると、高圧生成回路8で所定の高電圧を発生することが可能となる。

#### 【0044】

なお、上述の時間T11が、本発明のディレイ時間に相当する。また、上述の例では、時間T11は、インターロックスイッチ6が開閉状態となってから、実際にFET11がオン状態となるまでのスイッチング遅延時間（いわゆる、ゲート遅延時間）に相当している。

10

#### 【実施例2】

#### 【0045】

図7に、本発明のインターロックスистемの構成の別例を示す。図7の例は、図5の給電スイッチング回路13dにおけるFET11のゲート端子Gより抵抗9bを介して、トランジスタチップに抵抗を内蔵したデジタルトランジスタ10のコレクタ端子Cに接続し、エミッタ端子Eを接地したもので、その他の構成は図5と同様であるため、ここでの詳細な説明は割愛する。なお、デジタルトランジスタ10が本発明のトランジスタ回路に相当する。また、デジタルトランジスタ10のトランジスタ以外の構成要素については、図示を省略している。

#### 【0046】

20

後述のように、デジタルトランジスタ10は、インターロックスイッチ6の開閉状態すなわち抵抗4bの電位Vbに基づいてオン／オフのスイッチングを行い、デジタルトランジスタ10のスイッチング動作に基づいて、FET11のスイッチングを行う。

#### 【0047】

図8に、図7の構成におけるインターロックスイッチ6、デジタルトランジスタ10、FET11との、動作の関係を表すタイミングチャートを示す。インターロックスイッチ6が閉開状態となったときには、抵抗4bの電位Vbがほぼ0Vとなり、デジタルトランジスタ10がオン／オフ状態となって、FET11もオン／オフ状態となる。

#### 【0048】

その後、インターロックスイッチ6が閉開状態となったときには、時間T21だけ遅れてデジタルトランジスタ10がオフ／オン状態となる。さらに、デジタルトランジスタ10がオフ／オン状態となってから時間T22だけ遅れてFET11がオフ／オン状態となる。つまり、インターロックスイッチ6が閉開状態となってから、時間T2（=T21+T22）の間は、電源VHからの電流（突入電流）は、抵抗9を流れてコンデンサ14に充電され、上述の実施例1と同様に、高電圧電源50を保護したり、インターロックスイッチ6の溶着を防ぐことができる。

30

#### 【0049】

なお、上述の時間T21とT22との和であるT2が、本発明のディレイ時間に相当する。また、上述の例では、時間T21は、インターロックスイッチ6が閉開状態となってから、実際にデジタルトランジスタ10がオン状態となるまでのスイッチング時間に相当している。また、時間T22は、デジタルトランジスタ10がオン状態となってから、実際にFET11がオン状態となるまでのスイッチング遅延時間（いわゆる、ゲート遅延時間）に相当している。

40

#### 【実施例3】

#### 【0050】

図9に、本発明のインターロックスистемの構成の別例を示す。図9の例は、図7の構成において、インターロックスイッチ6の開閉検知信号となる抵抗4bの電位Vbが制御部100の入力端子Inに入力され、制御部100の出力端子Outとデジタルトランジスタ10のベース端子とが接続されている。

#### 【0051】

50

制御部100は、CPU101, ROM102, RAM103, および周知の入出力回路であるI/O104がバスライン105で接続されたマイクロコンピュータとして構成されている。そして、CPU101が、ROM102に記憶された制御プログラムを実行し、I/O104を介して、入力端子Inに入力された抵抗4bの電位Vbの値に応じて、出力端子Outの状態を切り替え、デジタルトランジスタ10のオン／オフの状態を切り替える。なお、RAM103は、制御プログラムを実行する際のワークエリアとして用いられる。

#### 【0052】

図10に、図9の構成におけるインターロックスイッチ6, 入力端子In, 出力端子Out, デジタルトランジスタ10, FET11の動作の関係を表すタイミングチャートを示す。インターロックスイッチ6が閉 閉状態となったときには、抵抗4bの電位Vbが0Vとなるので、入力端子InにはLレベルが入力される。制御プログラムでは、入力端子InがLレベルになったことを検知した場合、直ちに出力端子OutからLレベル(0V)を出力する。これにより、デジタルトランジスタ10がオン オフ状態となって、これに伴いFET11もオン オフ状態となる。

#### 【0053】

その後、インターロックスイッチ6が開 閉状態となったときには、電位Vbが例えば5Vとなるので、入力端子InにはHレベルが入力される。制御プログラムでは、入力端子InがL Hレベルになったことを検知した場合、タイマを作動させる。タイマ値T31は、例えば突入電流が発生する時間と同じかその時間よりも大きい値を設定する。そして、タイマの値が設定値を超えたときに出力端子OutからHレベル(すなわち、例えば5Vのようなデジタルトランジスタ10をオン状態とすることができる電圧値)を出力する。

#### 【0054】

出力端子OutからHレベルが出力されたときには、時間T32だけ遅れてデジタルトランジスタ10がオフ オン状態となる。さらに、デジタルトランジスタ10がオフ オン状態となってから時間T33だけ遅れてFET11がオフ オン状態となる。つまり、インターロックスイッチ6が開 閉状態となってから、時間T3 (= T31 + T32 + T33)の間は、電源VHからの電流(突入電流)は、抵抗9を流れてコンデンサ14に充電され、上述の実施例1と同様に、高電圧電源50を保護したり、インターロックスイッチ6の溶着を防ぐことができる。

#### 【0055】

なお、上述の時間(T31 + T32 + T33)が、本発明のディレイ時間に相当する。また、上述の実施例2と同様に、時間T32は、デジタルトランジスタ10のスイッチング時間に相当している。また、時間T33は、FET11のスイッチング遅延時間(いわゆる、ゲート遅延時間)に相当している。

#### 【0056】

図11を用いて、制御部110において、ROM102に記憶された制御プログラムに含まれてCPU101が実行する給電ライン開閉制御処理について説明する。なお、本処理は、制御プログラムに含まれる他の処理とともに繰り返し実行される。

#### 【0057】

まず、入力端子Inの状態をモニタする(S11)。そして、インターロックスイッチ6が閉状態となり、入力端子Inの状態がLレベルからHレベルに変化した場合(S12: Yes)、ディレイ時間を計測するためのタイマをスタートさせる(S13)。

#### 【0058】

なお、入力端子Inの状態がLレベルからHレベルに変化しない場合(S12: No)、ステップS11に戻るようになっているが、無限ループを形成するものではなく、適宜他の処理が実行されている。

#### 【0059】

タイマがスタートして、予め定められた時間T31を経過した場合(S14: Yes)

10

20

30

40

50

、出力端子 Out の状態を L レベルから H レベルに変化させる (S15)。上記と同様に、ディレイ時間を経過しない場合 (S14: No) も、無限ループを形成するものではない。

#### 【0060】

本実施例において、T31, T32, T33 の和である T3 をディレイ時間としているが、ディレイ時間 T3 の生成を制御部 10 のみで行うようにしてもよい。このようにすると、FET11 のゲート遅延時間 (T33) およびデジタルトランジスタ 10 のスイッチング時間 (T32) に関係なく、インターロックシステムに最適な部品を選択することができる。また、出力端子 Out と FET11 のゲート端子 G を直接接続することもでき、デジタルトランジスタ 10 を使用する必要もなくなり、部品コストを低減することもできる。10

#### 【実施例 4】

#### 【0061】

図 12 に、本発明のインターロックシステムの構成の別例を示す。図 12 の例は、図 9 の構成において、インターロックスイッチ 6 の開閉検知信号となる抵抗 4b の電位 Vb と、抵抗 15a, 15b により分圧された FET11 のドレイン端子 D の電位 Vd とが論理積回路である AND 回路 16 に入力されている。そして、この AND 回路 16 の出力端子とデジタルトランジスタ 10 のベース端子とが接続される。そして、デジタルトランジスタ 10 は、AND 回路 16 の出力状態に基づいてオン / オフのスイッチングを行い、デジタルトランジスタ 10 のスイッチング動作に基づいて、FET11 のスイッチングを行う。20

#### 【0062】

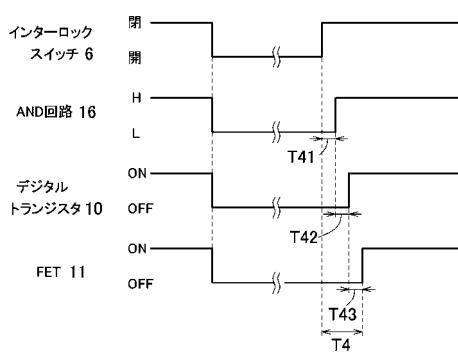

図 13 に、図 12 の構成におけるインターロックスイッチ 6, AND 回路 16, デジタルトランジスタ 10, FET11 との、動作の関係を表すタイミングチャートを示す。インターロックスイッチ 6 が閉 開状態となったときには、抵抗 4b の電位 Vb がほぼ 0V (L レベル) となり、FET11 のドレイン端子 D の電位 Vd の状態によらず AND 回路 16 は L レベルを出力し、デジタルトランジスタ 10 がオン オフ状態となって、FET11 もオン オフ状態となる。

#### 【0063】

その後、インターロックスイッチ 6 が開 閉状態となったときには、抵抗 4b の電位 Vb および FET11 のドレイン端子 D の電位 Vd は、FET11 をオン状態可能となる値 (H レベル) となり、AND 回路 16 は、双方の電位の H レベルが入力されてから時間 T41 遅れて H レベルを出力する。そして、デジタルトランジスタ 10 は、AND 回路 16 が H レベルを出力してから時間 T42 遅れてオフ オン状態となる。そして、FET11 は、デジタルトランジスタ 10 がオン状態となってから時間 T43 遅れてオフ オン状態となる。つまり、インターロックスイッチ 6 が開 閉状態となってから、時間 T4 (= T41 + T42 + T43) の間は、電源 VH からの電流 (突入電流) は、抵抗 9 を流れてコンデンサ 14 に充電され、上述の実施例 3 と同様に、高電圧電源 50 を保護したり、インターロックスイッチ 6 の溶着を防ぐことができる。30

#### 【0064】

なお、上述の時間 T4 が、本発明のディレイ時間に相当する。また、上述の例では、時間 T41 は、AND 回路 16 で出力信号 (すなわち AND 信号) を生成するために要する時間に相当している。また、上述の実施例 2 と同様に、時間 T42 は、デジタルトランジスタ 10 のスイッチング時間に相当している。また、時間 T43 は、FET11 のスイッチング遅延時間 (いわゆる、ゲート遅延時間) に相当している。40

#### 【0065】

図 12 の構成で、ディレイ時間 T4 が時間 T41 と時間 T43 の和で十分な場合は、デジタルトランジスタ 10 を使用しなくてもよい。この場合、AND 回路 16 の出力端子と FET11 のゲート端子 G とが接続される。

#### 【0066】

10

20

30

40

50

また、ディレイ時間T4を、AND回路16, デジタルトランジスタ10, FET11の特性によらず任意の値としたい場合には、AND回路16の出力端子と制御部100の入力端子Inとを接続し、さらに、制御部100の出力端子Outとデジタルトランジスタ10のベース端子とを接続する。そして、図11のような給電ライン開閉制御処理を実行し、入力端子Inの状態（すなわちAND回路16の出力状態）に基づいて、出力端子Outの状態を変化させる。また、ディレイ時間T4を制御部100で任意に決定できるため、デジタルトランジスタ10を使用しなくてもよい。この場合、出力端子OutとFET11のゲート端子Gとが接続される。

#### 【0067】

以上、本発明の実施の形態を説明したが、これらはあくまで例示にすぎず、本発明はこれらに限定されるものではなく、特許請求の範囲の趣旨を逸脱しない限りにおいて、当業者の知識に基づく種々の変更が可能である。

10

#### 【符号の説明】

#### 【0068】

|        |                         |    |

|--------|-------------------------|----|

| 6      | インターロックスイッチ             |    |

| 2a, 2b | コネクタ                    |    |

| 4a, 4b | 抵抗（開閉状態検出回路）            |    |

| 9      | 抵抗（抵抗素子）                |    |

| 8      | 高圧生成回路                  |    |

| 10     | デジタルトランジスタ（トランジスタ回路）    | 20 |

| 11     | FET（給電用トランジスタ）          |    |

| 13d    | 給電スイッチング回路              |    |

| 14     | コンデンサ                   |    |

| 16     | AND回路                   |    |

| 50     | 高電圧電源（負荷）               |    |

| 100    | 制御部（開閉状態入力回路, 制御信号出力回路） |    |

| 200    | インクジェットプリンタ             |    |

| L      | 給電ライン                   |    |

| VH     | 電源                      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図 10】

〔 111 〕

【习题 1 2】

【図 1-3】

---

フロントページの続き

(56)参考文献 特開2007-236103(JP,A)

特開2008-022597(JP,A)

特開2003-348747(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02H3/08 - 3/253

H02H7/00

H02H7/10 - 7/20

H02H9/00 - 9/08

H02J1/00 - 1/16