(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6000655号

(P6000655)

(45) 発行日 平成28年10月5日(2016.10.5)

(24) 登録日 平成28年9月9日(2016.9.9)

(51) Int.Cl.

F 1

|                |              |                  |                |              |          |

|----------------|--------------|------------------|----------------|--------------|----------|

| <b>G 0 6 F</b> | <b>1/32</b>  | <b>(2006.01)</b> | <b>G 0 6 F</b> | <b>1/32</b>  | <b>Z</b> |

| <b>B 4 1 J</b> | <b>29/38</b> | <b>(2006.01)</b> | <b>B 4 1 J</b> | <b>29/38</b> | <b>Z</b> |

| <b>B 4 1 J</b> | <b>29/46</b> | <b>(2006.01)</b> | <b>B 4 1 J</b> | <b>29/46</b> | <b>Z</b> |

請求項の数 15 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2012-122905 (P2012-122905)  |

| (22) 出願日  | 平成24年5月30日 (2012.5.30)        |

| (65) 公開番号 | 特開2013-250609 (P2013-250609A) |

| (43) 公開日  | 平成25年12月12日 (2013.12.12)      |

| 審査請求日     | 平成27年6月1日 (2015.6.1)          |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 相園 啓介<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

| 審査官 田川 泰宏 |                                            |

最終頁に続く

(54) 【発明の名称】情報処理装置、情報処理装置の制御方法及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

起動時に複数の記憶手段のそれぞれに記憶された特定のデータの整合性をチェックするチェック処理を実行する第1の起動モードと、起動時に前記チェック処理を実行しない第2の起動モードと、を含む複数の起動モードの何れかで起動可能な情報処理装置であって、

前記複数の記憶手段のそれぞれから第1の所定のデータを読み出す第1の読み出手段と、前記第1の読み出手段により読み出された前記第1の所定のデータを保持する保持手段と、

前記情報処理装置が前記第2の起動モードで起動する場合に、複数の記憶手段のそれぞれから第2の所定のデータを読み出す第2の読み出手段と、

前記保持手段により保持された前記第1の所定のデータと前記第2の読み出手段により読み出された前記第2の所定のデータとが一致しない場合に、前記チェック処理を実行するよう制御する制御手段と、を有することを特徴とする情報処理装置。

## 【請求項 2】

前記第1の所定のデータ及び前記第2の所定のデータは、記憶手段を特定するための個体情報である、ことを特徴とする請求項1に記載の情報処理装置。

## 【請求項 3】

前記第1の所定のデータ及び前記第2の所定のデータは、記憶手段のシリアルナンバーである、ことを特徴とする請求項1又は2に記載の情報処理装置。

10

20

**【請求項 4】**

前記複数の記憶手段のそれぞれで記憶される前記特定のデータは、セキュリティに関する情報、又は、課金に関する情報、であることを特徴とする請求項 1 乃至 3 の何れか 1 項に記載の情報処理装置。

**【請求項 5】**

前記制御手段は、前記保持手段により保持された前記第 1 の所定のデータと前記第 2 の読み出手段により読み出された前記第 2 の所定のデータとが一致しない場合に、前記情報処理装置を第 1 の起動モードで起動する、ことを特徴とする請求項 1 乃至 4 の何れか 1 項に記載の情報処理装置。

**【請求項 6】**

前記制御手段は、前記チェック処理を実行した結果として、前記複数の記憶手段のそれに記憶された前記特定のデータが互いに一致した場合に、前記情報処理装置を使用可能とする、ことを特徴とする請求項 1 乃至 5 の何れか 1 項に記載の情報処理装置。

**【請求項 7】**

前記制御手段は、前記チェック処理を実行した結果として、前記複数の記憶手段のそれに記憶された前記特定のデータが互いに一致しなかった場合に、エラーを通知する、ことを特徴とする請求項 1 乃至 6 の何れか 1 項に記載の情報処理装置。

**【請求項 8】**

前記第 1 の起動モードは、ブート処理を行う起動モードである、ことを特徴とする請求項 1 乃至 7 の何れか 1 項に記載の情報処理装置。

10

**【請求項 9】**

前記第 2 の起動モードは、ブート処理を行わずに揮発性のメモリに記憶されるデータを使ってレジューム処理を行う起動モードであることを特徴とする請求項 1 乃至 8 の何れか 1 項に記載の情報処理装置。

**【請求項 10】**

前記記憶手段は、不揮発性の記憶媒体である、ことを特徴とする請求項 1 乃至 9 の何れか 1 項に記載の情報処理装置。

20

**【請求項 11】**

画像を形成する画像形成手段を更に有する、ことを特徴とする請求項 1 乃至 10 の何れか 1 項に記載の情報処理装置。

30

**【請求項 12】**

前記制御手段は、前記保持手段により保持された前記第 1 の所定のデータと前記第 2 の読み出手段により読み出された前記第 2 の所定のデータとが一致する場合に、前記チェック処理を実行しない、ことを特徴とする請求項 1 乃至 11 の何れか 1 項に記載の情報処理装置。

**【請求項 13】**

前記複数の記憶手段は、第 1 記憶手段、第 2 記憶手段及び第 3 記憶手段を含み、前記制御手段は、前記チェック処理を実行した結果として、前記第 1 記憶手段と前記第 2 記憶手段とに記憶された前記特定のデータが互いに一致し、前記第 3 記憶手段に記憶されたデータが前記第 1 記憶手段及び前記第 2 記憶手段に記憶された前記特定のデータとは一致しない場合、前記第 1 記憶手段及び前記第 2 記憶手段に記憶された前記特定のデータを前記第 3 記憶手段に記憶する、ことを特徴とする請求項 1 乃至 11 の何れか 1 項に記載の情報処理装置。

40

**【請求項 14】**

起動時に複数の記憶手段のそれぞれに記憶された前記特定のデータの整合性をチェックするチェック処理を実行する第 1 の起動モードと、起動時に前記チェック処理を実行しない第 2 の起動モードと、を含む複数の起動モードの何れかで起動可能な情報処理装置の制御方法であって、

前記複数の記憶手段のそれから第 1 の所定のデータを読み出す第 1 の読み出工程と、前記第 1 の読み出工程で読み出された前記第 1 の所定のデータを保持する保持工程と、

50

前記情報処理装置が前記第2の起動モードで起動する場合に、複数の記憶手段のそれぞれから第2の所定のデータを読み出す第2の読み出工程と、

前記保持工程により保持された前記第1の所定のデータと前記第2の読み出工程により読み出された前記第2の所定のデータとが一致しない場合に、前記チェック処理を実行するよう制御する制御工程と、を有することを特徴とする制御方法。

【請求項15】

起動時に複数の記憶手段のそれぞれに記憶された前記特定のデータの整合性をチェックするチェック処理を実行する第1の起動モードと、起動時に前記チェック処理を実行しない第2の起動モードと、を含む複数の起動モードの何れかで起動可能な情報処理装置を、

前記複数の記憶手段のそれぞれから第1の所定のデータを読み出す第1の読み出手段、前記第1の読み出手段により読み出された前記第1の所定のデータを保持する保持手段、前記情報処理装置が前記第2の起動モードで起動する場合に、前記複数の記憶手段のそれぞれから第2の所定のデータを読み出す第2の読み出手段、及び、前記保持手段により保持された前記第1の所定のデータと前記第2の読み出手段により読み出された前記第2の所定のデータとが一致しない場合に、前記チェック処理を実行するよう制御する制御手段、として機能させるためのプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置、情報処理装置の制御方法及びプログラムに関する。

20

【背景技術】

【0002】

近年、情報処理装置は、多機能化等により、ユーザが電源スイッチをONにしてから実際に使用できるようになるまでに要する時間が長くなっている。

この解決方法の一つとして、特許文献1に記載されているような、サスペンドという技術がある。具体的には、ユーザが電源スイッチをOFFにした際に、シャットダウンを行うのではなく、RAMへの電力供給を継続することでデータを保持しつつ、その他の構成には電力供給を停止する(サスペンド)。そして、次にユーザが電源スイッチをONにした際には、ブートを行うのではなく、停止していた構成への電力供給を再開してから、RAMに保持されていたデータを使用して速やかに復帰する(リジューム)。これにより、ユーザからは電源がOFFになっているように見えつつも、実際には通常よりも高速に起動可能な状態を実現することができる。

30

一方、情報処理装置には、消えてしまうと動作上や運用上の観点から問題となるデータが存在する。例えば、データの信頼性が要求される、セキュリティに関する情報や、課金に関する情報等である。このようなデータを守るため、複数のメモリを用いて多重バックアップ(相互にバックアップし合うこと)を行うことにより、一つのメモリが故障しても、他のメモリからデータを修復することができる技術がある。この技術では、ブート時に、多重バックアップしている領域を全てチェックし、複数のメモリ間のデータの整合性を確認している。

【先行技術文献】

40

【特許文献】

【0003】

【特許文献1】特開2007-293806号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、複数のメモリを用いて多重バックアップを行う情報処理装置に対して、サスペンド機能を適用すると、次のような課題が発生する。すなわち、サスペンド機能において、リジューム時にブートは行わないため、当然のことながら、ブート時に行われる複数のメモリ間のデータの整合性の確認も行われない。このため、例えば、サスペンド状

50

態でユーザがメモリを交換した場合、その後は複数のメモリ間のデータの整合性がとれていらない状態が継続してしまうのである。

#### 【0005】

このような事態を回避するため、レジューム時にも複数のメモリ間のデータの整合性を確認するようにすることが考えられるが、そうすると、サスPEND状態から復帰するのに要する時間が長くなってしまい、レジューム機能を適用した意味が薄れてしまう。

#### 【0006】

本発明は、複数のメモリを用いて多重バックアップを行う情報処理装置に対してサスペンド機能を適用した際に、サスPEND状態でメモリが交換されることで複数のメモリ間のデータの整合性がとれなくなることを検知することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0007】

本発明に係る情報処理装置は、複数の記憶手段のそれぞれで特定のデータを記憶し、前記複数の記憶手段に記憶される前記特定のデータの整合性をチェックするチェック処理を実行する第1の起動モードと、前記チェック処理を実行しない第2の起動モードとを含む複数の起動モードの何れかで起動可能な情報処理装置であって、前記複数の記憶手段のそれぞれから第1の所定のデータを読み出す第1の読出手段と、前記第1の読出手段により読み出された前記第1の所定のデータを保持する保持手段と、前記情報処理装置が前記第2の起動モードで起動する場合に、複数の記憶手段のそれぞれから第2の所定のデータを読み出す第2の読出手段と、前記保持手段により保持された前記第1の所定のデータと前記第2の読出手段により読み出された前記第2の所定のデータとが一致しない場合に、前記チェック処理を実行するよう制御する制御手段と、を有する。

20

#### 【発明の効果】

#### 【0008】

本発明によれば、複数のメモリを用いて多重バックアップを行う情報処理装置に対してサスペンド機能を適用した際に、サスPEND状態でメモリが交換されることで複数のメモリ間のデータの整合性がとれなくなることを検知することが可能となる。

#### 【図面の簡単な説明】

#### 【0009】

【図1】画像形成装置の構成を示すブロック図

30

【図2】N V M E Mにおけるデータの配置例を示す図

【図3】N V M E Mにおけるデータの整合チェックパターンを示す図

【図4】画像形成装置において電源スイッチがONになった際の動作を示すフローチャート

【図5】整合性チェック処理Aの詳細を示すフローチャート

【図6】整合性チェック処理Bの詳細を示すフローチャート

【図7】画像形成装置において電源スイッチがONになった際の動作を示すフローチャート

#### 【発明を実施するための形態】

#### 【0010】

40

以下、本発明の実施形態について、図面を用いて詳細に説明する。

#### 【0011】

なお、以下の説明ではプリンタ等に代表される画像形成装置について説明するが、本発明はP C (パーソナルコンピュータ)等に代表される一般的な情報処理装置等に適用されてもよい。

#### 【0012】

##### 〔第1の実施形態〕

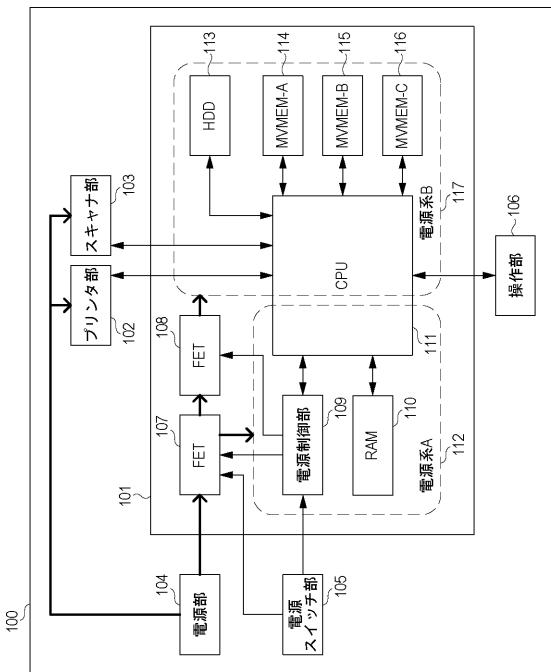

図1は、画像形成装置の構成を示すブロック図である。

#### 【0013】

画像形成装置100は、コントローラ部101、プリンタ部102、スキャナ部103

50

、電源部 104、電源スイッチ部 105、操作部 106 から構成されている。

【0014】

コントローラ部 101 は、デバイス制御 I/F を介してプリンタ部 102、スキャナ部 103 に接続されており、画像形成装置 100 の全体の制御を行う。詳細な構成は、後述する。

【0015】

プリンタ部 102 は、コントローラ部 101 から送信される画像データを印刷用紙にプリントする。

【0016】

スキャナ部 103 は、コントローラ部 101 からスキャン指示を受け付け、スキャン動作を行い、その画像データをコントローラ部 101 に送信する。10

【0017】

電源部 104 は、コントローラ部 101、プリンタ部 102、スキャナ部 103 に対して電力供給を行う。

【0018】

電源スイッチ部 105 は、電力状態の移行要因を監視するものであり、ユーザがこれを ON/OFF することによって、電源 ON/OFF やサスペンド状態への移行 / 復帰を指示することができる。

【0019】

操作部 106 は、LED、液晶ディスプレイ、操作用ボタンなどを備え、ユーザからの操作を受け付け、その操作内容の表示や装置の内部状態の表示を行う。操作部 106 の電力は、コントローラ部 101 経由で供給される。20

【0020】

コントローラ部 101 は、FET 107（半導体スイッチ）、FET 108（半導体スイッチ）、電源制御部 109、RAM 110、CPU 111、電源系 A 112、HDD 113（ハードディスク）から構成されている。また、コントローラ部 101 は、NVMe M-A 114（不揮発性メモリ）、NVMe M-B 115（不揮発性メモリ）、NVMe M-C 116（不揮発性メモリ）から構成されている。

【0021】

FET 107 は、電源部 104 から電力供給を受け、電源スイッチ部 105 からの指示または電源制御部 109 からの指示に従い、電源系 A 112 と FET 108 への電力の供給 / 遮断を行う。30

【0022】

FET 108 は、FET 107 から電力供給を受け、電源制御部 109 からの指示に従い、電源系 B 117 への電力供給 / 遮断を行う。

【0023】

電源制御部 109 は、電源スイッチ部 105 からの指示または CPU 111 からの指示を受け、FET 107、FET 108 の電力供給 / 遮断の指示を行う。また、CPU 111 に電源スイッチ部 105 が操作された等の電源管理に必要な情報を通知する。

【0024】

RAM 110 は、揮発性の記憶媒体であり、CPU 111 が使用するプログラムや画像データ等を一時的に記憶する。

【0025】

CPU 111 は、HDD 113 に内蔵されているコントローラファームの実行媒体であり、各メモリや各 I/F などを介して、コントローラ部 101 に接続されるデバイスの動作を制御する。

【0026】

電源系 A 112 は、電源制御部 109、RAM 110、CPU 111 の一部を含み、画像形成装置 100 の電源管理を行うためサスペンド状態でも電力は供給され続ける。

【0027】

50

HDD113は、磁気ディスクなどの記憶媒体であり、コントローラファームや画像データなどを記憶している。

**【0028】**

NVME-M-A114、NVME-M-B115、NVME-M-C116は、不揮発の記憶媒体であり、画像形成装置100の動作や表示などに必要なデータの中でも特に信頼性が要求されるデータを記憶している。多重バックアップの必要なデータは、同じ内容がNVME-M-A114、NVME-M-B115、NVME-M-C116に保持されている。このような多重バックアップを行うことで一部のNVME-Mの故障や交換があっても、他のNVME-Mから修復を行うことができる。NVME-M-A114、NVME-M-B115、NVME-M-C116は容量や記憶素子などが異なっていてもよい。

10

**【0029】**

電源系B117は、CPU111、HDD113、NVME-M-A114、NVME-M-B115、NVME-M-C116を含み、サスPEND状態で電力は遮断される。

**【0030】**

ここで、画像形成装置100が取り得る電力状態、画像形成装置100が起動可能な起動モードについて説明しておく。

**【0031】**

画像形成装置100の電力状態には、電源ON状態、省電力状態、電源OFF状態が存在する。電源ON状態とは、画像形成装置100の構成のうち、プリント部102、スキヤナ部103、操作部106、電源系A112、電源系B117を含む全ての構成に対して電力供給が行われる電力状態のことである。省電力状態とは、画像形成装置100の構成のうち、電源系A112に対しては電力供給が行われるが、プリント部102、スキヤナ部103、操作部106、電源系B117を含むその他の構成に対しては電力供給が行われない電力状態のことである。電源OFF状態とは、画像形成装置100の構成のうち、プリント部102、スキヤナ部103、操作部106、電源系A112、電源系B117を含む全ての構成に対して電力供給が行われない電力状態のことである。これらの電力状態を消費電力の大きい順に並べると、電源ON状態 > 省電力状態 > 電源OFF状態となる。

20

**【0032】**

画像形成装置100の起動モードには、通常起動モード（第1の起動モード）と高速起動モード（第2の起動モード）が存在する。通常起動モードとは、電源OFF状態で、電源スイッチがONにされ、ブート処理を行って、電源ON状態に移行する起動モードのことである。高速起動モードとは、省電力状態で、電源スイッチがONにされ、ブート処理を行うことなく、電源ON状態に移行する起動モードのことである。これらの起動モードを起動時間の速い順に並べると、高速起動モード > 通常起動モードとなる。

30

**【0033】**

図2は、NVMEMにおけるデータの配置例を示す図である。このような仕組みにより、メモリ内におけるデータの整合チェックを行うことができる。

**【0034】**

ここでは、4バイト単位でデータを保持しており、16バイト単位にブロックを分け、各ブロックでチェックサムを保持している。具体的には、0x0000 ~ 0x000Fが第1のブロック、0x0010 ~ 0x001Fが第2のブロック、0x0020 ~ 0x002Fが第3のブロックというように分けている。

40

**【0035】**

また、第1のブロックは、チェックサム0、データ01、データ02、データ03から構成されており、チェックサム0は0x0004 ~ 0x000Fをバイト単位で加算し、最後に1加算したものである。データ01、データ02、データ03のいずれかの書き込み時、チェックサムも再計算し書き込む。これにより、メモリ単位で、整合チェック時にデータ01、データ02、データ03の値が壊れていないかチェックすることができる。第2のブロック以降も同様の形式である。

50

**【0036】**

図3は、N V M E Mにおけるデータの整合チェックパターンを示す図である。このような方法により、複数のメモリ間におけるデータの整合チェックを行うことができる。

**【0037】**

パターン1は、全N V M E Mの値が”A”であり、整合がとれている状態を示している。そのため、修復処理を行う必要はなく、正常起動する。

**【0038】**

パターン2は、N V M E M - Bの値のみが”B”で異なっており、各メモリの多数決によりN V M E M - Bの値を”A”に修復し、正常起動する。

**【0039】**

パターン3は、N V M E M - Aの値ものが”A”で異なっており、各メモリの多数決によりN V M E M - Aの値を”B”に修復し、正常起動する。

**【0040】**

パターン4は、全N V M E Mの値が異なっており、各メモリの多数決では修復元を決定でないため、操作部106にエラーを表示する。

**【0041】**

パターン5は、N V M E M - Cの値がチェックサムエラーで特定できないことを示している（表中には” ”で表記する）。この場合、N V M E M - A / N V M E M - Bの値は”A”で一致しているため、N V M E M - Cの値を”A”に修復し、正常起動する。

**【0042】**

パターン6は、N V M E M - Cの値がチェックサムエラーで、かつ、N V M E M - AとN V M E M - Bの値が異なるため、修復元を決定できないため、操作部106にエラーを表示する。

**【0043】**

パターン7は、N V M E M - Aのみ値が正常なため、N V M E M - BとN V M E M - Cの値を”A”に修復し、正常起動する。

**【0044】**

パターン8は、全N V M E Mがチェックサムエラーとなっているため、操作部106にエラーを表示する。

**【0045】**

なお、これらのパターンは、代表的なものを示しており、予め整合チェック方法と修復方法が決まっていれば、これ以外の方法を採用してもよい。例えば、今回は単純な多数決による修復方法を例に示したが、各N V M E Mのハード的な信頼度などに応じて重みづけを行ってもよい。

**【0046】**

また、ここではN V M E Mの個数が3つの場合について説明したが、N V M E Mの個数は複数であれば3つ以外であってもよい。

**【0047】**

図4は、画像形成装置において電源スイッチがONになった際の動作を示すフローチャートである。図4の処理は、CPU111が、HDD113に記憶されたプログラムをRAM110に読み出して実行することによって実現される。なお、高速起動モードで起動する際には、プログラムは既にRAM110に保持されているため、プログラムをRAM110からHDD113に読み出す処理は省略される。

**【0048】**

S101において、電源スイッチ部105は、電源がONされたことを検知する。

**【0049】**

S102において、今回の起動が通常起動モードの起動であればS103に進み、今回の起動が高速起動モードの起動であればS108に進む。ここで、通常起動モードとは、電源系A112と電源系B117のどちらにも電力が供給されない電源OFF状態からブート処理を行って起動する起動方法であり、S103～S106に対応する。一方、高速

10

20

30

40

50

起動モードとは、RAM110に保持されたRAMイメージを用いて、電源系A112に電力供給され電源系B117には電力供給ないサスPEND状態からレジューム処理を行つて起動する起動方法であり、S108～S109に対応する。すなわち、S102においては、電源がONされた時の状態が電源OFF状態であればS103に進み、電源がONされた時の状態がサスPEND状態であればS108に進む。

#### 【0050】

S103において、FET107は、電源スイッチ部105からの指示を受け、電源部104から供給されている電力を、電源系A112とFET108に供給する。

#### 【0051】

S104において、電源制御部109は、FET107からの電力供給を受け起動し、

FET107とFET108に電力供給指示を行う。FET107は、すでに電源スイッチ部105から電力供給指示を受けている。しかし、電源制御部109からも電力供給指示を行うことで、FET107が電源スイッチ部105から電力遮断指示を受けても、FET107の電力は遮断されなくなる。そして、電源制御部109からの電力遮断指示も必要となる。これにより、CPU111で電力管理を行うことができるようになる。また、FET108は、電源制御部109から電源供給指示を受けることで、電源系B117に電力供給を行う。

#### 【0052】

S105において、CPU111は、RAMチェック等を含むブート処理を実行する。

#### 【0053】

S106において、CPU111は、HDD113に保存されているコントローラファームをRAM110に読み込み、その展開したプログラムに従い処理を実行し、システム全体を起動させる。

#### 【0054】

S107において、CPU111は、複数のM V M E Mに対して整合チェック処理Aを実行する。整合チェック処理Aの詳細は、図5を用いて後述する。

#### 【0055】

S108において、CPU111は、電源制御部109経由で、FET108に電力供給指示を行う。これを受け、FET108は、電源系Bに電力供給を行う。

#### 【0056】

S109において、CPU111は、サスPEND状態になっているコントローラファームのレジューム処理を実行し、システム全体を起動させる。

#### 【0057】

S107において、CPU111は、複数のM V M E Mに対して整合チェック処理Bを実行する。整合チェック処理Bの詳細は、図6を用いて後述する。

#### 【0058】

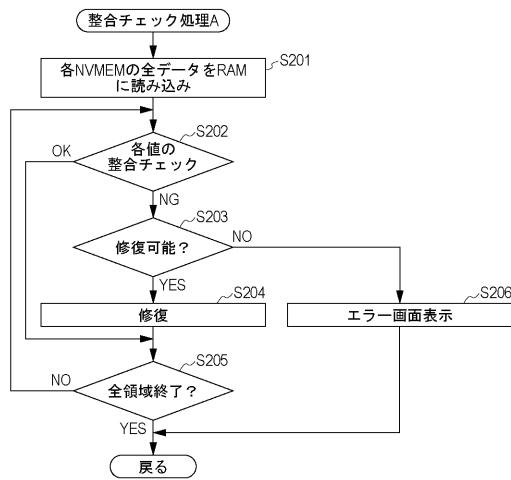

図5は、整合性チェック処理Aの詳細を示すフローチャートである。整合性チェック処理Aとは、通常起動モードで起動した際に複数のM V M E Mに対して行う整合チェック処理方法である。図5の処理は、CPU111が、HDD113に記憶されたプログラムをRAM110に読み出して実行することによって実現される。

#### 【0059】

S201において、CPU111は、各N V M E Mの全データを読出してRAM110に記憶する。なお、この時に読出す各N V M E Mのデータの中には、代表データ（所定のデータ）も含まれる。代表データとは、シリアルナンバーなどの個体情報等のように、前回起動時から今回起動時までの間に変化することのないデータである。代表データは、例えば、各N V M E Mにおいて、図2のデータ01に保持されている。

#### 【0060】

S202において、CPU111は、各N V M E M間のデータの値のチェックを一つずつ行う。このチェック方法は、図3を用いて説明した通りである。S202でOKであれば、S205に進む。S202でNGであれば、S203に進む。

10

20

30

40

50

**【0061】**

S203において、CPU111は、整合がとれなかったデータの修復が可能か否か判断する。S203でYESであれば、S204に進む。S203でNOであれば、S206に進む。

**【0062】**

S204において、CPU111は、S202でチェックした整合のパターンに対応する修復方法でデータの修復処理を行う。整合のパターンと修復処理の対応関係は、図3を用いて説明した通りである。

**【0063】**

S205において、CPU111は、全領域のデータのチェックが完了したか否か判断する。ここで、S205が正常に終了した際に、CPU111は、各NVMEMの代表データをRAM110に保持する。S205でYESであれば、メインフローに戻り、画像形成装置100を使用可能とする。S205でNOであれば、S202に進む。

10

**【0064】**

S206において、CPU111は、操作部106にエラーを表示する。

**【0065】**

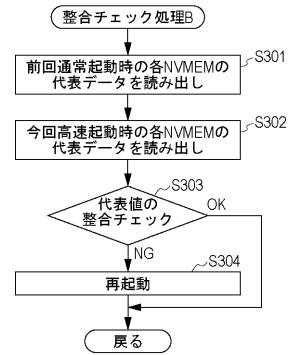

図6は、整合性チェック処理Bの詳細を示すフローチャートである。整合性チェック処理Bとは、高速起動モードで起動した際に複数のNVMEMに対して行う整合チェック処理方法である。図6の処理は、CPU111が、HDD113に記憶されたプログラムをRAM110に読み出して実行することによって実現される。

20

**【0066】**

S301において、CPU111は、RAM110に保持されている各NVMEMの整合チェック済みのデータにアクセスし、前回通常起動時の各NVMEMの代表データを読み出す(第1の読出)。

**【0067】**

S302において、CPU111は、現在接続されている各NVMEMの代表データにアクセスし、今回高速起動時の各NVMEMの代表データを読み出す(第2の読出)。

**【0068】**

S303において、CPU111は、各NVMEMについて、代表データのみを使用して、高速に各NVMEMの整合チェックを行う。具体的には、各NVMEMについて、S301で読み出した前回通常起動時のNVMEMの代表データと、S302で読み出した今回高速起動時のNVMEMの代表データとを比較し、代表データが一致するか否かチェックする。S303でOKであれば、メインフローに戻り、画像形成装置100を使用可能とする。S303でNGであれば、S304に進む。

30

**【0069】**

S304において、CPU111は、再起動を行う。この再起動には、S103～S106で説明した通常起動モードの起動処理と、S107で説明した整合チェックAが含まれる。

**【0070】**

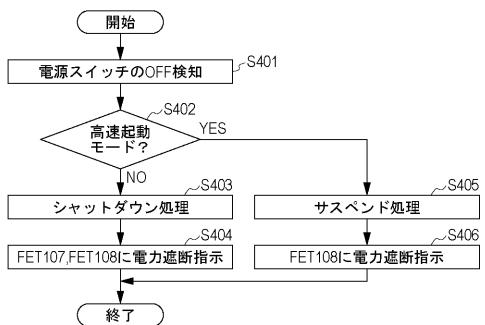

図7は、画像形成装置において電源スイッチがOFFになった際の動作を示すフローチャートである。図7の処理は、CPU111が、HDD113に記憶されたプログラムをRAM110に読み出して実行することによって実現される。図7の処理は、CPU111が、HDD113に記憶されたプログラムをRAM110に読み出して実行することによって実現される。

40

**【0071】**

S401において、CPU111は、電源制御部109経由で、電源スイッチ部105がOFFされたことを検知する。

**【0072】**

S402において、CPU111は、NVMEM-A114に保存されている起動モードを読み込み、高速起動モードが有効になっているか否か判断する。S402でYESで

50

あれば、S405に進む。S402でNOであれば、S403に進む。

【0073】

S403において、CPU111は、画像形成装置100のシャットダウン処理を行う。

【0074】

S404において、CPU111は、電源制御部109経由で、FET107及びFET108に電力遮断指示を行う。これにより、電源系A112及び電源系B117への電力供給が遮断され、画像形成装置100は電源OFF状態となる。

【0075】

S405において、CPU111は、画像形成装置100のサスPEND処理を行う。 10

【0076】

S406において、CPU111は、電源制御部109経由で、FET108に電力遮断指示を行う。これにより、電源系A112への電力供給は継続されつつ、電源系B117への電力供給が遮断され、画像形成装置100はサスPEND状態となる。

【0077】

第1の実施形態によれば、高速起動モードで起動する際に、各メモリについて、前回通常起動時の代表データと今回高速起動時の代表データを比較して、データの整合性のチェックを行う。これにより、複数のメモリを用いて多重バックアップを行う情報処理装置に対してサスPEND機能を適用した際に、サスPEND状態でメモリが交換されることで複数のメモリ間のデータの整合性がとれなくなることを検知することが可能となる。 20

【0078】

〔他の実施形態〕

本発明は、以下の処理を実行することによっても実現される。

【0079】

即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（またはCPUやMPU等）がプログラムを読み出して実行する処理である。

【図1】

【図2】

|        | 0       | 1   | 2   | 3   | 4     | 5   | 6   | 7     | 8   | 9   | A     | B   | C   | D   | E   | F |

|--------|---------|-----|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|-----|-----|---|

| 0x0000 | チェックサム0 |     |     |     | データ01 |     |     | データ02 |     |     | データ03 |     |     |     |     |   |

| 0x0010 | チェックサム1 |     |     |     | データ11 |     |     | データ12 |     |     | データ13 |     |     |     |     |   |

| 0x0020 | チェックサム2 |     |     |     | データ21 |     |     | データ22 |     |     | データ23 |     |     |     |     |   |

| 0x0030 | チェックサム3 |     |     |     | データ31 |     |     | データ32 |     |     | データ33 |     |     |     |     |   |

| 0x0040 | チェックサム4 |     |     |     | データ41 |     |     | データ42 |     |     | データ43 |     |     |     |     |   |

| 0x0050 | チェックサム5 |     |     |     | データ51 |     |     | データ52 |     |     | データ53 |     |     |     |     |   |

| ...    | ...     | ... | ... | ... | ...   | ... | ... | ...   | ... | ... | ...   | ... | ... | ... | ... |   |

【図3】

| パターン  | NVMeM-A<br>の値 | NVMeM-B<br>の値 | NVMeM-C<br>の値 | チェック結果            |

|-------|---------------|---------------|---------------|-------------------|

| パターン1 | A             | A             | A             | 正常起動              |

| パターン2 | A             | B             | A             | NVMeM-Bを値'A'で修復   |

| パターン3 | A             | B             | B             | NVMeM-Aを値'B'で修復   |

| パターン4 | A             | B             | C             | エラー               |

| パターン5 | A             | A             | —             | NVMeM-Cを値'A'で修復   |

| パターン6 | A             | B             | —             | エラー               |

| パターン7 | A             | —             | —             | NVMeM-B/Cを値'A'で修復 |

| パターン8 | —             | —             | —             | エラー               |

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開平10-222430(JP,A)

特開平06-214684(JP,A)

特開平07-093505(JP,A)

特開2001-142839(JP,A)

米国特許出願公開第2006/0282654(US,A1)

特開平11-327706(JP,A)

特開2010-128537(JP,A)

特開2000-322160(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 32

B 41 J 29 / 38

B 41 J 29 / 46