(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5666794号

(P5666794)

(45) 発行日 平成27年2月12日(2015.2.12)

(24) 登録日 平成26年12月19日(2014.12.19)

(51) Int.Cl.

H01L 21/02 (2006.01)

H01L 27/12 (2006.01)

F 1

H01L 27/12

B

請求項の数 7 (全 39 頁)

(21) 出願番号 特願2009-220730 (P2009-220730)

(22) 出願日 平成21年9月25日 (2009.9.25)

(65) 公開番号 特開2010-103515 (P2010-103515A)

(43) 公開日 平成22年5月6日 (2010.5.6)

審査請求日 平成24年9月3日 (2012.9.3)

(31) 優先権主張番号 特願2008-251335 (P2008-251335)

(32) 優先日 平成20年9月29日 (2008.9.29)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 倉田 求

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 笹川 慎也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 村岡 大河

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】 S O I 基板の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に絶縁膜を形成し、

前記絶縁膜を介して前記半導体基板に加速されたイオンを照射することにより、前記半導体基板に脆化領域を形成し、

前記半導体基板上の前記絶縁膜と、ベース基板の表面とを対向させ、前記絶縁膜の表面と前記ベース基板の表面とを接合させ、

热処理を行い、前記脆化領域において分離することにより、前記ベース基板上に前記絶縁膜を介して半導体層を形成し、

前記半導体層にエッティング処理を行って、前記半導体層の表面に形成された自然酸化膜を除去し、 10

前記エッティング処理を行った後、前記半導体層にレーザビームを照射し、前記半導体層を部分的に溶融して、前記半導体層の結晶性を向上させ、

前記レーザビームを照射した後、前記半導体層にプラズマを照射して、前記半導体層表面の平坦性を向上させることを特徴とする S O I 基板の作製方法。

## 【請求項 2】

半導体基板上に絶縁膜を形成し、

前記絶縁膜を介して前記半導体基板に加速されたイオンを照射することにより、前記半導体基板に脆化領域を形成し、

前記半導体基板上の前記絶縁膜と、ベース基板の表面とを対向させ、前記絶縁膜の表面 20

と前記ベース基板の表面とを接合させ、

熱処理を行い、前記脆化領域において分離することにより、前記ベース基板上に前記絶縁膜を介して半導体層を形成し、

前記半導体層に第1のエッチング処理を行って、前記半導体層の表面に形成された自然酸化膜を除去し、

前記第1のエッチング処理を行った後、前記半導体層にレーザビームを照射し、前記半導体層を部分的に溶融して、前記半導体層の結晶性を向上させ、

前記レーザビームを照射した後、前記半導体層に第2のエッチング処理を行って、前記半導体層の膜厚を減少させ、

前記第2のエッチング処理を行った後、前記半導体層にプラズマを照射して、前記半導体層表面の平坦性を向上させることを特徴とするSOI基板の作製方法。 10

#### 【請求項3】

半導体基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜を介して前記半導体基板に加速されたイオンを照射することにより、前記半導体基板に脆化領域を形成し、

ベース基板上に第2の絶縁膜を形成し、

前記半導体基板上の前記第1の絶縁膜と、前記ベース基板上の前記第2の絶縁膜とを対向させ、前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを接合させ、

熱処理を行い、前記脆化領域において分離することにより、前記ベース基板上に前記第1の絶縁膜及び第2の絶縁膜を介して半導体層を形成し、 20

前記半導体層にエッチング処理を行って、前記半導体層の表面に形成された自然酸化膜を除去し、

前記エッチング処理を行った後、前記半導体層にレーザビームを照射し、前記半導体層を部分的に溶融して、前記半導体層の結晶性を向上させ、

前記レーザビームを照射した後、前記半導体層にプラズマを照射して、前記半導体層表面の平坦性を向上させることを特徴とするSOI基板の作製方法。 20

#### 【請求項4】

半導体基板上に第1の絶縁膜を形成し、

前記第1の絶縁膜を介して前記半導体基板に加速されたイオンを照射することにより、前記半導体基板に脆化領域を形成し、 30

ベース基板上に第2の絶縁膜を形成し、

前記半導体基板上の前記第1の絶縁膜と、前記ベース基板上の前記第2の絶縁膜とを対向させ、前記第1の絶縁膜の表面と前記第2の絶縁膜の表面とを接合させ、

熱処理を行い、脆化領域において分離することにより、前記ベース基板上に前記第1の絶縁膜及び第2の絶縁膜を介して半導体層を形成し、

前記半導体層に第1のエッチング処理を行って、前記半導体層の表面に形成された自然酸化膜を除去し、

前記第1のエッチング処理を行った後、前記半導体層にレーザビームを照射し、前記半導体層を部分的に溶融して、前記半導体層の結晶性を向上させ、

前記レーザビームを照射した後、前記半導体層に第2のエッチング処理を行って前記半導体層の膜厚を減少させ、 40

前記第2のエッチング処理を行った後、前記半導体層にプラズマを照射して、前記半導体層表面の平坦性を向上させることを特徴とするSOI基板の作製方法。

#### 【請求項5】

請求項1又は請求項2において、

前記絶縁膜は、熱酸化処理によって形成されることを特徴とするSOI基板の作製方法。 50

#### 【請求項6】

請求項3又は請求項4において、

前記第1の絶縁膜は、熱酸化処理によって形成されることを特徴とするSOI基板の作

製方法。

【請求項 7】

請求項 1 乃至 請求項 6 のいずれか一項において、

前記半導体基板に照射するイオンとして、前記イオンの総量に対して  $H_3^+$  イオンの割合を 80 % 以上とすることを特徴とする SOI 基板の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は絶縁表面に単結晶半導体層が設けられた所謂 SOI (Silicon on Insulator) 構造を有する SOI 基板の製造方法及び SOI 構造を有する半導体装置の作製方法に関する。 10

【背景技術】

【0002】

単結晶半導体のインゴットを薄くスライスして作製されるシリコンウエハに代わり、絶縁表面に薄い単結晶半導体層を設けたシリコン・オン・インシュレータ（以下、「SOI」ともいう）と呼ばれる半導体基板を使った集積回路が開発されている。 SOI 基板を使った集積回路は、トランジスタのドレインと基板間における寄生容量を低減し、半導体集積回路の性能を向上させるものとして注目を集めている。

【0003】

SOI 基板を製造する方法としては、水素イオン注入剥離法が知られている（例えば、特許文献 1 参照。）。水素イオン注入剥離法は、シリコンウエハに水素イオンを注入することによって表面から所定の深さに脆化領域を形成し、別のシリコンウエハと貼り合わせる。次に、熱処理を行うことにより該脆化領域において分離することで、脆化領域が形成されたシリコンウエハと、別のシリコンウエハに薄いシリコン層を形成する。さらに、酸化性雰囲気下での熱処理にシリコン層に酸化膜を形成した後に該酸化膜を除去し、次に 1000 から 1300 で熱処理を行って接合強度を高める必要があるとされている。 20

【0004】

また、このようなスマートカット法を用いて、単結晶シリコン層をガラスからなるベース基板上に形成する方法が提案されている（例えば、特許文献 2 参照）。 30

【0005】

このようにして形成されたシリコン層は、脆化領域を形成するために行うイオン照射工程や、分離工程により、シリコン層の内部及び表面には結晶欠陥が残存し、表面の平坦性が著しく劣化した状態となっている。また、脆化領域における分離がスムーズに行われないと、シリコン層の表面が荒れたり、シリコン層の膜厚がばらついたり、シリコン層に微細なクラックが生じるといった問題が生じる。

【0006】

シリコン層の結晶欠陥の除去は、1000 以上の温度で加熱することで実現できるが、歪み点が 700 以下のガラス基板に貼り付けられたシリコン層の結晶欠陥の除去には、このような高温プロセスは用いることができない。そこで、特許文献 3 に示されるように、シリコン層にレーザビームを照射することで、シリコン層を再結晶化させてシリコン層の結晶品質を高める試みがなされている（特許文献 3）。 40

【先行技術文献】

【特許文献】

【0007】

【特許文献 1】特開 2000 - 124092 号公報

【特許文献 2】特開 2002 - 170942 号公報

【特許文献 3】特開 2005 - 252244 号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、単結晶シリコン基板を分離した後のシリコン層の表面には結晶欠陥や、分離の際に生じるダメージが残存している。このような状態で、単結晶シリコン層の結晶欠陥を除去するために、レーザを照射することで、シリコン層の表面から結晶欠陥やダメージが単結晶シリコン層内部に取り込まれてしまうという問題がある。また、シリコン層を溶融させて再結晶化させる際に、シリコン層の表面に凹凸が生じるという問題がある。

#### 【0009】

このような問題点に鑑み、ガラス基板のような耐熱性が低く、かつ撓みやすい基板をベース基板に用いても、ベース基板に固定された単結晶半導体層の平坦性の向上、および結晶性が向上したSOI基板の作製方法を提供することを課題の一とする。また、そのようなSOI基板を用いた半導体装置の作製方法を提供することを課題の一つとする。

10

#### 【課題を解決するための手段】

#### 【0010】

本発明に係るSOI基板の作製方法は、ベース基板に接着された単結晶半導体層の表面に対してエッティング処理を行い、単結晶半導体層の表面にレーザビームを照射し、単結晶半導体層の表面にプラズマ処理をすることを特徴としている。以下に、本発明の具体的な構成について説明する。

#### 【0011】

本発明の一態様は、半導体基板上に絶縁膜を形成し、絶縁膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板に脆化領域を形成し、半導体基板の表面とベース基板の表面とを対向させ、絶縁膜の表面とベース基板の表面とを接合させ、絶縁膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域において分離することにより、ベース基板上に絶縁膜を介して半導体層を形成し、半導体層にエッティング処理を行い、エッティング処理が行われた半導体層にレーザビームを照射し、レーザビームが照射された半導体層にプラズマを照射することを含む。

20

#### 【0012】

本発明の一態様は、半導体基板上に絶縁膜を形成し、絶縁膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板に脆化領域を形成し、半導体基板の表面とベース基板の表面とを対向させ、絶縁膜の表面とベース基板の表面とを接合させ、絶縁膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域において分離することにより、ベース基板上に絶縁膜を介して半導体層を形成し、半導体層に第1のエッティング処理を行い、第1のエッティング処理が行われた半導体層にレーザビームを照射し、レーザビームが照射された半導体層に第2のエッティング処理を行い、第2のエッティング処理が行われた半導体層にプラズマを照射することを含む。

30

#### 【0013】

なお、本明細書において単結晶とは、ある結晶軸に注目した場合、その結晶軸の方向が試料のどの部分においても同じ方向を向いている結晶のことをいい、かつ結晶と結晶との間に結晶粒界が存在しない結晶である。なお、本明細書では、結晶欠陥やダンギリグボンドを含んでいても、上記のように結晶軸の方向が揃っており、粒界が存在していない結晶であるものは単結晶とする。また、単結晶半導体層の再単結晶化とは、単結晶構造の半導体層が、その単結晶構造と異なる状態（例えば、液相状態）を経て、再び単結晶構造になることをいう。あるいは、単結晶半導体層の再単結晶化とは、単結晶半導体層を再結晶化して、単結晶半導体層を形成するということもできる。

40

#### 【0014】

本明細書において、脆化領域とは、単結晶半導体基板ヘイオンビームを照射し、イオンにより結晶欠陥を有するように脆弱化された領域である。この脆化領域を、熱処理によって亀裂を生じさせるなどにより分割することで、単結晶半導体基板より単結晶半導体層を分離することができる。

#### 【0015】

本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、表示装置、半導体回路及び電子機器は全て半導体装置である。

50

## 【0016】

また、本明細書において表示装置とは、液晶表示装置や発光装置含む。液晶表示装置は液晶素子を含み、発光装置は発光素子を含む。発光素子は、電流又は電圧によって輝度が抑制される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)素子、有機EL素子等が含まれる。

## 【発明の効果】

## 【0017】

本発明を適用することで、耐熱性の低い支持基板を用いた場合であっても、結晶欠陥を減少させ、平坦性を高めることができる。また、このようなSOI基板を用いて、優れた特性の半導体装置を作製することができる。

10

## 【図面の簡単な説明】

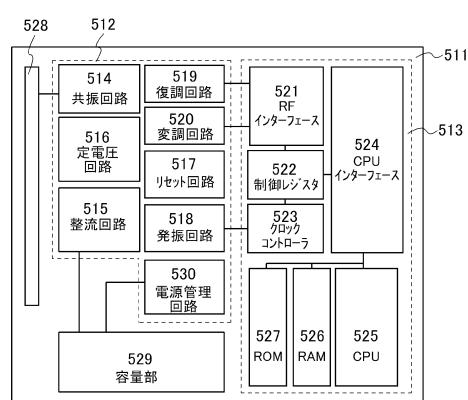

## 【0018】

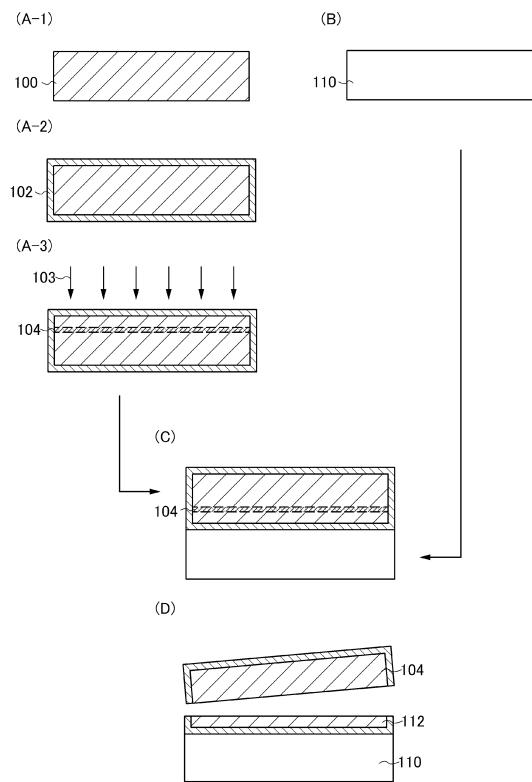

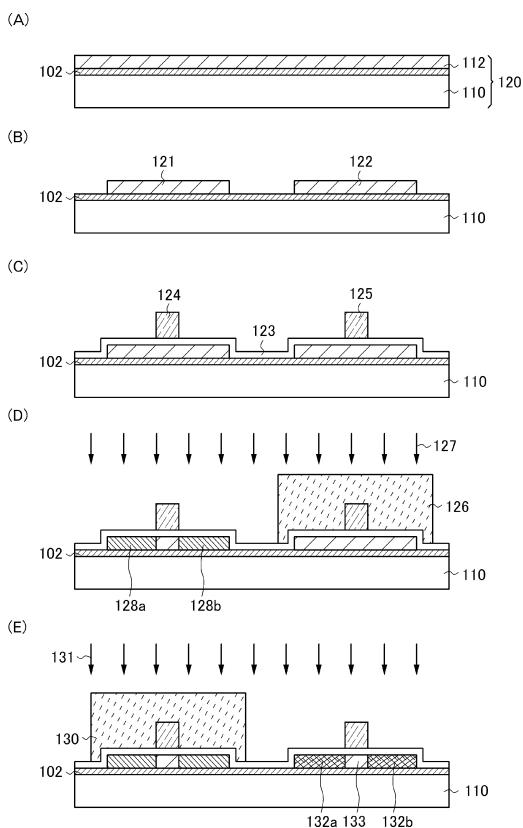

【図1】本発明に係るSOI基板の作製方法の一例を示す図。

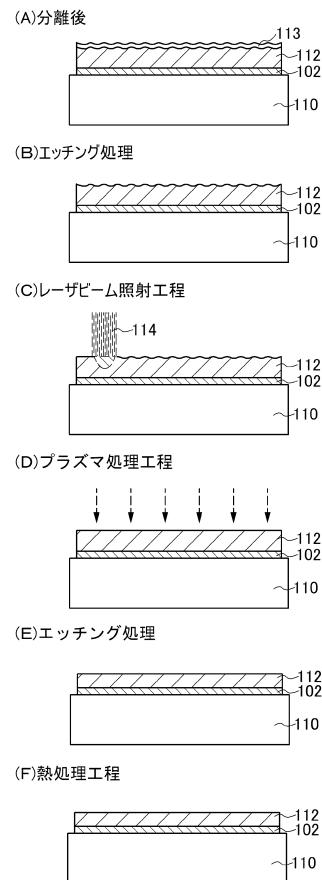

【図2】本発明に係るSOI基板の作製方法の一例を示す図。

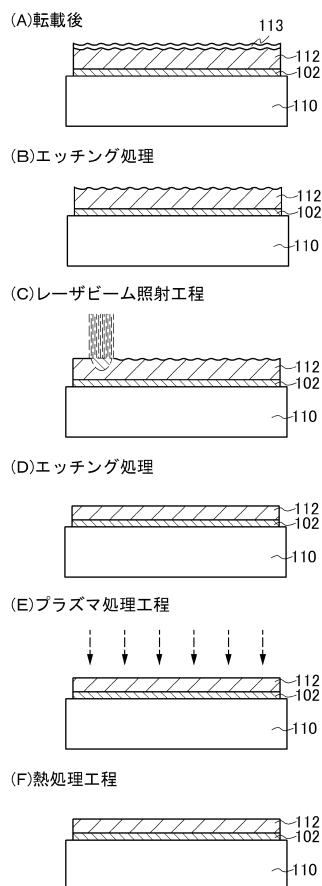

【図3】本発明に係るSOI基板の作製方法の一例を示す図。

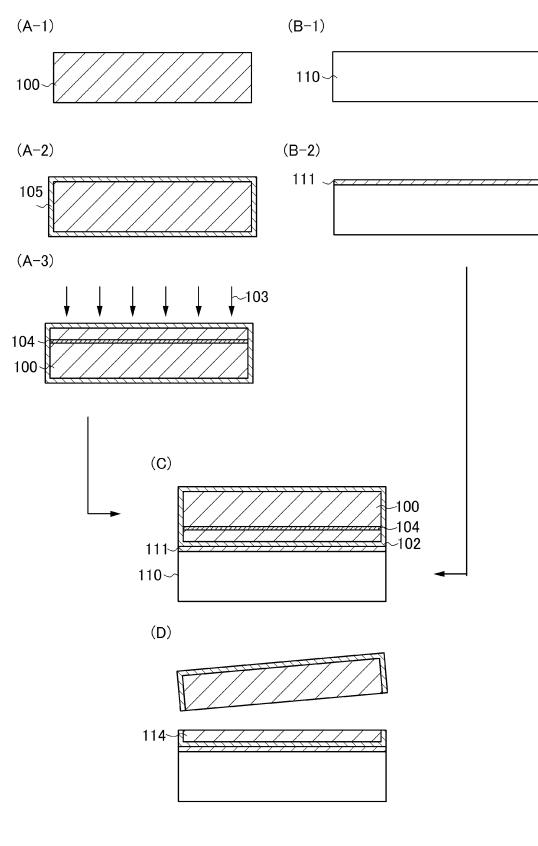

【図4】本発明に係るSOI基板の作製方法の一例を示す図。

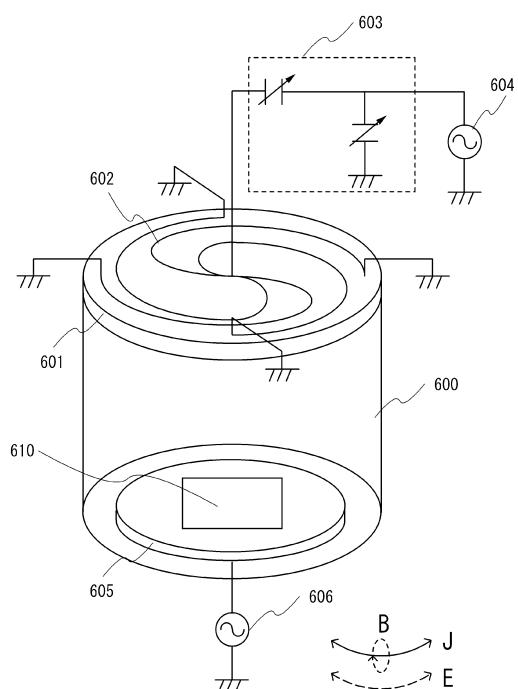

【図5】本発明に係るSOI基板の作製方法におけるプラズマ処理の一例を説明する図。

【図6】本発明に係るSOI基板を用いた半導体装置の一例を示す図。

【図7】本発明に係るSOI基板を用いた半導体装置の一例を示す図。

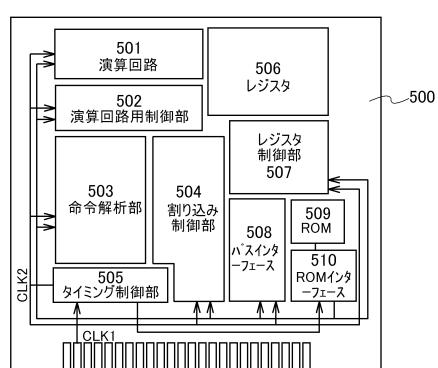

【図8】本発明に係るSOI基板により得られるマイクロプロセッサの構成を示すプロック図。

20

【図9】本発明に係るSOI基板により得られるRFCPUの構成を示すプロック図。

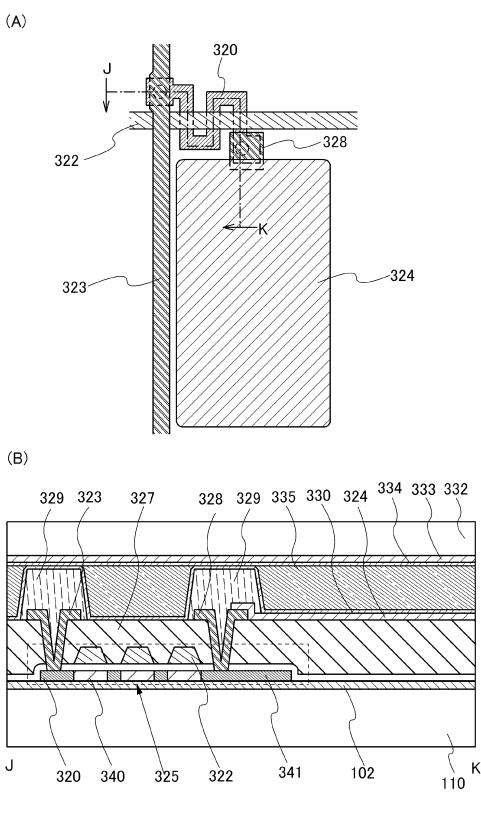

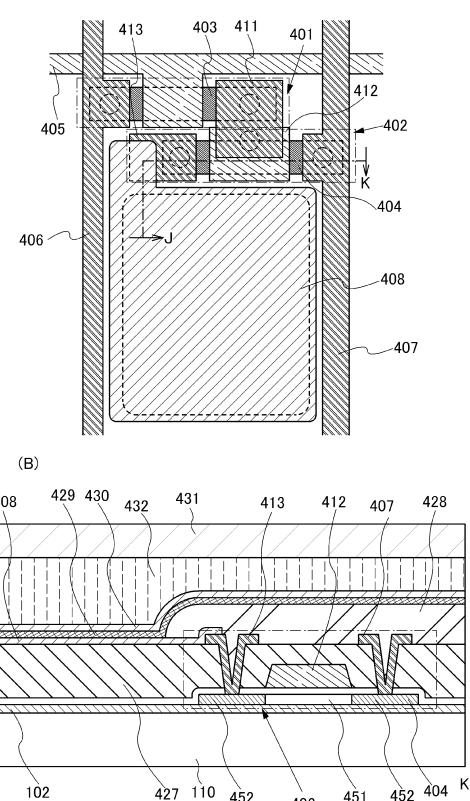

【図10】(A) 液晶表示装置の画素の平面図。(B) J-K切断線による図10(A)の断面図。

【図11】(A) エレクトロルミネセンス表示装置の画素の平面図。(B) J-K切断線による図11(A)の断面図。

【図12】本発明に係るSOI基板を用いた電子機器を示す図。

【図13】本発明に係るSOI基板を用いた携帯電話を示す図。

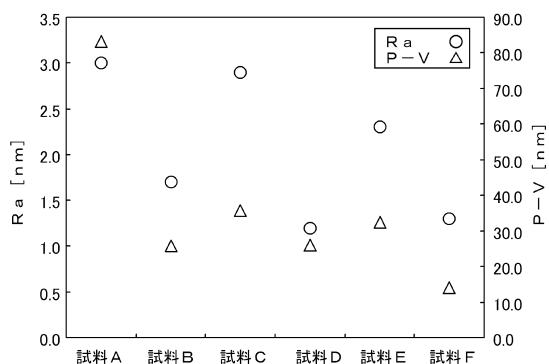

【図14】単結晶シリコン層の表面粗さを測定した結果を示す図。

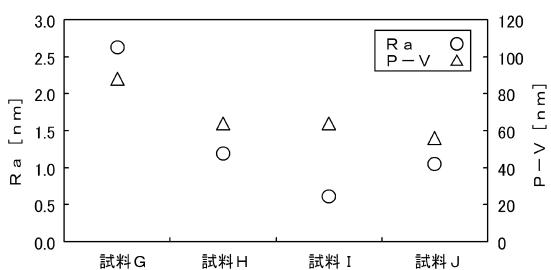

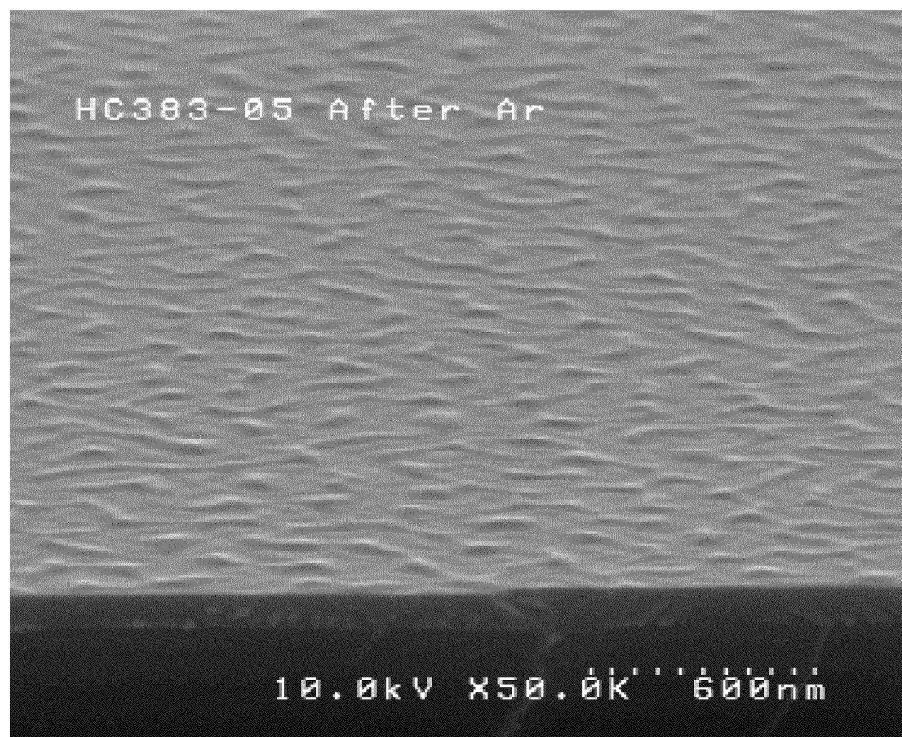

【図15】表面SEM像を示す図。

30

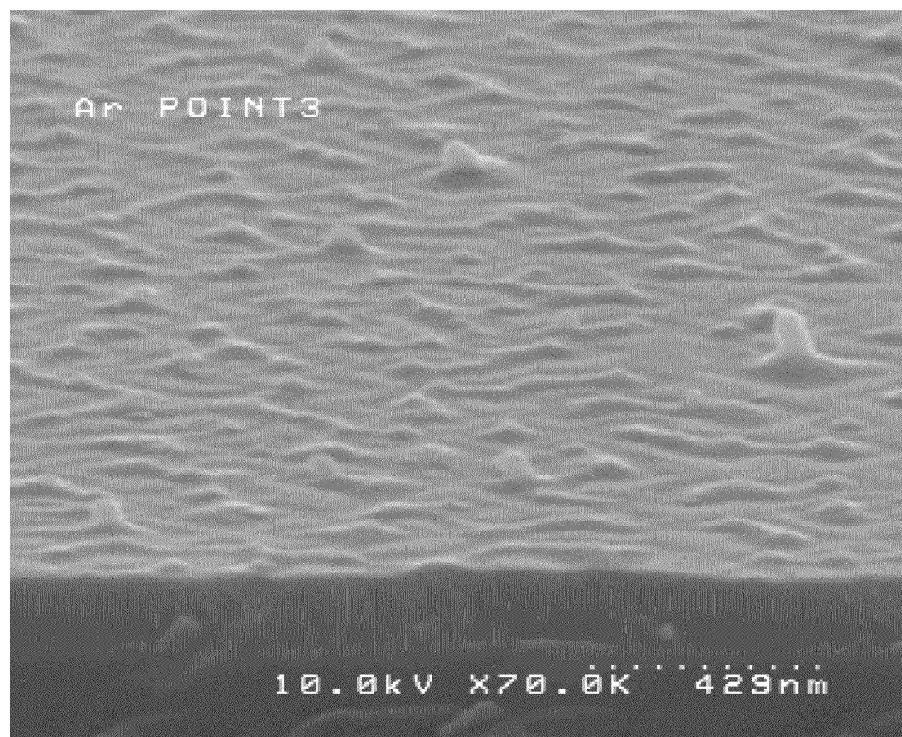

【図16】単結晶シリコン層の表面粗さを測定した結果を示す図。

## 【発明を実施するための形態】

## 【0019】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

## 【0020】

40

## (実施の形態1)

本実施の形態では、SOI基板の作製方法の一例に関して図面を参照して説明する。具体的には、ベース基板上に絶縁層を介して単結晶半導体層を形成し、当該単結晶半導体層の平坦性を向上させる工程に関して説明する。

## 【0021】

まず、単結晶半導体基板100とベース基板110とを準備する(図1(A-1)、(B)参照)。

## 【0022】

単結晶半導体基板100として、例えば、単結晶シリコン基板、単結晶ゲルマニウム基板、単結晶シリコンゲルマニウム基板など、第14族元素である単結晶半導体基板を用い

50

ることができる。また、ガリウムヒ素やインジウムリン等の化合物半導体基板も用いることができる。市販のシリコン基板としては、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)、直径16インチ(400mm)サイズの円形のものが代表的である。なお、単結晶半導体基板100の形状は円形に限られず、例えば、矩形状等に加工して用いることも可能である。また、単結晶半導体基板100は、CZ(チョクラルスキー)法やFZ(フローティングゾーン)法を用いて作製することができる。以下の説明では、単結晶半導体基板100として、CZ法を用いて作製された単結晶シリコン基板を用いる場合について示す。

#### 【0023】

ベース基板110として、絶縁体でなる基板を用いることができる。具体的には、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板が挙げられる。他にも、ベース基板110として単結晶半導体基板(例えば、単結晶シリコン基板等)を用いてもよい。本実施の形態では、ガラス基板を用いる場合について説明する。ベース基板110として大面積化が可能で安価なガラス基板を用いることにより、低コスト化を図ることができる。

#### 【0024】

次に、単結晶半導体基板100上に絶縁膜102を形成する(図1(A-2)参照)。絶縁膜102は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜等の絶縁層を単層又は積層させて形成することができる。これらの膜は、熱酸化法、CVD法又はスパッタリング法等を用いて形成することができる。

#### 【0025】

本明細書中において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50~70原子%、窒素が0.5~15原子%、シリコンが25~35原子%、水素が0.1~10原子%の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5~30原子%、窒素が20~55原子%、シリコンが25~35原子%、水素が10~30原子%の範囲で含まれるものという。ただし、酸化窒化シリコン又は窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

#### 【0026】

次に、絶縁膜を介して単結晶半導体基板にイオンを照射することにより、単結晶半導体基板100に脆化領域104を形成する(図1(A-3)参照)。脆化領域104は、運動エネルギーを有する水素等のイオンを単結晶半導体基板100に照射することにより形成することができる。

#### 【0027】

次に、絶縁膜102を介して単結晶半導体基板100とベース基板110とを貼り合わせる(接合するともいう)(図1(C)参照)。その後、熱処理を行い、前記脆化領域において分離(劈開)することにより、ベース基板110上に絶縁膜102を介して単結晶半導体層112を設ける(図1(D)参照)。なお、熱処理は、ベース基板110の歪点以下の温度で行うことが好ましい。

#### 【0028】

加熱処理を行うことで、温度上昇によって脆化領域104に形成されている微小な孔において内部の圧力が上昇する。圧力の上昇により、脆化領域104に沿って単結晶半導体基板100が分離する。絶縁膜102はベース基板110に接合しているので、ベース基板110上には単結晶半導体基板100から分離された単結晶半導体層112が形成され

10

20

30

40

50

る。

#### 【0029】

一般的に、劈開後におけるベース基板110上に形成された単結晶半導体層112の表層部には、脆化領域104の形成及び脆化領域における分離により、結晶欠陥等が形成され、平坦性が劣化した状態となっている(図2(A)参照)。また、単結晶半導体層112の表層部に、自然酸化膜113が形成される。自然酸化膜113の表面は汚染物が付着している。そこで、単結晶半導体層112の表面に形成された自然酸化膜113及び単結晶半導体層112の表層部に残存する結晶欠陥等を除去する(図2(B)参照)。

#### 【0030】

自然酸化膜113及び単結晶半導体層112の表層部に残存する結晶欠陥等の除去は、エッティング処理により行う。エッティング処理としては、ドライエッティング、ウェットエッティング、又は両者を組み合わせて行う。また、エッティング処理の代わりにCMP等の研磨処理を行ってもよい。なお、ここでのエッティング処理を第1のエッティング処理とも記す。

#### 【0031】

自然酸化膜113及び単結晶半導体層112のエッティング処理方法は、例えば、反応性イオンエッティング(RIE:Reactive Ion Etching)法、ICP(Inductively Coupled Plasma)エッティング法、ECR(Electron Cyclotron Resonance)エッティング法、平行平板型(容量結合型)エッティング法、マグネットロンプラズマエッティング法、2周波プラズマエッティング法またはヘリコン波プラズマエッティング法等を用いることができる。エッティングガスは、例えば、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>等の塩素系のガス、CHF<sub>3</sub>、CF<sub>4</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>2</sub>F<sub>6</sub>、NF<sub>3</sub>、フッ化硫黄等のフッ素系のガス、HBr等の臭素系のガスを用いることによりエッティングすることが可能である。その他、HeやArやXeなどの不活性ガス、又はO<sub>2</sub>ガス、H<sub>2</sub>ガスを用いることができる。なお、エッティング処理は、複数回に分けて行ってもよい。単結晶半導体層112に存在する欠陥の大きさや深さは、イオンを添加するエネルギーの大きさやドーズ量に起因するため、エッティング処理によって単結晶半導体層112の表面を除去する膜厚は、エッティング処理前の単結晶半導体層112の膜厚とその表面粗さの程度によって適宜設定すればよい。

#### 【0032】

このようにして、ベース基板110上に形成された単結晶半導体層112の表層部を除去することにより、単結晶半導体層112の結晶欠陥等の除去、平坦化を図ることができる。

#### 【0033】

次に、表層部が除去された単結晶半導体層112にレーザビーム114を照射する(図2(C)参照)。単結晶半導体層112の内部には、脆化領域104形成のためのイオン照射工程によって結晶欠陥が形成されている。単結晶半導体層112の分離面側から、または、ベース基板110側からレーザビーム114を照射することで、単結晶半導体層112を溶融させ、結晶性の改善および平坦性の向上を図る。単結晶半導体層112にレーザビーム114を照射することで、単結晶半導体層112を部分溶融又は完全溶融させる。

#### 【0034】

好ましくは、レーザビーム114の照射により、単結晶半導体層112を部分溶融させる。単結晶半導体層を部分溶融させることで、溶融されていない固相部分から結晶成長が進行するため、結晶性を低下させることなく、結晶欠陥を修復することができる。なお、本明細書において、部分溶融とは、単結晶半導体層の一部(例えば、上層部分)は溶融されて液相状態となるが、その他(例えば、下層部分)は溶融せずに固相状態のままであることをいう。また、完全溶融とは、単結晶半導体層が下部界面付近まで溶融されて、液相状態になることをいう。

#### 【0035】

レーザビーム114の照射により単結晶半導体層112を部分溶融させながら、単結晶

10

20

30

40

50

半導体層 112 に対してレーザビーム 114 を走査することで、溶融されていない固相部分から結晶成長が進行する。これにより、単結晶半導体層 112 の結晶欠陥が減少し、結晶性が向上する。溶融されていない部分は、単結晶であり、結晶方位が揃っているため、結晶粒界が形成されず、レーザビーム 114 照射後の単結晶半導体層 112 は、結晶粒界のない単結晶半導体層とすることができます。また、溶融された領域は凝固することで再単結晶化するが、隣接している溶融していない部分の単結晶半導体と結晶方位が揃った単結晶半導体が形成される。よって、主表面の面方位が (100) の単結晶シリコンを単結晶半導体基板 100 として用いた場合、単結晶半導体層 112 の主表面の面方位は (100) であり、レーザビーム 114 照射によって溶融し、再単結晶化された単結晶半導体層 112 の主表面の面方位 (100) になる。なお、レーザビーム 114 照射の代わりに R T A やフラッシュランプ照射を行ってもよい。

#### 【0036】

このように、単結晶半導体層の分離面の表層部を除去した後に、レーザビーム 114 を照射することで、単結晶半導体層に結晶欠陥や汚染物等が取り込まれてしまうことを防ぐことができる。また、自然酸化膜を除去することによって、レーザビーム 114 の照射による表面荒れを防ぐことができる。

#### 【0037】

次に、単結晶半導体層 112 の平坦化のためにプラズマ処理を行う（図 2 (D) 参照）。

#### 【0038】

ここでは、真空状態のチャンバーに不活性ガス（例えば、Ar ガス）を導入し、被処理面（ここでは、単結晶半導体層 112）にバイアス電圧を印加してプラズマ状態として行う。プラズマ中には電子と Ar の陽イオンが存在し、陰極方向（単結晶半導体層 112 側）に Ar の陽イオンが加速される。加速された Ar の陽イオンが単結晶半導体層 112 表面に衝突することによって、単結晶半導体層 112 表面がスパッタエッチングされる。このとき、単結晶半導体層 112 表面の凸部から優先的にスパッタエッチングされ、当該単結晶半導体層 112 表面の平坦性を向上させることができる。また、加速された Ar の陽イオンによって、単結晶半導体層 112 表面の有機物等の不純物を除去することができる。また、真空状態のチャンバーに不活性ガスに加えて、反応性ガス（例えば、O<sub>2</sub> ガス、N<sub>2</sub> ガス）を導入し被処理面にバイアス電圧を印加してプラズマ状態として行うこともできる。反応性ガスを導入する場合、単結晶半導体層 112 表面がスパッタエッチングされることにより生じる欠損を補修することができる。

#### 【0039】

本実施の形態では、アルゴンガスを用いて、誘導結合プラズマ（ICP：Inductively Coupled Plasma）方式のプラズマ処理で行う。図 5 に、プラズマ処理装置の簡略構造図を示す。チャンバー 600 上部の石英板 601 上にマルチスピライラルコイル 602 を配置し、マッチングボックス 603 を介して RF 電源 604 に接続されている。また、対向に配置された基板 610（ここでは、ベース基板上に形成された単結晶半導体層 112）側の下部電極 605 は RF 電源 606 に接続されている。基板 610 上方のマルチスピライラルコイル 602 に RF 電流が印加されると、マルチスピライラルコイル 602 に RF 電流 J が X 方向に流れ、Z 方向に磁界 B が発生する。なお、式中  $\mu_0$  は磁化率である。

#### 【0040】

#### 【数 1】

$$\mu_0 J = r_o t B$$

#### 【0041】

ファラデーの電磁誘導の法則に従い、X 方向に誘導電界 E が生じる。

## 【数2】

$$-\frac{\partial B}{\partial t} = \text{rot } E$$

## 【0042】

この誘導電界Eで電子が 方向に加速され、ガス分子と衝突し、プラズマが生成される。基板610側には、磁界Bがほとんどないので、電極間でシート状に広がった高密度のプラズマ領域が得られる。基板610側に印加するバイアス電圧により、陽イオンが加速されて基板610に衝突する。

## 【0043】

このようにして、プラズマ処理を行うことにより、単結晶半導体層表面の平均面粗さ( $R_a$ )及び最大高低差( $P-V$ )を低減させることができる。

## 【0044】

プラズマ処理の具体的な条件は、Arガスを用いて、ICP電力100～3000W、圧力0.1～5.0Pa、ガス流量5～300sccm、RFバイアス電圧75～300Wで行えばよい。より具体的には、ICP電力500W(0.11W/cm<sup>2</sup>)、圧力1.35Pa、ガス流量100sccm、RFバイアス電圧100W(0.61W/cm<sup>2</sup>)で行えばよい。

## 【0045】

ここで、単結晶半導体層112を薄膜化するための薄膜化工程を行ってもよい(図2(D)参照)。薄膜化工程を行うことによって、後に形成される半導体素子にとって最適となる膜厚とすることができます。また、単結晶半導体層112にプラズマ処理によるプラズマダメージが与えられたとしても、薄膜化工程を行うことによってプラズマダメージを除去することができる。単結晶半導体層112を薄膜化するには、第1のエッチング処理(図2(B)参照)と同様にして行うことができる。例えば、単結晶半導体層112がシリコンの場合、SF<sub>6</sub>とO<sub>2</sub>をプロセスガスに用いたドライエッチングで、単結晶半導体層112を薄膜化することができる。このエッチングにより、単結晶半導体層の膜厚は5nm以上100nm以下とすることが好ましく、5nm以上50nm以下がより好ましい。なお、ここでのエッチング処理を第2のエッティング処理とも記す。

## 【0046】

薄膜化処理を行った後、単結晶半導体層112に500以上700以下の加熱処理を行うことが好ましい。この加熱処理によって、レーザビーム114の照射で除去されなかった単結晶半導体層112の結晶欠陥の消滅、単結晶半導体層112の歪みの緩和をすることができる。この加熱処理には、RTA(Rapid Thermal Anneal)装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA装置には、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置を用いることができる。例えば、抵抗加熱炉を用いた場合は、550で4時間加熱するとよい。

## 【0047】

以上の工程により、SOI基板を作製することができる。

## 【0048】

以上の工程により、ベース基板110上に絶縁膜102を介して単結晶半導体層112が設けられたSOI基板を作製することができる。本実施の形態で示した作製方法を用いることによって、結晶欠陥が低減され、かつ平坦性の良好な単結晶半導体層112を有する半導体基板を提供することができる。このSOI基板を用いることで、特性の優れた半導体素子を形成することができる。

## 【0049】

なお、図2においては、レーザ照射後にプラズマ処理を行う場合について説明したが、本発明はこれに限定されない。例えば、図3の示す方法を用いることもできる。

## 【0050】

10

20

30

40

50

図3は、レーザ照射後に薄膜化工程（第2のエッチング処理）を行い、薄膜化工程を行った後にプラズマ処理を行った場合について示している。

#### 【0051】

図3(A)に、ベース基板110上に単結晶半導体基板100から分離された単結晶半導体層112を示す。図3(B)に示すように単結晶半導体層112にエッチング処理を行い、図3(C)に示すように、エッチング処理が行われた単結晶半導体層112にレーザビームを照射する。図3(B)、(C)の工程は、図2(B)、(C)の工程と同様にして行うことができるため、詳細な説明は省略する。

#### 【0052】

次に、単結晶半導体層112に薄膜化工程を行い(図3(D)参照)、薄膜化工程が行われた単結晶半導体層112にプラズマ処理を行う(図3(E)参照)。さらに、プラズマ処理が行われた単結晶半導体層112に熱処理を行っても良い(図3(F)参照)。熱処理は、図2(F)と同様にして行うことができる。図3(D)の薄膜化工程は図2(E)と、図3(E)のプラズマ処理工程は図2(D)と、図3(F)の熱処理工程は図2(F)とそれぞれ同様にして行うことができるため、詳細な説明は省略する。

10

#### 【0053】

薄膜化工程の後にプラズマ処理を行うことによって、単結晶半導体層112に存在する凹凸を平坦化することができる。また、プラズマ処理によるプラズマダメージが与えられたとしても、プラズマ処理の後に行う熱処理によって、プラズマダメージを回復させることができる。

20

#### 【0054】

このように、本発明を適用することで、耐熱性の低い支持基板を用いた場合であっても、単結晶半導体層の結晶欠陥を減少させ、平坦性を高めることができる。

#### 【0055】

なお、本実施の形態で示した構成は、本明細書の他の実施の形態で示す構成と適宜組み合わせて行うことができる。

#### 【0056】

##### (実施の形態2)

本実施の形態では、単結晶半導体基板100と、ベース基板110との貼り合わせに関して図面を参照して詳細に説明する。

30

#### 【0057】

まず、単結晶半導体基板100を準備する(図4(A-1)参照)。単結晶半導体基板100の表面は、あらかじめ硫酸過酸化水素水混合溶液(SPM)、アンモニア過水(APM: ammonium hydroxide / hydrogen peroxide mixture)、塩酸過酸化水素水混合溶液(HPM: hydrochloric acid / hydrogen peroxide mixture)、希フッ酸(DHF: dilute hydrofluoric acid)などを用いて適宜洗浄することが汚染除去の点から好ましい。また、希フッ酸とオゾン水を交互に吐出して洗浄してもよい。

#### 【0058】

40

次に、単結晶半導体基板100の表面に酸化膜105を形成する(図4(A-2)参照)。酸化膜105は、例えば、酸化シリコン膜、酸化窒化シリコン膜等の単層、又はこれらを積層させた膜を用いることができる。これらの膜は、熱酸化法、CVD法又はスパッタリング法等を用いて形成することができる。また、また、CVD法を用いて酸化膜105を形成する場合には、テトラエトキシシラン(略称; TEOS: 化学式Si(OCH<sub>3</sub>)<sub>4</sub>)等の有機シランを用いて作製される酸化シリコン膜を酸化膜105に用いることが生産性の点から好ましい。

#### 【0059】

本実施の形態では、単結晶半導体基板100に熱酸化処理を行うことにより酸化膜105(ここでは、SiO<sub>x</sub>膜)を形成する(図4(A-2)参照)。熱酸化処理は、酸化性

50

雰囲気中にハロゲンを添加して行うことが好ましい。

#### 【0060】

例えば、塩素（C1）が添加された酸化性雰囲気中で単結晶半導体基板100に熱酸化処理を行うことにより酸化膜105を形成する。この場合、酸化膜105は、塩素原子を含有した膜となる。

#### 【0061】

酸化膜105中に含有された塩素原子は、歪みを形成する。その結果、酸化膜105の水分に対する吸収割合が向上し、拡散速度が増大する。つまり、酸化膜105表面に水分が存在する場合に、当該表面に存在する水分を酸化膜105中にすばやく吸収し、拡散させることができる。

10

#### 【0062】

熱酸化処理の一例としては、酸素に対し塩化水素（HCl）を0.5～10体積%（好ましくは2体積%）の割合で含む酸化性雰囲気中で、900～1150（好ましくは1000）で行うことができる。処理時間は、0.1～6時間、好ましくは0.5～1時間とすればよい。形成される酸化膜としては、10nm～1000nm（好ましくは50nm～300nm）、例えば、100nmの厚さとする。

#### 【0063】

本実施の形態では、酸化膜105に含まれる塩素原子の濃度を $1 \times 10^{17}$ atoms/cm<sup>3</sup>～ $1 \times 10^{21}$ atoms/cm<sup>3</sup>となるように制御する。酸化膜105に塩素原子を含有させることによって、外因性不純物である重金属（例えば、Fe、Cr、Ni、Mo等）を捕集して単結晶半導体基板100が汚染されることを防止する効果を奏する。

20

#### 【0064】

酸化膜105として、HCl酸化などによって膜中に塩素等のハロゲンを含ませることにより、単結晶半導体基板100に悪影響を与える不純物（例えば、Na等の可動イオン）をゲッタリングすることができる。つまり、酸化膜105を形成した後に行われる熱処理により、単結晶半導体基板に含まれる不純物が酸化膜105に析出し、ハロゲン（例えば塩素）と反応して捕獲されることとなる。それにより酸化膜105中に捕集した当該不純物を固定して単結晶半導体基板100の汚染を防ぐことができる。また、酸化膜105はガラス基板と貼り合わせた場合に、ガラスに含まれるNa等の不純物を固定する膜として機能する。

30

#### 【0065】

特に、酸化膜105として、HCl酸化などによって膜中に塩素等のハロゲンを含ませることは、半導体基板の洗浄が不十分である場合や、繰り返し再利用して用いられる半導体基板の汚染除去に有効となる。

#### 【0066】

また、酸化膜105に含有させるハロゲン原子としては塩素原子に限られない。酸化膜105にフッ素原子を含有させてもよい。単結晶半導体基板100の表面をフッ素酸化するには、単結晶半導体基板100表面にDHF溶液に浸漬した後に酸化性雰囲気中で熱酸化処理を行うことや、NF<sub>3</sub>を酸化性雰囲気に添加して熱酸化処理を行えばよい。

40

#### 【0067】

次に、運動エネルギーを有するイオンを単結晶半導体基板100に照射することで、単結晶半導体基板100の所定の深さに結晶構造が損傷された脆化領域104を形成する（図4（A-3）参照）。図4（A-3）に示すように、酸化膜105を介して、加速されたイオン103を単結晶半導体基板100に照射することで、単結晶半導体基板100の表面から所定の深さの領域にイオン103が添加され、脆化領域104を形成することができる。イオン103は、ソースガスを励起して、ソースガスのプラズマから引き出して、加速したイオンである。

#### 【0068】

脆化領域104が形成される領域の深さは、イオン103の運動エネルギー、質量と電

50

荷、イオン 103 の入射角によって調節することができる。運動エネルギーは加速電圧、ドーズ量などにより調節できる。イオン 103 の平均侵入深さとほぼ同じ深さの領域に脆化領域 104 が形成される。そのため、イオン 103 の平均侵入深さで、単結晶半導体基板 100 から分離される単結晶半導体層の厚さが決定される。この単結晶半導体層の厚さが、10 nm 以上 500 nm 以下、好ましくは 50 nm 以上 200 nm 以下になるように、脆化領域 104 が形成される深さを調節する。

#### 【0069】

イオンドーピング装置の主要な構成は、被処理物を配置するチャンバー、所望のイオンを発生させるイオン源、およびイオンを加速し、照射するための加速機構である。イオン源は、所望のイオン種を生成するためのソースガスを供給するガス供給装置、ソースガスを励起して、プラズマを生成させるための電極などで構成される。プラズマを形成するための電極として、フィラメント型の電極や容量結合高周波放電用の電極などが用いられる。加速機構は、引出電極、加速電極、減速電極、接地電極など、およびこれらの電極に電力を供給するための電源などで構成される。加速機構を構成する電極には複数の開口やスリットが設けられており、イオン源で生成されたイオンは電極に設けられた開口やスリットを通過して加速される。なお、イオンドーピング装置の構成は上述したものに限定されず、必要に応じた機構が設けられる。

#### 【0070】

本実施形態では、イオンドーピング装置で、水素を単結晶半導体基板 100 に添加する。プラズマソースガスとして水素を含むガスを供給する。例えば、H<sub>2</sub> を供給する。水素ガスを励起してプラズマを生成し、質量分離せずに、プラズマ中に含まれるイオンを加速し、加速されたイオンを単結晶半導体基板 100 に照射する。

#### 【0071】

イオンドーピング装置において、水素ガスから生成されるイオン種 (H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>) の総量に対して H<sub>3</sub><sup>+</sup> の割合が 50 % 以上とする。より好ましくは、その H<sub>3</sub><sup>+</sup> の割合を 80 % 以上とする。イオンドーピング装置は質量分離を行わないため、プラズマ中に生成される複数のイオン種のうち、1つ (H<sub>3</sub><sup>+</sup>) を 50 % 以上とすることが好ましく、80 % 以上とすることが好ましい。同じ質量のイオンを照射することで、単結晶半導体基板 100 の同じ深さに集中させてイオンを添加することができる。

#### 【0072】

脆化領域 104 を浅い領域に形成するためには、イオン 103 の加速電圧を低くする必要があるが、プラズマ中の H<sub>3</sub><sup>+</sup> イオンの割合を高くすることで、原子状水素 (H) を効率よく、単結晶半導体基板 100 に添加できる。H<sub>3</sub><sup>+</sup> イオンは H<sup>+</sup> イオンの 3 倍の質量を持つことから、同じ深さに水素原子を 1 つ添加する場合、H<sub>3</sub><sup>+</sup> イオンの加速電圧は、H<sup>+</sup> イオンの加速電圧の 3 倍にすることが可能となる。イオンの加速電圧を大きくできれば、イオンの照射工程のタクトタイムを短縮することが可能となり、生産性やスループットの向上を図ることができる。

#### 【0073】

イオンドーピング装置は廉価で、大面積処理に優れているため、このようなイオンドーピング装置を用いて H<sub>3</sub><sup>+</sup> を照射することで、半導体特性の向上、大面積化、低コスト化、生産性向上などの顕著な効果を得ることができる。また、イオンドーピング装置を用いた場合、重金属も同時に導入されるおそれがあるが、塩素原子を含有する酸化膜 105 を介してイオンの照射を行うことによって、上述したようにこれらの重金属による単結晶半導体基板 100 の汚染を防ぐことができる。

#### 【0074】

なお、加速されたイオン 103 を単結晶半導体基板 100 に照射する工程は、イオン注入装置で行うこともできる。イオン注入装置は、チャンバー内に配置された被処理体に、ソースガスをプラズマ励起して生成された複数のイオン種を質量分離し、特定のイオン種を照射する質量分離型の装置である。したがって、イオン注入装置を用いる場合は、水素ガスや PH<sub>3</sub> を励起して生成された H<sup>+</sup> イオンおよび H<sub>2</sub><sup>+</sup> イオンを質量分離して、H<sup>+</sup>

10

20

30

40

50

イオンまたはH<sub>2</sub><sup>+</sup>イオンの一方のイオンを加速して、単結晶半導体基板100に照射する。

#### 【0075】

次に、ベース基板110を準備する(図4(B-1)参照)。ベース基板110は、絶縁体でなる基板を用いる。具体的には、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板が挙げられる。本実施の形態では、ガラス基板を用いる場合について説明する。ベース基板110として大面積化が可能で安価なガラス基板を用いることにより、低コスト化を図ることができる。

#### 【0076】

また、ベース基板110を用いるに際し、ベース基板110の表面をあらかじめ洗浄することが好ましい。具体的には、ベース基板110を、塩酸過水(HPM)、硫酸過水(SPM)、アンモニア過水(APM)、希フッ酸(DHF)等を用いて超音波洗浄を行う。例えば、ベース基板110の表面に塩酸過水を用いて超音波洗浄を行うことが好ましい。このような洗浄処理を行うことによって、ベース基板110表面の平坦化や残存する研磨粒子を除去することができる。

#### 【0077】

次に、ベース基板110の表面に窒素含有層111(例えば、窒化シリコン膜(SiNx)又は窒化酸化シリコン膜(SiNxOy)(x>y)等の窒素を含有する絶縁膜)を形成する(図4(B-2)参照)。

#### 【0078】

本実施の形態において、窒素含有層111は、単結晶半導体基板100上に設けられた酸化膜105と貼り合わされる層(接合層)となる。また、窒素含有層111は、後にベース基板上に単結晶構造を有する単結晶半導体層を設けた際に、ベース基板に含まれるNa(ナトリウム)等の不純物が単結晶半導体層に拡散することを防ぐためのバリア層として機能する。

#### 【0079】

また、窒素含有層111を接合層として用いるため、接合不良を抑制するには窒素含有層111の表面を平滑とすることが好ましい。具体的には、窒素含有層111の表面の平均面粗さ(Ra)を0.5nm以下、自乗平均粗さ(Rms)を0.60nm以下、より好ましくは、平均面粗さを0.35nm以下、自乗平均粗さを0.45nm以下となるよう窒素含有層111を形成する。膜厚は、10nm以上200nm以下、好ましくは50nm以上100nm以下の範囲で設けることが好ましい。

#### 【0080】

次に、単結晶半導体基板100の表面とベース基板110の表面とを対向させ、酸化膜105の表面と窒素含有層111の表面とを接合させる(図4(C)参照)。

#### 【0081】

ここでは、単結晶半導体基板100とベース基板110を酸化膜105と窒素含有層111を介して密着させた後、単結晶半導体基板100の一箇所に1~500N/cm<sup>2</sup>、好ましくは1~20N/cm<sup>2</sup>程度の圧力を加える。圧力を加えた部分から酸化膜105と窒素含有層111とが接合はじめ、自発的に接合が形成され全面におよぶ。この接合工程は、ファンデルワールス力や水素結合が作用しており、加熱処理を伴わず、常温で行うことができるため、ベース基板110に、ガラス基板のように耐熱温度が低い基板を用いることができる。

#### 【0082】

なお、単結晶半導体基板100とベース基板110との貼り合わせを行う前に、単結晶半導体基板100上に形成された酸化膜105と、ベース基板110上に形成された窒素含有層111の少なくとも一方に表面処理を行うことが好ましい。

#### 【0083】

表面処理としては、プラズマ処理、オゾン処理、メガソニック洗浄、2流体洗浄(純水

10

20

30

40

50

や水素添加水等の機能水を窒素等のキャリアガスとともに吹き付ける方法) 又はこれらの方法を組み合わせて行うことができる。特に、酸化膜 105、窒素含有層 111 の少なくとも一方の表面にプラズマ処理を行った後に、単結晶半導体基板 100 及びベース基板 110 にオゾン処理、メガソニック洗浄、2 流体洗浄等を行うことによって、被処理面の有機物等のゴミを除去し、表面を親水化することができる。その結果、酸化膜 105 と窒素含有層 111 の接合強度を向上させることができる。ここでのプラズマ処理は、不活性ガス(例えば、アルゴン(Ar)ガス)及び/又は反応性ガス(例えば、酸素(O<sub>2</sub>)ガス、窒素(N<sub>2</sub>)ガス)を用いて、RIE 法、ICP 法、大気圧プラズマを行う。

## 【0084】

ここで、オゾン処理の一例を説明する。例えば、酸素を含む雰囲気下で紫外線(UV)を照射することにより、被処理体表面にオゾン処理を行うことができる。酸素を含む雰囲気下で紫外線を照射するオゾン処理は、UV オゾン処理または紫外線オゾン処理などとも言われる。酸素を含む雰囲気下において、紫外線のうち 200 nm 未満の波長を含む光と 200 nm 以上の波長を含む光を照射することにより、オゾンを生成させるとともに、オゾンから一重項酸素を生成させることができる。紫外線のうち 180 nm 未満の波長を含む光を照射することにより、オゾンを生成させるとともに、オゾンから一重項酸素を生成させることもできる。

## 【0085】

酸素を含む雰囲気下で、200 nm 未満の波長を含む光および 200 nm 以上の波長を含む光を照射することにより起きる反応例を示す。

## 【0086】

上記反応式(1)において、酸素(O<sub>2</sub>)を含む雰囲気下で 200 nm 未満の波長(<sub>1</sub> nm)を含む光(h)を照射することにより基底状態の酸素原子(O(^3 P))が生成する。次に、反応式(2)において、基底状態の酸素原子(O(^3 P))と酸素(O<sub>2</sub>)とが反応してオゾン(O<sub>3</sub>)が生成する。そして、反応式(3)において、生成されたオゾン(O<sub>3</sub>)を含む雰囲気下で 200 nm 以上の波長(<sub>2</sub> nm)を含む光が照射されることにより、励起状態の一重項酸素 O(^1 D) が生成される。酸素を含む雰囲気下において、紫外線のうち 200 nm 未満の波長を含む光を照射することによりオゾンを生成させるとともに、200 nm 以上の波長を含む光を照射することによりオゾンを分解して一重項酸素を生成する。上記のようなオゾン処理は、例えば、酸素を含む雰囲気下での低圧水銀ランプの照射(<sub>1</sub> = 185 nm, <sub>2</sub> = 254 nm)により行うことができる。

## 【0087】

また、酸素を含む雰囲気下で、180 nm 未満の波長を含む光を照射することにより起きる反応例を示す。

## 【0088】

上記反応式(4)において、酸素(O<sub>2</sub>)を含む雰囲気下で 180 nm 未満の波長(<sub>3</sub> nm)を含む光を照射することにより、励起状態の一重項酸素 O(^1 D) と基底状態の酸素原子(O(^3 P))が生成する。次に、反応式(5)において、基底状態の酸素原子(O(^3 P))と酸素(O<sub>2</sub>)とが反応してオゾン(O<sub>3</sub>)が生成する。反応式(6)において、生成されたオゾン(O<sub>3</sub>)を含む雰囲気下で 180 nm 未満の波長(<sub>3</sub> nm)を含む光が照射されることにより、励起状態の一重項酸素と酸素が生成される。酸素を含む雰囲気下において、紫外線のうち 180 nm 未満の波長を含む光を照射することによりオゾンを生成させるとともにオゾンまたは酸素を分解して一重項酸素を生成する。上記のようなオゾン処理は、例えば、酸素を含む雰囲気下での Xe エキシマ UV ランプの照射(

10

20

30

40

50

$\lambda = 172 \text{ nm}$  )により行うことができる。

#### 【0089】

200 nm未満の波長を含む光により被処理体表面に付着する有機物などの化学結合を切断し、オゾンまたはオゾンから生成された一重項酸素により被処理体表面に付着する有機物、または化学結合を切断した有機物などを酸化分解して除去することができる。上記のようなオゾン処理を行うことで、被処理体表面の親水性および清浄性を高めることができ、接合を良好に行うことができる。

#### 【0090】

酸素を含む雰囲気下で紫外線を照射することによりオゾンが生成される。オゾンは、被処理体表面に付着する有機物の除去に効果を奏する。また、一重項酸素も、オゾンと同等またはそれ以上に、被処理体表面に付着する有機物の除去に効果を奏する。オゾン及び一重項酸素は、活性状態にある酸素の例であり、総称して活性酸素とも言われる。上記反応式等で説明したとおり、一重項酸素を生成する際にオゾンが生じる、またはオゾンから一重項酸素を生成する反応もあるため、ここでは一重項酸素が寄与する反応も含めて、便宜的にオゾン処理と称する。

#### 【0091】

また、酸化膜105と窒素含有層111を接合させた後、接合強度を増加させるための熱処理を行うことが好ましい。この熱処理の温度は、脆化領域104に亀裂を発生させない温度とし、例えば、室温以上400未満の温度範囲で処理する。また、この温度範囲で加熱しながら、酸化膜105と窒素含有層111を接合させてもよい。熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA(瞬間熱アニール、Rapid Thermal Anneal)装置、マイクロ波加熱装置などを用いることができる。

#### 【0092】

一般的に、酸化膜105と窒素含有層111を接合と同時又は接合させた後に熱処理を行うと、接合界面において脱水反応が進行し、接合界面同士が近づき、水素結合や共有結合が形成されることにより接合が強化される。脱水反応を促進させるためには、脱水反応により接合界面に生じる水分を高温で熱処理を行うことにより除去する必要がある。つまり、接合後の熱処理温度が低い場合には、脱水反応で接合界面に生じた水分を効果的に除去できないため、脱水反応が進まず接合強度を十分に向上させることが難しい。

#### 【0093】

一方で、酸化膜105として、塩素原子等を含有させた酸化膜を用いた場合、当該酸化膜105が水分を吸収し拡散させることができるため、接合後の熱処理を低温で行う場合であっても、脱水反応で接合界面に生じた水分を酸化膜105へ吸収、拡散させ脱水反応を効率良く促進させることができる。この場合、ベース基板110としてガラス等の耐熱性が低い基板を用いた場合であっても、酸化膜105と窒素含有層111の接合強度を十分に向上させることが可能となる。また、バイアス電圧を印加してプラズマ処理を行うことにより、水分を効果的に酸化膜105に吸収し拡散させ、低温の熱処理であっても酸化膜105と窒素含有層111の接合強度を向上させることができる。

#### 【0094】

次に、熱処理を行い脆化領域104にて分離(劈開)することにより、ベース基板110上に、酸化膜105及び窒素含有層111を介して単結晶半導体層112を設ける(図4(D)参照)。

#### 【0095】

加熱処理を行うことで、温度上昇によって脆化領域104に形成されている微小な孔において、内部の圧力が上昇する。圧力の上昇により、脆化領域104の微小な孔に体積変化が起こり、脆化領域104に亀裂が生じるので、脆化領域104に沿って単結晶半導体基板100が劈開する。酸化膜105はベース基板110に接合しているので、ベース基板110上には単結晶半導体基板100から分離された単結晶半導体層112が形成される。また、ここでの熱処理の温度は、ベース基板110の歪点以下の温度とする。

#### 【0096】

10

20

30

40

50

この加熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA（瞬間熱アニール、Rapid Thermal Anneal）装置、マイクロ波加熱装置などを用いることができる。例えば、RTA装置を用いる場合、加熱温度550以上730以下、処理時間0.5分以上60分以内で行うことができる。

#### 【0097】

なお、上述したベース基板110と酸化膜105との接合強度を増加させるための熱処理を行わず、図1(D)の熱処理を行うことにより、酸化膜105と窒素含有層111との接合強度の増加の熱処理工程と、脆化領域104における分離の熱処理工程を同時に実行してもよい。

#### 【0098】

以上の工程により、ベース基板110上に酸化膜105及び窒素含有層111を介して単結晶半導体層112が設けられたSOI基板を作製することができる。本実施の形態で示した作製方法を用いることによって、窒素含有層111を接合層として用いた場合であっても、ベース基板110と単結晶半導体層112との接合強度を向上させ、信頼性を向上させることができる。その結果、ベース基板110上に形成される単結晶半導体層112への不純物の拡散を抑制すると共に、ベース基板110と単結晶半導体層112とが強固に密着したSOI基板を形成することができる。

#### 【0099】

また、ベース基板側に窒素含有層を設け、半導体基板側に塩素等のハロゲンを有する酸化膜を形成することにより、作製工程を簡略化すると共に半導体基板とベース基板との貼り合わせ前に当該半導体基板へ不純物元素が浸入することを抑制することができる。また、半導体基板側に設ける接合層として塩素等のハロゲンを有する酸化膜を形成することにより、接合後の熱処理を低温で行う場合であっても、脱水反応を効率良く促進させることにより接合強度を向上させることができる。

#### 【0100】

その後、上記実施の形態1で示したように、第1のエッティング処理、レーザ照射、プラズマ処理、第2のエッティング処理、熱処理を行う。これらの処理は、図2(A)～図2(F)、又は図3(A)～図3(F)と同様にして行えばよい。

#### 【0101】

なお、本実施の形態では、単結晶半導体基板100上に酸化膜105を形成し、ベース基板110上に窒素含有層111を形成する場合を示したが、これに限られない。例えば、単結晶半導体基板100上に酸化膜105と窒素含有層を順に積層させて形成し、酸化膜105上に形成された窒素含有層の表面とベース基板110との表面とを接合させてもよい。この場合、窒素含有層は脆化領域104の形成前に設けてもよいし、形成後に設けてもよい。なお、窒素含有層上に酸化膜（例えば、酸化シリコン）を形成し、当該酸化膜105の表面とベース基板110の表面とを接合させても良い。

#### 【0102】

また、ベース基板110から単結晶半導体層112への不純物の混入が問題とならない場合には、ベース基板110上に窒素含有層111を設げずに、単結晶半導体基板100上に設けられた酸化膜105の表面とベース基板110の表面とを接合させてもよい。

#### 【0103】

なお、本実施の形態で示した構成は、本明細書の他の実施の形態で示す構成と適宜組み合わせて行うことができる。

#### 【0104】

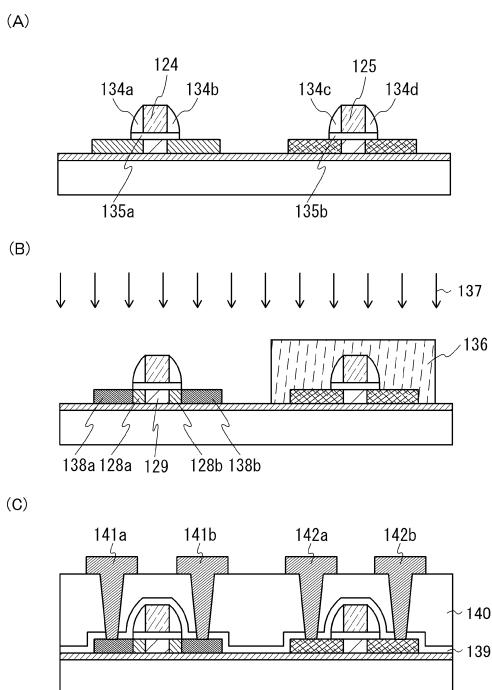

##### (実施の形態3)

本実施の形態では、高性能及び高信頼性な半導体素子を有する半導体装置を、歩留まりよく作製することを目的とした半導体装置の作製方法の一例としてnチャネル型薄膜トランジスタ、およびpチャネル型薄膜トランジスタを作製する方法に関して図6及び図7を用いて説明する。複数の薄膜トランジスタ(TFT)を組み合わせることで、各種の半導体装置を形成することができる。なお、実施の形態1及び実施の形態2と同一部分又は同

10

20

30

40

50

様な機能を有する部分の繰り返しの説明は省略する。

**【0105】**

図6(A)は、ベース基板110上に絶縁膜102、単結晶半導体層112が形成されている。なお、ここでは図2(D)に示す構成の半導体基板を適用する例を示すが、本明細書で示すその他の構成の半導体基板も適用できる。

**【0106】**

単結晶半導体層112は、単結晶半導体基板100より分離され、実施の形態1で示したように、エッティング処理を行った後にレーザビームを照射し、プラズマ処理を行うことによって、単結晶半導体層112は、結晶欠陥が低減され、表面の平坦性が高められている。

10

**【0107】**

単結晶半導体層112をエッティングして、半導体素子の配置に合わせて島状に分離した単結晶半導体層121、122を形成する(図6(B)参照)。

**【0108】**

なお、単結晶半導体層112のエッティングを行う前に、TFTのしきい値を制御するために、ホウ素、アルミニウム、ガリウムなどの不純物元素、又はリン、ヒ素などの不純物元素を単結晶半導体層112に添加することが好ましい。例えば、nチャネル型TFTが形成される領域に、ホウ素、アルミニウム、ガリウムなどの不純物元素を添加し、pチャネル型TFTが形成される領域にリン、ヒ素などの不純物元素を添加する。

20

**【0109】**

単結晶半導体層上の酸化膜を除去し、単結晶半導体層121、122を覆うゲート絶縁層123を形成する。本実施の形態における単結晶半導体層121、122は平坦性が高いため、単結晶半導体層121、122上に形成されるゲート絶縁層が薄膜のゲート絶縁層であっても被覆性よく覆うことができる。従ってゲート絶縁層の被覆不良による特性不良を防ぐことができ、高信頼性の半導体装置を歩留まりよく作製することができる。ゲート絶縁層123の薄膜化は、薄膜トランジスタを低電圧で高速に動作させる効果がある。

**【0110】**

ゲート絶縁層123は酸化珪素、若しくは酸化珪素と窒化珪素の積層構造で形成すればよい。ゲート絶縁層123は、プラズマCVD法や減圧CVD法により絶縁膜を堆積することで形成しても良いし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。単結晶半導体層を、プラズマ処理により酸化又は窒化することにより形成するゲート絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。

30

**【0111】**

また、ゲート絶縁層123として、酸化ジルコニウム、酸化ハフニウム、酸化チタン、酸化タンタルなどの高誘電率材料を用いても良い。ゲート絶縁層123に高誘電率材料を用いることにより、ゲートリーク電流を低減することができる。

**【0112】**

ゲート絶縁層123上にゲート電極層124及びゲート電極層125を形成する(図6(C)参照)。ゲート電極層124、125は、スパッタリング法、蒸着法、CVD法等の手法により形成することができる。ゲート電極層124、125はタンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、ゲート電極層124、125としてリン等の不純物元素をドーピングした多結晶シリコン層に代表される半導体層や、AgPdCu合金を用いてもよい。

40

**【0113】**

本発明に係るSOI基板は、単結晶半導体層表面が平坦化されているため、絶縁耐圧性の高いゲート絶縁層を形成することができる。

**【0114】**

単結晶半導体層122を覆うマスク126を形成する。マスク126及びゲート電極層

50

124をマスクとして、n型を付与する不純物元素127を添加し、第1のn型不純物領域128a、128bを形成する(図6(D)参照。)。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン(PH<sub>3</sub>)を用いる。ここでは、第1のn型不純物領域128a、128bに、n型を付与する不純物元素が $1 \times 10^{17} \sim 5 \times 10^{18}$ /cm<sup>3</sup>程度の濃度で含まれるように添加する。本実施の形態では、n型を付与する不純物元素としてリン(P)を用いる。

#### 【0115】

次に、マスク126を除去した後、単結晶半導体層121を覆うマスク130を形成する。マスク126、ゲート電極層125をマスクとしてp型を付与する不純物元素131を添加し、第1のp型不純物領域132a、第1のp型不純物領域132bを形成する(図6(E)参照。)。本実施の形態では、不純物元素としてボロン(B)を用いるため、不純物元素を含むドーピングガスとしてはジボラン(B<sub>2</sub>H<sub>6</sub>)などを用いる。

#### 【0116】

マスク130を除去した後、ゲート電極層124、125の側面にサイドウォール構造の側壁絶縁層134a～134d、ゲート絶縁層135a、135bを形成する(図7(A)参照。)。側壁絶縁層134a～134dは、ゲート電極層124、125を覆う絶縁層を形成した後、これをRIE(Reactive ion etching:反応性イオンエッティング)法による異方性のエッティングによって加工し、ゲート電極層124、125の側壁に自己整合的にサイドウォール構造の側壁絶縁層134a～134dを形成すればよい。ここで、絶縁層について特に限定ではなく、TEOS(tetraethyl-ortho silicate)若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性のよい酸化珪素であることが好ましい。絶縁層は熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD、スパッタリング等の方法によって形成することができる。ゲート絶縁層135a、135bはゲート電極層124、125及び側壁絶縁層134a～134dをマスクとしてゲート絶縁層123をエッティングして形成することができる。

#### 【0117】

また、本実施の形態では、絶縁層をエッティングする際、ゲート電極層上の絶縁層を除去し、ゲート電極層を露出させるが、絶縁層をゲート電極層上に残すような形状に側壁絶縁層134a～134dを形成してもよい。また、後工程でゲート電極層上に保護膜を形成してもよい。このようにゲート電極層を保護することによって、エッティング加工する際、ゲート電極層の膜減りを防ぐことができる。また、ソース領域及びドレイン領域にシリサイドを形成する場合、シリサイド形成時に成膜する金属膜とゲート電極層とが接しないので、金属膜の材料とゲート電極層の材料とが反応しやすい材料であっても、化学反応や拡散などの不良を防止することができる。エッティング方法は、ドライエッティング法でもウェットエッティング法でもよく、種々のエッティング方法を用いることができる。本実施の形態では、ドライエッティング法を用いる。エッティング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。

#### 【0118】

次に、単結晶半導体層122を覆うマスク136を形成する。マスク136、ゲート電極層124、側壁絶縁層134a、134bをマスクとしてn型を付与する不純物元素137を添加し、第2のn型不純物領域138a、138bが形成される。本実施の形態では、不純物元素を含むドーピングガスとしてPH<sub>3</sub>を用いる。ここでは、第2のn型不純物領域138a、138bにn型を付与する不純物元素が $5 \times 10^{19} \sim 5 \times 10^{20}$ /cm<sup>3</sup>程度の濃度で含まれるように添加する。また、単結晶半導体層121にチャネル形成領域129が形成される(図7(B)参照。)。

#### 【0119】

第2のn型不純物領域138a、第2のn型不純物領域138bは高濃度n型不純物領域であり、ソース、ドレインとして機能する。一方、第1のn型不純物領域128a、1

10

20

30

40

50

28bは低濃度不純物領域であり、LDD (Lightly Doped Drain) 領域となる。第1のn型不純物領域128a、128bはゲート電極層124に覆われていないLoft領域に形成されるため、オフ電流を低減する効果がある。この結果、さらに信頼性の高く、低消費電力の半導体装置を作製することが可能である。

#### 【0120】

マスク136を除去し、不純物元素を活性化するために加熱処理、強光の照射、又はレーザビームの照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と単結晶半導体層との界面へのプラズマダメージを回復することができる。

#### 【0121】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では10、層間絶縁層は、保護膜となる水素を含む絶縁膜139と、絶縁膜140との積層構造とする。絶縁膜139と絶縁膜140は、スパッタ法、またはプラズマCVDを用いた窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

#### 【0122】

さらに、窒素雰囲気中で、300～550で1～12時間の熱処理を行い、単結晶半導体層を水素化する工程を行う。好みしくは、400～500で行う。この工程は層間絶縁層である絶縁膜140に含まれる水素により単結晶半導体層のダンギングボンドを終端する工程である。本実施の形態では、410度( )で1時間加熱処理を行う。

#### 【0123】

絶縁膜139、絶縁膜140としては他に窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイヤモンドライクarbon(DLC)、窒素含有炭素(CN)その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、アリール基)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、ポリシラザンを用いることができる。平坦性のよい塗布法によってされる塗布膜を用いてもよい。

#### 【0124】

絶縁膜139、絶縁膜140は、ディップ、スプレー塗布、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー、CVD法、蒸着法等を採用することができる。液滴吐出法により絶縁膜139、絶縁膜140を形成してもよい。液滴吐出法を用いた場合には材料液を節約することができる。また、液滴吐出法のようにパターンが転写、または描写できる方法、例えば印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)なども用いることができる。

#### 【0125】

次いで、レジストからなるマスクを用いて絶縁膜139、絶縁膜140に単結晶半導体層に達するコンタクトホール(開口)を形成する。エッチングは、用いる材料の選択比によって、一回で行っても複数回行っても良い。エッチングによって、絶縁膜139、絶縁膜140を部分的に除去し、ソース領域又はドレイン領域である第2のn型不純物領域138a、138b、第2のp型不純物領域132a、132bに達する開口を形成する。エッチングは、ウェットエッチングでもドライエッチングでもよく、両方用いてもよい。ウェットエッチングのエッチャントは、フッ素水素アンモニウム及びフッ化アンモニウムを含む混合溶液のようなフッ酸系の溶液を用いるとよい。エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。

10

20

30

40

50

また用いるエッティング用ガスに不活性気体を添加してもよい。添加する不活性元素としては、He、Ne、Ar、Kr、Xeから選ばれた一種または複数種の元素を用いることができる。

#### 【0126】

開口を覆うように導電膜を形成し、導電膜をエッティングして各ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層として機能する配線層141a、141b、142a、142bを形成する。配線層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望の形状にエッティングして形成することができる。また、液滴吐出法、印刷法、電解メッキ法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。配線層の材料は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Zr、Ba等の金属、及びSi、Ge、又はその合金、若しくはその窒化物を用いて形成する。また、これらの積層構造としても良い。10

#### 【0127】

以上の工程でCMOS構造のnチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタを含む半導体装置を作製することができる（図7（C）参照。）。図示しないが、本実施の形態はCMOS構造であるため、nチャネル型薄膜トランジスタとpチャネル型薄膜トランジスタとは電気的に接続している。

#### 【0128】

本実施の形態に限定されず、薄膜トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリブルゲート構造であっても良い。20

#### 【0129】

本発明に係るSOI基板を用いた半導体装置は、単結晶半導体層表面が平坦化されているため、単結晶半導体層とゲート絶縁層との界面における局在準位密度を低くすることができます。また、単結晶半導体層の結晶欠陥も低減されているため、半導体素子の電気的特性を向上させることができる。以上のように、結晶欠陥が低減され、かつ平坦性も高い単結晶半導体層を有する半導体基板を用いることにより、高性能及び高信頼性な半導体装置を歩留まり良く作製することができる。

#### 【0130】

このように、半導体基板を用いて薄膜トランジスタを作製することができる。本発明を適用したSOI基板の単結晶半導体層は、結晶欠陥が低減され、ゲート絶縁層135a、135bとの界面準位密度が低減された単結晶半導体層であり、その表面が平坦化されている。このことにより、SOI基板に、低い駆動電圧、高い電界効果移動、小さいサブスレッショルド値など、優れた特性を備えた薄膜トランジスタを形成することができる。さらに、同一基板上に特性のばらつきの少ない、高性能なトランジスタを複数基板上に形成することが可能である。すなわち、本発明に係るSOI基板を用いることで、しきい値電圧や移動度などトランジスタ特性として重要な特性値の不均一性が抑制され、また高電界移動度などの高性能化が可能になる。30

#### 【0131】

従って、本発明に係る半導体基板を用いてTFTなど各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。

#### 【0132】

##### (実施の形態4)

実施の形態3を参照してTFTの作製方法を説明したが、本実施の形態では、TFTの他、容量、抵抗などTFTと共に各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。以下、図面を参照しながら半導体装置の具体的な態様を説明する。

#### 【0133】

まず、半導体装置の一例として、マイクロプロセッサについて説明する。図8はマイク40

ロプロセッサ 500 の構成例を示すブロック図である。

**【0134】**

マイクロプロセッサ 500 は、演算回路 501 (Arithmetic logic unit。ALUともいう。)、演算回路制御部 502 (ALU Controller)、命令解析部 503 (Instruction Decoder)、割り込み制御部 504 (Interrupt Controller)、タイミング制御部 505 (Timing Controller)、レジスタ 506 (Register)、レジスタ制御部 507 (Register Controller)、バスインターフェース 508 (Bus I/F)、読み出し専用メモリ 509、およびメモリインターフェース 510 を有している。

10

**【0135】**

バスインターフェース 508 を介してマイクロプロセッサ 500 に入力された命令は、命令解析部 503 に入力され、デコードされた後、演算回路制御部 502、割り込み制御部 504、レジスタ制御部 507、タイミング制御部 505 に入力される。演算回路制御部 502、割り込み制御部 504、レジスタ制御部 507、タイミング制御部 505 は、デコードされた命令に基づき様々な制御を行う。

**【0136】**

演算回路制御部 502 は、演算回路 501 の動作を制御するための信号を生成する。また、割り込み制御部 504 は、マイクロプロセッサ 500 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を処理する回路であり、割り込み制御部 504 は、割り込み要求の優先度やマスク状態を判断して、割り込み要求を処理する。レジスタ制御部 507 は、レジスタ 506 のアドレスを生成し、マイクロプロセッサ 500 の状態に応じてレジスタ 506 の読み出しや書き込みを行う。タイミング制御部 505 は、演算回路 501、演算回路制御部 502、命令解析部 503、割り込み制御部 504、およびレジスタ制御部 507 の動作のタイミングを制御する信号を生成する。例えば、タイミング制御部 505 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えている。図 8 に示すように、内部クロック信号 CLK2 は他の回路に入力される。

20

**【0137】**

次に、非接触でデータの送受信を行う機能、および演算機能を備えた半導体装置の一例を説明する。図 9 は、このような半導体装置の構成例を示すブロック図である。図 9 に示す半導体装置は、無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RFCPU」という）と呼ぶことができる。

30

**【0138】**

図 9 に示すように、RFCPU 511 は、アナログ回路部 512 とデジタル回路部 513 を有している。アナログ回路部 512 として、共振容量を有する共振回路 514、整流回路 515、定電圧回路 516、リセット回路 517、発振回路 518、復調回路 519、変調回路 520 と、電源管理回路 530 を有している。デジタル回路部 513 は、RF インターフェース 521、制御レジスタ 522、クロックコントローラ 523、CPU インターフェース 524、中央処理ユニット 525、ランダムアクセスメモリ 526、読み出し専用メモリ 527 を有している。

40

**【0139】**

RFCPU 511 の動作の概要は以下の通りである。アンテナ 528 が受信した信号は共振回路 514 により誘導起電力を生じる。誘導起電力は、整流回路 515 を経て容量部 529 に充電される。この容量部 529 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 529 は、RFCPU 511 を構成する基板に集積されている必要はなく、他の部品として RFCPU 511 に組み込むこともできる。

**【0140】**

リセット回路 517 は、デジタル回路部 513 をリセットし初期化する信号を生成する

50

。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 518 は、定電圧回路 516 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。復調回路 519 は、受信信号を復調する回路であり、変調回路 520 は、送信するデータを変調する回路である。

#### 【0141】

例えば、復調回路 519 はローパスフィルタで形成され、振幅変調（ASK）方式の受信信号を、その振幅の変動をもとに、二値化する。また、送信データを振幅変調（ASK）方式の送信信号の振幅を変動させて送信するため、変調回路 520 は、共振回路 514 の共振点を変化させることで通信信号の振幅を変化させている。

#### 【0142】

クロックコントローラ 523 は、電源電圧または中央処理ユニット 525 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 530 が行っている。

#### 【0143】

アンテナ 528 から RF C P U 511 に入力された信号は復調回路 519 で復調された後、RF インターフェース 521 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 522 に格納される。制御コマンドには、読み出し専用メモリ 527 に記憶されているデータの読み出し、ランダムアクセスメモリ 526 へのデータの書き込み、中央処理ユニット 525 への演算命令などが含まれている。

#### 【0144】

中央処理ユニット 525 は、インターフェース 524 を介して読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 にアクセスする。C P U インターフェース 524 は、中央処理ユニット 525 が要求するアドレスより、読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 のいずれかに対するアクセス信号を生成する機能を有している。

#### 【0145】

中央処理ユニット 525 の演算方式は、読み出し専用メモリ 527 に OS（オペレーティングシステム）を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の演算処理を行い、プログラムを使って、残りの演算を中央処理ユニット 525 が処理する方式を適用できる。

#### 【0146】

このような RF C P U は、結晶欠陥が低減され、結晶方位が一定の単結晶半導体層 112 によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部 529 を小型化しても長時間の動作が保証される。

#### 【0147】

##### （実施の形態 5）

本実施の形態では、本発明の半導体基板を用いた表示装置について図 10 及び図 11 を参照して説明する。

#### 【0148】

図 10 は液晶表示装置を説明するための図面である。図 10 (A) は液晶表示装置の画素の平面図であり、図 10 (B) は、J - K 切断線による図 10 (A) の断面図である。

#### 【0149】

図 10 (A) に示すように、画素は、単結晶半導体層 320、単結晶半導体層 320 と交差している走査線 322、走査線 322 と交差している信号線 323、画素電極 324、画素電極 324 と単結晶半導体層 320 を電気的に接続する電極 328 を有する。単結晶半導体層 320 は、本発明に係る SOI 基板の有する単結晶半導体層から形成された層であり、実施の形態 1 で示したように、エッチング処理を行った後にレーザビームを照射

10

20

30

40

50

し、プラズマ処理を行うことによって、単結晶半導体層 112 は、結晶欠陥が低減され、表面の平坦性が高められている。単結晶半導体層 320 は、画素の TFT325 を構成する。

#### 【 0150 】

半導体基板には上記実施の形態 1 及び実施の形態 2 で示した SOI 基板が用いられている。図 10 (B) に示すように、ベース基板 110 上に、絶縁膜 102 を介して単結晶半導体層 320 が積層されている。ベース基板 110 としては、ガラス基板を用いることができる。TFT325 の単結晶半導体層 320 は、SOI 基板の単結晶半導体層をエッチングにより素子分離して形成された膜である。単結晶半導体層 320 には、チャネル形成領域 340、不純物元素が添加された n 型の高濃度不純物領域 341 が形成されている。TFT325 のゲート電極は走査線 322 に含まれ、ソース電極およびドレイン電極の一方は信号線 323 に含まれている。10

#### 【 0151 】

層間絶縁膜 327 上には、信号線 323、画素電極 324 および電極 328 が設けられている。層間絶縁膜 327 上には、柱状スペーサ 329 が形成されている。信号線 323、画素電極 324、電極 328 および柱状スペーサ 329 を覆って配向膜 330 が形成されている。対向基板 332 には、対向電極 333、対向電極を覆う配向膜 334 が形成されている。柱状スペーサ 329 は、ベース基板 110 と対向基板 332 の隙間を維持するために形成される。柱状スペーサ 329 によって形成される隙間に液晶層 335 が形成されている。信号線 323 および電極 328 と高濃度不純物領域 341 との接続部は、コンタクトホールの形成によって層間絶縁膜 327 に段差が生じるので、この接続部では液晶層 335 の液晶の配向が乱れやすい。そのため、この段差部に柱状スペーサ 329 を形成して、液晶の配向の乱れを防ぐ。20

#### 【 0152 】

本発明に係る半導体基板の作製方法により作成された SOI 基板は結晶が低減され、表面の平坦性が高められているため、同一基板上に特性のばらつきの少ない、高性能なトランジスタを複数基板上に形成することが可能である。従って、本発明に係る SOI 基板を用いて液晶表示装置を作製することで、トランジスタごとの特性のばらつきを少なくすることができます。

#### 【 0153 】

次に、エレクトロルミネセンス表示装置（以下、EL 表示装置という。）について図 11 を参照して説明する。図 11 (A) は EL 表示装置の画素の平面図であり、図 11 (B) は、J - K 切断線による図 11 (A) の断面図である。30

#### 【 0154 】

図 11 (A) に示すように、画素は、トランジスタでなる選択用トランジスタ 401、表示制御用トランジスタ 402、走査線 405、信号線 406、および電流供給線 407、画素電極 408 を含む。エレクトロルミネセンス材料を含んで形成される層（EL 層）が一対の電極間に挟んだ構造の発光素子が各画素に設けられている。発光素子の一方の電極が画素電極 408 である。また、半導体膜 403 は、選択用トランジスタ 401 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体膜 404 は、表示制御用トランジスタ 402 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体膜 403、404 は、ベース基板上に設けられた単結晶半導体層 302 から形成された層である。40

#### 【 0155 】

選択用トランジスタ 401において、ゲート電極は走査線 405 に含まれ、ソース電極またはドレイン電極の一方は信号線 406 に含まれ、他方は電極 410 として形成されている。表示制御用トランジスタ 402 は、ゲート電極 412 が電極 411 と電気的に接続され、ソース電極またはドレイン電極の一方は、画素電極 408 に電気的に接続される電極 413 として形成され、他方は、電流供給線 407 に含まれている。

#### 【 0156 】

50

20

30

40

50

表示制御用トランジスタ402はpチャネル型のTFTである。図11(B)に示すように、半導体膜404には、チャネル形成領域451、およびp型の高濃度不純物領域452が形成されている。なお、半導体基板は、実施の形態1及び実施の形態2で作製した半導体基板が用いられている。

#### 【0157】

表示制御用トランジスタ402のゲート電極412を覆って、層間絶縁膜427が形成されている。層間絶縁膜427上に、信号線406、電流供給線407、電極411、413などが形成されている。また、層間絶縁膜427上には、電極413に電気的に接続されている画素電極408が形成されている。画素電極408は周辺部が絶縁性の隔壁層428で囲まれている。画素電極408上にはEL層429が形成され、EL層429上には対向電極430が形成されている。補強板として対向基板431が設けられており、対向基板431は樹脂層432によりベース基板110に固定されている。10

#### 【0158】

EL表示装置の階調の制御は、発光素子の輝度を電流で制御する電流駆動方式と、電圧でその輝度を制御する電圧駆動方式とがあるが、電流駆動方式は、画素ごとでトランジスタの特性値の差が大きい場合、採用することは困難であり、そのためには特性のばらつきを補正する補正回路が必要になる。しかし、本発明に係るSOI基板の作製方法により作製されたSOI基板は結晶欠陥が低減され、表面の平坦性が高められているため、同一基板上に特性のばらつきの少ない、高性能なトランジスタを複数基板上に形成することが可能である。従って、本発明に係るSOI基板を用いてEL表示装置を作製することで、選択用トランジスタ401および表示制御用トランジスタ402は画素ごとに特性のばらつきがなくなるため、電流駆動方式を採用することができる。20

#### 【0159】

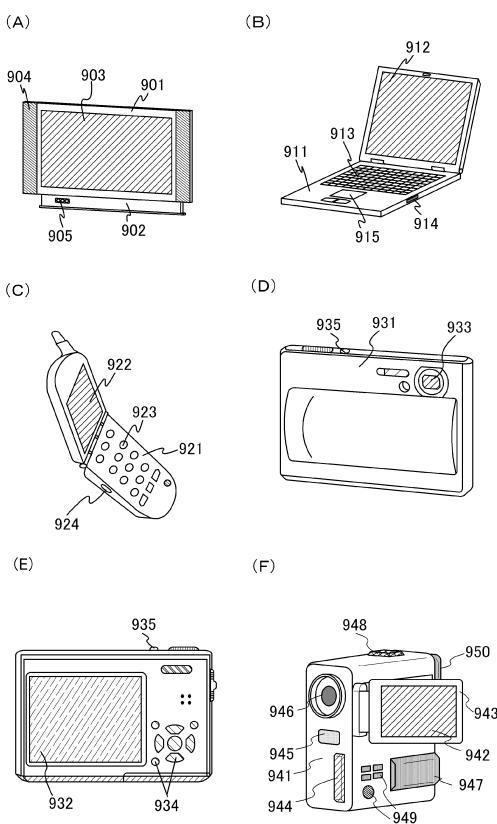

##### (実施の形態6)

本発明に係るSOI基板を用いてトランジスタ等の半導体装置を作製し、この半導体装置を用いてさまざまな電子機器を完成することができる。本発明に係るSOI基板に設けられた単結晶半導体層は結晶欠陥が低減され、表面の平坦性が高められているため、活性層として用いることで、電気的特性が向上した半導体素子を製造することができる。また、当該単結晶半導体層は結晶欠陥が低減されているため、ゲート絶縁層との界面において、局在準位密度を低減させることができるとなる。さらに、単結晶半導体層が高い平坦性を有するため、単結晶半導体層上に、薄く、且つ高い絶縁耐圧を有するゲート絶縁層を形成することができ、作製される半導体素子の移動度の向上、S値の向上または短チャネル効果抑制を実現することができる。すなわち、本発明に係るSOI基板を用いることで、電流駆動能力が高く、かつ信頼性の高い半導体素子を作製することができる。その結果、最終製品としての電子機器をスループット良く、良好な品質で作製することができる。この半導体素子を用いて、さまざまな半導体装置を作製することができる。本実施の形態では、図面を用いて具体的な例を説明する。なお、本実施の形態において、上記実施の形態と同様の部分には同じ符号を付し、詳しい説明を省略する。30

#### 【0160】

図12(A)は表示装置であり、筐体901、支持台902、表示部903、スピーカ部904、ビデオ入力端子905などを含む。この表示装置は、他の実施の形態で示した作製方法により形成したトランジスタを駆動ICや表示部903などに用いることにより作製される。なお、表示装置には液晶表示装置、発光表示装置などがあり、用途別にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用表示装置が含まれる。具体的には、ディスプレイ、ヘッドマウントディスプレイ、反射型プロジェクターなどを挙げることができる。40

#### 【0161】

図12(B)はコンピュータであり、筐体911、表示部912、キーボード913、外部接続ポート914、ポインティングデバイス915などを含む。本発明を用いて作製されたトランジスタは、表示部912の画素部だけではなく、表示用の駆動IC、本体内50

部のCPU、メモリなどの半導体装置にも適用が可能である。

#### 【0162】

また、図12(C)は携帯電話であり、携帯用の情報処理端末の1つの代表例である。この携帯電話は筐体921、表示部922、操作キー923などを含む。本発明に係るSOI基板を用いて作製されたトランジスタは表示部922の画素部やセンサ部924だけではなく、表示用の駆動IC、メモリ、音声処理回路などに用いることができる。センサ部924は光センサ素子を有しており、センサ部924で得られる照度に合わせて表示部922の輝度コントロールを行うことや、センサ部924で得られる照度に合わせて操作キー923の照明を抑えることによって、携帯電話の消費電力を抑えることができる。

#### 【0163】

上記の携帯電話を初めとして、PDA(Personal Digital Assistants、情報携帯端末)、デジタルカメラ、小型ゲーム機、携帯型の音響再生装置などの電子機器に、本発明を用いて形成した半導体材料を用いることもできる。例えば、CPU、メモリ、センサなどの機能回路を形成することや、これらの電子機器の画素部や、表示用の駆動ICにも適用することが可能である。

#### 【0164】

また、図12(D)、(E)はデジタルカメラである。なお、図12(E)は、図12(D)の裏側を示す図である。このデジタルカメラは、筐体931、表示部932、レンズ933、操作キー934、シャッターボタン935などを有する。本発明を用いて作製されたトランジスタは、表示部932の画素部、表示部932を駆動する駆動IC、メモリなどに用いることができる。

#### 【0165】

図12(F)はデジタルビデオカメラである。このデジタルビデオカメラは、本体941、表示部942、筐体943、外部接続ポート944、リモコン受信部945、受像部946、バッテリー947、音声入力部948、操作キー949、接眼部950などを有する。本発明を用いて作製されたトランジスタは、表示部942の画素部、表示部942を制御する駆動IC、メモリ、デジタル入力処理装置などに用いることができる。

#### 【0166】

この他にも、ナビゲーションシステム、音響再生装置、記録媒体を備えた画像再生装置などに用いることが可能である。これらの表示部の画素部や、表示部を制御する駆動IC、メモリ、デジタル入力処理装置、センサ部などの用途に、本発明を用いて作製されたトランジスタを用いることができる。

#### 【0167】

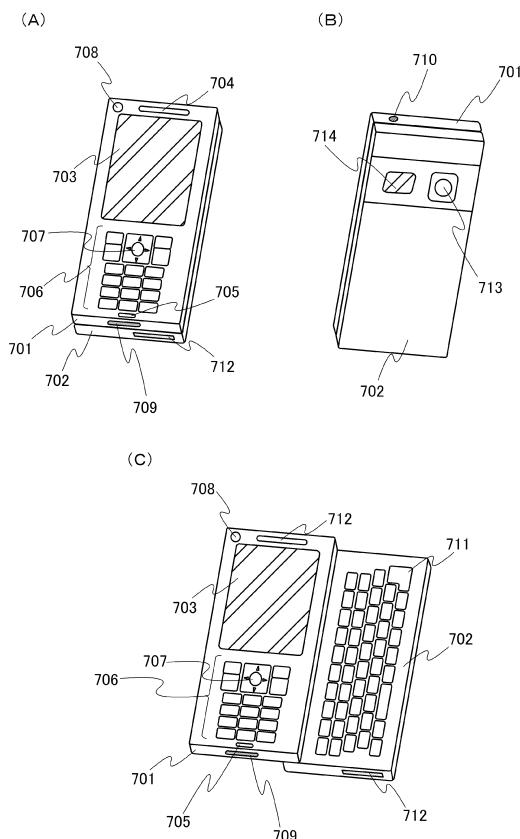

また、図13は、本発明を適用した携帯電話の別の一例であり、図13(A)が正面図、図13(B)が背面図、図13(C)が2つの筐体をスライドさせたときの正面図である。携帯電話700は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能な所謂スマートフォンである。

#### 【0168】

携帯電話700は、筐体701及び筐体702で構成されている。筐体701においては、表示部703、スピーカ704、マイクロフォン705、操作キー706、ポインティングデバイス707、カメラ用レンズ708、外部接続端子709及びイヤホン端子710等を備え、筐体702においては、キーボード711、外部メモリスロット712、裏面カメラ713、ライト714等により構成されている。また、アンテナは筐体701に内蔵されている。本発明に係るSOI基板を用いて作製された半導体素子は、表示部703の画素部、表示部703を駆動する駆動IC、メモリ、音声処理回路などに用いることができる。また、表示部703に、図10で説明した液晶表示装置又は図11で説明したEL表示装置を適用することで、表示むらが少なく画質の優れた表示部とすることができます。

#### 【0169】

また、携帯電話700には、上記の構成に加えて、非接触型ICチップ、小型記録装置

10

20

30

40

50

等を内蔵していてもよい。

【0170】

重なり合った筐体701と筐体702(図13(A)に示す。)は、スライドさせることが可能であり、スライドさせることで図13(C)のように展開する。表示部703とカメラ用レンズ708を同一の面に備えているため、テレビ電話としての使用が可能である。また、表示部703をファインダーとして用いることで、裏面カメラ713及びライト714で静止画及び動画の撮影が可能である。

【0171】

スピーカ704及びマイクロフォン705を用いることで、携帯電話700は、音声記録装置(録音装置)又は音声再生装置として使用することができる。また、操作キー706により、電話の発着信操作、電子メール等の簡単な情報入力操作、表示部に表示する画面のスクロール操作、表示部に表示する情報の選択等を行うカーソルの移動操作等が可能である。

10

【0172】

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード711を用いると便利である。更に、重なり合った筐体701と筐体702(図13(A))をスライドさせることで、図13(C)のように展開させることができる。携帯情報端末として使用する場合には、キーボード711及びポインティングデバイス707を用いて、円滑な操作が可能である。外部接続端子709はACアダプタ及びUSBケーブル等の各種ケーブルと接続可能であり、充電及びパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロット712に記録媒体を挿入し、より大量のデータ保存及び移動が可能になる。

20

【0173】

筐体702の裏面(図13(B))には、裏面カメラ713及びライト714を備え、表示部703をファインダーとして静止画及び動画の撮影が可能である。

【0174】

また、上記の機能構成に加えて、赤外線通信機能、USBポート、テレビワンセグ受信機能、非接触ICチップ又はイヤホンジャック等を備えたものであってもよい。

【0175】

以上のように、本発明により作製された半導体装置の適用範囲は極めて広く、本発明に係る半導体基板を材料として、あらゆる分野の電子機器に用いることができる。

30

【実施例1】

【0176】

本実施例では、単結晶半導体層の表面にプラズマ処理を行った場合の表面特性の変化に関する説明する。

【0177】

本実施例で用いた試料について説明する。まず、単結晶シリコン基板の表面に塩酸が含まれたガスで酸化させることにより酸化膜を形成した。該酸化膜を介して水素イオンを照射して、単結晶シリコン基板に脆化領域を形成した。次に、脆化領域を形成するため水素イオンが添加された単結晶シリコン基板の面と、ガラス基板の表面とを貼り合わせ、熱処理を行い、脆化領域において分離した。以上により、ガラス基板上に酸化膜を介して単結晶シリコン層を形成した。このようにして、ガラス基板上に酸化膜を介して単結晶シリコン層が形成された複数の試料(試料A～試料F)を用意した。

40

【0178】

次に、試料A～試料Fにドライエッティングを行い、単結晶シリコン層の表層部を除去した。ドライエッティングの条件は、ICPエッティング法を用いて、ICP電力1000W、下部電極に投入する電力50W、反応圧力1.5Pa、塩素ガス100sccmとして行った。

【0179】

次に、試料A、試料Bについて単結晶シリコン層に形成された自然酸化膜を除去するた

50

め、三フッ化窒素ガスを用いてドライエッティングを行った。ドライエッティングの条件は、ICPエッティング法を用いて、ICP電力500W(0.71W/cm<sup>2</sup>)、RFバイアス0W、反応圧力1.0Pa、三フッ化窒素ガス50sccm、10秒として行った。次に、試料A、試料Bについて、単結晶シリコン層にレーザビームを照射した。

#### 【0180】

さらに、試料Bについては、レーザビームを照射した後、プラズマ処理を行った。プラズマ処理の条件は、ICP方式で、東京エレクトロン社製の装置(ME-500 ICPプラズマドライエッティング装置)を用い、ICP電力500W(0.11W/cm<sup>2</sup>)、RFバイアス100W(0.61W/cm<sup>2</sup>)、圧力1.35Pa、アルゴンガス流量100sccm、240秒として行った。

10

#### 【0181】

次に、試料C、試料Dについて単結晶シリコン層に形成された自然酸化膜を除去するため、アルゴンガスを用いてドライエッティングを行った。ドライエッティングの条件は、ICPエッティング法を用いて、ICP電力500W(0.11W/cm<sup>2</sup>)、RFバイアス100W(0.61W/cm<sup>2</sup>)、反応圧力1.35Pa、アルゴンガス100sccm、240秒として行った。次に、試料C、試料Dについて、単結晶シリコン層にレーザビームを照射した。

#### 【0182】

さらに、試料Dについては、レーザビームを照射した後、プラズマ処理を行った。プラズマ処理の条件は、試料Bと同様にして行った。

20

#### 【0183】

次に、単結晶シリコン層に形成された自然酸化膜を除去するため、希フッ酸(1/100希釈)を用いてウェットエッティングを行った。次に、試料F、試料Dについて、単結晶シリコン層にレーザビームを照射した。

#### 【0184】

さらに、試料Fについては、レーザビームを照射した後、プラズマ処理を行った。プラズマ処理の条件は、試料Bと同様にして行った。

#### 【0185】

次に、試料A～試料Fについて、単結晶シリコン層の表面粗さの測定を行った。本実施例においてはシリコン層の表面粗さの測定には、原子間力顕微鏡(AFM; Atomic Force Microscope)を用いて、シリコン層の平均面粗さ(Ra)、山谷の最大高低差(P-V)を測定した。

30

#### 【0186】

ここで、平均面粗さ(Ra)とは、JIS B 0601:2001(ISO 4287:1997)で定義されている中心線平均粗さRaを、測定面に対して適用できるよう三次元に拡張したものである。基準面から指定面までの偏差の絶対値を平均した値と表現でき、次式で与えられる。

#### 【0187】

#### 【数3】

$$R_a = \frac{1}{S_0} \int_{Y_1}^{Y_2} \int_{X_1}^{X_2} |F(X, Y) - Z_0| dXdY$$

40

#### 【0188】

なお、測定面とは、全測定データの示す面であり、下記の式で表す。

#### 【0189】

#### 【数4】

$$Z = F(X, Y)$$

#### 【0190】

また、指定面とは、粗さ計測の対象となる面であり、座標(X<sub>1</sub>, Y<sub>1</sub>) (X<sub>1</sub>, Y<sub>2</sub>)

50

) (X<sub>2</sub>, Y<sub>1</sub>) (X<sub>2</sub>, Y<sub>2</sub>) で表される 4 点により囲まれる長方形の領域とし、指定面が理想的にフラットであるとしたときの面積を S<sub>0</sub> とする。なお、S<sub>0</sub> は下記の式で求められる。

### 【0191】

#### 【数5】

$$S_0 = (X_2 - X_1) \cdot (Y_2 - Y_1)$$

### 【0192】

自乗平均面粗さ (R<sub>MS</sub>) とは、断面曲線に対する R<sub>MS</sub> を、測定面に対して適用できるよう、R<sub>a</sub> と同様に三次元に拡張したものである。基準面から指定面までの偏差の自乗を平均した値の平方根と表現でき、次式で与えられる。

### 【0193】

#### 【数6】

$$R_{ms} = \sqrt{\frac{1}{S_0} \int_{Y_1}^{Y_2} \int_{X_1}^{X_2} \{F(X, Y) - Z_0\}^2 dXdY}$$

### 【0194】

また、基準面とは、指定面の高さの平均値を Z<sub>0</sub> とするとき、Z = Z<sub>0</sub> で表される平面である。基準面は XY 平面と平行となる。なお、Z<sub>0</sub> は下記の式で求められる。

### 【0195】

#### 【数7】

$$Z_0 = \frac{1}{S_0} \int_{Y_1}^{Y_2} \int_{X_1}^{X_2} F(X, Y) dXdY$$

### 【0196】

山谷の最大高低差 (P-V) とは、指定面において、最も高い山頂の標高 Z<sub>max</sub> と最も低い谷底の標高 Z<sub>min</sub> の差と表現でき、次式で与えられる。

### 【0197】

#### 【数8】

$$P-V = Z_{max} - Z_{min}$$

### 【0198】

ここでいう山頂と谷底とは JIS B 0601 : 2001 (ISO 4287 : 1997) で定義されている「山頂」「谷底」を三次元に拡張したものであり、山頂とは指定面の山において最も標高の高いところ、谷底とは指定面において最も標高の低いところと表現される。

### 【0199】

本実施例における平均面粗さ (R<sub>a</sub>)、山谷の最大高低差 (P-V) の測定条件を以下に記す。

- ・原子間力顕微鏡 (AFM)：走査型プローブ顕微鏡 SPI 3800N / SPA 500 (セイコーアイノスツルメンツ(株)製)

- ・測定モード：ダイナミックフォースモード (DFM モード)

- ・カンチレバー：SII-DFA 40 (シリコン製バネ定数 42 N/m、共振周波数 250 ~ 390 kHz、探針の先端 R 10 nm)

- ・走査速度：1.0 Hz

- ・測定面積：10 μm × 10 μm

- ・測定点数：256 × 256 点

なお、DFM モードとは、ある周波数 (カンチレバーに固有の周波数) でカンチレバーを共振させた状態で、レバーの振動振幅が一定になるように探針と試料との距離を制御しながら、試料の表面形状を測定する測定モードのことである。この DFM モードは試料の

10

20

30

40

50

表面に非接触で測定するため、試料の表面を傷つけることなく、元の形状を保ったまま測定できる。

#### 【0200】

単結晶シリコン層の表面粗さの測定は、上記条件にて、試料A～試料Fに対して行い、三次元表面形状の像を得た。この得られた測定画像の基板断面の曲率を考慮し、付属のソフトウェアにより、画像の全データから最小二乗法により一次平面を求めてフィッティングし、面内の傾きを補正する一次傾き補正を行い、続いて二次曲線を補正する二次傾き補正を行ったのち、付属のソフトウェアにより、表面粗さ解析を行い、平均面粗さ( $R_a$ )、山谷の最大高低差( $P-V$ )をそれぞれ算出した。

#### 【0201】

表1及び図14に、算出された平均面粗さ $R_a$ と、山谷の最大高低差 $P-V$ を示す。

#### 【0202】

#### 【表1】

|     | 平均面粗さ<br>$R_a$ (nm) | 山谷の最大高低差<br>$P-V$ (nm) |

|-----|---------------------|------------------------|

| 試料A | 3.0                 | 83.2                   |

| 試料B | 1.7                 | 25.7                   |

| 試料C | 2.9                 | 35.8                   |

| 試料D | 1.2                 | 26.1                   |

| 試料E | 2.3                 | 32.4                   |

| 試料F | 1.3                 | 14.1                   |

10

20

#### 【0203】

表1及び図14に示すように、 $NF_3$ ガスを用いたドライエッティングの後にレーザビーム照射を行った試料Aの山谷の最大高低差 $P-V$ が83.2nmだったのに対し、レーザビーム照射の後にArガスを用いたプラズマ処理を行う(試料B)ことによって、25.7nmにまで低減した。また、試料Cと試料Dを比較しても、プラズマ処理を行った試料Dの方が平均面粗さ、山谷の最大高低差とともに低減し、試料Eと試料Fを比較しても、プラズマ処理を行った試料Fの方が平均面粗さ、山谷の最大高低差とともに低減するという結果が得られた。

#### 【0204】

30

次に、試料C及び試料Dについて図15に、SEM(Scanning Electron on Microscope)像を示す。図15(A)は、単結晶半導体層にレーザビームを照射したあと(試料C)のSEM像である。図15(A)には、単結晶半導体層の表面に凸部があることがわかる。図15(B)は、単結晶半導体層にレーザビームを照射し、Arプラズマ処理を行ったあと(試料D)の写真である。単結晶半導体層の表面には凸部が低減されていることがわかる。

#### 【0205】

以上の結果から、プラズマ処理を行うことで、レーザ照射後の平均面粗さや山谷の最大高低差が低減できることが確認できた。

#### 【実施例2】

40

#### 【0206】

本実施例では、単結晶半導体層にレーザビームを照射した後、プラズマ処理を時間を変化させて行った場合の表面特性の変化に関して説明する。

#### 【0207】

まず、単結晶シリコン基板の表面に塩酸が含まれたガスで酸化させることにより酸化膜を形成した。該酸化膜を介して水素イオンを照射して、単結晶シリコン基板に脆化領域を形成した。次に、脆化領域を形成するため水素イオンが添加された単結晶シリコン基板の面と、ガラス基板の表面とを貼り合わせ、熱処理を行い、脆化領域において分離した。以上により、ガラス基板上に酸化膜を介して単結晶シリコン層を形成した。このようにして、ガラス基板上に酸化膜を介して単結晶シリコン層が形成された複数の試料を用意した。

50

## 【0208】

次に、複数の試料の単結晶シリコン層にドライエッチングを行い、単結晶シリコン層の表層部を除去した。ドライエッチングの条件は、ICPエッチング法を用いて、ICP電力150W、RFバイアス40W、反応圧力1.0Pa、塩素ガスの流量100sccmとして行った。

## 【0209】

複数の試料にドライエッチングを行った後、レーザビームを照射した。レーザビームを照射した後、プラズマ処理を行った。プラズマ処理の条件は、東京エレクトロン社製の装置(ME-500 ICPプラズマドライエッチング装置)を用い、ICP方式で、ICP電力500W(0.11W/cm<sup>2</sup>)、RFバイアス100W(0.61W/cm<sup>2</sup>)、圧力1.35Pa、アルゴンガス流量100sccm、処理時間(2分、3分、4分)の条件で行った。プラズマ処理を行っていないものを試料G、プラズマ処理を2分行ったものを試料H、プラズマ処理を3分行ったものを試料I、プラズマ処理を4分行ったものを試料Jとした。

## 【0210】

次に、試料G～試料Jについて、単結晶シリコン層の表面粗さの測定を行った。表面粗さの測定は、実施例1で行った測定と同様にして行った。次に、平均面粗さRaと山谷の最大高低差P-Vをそれぞれ算出した。平均面粗さと山谷の最大高低差の算出方法も実施例1と同様にして行った。

## 【0211】

表2及び図16に、算出された平均面粗さRaと、山谷の最大高低差P-Vを示す。

## 【0212】

## 【表2】

|     | 平均面粗さ<br>Ra(nm) | 山谷の最大高低差<br>P-V(nm) |

|-----|-----------------|---------------------|

| 試料G | 2.2             | 105.3               |

| 試料H | 1.6             | 47.8                |

| 試料I | 1.6             | 24.7                |

| 試料J | 1.4             | 42.1                |

## 【0213】

表2及び図16に示すように、ドライエッチングの後にレーザ照射を行った試料Gの山谷の最大高低差P-Vが105.3nmだったのに対し、Arガスによるプラズマ処理を4分行うこと(試料J)によって、42.1nmに低減した。また、試料Gの平均面粗さRaが2.2nmだったのに対し、試料Jは1.4nmにまで低減した。

## 【符号の説明】

## 【0214】

- 100 単結晶半導体基板

- 102 絶縁膜

- 110 ベース基板

- 112 単結晶半導体層

- 114 レーザビーム

- 121 単結晶半導体層

- 122 単結晶半導体層

- 123 ゲート絶縁層

- 124 ゲート電極層

- 125 ゲート電極層

- 126 マスク

- 127 不純物元素

- 128a n型不純物領域

- 129 チャネル形成領域

10

20

40

50

30

|         |             |    |

|---------|-------------|----|

| 1 3 0   | マスク         |    |

| 1 3 1   | 不純物元素       |    |

| 1 3 2 a | p型不純物領域     |    |

| 1 3 2 b | p型不純物領域     |    |

| 1 3 4 a | 側壁絶縁層       |    |

| 1 3 5 a | ゲート絶縁層      |    |

| 1 3 6   | マスク         |    |

| 1 3 7   | 不純物元素       |    |

| 1 3 8 a | n型不純物領域     | 10 |

| 1 3 8 b | n型不純物領域     |    |

| 1 3 9   | 絶縁膜         |    |

| 1 4 0   | 絶縁膜         |    |

| 1 4 1 a | 配線層         |    |

| 3 0 2   | 単結晶半導体層     |    |

| 3 2 0   | 単結晶半導体層     |    |

| 3 2 2   | 走査線         |    |

| 3 2 3   | 信号線         |    |

| 3 2 4   | 画素電極        |    |

| 3 2 5   | TFT         |    |

| 3 2 7   | 層間絶縁膜       | 20 |

| 3 2 8   | 電極          |    |

| 3 2 9   | 柱状スペーサ      |    |

| 3 3 0   | 配向膜         |    |

| 3 3 2   | 対向基板        |    |

| 3 3 3   | 対向電極        |    |

| 3 3 4   | 配向膜         |    |

| 3 3 5   | 液晶層         |    |

| 3 4 0   | チャネル形成領域    |    |

| 3 4 1   | 高濃度不純物領域    |    |

| 3 4 2   | 高濃度不純物領域    | 30 |

| 4 0 1   | 選択用トランジスタ   |    |

| 4 0 2   | 表示制御用トランジスタ |    |

| 4 0 3   | 半導体膜        |    |

| 4 0 4   | 半導体膜        |    |

| 4 0 5   | 走査線         |    |

| 4 0 6   | 信号線         |    |

| 4 0 7   | 電流供給線       |    |

| 4 0 8   | 画素電極        |    |

| 4 1 0   | 電極          |    |

| 4 1 1   | 電極          | 40 |

| 4 1 2   | ゲート電極       |    |

| 4 1 3   | 電極          |    |

| 4 2 7   | 層間絶縁膜       |    |

| 4 2 8   | 隔壁層         |    |

| 4 2 9   | E-L層        |    |

| 4 3 0   | 対向電極        |    |

| 4 3 1   | 対向基板        |    |

| 4 3 2   | 樹脂層         |    |

| 4 5 1   | チャネル形成領域    |    |

| 4 5 2   | 高濃度不純物領域    | 50 |

|       |              |    |

|-------|--------------|----|

| 5 0 0 | マイクロプロセッサ    |    |

| 5 0 1 | 演算回路         |    |

| 5 0 2 | 演算回路制御部      |    |

| 5 0 2 | 演算回路制御部      |    |

| 5 0 3 | 命令解析部        |    |

| 5 0 4 | 制御部          |    |

| 5 0 5 | タイミング制御部     | 10 |

| 5 0 6 | レジスタ         |    |

| 5 0 7 | レジスタ制御部      |    |

| 5 0 8 | バスインターフェース   |    |

| 5 0 9 | 専用メモリ        |    |

| 5 1 0 | メモリインターフェース  |    |

| 5 1 1 | R F C P U    |    |

| 5 1 2 | アナログ回路部      |    |

| 5 1 3 | デジタル回路部      |    |

| 5 1 4 | 共振回路         |    |

| 5 1 5 | 整流回路         |    |

| 5 1 6 | 定電圧回路        |    |

| 5 1 7 | リセット回路       |    |

| 5 1 8 | 発振回路         | 20 |

| 5 1 9 | 復調回路         |    |

| 5 2 0 | 変調回路         |    |

| 5 2 1 | R F インターフェース |    |

| 5 2 2 | 制御レジスタ       |    |

| 5 2 3 | クロックコントローラ   |    |

| 5 2 4 | インターフェース     |    |

| 5 2 5 | 中央処理ユニット     |    |

| 5 2 6 | ランダムアクセスメモリ  |    |

| 5 2 7 | 専用メモリ        |    |

| 5 2 8 | アンテナ         | 30 |

| 5 2 9 | 容量部          |    |

| 5 3 0 | 電源管理回路       |    |

| 5 5 0 | 加熱温度         |    |

| 6 0 0 | チャンバー        |    |

| 6 0 1 | 石英板          |    |

| 6 0 2 | マルチスピアラルコイル  |    |

| 6 0 3 | マッチングボックス    |    |

| 6 0 4 | R F 電源       |    |

| 6 0 5 | 下部電極         |    |

| 6 0 6 | R F 電源       | 40 |

| 6 1 0 | 基板           |    |

| 7 0 0 | 携帯電話         |    |

| 7 0 1 | 筐体           |    |

| 7 0 2 | 筐体           |    |

| 7 0 3 | 表示部          |    |

| 7 0 4 | スピーカ         |    |

| 7 0 5 | マイクロフォン      |    |

| 7 0 6 | 操作キー         |    |

| 7 0 7 | ポインティングデバイス  |    |

| 7 0 8 | カメラ用レンズ      | 50 |

|       |             |    |

|-------|-------------|----|

| 7 0 9 | 外部接続端子      |    |

| 7 1 0 | イヤホン端子      |    |

| 7 1 1 | キー ボード      |    |

| 7 1 2 | 外部メモリスロット   |    |

| 7 1 3 | 裏面カメラ       |    |

| 7 1 4 | ライト         |    |

| 9 0 1 | 筐体          |    |

| 9 0 2 | 支持台         |    |

| 9 0 3 | 表示部         |    |

| 9 0 4 | スピーカ部       | 10 |

| 9 0 5 | ビデオ入力端子     |    |

| 9 1 1 | 筐体          |    |

| 9 1 2 | 表示部         |    |

| 9 1 3 | キー ボード      |    |

| 9 1 4 | 外部接続ポート     |    |

| 9 1 5 | ポインティングデバイス |    |

| 9 2 1 | 筐体          |    |

| 9 2 2 | 表示部         |    |

| 9 2 3 | 操作キー        |    |

| 9 2 4 | センサ部        | 20 |

| 9 3 1 | 筐体          |    |

| 9 3 2 | 表示部         |    |

| 9 3 3 | レンズ         |    |

| 9 3 4 | 操作キー        |    |

| 9 3 5 | シャッター ボタン   |    |

| 9 4 1 | 本体          |    |

| 9 4 2 | 表示部         |    |

| 9 4 3 | 筐体          |    |

| 9 4 4 | 外部接続ポート     |    |

| 9 4 5 | リモコン受信部     | 30 |

| 9 4 6 | 受像部         |    |

| 9 4 7 | バッテリー       |    |

| 9 4 8 | 音声入力部       |    |

| 9 4 9 | 操作キー        |    |

| 9 5 0 | 接眼部         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

(A)

(B)

---

フロントページの続き

(56)参考文献 特開2007-142229(JP,A)

特開平11-340444(JP,A)

特開2000-294754(JP,A)

特開2009-224721(JP,A)

特開2005-252244(JP,A)

特開平11-102848(JP,A)

特開2005-251912(JP,A)

特開2000-077287(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 27/12