(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-302950

(P2006-302950A)

(43) 公開日 平成18年11月2日(2006.11.2)

(51) Int.C1.

F 1

テーマコード(参考)

HO1L 21/8247 (2006.01)

HO1L 29/792 (2006.01)

HO1L 29/788 (2006.01)

HO1L 27/115 (2006.01)

HO1L 29/78 371

HO1L 27/10 434

5FO83

5F1O1

審査請求 未請求 請求項の数 11 O L (全 16 頁)

(21) 出願番号

(22) 出願日

特願2005-118505 (P2005-118505)

平成17年4月15日 (2005.4.15)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】不揮発性半導体装置および不揮発性半導体装置の製造方法

## (57) 【要約】

【課題】 不揮発性半導体装置の機能を確保することができ、フローティングゲートのしきい値電圧の変動が抑制された不揮発性半導体装置を提供する。

【解決手段】 主表面を有する半導体基板11と、半導体基板11の主表面上に間隔をあけて形成された第1と第2フローティングゲート15a、15bと、第1と第2コントロールゲート12a、12bと、第1コントロールゲート12a上に形成された第1絶縁膜32aと、第2コントロールゲート12b上に形成され、第1絶縁膜32aに接触するように形成された第2絶縁膜32bと、第1絶縁膜32aと、第2絶縁膜32bとを接触させることで、少なくとも第1フローティングゲート15aと第2フローティングゲート15b間に形成された空隙部26aとを備える。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

主表面を有する半導体基板と、

前記半導体基板の主表面上に間隔をあけて形成された第1と第2フロー・ティングゲートと、

前記第1と第2フロー・ティングゲート上の第1と第2コントロールゲートと、

前記第1コントロールゲート上に形成された第1絶縁膜と、

前記第2コントロールゲート上に形成され、前記第1絶縁膜に接触するように形成された第2絶縁膜と、

前記第1絶縁膜と、前記第2絶縁膜とを接触させることで、少なくとも前記第1フロー・ティングゲートと前記第2フロー・ティングゲート間に形成された空隙部と、

を備えた不揮発性半導体装置。 10

**【請求項 2】**

前記空隙部は、前記第1と第2フロー・ティングゲート間から、前記第1と第2コントロールゲートの上端部より上方に亘って形成された、請求項1に記載の不揮発性半導体装置。

。

**【請求項 3】**

前記第1絶縁膜と前記第2絶縁膜とは、酸化シリコン膜より誘電率が低い多孔質の絶縁膜から形成された、請求項1または請求項2に記載の不揮発性半導体装置。 20

**【請求項 4】**

前記第1絶縁膜および前記第2絶縁膜の表面上に形成され、前記第1絶縁膜と前記第2絶縁膜との接触部を覆う第3絶縁膜が形成された、請求項1から請求項3のいずれかに記載の不揮発性半導体装置。 20

**【請求項 5】**

主表面を有する半導体基板と、

前記半導体基板の主表面上に形成された第1と第2フロー・ティングゲートと、

前記第1フロー・ティングゲートと前記第2フロー・ティングゲートとの間に形成され、酸化シリコン膜より誘電率が低く、多孔質の絶縁膜と、

を備えた不揮発性半導体装置。 30

**【請求項 6】**

前記第1と第2フロー・ティングゲート上に形成された第1と第2コントロールゲートをさらに備え、

前記第1フロー・ティングゲートと前記第2フロー・ティングゲートとの間および前記第1コントロールゲートと前記第2コントロールゲートとの間に前記絶縁膜が形成された請求項5に記載の不揮発性半導体装置。 30

**【請求項 7】**

前記絶縁膜の表面上に形成された他の絶縁膜をさらに備える、請求項5または請求項6に記載の不揮発性半導体装置。 30

**【請求項 8】**

半導体基板の主表面上に第1と第2フロー・ティングゲートを形成する工程と、

前記第1と第2フロー・ティングゲート上に第1と第2コントロールゲートを形成する工程と、

前記第1と第2コントロールゲート上に第1と第2絶縁膜を形成し、前記第1絶縁膜と前記第2絶縁膜とを接触させることで、少なくとも前記第1フロー・ティングゲートと前記第2フロー・ティングゲートとの間に空隙部を形成する工程と、

を備えた不揮発性半導体装置の製造方法。 40

**【請求項 9】**

前記第1と第2フロー・ティングゲートおよび前記第1と第2コントロールゲートの表面上に第3絶縁膜を形成する工程をさらに備える、請求項8に記載の不揮発性半導体装置の製造方法。 50

**【請求項 10】**

前記第1絶縁膜および前記第2絶縁膜の表面上に、他の絶縁膜を形成する工程をさらに備える、請求項8または請求項9に記載の不揮発性半導体装置の製造方法。

**【請求項 11】**

半導体基板の主表面上に複数のフローティングゲートを形成する工程と、

前記フローティングゲート間に酸化シリコン膜より誘電率が低く、多孔質の絶縁膜を形成する工程と、

を備えた、不揮発性半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は、フローティングゲート間の容量結合の軽減が図られた不揮発性半導体装置およびその製造方法に関する。

**【背景技術】****【0002】**

一般に、電気的に書き込み、消去可能な不揮発性半導体装置としては、半導体基板の主表面上に形成された複数のフローティングゲート電極と、このフローティングゲート電極上に形成されたコントロールゲート電極とを備えたものが知られている。近年、半導体集積回路の高集積化に伴い、フローティングゲート間の寸法が狭くなり、隣接するフローティングゲート同士間に、大きな容量が生じ易くなっていた。このため、周囲のフローティングゲートの電位によって、フローティングゲートの読み出し時のしきい値電圧が変動するという、いわゆる容量連結による問題が生じていた。

20

**【0003】**

そこで、従来から、隣接するフローティングゲート同士の容量結合が抑制された不揮発性半導体装置が提案されている。例えば、特開2000-100976号公報には、隣接するフローティングゲート間および隣接するコントロールゲート間に空洞が形成された不揮発性半導体装置や、隣接するフローティングゲート間および隣接するコントロールゲート間に酸化シリコンより比誘電率が低い絶縁膜が形成された不揮発性半導体装置が記載されている。

30

**【0004】**

このフローティングゲート電極間およびコントロールゲート電極間に空洞が形成された不揮発性半導体装置の製造工程は、半導体基板の表面上に、複数のコントロールゲート電極を形成する工程と、常圧の気相成長法により絶縁膜を堆積する工程とを備えている。

**【0005】**

そして、絶縁膜を堆積する工程においては、堆積される絶縁膜がコントロールゲート電極間およびコントロールゲート間に埋まりきらず、空洞が形成される。

**【0006】**

また、フローティングゲート電極およびコントロールゲート電極間に、酸化シリコン膜より誘電率が低い絶縁膜が形成された不揮発性半導体装置の製造工程は、半導体基板に複数のコントロールゲート電極を形成する工程と、フローティングゲート電極を形成する工程と、形成されたコントロールゲート電極およびフローティングゲート電極間にフッ素添加ポリイミド(比誘電率2.7)を形成する工程とを備えている。

40

**【0007】**

また、特開2002-76299号公報には、表面を有する半導体基板と、半導体基板の主表面上に形成された溝と、溝に埋込まれた第1絶縁膜と、第1絶縁膜上に間隔を隔てて形成された2つの導電層と、2つの導電層によって挟まれた領域の直下に位置する半導体基板の表面を露出する、第1絶縁膜に形成された開口部と、開口部を埋込むとともに、2つの導電層を覆うように形成された第2絶縁膜と、第2絶縁膜によって埋込まれた開口部内に形成された空隙とを備えた半導体装置が記載されている。

**【0008】**

50

この不揮発性半導体装置においても、2つの導電層の間に位置する空隙により2つの導電層間の容量が低減されている。

【特許文献1】特開2000-100976号公報

【特許文献2】特開2002-76299号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、コントロールゲート間およびフローティングゲート間に空洞が形成された不揮発性半導体装置においては、フローティングゲート間およびコントロールゲート間に空洞を形成する工程において、フローティングゲート間やコントロールゲート間に絶縁膜が入り込む場合が生じやすいという問題があった。また、コントロールゲートの側面やフローティングゲートの側面に形成された膜厚が厚くなり易いという問題があった。これに伴い、隣接するフローティングゲート間の容量結合を抑制することが困難なものとなり、選択されたフローティングゲートのしきい値電圧が変動するという問題があった。さらに、フローティングゲート間およびコントロールゲート間に、酸化シリコン膜より誘電率が小さい低誘電率膜が形成された不揮発性半導体装置においては、水素や水分がゲート絶縁膜に染み出すおそれがあるという問題があり、不揮発性半導体装置の機能が阻害されるという問題があった。

【0010】

本発明は、上記の課題に鑑みてなされたものであり、その目的は、不揮発性半導体装置の機能を確保することができ、フローティングゲートのしきい値電圧の変動が抑制された不揮発性半導体装置を提供することである。

【課題を解決するための手段】

【0011】

本発明に係る不揮発性半導体装置は、主表面を有する半導体基板と、半導体基板の主表面上に間隔をあけて形成された第1と第2フローティングゲートと、第1と第2フローティングゲート上の第1と第2コントロールゲートと、第1コントロールゲート上に形成された第1絶縁膜と、第2コントロールゲート上に形成され、第1絶縁膜に接触するように形成された第2絶縁膜と、第1絶縁膜と、第2絶縁膜とを接触させることで、少なくとも第1フローティングゲートと第2フローティングゲート間に形成された空隙部とを備える。

【発明の効果】

【0012】

本発明に係る不揮発性半導体装置およびその製造方法によれば、不揮発性半導体装置の機能を確保しつつ、フローティングゲートのしきい値電圧の変動を抑制することができる。

【発明を実施するための最良の形態】

【0013】

図1から図17を用いて、本発明に係る不揮発性半導体装置の実施の形態について説明する。

【0014】

(実施の形態1)

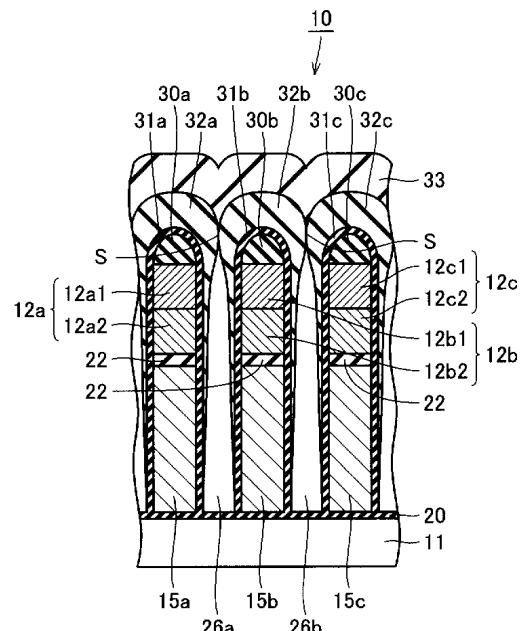

図1は、本実施の形態1に係る不揮発性半導体装置10の平面図である。この図1に示されるように、主表面を有する半導体基板11と、半導体基板11の主表面上に形成され一方向に向けて延在し、間隔を隔てて形成されたアシストゲート13a、13bと、半導体基板11の主表面上に形成されたフローティングゲート(第1フローティングゲート)14a～16a、14c～16cと、フローティングゲート14a～16a、14c～16cと間隔をあけて形成されたフローティングゲート(第2フローティングゲート)14b～16bとを備えている。

【0015】

10

20

30

40

50

また、不揮発性半導体装置 10 は、フローティングゲート 14a～16a、14c～16c 上に形成されたコントロールゲート（第 1 コントロールゲート）12a、12c と、フローティングゲート 14b～16b 上に形成されたコントロールゲート（第 2 コントロールゲート）12b とを備えている。

## 【0016】

フローティングゲート 15a～15c は、アシストゲート 13a、13b 間に形成されており、アシストゲート 13a、13b が延在する方向に沿って、間隔を隔てて、複数形成されている。そして、アシストゲート 13a、13b が延在する方向に隣接するフローティングゲート 14a～16a、14b～16b、14c～16c 間には、空隙部 25a～27a、25b～27b が形成されている。

10

## 【0017】

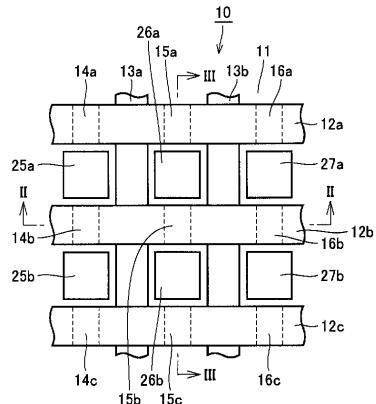

図 2 は、図 1 の II - II 線における断面図である。この図 2 に示されるように、半導体基板 11 の主表面上には、絶縁膜 20 が形成されており、この絶縁膜 20 を介して、半導体基板 11 の主表面上に、アシストゲート 13a、13b と、フローティングゲート 14b～16b とが形成されている。アシストゲート 13a、13b の上面には、キャップ絶縁膜 21a、21b が形成されている。そして、フローティングゲート 14b～16b の上端部側には、ONO 膜 22 が形成されており、このONO 膜 22 を介してコントロールゲート 12b が形成されている。なお、ONO 膜 22 は、例えば酸化シリコン、窒化シリコンおよび酸化シリコンを下層から順に積層して形成されている。そして、フローティングゲート 14b～16b 間には、アシストゲート 13a、13b が配置されており、アシストゲート 13a、13b とフローティングゲート 14b～16b との間には、絶縁膜 23 が形成されている。

20

## 【0018】

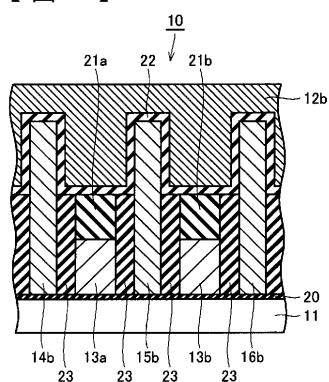

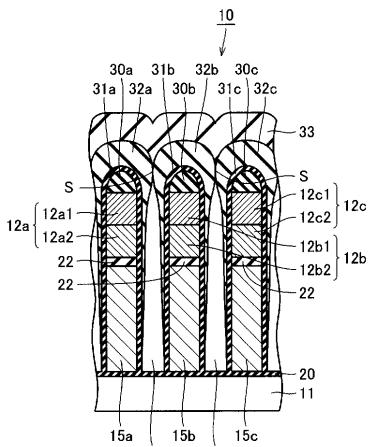

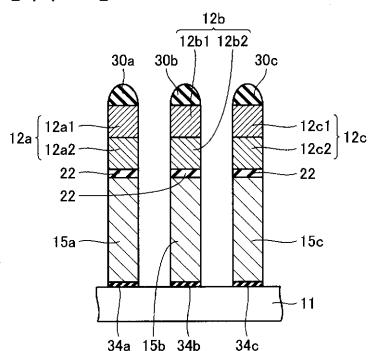

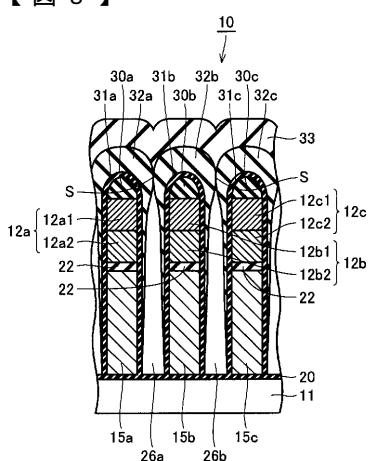

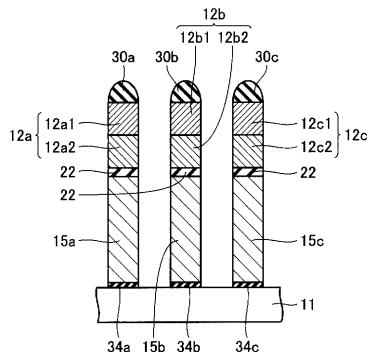

図 3 は、図 1 の III - III 線における断面図である。この図 3 に示されるように、コントロールゲート 12a～12c は、低抵抗な多結晶シリコンからなる導体膜 12a2～12c2 と、この導体膜 12a2～12c2 の上面に形成されたタンクステンシリサイド (WSi<sub>x</sub>) 等のような高融点金属シリサイド膜 12a1～12c1 とから構成されている。このコントロールゲート 12a～12c の上端面には、TEOS (Tetraethoxysilane) 膜が形成されている。そして、このTEOS 膜のキャップ絶縁膜 30a～30c の表面上と、コントロールゲート 12a～12c の側面と、ONO 膜 22 の側面と、フローティングゲート 15a～15c の側面とを覆う絶縁膜 31a～31c が形成されている。

30

## 【0019】

そして、キャップ絶縁膜 30a、30c および絶縁膜 31a、31c を介して、コントロールゲート 12a、12c 上に絶縁膜（第 1 絶縁膜）32a、32c が形成されている。そして、キャップ絶縁膜 30b および絶縁膜 31b を介して、コントロールゲート 12b 上に絶縁膜（第 2 絶縁膜）32b が形成されている。

## 【0020】

そして、絶縁膜 32a、32c は、上方に向かうに従って、側方に膨出するように形成されており、絶縁膜 32b は、絶縁膜 32a、32c に接触するように形成されている。絶縁膜 32a、32c と、絶縁膜 32b とが接触することで、コントロールゲート 12a～12c 間およびフローティングゲート 15a～15c 間は、コントロールゲート 12a～12c より上方で閉塞されている。このため、少なくとも、フローティングゲート 15a、15c と、フローティングゲート 15b との間に空隙部 26a、26b が形成されている。ここで、絶縁膜 32a～32c は、コントロールゲート 12a～12c の上端部から下方に向かうに従って、漸次厚さが薄くなるように形成されている。そして、フローティングゲート 15a～15c の下端部側では、絶縁膜 32a～32c が殆んど形成されおらず、また、フローティングゲート 15a～15c 間に位置する半導体基板 11 の主表面上には、絶縁膜 32a～32c が殆んど形成されていない。

40

## 【0021】

50

このため、形成された空隙部 26a、26b は、コントロールゲート 12a～12c の上端部側から下方に向かうに従って、幅が漸次広くなるように形成されている。特に、コントロールゲート 12a～12c 間およびフローティングゲート 15a～15c 間では、空隙部 26a、26b の幅は広く形成されている。

## 【0022】

そして、絶縁膜 32a～32c 同士の接触部 S は、コントロールゲート 12a～12c より上方に位置している。このため、空隙部 26a、26b は、フローティングゲート 15a～15c 間からコントロールゲート 12a～12c の上端部より上方に亘って形成されている。なお、絶縁膜 32a～32c は、酸化シリコン膜より誘電率の低い多孔質の絶縁膜から形成してもよい。例えば、シリセスキオンサン、ポーラスシリカ、エアロゲル薄膜、HSG-255 等のポーラス膜が好適である。

## 【0023】

そして、このような絶縁膜 32a～32c の表面上に形成され、絶縁膜 32a～32c 同士の接触部 S を覆う絶縁膜 33 が形成されている。この絶縁膜 33 は、耐湿性がよく、絶縁膜 32a～32c と材質が異なる絶縁膜により形成されている。

## 【0024】

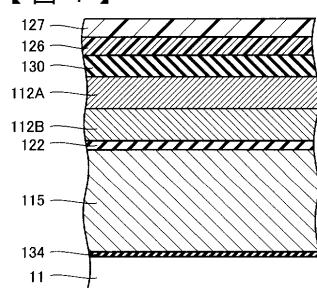

図 4 から図 8 は、上記のように構成された不揮発性半導体装置 10 の製造工程を示す図である。図 4 は、不揮発性半導体装置 10 の第 1 工程を示す断面図である。この図 4 に示されるように、半導体基板 11 の主表面上に絶縁膜 134 を形成する。この絶縁膜 134 は、形成されるフローティングゲートのトンネル絶縁膜として機能する絶縁膜であり、例えば酸窒化シリコン (SiON) 等からなる。

## 【0025】

そして、この絶縁膜 134 の表面上に、例えば低抵抗な多結晶シリコンからなる導体膜 115 を CVD 法等により堆積する。そして、この導体膜 115 の表面上に、酸化シリコンからなる絶縁膜、窒化シリコンからなる絶縁膜および酸化シリコンからなる絶縁膜を CVD 法等により下層から順に堆積することにより、ONO 膜 122 を形成する。続いて、低抵抗な多結晶シリコンからなる導体膜 112A と、導体膜 112A よりも低抵抗な導体膜 112B として、例えばタンゲステンシリサイド等のような高融点金属シリサイド膜とを下層から順に CVD (Chemical Vapor Deposition) 法等により堆積する。

## 【0026】

例えば酸化シリコンからなる絶縁膜 130 を TEOS ガスを用いた CVD 法等により堆積した後、その上に、例えば低抵抗な多結晶シリコンからなるハードマスク膜 126 を CVD 法等により堆積し、さらにその上に、例えば酸窒化シリコン (SiON) からなる反射防止膜 127 を CVD 法等により堆積する。

## 【0027】

次いで、反射防止膜 127 上にコントロールゲート形成用のレジストパターンを形成し、これをエッティングマスクとして反射防止膜 127 およびハードマスク膜 126 をパテニングした後、ワード線形成用のレジストパターンを除去する。続いて、残されたハードマスク膜 126 と反射防止膜 127 との積層膜をエッティングマスクとして、そこから露出される絶縁膜 130、高融点金属シリサイド膜 112A および導体膜 112B をエッティングする。

## 【0028】

図 5 は、不揮発性半導体装置 10 の第 2 工程を示す断面図である。この図 5 に示されるように、形成されたコントロールゲート 12a～12c をマスクとして、図 4 に示された ONO 膜 122 と、導体膜 115 と、絶縁膜 134 とにエッティングを施す。そして、図 5 に示すように、フローティングゲート 15a、15c が形成される。図 6 は、不揮発性半導体装置 10 の第 3 工程を示す断面図である。この図 6 に示されるように、フローティングゲート 15a～15c の両側面と、コントロールゲート 12a～12c の両側面と、キヤップ絶縁膜 30a～30c の表面上に、CVD (Chemical Vapor Deposition) 法等により絶縁膜 31a～31c を形成する。なお、絶縁膜 31a～31c は、シリコン酸化膜

10

20

30

40

50

またはシリコン窒化膜から構成されている。この際、フローティングゲート 15a～15c 間から外方に露出する半導体基板 11 の主表面上に絶縁膜が形成され、図 5 に示す絶縁膜 34a～34c と連結して、半導体基板 11 の主表面上の全面に、絶縁膜 20 が形成される。

【0029】

図 7 は、不揮発性半導体装置 10 の第 4 工程を示す断面図である。この図 7 に示されるように、第 4 工程においては、キャップ絶縁膜 30a～30c および絶縁膜 31a～31c を介して、絶縁膜 32a～32c を形成する。この絶縁膜 32a～32c を形成するには、図示されないプラズマ CVD 装置の成膜ガスの流量を増加させる。ガスの供給量を過剰にすることにより、デポートが上がり、埋め込み性が低下する。例えば、N<sub>2</sub>O ガスの供給量を 500 sccm 以上 600 sccm 以下に設定し、SiH<sub>4</sub> のガス供給量を 3 sccm 以上 5 sccm 以下程度に設定するのが好ましい。

【0030】

特に、絶縁膜 32a～32c の成膜の際に、N<sub>2</sub>O / SiH<sub>4</sub> 比を上げるのが好ましい。N<sub>2</sub>O / SiH<sub>4</sub> 比を上げることにより、カバレッジ (Coverage) を悪化させることができ、埋め込み性を低下させることができる。例えば、N<sub>2</sub>O / SiH<sub>4</sub> 比は、1～2 の範囲が好ましい。

【0031】

さらに、絶縁膜 32a～32c の成膜の際に、成膜温度を通常より低く設定する。成膜温度を低く設定すると、表面反応が停滞し、カバレッジを低下させることができ、埋め込み性を低下させることができる。例えば、成膜温度は、200 以上 250 以下の範囲が好ましい。

【0032】

また、絶縁膜 32a～32c の成膜の際に、プラズマ発生源のパワーを低く設定する。パワーを低く設定することにより、プラズマ密度が下がり、ラジカル (radical) が減少し、カバレッジが低くなり、埋め込み性が低下する。例えば、プラズマ発生源のパワーは、125 W～925 W 程度の範囲が好ましい。

【0033】

そして、絶縁膜 32a～32c の成膜の際に、成膜圧力を通常時より低下させる。成膜圧力が低下すると、成膜の指向性が向上して、コントロールゲート 12a～12c の側面やフローティングゲート 15a～15c の側面に絶縁膜が形成されることが抑制される。例えば、成膜圧力としては、10<sup>-2</sup> Torr 以上 9 torr 以下の範囲が好ましい。

【0034】

このように、成膜ガスの流量と、N<sub>2</sub>O / SiH<sub>4</sub> 比と、成膜温度と、成膜時のパワーと、成膜圧力を調整することにより、絶縁膜 32a、32c の埋め込み性を低下させる。また、コントロールゲート 12a～12c 間およびフローティングゲート 15a～15c 間のアスペクト比は、3.5～5.0 程度と高アスペクト比とされているため、絶縁膜 32a～32b がコントロールゲート 12a～12c 間およびフローティングゲート 15a～15c 間に入り込み難い形状となっている。このため、絶縁膜 32a～32c がコントロールゲート 12a～12c の上端部側に形成される。

【0035】

絶縁膜 32a～32c は、コントロールゲート 12a～12c の上端部に順次積層されると共に、側方に向けて膨出する。さらに、絶縁膜 32a～32c は、成長することにより、隣接するコントロールゲート 12a～12c の上端部に形成された絶縁膜 32a～32c と接触して、コントロールゲート 12a～12c 間の開口部を閉鎖する。この際、絶縁膜 32a～32c は、コントロールゲート 12a～12c の上端部に順次積層された後に、コントロールゲート 12a～12c の開口部を閉鎖するため、絶縁膜 32a～32c の接触部 S は、コントロールゲート 12a～12c の上端部より上方に位置する。また、コントロールゲート 12a～12c の上端部には、キャップ絶縁膜膜 30a～30c が形成されているため、絶縁膜 32a～32c 同士の接触部 S は、確実にコントロールゲート

10

20

30

40

50

12a～12cの上端部より上方に位置する。

【0036】

このため、絶縁膜32a～32cの接触部Sより下方に形成される空隙部26a、26bは、半導体基板11の主表面上からコントロールゲート12a～12cの上端部より上方に亘って形成される。また、絶縁膜32a～32cの埋め込み性が低く設定されているため、コントロールゲート12a～12cの側面およびフローティングゲート15a～15cの側面に絶縁膜32a～32cが形成され難く、空隙部26a、26bの幅は、上端部から下端部に亘って確保されている。特に、フローティングゲート15a～15cは、コントロールゲート12a～12cの下面側に形成されているため、フローティングゲート15a～15cの側面には、絶縁膜32a～32cが形成され難くなっている。 10

【0037】

なお、絶縁膜32a、32cを形成する際には、コントロールゲート12a～12cおよびフローティングゲート15a～15cの表面上に絶縁膜が形成されているため、コントロールゲート12a～12cおよびフローティングゲート15a～15cへのプラズマダメージ等が軽減されている。また、本実施の形態1においては、絶縁膜32a～32cを形成する際には、コントロールゲート12a～12cの上端部には、キャップ絶縁膜30a～30cが残留しているが、除去してもよい。キャップ絶縁膜30a～30cを除去した場合には、形成する絶縁膜32a～32cの形状を制御しやすくなる。このため、絶縁膜32a～32cを、コントロールゲート12a～12cの上端部から上方に向かうに従って、確実に側方に膨出させることができる。 20

【0038】

図8は、不揮発性半導体装置10の第5工程を示す断面図である。この図8に示されるように、絶縁膜32a～32cの表面上に形成され、絶縁膜32a～32c同士の接触部Sを覆うように酸化シリコン等からなる絶縁膜33を形成する。このように、絶縁膜33が絶縁膜32a～32c同士の接触部Sを覆うため、後のCMP(Chemical Mechanical Polishing)工程の際に、空隙部26a、26b内へ水分が入り込むことが抑制されている。 20

【0039】

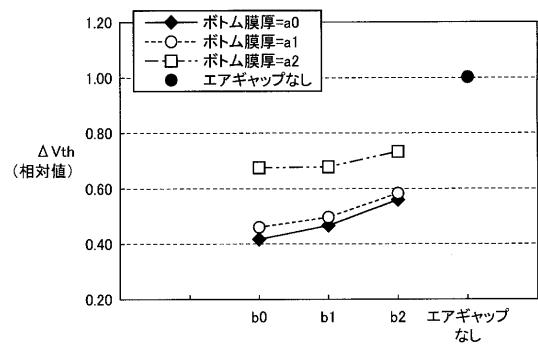

図9は、フローティングゲートのポテンシャルの変動量(相対比)Vthと絶縁膜の厚さとの関係を示したグラフである。この図9において、ボトム膜厚a0、a1、a2とは、図8において、フローティングゲート15a～15c間から外方に露出する半導体基板11の主表面上に形成された絶縁膜の膜厚を意味する。そして、a0=0nm < a1 < a2 < < エアギャップなしとする。また、側壁膜厚b0、b1、b2とは、フローティングゲート15a～15cの側面部分に形成された絶縁膜の厚さを意味する。そして、b0=0nm < b1 < b2 < < エアギャップなしとする。なお、エアギャップとは、図1において、空隙部25a～27a、25b～27b、25c～27cのことを意味し、エアギャップなしとは、フローティングゲート間およびコントロールゲート間が絶縁膜により充填されていることを意味する。 30

【0040】

図1において、フローティングゲート15bと、これに隣接するフローティングゲート14a～14c、15a～15c、16a～16cのうち、いずれかフローティングゲートの電位がVHからVLへ変動したとする。このときのフローティングゲート15bのポテンシャルの変動量(相対比)Vthは、下記式により示される。 40

【0041】

【数1】

$$\Delta V_{th} = \sum_{\alpha=1}^m (C_{fg15b} - f_{g\alpha}) / C_{fgtotal} \times (V_{h\alpha} - V_{l\alpha})$$

【0042】

(但し、(C<sub>fg15b</sub> - f<sub>g</sub>)は、フローティングゲート15bとこれと隣接するフ 50

ローティングゲートとの間の容量、 $m$ は、電位変動したフローティングゲートの数、 $C_{fg tot a1}$ は、フローティングゲート15bとこれに隣接するフローティングゲートとの間に形成される全容量を意味する。)

図9に示されるように、ボトム膜厚が厚くなるほど、 $V_{th}$ が大きくなり、側壁膜厚が大きくなる程、 $V_{th}$ が大きくなる。そして、図8に示された空隙部26a、26bが形成されない場合においては、 $V_{th}$ が大きくなっていることがわかる。すなわち、図1において、空隙部25a～27a、25b～27b、25c～27cの底面および側面に形成された絶縁膜の厚さが薄いほどフローティングゲート14a～14c、15a～15c、16a～16c間の容量結合を低減することができる事が分かる。

#### 【0043】

ここで、本実施の形態1に係る不揮発性半導体装置10の製造工程においては、絶縁膜32a～32cを形成する際に、成膜圧力を低減して、成膜の指向性を向上させているため、空隙部25a～27a、25b～27b、25c～27cの側面に絶縁膜が形成され難くなっている。さらに、絶縁膜32a～32cの成膜工程においては、成膜ガスの流量と、 $N_2O/SiH_4$ 比と、成膜温度と、成膜時のパワーとを上記の範囲に設定することにより、埋め込み性を低く設定しているので、絶縁膜が半導体基板11の主表面にまで到らず、空隙部25a～27a、25b～27b、25c～27cの底面に絶縁膜が形成され難くなっている。このため、本実施の形態1に係る不揮発性半導体装置10においては、フローティングゲート14a～14c、15a～15c、16a～16cのボテンシャルの変動量(相対比) $V_{th}$ が低減されることが分かる。

#### 【0044】

ここで、本実施の形態1に係る不揮発性半導体装置10においては、図3に示されるように、空隙部26a、26bは、フローティングゲート15a～15c間からコントロールゲート12a～12cの上端部より上方に亘って形成されているため、隣接するコントロールゲート12a～12c間に形成される容量が低減されている。また、空隙部26a、26bにより、例えば、フローティングゲート15bと、このフローティングゲート15bに隣接するフローティングゲート15a、15cの上面上のコントロールゲート12a、12cとの間に形成される容量が低減されている。特に、空隙部26a、26bの上端部は、コントロールゲート12a、12cの上端部より上方に位置させることにより、コントロールゲート12a、12cの側面に形成された絶縁膜の膜厚が薄くすることができる。このため、コントロールゲート間12a、12c間の容量および、フローティングゲート15bと、このフローティングゲート15bに隣接するフローティングゲート15a、15cの上面上のコントロールゲート12a、12cとの間に形成される容量を確実に軽減される。

#### 【0045】

このように本実施の形態1に係る不揮発性半導体装置10によれば、図1において、フローティングゲート14a～14c、15a～15c、16a～16c間に形成される容量連結を抑制することができるため、隣接するフローティングゲート14a～14c、15a～15c、16a～16cの電位が変化しても、フローティングゲート14a～14c、15a～15c、16a～16cのしきい値電圧の変動を小さく抑えることができ、正確に読み出しを行なうことができる。さらに、フローティングゲート14a～16cと、このフローティングゲート14a～16cに隣接するフローティングゲート14a～16c上に形成されたコントロールゲート12a～12cとの間の容量を軽減することができる、さらに、正確に読み出しを行なうことができる。特に、絶縁膜32a～32cのうち、フローティングゲート15a～15cの側面の部分の厚さは、薄いため、フローティングゲート15a～15c間の容量を確実に小さく抑えることができる。

#### 【0046】

すなわち、空隙部26a、26bの上端部をコントロールゲート12a～12cの上端部より上方に位置させることにより、コントロールゲート12a～12cの側面およびフローティングゲート15a～15cの側面に形成される絶縁膜32a～32cの膜厚を薄

10

20

30

40

50

くすることができ、フローティングゲート 15 a ~ 15 c およびコントロールゲート 12 a ~ 12 c に形成される容量を小さく低減することができる。

【0047】

また、隣接するコントロールゲート 12 a ~ 12 c 間の容量も低減することができ、動作速度の高速化を確保することができる。特に、絶縁膜 32 a ~ 32 c のうち、コントロールゲート 12 a ~ 12 c の側面の部分の膜厚は、薄く、空隙部 26 a、26 b がコントロールゲート 12 a ~ 12 c の上端部より上方にまで形成されているので、コントロールゲート 12 a ~ 12 c 間に生じる容量を小さく抑えることができる。

【0048】

さらに、上記不揮発性半導体装置 10 の製造方法によれば、絶縁膜 32 a ~ 32 c の成膜工程において、N<sub>2</sub>O / SiH<sub>4</sub> 比を、1 ~ 2 とし、成膜温度を、200 以上 250

10

以下の範囲とし、プラズマ発生源のパワーを、125 W ~ 925 W 程度の範囲とし、成膜圧力を、10<sup>-2</sup> Torr 以上 9 torr 以下の範囲とすることにより、絶縁膜 32 a ~ 32 c をコントロールゲート 12 a ~ 12 c の上端部に確実に形成することができる。すなわち、成膜条件を上記の範囲に設定することにより、絶縁膜 32 a ~ 32 c の埋め込み性を低減させることができ、絶縁膜 32 a ~ 32 c をコントロールゲート 12 a ~ 12 c の上端部側にのみ形成することができる。

【0049】

また、絶縁膜 32 a ~ 32 c の成膜工程前に、コントロールゲート 12 a ~ 12 c の表面上に絶縁膜が形成されているため、絶縁膜 32 a ~ 32 c を形成する際に、コントロールゲート 12 a ~ 12 c およびフローティングゲート 15 a ~ 15 c へのプラズマダメージ等を軽減することができる。さらに、絶縁膜 32 a ~ 32 c の成膜工程後に、絶縁膜 33 を形成するため、後の CMP 工程等の際に、空隙部 26 a、26 b 間へ水分が入り込むことを抑制することができる。

20

【0050】

(実施の形態 2)

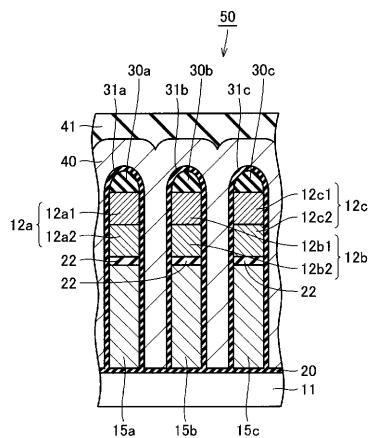

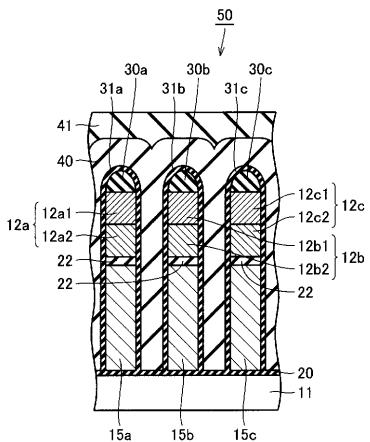

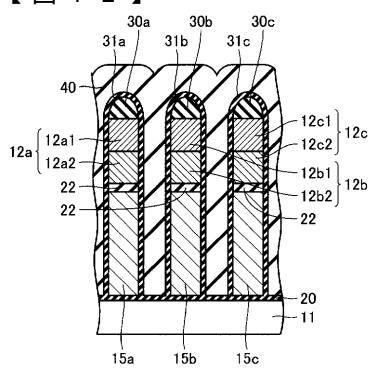

図 10 から図 17 を用いて、実施の形態 2 に係る不揮発性半導体装置 50 について、説明する。図 10 は、本実施の形態 2 に係る不揮発性半導体装置 50 の断面図である。この図 10 に示されるように、不揮発性半導体装置 50 は、半導体基板 11 の主表面上に形成された絶縁膜 20 と、絶縁膜 20 を介して主表面上に形成されたフローティングゲート 15 a ~ 15 c と、このフローティングゲート 15 a ~ 15 c の上面に形成された ONO 膜 22 と、この ONO 膜 22 を介してフローティングゲート 15 a ~ 15 c 上に形成されたコントロールゲート 12 a ~ 12 c とを備えている。

30

【0051】

そして、不揮発性半導体装置 50 は、コントロールゲート 12 a ~ 12 c 間およびフローティングゲート 15 a ~ 15 c 間に、形成された絶縁膜 40 を備えている。この絶縁膜 40 は、酸化シリコン膜より誘電率が低く、多孔質の絶縁膜である。この絶縁膜 40 としては、誘電率が 2.6 程度のポーラス膜が用いられ、具体的には、シリセスキオンサン、ポーラスシリカ、エアロゲル薄膜、HSG-255 (高強度低誘電率有機SOG材料) 等が挙げられる。このようなポーラス膜等から構成された絶縁膜 40 は、複数の孔が内部に形成されている。このため、絶縁膜 40 の表面積は大きく、絶縁膜 40 は、吸湿性や水素を吸収する性質を有している。

40

【0052】

絶縁膜 40 の表面上には、絶縁膜 41 が形成されている。絶縁膜 41 は、絶縁膜 40 と異なり、耐湿性を有する絶縁材料により形成されている。

【0053】

図 11 から図 13 を用いて上記不揮発性半導体装置 50 の製造方法を説明する。図 11 は、不揮発性半導体装置 50 の製造工程の第 1 工程を示す断面図である。この図 11 に示されるように、半導体基板 11 の主表面上に間隔を隔てて形成された絶縁膜 34 a ~ 34 c と、この絶縁膜 34 a ~ 34 c の上面に形成されたフローティングゲート 15 a ~ 1

50

5 c と、フローティングゲート 15 a ~ 15 c の上面に形成された ONO 膜 22 と、この ONO 膜 22 の上面に形成されたコントロールゲート 12 a ~ 12 c と、このコントロールゲート 12 a ~ 12 c とを形成する。なお、コントロールゲート 12 a ~ 12 c の上面には、コントロールゲート 12 a ~ 12 c のマスクとして機能したキャップ絶縁膜 30 a、30 c が残留している。

【0054】

図 12 は、不揮発性半導体装置 50 の製造工程の第 2 工程を示す断面図である。図 12 に示されるように、フローティングゲート 15 a ~ 15 c の側面と、コントロールゲート 12 a ~ 12 c の側面と、キャップ絶縁膜 30 a ~ 30 c の表面上を覆う絶縁膜 31 a ~ 31 c を形成する。そして、フローティングゲート 15 a ~ 15 c 間およびコントロールゲート 12 a ~ 12 c 間に絶縁膜 40 を充填する。

10

【0055】

図 13 は、不揮発性半導体装置 50 の製造工程の第 3 工程を示す断面図である。この図 13 に示されるように、絶縁膜 40 の上面に絶縁膜 41 を形成する。

【0056】

上記のようにして形成された不揮発性半導体装置 50 は、図 10 において、フローティングゲート 15 a ~ 15 c 間に低誘電率膜の絶縁膜 40 が充填されているため、フローティングゲート 15 a ~ 15 c 間に形成される容量を低減することができる。これにより、各フローティングゲート 15 a ~ 15 c のしきい値電圧の変動を抑制することができる。

【0057】

また、絶縁膜 40 がコントロールゲート 12 a ~ 12 c 間にも充填されているため、コントロールゲート 12 a ~ 12 c 間に形成される容量を低減することができる。これにより、動作速度の高速化を図ることができる。また、絶縁膜 40 は、コントロールゲート 12 a ~ 12 c の上端部より上方にまで充填されているため、フローティングゲート 15 a ~ 15 c と、コントロールゲート 12 a ~ 12 c 間に形成される容量も確実に低減することができる。

20

【0058】

また、絶縁膜 40 は、水分や水素を吸着するため、絶縁膜 20 に水分や水素が染み出すことを防止することができる。このため、書き込み動作や読み出し動作および消去動作を正確に行なうことができる。さらに、この絶縁膜 40 の上面には、耐湿性を有する絶縁膜 41 が形成されているため、後の CMP (Chemical Mechanical Polishing) 工程の際に、絶縁膜 40 に水分が入り込むことを防止することができる。このため、絶縁膜 40 の吸湿性や水素を吸着する機能を確保することができる。なお、上記実施の形態 1 および実施の形態 2 においては、AG (アシストゲート) - AND 型のフラッシュメモリに適用した場合について説明したが、これに限られない。

30

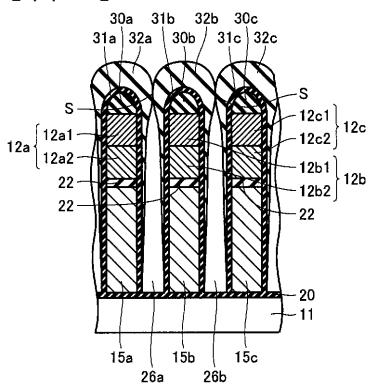

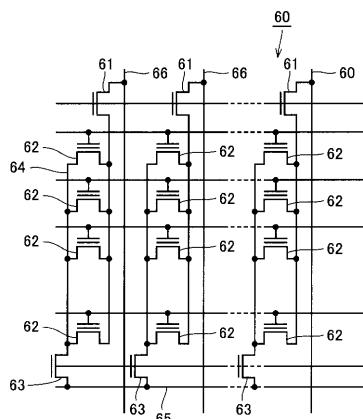

【0059】

図 14 は、一般的な AND 型フラッシュ・アレイ構造 60 を示す回路図である。この図 14 に示されるように、一般的な AND 型フラッシュ・アレイ構造 60 は、ワード線 64 により接続された複数のメモリセルトランジスタ 62 と、主ビット線 66 に接続された選択トランジスタ 61 と、ソース線に接続された選択トランジスタ 63 とを備えている。

40

【0060】

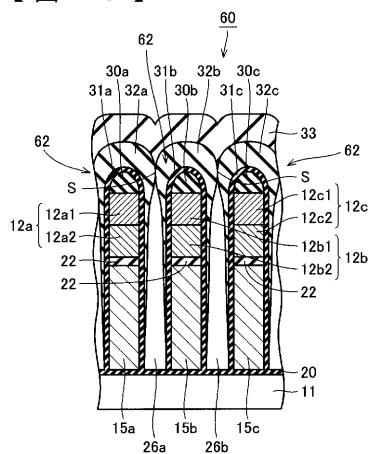

図 15 は、メモリセルトランジスタ 62 の断面図であり、この図 15 に示すように、メモリセルトランジスタ 62 は、フローティングゲート 15 a ~ 15 c 間からコントロールゲート 12 a ~ 12 c の上端部より上方にまで亘って形成された空隙部 26 a、26 b を備えている。また、上記実施の形態 2 と同様に、酸化シリコン膜より誘電率が低く、多孔質性の絶縁膜を、フローティングゲート 15 a ~ 15 c 間からコントロールゲート 12 a ~ 12 c の上端部より上方に亘って、充填してもよい。このように形成された一般的な AND 型フラッシュ・アレイ構造 60 によれば、フローティングゲート 15 a、15 c 同士間等に形成される容量を低減することができ、しきい値電圧の変動を抑制することができる。

50

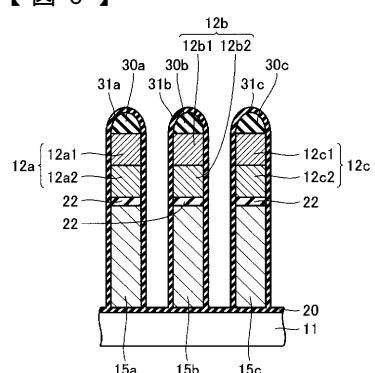

## 【0061】

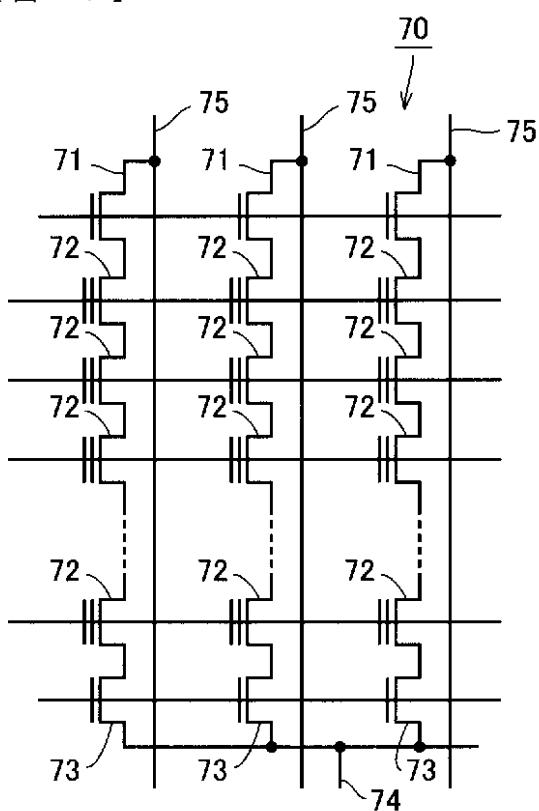

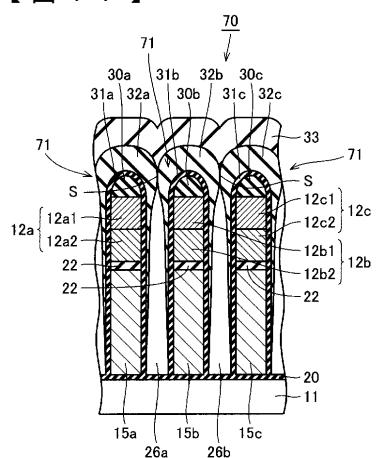

図16は、一般的なNAND型フラッシュ・アレイ構造70を示す回路図である。この図16に示されるように、NAND型フラッシュ・アレイ構造70は、ビット線75にそれぞれ接続された複数の選択トランジスタ71と、ソース線に接続された選択トランジスタ73と、各選択トランジスタ71と各選択トランジスタ73との間に配置された複数のメモリセルトランジスタ72とを備えている。図17は、メモリセルトランジスタ72の詳細断面図であり、この図17に示されるように、メモリセルトランジスタ72は、フローティングゲート15a～15c間からコントロールゲート12a～12cの上端部より上方にまで形成された空隙部26a～26bを備えている。また、上記実施の形態2と同様に、酸化シリコン膜より誘電率が低く、多孔質性の絶縁膜を、フローティングゲート15a～15c間からコントロールゲート12a～12cの上端部より上方に亘って、充填してもよい。このように、構成されたNAND型フラッシュ・アレイ構造70によれば、フローティングゲート15a、15c間に形成される容量を低減することができる。また、上記実施の形態1、実施の形態2に係る不揮発性半導体装置と同様の効果を得ることができる。

10

20

30

40

## 【0062】

以上のように本発明の実施の形態について説明を行なったが、今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

## 【産業上の利用可能性】

## 【0063】

本発明は、不揮発性半導体装置および不揮発性半導体装置の製造方法に良好に適用することができる。

## 【図面の簡単な説明】

## 【0064】

【図1】本実施の形態1に係る不揮発性半導体装置の平面図である。

【図2】図1のI—I-I—I線における断面図である。

【図3】図1のI—I—I—I—I—I線における断面図である。

【図4】不揮発性半導体装置の第1工程を示す断面図である。

【図5】不揮発性半導体装置の第2工程を示す断面図である。

【図6】不揮発性半導体装置の第3工程を示す断面図である。

【図7】不揮発性半導体装置の第4工程を示す断面図である。

【図8】不揮発性半導体装置の第5工程を示す断面図である。

【図9】フローティングゲートのポテンシャルの変動量(相対比)  $V_{th}$  と絶縁膜の厚さとの関係を示したグラフである。

【図10】本実施の形態2に係る不揮発性半導体装置の断面図である。

【図11】不揮発性半導体装置の製造工程の第1工程を示す断面図である。

【図12】不揮発性半導体装置の製造工程の第2工程を示す断面図である。

【図13】不揮発性半導体装置の製造工程の第3工程を示す断面図である。

【図14】一般的なAND型フラッシュ・アレイ構造を示す回路図である。

【図15】メモリセルトランジスタの断面図である。

【図16】一般的なNAND型フラッシュ・アレイ構造を示す回路図である。

【図17】メモリセルトランジスタの詳細断面図である。

## 【符号の説明】

## 【0065】

10 不揮発性半導体装置、11 半導体基板、12a, 12b コントロールゲート、14a～14c、15a～15c、16a～16c フローティングゲート、50 不揮発性半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図13】

【図11】

【図12】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 米持 泰明

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 音居 尚和

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 西田 彰男

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 白竹 茂

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F083 EP02 EP27 EP55 EP76 EP79 JA05 JA35 JA39 JA56 NA05

NA08 PR21

5F101 BA02 BA29 BA36 BB05 BD02 BD34 BD35 BH02