(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5087869号

(P5087869)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

F 1

H01L 21/822 (2006.01)

H01L 27/04

E

H01L 27/04 (2006.01)

H01L 27/04

M

H01L 23/50 (2006.01)

H01L 23/50

X

請求項の数 10 (全 19 頁)

(21) 出願番号

特願2006-187949 (P2006-187949)

(22) 出願日

平成18年7月7日(2006.7.7)

(65) 公開番号

特開2007-67377 (P2007-67377A)

(43) 公開日

平成19年3月15日(2007.3.15)

審査請求日

平成21年6月17日(2009.6.17)

(31) 優先権主張番号

特願2005-228082 (P2005-228082)

(32) 優先日

平成17年8月5日(2005.8.5)

(33) 優先権主張国

日本国(JP)

(73) 特許権者

000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人

100090479

弁理士 井上 一

(74) 代理人

100104710

弁理士 竹腰 昇

(74) 代理人

100124626

弁理士 榎並 智和

(74) 代理人

100124682

弁理士 黒田 泰

(72) 発明者

小松 史和

長野県諏訪市大和3丁目3番5号 セイコ

エプソン株式会社内

最終頁に続く

(54) 【発明の名称】基板の両面に実装可能な集積回路装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項1】

順番に配列された第1～第4の端子を含み、前記第1～第4の端子の中心軸に対して前記第1及び第4の端子が線対称に配置され、前記中心軸に対して前記第2及び第3の端子が線対称に配置され、基板の表面及び裏面の双方のいずれかに選択して実装できる集積回路装置であって、

前記第1及び第2の端子に接続されて、第1及び第2の差動信号対の一方が入力される第1の受信回路と、

前記第3及び第4の端子に接続されて、前記第1及び第2の差動信号対の他方が入力される第2の受信回路と、

前記第1の受信回路からの出力の正転信号と反転信号との一方を、セレクト信号に基づいて選択する第1のセレクタと、

前記第2の受信回路からの出力の正転信号と反転信号との一方を、前記セレクト信号に基づいて選択する第2のセレクタと、

前記第1及び第2のセレクタからの各出力を、前記セレクト信号に基づいて、第1の出力線及び第2の出力線に切り換えて出力する第3のセレクタと、

を有することを特徴とする集積回路装置。

## 【請求項2】

請求項1において、

前記セレクト信号に基づいて設定された第1のモードでは、前記第1及び第2のセレク

10

20

タは、前記第1及び第2の受信回路の各正転信号を選択し、前記第3のセレクタは、前記第1の受信回路の正転信号を前記第1の出力線に、前記第2の受信回路の正転信号を前記第2の出力線にそれぞれ出力し、

前記セレクト信号に基づいて設定された第2のモードでは、前記第1及び第2のセレクタは、前記第1及び第2の受信回路の前記反転信号を選択し、前記第3のセレクタは、前記第1の受信回路の前記反転信号を前記第2の出力線に、前記第2の受信回路の前記反転信号を前記第1の出力線にそれぞれ出力することを特徴とする集積回路装置。

#### 【請求項3】

請求項1または2において、

前記第1及び第2の受信回路の各々に設けられたイネーブル信号入力端子と、

10

前記第1の受信回路の前記イネーブル信号入力端子に、それぞれ異なる第1及び第2のイネーブル信号を前記セレクト信号に基づいて切り換えて入力させる第4のセレクタと、

記第2の受信回路の前記イネーブル信号入力端子に、前記第1のイネーブル信号と、前記第1のイネーブル信号とは異なる第3のイネーブル信号とを、前記セレクト信号に基づいて切り換えて入力させる第5のセレクタと、

をさらに有し、

前記第4及び第5のセレクタは、前記セレクト信号に基づいて互いに異なる前記イネーブル信号を選択することを特徴とする集積回路装置。

#### 【請求項4】

請求項1乃至3のいずれかにおいて、

20

前記第1～第4の端子の各々は、バンプにて形成されていることを特徴とする集積回路装置。

#### 【請求項5】

請求項1乃至4のいずれかにおいて、

第5～第8の端子をさらに含み、前記中心軸に対して前記第5及び第8の端子が線対称に配置され、前記中心軸に対して前記第6及び第7の端子が線対称に配置され、前記第1及び第2の端子、前記第5～第8の端子、前記第3の端子及び前記第4の端子がその順番に配置され、

前記第1及び第2の受信回路と前記第1～第3のセレクタとを一組とする受信ブロックが2つ設けられ、前記2つの受信ブロックにはそれぞれ異なる各2組の差動信号対が入力されることを特徴とする集積回路装置。

30

#### 【請求項6】

請求項5において、

前記第1～第8の端子のうち、同一受信回路に接続された2つの端子には、クロック用差動信号対が入力されることを特徴とする集積回路装置。

#### 【請求項7】

請求項1乃至6のいずれかにおいて、

第1の電源電位が入力される2つの第1電源電位入力端子と、前記第1の電源電位とは異なる第2の電源電位が入力される2つの第2電源電位入力端子とをさらに有し、

前記2つの第1電源電位入力端子が前記中心軸に対して線対称に配置され、前記2つの第2電源電位入力端子が前記中心軸に対して線対称に配置されることを特徴とする集積回路装置。

40

#### 【請求項8】

主要回路が表面に搭載された基板と、

前記基板の前記表面に実装され、前記セレクト信号が表面実装用の論理に設定された請求項1乃至7のいずれかに記載の集積回路装置と、

を有することを特徴とする電子機器。

#### 【請求項9】

主要回路が表面に搭載された基板と、

前記基板の裏面に実装され、前記セレクト信号が裏面実装用の論理に設定された請求項

50

1乃至7のいずれかに記載の集積回路装置と、

を有することを特徴とする電子機器。

【請求項10】

請求項8または9において、

前記基板は、前記集積回路装置が実装された面に形成された信号パターンに接続される

フレキシブル印刷回路基板をさらに有することを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板の両面いずれにも実装可能なインターフェース回路を備えた集積回路裝置及び電子機器に関する。 10

【背景技術】

【0002】

インターフェース回路、例えば高速シリアルインターフェース回路を搭載したドライバI Cが望まれている。例えば、液晶表示装置では、液晶表示部が搭載されるガラス基板の表面にドライバI Cを実装するのが通常である。しかし、機器の設計の都合上や機器のコンパクト化等の種々の要因により、ドライバI Cをガラス基板の裏面に実装したいニーズもある。

【0003】

しかし、ドライバI Cには様々な端子があり、表面実装と裏面実装では、ドライバI Cの端子の位置が逆になってしまふ。よって、ガラス基板上の配線パターンを表面実装、裏面実装で変更すると共に、ドライバI C内の回路配置も変更しなければならず、特に手作業にて配線や回路セル配置が行なわれるマクロセルの変更を伴うので、上記ニーズへの対応が困難であった。 20

【0004】

特に、差動信号対を用いて受信及び/又は送信するインターフェース回路を内蔵するドライバI Cでは、表面実装と裏面実装とで差動信号対のための2つの端子も逆に配置されてしまい、問題をより複雑化させる。下記の特許文献1, 2の発明でも、上述した課題は解決できない。

【特許文献1】特開2001-236303号公報

30

【特許文献2】特開2003-256352号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

そこで、本発明の目的は、マクロセルの変更等を伴わずに、基板の両面いずれにも実装可能なインターフェース回路を備えた集積回路装置及び電子機器を提供することにある。

【課題を解決するための手段】

【0006】

本発明の一態様に係る集積回路装置は、順番に配列された第1～第4の端子を含み、前記第1～第4の端子の中心軸に対して前記第1及び第4の端子が線対称に配置され、前記中心軸に対して前記第2及び第3の端子が線対称に配置され、基板の表面及び裏面の双方のいずれかに選択して実装できる集積回路装置であつて、前記第1及び第2の端子に接続されて、第1及び第2の差動信号対の一方が入力される第1の受信回路と、前記第3及び第4の端子に接続されて、前記第1及び第2の差動信号対の他方が入力される第2の受信回路と、前記第1の受信回路からの出力の正転信号と反転信号との一方を、セレクト信号に基づいて選択する第1のセレクタと、前記第2の受信回路からの出力の正転信号と反転信号との一方を、前記セレクト信号に基づいて選択する第2のセレクタと、前記第1及び第2のセレクタからの各出力を、前記セレクト信号に基づいて、第1の出力線及び第2の出力線に切り換えて出力する第3のセレクタとを有することを特徴とする。 40

【0007】

50

集積回路装置が、基板の表面に実装された場合と、裏面に実装された場合とでは、第1，第2の受信回路に対して、第1，第2の差動信号対の入力位置と符号が逆転する。本発明の一態様では、第1～第4の端子が線対称配置され、実装面の情報がセレクト信号として供給される。このセレクト信号に従って動作する第1～第3のセレクタにより、第1，第2の受信回路からの出力信号の出力位置と符号（正転または反転）が変更される。

#### 【0008】

本発明の一態様では、前記セレクト信号に基づいて設定された第1のモードでは、前記第1及び第2のセレクタは、前記第1及び第2の受信回路の各正転信号を選択し、前記第3のセレクタは、前記第1の受信回路の正転信号を前記第1の出力線に、前記第2の受信回路の正転信号を前記第2の出力線にそれぞれ出力することができる。また、前記セレクト信号に基づいて設定された第2のモードでは、前記第1及び第2のセレクタは、前記第1及び第2の受信回路の前記反転信号を選択し、前記第3のセレクタは、前記第1の受信回路の前記反転信号を前記第2の出力線に、前記第2の受信回路の前記反転信号を前記第1の出力線にそれぞれ出力することができる。10

#### 【0009】

これにより、第1のモードと第2のモードとで、第1，第2の受信回路からの出力信号の出力位置と符号（正転または反転）を逆転させることができる。

#### 【0010】

本発明の一態様では、前記第1及び第2の受信回路の各々に設けられたイネーブル信号入力端子と、前記第1の受信回路の前記イネーブル信号入力端子に、それぞれ異なる第1及び第2のイネーブル信号を前記セレクト信号に基づいて切り換えて入力させる第4のセレクタと、記第2の受信回路の前記イネーブル信号入力端子に、前記第1のイネーブル信号と、前記第1のイネーブル信号とは異なる第3のイネーブル信号とを、前記セレクト信号に基づいて切り換えて入力させる第5のセレクタとをさらに有し、前記第4及び第5のセレクタは、前記セレクト信号に基づいて互いに異なる前記イネーブル信号を選択することができる。20

#### 【0011】

これにより、第1，第2の受信回路の動作タイミングをずらすことができる。例えば、第1，第2の受信回路の一方にクロック用差動信号対が入力される場合、表面実装時でも裏面実装時でも、クロック用差動信号対が入力される側の受信回路を先に動作させて、クロック用差動信号対に基づいたサンプリング信号を、データ受信前に予め生成することができる。30

#### 【0012】

本発明の一態様では、前記第1～第4の端子の各々は、バンプにて形成することができる。こうすると、この集積回路装置をバンプを介して基板に面実装でき、ワイヤボンディングと比べて基板の小型化が図れる。このとき、一つの端子を、シングルバンプにて形成しても、ダブルバンプにて形成しても良い。

#### 【0013】

本発明の一態様では、第5～第8の端子をさらに含み、前記中心軸に対して前記第5及び第8の端子が線対称に配置され、前記中心軸に対して前記第6及び第7の端子が線対称に配置され、前記第1及び第2の端子、前記第5～第8の端子、前記第3の端子及び前記第4の端子がその順番に配置され、前記第1及び第2の受信回路と前記第1～第3のセレクタとを一組とする受信ブロックを2つ設けることができる。この2つの受信ブロックにはそれぞれ異なる各2組の差動信号対が入力される。40

#### 【0014】

このように、2つの受信ブロックに必要な全ての端子を線対称配置させ、かつ、2つの受信ブロックにそれぞれ第1～第3のセレクタを配置することで、各受信ブロックにて差動信号対の出力位置と符号を逆転させることができる。

#### 【0015】

本発明の一態様では、前記第1～第8の端子のうち、同一受信回路に接続された2つの50

端子には、クロック用差動信号対を入力させることができる。

【0016】

外部からのクロック用差動信号対に基づいて、外部から受信されるデータのサンプリング信号を生成することができる。

【0017】

本発明の他の態様は、順番に配列された第1～第4の端子を含み、前記第1～第4の端子の中心軸に対して前記第1及び第4の端子が線対称に配置され、前記中心軸に対して前記第2及び第3の端子が線対称に配置され、基板の表面及び裏面の双方のいずれかに選択して実装できる集積回路装置であって、前記第1及び第2の端子に接続されて、第1及び第2の差動信号対の一方が出力される第1の送信回路と、前記第3及び第4の端子に接続されて、前記第1及び第2の作動信号対の他方が出力される第2の送信回路と、前記第1の作動信号対の元になる第1の信号の正転信号と反転信号との一方を、セレクト信号に基づいて選択する第1のセレクタと、前記第2の差動信号対の元になる第2の信号の正転信号と反転信号との一方を、前記セレクト信号に基づいて選択する第2のセレクタと、10

前記第1及び第2のセレクタからの各出力を、前記セレクト信号に基づいて、前記第1及び第2の送信回路に切り換えて出力する第3のセレクタと有することを特徴とする。

【0018】

集積回路装置が、基板の表面に実装された場合と、裏面に実装された場合とでは、第1，第2の送信回路に対して、第1，第2の差動信号対の出力位置と符号が逆転する。本発明の他の態様では、第1～第4の端子が線対称配置され、実装面の情報がセレクト信号として供給される。このセレクト信号に従って動作する第1～第3のセレクタにより、第1，第2の送信回路からの出力信号の出力位置と符号（正転または反転）が変更される。20

【0019】

本発明の他の態様では、前記セレクト信号に基づいて設定された第1のモードでは、前記第1及び第2のセレクタは、前記第1及び第2の信号の各正転信号を選択し、前記第3のセレクタは、前記第1の信号の正転信号を前記第1の送信回路に、前記第2の信号の正転信号を前記第2の送信回路にそれぞれ出力し、前記セレクト信号に基づいて設定された第2のモードでは、前記第1及び第2のセレクタは、前記第1及び第2の信号の各反転信号を選択し、前記第3のセレクタは、前記第1の信号の反転信号を前記第2の送信回路に、前記第2の信号の反転信号を前記第1の送信回路にそれぞれ出力することができる。30

【0020】

これにより、第1のモードと第2のモードとで、第1，第2の送信回路からの出力信号の出力位置と符号（正転または反転）を逆転させることができる。

【0021】

本発明の他の態様においても、本発明の一態様と同じ理由により、前記第1～第4の端子の各々は、バンプにて形成することができる。

【0022】

本発明の他の態様では、第5～第8の端子をさらに含み、前記中心軸に対して前記第5及び第8の端子が線対称に配置され、前記中心軸に対して前記第6及び第7の端子が線対称に配置され、前記第1及び第2の端子、前記第5～第8の端子、前記第3及び第4の端子がその順番に配置され、前記第1及び第2の送信回路と前記第1～第3のセレクタとを一組とする送信ブロックを2つ設けることができる。この2つの送信ブロックからはそれぞれ異なる各2組の差動信号対が出力される。40

【0023】

このように、2つの送信ブロックに必要な全ての端子を線対称配置させ、かつ、2つの送信ブロックにそれぞれ第1～第3のセレクタを配置することで、各送信ブロックにて差動信号対の出力位置と符号を逆転させることができる。

【0024】

前記第1～第8の端子のうち、同一送信回路に接続された2つの端子からは、クロック用差動信号対を出力させることができる。50

## 【0025】

データ用差動信号対と共にクロック用差動信号対を出力することで、データ用差動信号対を受信する受信回路にて、クロック用差動信号対に基づいたサンプリングクロックにより、データ用差動信号対に基づいたデータをサンプリングすることができる。

## 【0026】

本発明の一態様及び他の態様では、第1の電源電位が入力される2つの第1電源電位入力端子と、前記第1の電源電位とは異なる第2の電源電位が入力される2つの第2電源電位入力端子端子とをさらに有し、前記2つの第1電源電位入力端子を前記中心軸に対して線対称に配置し、前記2つの第2電源電位入力端子を前記中心軸に対して線対称に配置することができる。

10

## 【0027】

こうすると、表面実装または裏面実装により電源入力端子の位置等が逆転しても、線対称位置に同種の電源入力端子が配置されるので、セレクタを設けることなく常に一定の電源電位を入力することができる。

## 【0028】

本発明のさらに他の態様に係る電子機器は、主要回路が表面に搭載された基板と、前記基板の前記表面に実装され、前記セレクト信号が表面実装用の論理に設定された上述の集積回路装置とを有する。あるいは、この電子機器は、主要回路が表面に搭載された基板と、前記基板の裏面に実装され、前記セレクト信号が裏面実装用の論理に設定された上述の集積回路装置とを有することができる。

20

## 【0029】

これらの電子機器は、同一構成の集積回路装置をセレクタ信号の論理によって、表面実装タイプまたは裏面実装タイプに切り換えられている。

## 【0030】

この電子機器に搭載される前記基板は、前記集積回路装置が実装された面に形成された信号パターンに接続されるフレキシブル印刷回路基板をさらに有することができる。このフレキシブル印刷回路基板は、表面実装タイプ及び裏面実装タイプに兼用することができる。

## 【発明を実施するための最良の形態】

## 【0031】

30

以下、本発明の一実施形態について、図面を参照して説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の必須構成要件であるとは限らない。なお、以下の図において同符号のものは同様の意味を表す。

## 【0032】

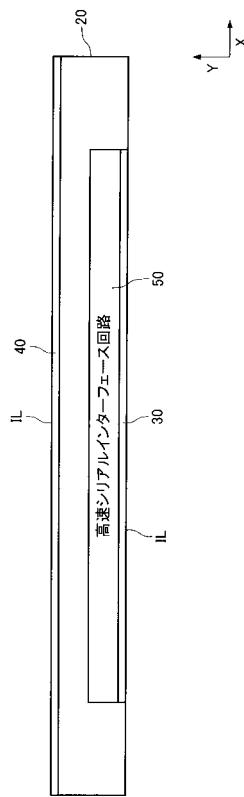

## 1. 表示ドライバ

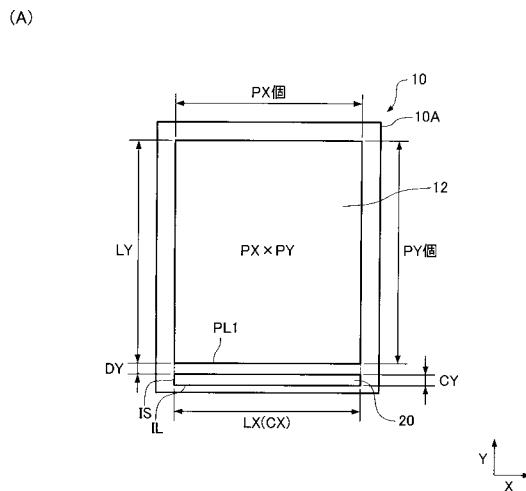

図1(A)は、表示ドライバ20(広義には集積回路装置)が実装された表示パネル10を示す。本実施形態では、表示ドライバ20や、表示ドライバ20が実装された表示パネル10を小型電子機器(図示せず)に搭載することができる。小型電子機器には例えば携帯電話、PDA、表示パネルを有するデジタル音楽プレーヤー等がある。表示パネル10は例えばガラス基板10A上に複数の表示画素が形成される。その表示画素に対応して、Y方向に伸びる複数のデータ線(図示せず)及びX方向に伸びる走査線(図示せず)が表示パネル10に形成される。本実施形態の表示パネル10に形成される表示画素は液晶素子であるが、これに限定されず、EL(Electro-Luminescence)素子等の発光素子であってもよい。また、表示画素はトランジスタ等を伴うアクティブ型であっても、トランジスタ等を伴わないパッシブ型であっても良い。例えば、表示領域12にアクティブ型が適用された場合、液晶画素はアモルファスTFTであっても良いし、低温ポリシリコンTFTであっても良い。

40

## 【0033】

表示ドライバ20のサイズは、X方向の長さCX、Y方向の長さCYに設定される。そ

50

して、長さ  $C_X$  である表示ドライバ 20 の長辺  $I_L$  は、表示領域 12 の表示ドライバ 20 側の一辺  $P_L 1$  と平行である。即ち、表示ドライバ 20 は、その長辺  $I_L$  が表示領域 12 の一辺  $P_L 1$  と平行になるように表示パネル 10 に実装される。

#### 【0034】

図 1 (B) は表示ドライバ 20 サイズを示す図である。長さ  $C_Y$  である表示ドライバ 20 の短辺  $I_S$  と表示ドライバ 20 の長辺  $I_L$  の比は、例えば 1 : 9 ~ 1 : 11 と、その長辺  $I_L$  に対して、その短辺  $I_S$  が非常に短く設定される。このように細長い形状に形成することで、表示ドライバ 20 の Y 方向のチップサイズを極限まで小さくすることができる。

#### 【0035】

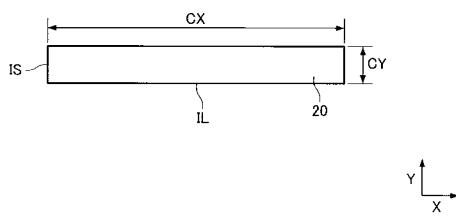

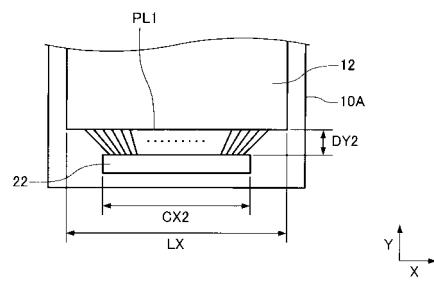

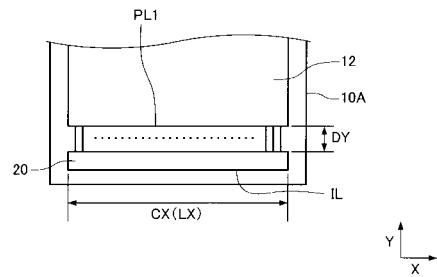

また、図 1 (A) によると、表示領域 12 の X 方向の長さ  $L_X$  は表示ドライバ 20 の X 方向の長さ  $C_X$  と等しい。特に図 1 (A) に限定はされないが、このように長さ  $L_X$  及び長さ  $C_X$  が等しく設定されるのが好ましい。その理由として、図 2 (A) を示す。

#### 【0036】

図 2 (A) に示す表示ドライバ 22 は方向 X の長さが  $C_X 2$  に設定されている。この長さ  $C_X 2$  は、表示領域 12 の一辺  $P_L 1$  の長さ  $L_X$  よりも短いため、図 2 (A) に示すように、表示ドライバ 22 と表示領域 12 とを接続する複数の配線を方向 Y に平行に設けることができない。このため、表示領域 12 と表示ドライバ 22 との距離  $D_Y 2$  を余分に設ける必要がある。これは表示パネル 10 のガラス基板 10 A のサイズを無駄に要するため、コスト削減を妨げる。そして、より小型の電子機器に表示パネル 10 を搭載する場合、表示領域 12 以外の部分が大きくなり、電子機器の小型化の妨げにもなる。

#### 【0037】

これに対して、図 2 (B) に示すように本実施形態の表示ドライバ 20 は、その長辺  $I_L$  の長さ  $C_X$  が表示領域 12 の一辺  $P_L 1$  の長さ  $L_X$  に一致するように形成されているため、表示ドライバ 20 と表示領域 12 との間の複数の配線を方向 Y に平行に設けることができる。これにより、表示ドライバ 20 と表示領域 12 との距離  $D_Y$  を図 2 (A) の場合に比べて短くすることができる。さらに、表示ドライバ 20 の Y 方向の長さ  $I_S$  が短いので、表示パネル 10 のガラス基板 10 A の Y 方向のサイズが小さくなり、電子機器の小型化に寄与できる。

#### 【0038】

なお、本実施形態では、表示ドライバ 20 の長辺  $I_L$  の長さ  $C_X$  が、表示領域 12 の一辺  $P_L 1$  の長さ  $L_X$  に一致するように形成されるが、これに限定されない。例えば、表示ドライバ 20 の長辺  $I_L$  は、表示領域 12 の一辺  $P_L 1$  の長さ  $L_X$  より長く設定されても同様の効果を奏する。

#### 【0039】

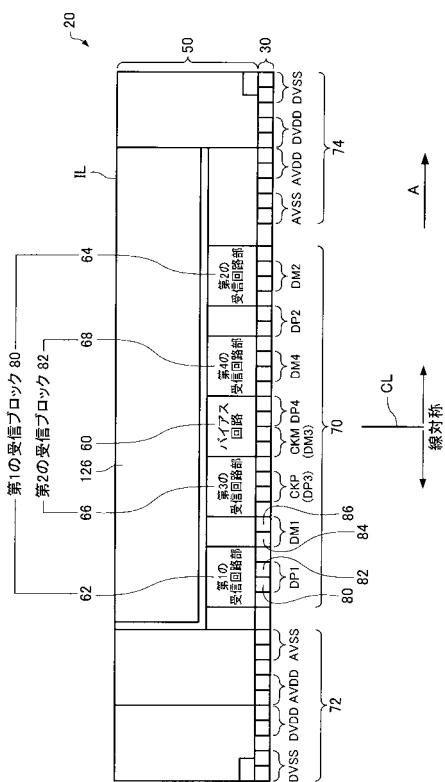

図 3 に示すように、表示ドライバ 20 の 2 つの長辺  $I_L$  に沿って入力パッド領域 30 及び出力パッド領域 40 が設けられている。さらに、表示ドライバ 20 は、長辺  $I_L$  に沿った X 方向の中央領域であって、入力パッド領域 30 の内側領域に高速シリアルインターフェース回路（広義にはインターフェース回路）50 を有する。このような配置とした理由は、高速シリアルインターフェース回路 50 に入力されるデータ信号が重要であるからである。高速シリアルインターフェース回路 50 が長辺  $I_L$  の中央領域にあれば、それに接続されるパッドも長辺  $I_L$  の中央領域に配置される。本実施形態では、パッドにはバンプが形成され、ガラス基板上のパターンに導電性接着剤を介して接続される。表示ドライバ 20 の長辺  $I_L$  の中央領域はバンプの接触性は両端領域よりも良好であり、接触不良に伴いデータ信号が欠損することがない。

#### 【0040】

##### 2. 高速シリアルインターフェース回路

図 4 は、高速シリアルインターフェース 50 及びそれに対応する入力パッド領域 30 の拡大平面図である。高速シリアルインターフェース回路 50 には、表示ドライバ 20 の長辺  $I_L$  の中央領域にバイアス回路 60 が設けられ、例えばバイアス回路 60 の両側に 2 つ

10

20

30

40

50

ずつ、計4つの第1～第4の受信回路部62, 64, 66, 68が設けられている。なお、第1の受信回路部62と第2の受信回路部64とは、例えば表示ドライバの一辺を二等分する中心軸CLに対して線対称配置となっている。同様に、第3の受信回路部66と第4の受信回路部68とは、中心軸CLに対して線対称配置となっている。第1～第4の受信回路部62～68には、バイアス回路60より定電圧、イネーブル信号等が供給される。

#### 【0041】

入力パッド領域30は、長辺ILの中央領域が差動信号入力領域70であり、その両側が第1及び第2の電源入力領域72, 74である。

#### 【0042】

入力パッド領域30には、第1～第4の受信回路部62～68の各々に対応して4つずつ、例えば第1の受信回路部62に対応して4つのバンプ80, 82, 84, 86が設けられ、計16個のバンプが設けられている。本実施形態では、第1～第4の受信回路部62～68は差動信号対(DP, DM)の受信回路部である。差動信号DPはD+、差動信号DMはD-を意味する。後述する通り、表示ドライバ20が基板10Aの表面に実装された時には、第1の受信回路部62にはバンプ80～86を介して第1の差動信号対(DP1, DM1)が入力され、第2の受信回路部64には第2の差動信号対(DP2, DM2)が入力され、第3の受信回路部66には第3の差動信号対(DP3, DM3)が入力され、第4の受信回路部68には第4の差動信号対(DP4, DM4)が入力される。なお、第2の差動信号対(DP2, DM2)は、本実施形態ではクロック用差動信号対(CKP, CKM)である。

10

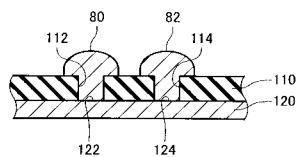

#### 【0043】

隣合う一対のバンプ、例えばバンプ80, 82は、図5に示すように、パッシベーション膜110に設けられた開口112, 114にて露出する、最上層の金属層(本実施形態では第5層金属)120に設けられ2つのパッド122, 124(広義には第1及び第2パッドまたは差動信号入力パッド)上に例えばAu等にて形成されている。この一対のバンプ80, 82は金属層120で導通されたダブルバンプであり、本実施形態では第1の差動信号対(DP1, DM1)の一方の差動信号DM1が共通入力される。従って、本実施形態では2つのバンプ80, 82が広義には一つの端子を構成している。もちろん、この端子は、一つのパッドであっても良いし、ひとつのバンプであっても良いし、あるいは本実施形態のようにダブルバンプであっても良い。

20

#### 【0044】

他の各一対のバンプも同様に導通されたダブルバンプを構成し、各一対のバンプは、それぞれに共通信号が入力される端子として設けられている。

#### 【0045】

これらの差動信号対のためのバンプの両側に、アナログ用VSS電源(AVSS:広義には第1電源)のための各一対のバンプが設けられている。この一対のバンプは、図示しない第1電源電圧入力パッドに接続されている。さらにそれらの外側にアナログ用VDD電源(ADVV:広義には第2電源)のための各一対のバンプが設けられている。この一対のバンプも、図示しない第2電源電圧入力パッドに接続されている。電源入力領域72, 74の両端部側には、ロジック用VDD電源(DVDD:広義には第2電源電圧)のための各一対のバンプが設けられ、この一対のバンプも、図示しない第2電源電圧入力パッドに接続されている。さらにその外側にロジック用VSS電源(DVSS:広義には第1電源電圧)のための各一対のバンプが設けられている。この一対のバンプは、図示しない第1電源電圧入力パッドに接続されている。

30

#### 【0046】

このように、差動信号のためのバンプをダブルバンプとすることで、差動信号ライン途中の接触抵抗を下げる低インピーダンスとすることができます、差動信号の遅延、信号なまりを防止できる。加えて、ダブルバンプとすることで、電流供給端子と電圧測定端子とでバンプを使い分けた四端子法を用いて、終端抵抗を高精度で測定することができる。

40

50

**【 0 0 4 7 】**

ここで、図4に示すように、第1の方向Aに沿って配列された全ての端子は、これら端子配列の中心軸CLに対して線対称に配置されている。図4において、DP1端子とDM2端子は線対称位置にあり、DM1端子とDP2端子は線対称位置にあり、DP3端子とDM4端子は線対称位置にあり、DM3端子とDP4端子は線対称位置にある。加えて、電源入力領域72, 74内の各同一電源端子も線対称位置にある。なお、中心軸CLとは、端子配列の中心を示せば、必ずしも表示ドライバ20の中心軸でなくても良い。

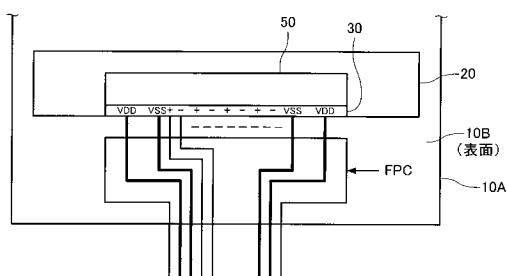

**【 0 0 4 8 】**

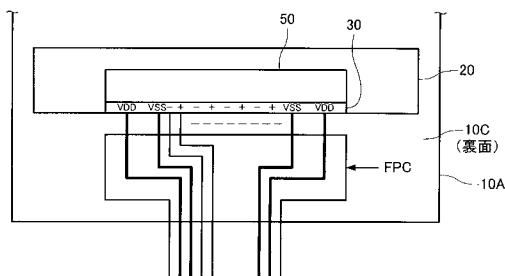

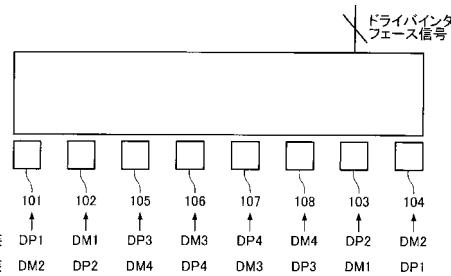

図6は、表示パネル10が形成されるガラス基板（広義には基板）10Aの表面10Bに表示ドライバ20を搭載し、表示ドライバ20とホスト（図示せず）とをフレキシブル印刷回路基板FPCにて接続した状態を模式的に図示している。図7は、ガラス基板10の裏面10Cに、図6と全く同一の表示ドライバ20及びフレキシブル印刷回路基板FPCを搭載した状態を模式的に表している。表面実装と裏面実装とで逆転する差動信号対の位置と符号を示す図である。図4ではダブルバンプを採用したが、図6～図8では説明の便宜上シングルバンプを採用した時のパターンを示しており、かつ、図6及び図7ではVDD, VSSについてアナログ用、ロジック用で分けずにアナログ用VDD, VSSのみ図示した。なお、図8の端子101は図4のダブルバンプ80, 82に対応し、端子102は図4のダブルバンプ84, 86に対応する。

**【 0 0 4 9 】**

図8に示すように、図6の表面実装の場合と図7の裏面実装の場合とでは、4つの差動信号対の位置と極性（+，-）とが逆転する。つまり、図8に示すように、表面実装時に左端に位置するDP1端子は、裏面実装時では、中心軸CLに対して線対称位置となる右端に移動する。逆に、裏面実装時に左端に位置するDM2端子は、表面実装時では、中心軸CLに対して線対称位置となる右端に移動する。

**【 0 0 5 0 】**

このことを、表示ドライバ20側から見ると、図8の端子101に対して、図6の表面実装時にはDP1が入力され、図7の裏面実装時にはDM2が入力されることを意味する。同様に、他の端子102に対しては、図6の表面実装時にはDM1が入力され、図7の裏面実装時にはDP2が入力されることになる。つまり、図4の第1, 第2の受信回路60, 62を第1の受信ブロック80とすると、この第1の受信ブロック80内で切り換えが必要なことが分かる。同様に、図4の第3, 第4の受信回路部66, 68を第2の受信ブロック82とすると、この第2の受信ブロック82内でも切り換えが必要なことが分かる。

**【 0 0 5 1 】****3. 両面実装を可能とする受信切り換え回路**

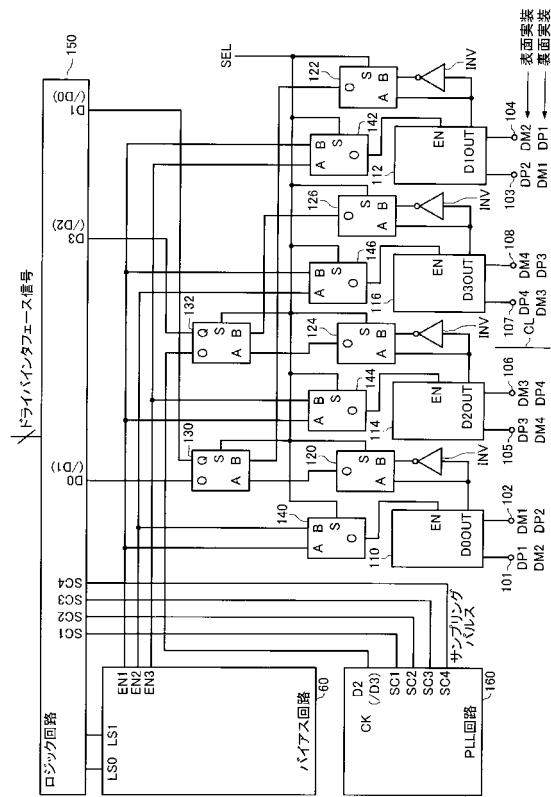

図9は、図6の表面実装と図7の裏面実装の双方を可能とするために表示ドライバ20内に設けられた第1～第4の受信回路部62-68の詳細を示している。

**【 0 0 5 2 】**

図9においても、図4に示す8組のダブルバンプ（計16個のバンプ）を8つの端子101-108（広義には第1～第8の端子）と略記する。

**【 0 0 5 3 】**

図9において、第1の受信回路110は、端子101（広義は第1の端子）及び端子102（広義には第2の端子）に接続されて、第1の差動信号対（DP1, DM1）及び第2の差動信号対（DM2, DP2）の一方が入力される。第2の受信回路112は、端子103（広義は第3の端子）及び端子104（広義には第4の端子）に接続されて、第1の差動信号対（DM1, DP1）及び第2の差動信号対（DP2, DM2）の他方が入力される。

**【 0 0 5 4 】**

同様に、第3の受信回路114は、端子105（広義は第5の端子）及び端子106（広義には第6の端子）に接続されて、第3の差動信号対（DP3, DM3）及び第4の差

10

20

30

40

50

動信号対 (D M 4 , D P 4 ) の一方が入力される。第 4 の受信回路 1 1 6 は、端子 1 0 7 (広義は第 7 の端子) 及び端子 1 0 8 (広義には第 8 の端子) に接続されて、第 3 の差動信号対 (D M 3 , D P 3 ) 及び第 4 の差動信号対 (D P 4 , D M 4 ) の他方が入力される。

#### 【 0 0 5 5 】

ここで、第 1 ~ 第 4 の受信回路 1 1 0 ~ 1 1 6 は例えば差動コンパレータであり、入力される差動信号対に基づいて比較出力を出力する。

#### 【 0 0 5 6 】

第 1 ~ 第 4 の受信回路 1 1 0 ~ 1 1 6 のデータ出力端子は 2 ルートに分岐され、一方のルートに反転素子 (インバータ) I N V が接続されている。よって、第 1 ~ 第 4 の受信回路 1 1 0 ~ 1 1 6 の各々の出力信号 D 0 ~ D 3 は、正転信号とその反転信号に変換される。この意味は、後述する通り、図 6 及び図 7 にて説明した実装形態に応じて差動信号対の符号 (+, -) が逆転して入力されるため、それを補正するためである。10

#### 【 0 0 5 7 】

第 1 ~ 第 4 の受信回路 1 1 0 ~ 1 1 6 の各々の出力信号に基づく正転信号及び反転信号は、第 1 段目の第 1 ~ 第 4 のデータセレクタ 1 2 0 ~ 1 2 6 に入力される。なお、第 1 段目の第 1 , 第 3 のデータセレクタ 1 1 0 , 1 1 4 が広義には第 1 のセレクタであり、第 1 段目の第 2 , 第 4 のデータセレクタ 1 1 2 , 1 1 6 は広義には第 2 のセレクタである。各データセレクタ 1 2 0 ~ 1 2 6 の A 端子には対応する受信回路の正転信号が、B 端子には正転信号がインバータ I N V にて反転された反転信号が入力される。第 1 段目の第 1 ~ 第 4 のデータセレクタ 1 2 0 ~ 1 2 6 は、セレクト端子 (S) より共通に入力されるセレクト信号 S E L の論理に基づいて、対応する各受信回路からの出力に基づく正転信号及び反転信号の一方が選択されて出力端子 (O) より出力される。20

#### 【 0 0 5 8 】

なお、第 1 段目の第 1 , 第 2 のデータセレクタ 1 2 0 , 1 2 2 は、図 4 に示す第 1 の受信ブロック 8 0 に設けられた広義の第 1 , 第 2 のセレクタである。一方、第 1 段目の第 3 , 第 4 のデータセレクタ 1 2 4 , 1 2 6 は、図 4 に示す第 2 の受信ブロック 8 2 に設けられたもので、広義には他の一組の第 1 , 第 2 のセレクタを構成する。

#### 【 0 0 5 9 】

図 1 0 に、セレクト信号と選択される出力との関係が示されている。つまり、セレクト信号 S E L の論理 “1” (表面実装：広義には第 1 のモード) であれば、端子 A の正転信号が選択される。また、セレクト信号 S E L の論理が “0” (裏面実装：広義には第 2 のモード) であれば、表面実装時とは差動信号対の符号が反転されるので、端子 B の反転信号が選択される。なお、本実施形態では、図 6 の表面実装時にセレクト信号 S E L の論理は “1” に、図 7 の裏面実装時にはセレクト信号 S E L の論理は “0” にそれぞれ設定されるが、逆であっても良い。表示ドライバ 2 0 にはセレクト信号 S E L の論理設定手段として例えばヒューズやレジスタが配置されている。このセレクト信号 S E L の論理は、実装形態に応じてユーザが設定しても良いし、あるいは実装形態が予めロット毎に分かっていれば、I C メーカ側にて表示ドライバ 2 0 の製造時に設定することができる。30

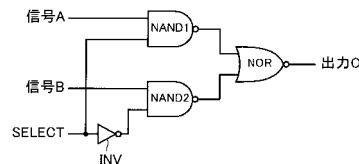

#### 【 0 0 6 0 】

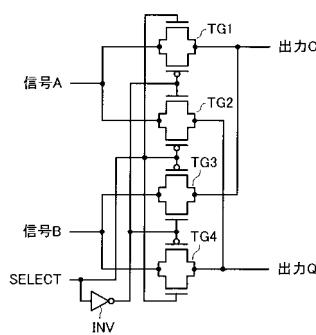

図 1 1 に、図 1 0 に示す真理値表の論理を実現するための回路例を示す。第 1 段目の第 1 ~ 第 4 のデータセレクタ 1 2 0 ~ 1 2 6 は、それぞれ図 1 1 に示す共通の構成を有する。図 1 1 において、第 1 段目の第 1 ~ 第 4 のデータセレクタ 1 2 0 ~ 1 2 6 の各々は、2 つの NAND 回路 N A N D 1 , 2 とノア回路 N O R とインバータ I N V とを有する。一方の NAND 回路 N A N D 1 には入力端子 A からの正転信号とセレクト信号 S E L とが入力され、他方の NAND 回路 N A N D 2 には入力端子 B からの反転信号とセレクト信号 S E L の反転信号が入力される。ノア回路 N O R には 2 つの NAND 回路 N A N D 1 , 2 の出力が入力され、セレクタ出力 O が出力される。40

#### 【 0 0 6 1 】

図 9 において、第 1 段目の第 1 ~ 第 4 のデータセレクタ 1 2 0 ~ 1 2 6 の次段に、第 2

段目の第1及び第2のデータセレクタ130, 132(広義には第3のセレクタ)が設けられている。第2段目の第1のデータセレクタ130には、第1段目の第1, 第2のデータセレクタ120, 122の出力が入力される。第2段目の第2のデータセレクタ132には、第1段目の第3, 第4のデータセレクタ124, 126の出力が入力される。

#### 【0062】

これら第2段目の第1, 第2のデータセレクタ130, 132の各々は、実装形態に応じて信号の行き先を切り換えるものであり、2つの入力端子(A, B)、2つの出力端子(O, Q)及びセレクタ信号入力端子(S)を有する。第2段目の第1, 第2のデータセレクタ130, 132は、セレクト端子(S)より共通に入力されるセレクト信号SELの論理に基づいて、入力端子(A, B)からの入力信号を切り換えて出力端子(O, Q)より出力する。10

#### 【0063】

図12に、セレクト信号と切り換え出力との関係が示されている。つまり、セレクト信号SELの論理“1”(表面実装)であれば、入力端子Aからの信号が出力端子Oから出力され、かつ、端子Bからの信号が出力端子Qより出力される。逆に、セレクト信号SELの論理が“0”(裏面実装)であれば、入力端子Bからの信号が出力端子Oから出力され、入力端子Aからの信号が出力端子Qから出力される。

#### 【0064】

こうして、表面実装時には第1, 第2, 第4の受信回路110, 112, 116からの正転信号D0, D1, D3がロジック回路150に入力され、第3の受信回路114からの正転信号D2がクロック信号CKとしてPLL回路160に入力される。逆に、裏面実装時には、第1, 第2, 第3の受信回路110, 112, 114からの反転信号/D0, /D1, /D2がロジック回路150に入力され、第4の受信回路116からの反転信号/D3がクロック信号CKとしてPLL回路160に入力される。20

#### 【0065】

ここで、上述した切り換えによって、表面実装時に選択される正転信号D0～D3と、裏面実装時に選択される反転信号/D0～/D3との間には、D0=/D1, D1=/D0, D2=/D3, D3=/D2の関係が成立している。よって、表面実装及び裏面実装に拘らず、ロジック回路10の3箇所の各位置に第1の差動信号対(DP1, DM1), 第2の差動信号対(DP2, DM2), 第4の差動信号対(DP4, DM4)に基づくデータ信号が入力され、PLL回路160には第3の差動信号対(DP3, DM3:クロック用差動信号対)に基づくクロック信号CKが入力される。PLL回路160は、入力されたクロック信号CKに基づいて、例えばサンプリングパルスSC1～SC4をロジック回路150に出力する。ロジック回路150では、サンプリングパルスSC1～SC4に基づいて、入力された信号(D0, D1, D3)または(/D0, /D1, /D2)をサンプリングし、ドライバインターフェース信号としてパラレル出力する。30

#### 【0066】

図13は、図12に示す真理値表の論理を実現するための回路例を示す。第2段目の第1, 第2のデータセレクタ130, 132は、それぞれ図12に示す共通の構成を有する。図13において、4つのトランスマニアゲートTG1～TG4とインバータINVが設けられている。トランスマニアゲートTG1, TG2には入力端子Aからの信号が共通入力され、トランスマニアゲートTG3, TG4には入力端子Bからの信号が共通入力される。トランスマニアゲートTG1, TG3の出力線は出力端子Oに、トランスマニアゲートTG2, TG4の出力線は出力端子Qに接続されている。そして、図12に示す真理値表での論理を実現するために、セレクト信号SELの正転信号と反転信号とが、各トランスマニアゲートTG1～TG4に入力される。40

#### 【0067】

図9において、バイアス回路60は、第1～第4の受信回路110～116をイネーブル状態にするための例えば第1～第3のイネーブル信号EN1～EN3を出力する。この第1～第3のイネーブル信号EN1～EN3のいずれか2つを切り換えて、第1～第4の50

受信回路 110～116 のイネーブル信号入力端子 EN に入力させる第 1～第 4 のイネーブル信号セレクタ 140～146 を設けることができる。この第 1～第 4 のイネーブル信号セレクタ 140～146 は、第 1 段目の第 1～第 4 のデータセレクタ 120～126 と同じく、図 10 に示す真理値表に従って作動する図 11 の回路により構成することができる。

#### 【0068】

図 9 に示すように、第 1 のイネーブル信号セレクタ（広義には第 4 のセレクタ）140 は、A 端子に入力される第 1 のイネーブル信号 EN1 と、B 端子に入力される第 2 のイネーブル信号 EN2 とのいずれか一方を、セレクタ信号入力端子 S に入力されるセレクタと信号 SEL の論理に基づき、図 10 に示す真理値表に従って、出力端子 O より出力する。

第 2 のイネーブル信号セレクタ（広義には第 5 のセレクタ）142 は、A 端子に入力される第 3 のイネーブル信号 EN3 と、B 端子に入力される第 1 のイネーブル信号 EN1 とのいずれか一方を、セレクタ信号入力端子 S に入力されるセレクタと信号 SEL の論理に基づき、図 10 に示す真理値表に従って、出力端子 O より出力する。第 3 のイネーブル信号セレクタ 144 は広義の第 4 のセレクタとして機能し、A 端子には第 1 のイネーブル信号 EN1 が、B 端子には第 3 のイネーブル信号 EN3 が入力される。第 4 のイネーブル信号セレクタ 146 は広義の第 5 のセレクタとして機能し、A 端子には第 2 のイネーブル信号 EN2 が、B 端子には第 1 のイネーブル信号 EN1 が入力される。

#### 【0069】

動作上、表面実装時及び裏面実装時のいずれでも、第 1 のタイミング信号 EN1 が先ずアクティブとなる。表面実装時には A 端子が選択される第 1、第 3 のイネーブル信号セレクタ 140、144 が動作し、第 3 の受信回路 114 の出力 D2 がクロック信号 CK として PLL 回路 160 に入力され、PLL 回路 160 にてサンプリングパルス SC1～SC4 を発生させる。裏面実装時では、B 端子が選択される第 2、第 4 のイネーブル信号セレクタ 142、146 が動作し、第 2 の受信回路 112 の出力 /D1 がロジック回路 150 に入力され、第 4 の受信回路 116 の出力 /D3 がクロック信号 CK として PLL 回路 160 に入力される。なお、第 1 のイネーブル信号 EN1 がアクティブとなることで、第 1 の受信回路 110 の出力 D0 がロジック回路 150 に入力可能となるが、この時点では第 1 の作動信号対 (DP1, DM1) は入力されていない。

#### 【0070】

サンプリングパルス SC1～SC4 の発生後に、第 2 及び第 3 のイネーブル信号 EN2 もアクティブとなり、第 1 及び第 3 の受信回路 110、114 からの出力 D0、D2（表面実装時）または /D0、/D2（裏面実装時）がロジック回路 150 に入力可能となる。こうして、受信時には必ずクロック信号 CK が PLL 回路 160 にて先行して生成されるので、出力 D0、D1、D3 または /D0、/D1、/D2 が揃ってロジック回路 150 に入力された時には、クロック信号 CK に基づいたサンプリング動作を適正に実施することができる。

#### 【0071】

##### 4. 両面実装を可能とする送信切り換え回路

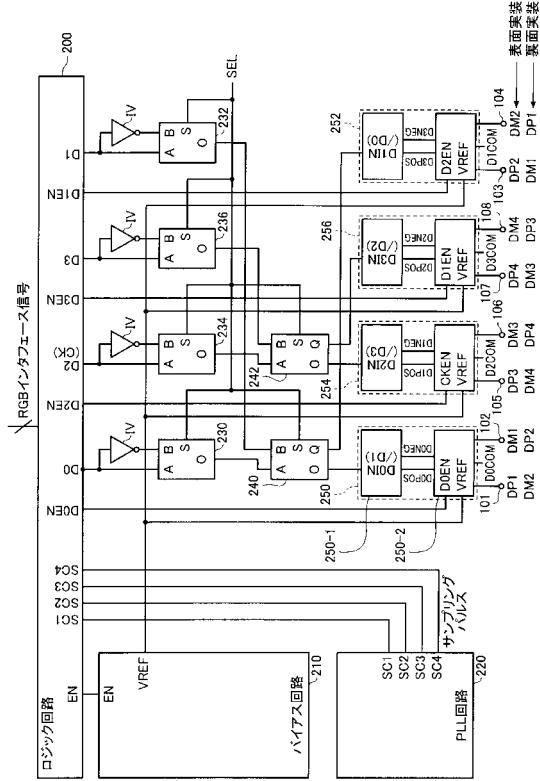

図 4 の第 1～第 4 の受信回路部 62～68 を、第 1～第 4 の送受信回路部または第 1～第 4 の送信回路部に変更することができる。このとき、第 1～第 8 の端子 101～108 は、入出力端子または出力端子として機能する。このいずれの場合にも、表示ドライバ 20 は図 14 に示す例えれば 2 つの送信回路ブロックを内蔵することになる。

#### 【0072】

図 14 に示すロジック回路 200 は、送受信機能を有する場合には図 9 のロジック回路 150 を兼用することができ、別個に設ける必要はない。このロジック回路 200 にはパラレルの RGB インターフェース信号が入力される。この RGB インターフェース信号の一例としては、例えば外部の MPU からの指令により表示ドライバ 20 内の液晶表示データ RAM のデータを書き換えた時に、その書き換えられたデータを MPU 側に読み出す場合の信号を挙げることができる。この場合、ロジック回路 200 からは、信号 D0、D1

10

20

30

40

50

, D<sub>2</sub> ( C K ), D<sub>3</sub> がシリアルで出力される。また、ロジック回路 200 には、バイアス回路 210 よりイネーブル信号 E N が、PLL 回路 220 からはサンプリングパルス S C<sub>1</sub> ~ S C<sub>4</sub> が入力される。なお、図 14 に示すロジック回路 200 が送受信機能を有する場合には、図 14 のバイアス回路 210 と PLL 回路 220 として、図 9 のバイアス回路 60 と PLL 回路 160 を代用でき、別個に設ける必要はない。

#### 【0073】

図 14において、第1段目の第1～第4のデータセレクタ 230～236 が設けられている。なお、第1, 第2のデータセレクタ 239, 232 は第1の送信ブロックに設けられ、第3, 第4のデータセレクタ 234, 236 は第2の送信ブロックに設けられる。第1段目の第1, 第3のデータセレクタ 230, 234 が広義には第1のセレクタであり、第1段目の第2, 第4のデータセレクタ 232, 236 は広義には第2のセレクタである。ロジック回路 200 からのデータは 2 ルートに分岐され、正転信号は第1～第4のデータセレクタ 230～236 の A 端子に、正転信号がインバータ INV にて反転された反転信号は第1～第4のデータセレクタ 230～236 の B 端子に入力される。10

#### 【0074】

第1段目の第1～第4のデータセレクタ 230～236 の各々は、図 9 の第1段目の第1～第4のデータセレクタ 120～126 の各々と同じく、図 10 に示す真理値表に従って動作する図 11 に示す回路にて構成される。つまり、セレクト信号 SEL の論理 “1” (表面実装：広義には第1のモード) であれば、端子 A の正転信号が選択される。また、セレクト信号 SEL の論理が “0” (裏面実装：広義には第2のモード) であれば、表面実装時とは差動信号対の符号が反転されるので、端子 B の反転信号が選択される。20

#### 【0075】

図 14において、第1段目の第1～第4のデータセレクタ 230～236 の次段に、第2段目の第1及び第2のデータセレクタ 240, 242 (広義には第3のセレクタ) が設けられている。第1の送信ブロックに設けられる第2段目の第1のデータセレクタ 240 には、第1段目の第1, 第2のデータセレクタ 230, 232 の出力が入力される。第2の送信ブロックに設けられる第2段目の第2のデータセレクタ 242 には、第1段目の第3, 第4のデータセレクタ 234, 236 の出力が入力される。

#### 【0076】

これら第2段目の第1, 第2のデータセレクタ 240, 242 の各々は、実装形態に応じて信号の行き先を切り換えるものであり、図 9 の第2段目の第1, 第2のデータセレクタ 130, 132 の各々と同じく、2つの入力端子 (A, B)、2つの出力端子 (O, Q) 及びセレクタ信号入力端子 (S) を有する。セレクト信号 SEL の論理 “1” (表面実装) であれば、入力端子 A からの信号が出力端子 O から出力され、かつ、端子 B からの信号が出力端子 Q より出力される。逆に、セレクト信号 SEL の論理が “0” (裏面実装) であれば、入力端子 B からの信号が出力端子 O から出力され、入力端子 A からの信号が出力端子 Q から出力される。30

#### 【0077】

こうして、表面実装時にはロジック回路 200 からの正転信号 D<sub>0</sub>～D<sub>3</sub> が第2段目の第1, 第2のデータセレクタ 240, 242 から出力される。このうち、本実施形態ではデータ D<sub>2</sub> がクロック信号 CK となる。一方、裏面実装時には、ロジック回路 200 からの正転信号 D<sub>0</sub>～D<sub>4</sub> がインバータ INV にてそれぞれ反転された反転信号 /D<sub>0</sub>～/D<sub>3</sub> が、第2段目の第1, 第2のデータセレクタ 240, 242 から出力される。このうち、反転信号 /D<sub>3</sub> がクロック信号 CK となる。40

#### 【0078】

第2段目の第1, 第2のデータセレクタ 240, 242 の後段には、第1～第4の送信回路 250～256 が設けられている。第1, 第2の送信回路 250, 252 は第1の送信ブロックに設けられ、第3, 第4の送信回路 254, 256 は第2の送信ブロックに設けられる。

#### 【0079】

10

20

30

40

50

ここで、図8と同様に、図14においても、表面実装時には端子101（広義は第1の端子）より信号D P 1が、端子102（広義には第2の端子）より信号D M 1が、端子103（広義は第3の端子）から信号D P 2が、端子104（広義には第4の端子）から信号D M 2が、端子105（広義は第5の端子）から信号D P 3が、端子106（広義には第6の端子）から信号D M 3が、端子107（広義は第7の端子）から信号D P 4が、端子108（広義には第8の端子）から信号D M 4が出力される。一方、裏面実装時には端子101より信号D M 2が、端子102より信号D P 2が、端子103から信号D M 1が、端子104から信号D P 1が、端子105から信号D M 4が、端子106から信号D P 4が、端子107から信号D M 3が、端子108から信号D P 3が出力される。

## 【0080】

10

ここで、上述した切り換えによって、表面実装時には、第1の送信回路250に正転信号D 0が、第2の送信回路252に正転信号D 1が、第3の送信回路254に正転信号D 2が、第4の送信回路256に正転信号D 3がそれぞれ入力される。一方、裏面実装時には、第1の送信回路250に反転信号/D 1が、第2の送信回路252に反転信号/D 0が、第3の送信回路254に反転信号/D 3が、第4の送信回路256に反転信号/D 2がそれぞれ入力される。

## 【0081】

この際、D 0及び/D 0はD P 1, D M 1を生成する元信号であり、D 1及び/D 1はD P 2, D M 2を生成する元信号であり、D 2及び/D 2はD P 3, D M 3を生成する元信号であり、D 3及び/D 3はD P 4, D M 4を生成する元信号である。よって、実装形態に応じて、図8の通りに、各端子101～108に適正な信号を送信することができる。

20

## 【0082】

第1～第4の送信回路250～256の各々は、図14に示すように、プリドライバと送信ドライバとを有する。例えば、第1の送信回路250に設けられたプリドライバ250-1は、第2段目の第1のデータセレクタ240からの信号(D 0または/D 1)に基づいて、正極性信号D 0 P O Sと負極性信号D 0 N E Gとを出力する。第1の送信回路250に設けられた送信ドライバ250-2は、プリドライバ250-1からの信号に基づいて、かつ、ロジック回路200からのイネーブル信号D 0 E Nと参照電圧V R E Fとに基づいて、信号D P 1, D M 1を生成する。なお、送信ドライバ250-2の出力D 0 C O Mは、送信回路250にてコモン電圧を制御するために、バイアス回路210内のオペアンプにフィードバックする信号であり、表示ドライバ20の外部に出力されるものではない。第2～第3の送信回路252～256も、プリドライバ252-1～256-1と、送信ドライバ252～256-2を有し、第2段目の第1, 第2のデータセレクタ240, 242からの出力と、ロジック回路200からのイネーブル信号D 1 E N～D 3 E N及び参照電圧V R E Fとに基づいて、信号D P 2～D P 4, D M 2～D M 4を送信する。なお、イネーブル信号D 0 E N～D 3 E Nは、表面実装時または裏面実装時にクロックC Kを発生させる送信回路を他の送信回路に先駆けて動作させるタイミングに設定される。

30

## 【0083】

## 5. 变形例

40

上記のように、本発明の実施形態について詳細に説明したが、本発明の新規事項及び効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。したがって、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書または図面において、少なくとも一度、より広義又は同義な異なる用語と共に記載された用語は、明細書または図面のいかなる箇所においても、その異なる用語に置き換えることができる。

## 【0084】

本発明に係るインターフェース回路は、上述した液晶ドライバI C内のインターフェース回路に限定されない。また、本発明のインターフェース回路は、U S BやI E E E 1394、あるいはO T Gに適用することもできる。

50

**【0085】**

なお、図6～図8に示すように、図4のようなバンプ配列を採用した結果、ガラス基板10A及びフレキシブル印刷回路基板FPC上の各配線パターンでは、4組の差動信号対の信号線は、一定電位の電源線、図6では2本のVSS電源線に挟まれて配置されることになる。ここで、ガラス基板10A上に形成される配線パターンは、単一層しか実現できないので、異なるパターンは交差できず、表示ドライバ20のパッド配列に従ったパターン配列とせざるを得ない。しかも、ガラス基板10A上ではマイクロストリップのように多層配線は不可能である。

**【0086】**

本実施形態の高速シリアルインターフェース回路50に入力される差動信号の信号振幅は小さく、シリアル転送による高速化により外部ノイズの影響を受けやすい。しかし、図6に示すように、4組の差動信号線対の両側にVSS電源線（ダブルパッドの場合は両側に各2本のVSS電源線）を配置することにより、差動信号線対をその両側のVSS電源線によりシールドすることができる。この結果、外部ノイズとしてEMIノイズ対策ができる他、電界の遮蔽効果による電圧性ノイズ対策と、磁界の遮蔽効果による電流性ノイズ対策とを実現することができる。10

**【図面の簡単な説明】****【0087】**

【図1】図1(A)及び図1(B)は、本実施形態に係る集積回路装置を示す図である。

【図2】図2(A)は本実施形態に係る比較例の一部を示す図であり、図2(B)は本実施形態に係る集積回路装置の一部を示す図である。20

【図3】本実施形態に係る集積回路装置の一部の平面レイアウトを示す図である。

【図4】図3に示す高速シリアルインターフェース回路及びそれに対応する入力パッド領域の拡大平面図である。

【図5】図4に示すダブルバンプの断面図である。

【図6】表示ドライバがガラス基板の表面に実装された状態を示す図である。

【図7】表示ドライバがガラス基板の裏面に実装された状態を示す図である。

【図8】表面実装と裏面実装とで逆転する差動信号対の位置と符号を示す図である。

【図9】2つの受信回路ブロックを示す図である。

【図10】図9に示す第1段目の第1～第4のデータセレクタでの切り換え論理を示す図である。30

【図11】図9に示す第1段目の第1～第4のデータセレクタ及び第1～第4のイネーブル信号セレクタの回路例を示す図である。

【図12】図9に示す第2段目の第1, 第2のデータセレクタでの切り換え論理を示す図である。

【図13】図9に示す第2段目の第1, 第2のデータセレクタの回路例を示す図である。

【図14】2つの送信回路ブロックを示す図である。

**【符号の説明】****【0088】**

10 表示パネル、10A 基板、10B 表面、10C 裏面、20 表示ドライバ

、30 入力パッド領域、50 高速シリアルインターフェース、60, 210 バイアス回路、62～68 第1～第4の受信回路部、101～108 第1～第8の端子、110～116 第1～第4の受信回路、120～126, 230～236 第1段目の第1～第4のデータセレクタ、130, 132, 240, 242 第2段目の第1, 第2のデータセレクタ、140～146 第1～第4のイネーブル信号セレクタ、150, 200 ロジック回路、160, 230 PLL回路、250～256 第1～第4の送信回路40

【図1】

(B)

【図2】

(B)

【 3 】

【図4】

【図5】

【図6】

【図7】

【図9】

【 四 8 】

【図10】

| SELECT | 出力O |

|--------|-----|

| 1      | A   |

| 0      | B   |

【 図 1 1 】

( 1 2 )

| SELECT | 出力O | 出力Q |

|--------|-----|-----|

| 1      | A   | B   |

| 0      | B   | A   |

【 図 1 3 】

【図14】

---

フロントページの続き

(72)発明者 井伊 巨樹

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 須原 宏光

(56)参考文献 特開2005-198024(JP,A)

特開平10-303366(JP,A)

特開2004-341101(JP,A)

特開2000-208717(JP,A)

特開2001-183689(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 23/50

H01L 27/04

H01L 29/792

H01L 29/786

H01L 21/336

G02F 1/133