(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0103337

(43) 공개일자 2014년08월26일

- (51) 국제특허분류(Int. Cl.)

**H01L 33/14** (2010.01)

- (21) 출원번호 10-2014-7019705(분할)

- (22) 출원일자(국제) 2008년02월19일

심사청구일자 2014년08월06일

- (62) 원출원 특허 10-2014-7007701

원출원일자(국제) 2008년02월19일

심사청구일자 2014년03월24일

- (85) 번역문제출일자 2014년07월15일

- (86) 국제출원번호 PCT/US2008/002140

- (87) 국제공개번호 WO 2008/112064

국제공개일자 2008년09월18일

- (30) 우선권주장

11/715,687 2007년03월08일 미국(US)

- (71) 출원인

**크리 인코포레이티드**

미국 노쓰 캐롤라이나 27703-8475 더럼 실리콘 드

라이브 4600

- (72) 발명자

**에머슨 테이비드 토드**

미국 노쓰캐롤라이나 27516 더럼 뉴 라이즈 코트

5519

**해버린 케빈**

미국 노쓰캐롤라이나 27511 캐리 롱브릿지 드라이

브 105

(뒷면에 계속)

- (74) 대리인

**백만기, 양영준, 정은진**

전체 청구항 수 : 총 14 항

(54) 발명의 명칭 전류 저감 구조물들을 갖는 발광 소자들 및 전류 저감 구조물들을 갖는 발광 소자들을 형성하는 방법

### (57) 요 약

발광 소자는 p형 반도체 층, n형 반도체 층, 및 상기 p형 반도체 층과 상기 n형 반도체 층 사이의 활성 영역을 포함한다. 와이어 본딩 패드와 같은 불투명 특징부가 상기 p형 반도체 층 상에, 또는 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 배치되며, 감소된 도전성 영역은 상기 p형 반도체 층 또는 상기 n형 반도체 층 내에 배치되며 상기 불투명 특징부와 정렬된다. 상기 감소된 도전성 영역은 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장될 수 있으며, 또는 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장될 수 있다.

### 대 표 도 - 도1

(72) 발명자

**버그만 마이클 존**

미국 노쓰캐롤라이나 27516 채플 힐 하이더웨이 드

라이브 5700

**슬라티 테이비드**

미국 노쓰캐롤라이나 27617 룰리 케이프 찰스 드라

이브 6424

**도노프리오 매튜**

미국 노쓰캐롤라이나 27613 룰리 노쓰 크릭 런

8120

**에드몬드 존**

미국 노쓰캐롤라이나 27511 캐리 웨스트 줄스 번

웨이 206

## 특허청구의 범위

### 청구항 1

발광 소자로서,

p형 반도체 층;

n형 반도체 층;

상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역;

상기 활성 영역에 대향하는, 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 하나의 층 상의 본딩 패드 - 상기 본딩 패드는 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 하나의 층에 전기적으로 연결됨 -;

상기 본딩 패드로부터 확장하며 상기 본딩 패드에 전기적으로 연결된 도전성 핑거; 및

상기 도전성 핑거와 정렬되는 상기 발광 소자 내의 감소된 도전성 영역

을 포함하는 발광 소자.

### 청구항 2

제1항에 있어서,

상기 감소된 도전성 영역은 또한 상기 본딩 패드와 정렬되는 발광 소자.

### 청구항 3

제1항에 있어서,

상기 본딩 패드는 제1 본딩 패드이고, 상기 도전성 핑거는 제1 도전성 핑거이고, 상기 감소된 도전성 영역은 제1 감소된 도전성 영역이며,

상기 발광 소자는,

상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층에 전기적으로 연결되는 제2 본딩 패드;

상기 제2 본딩 패드로부터 연장하며 상기 제2 본딩 패드에 전기적으로 연결되는 제2 도전성 핑거; 및

상기 제2 도전성 핑거와 정렬되는 상기 발광 소자 내의 제2 감소된 도전성 영역

을 더 포함하는 발광 소자.

### 청구항 4

제3항에 있어서,

상기 제2 감소된 도전성 영역은 또한 상기 제2 본딩 패드와 정렬되는 발광 소자.

### 청구항 5

제3항에 있어서,

상기 제2 본딩 패드와 상기 제2 도전성 핑거는, 상기 활성 영역에 대향하는, 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층 상에 존재하는 발광 소자.

### 청구항 6

제3항에 있어서,

상기 제2 본딩 패드와 상기 제2 도전성 핑거는, 상기 활성 영역에 인접하는, 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층 상에 존재하는 발광 소자.

**청구항 7**

제5항에 있어서,

상기 활성 영역에 대향하는, 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층 상에 기판을 더 포함하며,

상기 제2 본딩 패드와 상기 제2 도전성 펑거는 상기 활성 영역에 대향하는 상기 기판 상에 존재하는 발광 소자.

**청구항 8**

제3항에 있어서,

상기 활성 영역에 대향하는, 상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층 상에 기판을 더 포함하며,

상기 제1 본딩 패드와 상기 제2 본딩 패드는 상기 기판에 대향하는 상기 발광 소자의 노출된 표면 상에 존재하는 발광 소자.

**청구항 9**

제8항에 있어서,

상기 기판은 경사진 측벽(beveled sidewall)들을 포함하는 발광 소자.

**청구항 10**

제7항에 있어서,

상기 p형 반도체 층 또는 상기 n형 반도체 층 중 나머지 하나의 층과 상기 기판 사이의 반사 층과, 상기 반사 층과 상기 기판 사이의 본딩 층을 더 포함하는 발광 소자.

**청구항 11**

제3항에 있어서,

상기 p형 반도체 층 또는 상기 n형 반도체 층 중 하나의 층과, 상기 제1 본딩 패드 및 상기 제1 도전성 펑거 사이에 투명 도전성 층을 더 포함하는 발광 소자.

**청구항 12**

발광 소자로서,

반대의 도전성 타입을 갖는, 대향하는 제1 반도체 표면 및 제2 반도체 표면을 구비한 반도체 다이오드;

상기 제1 반도체 표면 상의 불투명 특징부; 및

상기 불투명 특징부와 정렬되지 않은 상기 발광 소자 내의 감소된 도전성 영역

을 포함하는 발광 소자.

**청구항 13**

제12항에 있어서,

상기 감소된 도전성 영역은 제1 감소된 도전성 영역이고,

상기 발광 소자는 상기 불투명 특징부와 정렬된 상기 발광 소자 내의 제2 감소된 도전성 영역을 더 포함하는 발광 소자.

**청구항 14**

제12항에 있어서,

상기 감소된 도전성 영역은 상기 발광 소자의 발광 패턴을 형상화하도록 구성된 발광 소자.

## 명세서

### 기술분야

[0001] 본 발명은 반도체 발광 소자들 및 이를 제조하는 방법에 관한 것이다.

### 관련 출원

[0003] 본 출원은 2004년 6월 30일에 출원된 미국 특허 출원 제11/881,814호의 계속 출원이며, 이의 전체 내용이 개시되는 것과 같이 상기 출원의 명세서는 본 출원에 참조로서 포함된다.

### 배경기술

[0004] 발광 다이오드(LED) 또는 레이저 다이오드와 같은 반도체 발광 소자들은 많은 응용제품들에서 광범위하게 사용된다. 본 기술분야의 당업자들에게 잘 알려져 있다시피, 반도체 발광 소자는 통전(energization) 시에 간섭성 광(coherent light) 및/또는 비간섭성 광(incoherent light)을 방출하도록 구성된 하나 이상의 반도체 층들을 구비하는 반도체 발광 요소를 포함한다. 본 기술분야의 당업자들에게 잘 알려져 있다시피, 발광 다이오드 또는 레이저 다이오드는 일반적으로 마이크로전자 기판(microelectronic substrate) 상의 다이오드 영역을 포함한다. 마이크로전자 기판은, 예컨대, 갈륨 비소화물, 갈륨 인화물, 이들의 혼합물, 실리콘 탄화물 및/또는 사파이어일 수 있다. LED 분야의 지속적인 개발은 가시광 스펙트럼과 그 이상을 커버할 수 있는 효율이 높고 기계적으로 튼튼한 광원들을 달성하였다. 이러한 특징들은, 고상 소자들(solid state devices)의 잠재적으로 긴 사용 기간과 결합하여, 새로운 디스플레이 어플리케이션들을 가능하게 할 수 있으며, LED를 완전히 확립된 백열등 및 형광등과 경쟁할 수 있는 위치까지 옮겨놓을 수 있다.

[0005] 최근의 상당한 개발 과제와 상업적인 활동은 실리콘 탄화물 내에서 또는 상에서 제조되는 LED에 초점 맞춰지는 데, 그 이유는 이러한 LED가 가시광 스펙트럼 중 청색/녹색 부분의 광을 방출할 수 있기 때문이다. 예를 들면, 본 출원의 양수인에게 양도된 "Blue Light-Emitting Diode With High External Quantum Efficiency"이란 제목의 Edmond et al.의 미국 특허 제5,416,342호를 참조할 것이며, 이의 전체 내용을 본 출원이 완전히 개시하는 것과 같이, 상기 출원의 명세서는 본 출원에 참조로서 포함된다. 또한, 실리콘 탄화물 기판을 상의 갈륨 질화물-계 다이오드 영역들을 포함하는 LED들도 많은 관심을 받고 있으며, 그 이유는 이러한 소자들이 고 효율로 발광할 수 있기 때문이다.

[0006] 종래 LED들의 효율성은 이들의 활성 영역에 의해 생성되는 광 전체를 방출할 수 없는 것에 의해 제한될 수 있다. LED가 통전(energized)될 때, 이의 활성 영역으로부터 (모든 방향으로) 방출되는 광은, 예컨대 비-투-과 성 와이어 본딩 패드에 의해 LED로부터 나오는 것을 방해받을 수 있다. 통상적으로, 갈륨 질화물-계 LED에서, 전류 퍼짐 콘택 층(current spreading contact layer)은 발광 소자의 단면 전체에 대한 캐리어 주입 균일성을 향상시키기 위해 제공된다. 전류는 본딩 패드와 p형 콘택을 통해 LED의 p-측으로 주입된다. 소자의 활성 영역에서 생성되는 광은 캐리어 주입에 비례한다. 따라서, 활성 영역 전체에 대해 실질적으로 균일한 광자 방출은, 실질적으로 투명한 p형 콘택 층과 같은 전류 퍼짐 층(current spreading layer)을 사용하여 달성될 수 있다. 그러나, 와이어 본딩 패드는 통상적으로 투명한 구조물이 아니며, 따라서, LED의 활성 영역으로부터 방출되어 와이어 본딩 패드로 입사하는 광자들은 와이어 본딩 패드에 의해 흡수될 수 있다. 예를 들면, 일부 예들에서, 와이어 본딩 패드에 입사하는 광의 약 70%가 흡수될 수 있다. 이러한 광자 흡수는 LED로부터 방출되는 광량을 감소시킬 수 있으며, LED의 효율성을 감소시킬 수 있다.

### 발명의 내용

#### 해결하려는 과제

[0007] 본 발명의 일부 실시예들에 따르는 발광 소자는 p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 포함한다. 불투명 특징부는 상기 p형 반도체 층 상에, 또는 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 배치되며, 감소된 도전성 영역은 상기 p형 반도체 층 내에 배치되고 상기 불투명 특징부와 정렬된다. 상기 감소된 도전성 영역은 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장된다. 상기 불투명 영역은 와이어 본딩 패드, 패시베이션 영역, 및/또는 전류 퍼짐 팽거를 포함할 수 있다.

[0008] 상기 발광 소자는 서로 대향하는 제 1 및 제 2 표면들을 포함하는 기판을 더 포함할 수 있으며, 상기 n형 반도

체는 상기 기판의 상기 제 1 표면 상에 배치될 수 있으며, 상기 와이어 본딩 패드는 상기 n형 반도체 층의 반대 쪽에 상기 기판의 상기 제 2 표면 상에 배치될 수 있다.

[0009] 상기 발광 소자는 상기 p형 반도체 층의 상기 표면 상의 금속 스택을 더 포함할 수 있다. 상기 금속 스택은 상기 p형 반도체 층 바로 위의 오믹 층, 상기 오믹 층 상의 반사 층, 및 상기 반사 층 상의 본딩 층을 포함할 수 있다. 상기 발광 소자는 상기 반사 층과 상기 본딩 층 사이의 배리어 층을 더 포함할 수 있다.

[0010] 상기 감소된 도전성 영역은 상기 p형 반도체 층의 상기 표면으로부터 상기 활성 영역으로/안으로/관통하여 연장될 수 있다. 상기 감소된 도전성 영역은 상기 p형 반도체 층 및 상기 활성 영역을 관통하여 상기 n형 반도체 층 안으로 또는 관통하여 연장될 수 있다.

[0011] 상기 와이어 본딩 패드는 상기 감소된 도전성 영역과 콘택하도록 배치될 수 있으며, 상기 발광 소자는 상기 와이어 본딩 패드에 인접하고 상기 와이어 본딩 패드와 전기적으로 콘택하는 상기 n형 반도체 층 상의 오믹 콘택을 더 포함할 수 있다.

[0012] 상기 활성 영역은 III족-질화물-계 활성 영역을 포함할 수 있다. 상기 감소된 도전성 영역은 절연 영역 및/또는 불투명하지 않은 영역을 포함할 수 있다. 일부 실시예들에서, 상기 감소된 도전성 영역은 임플란트된 영역을 포함할 수 있다. 상기 감소된 도전성 영역은 상기 금속 스택과 상기 p형 반도체 층 사이의 경계에서 손상된 영역에 대응할 수 있다. 상기 손상된 영역은 상기 p형 반도체 층의 습식 또는 건식 식각된 영역, 상기 p형 반도체 층의 고 에너지 플라즈마에 노출된 영역, 상기 p형 반도체 층의 H<sub>2</sub>에 노출된 영역 및/또는 상기 p형 반도체 층의 고 에너지 레이저에 노출된 영역을 포함할 수 있다.

[0013] 본 발명의 추가 실시예들에 따르는 발광 소자는 p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 포함한다. 상기 소자는 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 배치되는 불투명 특징부, 및 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면 상의 금속 콘택을 포함한다. 상기 금속 콘택은 상기 불투명 특징부와 정렬되는 p형 반도체 층의 상기 표면의 감소된 도전성 부분 외의 다른 영역 내에서 상기 p형 반도체 층에 오믹 콘택을 형성한다. 상기 불투명 영역은 와이어 본딩 패드, 패시베이션 영역 및/또는 전류 퍼짐 링거를 포함할 수 있다.

[0014] 상기 발광 소자는 상기 p형 반도체 층 내에 배치되며 상기 불투명 특징부 및 상기 감소된 도전성 부분과 정렬되며 상기 p형 반도체 층의 상기 표면으로부터 상기 활성 영역을 향하여 연장될 수 있는 감소된 도전성 영역을 더 포함할 수 있다.

[0015] 상기 발광 소자는 상기 n형 반도체 층 내에 배치되며 상기 불투명 특징부와 정렬되며 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장되는 감소된 도전성 영역을 더 포함할 수 있다.

[0016] 상기 발광 소자는 상기 p형 반도체 층의 상기 표면 상의 비-오믹 콘택을 더 포함할 수 있다. 상기 비-오믹 콘택은 상기 p형 반도체 층과 오믹 콘택을 형성하지 않는 금속 및/또는 상기 p형 반도체 층의 상기 표면 상의 절연체를 포함할 수 있다.

[0017] 본 발명의 추가 실시예들에 따르는 발광 소자는 p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 포함한다. 상기 소자는 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 배치되는 와이어 본딩 패드, 및 상기 n형 반도체 층 내에 배치되고 상기 와이어 본딩 패드와 정렬되는 감소된 도전성 영역을 더 포함한다. 상기 감소된 도전성 영역은 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장된다. 상기 소자는 상기 와이어 본딩 패드에 인접하고 상기 와이어 본딩 패드와 전기적으로 콘택하는 상기 n형 반도체 층 상의 오믹 콘택을 더 포함한다.

[0018] 상기 발광 소자는 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면 상의 금속 스택을 더 포함할 수 있다. 상기 금속 스택은 상기 p형 반도체 층 바로 위의 오믹 층, 상기 오믹 층 상의 반사 층, 및 상기 반사 층 상의 본딩 층을 포함할 수 있다.

[0019] 상기 감소된 도전성 영역은 제 1 감소된 도전성 영역을 포함할 수 있으며, 상기 발광 소자는 상기 p형 반도체 층 내에 배치되고 상기 와이어 본딩 패드와 정렬되는 제 2 감소된 도전성 영역을 더 포함할 수 있다. 상기 제 2 감소된 도전성 영역은 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장될 수 있다.

- [0020] 상기 발광 소자는 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면 상의 금속 콘택을 더 포함할 수 있다. 상기 금속 콘택은 상기 와이어 본딩 패드와 정렬되는 상기 p형 반도체 층의 상기 표면의 감소된 도전성 부분 외의 다른 영역 내에서 상기 p형 반도체 층에 오믹 콘택을 형성한다.

- [0021] 본 발명의 일부 실시예들에 따르는 방법들은, p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 형성하는 단계, 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 불투명 특징부를 형성하는 단계, 및 상기 p형 반도체 층 내에 배치되고 상기 불투명 특징부와 정렬되는 감소된 도전성 영역을 형성하는 단계를 포함한다. 상기 감소된 도전성 영역은 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장된다.

- [0022] 본 발명의 추가 실시예들에 따르는 발광 소자를 형성하는 방법들은, p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 형성하는 단계, 상기 n형 반도체 층의 상기 p형 반도체 층 반대 쪽 상에 와이어 본딩 패드를 형성하는 단계, 및 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면 상에 금속 콘택을 형성하는 단계를 포함한다. 상기 금속 콘택은 상기 와이어 본딩 패드와 정렬되는 상기 p형 반도체 층의 상기 표면의 감소된 도전성 부분 외의 다른 영역 내에서 상기 p형 반도체 층에 오믹 콘택을 형성한다.

- [0023] 본 발명의 추가 실시예들에 따르는 발광 소자는 p형 반도체 층, n형 반도체 층, 및 상기 n형 반도체 층과 상기 p형 반도체 층 사이의 활성 영역을 포함한다. 본딩 패드는 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 상에 배치되며, 감소된 도전성 영역은 상기 p형 반도체 층 내에 배치되고 상기 본딩 패드와 정렬된다. 상기 감소된 도전성 영역은 상기 p형 반도체 층의 상기 n형 반도체 층 반대 쪽 표면으로부터 상기 활성 영역을 향하여 연장된다.

- [0024] 상기 발광 소자는 상기 본딩 패드와 상기 p형 반도체 층 사이에 배치되는 반사체, 및/또는 상기 p형 반도체 층 상의 전류 퍼짐 평거를 더 포함할 수 있으며, 상기 감소된 도전성 영역은 상기 전류 퍼짐 평거와도 추가로 정렬될 수 있다.

### 도면의 간단한 설명

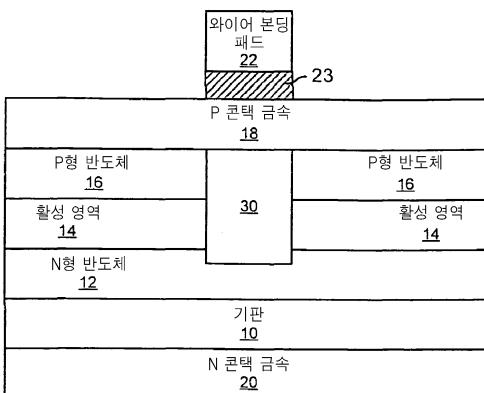

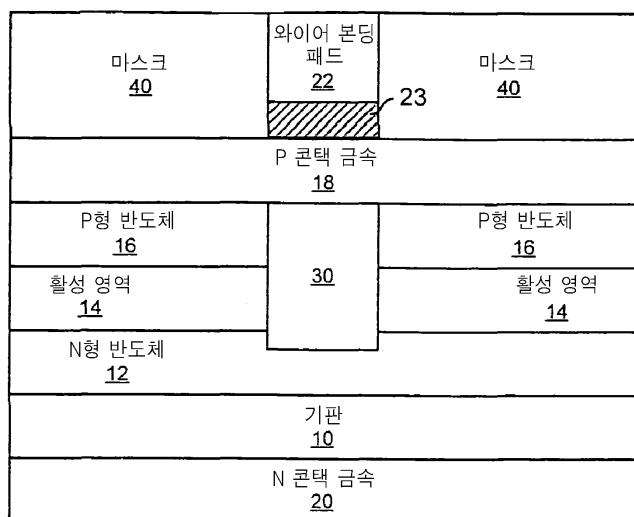

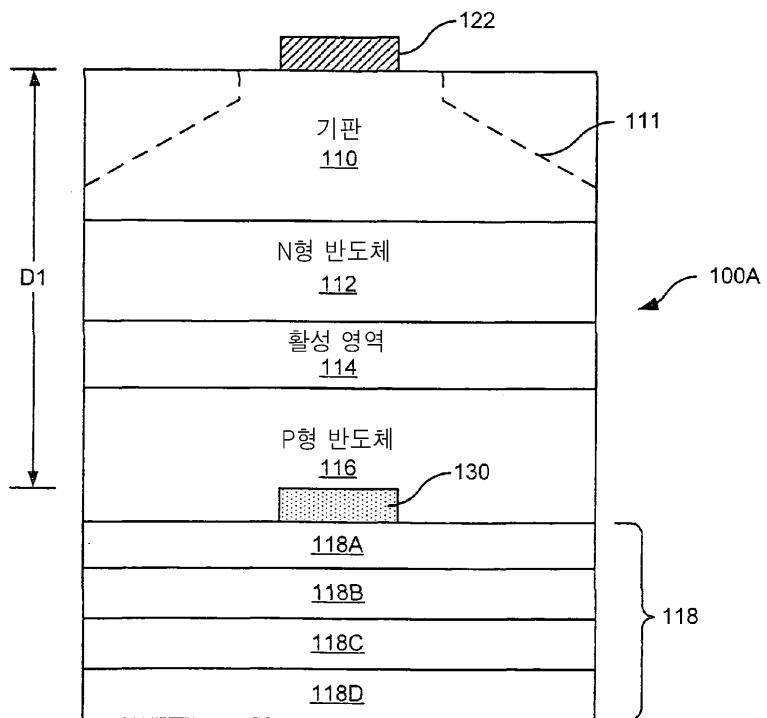

- [0025] 도 1은 본 발명의 일부 실시예들에 따라서 전류 차단 구조물을 갖는 반도체 발광 소자들을 도시하는 단면도이다.

- 도 2a 및 2b는 본 발명의 일부 실시예들에 따라서 반도체 소자들의 제조를 도시하는 단면도들이다.

- 도 3 내지 11은 본 발명의 추가 실시예들에 따르는 발광 소자들의 단면도들이다.

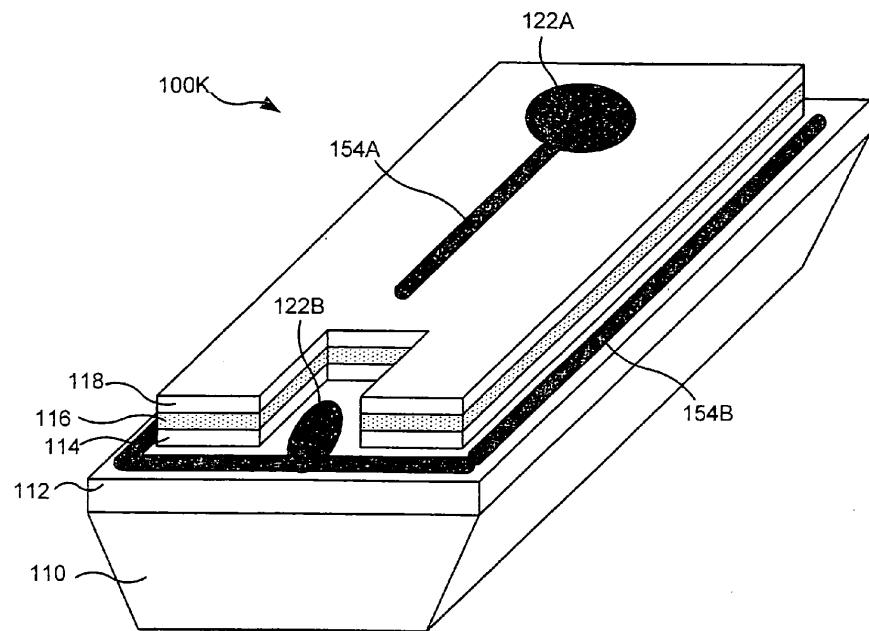

- 도 12 및 13은 본 발명의 일부 실시예들에 따르는 발광 소자들의 사시도들이다.

### 발명을 실시하기 위한 구체적인 내용

- [0026] 이제, 본 발명의 실시예들이 도시되는 첨부한 도면들을 참조로 아래에서 더욱 자세히 본 발명이 설명될 것이다. 그러나, 본 발명은 본 명세서에서 설명되는 실시예들로 한정되는 것으로 간주되어서는 안 된다. 차라리, 실시예들이 제공됨으로써, 본 명세서가 더욱 완전하고 완벽해질 것이며, 본 기술분야의 당업자들에게 본 발명의 범위를 완벽히 전달할 것이다. 도면에서, 층 및 영역의 두께는 명확함을 위해 과장된다. 동일한 참조 번호는 전체에 걸쳐 동일한 요소를 가리킨다. 본 명세서에서 사용되는 용어 "및/또는"은 관련되어 나열된 아이템들의 하나 이상의 임의의 그리고 모든 조합들을 포함한다.

- [0027] 본 명세서에서 사용되는 용어는 특정 실시예들을 설명하기 위한 목적으로만 사용되며, 본 발명을 한정하고자 함이 아니다. 본 명세서 사용되는 단수 형태 "하나의(a, an)" 및 "그(the)"는 문맥에서 명확히 지시하지 않는 한 복수의 형태도 포함하는 것으로 의도된다. "포함한다" 및/또는 "포함하는"이란 용어가 본 명세서에서 사용될 때 상기 용어는 언급된 특징들, 숫자들, 단계들, 동작들, 요소들 및/또는 구성요소들의 존재를 나타내며, 하나 이상의 다른 특징들, 숫자들, 단계들, 동작들, 요소들, 구성요소들, 및/또는 이들의 그룹들의 존재 또는 부가를 배제하지 않는 것으로 이해될 것이다.

- [0028] 층, 영역 또는 기판과 같은 요소가 다른 요소 "상에" 위치하거나 "위로" 연장하는 것으로 지칭될 때, 상기 요소가 다른 요소 위에 직접 위치하거나 다른 요소 위로 직접 연장할 뿐만 아니라, 중간 삽입 요소들이 존재할 수도 있다고 이해될 것이다. 반대로, 어느 한 요소가 다른 요소 "바로 위에" 위치하거나 다른 요소 "위로 직접" 연

장하는 것으로 지칭될 때에는, 중간 삽입 요소들은 존재하지 않는다. 어느 한 요소가 다른 요소에 "연결"되거나 "결합"되는 것으로 지칭될 때, 상기 한 요소는 다른 요소에 직접 연결되거나 결합될 수도 있으며, 이들 사이에 중간 삽입 요소들이 존재할 수도 있다. 반대로, 어느 한 요소가 다른 요소에 "직접 연결"되거나 "직접 결합"되는 것으로 지칭될 때에는, 이들 사이에 중간 삽입 요소들은 존재하지 않는다. 본 명세서 전체에 걸쳐, 동일한 참조 번호는 동일한 요소를 지칭한다.

[0029] 제 1, 제 2 등과 같은 용어가 다양한 요소들, 구성요소들, 영역들, 층들 및/또는 부분들을 설명하기 위해서 사용될 수 있으며, 이러한 요소들, 구성요소들, 영역들, 층들 및/또는 부분들은 이러한 용어들에 의해 한정되는 것이 아님을 이해하여야 한다. 이러한 용어들은 오로지 어느 한 요소, 구성요소, 층 또는 부분을 다른 영역, 층 또는 부분들과 구별하기 위해서만 사용된다. 따라서, 아래에서 설명되는 제 1 요소, 구성요소, 영역, 층 또는 부분은 본 발명의 교시로부터 벗어남 없이 제 2 요소, 구성요소, 영역, 층 또는 부분으로 불릴 수도 있다.

[0030] 또한, "하부" 또는 "바닥" 및 "상부" 또는 "천장"과 같은 상대적 용어들은 도면들에서 도시되는 어느 한 요소의 다른 요소들과의 관계를 설명하기 위해 본 명세서에서 사용될 수 있다. 상대적 용어들은 도면에 도시된 방향 외에 소자의 다른 방향들을 포함하는 것으로 의도됨을 이해할 것이다. 예를 들면, 도면에서의 소자가 뒤집히면, 다른 요소들의 "하부" 방향에 있는 것으로 설명된 요소들이 상기 다른 요소들의 "상부" 방향에 있는 것으로 될 것이다. 따라서, 예시적인 용어 "하부"는 도면의 특정 방향에 따라 "하부" 및 "상부"의 방향 모두를 포함할 수 있다. 유사하게, 도면들 중 하나의 소자가 뒤집히면, 다른 요소들 "아래에" 또는 "밑에" 위치하는 것으로 설명된 요소들이 다른 요소들의 "위에" 위치하는 것으로 될 것이다. 따라서, 예시적인 용어 "아래" 또는 "밑"은 위와 아래의 방향 모두를 포함할 수 있다.

[0031] 본 발명의 실시예들은 본 발명의 이상화된 실시예들의 개념적인 도면들인 단면 도면들을 참조로 본 명세서에서 설명된다. 예컨대, 제조 기술들 및/또는 공차들의 결과로서, 도면들의 형태로부터의 변형들이 예상될 것이다. 따라서, 본 발명의 실시예들은 본 명세서에서 도시된 영역들의 특정 형태로 한정되는 것으로 간주되어서는 안 되며, 예컨대 제조의 결과로 생성된 형태의 변형들을 포함하는 것으로 간주되어야 한다. 예를 들면, 직사각형으로 도시되거나 설명된 식각된 영역은 통상적으로 둑글거나 굽은 부분들을 가질 것이다. 따라서 도면들에서 도시된 영역들은 순전히 개념적이며, 이들의 형태들은 소자의 영역의 정확한 형태를 도시하고자 함이 아니며, 본 발명의 범위를 한정하고자 함이 아니다.

[0032] 다르게 정의되지 않는 한, 본 명세서에서 사용되는 (기술적 용어 및 과학적 용어를 포함하는) 모든 용어는 본 발명이 속하는 기술분야의 당업자들에 일반적으로 이해되는 것과 동일한 의미를 갖는다. 일반적으로 사용되는 사전에서 정의된 용어들과 같은 용어들은 본 명세서의 문맥에서 그리고 관련 기술에서의 의미와 일치하는 의미를 갖는 것으로 해석되어야 하며, 본 명세서에서 명시적으로 정의되지 않는 한 이상적으로 형식적인 의미로 해석되거나, 과도하게 형식적인 의미로 해석되어서는 안 될 것이다.

[0033] 다른 특징에 "인접하게" 배치된 어느 한 구조물 또는 특징에 대한 참조는 상기 인접한 특징과 중첩하거나 아래에 놓인 부분들을 가질 수 있는 것으로 본 기술분야의 당업자들에게 이해되어야 할 것이다.

[0034] 본 명세서에서 개시된 LED들의 다양한 실시예들이 기판을 포함하지만, 본 기술분야의 당업자들은, LED를 포함하는 에피택셜 층들이 성장되는 결정질 에피택셜 성장 기판이 제거될 수 있으며, 원 기판보다 더 좋은 열적, 전기적, 구조적 및/또는 광학적 특성들을 가질 수 있는 대체 캐리어 기판(substitute carrier substrate) 또는 서브마운트(submount) 상에 독립적인 에피택셜 층들이 배치될 수 있다는 것을 이해할 것이다. 본 명세서에서 설명되는 본 발명은 결정질 에피택셜 성장 기판들을 갖는 구조물들로 한정되지 않으며, 에피택셜 층들이 원 성장 기판들로부터 제거되고 대체 캐리어 기판들에 접합(bond)되는 구조물과 관련하여 사용될 수 있다.

[0035] 본 발명의 일부 실시예들은 와이어 본딩 패드 또는 다른 불투명 구조물 아래의 영역 내의 소자의 활성 영역 내에서의 전류 흐름을 감소 및/또는 방지함으로써 발광 소자의 개선된 효율을 제공할 수 있다. 따라서, 본 발명의 일부 실시예들은 와이어 본딩 패드 아래에 전류 차단 메커니즘을 갖는 발광 소자 및 이를 제조하는 방법을 제공할 수 있다. 전류가 와이어 본딩 패드 아래에 직접 주입되는 것을 감소 및/또는 방지함으로써, 전류는 와이어 본딩 패드의 아래가 아닌 소자의 영역들에서 광 방출로 변환될 가능성이 높아질 수 있다. 따라서, 광이 와이어 본딩 패드에 의해 흡수될 가능성이 감소될 수 있다. 본 발명의 일부 실시예들에서, 본 발명의 일부 실시예들에 따르는 발광 소자의 효율성 증가는 와이어 본딩 패드의 크기에 비례할 수 있다.

[0036] 본 발명의 실시예들은 III족-질화물-계 소자들과 같은 질화물-계 발광 소자들에서 사용되는 것이 특히 적합할 수 있다. 본원에서 사용되는 "III족 질화물(Group III nitride)"라는 용어는 알루미늄(Al), 갈륨(Ga), 및/또

는 인듐(In)과 같은 주기율 표의 III족의 원소들과 질화물 간에 형성되는 반도체성 화합물들을 지칭한다. 상기 용어는 AlGaN 및 AlInGaN과 같은 3원 화합물 및 4원 화합물도 지칭한다. 본 기술분야의 당업자들은 잘 알고 있겠지만, III족 원소들은 질소와 결합하여, (예컨대, GaN과 같은) 2원 화합물, (예컨대, AlGaN, AlInN과 같은) 3원 화합물, 및 (예컨대, AlInGaN과 같은) 4원 화합물을 형성할 수 있다. 이러한 화합물들 모두는 질소 1몰이 III족 원소들의 총 1몰과 결합되는 실험식을 갖는다. 따라서,  $Al_xGa_{1-x}N$ (여기서,  $0 \leq x \leq 1$ )과 같은 식이 이들을 설명하기 위해 종종 사용된다. 그러나, 본 발명의 실시예들이 갈륨 질화물-계 발광 소자들과 같은 III족-질화물-계 발광 소자들을 참조로 본 명세서에서 설명되지만, 본 발명의 특정 실시예들은 예컨대, GaAs 및/또는 GaP-계 소자들과 같은 다른 반도체 발광 소자들에서 사용되는 것이 적합할 수 있다.

[0037] 본 발명의 일부 실시예들에 따르는 발광 소자들은, 발광 다이오드, 레이저 다이오드 및/또는 다른 반도체 소자를 포함할 수 있으며, 상기 다른 반도체 소자는, 실리콘, 실리콘 탄화물, 갈륨 질화물 및/또는 다른 반도체 물질들을 포함할 수 있는 하나 이상의 반도체 층들, 사파이어, 실리콘, 실리콘 탄화물 및/또는 다른 마이크로전자기판들을 포함할 수 있는 기판, 및 금속 및/또는 다른 도전성 층들을 포함할 수 있는 하나 이상의 콘택 층들을 포함한다. 일부 실시예들에서, 자외선, 청색 및/또는 녹색 LED들이 제공될 수 있다. 반도체 발광 소자들의 디자인 및 제조는 본 기술분야의 당업자들에게 잘 알려져 있으므로 본 명세서에서 자세히 설명될 필요는 없다.

[0038] 예를 들면, 본 발명의 일부 실시예들에 따르는 발광 소자들은, Durham, North Carolina에 위치한 Cree, Inc.에 의해 제조 및 판매되는 소자들과 같은 실리콘 탄화물 기판 상에 제조되는 갈륨 질화물-계 LED 및/또는 레이저 구조물들과 같은 구조물들을 포함할 수 있다. 본 발명은 미국 특허 제6,201,262호, 제6,187,606호, 제6,120,600호, 제5,912,477호, 제5,739,554호, 제5,631,190호, 제5,604,135호, 제5,523,589호, 제5,416,342호, 제5,393,993호, 제5,338,944호, 제5,210,051호, 제5,027,168호, 제5,027,168호, 제4,966,862호 및/또는 제4,918,497호에 설명되는 것과 같은 활성 영역들을 제공하는 LED 및/또는 레이저 구조물들과 함께 사용되는 것이 적합할 수 있으며, 이들 특허의 명세서들은 본 명세서에 완전히 설명되다시피 본 출원에 참조로서 포함된다. 다른 적합한 LED 및/또는 레이저 구조물들은, 2003년 1월 9일에 공개되고 Group III Nitride Based Light Emitting Diode Structures With a Quantum Well and Superlattice, Group III Nitride Based Quantum Well Structures and Group III Nitride Based Superlattice Structures이란 제목의 미국 특허 공개 제US 2003/0006418 A1호, 및 Light Emitting Diodes Including Modifications for Light Extraction and Manufacturing Methods Therefor이란 제목의 미국 특허 공개 제 US 2002/0123164 A1호에서 설명된다. 또한, 2003년 9월 9일에 출원되고 Phosphor-Coated Light Emitting Diodes Including Tapered Sidewalls and Fabrication Methods Therefor이란 제목을 갖는 미국 출원 제10/659,241호에 개시된 것과 같은 인 코팅된 LED들(phosphor coated LEDs)도 본 발명의 실시예들에서 사용되기에 적합할 수 있으며, 상기 출원의 전체 개시는 본 출원에 참조로서 포함된다. LED들 및/또는 레이저들은 광 방출이 기판을 관통하여 발생하도록 동작하게 구성될 수 있다. 이러한 실시예들에서, 기판은, 예컨대 위에서 인용된 미국 특허 출원 제 US 2002/0123164 A1에서 설명되다시피, 소자들의 광 출력을 강화시키기 위해 패터닝될 수 있다. 이러한 구조물들은 본 발명의 일부 실시예들에 따르는 차단 구조물을 제공하기 위해서 본 명세서에서 설명되는 바와 같이 수정될 수 있다.

[0039] 따라서, 예컨대, 본 발명의 실시예들은 다른 형태와 크기를 갖는 본딩 패드들을 갖는 발광 소자들과 함께 사용될 수 있다. 발광 소자들은 실리콘 탄화물, 사파이어, 갈륨 질화물, 실리콘 또는 III족-질화물 소자들을 제공하기에 적합한 다른 기판과 같은 다른 기판 상에 형성될 수 있다. 발광 소자들은 후속 싱글레이션에 적합할 수 있으며, 적절한 캐리어 상에 마운팅되기에 적합할 수 있다. 발광 소자들은 예컨대, 단일 퀸텀 웨일(single quantum well), 다중-퀸텀 웨일(multi-quantum well) 및/또는 별크 활성 영역 소자들을 포함할 수 있다. 본 발명의 일부 실시예들은 소자의 p-측 상의 터널링 콘택을 이용하는 소자들과 함께 사용될 수 있다.

[0040] 도 1은 본 발명의 일부 실시예들에 따르는 발광 소자의 개념적인 단면도이다. 도 1에 도시된 바와 같이, 기판(10), 예컨대, n형 실리콘 탄화물 기판은 그 위에 제공되는 선택적인 n형 반도체 층(12), 예컨대 갈륨 질화물-계 층을 갖는다. n형 반도체 층(12)은 다중 층들, 예컨대 버퍼층들 등을 포함할 수 있다. 본 발명의 일부 실시예들에서, n형 반도체 층(12)은, 균일하거나 구배 있는 조성으로 이루어질 수 있는, AlGaN 층 및/또는 GaN 층으로서 제공된다. n형 반도체 층(12)은, 예컨대 실리콘, 게르마늄 및/또는 텔루륨으로 도핑될 수 있다.

[0041] 실리콘 탄화물 기판을 참조로 여기서 설명되지만, 본 발명의 일부 실시예들에서는 다른 기판 물질도 사용될 수 있다. 예를 들면, 사파이어 기판, GaN 또는 다른 기판 물질이 이용될 수 있다. 이 경우, 소자에 제 2 콘택을 제공하기 위해서, 예컨대 n형 반도체 층(12)과 콘택하는 리세스 내에 콘택(20)이 위치할 수 있다. 또한, 다른 구성들이 사용될 수도 있다.

- [0042] 활성 영역(14), 예컨대 단일 또는 이중 이종구조(heterostructure), 퀀텀 웰(quantum well), 멀티-퀀텀 웰 또는 이와 다른 활성 영역이 n형 반도체 층 상에 제공될 수 있다. 본원에서 사용되는 "활성 영역"이란 용어는 발광 소자의 반도체 물질로 이루어진 영역을 지칭하며, 이것은 하나 이상의 층들 및/또는 이들의 일부들일 수 있으며, 여기서 동작 중에 소자에 의해 방출되는 광자들의 상당한 일부분이 캐리어 재결합(carrier recombination)에 의해 생성된다. 본 발명의 일부 실시예들에서, 활성 영역은 소자에 의해 방출되는 실질적으로 모든 광자들이 캐리어 재결합에 의해 생성되는 영역을 지칭한다.

- [0043] 또한, 도 1에서 선택적인 p형 반도체 층(16)이 도시된다. p형 반도체 물질 층(16)은 예컨대 GaN 층과 같은 갈륨 질화물-계 층일 수 있다. 본 발명의 특정 실시예들에서, p형 반도체 층(16)은 마그네슘으로 도핑된 GaN을 포함한다. p형 반도체 층(16)은 단일 층 또는 다중 층들을 포함할 수 있으며, 균일하거나 구배 있는 조성으로 이루어질 수 있다. 본 발명의 일부 실시예들에서, p형 반도체 층(16)은 활성 영역(14)의 일부분이다.

- [0044] p형 반도체 물질 층(16)에 오믹 콘택을 제공하는 콘택 금속으로 이루어진 제 1 콘택 금속 층(18)도 또한 제공된다. 일부 실시예들에서, 제 1 콘택 금속 층(18)은 전류 퍼짐 층으로 기능할 수 있다. p형 반도체 물질 층(16)이 GaN인 본 발명의 특정 실시예들에서, 제 1 콘택 금속 층(18)은 Pt, 인듐-주석-산화물(ITO) 또는 p형 GaN에 오믹 콘택을 형성할 수 있는 다른 투명 물질을 포함할 수 있다. 본 발명의 특정 실시예들에서, 제 1 콘택 금속 층(18)은 광 투과성이며, 일부 실시예들에서는 실질적으로 투명하다. 일부 실시예들에서, 제 1 콘택 금속 층(18)은 Pt로 이루어진 상대적으로 얇은 층일 수 있다. 예를 들면, 제 1 콘택 금속 층(18)은 약 15Å 두께의 Pt 층일 수 있다. 선택적인 반사 층(23)이 제 1 금속 콘택 층(18) 상에 제공될 수 있다. 와이어 본딩 패드(22) 또는 다른 흡광 (또는 불투명) 특징부(feature)가 제 1 콘택 금속 층(18) 상에 제공된다. 도 1에 도시된 실시예들에서, 와이어 본딩 패드(22)가 반사 층(23) 상에 제공되어, 반사 층(23)은 와이어 본딩 패드(22)와 p형 반도체 물질 층(16) 사이에 위치한다. 일부 실시예들에서, 전류 퍼짐 핑거(finger)(154A(도 13))가 제 1 콘택 금속 층(18) 상에 위치할 수 있다.

- [0045] n형 반도체 물질에 오믹 콘택을 제공하는 콘택 금속으로 이루어진 제 2 콘택 금속 층도 제공된다. 제 2 콘택 금속 층(20)은 기판(10)의 활성 영역(14) 반대편 상에 제공될 수 있다. 위에서 논의된 바와 같이, 본 발명의 일부 실시예들에서, 제 2 콘택 금속 층은, 예컨대, 활성 영역을 포함하는 메사(mesa)의 베이스(base) 또는 리세스 내의 n형 반도체 물질 층(12)의 일부 상에 제공될 수 있다. 또한, 본 발명의 일부 실시예들에서, 선택적인 배면 임플란트 또는 추가적인 에피택셜 층들이 기판(10)과 제 2 콘택 금속 층(20) 사이에 제공될 수 있다.

- [0046] 도 1에 도시된 바와 같이, 감소된 도전성 영역(30)이 활성 영역(14) 내에 제공된다. 감소된 도전성 영역(30)은 소자의 흡광 및/또는 불투명 특징부들 및/또는 영역들 아래에 위치할 수 있다. 예를 들면, 도 1에 도시된 바와 같이, 감소된 도전성 영역(30)은 와이어 본딩 패드(22) 아래에 위치할 수 있다. 또한, 감소된 도전성 영역(30)은 칩의 다른 특징부들, 예컨대 칩의 에지를 따라 형성된 패시베이션 영역들, 칩의 표면 상에 위치하는 전류 퍼짐 핑거들, 또는 칩에 의해 방출되는 광을 흡수하는 경향이 있을 수 있는 칩의 다른 특징부들 또는 영역들 아래에 위치할 수도 있다.

- [0047] 본 발명의 일부 실시예들에서, 감소된 도전성 영역(30)은 활성 영역(14)을 관통하여 연장된다. 본원에서 사용되는 감소된 도전성(reduced conductivity)은 활성 영역의 다른 부분들에 비해 전류 흐름이 감소된 영역을 지칭한다. 특정 실시예들에서, 최소한 1/10배가 감소되며, 일부 실시예들에서는 감소된 도전성 영역에서 실질적으로 모든 전류 흐름이 차단된다.

- [0048] 상술된 바와 같이, 본 발명의 일부 실시예들에서, 감소된 도전성 영역(30)은 활성 영역(14)을 관통하여 연장된다. 본 발명의 추가 실시예들에서, 감소된 도전성 영역(30)은 제 1 콘택 금속 층(18)에서 활성 영역(14)까지 연장된다. 일부 실시예들에서, 감소된 도전성 영역은 제 1 콘택 층(18)에서 활성 영역(14) 안으로 연장된다. 일부 실시예들에서, 감소된 도전성 영역은 제 1 콘택 금속 층(18) 상의 와이어 본딩 패드(22) 영역과 실질적으로 동일한 형태 및/또는 면적을 가질 수 있다. 본 발명의 일부 실시예들에서, 감소된 도전성 영역(30)은 와이어 본딩 패드(22)보다 약간 더 큰 면적을 갖지만, 본 발명의 다른 실시예들에서는 감소된 도전성 영역(30)이 와이어 본딩 패드(22)보다 약간 작은 면적을 갖는다. 본 발명의 특정 실시예들에서, 감소된 도전성 영역(30)은 광을 흡수하지 않거나, 오로지 상대적으로 작은 양의 광만을 흡수한다. 본 발명의 일부 실시예들에서, 감소된 도전성 영역(30)은 절연 영역이다.

- [0049] 감소된 도전성 영역(30)은 와이어 본딩 패드(22) 아래의 영역 내의 활성 영역(14)을 관통하는 전류 흐름을 감소 및/또는 차단할 수 있으며, 그에 따라 캐리어들이 감소된 도전성 영역(30) 외의 다른 영역으로 주입되는 경향을

갖는다. 따라서, 감소된 도전성 영역(30)의 존재는 이러한 영역 내의 캐리어 재결합을 통한 광 생성을 감소 및/또는 방지할 수 있다. 동작의 구체적인 이론이 정립되지는 않았지만, 이것은 와이어 본딩 패드(22) 아래의 활성 영역 부분 내에서 생성되는 광자가 와이어 본딩 패드(22)에 의해 흡수될 가능성이 와이어 본딩 패드(22) 아래가 아닌 활성 영역의 다른 부분에서 광자가 생성될 가능성보다 높을 수 있기 때문일 수 있다. 와이어 본딩 패드(22) 아래의 활성 영역에서 생성되는 광을 감소 및/또는 제거시킴으로써, 와이어 본딩 패드(22)에 의해 흡수되는, 발광 소자에 의해 생성되는 광의 비율이 감소될 수 있다. 주어진 동작 조건들의 세트의 경우, 와이어 본딩 패드(22)에 의해 흡수되는 광량이 이와 같이 감소함에 따라, 와이어 본딩 패드(22) 아래의 영역에서 광이 생성되는 동일한 조건 하에서 동작하는 소자와 비교할 때, 발광 소자로부터 방출되는 광이 증가될 수 있다. 따라서, 본 발명의 일부 실시예들은 와이어 본딩 패드(22) 아래의 영역 내의 활성 영역(14) 안으로 연장되는 감소된 도전성 영역(30)을 제공하며, 일부 실시예들에서는, 와이어 본딩 패드(22) 아래의 영역 내의 활성 영역(14)을 관통하여 연장되는 감소된 도전성 영역(30)을 제공한다. 이것은 캐리어들이 와이어 본딩 패드(22) 아래의 활성 영역(14)으로 퍼져 상기 영역 안으로 주입되며, 그에 따라 와이어 본딩 패드(22) 아래의 영역 내에서 광이 생성될 가능성을 감소시킬 수 있다.

[0050]

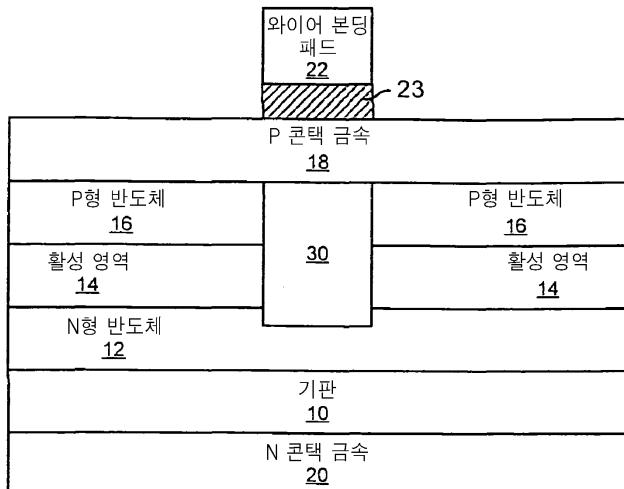

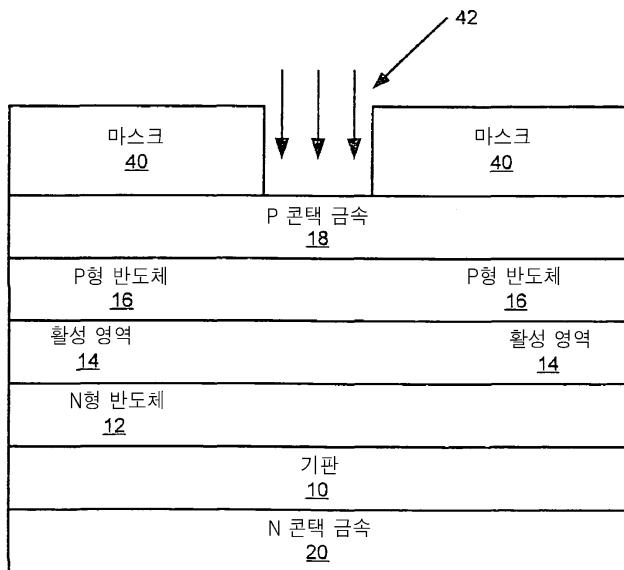

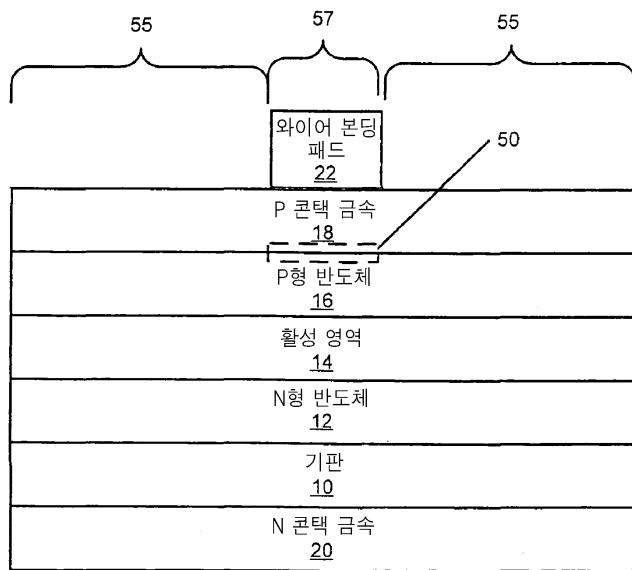

도 2a 및 2b는 도 1에 도시된 바와 같은 감소된 도전성 영역을 갖는 발광 소자들을 형성하기 위한 본 발명의 일부 실시예들에 따른 공정들을 도시한다. 도 2a에 도시된 바와 같이, 발광 소자의 여러 층들/영역들이 제조된다. 발광 소자의 제조를 위한 특정 공정들은 제조될 구조물들에 따라 달라질 것이며, 위에서 참조로서 포함되는 미국 특허 및/또는 출원에 설명되거나, 본 기술분야의 당업자들에게 잘 알려져 있으므로 여기서 반복할 필요는 없을 것이다. 도 2a는 와이어 본딩 패드(22)가 형성될 영역에 대응하는 윈도우(42)를 갖는 마스크(40)를 형성하는 것을 도시한다.

[0051]

와이어 본딩 패드(22)의 영역 내의 활성 영역(14) 안으로 원자들을 주입하기 위해, 마스크(40)를 이용하여 임플란트가 수행됨으로써 도 2b에 도시된 바와 같이 감소된 도전성 영역(30)이 형성된다. 이러한 임플란트는 예컨대 질화물 임플란트일 수 있다. 예를 들어, 갈륨 질화물-계 소자의 경우,  $60\text{KeV}$ ,  $2 \times 10^{13} \text{ cm}^{-3}$   $\text{N}_2$ 의 임플란트 조건들이 Mg로 도핑된 GaN 내에 비흡수(non-absorbing) 및 절연 영역을 생성하는데 사용될 수 있다. 구체적인 임플란트 에너지 및/또는 원자들은 감소된 도전 영역(30)이 형성되는 구조물에 따라 달라질 수 있다.

[0052]

도 2b에 도시된 바와 같이, 임플란트 후에, 와이어 본딩 패드(22)가 윈도우(42) 내에 형성될 수 있다. 일부 실시예들에서는, 와이어 본딩 패드(22)가 형성되기 전에, 반사 층(23)이 윈도우(42) 내에 형성될 수 있다. 따라서, 본 발명의 일부 실시예들에서, 와이어 본딩 패드(22) (및 가능하다면 반사 층(23)) 및 감소된 도전성 영역(30)은 자기 정렬될 수 있다. 와이어 본딩 패드(22)는, 예컨대, 금속 층 또는 금속 층들을 형성한 후, 와이어 본딩 패드(22)를 제공하기 위해 상기 층들을 평탄화함으로써, 형성될 수 있다. 그 후, 마스크(40)는 제거될 수 있다. 선택적으로, 마스크(40)는 절연 물질, 예컨대  $\text{SiO}_2$  및/또는  $\text{AlN}$ 으로 이루어질 수 있으며, 예컨대 패시베이션 층으로 소자 상에 잔존할 수도 있고, 또는 제거될 수도 있다.

[0053]

도 3은 본 발명의 추가 실시예들에 따른 발광 소자들을 도시한다. 도 3에서, 제 1 콘택 금속 층(18)은 p형 반도체 물질 층(16)에 오믹 콘택을 제공하는 p형 반도체 물질 층(16)과 콘택하는 제 1 영역(55), 및 p형 반도체 물질 층(16)에 오믹 콘택을 형성하지 않는 p형 반도체 물질 층(16)과 콘택하는 제 2 영역(57)을 포함한다. 본원에서 사용되는 "오믹 콘택(ohmic contact)"이란 용어는 약  $10 \text{ e-}03 \text{ ohm-cm}^2$  미만의 고유 콘택 저항률을 갖는 콘택을 지칭하며, 일부 실시예들에서는 약  $10 \text{ e-}04 \text{ ohm-cm}^2$  미만의 고유 콘택 저항률을 갖는 콘택을 지칭한다. 따라서, 정류(rectifying)하거나, 예컨대  $10 \text{ e-}03 \text{ ohm-cm}^2$ 를 초과하는 고유 콘택 저항률을 갖는 높은 고유 콘택 저항률을 갖는 콘택은 본 명세서에서 사용되는 용어로서 오믹 콘택이 아니다.

[0054]

제 2 영역(57)은 와이어 본딩 패드(22)의 위치에 대응한다. 오믹 콘택을 형성하지 않음으로써, 상기 영역(57) 내의 p형 반도체 물질 층(16) 안으로 주입되는 전류는 감소되거나 방지될 수 있다. 오믹 콘택을 형성하지 않는 상기 영역(57)은 와이어 본딩 패드(22) 아래에 위치한 영역(50) 내의 p형 반도체 층(16) 및/또는 제 1 콘택 금속 층(18)에 손상을 가함으로써 제공될 수 있다.

[0055]

예를 들면, 갈륨 질화물-계 소자들에서, 콘택 금속과 p형 반도체 물질 간의 경계 특성(quality of interface)은 생성된 오믹 콘택의 특성을 결정할 수 있다. 따라서, 예를 들어, 영역(50) 내의 p형 반도체 물질 층(16)은 제 1 콘택 금속 층(18)이 형성되기 전에 p형 도전성을 감소시키기 위해, 예컨대 Ar과 같은 고 에너지 플라즈마에 노출될 수 있다. 또한, 영역(50) 내의 p형 반도체 물질 층(16)과 제 1 콘택 금속 층(18)은 제 1 콘택 금속 층

(18)이 형성된 후에 금속/GaN 경계를 손상시키기 위해 고 에너지 플라즈마에 노출될 수 있다. 영역(50) 내의 p형 반도체 물질(16)은 제 1 콘택 금속 층(18)이 형성되기 전에 p형 반도체 물질 층(16)의 다른 영역들을 보호하면서 H<sub>2</sub>에 노출될 수 있다. 영역(50) 내의 p형 반도체 물질(16)은 제 1 콘택 금속 층(18)이 형성되기 전에 p형 반도체 물질 층(16)의 다른 영역들을 보호하면서 습식 또는 건식 식각될 수 있다. 또한, 영역(50) 내의 p형 반도체 물질(16)은 제 1 콘택 금속 층(18)이 형성되기 전에 p형 반도체 물질 층(16)의 다른 영역들을 보호하면서 고 에너지 레이저에 노출될 수 있다.

[0056] p형 반도체 물질 층(16) 및/또는 금속 층(18)의 위와 같은 선택적인 손상은, 예컨대, 도 2a 및 2b를 참조로 위에서 설명된 마스크를 사용하거나 레이저를 컨트롤함으로써 제공될 수 있다. 사용되는 구체적인 조건들은 사용되는 과정 및 p형 반도체 물질 층(16) 및/또는 제 1 금속 콘택 층(18)의 조성에 따라 달라질 수 있다.

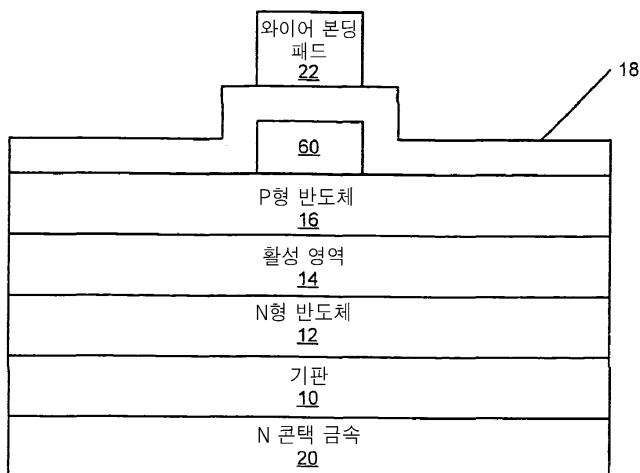

[0057] 도 4a는 본 발명의 추가 실시예들에 따른 발광 소자들을 도시한다. 도 4a에서, 쇼트키 콘택(60)은 p형 반도체 물질 층(16) 상에 제공되며, 제 1 콘택 금속 층(18')은 p형 반도체 물질 층(16)과 쇼트키 콘택(60) 상에 형성된다. 와이어 본딩 패드(22)는 쇼트키 콘택(60) 상의 제 1 금속 층(18')의 일부분 상에 제공된다. 쇼트키 콘택(60)을 형성함으로써, 제 1 콘택 금속 층(18')으로부터 p형 반도체 물질 층(16) 안으로 주입되는 전류는 쇼트키 콘택(60)의 영역 내에서 감소 및/또는 차단될 수 있다.

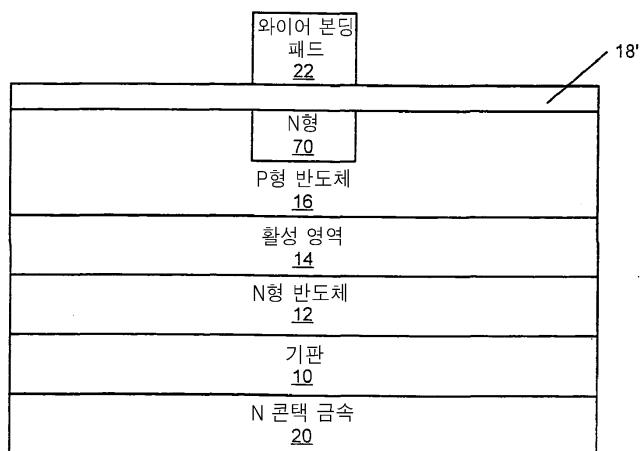

[0058] 대안적으로, 도 4b에 도시된 바와 같이, 정류 정션(rectifying junction)이 와이어 본딩 패드(22) 아래의 영역 내에 제공될 수 있다. 정류 정션은, 예컨대, p형 반도체 물질 층(16)을 n형 이온들로 임플란트하여 와이어 본딩 패드(22) 아래의 영역(70)을 n형 반도체 물질로 변환시킴으로써 제공될 수 있다. 이러한 임플란트는, 예컨대, 도 2a 및 2b를 참조로 위에서 설명된 마스크를 사용하여 수행될 수 있다. 대안적으로, n형 물질 영역은 쇼트키 콘택(60)이 도 4a에서 도시된 곳에 형성될 수 있으며, 제 1 콘택 금속(18')은 n형 반도체 물질 영역 및 p형 반도체 물질 층(16) 상에 형성될 수 있다.

[0059] 도 5를 참조하면, 본 발명의 일부 실시예들은 n형 반도체 층(112), 활성 영역(114) 및 p형 반도체 층(116)이 상부에 형성되는 기판(110)을 포함하는 발광 소자(100A)를 제공한다. 반도체 기판(110)은, 예컨대, 도전성 실리콘 탄화물 기판을 포함할 수 있으며, n형 반도체 층(112), 활성 영역(114) 및 p형 반도체 층(116)은 III족-질화물-계 반도체 층들을 포함할 수 있다. 발광 소자(100A)는 p형 반도체 층(116) 내에 형성된 감소된 도전성 영역(130)을 더 포함한다. 도 5에 도시된 바와 같이, 기판(110)은 형상을 갖는 측벽들(shaped sidewalls)(111)을 포함할 수 있으며, 상기 측벽들(111)은 활성 영역(114)에서 생성된 광이 소자(100A)의 측벽들과 부딪치는 각도를 변화시킴으로써, 소자(100A)로부터의 광 방출 효율을 증가시킬 수 있다. 도 5에 도시된 구조물에서, 감소된 도전성 영역(130)은 본딩 패드(122)로부터 약 50 내지 400 μm의 거리(D1)에 위치할 수 있다. 감소된 도전성 영역(130)은, p형 반도체 층(116) 안으로 이온들을 주입하는 것을 포함하여, 상술된 임의의 방법들을 사용하여 형성될 수 있다.

[0060] 발광 소자(100A)는 하부 지지부 상에 마운팅되는 소위 "플립 칩(flip chip)"에 적합할 수 있다. 구체적으로, 반도체 구조물은 p형 반도체층이 아래를 향하고 기판(110)이 위를 향하도록 서브마운트(submount), 본딩 패드 또는 다른 표면 상에 마운팅될 수 있다. 발광 소자(100A)를 지지부에 본딩하는 것을 용이하게 하기 위해서, p-콘택 금속 스택(118)이 p형 반도체 층(116)의 노출된 표면 상에 형성된다. 광전자(optoelectronic) 소자들의 플립 칩 마운팅에 적합한 금속 스택들은, 예컨대, "Light Emitting Diodes Including Modifications For Submount Bonding And Manufacturing Methods Therefor"이란 제목의 미국 특허 출원 제2003/0015721호에 설명되며, 이의 전체 내용은 본 명세서에 참조로서 포함된다. 구체적으로, p-콘택 금속 스택(118)은, p형 반도체 층(116)과 오믹 콘택을 형성하는, 예컨대 백금과 같은 금속으로 이루어진 오믹 층(118A)을 포함할 수 있다. 금속 스택(118)은 반사 층(118B), 배리어 층(118C) 및/또는 본딩 층(118D)을 더 포함할 수 있다.

[0061] 본딩 층(118D)은 금 및/또는 주석을 포함할 수 있으며 소자(110A)를 서브마운트에 용이하게 열음파(thermosonic) 및/또는 열압착(thermocompression) 본딩하기 위해 제공될 수 있다. 반사 층(118B)은 반사 물질, 예컨대 은 또는 알루미늄을 포함할 수 있으며 광이 서브마운트에서 반사되어 소자(100A) 쪽으로 향하도록 제공될 수 있으며, 그에 따라 광은 유용하게 방출될 수 있다. 배리어 층(118C)은 금속, 예컨대 텅스텐, 티타늄, 티타늄 질화물 및/또는 니켈을 포함할 수 있으며, 이것은 본딩 층(118B)의 금속이 오믹 금속(118A) 및/또는 반사체(118B)를 오염시키는 것을 방지할 수 있다. 배리어 층들은, "Light Emitting Diodes Including Barrier Layers/Sublayers And Manufacturing Methods Therefor"이란 제목의 미국 특허 출원 제2005/0194603호에 설명된 바와 같이 형성될 수 있으며, 이의 전체 내용은 본 명세서에 참조로서 포함된다. 선택적인 접착층(미 도시)이 배리어 층(118C)과 본딩 층(118D) 사이에 제공될 수 있다.

- [0062] 예컨대 도 5에 도시된 소자(100A)와 같은 광전자 소자가 소자(100A)의 p측이 아래를 향하도록(즉, 지지부를 향하도록) 불투명지지 부재 상에 마운팅될 때, 기판(110)의 도전성이 충분히 높을 수 있어서 전류가 소자 내에서 자연히 퍼질 수 있기 때문에, 노출된 기판(110) 상에 투명 전극 또는 전류 퍼짐 층을 형성하는 것이 필수적이지 않을 수 있다. 따라서, 도 5에 도시된 바와 같이, 상기 소자는 기판(110) 상에 형성된 와이어 본딩 패드(122)를 포함할 수 있다. 오믹 콘택(미 도시)이 와이어 본딩 패드(122)와 기판(110) 사이에 형성될 수 있다. 일부 실시예들에서 오믹 콘택은 본딩 패드(122)와 자기 정렬되어 형성될 수 있다.

- [0063] 감소된 도전성 영역(130)은 p형 반도체 층(116)의 활성 영역(114) 반대쪽 표면으로부터 p형 반도체 층(116) 안으로 연장될 수 있다. 감소된 도전성 영역(130)은 p형 반도체 층(116)을 부분적으로 및/또는 완전히 관통하도록 연장될 수 있다. 기판(110)을 포함하는 실시예들을 포함하는 일부 실시예들에서, 감소된 도전성 영역(130)은 활성 영역(114)을 완전히 관통하여 n형 반도체 층(112)으로/안으로 연장될 수 있다. 감소된 도전성 영역(130)은 도 1 내지 4를 참조로 위에서 설명된 기술들과 같은 기술들을 사용하여 형성될 수 있다. 예를 들면, 감소된 도전성 영역(130)은 도 2a를 참조로 위에서 설명된 바와 같이, 마스크를 이용하여 p형 반도체 층(116) 안으로 이온들을 임플란트 함으로써 형성될 수 있다.

- [0064] 도 5에 추가로 도시되는 바와 같이, 감소된 도전성 영역(130)은 본딩 패드(122)와 일반적으로 정렬될 수 있다. p형 반도체 층(116)은 예컨대 기판(110)과 비교할 때 상대적으로 얇을 수 있기 때문에, 그리고 전류가 p형 반도체 층(116) 내에서 쉽게 퍼지지 않을 수 있기 때문에, 감소된 도전성 영역(130)의 존재는 와이어 본딩 패드(122)의 바로 아래의 소자(100A) 내에서 생성되는 광자들을 수를 감소시킬 수 있다. 따라서, 감소된 도전성 영역(130)은 와이어 본딩 패드의 형상과 대략 똑같은 형상을 가질 수 있다. 또한, 감소된 도전성 영역(130)은 와이어 본딩 패드(122)의 면적과 거의 동일하거나, 약간 작거나, 약간 큰 면적을 가질 수 있다. 일부 실시예들에서, 감소된 도전성 영역은 본딩 패드(122)의 직경보다 약 6 내지 약 30  $\mu\text{m}$  정도 큰 직경을 가질 수 있다. 구체적으로, 본딩 패드(122)는 약 100 내지 105  $\mu\text{m}$ 의 직경을 가질 수 있으며, 감소된 도전성 영역(130)은 본딩 패드(122)의 직경보다 약 14  $\mu\text{m}$  정도 더 큰 직경을 가질 수 있다. 기판을 포함하는(즉, 기판(110)이 제거되지 않은) 실시예들에서, 본딩 패드(122)의 면적보다 더 큰 면적에 감소된 도전성 영역(130)을 제공하는 것이 바람직할 수 있다. 예를 들면, 만약 와이어 본딩 패드(122)가 원형이라면, 감소된 도전성 영역(130)도 와이어 본딩 패드(122)의 직경과 거의 같거나, 약간 작거나, 약간 큰 면적을 갖는 원형일 수 있다.

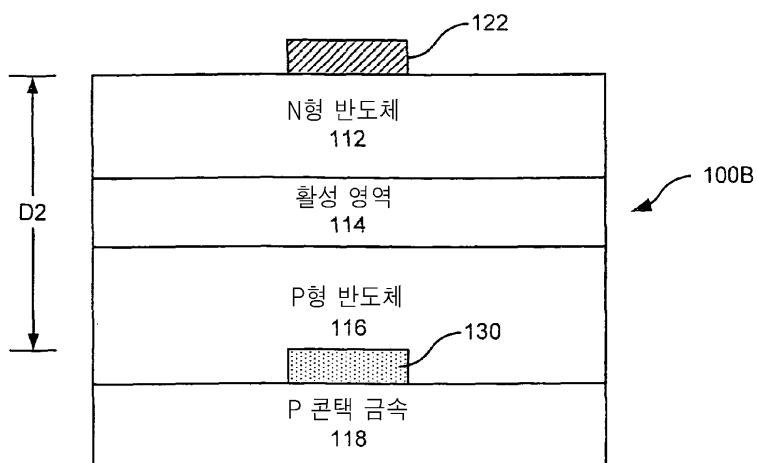

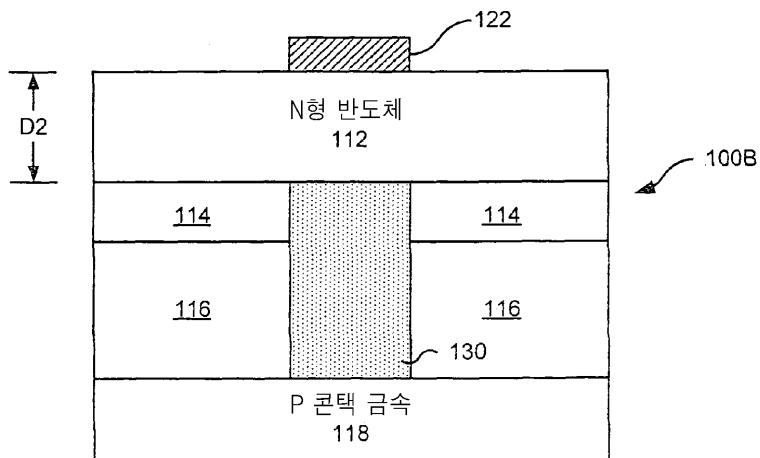

- [0065] 본 발명의 추가 실시예들이 도 6a 및 6b에 도시되며, 여기서 p형 반도체 층(116), 활성 영역(114) 및 n형 반도체 층(112)을 포함하는 발광 소자(100B)가 도시된다. p-콘택 금속 스택(118)이 p형 반도체 층(116)의 표면 상에 형성되며, 와이어 본딩 패드(122)가 n형 반도체 층(112)의 p형 반도체 층(116) 반대 쪽 표면 상에 형성된다. 구체적으로, 도 6a 및 6b에 도시된 발광 소자(100B)는 기판을 포함하지 않을 수 있다.

- [0066] 도 6a에 추가로 도시되는 바와 같이, 감소된 도전성 영역(130)은 와이어 본딩 패드(122)와 일반적으로 정렬되어 p형 반도체 층(116) 내에 제공된다. 감소된 도전성 영역(130)은 p형 반도체 층(116)의 활성 영역(114) 반대 쪽 표면으로부터 p형 반도체 층(116) 안으로 연장될 수 있다. 감소된 도전성 영역(130)은 p형 반도체 층(116)을 부분적으로 및/또는 완전히 관통하도록 연장될 수 있다. 감소된 도전성 영역(130)은 와이어 본딩 패드(122)의 면적과 같거나, 크거나, 작은 면적을 가질 수 있다. 감소된 도전성 영역(130)은 소자(100B) 내부에 와이어 본딩 패드(122)로부터 거리(D2)에 위치될 수 있다. 일부 실시예들에서, 거리(D2)는 0.3 내지 10  $\mu\text{m}$ 일 수 있다. 구체적으로, 거리(D2)는 약 2 내지 3  $\mu\text{m}$ 일 수 있다.

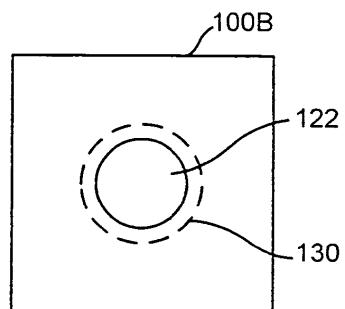

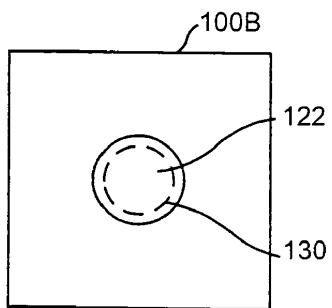

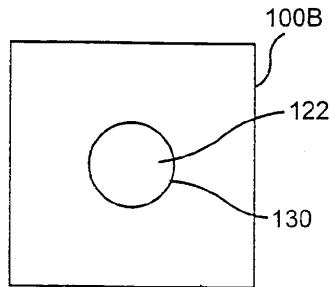

- [0067] 도 11a 내지 11c는 와이어 본딩 패드(122) 및 정렬된 감소된 도전성 영역(130)을 포함하는 발광 소자(100B)의 평면도들이다. 도 11a 내지 11c에 도시되는 바와 같이, 감소된 도전성 영역(130)은 와이어 본딩 패드(122)의 주변 형상(peripheral shape)과 유사한 주변 형상을 가질 수 있으며, 와이어 본딩 패드(122)는 도 11a 내지 11c에 도시된 실시예들에서 일반적으로 원형이다. 와이어 본딩 패드(122)와 감소된 도전성 영역(130)은, 예컨대, 직사각형, 별형, 십자가형 또는 다른 형상 또는 상기 형상들의 조합과 같은 다른 주변 형상들을 가질 수 있다.

- [0068] 도 11a에 도시된 바와 같이, 일부 실시예들에서는, 감소된 도전성 영역(130)이 와이어 본딩 패드(122)의 면적보다 약간 큰 면적을 가질 수 있으며, 다른 실시예들에서는, 감소된 도전성 영역(130)이 와이어 본딩 패드(122)의 면적보다 약간 작거나(도 11b), 거의 동일한(도 11c) 면적을 가질 수 있다.

- [0069] 도 6b를 참조하면, 감소된 도전성 영역(130)은 p형 반도체 층(116)을 완전히 관통하여 활성 영역(114) 안으로 연장될 수 있다. 기판을 포함하지 않는 실시예들을 포함하는 일부 실시예들에서, 감소된 도전성 영역(130)은 활성 영역(114)을 완전히 관통하여 n형 반도체 층(112)으로/안으로 연장될 수 있다.

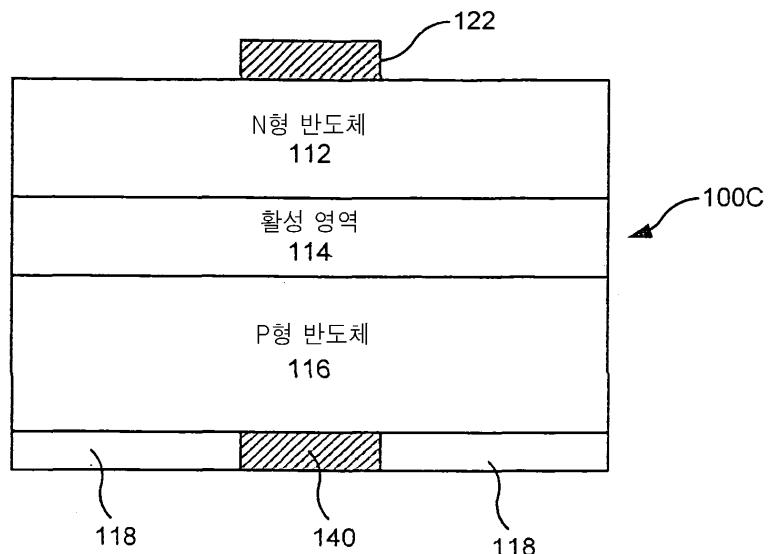

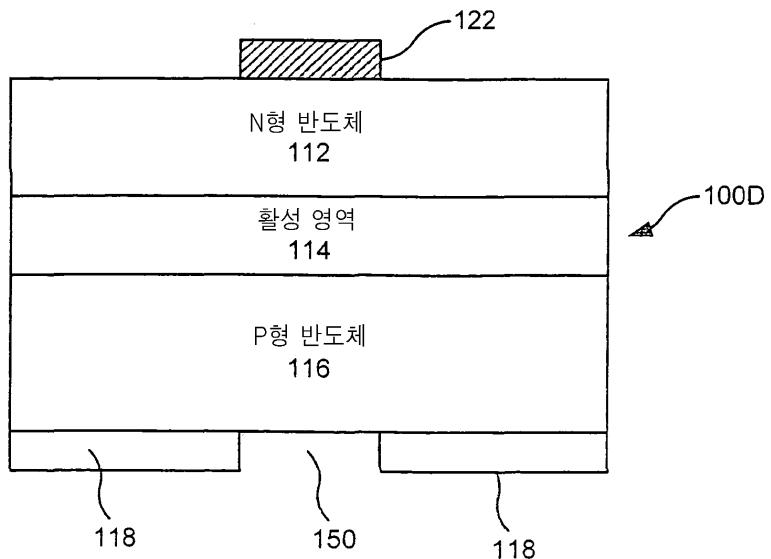

- [0070] 본 발명의 추가 실시예들이 도 7a에 도시되며, 도 7a는 p형 반도체 층(116), 활성 영역(114) 및 n형 반도체 층(112)을 포함하는 발광 소자(100C)를 도시한다. 와이어 본딩 패드(122)는 n형 반도체 층(112)의 표면 상에 형성된다. 패터닝된 오믹 콘택(118)은 p형 반도체 층(116)의 n형 반도체 층(112) 반대 쪽 표면 상에 형성된다. 또한, 발광 소자(100C)는 p형 반도체 층(116)의 와이어 본딩 패드(122) 반대 쪽 상에 비-오믹(non-ohmic) 콘택(140)을 포함한다. 일부 실시예들에서, 비-오믹 콘택(140)은, 예컨대, 정류 쇼트키 콘택(rectifying Schottky contact)을 포함할 수 있다. 질화물-계 반도체 물질들 상에 정류 쇼트키 콘택들을 형성하는 것은 본 기술분야의 당업자들에게 잘 알려져 있다. 다른 실시예들에서, 비-오믹 콘택(140)은 실리콘 이산화물과 같은 비-도전성 물질을 포함할 수 있다.

- [0071] 비-오믹 콘택(140)은 와이어 본딩 패드(122)의 형상과 대략 동일한 형상을 가질 수 있다. 콘택(140)은 와이어 본딩 패드(122)의 면적과 거의 같거나, 약간 작거나, 약간 큰 면적을 가질 수 있다. 따라서, 소자(100C)의 단자들 양단에 전압이 인가될 때, 전류가 비-오믹 콘택(140)에서 p형 반도체 층(116) 안으로 흐르지 않을 수 있으며, 이것은 와이어 본딩 패드(122) 아래의 활성 층(114)에서 생성되는 광자들의 수를 감소시킬 수 있다.

- [0072] 도 7b를 참조하면, 일부 실시예들에서, 금속 스택(118)이 와이어 본딩 패드(122) 반대 쪽의 감소된 도전성의 영역(150) 외의 다른 영역들 내에 p형 반도체 층(116)의 표면 상에 형성될 수 있다. 즉, 금속 스택(118)이 상기 영역(150) 내에 형성되지 않기 때문에, 소자가 활성화될 때, 영역(150)을 관통하여 흐르는 전류는 감소될 수 있으며, 이것은 와이어 본딩 패드(122) 아래의 활성 층(114) 내에서 생성되는 광자들의 수를 감소시킬 수 있다.

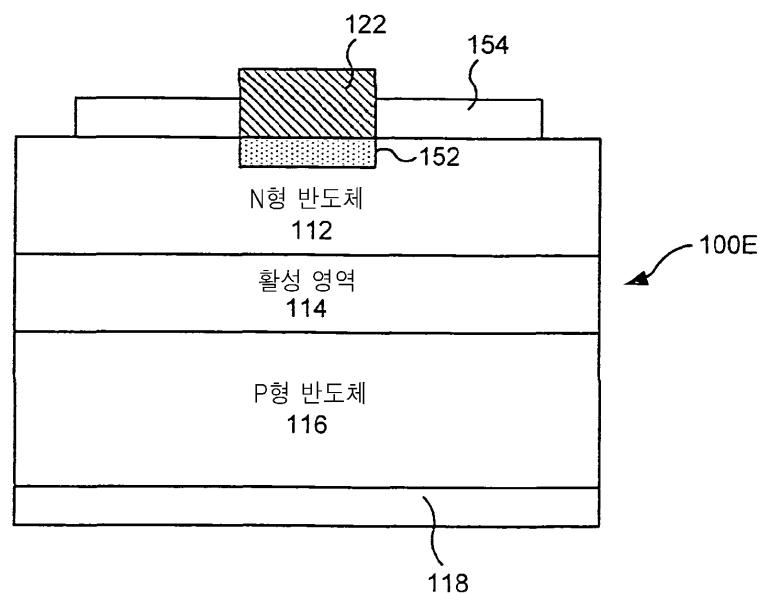

- [0073] 본 발명의 추가 실시예들이 도 8에 도시된다. 도 8의 실시예들에서, 소자(100E)는 p형 반도체 층(116), 활성 영역(114) 및 n형 반도체 층(112)을 포함한다. p형 콘택(117)은 p형 반도체 층(116)의 n형 반도체 층(112) 반대 쪽 표면 상에 형성된다. 와이어 본딩 패드(122)는 n형 반도체 층(112)의 p형 반도체 층(116) 반대 쪽 표면 상에 형성된다. 오믹 콘택(154)은 n형 반도체 층(112)의 와이어 본딩 패드(122)와 동일한 표면 상에 형성되며 와이어 본딩 패드(122)에 전기적으로 연결된다. 오믹 콘택(154)은 n형 반도체 층(112)에 오믹 콘택을 형성하는 투명 물질, 예컨대 ITO를 포함할 수 있다.

- [0074] 감소된 도전성 영역(152)은 와이어 본딩 패드(122) 아래의 n형 반도체 층(112) 내에 형성된다. 감소된 도전성 영역(152)은 n형 반도체 층(112)의 표면으로부터 n형 반도체 층(112)의 적어도 부분적으로 안으로 연장될 수 있다. 일부 실시예들에서, 감소된 도전성 영역(152)은 n형 반도체 층(112)을 완전히 관통하여 활성 영역(114)으로/안으로 연장될 수 있다.

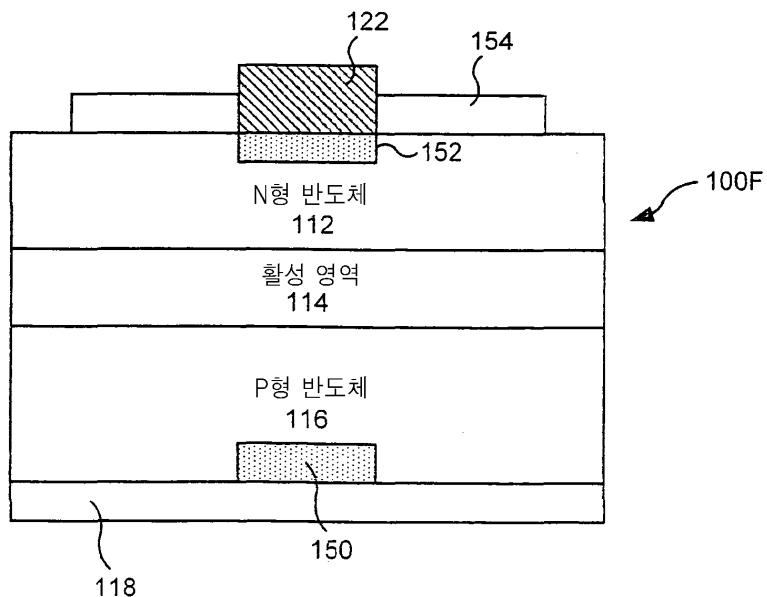

- [0075] 도 9a는 본 발명의 추가 실시예들에 따른 소자(100F)를 도시한다. 소자(100F)도 p형 반도체 층(116), 활성 영역(114) 및 n형 반도체 층(112)을 포함한다. p형 콘택(118)은 p형 반도체 층(116)의 n형 반도체 층(112) 반대 쪽 표면 상에 형성된다. 와이어 본딩 패드(122)는 n형 반도체 층(112)의 p형 반도체 층(116) 반대 쪽 표면 상에 형성된다. 오믹 콘택(154)은 n형 반도체 층(112)의 와이어 본딩 패드(122)와 같은 표면 상에 형성된다.

- [0076] 제 1 감소된 도전성 영역(152)은 와이어 본딩 패드(122) 아래의 n형 반도체 층(112) 내에 형성된다. 제 1 감소된 도전성 영역(152)은 와이어 본딩 패드(122)와 정렬될 수 있으며, n형 반도체 층(112)의 표면으로부터 n형 반도체 층(112)의 적어도 부분적으로 안으로 연장될 수 있다. 일부 실시예들에서, 제 1 감소된 도전성 영역(152)은 n형 반도체 층(112)을 완전히 관통하여 활성 영역(114)으로/안으로/관통하여 연장될 수 있다.

- [0077] 제 2 감소된 도전성 영역(150)은 p형 반도체 층(116) 내에 형성된다. 제 2 감소된 도전성 영역(150)은 제 1 감소된 도전성 영역(152) 및/또는 와이어 본딩 패드(122)와 정렬될 수 있다. 제 2 감소된 도전성 영역(150)은 p형 반도체 층(116)의 표면으로부터 p형 반도체 층(116)의 적어도 부분적으로 안으로 연장될 수 있으며, 일부의 경우에는, 활성 영역(114)까지/안으로/관통하여 연장될 수 있다.

- [0078] 예컨대, 소자(100F)의 제 1 감소된 도전성 영역(152)과 제 2 감소된 도전성 영역(150)과 같은, 소자의 양쪽에 형성된 감소된 도전성 영역(150, 152)을 포함하는 실시예들에서, 감소된 도전성 영역들(150, 152)은 동일한 기술들을 이용하여 형성될 필요는 없지만, 예컨대 다른 기술들을 이용하여 형성될 수도 있다. 예를 들면, 제 1 감소된 도전성 영역(152)은 이온 임플란트를 통해 형성될 수 있으며, 제 2 감소된 도전성 영역(150)은 플라즈마 처리를 이용하거나 수소 가스에 노출시킴으로써 형성될 수 있으며, 이와 반대도 가능하다. 또한, 감소된 도전성 영역들(150, 152) 중 하나 또는 모두는, 상부에 전기적 콘택을 형성하기 전에, 각각의 반도체 층(116, 112)의 표면 상에 비-오믹 물질을 형성함으로써 형성될 수 있으며, 또는 본딩 패드(122)에 대응하는 반도체 층의 표면 영역 상에 오믹 콘택을 형성하지 않음으로써 형성될 수 있다.

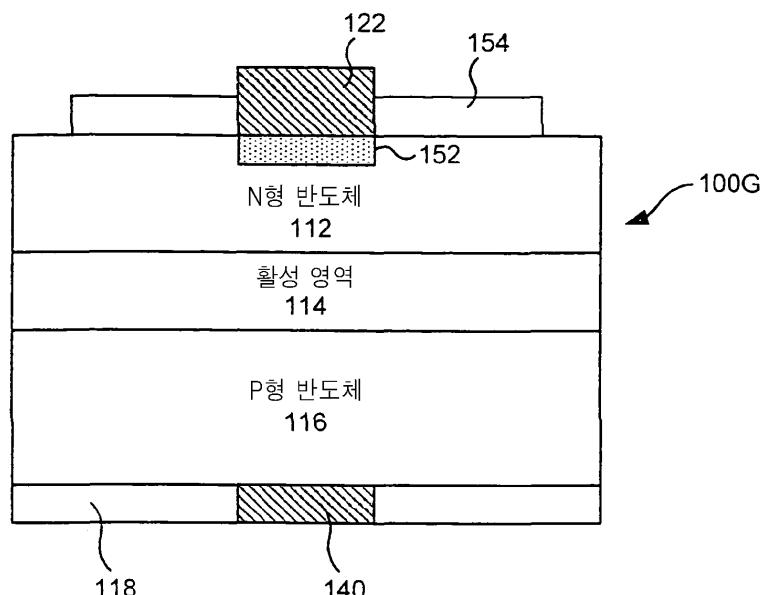

- [0079] 도 9b는 본 발명의 추가 실시예들에 따른 소자(100G)를 도시한다. 소자(100G)도 p형 반도체 층(116), 활성 영

역(114) 및 n형 반도체 층(112)을 포함한다. p형 콘택(118)은 p형 반도체 층(116)의 n형 반도체 층(112) 반대 쪽 표면 상에 형성된다. 와이어 본딩 패드(122)는 n형 반도체 층(112)의 p형 반도체 층(116) 반대 쪽 표면 상에 형성된다. 오믹 콘택(154)은 n형 반도체 층(112)의 와이어 본딩 패드(122)와 동일한 표면 상에 형성된다.

[0080] 감소된 도전성 영역(152)은 와이어 본딩 패드(122) 아래의 n형 반도체 층(112) 내에 형성된다. 감소된 도전성 영역(152)은 와이어 본딩 패드(122)와 정렬될 수 있으며, n형 반도체 층(112)의 표면으로부터 n형 반도체 층(112)의 적어도 부분적으로 안으로 연장될 수 있다. 일부 실시예들에서, 감소된 도전성 영역(152)은 n형 반도체 층(112)을 완전히 관통하여 활성 영역(114)으로/안으로/관통하여 연장될 수 있다.

[0081] 금속 콘택(118)은 p형 반도체 층(116)의 n형 반도체 층(112) 반대 쪽 표면 상에 형성된다. 금속 콘택(118)은 와이어 본딩 패드(122)와 정렬되는 p형 반도체 층(116)의 표면의 감소된 도전성 영역 외의 다른 영역 내의 p형 반도체 층(116)에 오믹 콘택을 형성한다.

[0082] 또한, 발광 소자(100G)는 p형 반도체 층(116)의 와이어 본딩 패드(122) 반대 쪽 상에 형성된 비-오믹 콘택(140)을 포함한다. 일부 실시예들에서, 비-오믹 콘택(140)은, 예컨대, 정류 쇼트키 콘택을 포함할 수 있다. 다른 실시예들에서, 비-오믹 콘택(140)은 비-도전성 물질, 예컨대 실리콘 이산화물을 포함할 수 있다.

[0083] 비-오믹 콘택(140)은 와이어 본딩 패드(122)의 형상과 대략 동일한 형상을 가질 수 있다. 콘택(140)은 와이어 본딩 패드(122)의 면적과 거의 같거나, 약간 작거나, 약간 큰 면적을 가질 수 있다. 다른 실시예들에서, 비-오믹 콘택(140)은 상부에 콘택이 형성되지 않는 갭(gap)을 포함할 수 있다.

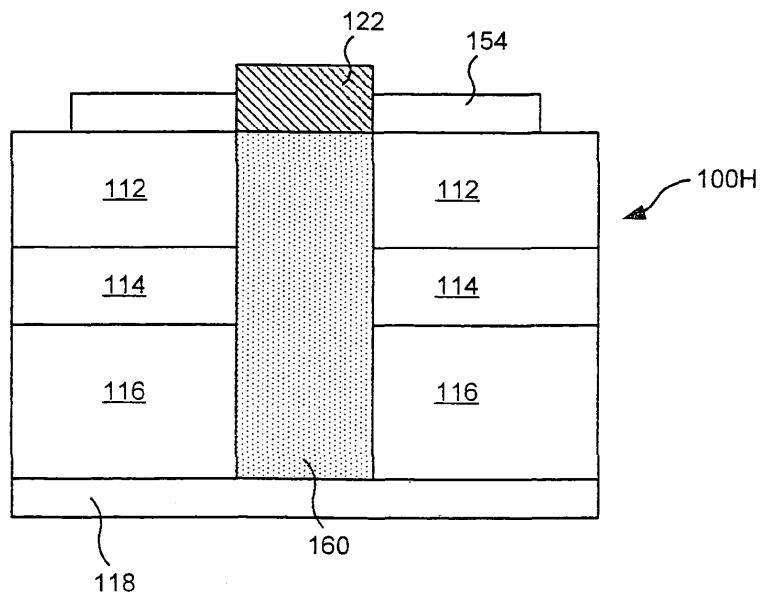

[0084] 본 발명의 추가 실시예들이 도 10에 도시되며, 도 10은 와이어 본딩 패드(122) 아래에서 n형 반도체 층(112)의 표면으로부터 소자(100G)를 관통하여 p형 반도체 층(116)의 대향 표면까지 연장되는 감소된 도전성 영역(160)을 포함하는 반도체 발광 소자(100H)를 도시한다.

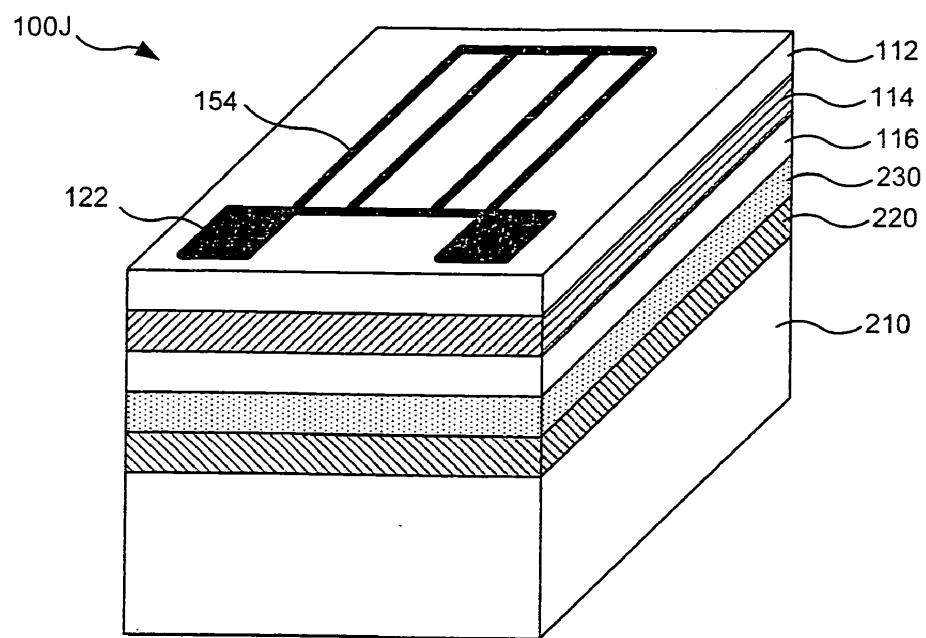

[0085] 본 발명의 실시예들이 사용될 수 있는 일부 칩 구조물들이 도 12 및 13에서 사시도로 도시된다. 예를 들면, 도 12는 캐리어 기판(210), 예컨대 실리콘 기판을 포함하는 칩 구조물(100J)을 도시하며, 캐리어 기판(210) 상에 LED 구조물이 금속 본딩 층(220)을 통해 본딩되어 있다. 반사 층(230)이 본딩 층(220)과 LED 구조물 사이에 배치되며, LED 구조물은 p형 반도체 층(116), 활성 층(114) 및 n형 반도체 층(112)을 포함한다.

[0086] 한 쌍의 본딩 패드(122)는 n형 반도체 층(112)의 기판(210) 반대 쪽 표면 상에 배치된다. 본딩 패드들(122)은 n형 반도체 층(112) 상에 다수의 전류 퍼짐 평거들(154)을 포함하는 전류 퍼짐 구조물에 전기적으로 연결된다.

[0087] 감소된 도전성 영역(30)은 본딩 패드들(122) 아래에, 전류 퍼짐 평거들(154) 아래에, 및/또는 본딩 패드들(122)과 전류 퍼짐 평거들(154) 모두의 아래에 형성될 수 있다.

[0088] 예시적인 수평 칩 구조물(100K)이 도 13에 도시된다. 칩 구조물(100K)은 n형 반도체 층(112)이 상부에 형성되는 투명 기판(110)을 포함한다. 활성 영역(114)과 p형 반도체 층(116)을 포함하는 메사 구조물은 n형 반도체 층 상에 배치된다. ITO를 포함할 수 있는 투명 오믹 콘택(118)은 p형 반도체 층(116) 상에 배치된다. 본딩 패드(112A)는 투명 오믹 콘택(118) 상에 배치되며, 전류 퍼짐 평거(154A)는 본딩 패드(112A)로부터 연장된다. 본딩 패드(122B)는 n형 반도체 층(112) 상에 배치되며, 전류 퍼짐 평거(154B)는 본딩 패드(122B)로부터 연장된다. 반사 층(23)이 본딩 패드(122A) 및/또는 전류 퍼짐 평거(154A) 아래에 제공될 수 있다.

[0089] 감소된 도전성 영역(30)이 본딩 패드(122A) 아래에, 전류 퍼짐 평거들(154A) 아래에, 및/또는 본딩 패드(122A)와 전류 퍼짐 평거(154A) 모두의 아래에 형성될 수 있다.

[0090] 본 발명의 실시예들은 특정 발광 소자 구조물들을 참조로 도 1 내지 13에 도시되지만, 다른 구조물들도 본 발명의 일부 실시예들에 따라서 제공될 수 있다. 따라서, 본 발명의 실시예들은 위에서 설명된 바와 같은 하나 이상의 다양한 전류 차단 메커니즘들을 포함하는 임의의 발광 구조물에 의해 제공될 수 있다. 예를 들면, 본 발명의 일부 실시예들에 따르는 전류 차단 메커니즘들은 위에서 참조로서 포함되는 미국 특허 및/또는 출원에서 논의되는 예시적인 발광 소자 구조물들과 결합하여 제공될 수 있다.

[0091] 본 발명의 실시예들은 와이어 본딩 패드(22, 122)를 참조로 설명되었다. 본 명세서에서 사용되는 본딩 패드(bond pad)라는 용어는 흡광 콘택 구조물(light absorbing contact structure)을 포함한다. 본딩 패드는 단일 층 또는 다중 층들일 수 있으며, 금속 및/또는 금속 합금일 수 있으며, 균일한 조성으로 이루어질 수도 있고 불균일한 조성으로 이루어질 수도 있다.

[0092] 또한, 본 발명의 실시예들은 특정 공정 시퀀스를 참조로 설명되었지만, 본 발명의 교시들로부터 여전히 이득을

얻으면서, 설명된 시퀀스의 변형들이 제공될 수 있다. 따라서, 둘 이상의 단계들이 하나의 단계 또는 본 명세서에서 설명되는 시퀀스를 벗어나 수행되는 단계들로 결합될 수 있다. 예를 들면, 감소된 도전성 영역은, 반도체 층 상에 금속 층을 형성하기 전에 또는 형성한 후에, 반도체 층 내에 형성될 수 있다. 따라서, 본 발명의 실시예들은, 본 명세서에서 다르게 서술하지 않는 한, 본 명세서에서 설명된 특정 공정 시퀀스로 한정되는 것으로 간주되어서는 안 된다.

[0093] 본 발명의 다양한 실시예들이 도 1 내지 13과 관련하여 개별적으로 설명되었다는 것을 본 기술분야의 당업자들은 이해할 것이다. 그러나, 도 1 내지 13의 실시예들의 조합들 및 하위조합들(subcombination)이 본 발명의 다양한 실시예들에 따라서 제공될 수 있다. 상술된 바와 같이, 감소된 도전성 영역들(30)은 생성된 광이 소자의 일부 특징부들, 예컨대, 본딩 패드, 전류 퍼짐 평거, 패시베이션 영역 등에 의해 흡수될 가능성이 있는 소자의 영역들에서 캐리어 재결합을 감소/방지하는데 사용될 수 있다. 따라서, 일부 실시예들에서, 감소된 도전성 영역들(30)은 소자의 흡광 특징부들 및/또는 영역들과 정렬될 수 있다. 그러나, 일부의 경우에는, 소자의 흡광 영역들 또는 특징부들과 정렬되지 않는 다른 영역들에 감소된 도전성 영역들(30)을 형성하는 것이 바람직할 수 있다. 예를 들면, 소자가 목적하는 원거리장 방출 패턴(desired far-field emission pattern)을 갖는 광을 생성하게 하는 소자 내에 감소된 도전성 영역들(30)을 제공하는 것이 바람직할 수 있다. 따라서, 일부 실시예들에서, 감소된 도전성 영역들(30)은 발광 소자의 발광 패턴을 형상화(shaping)하는데 사용될 수 있다.

[0094] 도면들 및 명세서에서, 본 발명의 실시예들이 개시되었으며, 특정 용어들이 사용되었지만, 이것들은 한정을 위한 것이 아니라 일반적이고 설명을 위한 것으로서만 사용된 것이며, 본 발명의 범위는 다음의 청구범위에 의해 결정된다.

## 도면

### 도면1

## 도면2a

## 도면2b

도면3

도면4a

도면4b

도면5

도면6a

도면6b

도면7a

도면7b

도면8

도면9a

도면9b

도면10

도면11a

도면11b

도면11c

도면12

도면13