(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6031765号

(P6031765)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年11月4日(2016.11.4)

(51) Int.Cl.

F 1

H01L 21/768

(2006.01)

H01L 21/90

B

H01L 23/522

(2006.01)

H01L 27/14

D

H01L 27/14

(2006.01)

H04N 5/335

690

H04N 5/369

(2011.01)

請求項の数 4 (全 40 頁)

(21) 出願番号

特願2012-6356 (P2012-6356)

(22) 出願日

平成24年1月16日(2012.1.16)

(65) 公開番号

特開2013-33900 (P2013-33900A)

(43) 公開日

平成25年2月14日(2013.2.14)

審査請求日

平成27年1月9日(2015.1.9)

(31) 優先権主張番号

特願2011-148883 (P2011-148883)

(32) 優先日

平成23年7月5日(2011.7.5)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 110000925

特許業務法人信友国際特許事務所

(72) 発明者 香川 恵永

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 河合 俊英

最終頁に続く

(54) 【発明の名称】半導体装置、電子機器、及び、半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

接合界面側の表面に形成された第1金属膜を有する第1半導体部と、前記接合界面で前記第1金属膜と接合されかつ前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜を有し、前記接合界面で前記第1半導体部と貼り合わせて設けられた第2半導体部と、

前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア部と、を備え、

前記界面バリア部は、前記接合界面で前記第1半導体部と接合されるべく前記第2金属膜と面一に形成される、絶縁体の界面バリア膜により構成され、

前記第2半導体部は、前記第2金属膜の側部を覆うように設けられた絶縁膜を有し、前記界面バリア膜が、前記絶縁膜の前記接合界面側の表面に形成される、半導体装置。

## 【請求項2】

前記界面バリア膜が、SiN、SiON、SiCN、及び、有機系樹脂材料のいずれかで形成される、

請求項1に記載の半導体装置。

## 【請求項3】

半導体装置と、前記半導体装置の出力信号を処理する信号処理回路とを備える電子機器であって、

前記半導体装置は、

接合界面側の表面に形成された第1金属膜を有する第1半導体部と、

前記接合界面で前記第1金属膜と接合されかつ前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜を有し、前記接合界面で前記第1半導体部と貼り合わせて設けられた第2半導体部と、

前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア部とを有し、

前記界面バリア部は、前記接合界面で前記第1半導体部と接合されるべく前記第2金属膜と面一に形成される、絶縁体の界面バリア膜により構成され、

前記第2半導体部は、前記第2金属膜の側部を覆うように設けられた絶縁膜を有し、前記界面バリア膜が、前記絶縁膜の前記接合界面側の表面に形成される、

電子機器。

【請求項4】

接合界面側の表面に形成された第1金属膜を有する第1半導体部を作製するステップと、

前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜と、前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に、前記接合界面で前記第1半導体部と接合されるべく前記第2金属膜と面一に形成される、絶縁体の界面バリア膜により構成される界面バリア部とを有し、

前記第2金属膜の側部を覆うように設けられた絶縁膜を有し、前記界面バリア膜が、前記絶縁膜の前記接合界面側の表面に形成される、

第2半導体部を作製するステップと、

前記第1半導体部の前記第1金属膜側の表面と前記第2半導体部の前記第2金属膜側の表面とを貼り合わせて、前記第1金属膜と前記第2金属膜とを接合するステップと、を含む半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体装置、電子機器、及び、半導体装置の製造方法に関し、より詳細には、製造時に2枚の基板を貼り合わせて配線接合を行う半導体装置、それを備える電子機器、及び、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、2枚の半導体基板（ウエハ）を貼り合わせて、それぞれの半導体基板に形成された銅配線同士を接合（以下、Cu-Cu接合という）する技術が開発されている（例えば、特許文献1参照）。

【0003】

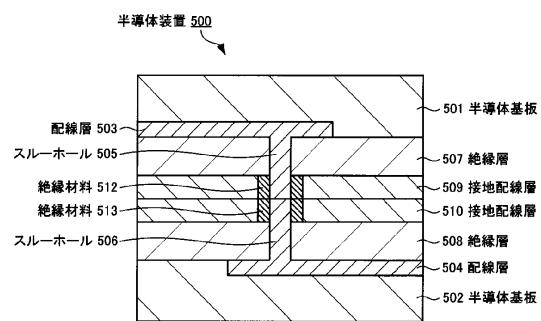

図58に、特許文献1で提案されている半導体装置のCu-Cu接合界面付近の概略構成断面図を示す。特許文献1の半導体装置500は、半導体基板501、配線層503、スルーホール505（縦孔配線部）、絶縁層507、接地配線層509、及び、絶縁材料512を含む第1の半導体部材を備える。また、半導体装置500は、半導体基板502、配線層504、スルーホール506、絶縁層508、接地配線層510、及び、絶縁材料513を含む第2の半導体部材を備える。

【0004】

第1の半導体部材では、配線層503は、半導体基板501の一方の表面（接合側の表面）に埋め込むように形成される。絶縁層507及び接地配線層509は、この順で、半導体基板501の一方の表面上に積層される。また、スルーホール505は、絶縁層507及び接地配線層509からなる積層膜に形成される。この際、スルーホール505は、積層膜の厚さ方向に沿って、積層膜を貫通するように形成される。なお、スルーホール505の一方の端部は、配線層503に接続され、他方の端部は、第1の半導体部材の接合

10

20

30

40

50

側の面（接地配線層 509 側の表面）に露出するように設けられる。さらに、絶縁材料 512 は、スルーホール 505 と接地配線層 509 との間に設けられる。

#### 【0005】

一方、第 2 の半導体部材では、配線層 504 は、半導体基板 502 の一方の表面（接合側の表面）に埋め込むように形成される。絶縁層 508 及び接地配線層 510 は、この順で、半導体基板 502 の一方の表面上に積層される。また、スルーホール 506 は、絶縁層 508 及び接地配線層 510 からなる積層膜に形成される。この際、スルーホール 506 は、積層膜の厚さ方向に沿って、積層膜を貫通するように形成される。なお、スルーホール 506 の一方の端部は、配線層 504 に接続され、他方の端部は、第 2 の半導体部材の接合側の面（接地配線層 510 側の表面）に露出するように設けられる。さらに、絶縁材料 513 は、スルーホール 506 と接地配線層 510 との間に設けられる。

10

#### 【0006】

そして、特許文献 1 では、上記構成の第 1 の半導体部材の接地配線層 509 側の表面と、上記構成の第 2 の半導体部材の接地配線層 510 側の表面とを接合することにより、半導体装置 500 が作製される。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

#### 【特許文献 1】特開 2000-299379 号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

上述のように、従来、半導体装置の技術分野において、2枚の半導体基板を貼り合わせて、Cu-Cu 接合を行う技術が提案されている。しかしながら、この技術分野では、Cu-Cu 接合界面（以下、単に接合界面という）における例えば電気特性や密着性などの劣化をより一層抑制して、より信頼性の高い接合界面を有する半導体装置の開発が望まれている。

#### 【0009】

本開示は、上記要望に応えるためになされたものであり、本開示の目的は、より信頼性の高い接合界面を有する半導体装置、電子機器、及び、半導体装置の製造方法を提供することである。

30

#### 【課題を解決するための手段】

#### 【0010】

上記課題を解決するために、本開示の半導体装置は、接合界面側の表面に形成された第 1 金属膜を有する第 1 半導体部と、接合界面で第 1 金属膜と接合されかつこの接合界面側の表面面積が第 1 金属膜の接合界面側の表面面積より小さい第 2 金属膜を有し、接合界面で第 1 半導体部と貼り合わせて設けられた第 2 半導体部と、第 1 金属膜の接合界面側の面領域のうち第 2 金属膜と接合しない面領域を含む領域に設けられた界面バリア部と、を備える。

そして、界面バリア部は、接合界面で第 1 半導体部と接合されるべく第 2 金属膜と面一に形成される、絶縁体の界面バリア膜により構成され、第 2 半導体部は、第 2 金属膜の側部を覆うように設けられた絶縁膜を有し、界面バリア膜が、絶縁膜の接合界面側の表面に形成される。

40

#### 【0011】

また、本開示の電子機器は、上記本開示の半導体装置と、半導体装置の出力信号を処理する信号処理回路とを備える構成とする。

#### 【0012】

さらに、本開示の半導体装置の製造方法は、以下に示す手順で行う。

まず、接合界面側の表面に形成された第 1 金属膜を有する第 1 半導体部を作製する。次に、接合界面側の表面面積が第 1 金属膜の接合界面側の表面面積より小さい第 2 金属膜と

50

、第1金属膜の接合界面側の面領域のうち第2金属膜と接合しない面領域を含む領域に、接合界面で第1半導体部と接合されるべく第2金属膜と面一に形成される、絶縁体の界面バリア膜により構成される界面バリア部とを有し、第2金属膜の側部を覆うように設けられた絶縁膜を有し、界面バリア膜が、絶縁膜の接合界面側の表面に形成される、第2半導体部を作製する。次いで、第1半導体部の第1金属膜側の表面と第2半導体部の第2金属膜側の表面とを貼り合わせて、第1金属膜と第2金属膜とを接合するステップ。

#### 【発明の効果】

##### 【0013】

上述のように、本開示の半導体装置（電子機器）、及び、その製造方法では、第1金属膜と接合する第2金属膜の接合側の表面面積を、第1金属膜の接合側の表面面積より小さくする。そして、第1金属膜の接合界面側の面領域のうち第2金属膜と接合しない面領域を含む領域に界面バリア部を設ける。この本開示の構成によれば、接合界面における電気特性の劣化をより一層抑制して、より信頼性の高い接合界面を有する半導体装置（電子機器）、及び、その製造方法を提供することができる。

10

#### 【図面の簡単な説明】

##### 【0014】

【図1】Cu-Cu接合時に発生する問題を説明するための図である。

【図2】Cu-Cu接合時に発生する問題を説明するための図である。

【図3】本開示の第1の実施形態に係る半導体装置における接合界面付近の概略断面図である。

20

【図4】第1の実施形態に係る半導体装置の接合界面付近の概略上面図である。

【図5】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図6】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図7】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図8】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図9】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図10】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図11】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図12】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図13】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

30

【図14】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図15】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図16】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図17】第1の実施形態に係る半導体装置の作製手順を説明するための図である。

【図18】本開示の第2の実施形態に係る半導体装置における接合界面付近の概略断面図である。

【図19】第2の実施形態に係る半導体装置の接合界面付近の概略上面図である。

【図20】第2の実施形態に係る半導体装置の作製手順を説明するための図である。

【図21】第2の実施形態に係る半導体装置の作製手順を説明するための図である。

【図22】第2の実施形態に係る半導体装置の作製手順を説明するための図である。

40

【図23】第2の実施形態に係る半導体装置の作製手順を説明するための図である。

【図24】第2の実施形態に係る半導体装置の作製手順を説明するための図である。

【図25】本開示の第3の実施形態に係る半導体装置における接合界面付近の概略断面図である。

【図26】第3の実施形態に係る半導体装置の接合界面付近の概略上面図である。

【図27】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

【図28】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

【図29】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

【図30】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

【図31】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

50

- 【図32】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

- 【図33】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

- 【図34】第3の実施形態に係る半導体装置の作製手順を説明するための図である。

- 【図35】変形例1の半導体装置における接合界面付近の概略断面図である。

- 【図36】変形例1の半導体装置の作製手順を説明するための図である。

- 【図37】変形例3の半導体装置における接合界面付近の概略断面図である。

- 【図38】変形例4の半導体装置における接合界面付近の概略断面図である。

- 【図39】参考例1の半導体装置における接合界面付近の概略断面図である。

- 【図40】参考例2の半導体装置における接合界面付近の概略断面図である。

- 【図41】従来のCu-Cu接合手法において発生し得る問題を説明するための図である 10

- 。

- 【図42】従来のCu-Cu接合手法において発生し得る問題を説明するための図である

- 。

- 【図43】本開示の第4の実施形態に係る半導体装置における接合界面付近の概略断面図である。

- 【図44】第4の実施形態に係る半導体装置の接合界面付近の概略上面図である。

- 【図45】第4の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図46】第4の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図47】第4の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図48】第4の実施形態に係る半導体装置の作製手法を説明するための図である 20

- 【図49】本開示の第5の実施形態に係る半導体装置における接合界面付近の概略断面図である。

- 【図50】第5の実施形態に係る半導体装置の接合界面付近の概略上面図である。

- 【図51】第5の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図52】第5の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図53】第5の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図54】第5の実施形態に係る半導体装置の作製手法を説明するための図である。

- 【図55】本開示のCu-Cu接合技術を適用することのできる応用例1の半導体装置の構成例を示す図である。

- 【図56】本開示のCu-Cu接合技術を適用することのできる応用例2の半導体装置の構成例を示す図である 30

- 【図57】本開示のCu-Cu接合手技術を適用することのできる応用例3の電子機器の構成例を示す図である。

- 【図58】従来の半導体装置における接合界面付近の概略断面図である。

- 【発明を実施するための形態】

- 【0015】

- 以下に、本開示の実施形態に係る半導体装置、及び、その製造手法の例を、図面を参照しながら下記の順で説明する。ただし、本開示は下記の例に限定されない。

1. 第1の実施形態

2. 第2の実施形態

3. 第3の実施形態

4. 各種変形例及び参考例

5. 第4の実施形態

6. 第5の実施形態

7. 各種応用例 40

- 【0016】

- <1. 第1の実施形態>

- [従来のCu-Cu接合技術の問題点]

- まず、本開示の第1の実施形態に係る半導体装置について説明する前に、従来のCu-Cu接合技術で発生し得る問題点を、図1(a)及び(b)、並びに、図2を参照しながら 50

ら説明する。なお、図1(a)は、2つの半導体部材を接合する前の各半導体部材の概略構成断面図であり、図1(b)は、接合後の接合界面付近の概略断面図である。また、図2は、2つの半導体部材の貼り合わせ時に接合アライメントずれが発生した場合に発生し得る問題を説明するための図である。

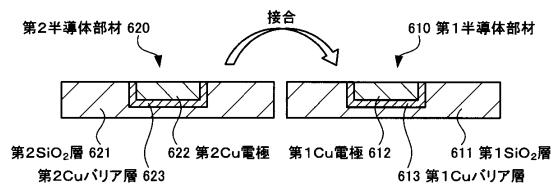

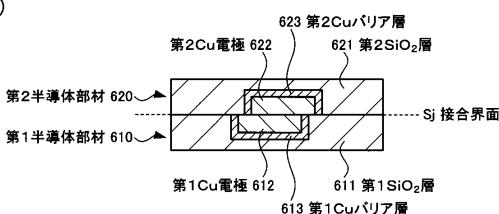

#### 【0017】

ここでは、第1SiO<sub>2</sub>層611、第1Cu電極612、及び、第1Cuバリア層613を含む第1半導体部材610と、第2SiO<sub>2</sub>層621、第2Cu電極622、及び、第2Cuバリア層623を含む第2半導体部材620とを接合する例を示す。

#### 【0018】

なお、図1(a)及び(b)に示す例では、各半導体部材において、Cu電極は、SiO<sub>2</sub>層の一方の表面に埋め込むようにして形成される。すなわち、Cu電極は、SiO<sub>2</sub>層の一方の表面に露出し、かつ、その露出面がSiO<sub>2</sub>層の一方の表面と略面一となるように形成される。また、Cuバリア層は、Cu電極とSiO<sub>2</sub>層との間に設けられる。そして、第1半導体部材610の第1Cu電極612側の表面と、第2半導体部材620の第2Cu電極622側の表面とが貼り合わされる。

#### 【0019】

第1半導体部材610と第2半導体部材620とを接合する際、両者の間に接合アライメントずれが発生すると、図1(b)に示すように、接合界面Sjにおいて、一方の半導体部材のCu電極と他方の半導体部材のSiO<sub>2</sub>層との接触領域が生成される。

#### 【0020】

この場合、接合時のアニール処理等により、図2に示すように、各Cu電極からSiO<sub>2</sub>層にCu630が拡散し、接合界面Sjにおいて、隣り合うCu電極間が短絡する可能性がある。また、各Cu電極からSiO<sub>2</sub>層へのCu630の拡散量が大きいとCu電極内のCuの量が減るので、例えば、接触抵抗の上昇や導通不良などの不具合が生じる場合も考えられる。

#### 【0021】

上述のような接合界面Sjにおける電気特性の不具合が生じると、半導体装置の性能が劣化する。そこで、本実施形態では、上述のような接合界面Sjにおける電気特性の不具合を解消することができる半導体装置の構成について説明する。

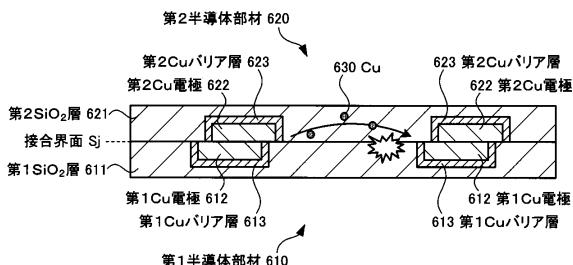

#### 【0022】

##### [半導体装置の構成]

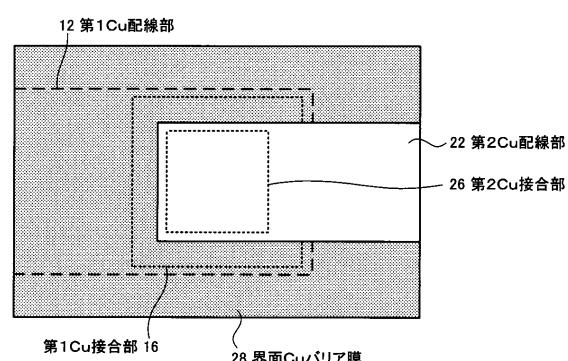

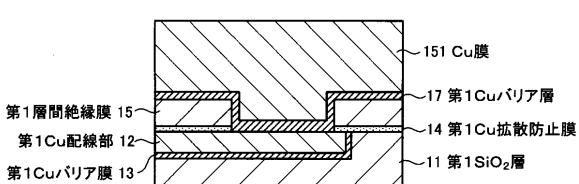

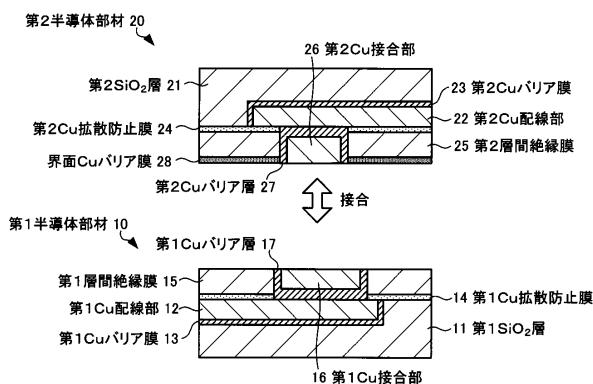

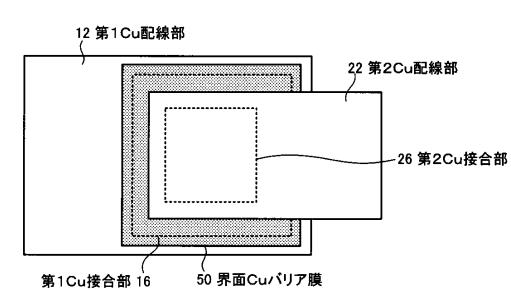

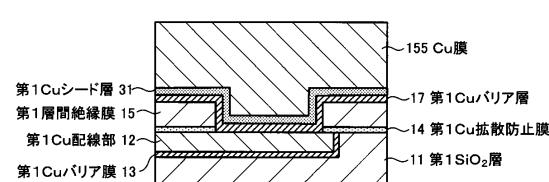

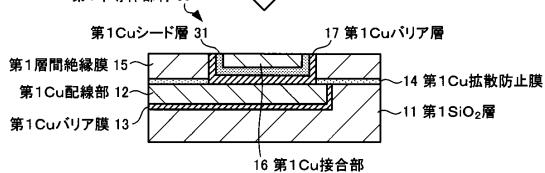

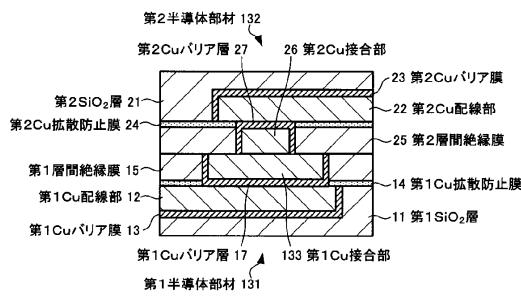

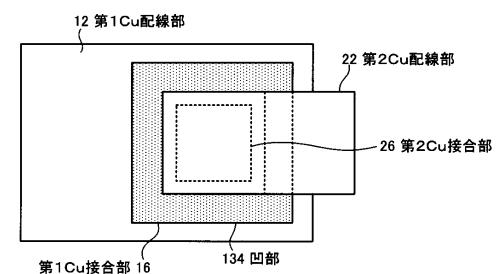

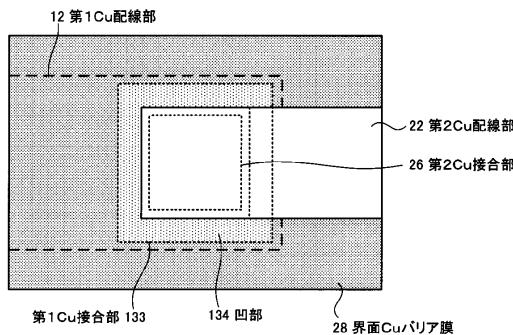

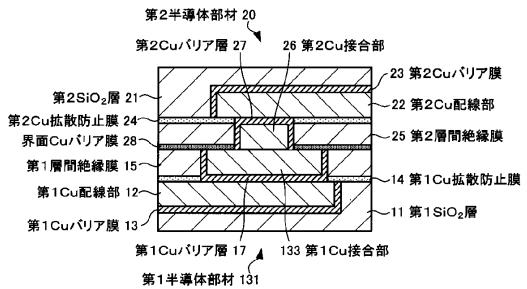

図3及び4に、第1の実施形態に係る半導体装置の概略構成を示す。図3は、第1の実施形態の半導体装置の接合界面付近の概略断面図であり、図4は、各Cu接合部及び後述の界面Cuバリア膜間の配置関係を示す接合界面付近の概略上面図である。なお、図3及び4では、説明を簡略化するため、1つの接合界面付近の構成のみを示す。

#### 【0023】

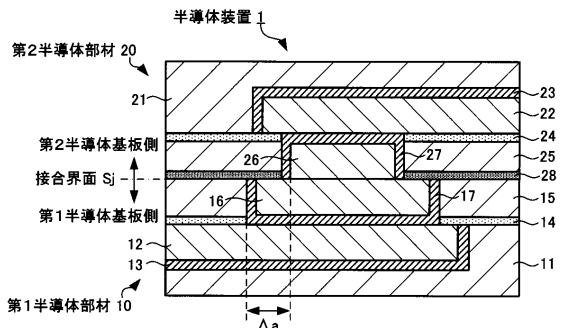

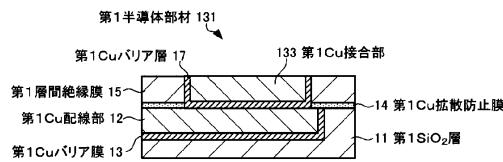

半導体装置1は、図3に示すように、第1半導体部材10(第1半導体部)と、第2半導体部材20(第2半導体部)とを備える。そして、本実施形態の半導体装置1では、第1半導体部材10の後述する第1層間絶縁膜15側の面が、第2半導体部材20の後述する界面Cuバリア膜28側の面と接合される。

#### 【0024】

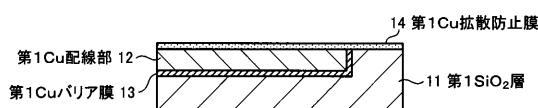

第1半導体部材10は、第1半導体基板(不図示)、第1SiO<sub>2</sub>層11、第1Cu配線部12、第1Cuバリア膜13、第1Cu拡散防止膜14、第1層間絶縁膜15、第1Cu接合部16、及び、第1Cuバリア層17を有する。

#### 【0025】

第1SiO<sub>2</sub>層11は、第1半導体基板上に形成される。第1Cu配線部12は、第1SiO<sub>2</sub>層11の第1半導体基板側とは反対側の表面に埋め込むようにして形成される。なお、第1Cu配線部12は、図4に示すように、所定方向に延在したCu膜であり、例えば、図示しない半導体装置1内及び/又は半導体装置1を含む電子機器内の所定のデバイス、信号処理回路等に接続される。

10

20

30

40

50

## 【0026】

第1Cuバリア膜13は、第1SiO<sub>2</sub>層11と第1Cu配線部12との間に形成される。なお、第1Cuバリア膜13は、第1Cu配線部12から第1SiO<sub>2</sub>層11へのCu(銅)の拡散を防止するための薄膜であり、例えば、Ti、Ta、Ru、又は、それらの窒化物(TiN、TaN、RuN)で形成される。

## 【0027】

第1Cu拡散防止膜14は、第1SiO<sub>2</sub>層11及び第1Cu配線部12の領域上であり、かつ、第1Cuバリア層17の形成領域以外の領域上に形成される。なお、第1Cu拡散防止膜14は、第1Cu配線部12から第1層間絶縁膜15へのCuの拡散を防止するための薄膜であり、例えばSiC、SiN、又は、SiCN等の薄膜で構成される。

10

## 【0028】

第1層間絶縁膜15は、第1Cu拡散防止膜14上に形成され、例えばSiO<sub>2</sub>膜等の酸化膜で構成される。

## 【0029】

第1Cu接合部16(第1金属膜)は、第1層間絶縁膜15の第1Cu拡散防止膜14側とは反対側の表面に埋め込むようにして設けられる。なお、本実施形態では、第1Cu接合部16を、図4に示すように、表面(膜面)が正方形状のCu膜で構成する。ただし、本開示はこれに限定されず、第1Cu接合部16の表面形状は、例えば、必要とする接触抵抗、デザインルール等の条件を考慮して適宜変更することができる。

## 【0030】

20

第1Cuバリア層17は、第1Cu接合部16と、第1Cu配線部12、第1Cu拡散防止膜14及び第1層間絶縁膜15との間に設けられ、第1Cu接合部16を覆うように設けられる。これにより、第1Cu接合部16は、第1Cuバリア層17を介して第1Cu配線部12に電気的に接続される。なお、第1Cuバリア層17は、第1Cu接合部16から第1層間絶縁膜15へのCuの拡散を防止するための薄膜であり、例えば、Ti、Ta、Ru、又は、それらの窒化物で形成される。

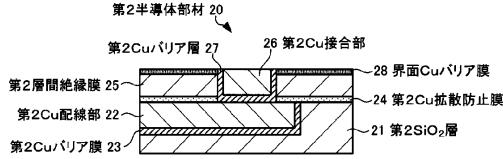

## 【0031】

第2半導体部材20は、第2半導体基板(不図示)、第2SiO<sub>2</sub>層21、第2Cu配線部22、第2Cuバリア膜23、第2Cu拡散防止膜24、第2層間絶縁膜25、第2Cu接合部26、第2Cuバリア層27、及び、界面Cuバリア膜28を有する。

30

## 【0032】

なお、本実施形態では、第2半導体部材20の第2半導体基板、第2SiO<sub>2</sub>層21、及び、第2Cu配線部22は、それぞれ、第1半導体部材10の第1半導体基板、第1SiO<sub>2</sub>層11、及び、第1Cu配線部12と同様の構成である。また、第2半導体部材20の第2Cuバリア膜23、第2Cu拡散防止膜24、及び、第2層間絶縁膜25は、それぞれ、第1半導体部材10の第1Cuバリア膜13、第1Cu拡散防止膜14、及び、第1層間絶縁膜15と同様の構成である。

## 【0033】

第2Cu接合部26(第2金属膜)は、第2層間絶縁膜25(絶縁膜)の第2Cu拡散防止膜24側とは反対側の表面に埋め込むようにして設けられる。なお、本実施形態では、第2Cu接合部26を、図4に示すように、表面が正方形状のCu膜で構成する。ただし、本開示はこれに限定されず、第2Cu接合部26の表面形状は、例えば、必要とする接触抵抗、デザインルール等の条件を考慮して適宜変更することができる。

40

## 【0034】

また、本実施形態では、図3及び4に示すように、第2Cu接合部26の接合側(接合界面Sj側)の表面面積(接合側表面の寸法)を、第1Cu接合部16のそれより小さくする。この際、第1半導体部材10及び第2半導体部材20間で想定される最大の接合アライメントずれが発生しても、接合界面Sjにおいて、第2Cu接合部26と第1層間絶縁膜15とが接触しないように、第2Cu接合部26のサイズを設定する。より具体的には、例えば、図3に示すように、第2Cu接合部26の側面と第1Cuバリア層17の側

50

面との最短距離を  $a$  としたとき、 $a$  が想定される最大の接合アライメントずれ以上の寸法となるように、第 2 Cu 接合部 26 のサイズを設定する。

【0035】

第 2 Cu バリア層 27 は、第 2 Cu 接合部 26 と、第 2 Cu 配線部 22、第 2 Cu 拡散防止膜 24 及び第 2 層間絶縁膜 25 との間に設けられ、第 2 Cu 接合部 26 を覆うように設けられる。これにより、第 2 Cu 接合部 26 は、第 2 Cu バリア層 27 を介して第 2 Cu 配線部 22 に電気的に接続される。なお、第 2 Cu バリア層 27 は、第 1 Cu バリア層 17 と同様に、第 2 Cu 接合部 26 から第 2 層間絶縁膜 25 への Cu の拡散を防止するための薄膜であり、例えば、Ti、Ta、Ru、又は、それらの窒化物で形成される。

【0036】

界面 Cu バリア膜 28（界面バリア膜、界面バリア部）は、第 2 層間絶縁膜 25 上に形成される。この際、界面 Cu バリア膜 28 の表面と、第 2 Cu 接合部 26 の接合側の表面とが略面一となるように、界面 Cu バリア膜 28 を形成する。すなわち、界面 Cu バリア膜 28 は、第 1 Cu 接合部 16 の接合界面  $S_j$  側の面領域のうち第 2 Cu 接合部 26 と接合しない面領域を含む領域に設けられる。このような領域（位置）に界面 Cu バリア膜 28 を設けることにより、接合界面  $S_j$  における第 1 Cu 接合部 16 と第 2 層間絶縁膜 25 との対向領域を介して、Cu 接合部から層間絶縁膜（ $SiO_2$  膜）に Cu が拡散することを防止することができる。

【0037】

なお、界面 Cu バリア膜 28 は、例えば、SiN、SiON、SiCN、有機系樹脂等の材料で形成することができる。ただし、Cu 膜との密着性向上という観点では、特に、界面 Cu バリア膜 28 を SiN で形成することが好ましい。

【0038】

【半導体装置の製造手法】

次に、本実施形態の半導体装置 1 の製造手法を、図 5～17 を参照しながら説明する。なお、図 5～16 には、各工程で作製される半導体部材の Cu 接合部付近の概略断面を示し、図 17 には、第 1 半導体部材 10 と第 2 半導体部材 20 との接合処理の様子を示す。

【0039】

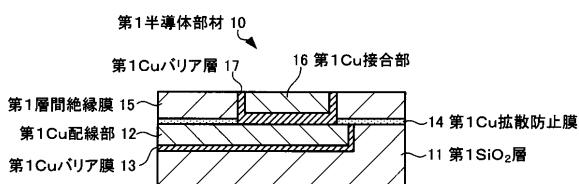

最初に、図 5～10 を参照しながら、第 1 半導体部材 10 の作製手法を説明する。本実施形態では、図示しないが、まず、第 1 SiO<sub>2</sub> 層 11（下地絶縁層）の一方の表面の所定領域に、第 1 Cu バリア膜 13、及び、第 1 Cu 配線部 12 をこの順で形成する。この際、第 1 Cu 配線部 12 を、第 1 SiO<sub>2</sub> 層 11 の一方の表面に埋め込むように（第 1 Cu 配線部 12 が該表面に露出するように）形成する。

【0040】

次いで、図 5 に示すように、第 1 SiO<sub>2</sub> 層 11、第 1 Cu 配線部 12、及び、第 1 Cu バリア膜 13 からなる半導体部材の第 1 Cu 配線部 12 側の表面上に、第 1 Cu 拡散防止膜 14 を形成する。なお、第 1 SiO<sub>2</sub> 層 11、第 1 Cu 配線部 12、第 1 Cu バリア膜 13、及び、第 1 Cu 拡散防止膜 14 は、従来の例えば固体撮像装置等の半導体装置の製造手法（例えば特開 2004-63859 号公報参照）と同様にして形成することができる。

【0041】

次いで、第 1 Cu 拡散防止膜 14 上に、第 1 層間絶縁膜 15 を形成する。具体的には、例えば、第 1 Cu 拡散防止膜 14 上に、厚さが約 50～500 nm 程度の SiO<sub>2</sub> 膜又は炭素含有酸化シリコン（SiOC）膜を成膜して第 1 層間絶縁膜 15 を形成する。なお、このような第 1 層間絶縁膜 15 は、例えば CVD（Chemical Vapor Deposition）法、又は、スピンドルコート法で形成することができる。

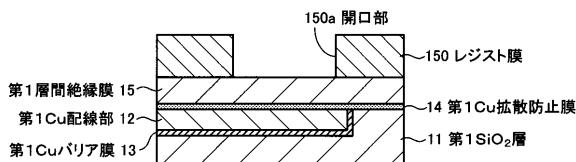

【0042】

次いで、図 6 に示すように、第 1 層間絶縁膜 15 上にレジスト膜 150 を形成する。そして、フォトリソグラフィ技術を用いて、レジスト膜 150 に対してパターニング処理を施し、第 1 Cu 接合部 16 の形成領域のレジスト膜 150 を除去して開口部 150a を形

10

20

30

40

50

成する。

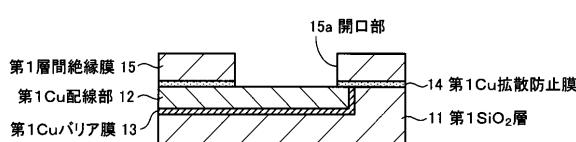

【0043】

次いで、レジスト膜150が形成された半導体部材の開口部150a側の表面に対して、例えは從来既知のマグネットロン方式のエッティング装置を用いて、ドライエッティング処理を行う。これにより、レジスト膜150の開口部150aに露出した第1層間絶縁膜15の領域がエッティングされる。このエッティング処理では、図7に示すように、レジスト膜150の開口部150aの領域の第1層間絶縁膜15、及び、第1Cu拡散防止膜14を除去し、第1層間絶縁膜15の開口部15aに第1Cu配線部12を露出させる。なお、本実施形態では、第1層間絶縁膜15の開口部15aの開口径を、例えは、約4～100μm程度とする。

10

【0044】

その後、エッティング処理された面に対して、例えは酸素(O<sub>2</sub>)プラズマを用いたアッシング処理、及び、有機アミン系の薬液を用いた洗浄処理を施す。これにより、第1層間絶縁膜15上に残留したレジスト膜150、及び、上記エッティング処理で発生した残留付着物を除去する。

【0045】

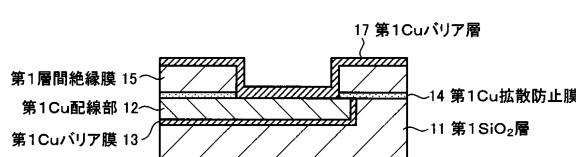

次いで、図8に示すように、第1層間絶縁膜15上、及び、第1層間絶縁膜15の開口部15aに露出した第1Cu配線部12上に、Ti、Ta、Ru、又は、それらの窒化物からなる第1Cuバリア層17を形成する。具体的には、例えはRF(Radio Frequency)スパッタリング法等の手法を用いて、Ar/N<sub>2</sub>雰囲気中で、厚さが約5～50nmの第1Cuバリア層17を、第1層間絶縁膜15及び第1Cu配線部12上に形成する。

20

【0046】

次いで、図9に示すように、第1Cuバリア層17上に、例えはスパッタリング法及び電解メッキ法等の手法を用いて、Cu膜151を形成する。この処理により、第1層間絶縁膜15の開口部15aの領域にCu膜151が埋め込まれる。

【0047】

次いで、Cu膜151が形成された半導体部材を、例えはホットプレートやシンターアニール装置等の加熱装置を用いて、窒素雰囲気中又は真空中で、約100～400で1～60分程度加熱する。この加熱処理により、Cu膜151を引き締めて緻密な膜質のCu膜151を形成する。

30

【0048】

その後、図10に示すように、Cu膜151及び第1Cuバリア層17の不要な部分を化学機械研磨(CMP)法により除去する。具体的には、第1層間絶縁膜15が表面に露出するまで、Cu膜151側の表面をCMP法で研磨する。

【0049】

本実施形態では、上述した図5～10の各種工程を行い、第1半導体部材10を作製する。次に、第2半導体部材20の作製手法を、図11～16を参照しながら説明する。

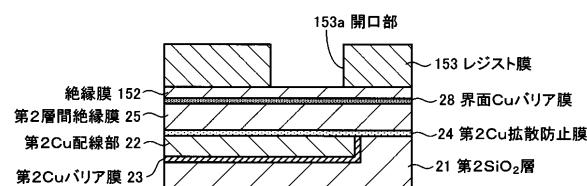

【0050】

まず、第1半導体部材10と同様にして(図5の工程)、第2SiO<sub>2</sub>層21の一方の表面の所定領域に、第2Cuバリア膜23、及び、第2Cu配線部22をこの順で形成する。次いで、第2SiO<sub>2</sub>層21、第2Cu配線部22、及び、第2Cuバリア膜23からなる半導体部材の第2Cu配線部22側の表面上に、第2Cu拡散防止膜24を形成する。

40

【0051】

次いで、第2Cu拡散防止膜24上に、第2層間絶縁膜25を形成する。具体的には、例えは、第2Cu拡散防止膜24上に、厚さが約50～500nm程度のSiO<sub>2</sub>膜又はSiOC膜を成膜して第2層間絶縁膜25を形成する。なお、このような第2層間絶縁膜25は、例えはCVD法又はスピノコート法で形成することができる。次いで、第2層間絶縁膜25上に、例えはCVD法又はスピノコート法等の手法を用いて、厚さが約5～100nm程度の界面Cuバリア膜28を形成する。次いで、界面Cuバリア膜28上に、

50

例えばCVD法又はスピンドル法等の手法を用いて、厚さが約50~200nm程度のSiO<sub>2</sub>膜又はSiOC膜を成膜して絶縁膜152を形成する。

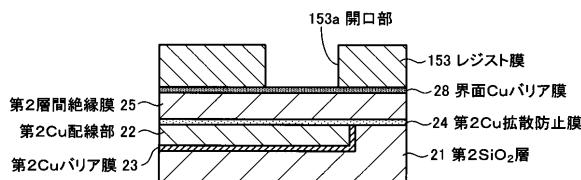

#### 【0052】

次いで、図11に示すように、絶縁膜152上にレジスト膜153を形成する。そして、フォトリソグラフィ技術を用いて、レジスト膜153に対してパターニング処理を施し、第2Cu接合部26の形成領域のレジスト膜153を除去して開口部153aを形成する。なお、開口部153aの開口径は、図6の工程で形成したレジスト膜150の開口部150aのそれより小さくする。

#### 【0053】

ただし、上述したレジスト膜153に開口部153aが形成された半導体部材の作製工程は、図11に示す例に限定されず、例えば、界面Cuバリア膜28上に直接、レジスト膜153を設け、さらに、開口部153aを形成してもよい。図12に、その手法で開口部153aを形成した際の半導体部材の概略断面図を示す。

#### 【0054】

ただし、図12に示す手法を採用した場合、界面Cuバリア膜28上に直接、第2Cuバリア層27を介してCu膜が形成され、その後、該Cu膜をCMP処理で研磨することにより第2Cu接合部26が形成される。しかしながら、通常、界面Cuバリア膜28はCMP処理で研磨することが難しい膜であるので、図12に示す手法を採用した場合には、CMP処理時に、Cu膜の削り残しが界面Cuバリア膜28上に発生する場合もある。

#### 【0055】

それに対して、図11に示す開口部153aの形成手法では、界面Cuバリア膜28上に絶縁膜152が形成されるので、Cu膜のCMP処理時に絶縁膜152も一緒に研磨することにより、Cu膜の削り残しをより確実に無くすことができる。すなわち、第2Cu接合部26を形成する際のCu膜の削り残しを防止する観点では、図11に示す開口部153aの形成手法が図12に示す開口部153aの形成手法より好適である。

#### 【0056】

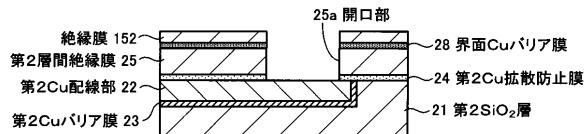

次いで、レジスト膜153が形成された半導体部材の開口部153a側の表面に対して、例えば従来既知のマグネットロン方式のエッチャリング装置を用いて、ドライエッチャリング処理を行う。これにより、レジスト膜153の開口部153aに露出した絶縁膜152の領域がエッチャリングされる。このエッチャリング処理では、図13に示すように、開口部153aの領域の絶縁膜152、界面Cuバリア膜28、第2層間絶縁膜25、及び、第2Cu拡散防止膜24を除去し、第2層間絶縁膜25の開口部25aに第2Cu配線部22を露出させる。なお、本実施形態では、第2層間絶縁膜25の開口部25aの開口径は、例えば、約1~95μm程度とする。

#### 【0057】

その後、エッチャリング処理された面に対して、例えば酸素(O<sub>2</sub>)プラズマを用いたアッシング処理、及び、有機アミン系の薬液を用いた洗浄処理を施す。これにより、絶縁膜152上に残留したレジスト膜153、及び、上記エッチャリング処理で発生した残留付着物を除去する。

#### 【0058】

次いで、図14に示すように、絶縁膜152上、及び、第2層間絶縁膜25の開口部25aに露出した第2Cu配線部22上に、Ti、Ta、Ru、又は、それらの窒化物からなる第2Cuバリア層27を形成する。具体的には、例えばRFスパッタリング法等の手法を用いて、Ar/N<sub>2</sub>雰囲気中で、厚さが約5~50nmの第2Cuバリア層27を、絶縁膜152及び第2Cu配線部22上に形成する。

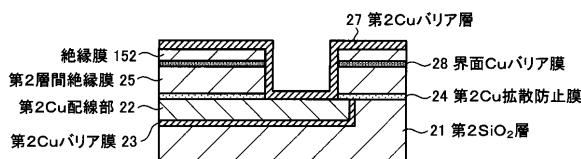

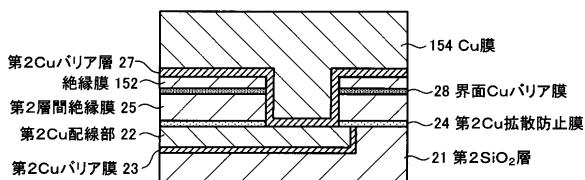

#### 【0059】

次いで、図15に示すように、第2Cuバリア層27上に、例えばスパッタリング法及び電解メッキ法等の手法を用いて、Cu膜154を形成する。この処理により、第2層間絶縁膜25の開口部25aの領域にCu膜154が埋め込まれる。

#### 【0060】

10

20

30

40

50

次いで、Cu膜154が形成された半導体部材を、例えばホットプレートやシンターアニール装置等の加熱装置を用いて、窒素雰囲気中又は真空中で、約100～400で1～60分程度加熱する。この加熱処理により、Cu膜154を引き締めて緻密な膜質のCu膜154を形成する。

【0061】

そして、図16に示すように、Cu膜154、第2Cuバリア層27及び絶縁膜152の不要な部分を化学機械研磨(CMP)法により除去する。具体的には、界面Cuバリア膜28が表面に露出するまで、Cu膜154側の表面をCMP法で研磨する。本実施形態では、上述した図11～16の各種工程を行い、第2半導体部材20を作製する。

【0062】

次いで、上記手順で作製された第1半導体部材10(図10)と第2半導体部材20(図16)とを貼り合わせる。この貼り合わせ工程(接合工程)の具体的な処理内容は、次の通りである。

【0063】

まず、第1半導体部材10の第1Cu接合部16側の表面、及び、第2半導体部材20の第2Cu接合部26側の表面に対して還元処理を施し、各Cu接合部の表面の酸化膜(酸化物)を除去する。これにより、各Cu接合部の表面に清浄なCuを露出させる。なお、この際、還元処理としては、例えば蟻酸等の薬液を用いたウェットエッチング処理、又は、例えばAr、NH<sub>3</sub>、H<sub>2</sub>等のプラズマを用いたドライエッチング処理が用いられる。

【0064】

次いで、図17に示すように、第1半導体部材10の第1Cu接合部16側の表面と、第2半導体部材20の第2Cu接合部26側の表面とを接触させる(貼り合わせる)。この際、第1Cu接合部16と、それに対応する第2Cu接合部26とが対向するように位置合わせを行ってから両者を貼り合わせる。

【0065】

次いで、第1半導体部材10及び第2半導体部材20を貼り合わせた状態で、例えばホットプレートやRTA(Rapid Thermal Annealing)装置等の加熱装置を用いて貼り合わせ部材をアニールして、第1Cu接合部16と第2Cu接合部26とを接合する。具体的には、例えば、大気圧のN<sub>2</sub>雰囲気中、又は、真空中で約100～400で5分～2時間程度、貼り合わせ部材を加熱する。

【0066】

また、この接合処理により、第1Cu接合部16の接合界面Sj側の面領域のうち第2Cu接合部26と接合しない面領域を含む領域に界面Cuバリア膜28が配置される。より具体的には、図3に示すように、第1Cu接合部16と、第2層間絶縁膜25とが対向する接合界面Sjの領域を含む領域に界面Cuバリア膜28が配置される。

【0067】

本実施形態では、このようにして、Cu-Cu接合処理を行う。なお、上述した接合工程以外の半導体装置1の製造工程は、従来の例えば固体撮像装置等の半導体装置の製造手法(例えば特開2007-234725号公報参照)と同様にすることができます。

【0068】

上述のように、本実施形態の半導体装置1では、第1半導体部材10の第1Cu接合部16と、第2半導体部材20の第2層間絶縁膜25とが対向する接合界面領域を含む領域には、界面Cuバリア膜28が設けられる。それゆえ、本実施形態では、半導体部材の接合時に、接合アライメントずれが発生しても、接合界面Sjにおいて、Cu接合部と層間絶縁膜との接触領域が発生せず、上述した接合界面Sjにおける電気特性の不具合を解消することができる。

【0069】

また、本実施形態では、上述のように、第1Cu接合部16の接合側の表面面積を、第2Cu接合部26のそれより十分大きくする。それゆえ、本実施形態では、第1半導体部

10

20

30

40

50

材10及び第2半導体部材20の接合時に接合アライメントずれが発生しても、Cu接合部間の接触面積（接触抵抗）は変化せず、半導体装置1の電気特性（性能）の劣化を抑制することができる。すなわち、本実施形態では、接合界面Sjにおける接触抵抗の増大を抑制することができるので、半導体装置1の消費電力の増大、及び、処理速度の遅延を抑制することができる。

【0070】

さらに、本実施形態では、第1Cu接合部16と第2層間絶縁膜25との間には、界面Cuバリア膜28が設けられるので、両者間の密着力を向上させることができる。これにより、本実施形態では、第1半導体部材10及び第2半導体部材20間の接合強度を増大させることができます。

10

【0071】

以上のことから、本実施形態では、接合界面における電気特性の劣化をより一層抑制することができ、より信頼性の高い接合界面Sjを有する半導体装置1を提供することができる。

【0072】

<2. 第2の実施形態>

[半導体装置の構成]

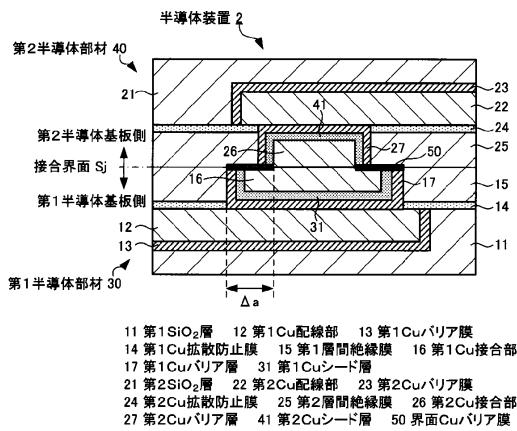

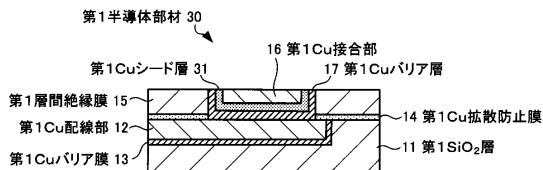

図18及び19に、第2の実施形態に係る半導体装置の概略構成を示す。図18は、第2の実施形態に係る半導体装置の接合界面付近の概略断面図であり、図19は、各Cu接合部及び界面Cuバリア膜間の配置関係を示す接合界面付近の概略上面図である。なお、図18及び19では、説明を簡略化するため、1つの接合界面付近の構成のみを示す。また、図18及び19に示す本実施形態の半導体装置2において、図3及び4に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

20

【0073】

半導体装置2は、図18に示すように、第1半導体部材30（第1半導体部）と、第2半導体部材40（第2半導体部）と、界面Cuバリア膜50（界面バリア膜、界面バリア部）とを備える。

【0074】

第1半導体部材30は、第1半導体基板（不図示）、第1SiO<sub>2</sub>層11、第1Cu配線部12、第1Cuバリア膜13、第1Cu拡散防止膜14、第1層間絶縁膜15、第1Cu接合部16、第1Cuバリア層17、及び、第1Cuシード層31を有する。

30

【0075】

図18と図3との比較から明らかなように、本実施形態の第1半導体部材30は、第1の実施形態の第1半導体部材10において、第1Cu接合部16と第1Cuバリア層17との間に第1Cuシード層31を設けた構成となる。それ以外の第1半導体部材30の構成は、上記第1の実施形態の第1半導体部材10の対応する構成と同様である。それゆえ、ここでは、第1Cuシード層31の構成についてのみ説明する。

【0076】

第1Cuシード層31（シード層）は、上述のように、第1Cu接合部16と第1Cuバリア層17との間に設けられ、第1Cu接合部16を覆うように形成される。

40

【0077】

第1Cuシード層31は、酸素と反応し易い金属材料を含有するCu層（Cu合金層）で形成される。第1Cuシード層31に含有する金属材料としては、例えば、酸素に対して水素よりも反応し易い金属材料を用いることができる。具体的には、Fe、Mn、V、Cr、Mg、Si、Ce、Ti、Al等の金属材料を用いることができる。なお、これらの金属材料のうち、Mn、Mg、Ti、又は、Alは、半導体装置に好適な材料である。さらに、接合界面Siの配線抵抗の低下という観点では、第1Cuシード層31に含有する金属材料として、Mn、又は、Tiを用いることが特に好ましい。

【0078】

第2半導体部材40は、第2半導体基板（不図示）、第2SiO<sub>2</sub>層21、第2Cu配

50

線部 22、第 2 Cu バリア膜 23、第 2 Cu 拡散防止膜 24、第 2 層間絶縁膜 25、第 2 Cu 接合部 26、第 2 Cu バリア層 27、及び、第 2 Cu シード層 41 を有する。

【 0079 】

図 18 と図 3 との比較から明らかなように、本実施形態の第 2 半導体部材 40 は、第 1 の実施形態の第 2 半導体部材 20 において、界面 Cu バリア膜 28 を省略し、かつ、第 2 Cu 接合部 26 及び第 2 Cu バリア層 27 間に第 2 Cu シード層 41 を設けた構成となる。それ以外の第 2 半導体部材 40 の構成は、上記第 1 の実施形態の第 2 半導体部材 20 の対応する構成と同様である。それゆえ、ここでは、第 2 Cu シード層 41 の構成についてのみ説明する。

【 0080 】

第 2 Cu シード層 41 は、上述のように、第 2 Cu 接合部 26 と第 2 Cu バリア層 27 との間に設けられ、第 2 Cu 接合部 26 を覆うように形成される。第 2 Cu シード層 41 は、第 1 Cu シード層 31 と同様に、酸素と反応し易い金属材料を含有する Cu 層 (Cu 合金層) で形成される。また、第 2 Cu シード層 41 に含有する金属材料は、上記第 1 Cu シード層 31 で説明した各種金属材料から適宜選択することができる。なお、本実施形態では、第 2 Cu シード層 41 に含まれる金属材料は、第 1 Cu シード層 31 に含まれる金属材料と同じとする。

【 0081 】

界面 Cu バリア膜 50 は、第 1 半導体部材 30 と第 2 半導体部材 40 とを接合する際の熱処理 (アニール処理) により、各 Cu シード層に含まれる金属材料と各層間絶縁膜 (主に第 2 層間絶縁膜 25) 中の酸素とが反応して生成される膜 (自己形成膜) である。それゆえ、界面 Cu バリア膜 50 は、第 1 半導体部材 30 の第 1 Cu 接合部 16 と、第 2 半導体部材 40 の第 2 層間絶縁膜 25 とが対向する接合界面 Sj の領域に形成され、例えば、MnOx、MgOx、TiOx、AlOx 等の酸化膜で構成される。

【 0082 】

なお、図 18 では、界面 Cu バリア膜 50 の形成位置を明確にするために、界面 Cu バリア膜 50 が、接合界面 Sj に沿って、第 2 Cu 接合部 26 の側面から第 1 Cu バリア層 17 の側面に渡って形成された例を示す。しかしながら、界面 Cu バリア膜 50 の形成領域は、この例に限定されない。

【 0083 】

界面 Cu バリア膜 50 は、第 1 Cu 接合部 16 と第 2 層間絶縁膜 25 との対向領域を介して、Cu 接合部から層間絶縁膜に Cu が拡散することを防止するための膜である。それゆえ、接合界面 Sj において、少なくとも、第 1 Cu 接合部 16 と第 2 層間絶縁膜 25 との対向領域に界面 Cu バリア膜 50 を形成すればよい。なお、界面 Cu バリア膜 50 の形成領域は、例えば、第 1 半導体部材 30 と第 2 半導体部材 40 との接合処理時のアニール条件や、各 Cu シード層中の金属材料の含有量などを調整することにより適宜設定することができる。

【 0084 】

[ 半導体装置の製造手法 ]

次に、本実施形態の半導体装置 2 の製造手法を、図 20 ~ 24 を参照しながら説明する。なお、図 20 ~ 23 には、各工程で作製される半導体部材の Cu 接合部付近の概略断面を示し、図 24 には、第 1 半導体部材 30 と第 2 半導体部材 40 との接合処理の様子を示す。また、下記説明において、上記第 1 の実施形態の半導体装置の製造手法と同様の工程の説明では、上記第 1 の実施形態の工程の図面 (図 5 ~ 17) を適宜参照する。

【 0085 】

まず、本実施形態では、上記図 5 で説明した第 1 の実施形態の第 1 半導体部材 10 の作製工程と同様にして、第 1 SiO<sub>2</sub> 層 11 上に、第 1 Cu バリア膜 13、第 1 Cu 配線部 12、及び、第 1 Cu 拡散防止膜 14 をこの順で形成する。次いで、上記図 6 及び 7 で説明した第 1 の実施形態の第 1 半導体部材 10 の作製工程と同様にして、第 1 Cu 拡散防止膜 14 上に、第 1 層間絶縁膜 15 (第 1 酸化膜)、及び、その開口部 15a を形成する。

10

20

30

40

50

なお、本実施形態においても、第1層間絶縁膜15の開口部15aの開口径は、例えば、約4～100μm程度とする。そして、上記図8で説明した第1の実施形態の第1半導体部材10の作製工程と同様にして、第1層間絶縁膜15上、及び、その開口部15aに露出した第1Cu配線部12上に、第1Cuバリア層17を形成する。

【0086】

次いで、図20に示すように、第1Cuバリア層17上に、例えばRFスパッタリング法等の手法を用いて、Ar/N<sub>2</sub>雰囲気中で、厚さが約5～50nmの第1Cuシード層31（例えばCuMn層、CuAl層、CuMg層、CuTi層等）を形成する。

【0087】

次いで、図21に示すように、第1Cuシード層31上に、例えばスパッタリング法及び電解メッキ法等の手法を用いて、Cu膜155を形成する。この処理により、第1層間絶縁膜15の開口部15aの領域にCu膜155が埋め込まれる。

【0088】

次いで、Cu膜155が形成された半導体部材を、例えばホットプレートやシンターアニール装置等の加熱装置を用いて、窒素雰囲気中又は真空中で、約100～400で1～60分程度加熱する。この加熱処理により、Cu膜155を引き締めて緻密な膜質のCu膜155を形成する。

【0089】

次いで、図22に示すように、Cu膜155、第1Cuシード層31及び第1Cuバリア層17の不要な部分をCMP法により除去する。具体的には、第1層間絶縁膜15が表面に露出するまで、Cu膜155側の表面をCMP法で研磨する。

【0090】

本実施形態では、上述のようにして、第1半導体部材30を作製する。また、本実施形態では、上述した第1半導体部材30と同様にして第2半導体部材40を作製する。

【0091】

図23に、本実施形態で作製された第2半導体部材40の概略断面図を示す。ただし、本実施形態では、第2半導体部材40の作製途中で、第2層間絶縁膜25（第2酸化膜）に開口部を形成する際に、その開口部の開口径を、図7で説明した第1層間絶縁膜15の開口径（約4～100μm程度）より小さくする。具体的には、第2層間絶縁膜25に開口部の開口径を約1～95μm程度にする。

【0092】

その後、上述のようにして作製された第1半導体部材30（図22）と第2半導体部材40（図23）とを、上記第1の実施形態と同様にして貼り合わせる。

【0093】

具体的には、まず、第1半導体部材30の第1Cu接合部16側の表面、及び、第2半導体部材40の第2Cu接合部26側の表面に対して還元処理を施し、各Cu接合部の表面の酸化膜（酸化物）を除去して、各Cu接合部の表面に清浄なCuを露出させる。なお、この際、還元処理としては、例えば蟻酸等の薬液を用いたウェットエッティング処理、又は、例えばAr、NH<sub>3</sub>、H<sub>2</sub>等のプラズマを用いたドライエッティング処理が用いられる。

【0094】

次いで、図24に示すように、第1半導体部材30の第1Cu接合部16側の表面と、第2半導体部材40の第2Cu接合部26側の表面とを接触させる（貼り合わせる）。そして、第1半導体部材30と第2半導体部材40とを貼り合わせた状態で、例えばホットプレートやRTA装置等の加熱装置を用いて貼り合わせ部材をアニールして、第1Cu接合部16と第2Cu接合部26とを接合する。具体的には、例えば、大気圧のN<sub>2</sub>雰囲気中、又は、真空中で約100～400で5分～2時間程度、貼り合わせ部材を加熱する。

【0095】

また、上述した接合処理時には、各Cuシード層中の金属材料（例えばMn、Mg、T

10

20

30

40

50

i、A1など)が層間絶縁膜(主に、第2層間絶縁膜25)中の酸素と選択的に反応する。これにより、第1半導体部材30の第1Cu接合部16と、第2半導体部材40の第2層間絶縁膜25とが対向する接合界面Sjの領域に、界面Cuバリア膜50が形成される。すなわち、上記接合処理により、第1Cu接合部16の接合界面Sj側の面領域のうち第2Cu接合部26と接合しない面領域を含む領域に界面Cuバリア膜50が設けられる。

#### 【0096】

本実施形態では、上述のようにして、Cu-Cu接合処理を行う。なお、上述した接合工程以外の半導体装置2の製造工程は、従来の例えば固体撮像装置等の半導体装置の製造手法(例えば特開2007-234725号公報参照)と同様にすることができる。

10

#### 【0097】

上述のように、本実施形態の半導体装置2においても、上記第1の実施形態と同様に、第1半導体部材30の第1Cu接合部16と、第2半導体部材40の第2層間絶縁膜25とが対向する接合界面Sjの領域には、界面Cuバリア膜50が設けられる。それゆえ、本実施形態においても、第1の実施形態と同様の効果が得られる。

#### 【0098】

また、本実施形態のように、Cuシード層を設け、さらにCuシード層上にCu接合部を電解メッキ法で形成した場合、Cuシード層中のCuが、Cuメッキ膜の核となる。それゆえ、本実施形態では、Cu接合部及び層間絶縁膜間の密着力を向上させることができる。

20

#### 【0099】

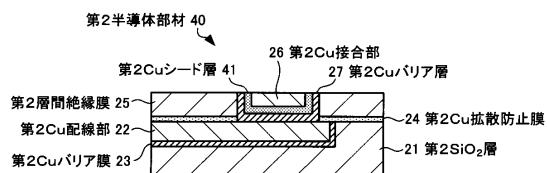

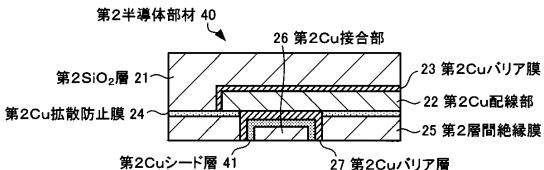

<3. 第3の実施形態>

#### [半導体装置の構成]

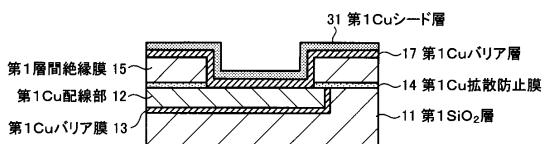

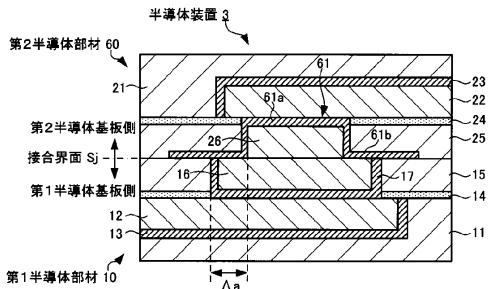

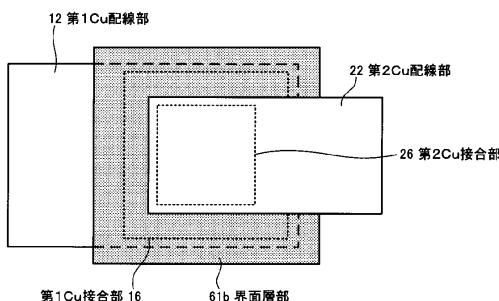

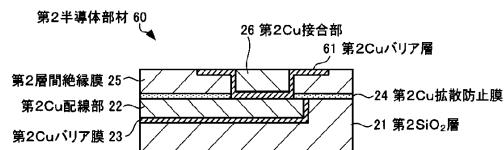

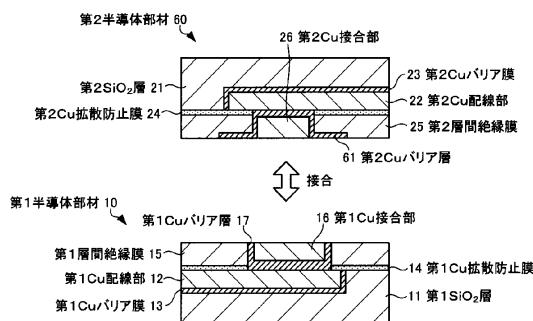

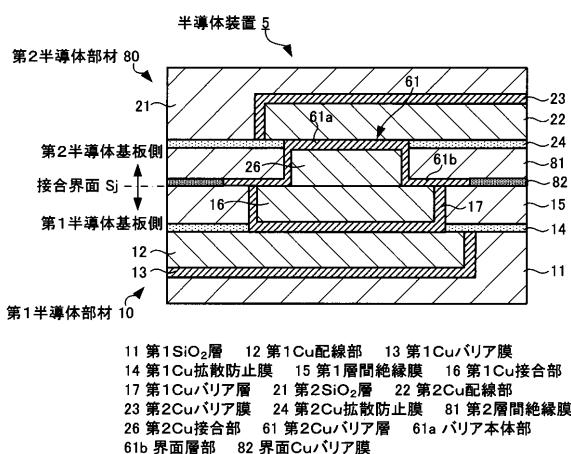

図25及び26に、第3の実施形態に係る半導体装置の概略構成を示す。図25は、第3の実施形態に係る半導体装置の接合界面付近の概略断面図であり、図26は、各Cu接合部及び後述の第2Cuバリア層の界面層部間の配置関係を示す接合界面付近の概略上面図である。なお、図25及び26では、説明を簡略化するため、1つの接合界面付近の構成のみを示す。また、図25及び26に示す本実施形態の半導体装置3において、図3及び4に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

#### 【0100】

30

半導体装置3は、図25に示すように、第1半導体部材10(第1半導体部)と、第2半導体部材60(第2半導体部)とを備える。なお、本実施形態の半導体装置3における第1半導体部材10の構成は、上記第1の実施形態(図3)のそれと同様の構成であるので、ここでは、第1半導体部材10の説明は省略する。

#### 【0101】

第2半導体部材60は、第2半導体基板(不図示)、第2SiO<sub>2</sub>層21、第2Cu配線部22、第2Cuバリア膜23、第2Cu拡散防止膜24、第2層間絶縁膜25、第2Cu接合部26、及び、第2Cuバリア層61(バリアメタル層)を有する。

#### 【0102】

図25と図3との比較から明らかなように、本実施形態の第2半導体部材60は、第1の実施形態の第2半導体部材20において、界面Cuバリア膜28を省略し、かつ、第2Cuバリア層27の構成を変えたものとなる。それ以外の第2半導体部材60の構成は、上記第1の実施形態の第2半導体部材20の対応する構成と同様である。それゆえ、ここでは、第2Cuバリア層61の構成についてのみ説明する。

40

#### 【0103】

第2Cuバリア層61は、図25に示すように、第2Cu接合部26を被覆するように設けられたバリア本体部61aと、該バリア本体部61aの接合界面Sj側の端部から接合界面Sjに沿って延在して形成された界面層部61b(界面バリア部)とを有する。

#### 【0104】

すなわち、本実施形態では、第1半導体部材10の第1Cu接合部16と、第2半導体

50

部材 6 0 の第 2 層間絶縁膜 2 5 とが対向する接合界面 S j の領域に、第 2 Cu バリア層 6 1 の界面層部 6 1 b を配置する。そして、第 2 Cu バリア層 6 1 の界面層部 6 1 b が、第 1 Cu 接合部 1 6 と第 2 層間絶縁膜 2 5 との対向領域を介して、Cu 接合部から層間絶縁膜に Cu が拡散することを防止する。それゆえ、本実施形態では、接合時に想定される最大の接合アライメントずれが発生しても、接合界面 S j に、第 1 Cu 接合部 1 6 と第 2 層間絶縁膜 2 5 との接触領域が発生しないように、界面層部 6 1 b の接合界面 S j に沿う方向の幅を設定する。なお、第 2 Cu バリア層 6 1 は、上記第 1 の実施形態と同様に、例えば、T i、T a、R u、又は、それらの窒化物等で形成される。

#### 【 0 1 0 5 】

##### [ 半導体装置の製造手法 ]

10

次に、本実施形態の半導体装置 3 の製造手法を、図 2 7 ~ 3 4 を参照しながら説明する。なお、図 2 7 ~ 3 3 には、各工程で作製される半導体部材の Cu 接合部付近の概略断面を示し、図 3 4 には、第 1 半導体部材 1 0 と第 2 半導体部材 6 0 との接合処理の様子を示す。また、下記説明において、上記第 1 の実施形態の半導体装置の製造手法と同様の工程の説明では、上記第 1 の実施形態の工程の図面（図 5 ~ 1 7 ）を適宜参照する。さらに、本実施形態の第 1 半導体部材 1 0 の作製手法は、上記第 1 の実施形態のそれ（図 5 ~ 1 0 ）と同様であるので、ここでは、第 1 半導体部材 1 0 の作製手法の説明を省略し、第 2 半導体部材 6 0 の作製手法、及び、Cu - Cu 接合手法について説明する。

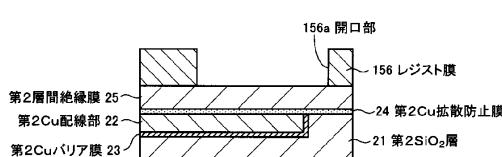

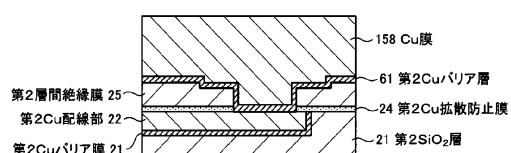

#### 【 0 1 0 6 】

まず、本実施形態では、上記図 5 で説明した第 1 の実施形態の第 1 半導体部材 1 0 の作製工程と同様にして、第 2 SiO<sub>2</sub> 層 2 1 上に、第 2 Cu バリア膜 2 3 、第 2 Cu 配線部 2 2 、及び、第 2 Cu 拡散防止膜 2 4 をこの順で形成する。次いで、上記図 6 で説明した第 1 の実施形態の第 1 半導体部材 1 0 の作製工程と同様にして、第 2 Cu 拡散防止膜 2 4 上に、第 2 層間絶縁膜 2 5 を形成する。

20

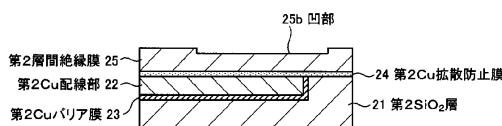

#### 【 0 1 0 7 】

次いで、図 2 7 に示すように、第 2 層間絶縁膜 2 5 上にレジスト膜 1 5 6 を形成する。そして、フォトリソグラフィ技術を用いて、レジスト膜 1 5 6 に対してパターニング処理を施し、第 2 Cu バリア層 6 1 の形成領域のレジスト膜 1 5 6 を除去して開口部 1 5 6 a を形成する。これにより、レジスト膜 1 5 6 の開口部 1 5 6 a に第 2 層間絶縁膜 2 5 が露出する。

30

#### 【 0 1 0 8 】

次いで、レジスト膜 1 5 6 が形成された半導体部材の開口部 1 5 6 a 側の表面に対して、例えば従来既知のマグネットロン方式のエッチング装置を用いて、ドライエッチング処理を行う。これにより、レジスト膜 1 5 6 の開口部 1 5 6 a に露出した第 2 層間絶縁膜 2 5 の領域がエッチングされる。この際、第 2 層間絶縁膜 2 5 を、約 1 0 ~ 5 0 nm 程度、エッチングして除去する。この結果、図 2 8 に示すように、第 2 層間絶縁膜 2 5 の表面には、深さが約 1 0 ~ 5 0 nm 程度の凹部 2 5 b が形成される。

#### 【 0 1 0 9 】

その後、エッチング処理された面に対して、例えば酸素 (O<sub>2</sub>) プラズマを用いたアッシング処理、及び、有機アミン系の薬液を用いた洗浄処理を施す。これにより、第 2 層間絶縁膜 2 5 上に残留したレジスト膜 1 5 6 、及び、上記エッチング処理で発生した残留付着物を除去する。

40

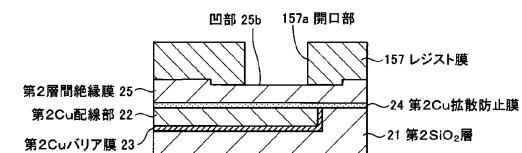

#### 【 0 1 1 0 】

次いで、図 2 9 に示すように、再度、第 2 Cu 拡散防止膜 2 4 上にレジスト膜 1 5 7 を形成する。そして、フォトリソグラフィ技術を用いて、レジスト膜 1 5 7 に対してパターニング処理を施し、第 2 Cu バリア層 6 1 のバリア本体部 6 1 a の形成領域のレジスト膜 1 5 7 を除去して開口部 1 5 7 a を形成する。これにより、レジスト膜 1 5 7 の開口部 1 5 7 a に第 2 層間絶縁膜 2 5 の凹部 2 5 b の底部が露出する。

#### 【 0 1 1 1 】

次いで、レジスト膜 1 5 7 が形成された半導体部材の開口部 1 5 7 a 側の表面に対して

50

、例えば従来既知のマグネットロン方式のエッティング装置を用いて、ドライエッティング処理を行う。これにより、レジスト膜 157 の開口部 157a に露出した第 2 層間絶縁膜 25 の凹部 25b の一部領域がエッティングされる。

【0112】

このエッティング処理では、図 30 に示すように、開口部 157a の領域の第 2 層間絶縁膜 25 及び第 2 Cu 拡散防止膜 24 を除去し、第 2 層間絶縁膜 25 の開口部 25a に第 2 Cu 配線部 22 を露出させる。また、本実施形態では、第 2 層間絶縁膜 25 の開口部 25a の開口径は、例えば、約 1 ~ 95  $\mu\text{m}$  程度とする。なお、このエッティング処理で除去されない第 2 層間絶縁膜 25 の凹部 25b の領域は、第 2 Cu バリア層 61 の界面層部 61b の形成領域となる。

10

【0113】

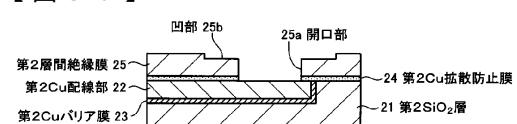

その後、エッティング処理された面に対して、例えば酸素 ( $\text{O}_2$ ) プラズマを用いたアッシング処理、及び、有機アミン系の薬液を用いた洗浄処理を施す。これにより、第 2 層間絶縁膜 25 上に残留したレジスト膜 157、及び、上記エッティング処理で発生した残留付着物を除去する。

【0114】

次いで、図 31 に示すように、第 2 層間絶縁膜 25 上、及び、第 2 層間絶縁膜 25 の開口部 25a に露出した第 2 Cu 配線部 22 上に、Ti、Ta、Ru、又は、それらの窒化物からなる第 2 Cu バリア層 61 を形成する。具体的には、例えば RF スパッタリング法等の手法を用いて、Ar / N<sub>2</sub> 雰囲気中で、厚さが約 5 ~ 50 nm の第 2 Cu バリア層 61 を、第 2 層間絶縁膜 25 上、及び、第 2 Cu 配線部 22 上に形成する。この処理により、第 2 層間絶縁膜 25 の開口部 25a に露出した第 2 Cu 配線部 22 上、及び、第 2 層間絶縁膜 25 の側面上に、バリア本体部 61a が形成される。また、この処理により、第 2 層間絶縁膜 25 の凹部 25b 上に、界面層部 61b が形成される。

20

【0115】

次いで、図 32 に示すように、第 2 Cu バリア層 61 上に、例えばスパッタリング法及び電解メッキ法等の手法を用いて、Cu 膜 158 を形成する。この処理により、第 2 層間絶縁膜 25 の開口部 25a の領域に Cu 膜 158 が埋め込まれる。

【0116】

次いで、Cu 膜 158 が形成された半導体部材を、例えばホットプレートやシンターアニール装置等の加熱装置を用いて、窒素雰囲気中又は真空中で、約 100 ~ 400 °C で 1 ~ 60 分程度加熱する。この加熱処理により、Cu 膜 158 を引き締めて緻密な膜質の Cu 膜 158 を形成する。

30

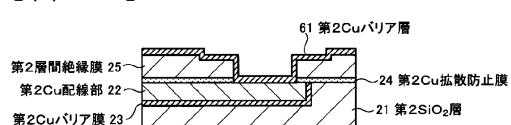

【0117】

そして、図 33 に示すように、Cu 膜 158 及び第 2 Cu バリア層 61 の不要な部分を化学機械研磨 (CMP) 法により除去する。この際、第 2 層間絶縁膜 25 の凹部 25b 上に、界面層部 61b が残るように、CMP 法の処理条件を調整する。具体的には、第 2 層間絶縁膜 25 が表面に露出するまで、Cu 膜 158 側の表面を CMP 法で研磨する。本実施形態では、上述のようにして第 2 半導体部材 60 を作製する。

【0118】

40

その後、上述のようにして作製された第 2 半導体部材 60 (図 33) と、上記第 1 の実施形態と同様にして作製された第 1 半導体部材 10 (図 10) とを、上記第 1 の実施形態と同様にして貼り合わせる。

【0119】

具体的には、まず、第 1 半導体部材 10 の第 1 Cu 接合部 16 側の表面、及び、第 2 半導体部材 60 の第 2 Cu 接合部 26 側の表面に対して還元処理を施し、各 Cu 接合部の表面の酸化膜 (酸化物) を除去して、各 Cu 接合部の表面に清浄な Cu を露出させる。なお、この際、還元処理としては、例えば蟻酸等の薬液を用いたウェットエッティング処理、又は、例えば Ar、NH<sub>3</sub>、H<sub>2</sub> 等のプラズマを用いたドライエッティング処理が用いられる。

50

## 【0120】

次いで、図34に示すように、第1半導体部材10の第1Cu接合部16側の表面と、第2半導体部材60の第2Cu接合部26側の表面とを接触させる(貼り合わせる)。そして、第1半導体部材10と第2半導体部材60とを貼り合わせた状態で、例えばホットプレートやRTA装置等の加熱装置を用いて貼り合わせ部材をアニールして、第1Cu接合部16と第2Cu接合部26とを接合する。具体的には、例えば、大気圧のN<sub>2</sub>雰囲気中、又は、真空中で約100～400℃で5分～2時間程度、貼り合わせ部材を加熱する。

## 【0121】

また、この接合処理により、第1Cu接合部16の接合界面Sj側の面領域のうち第2Cu接合部26と接合しない面領域を含む領域に第2Cuバリア層61の界面層部61bが配置される。より具体的には、図25に示すように、第1Cu接合部16と、第2層間絶縁膜25とが対向する接合界面Sjの領域を含む領域に第2Cuバリア層61の界面層部61bが配置される。

## 【0122】

本実施形態では、上述のようにして、Cu-Cu接合処理を行う。なお、上述した接合工程以外の半導体装置2の製造工程は、従来の例えば固体撮像装置等の半導体装置の製造手法(例えば特開2007-234725号公報参照)と同様にすることができる。

## 【0123】

上述のように、本実施形態においても、上記第1の実施形態と同様に、第1半導体部材10の第1Cu接合部16と、第2半導体部材60の第2層間絶縁膜25とが対向する接合界面Sjの領域には、第2Cuバリア層61の界面層部61bが設けられる。それゆえ、本実施形態においても、第1の実施形態と同様の効果が得られる。

## 【0124】

## &lt;4. 各種変形例及び参考例&gt;

次に、上述した各種実施形態の半導体装置の変形例を説明する。

## 【0125】

## [変形例1]

上記第1の実施形態の半導体装置1(図3)では、第2半導体部材20の第2Cu配線部22上に、第2Cu拡散防止膜24、第2層間絶縁膜25、及び、界面Cuバリア膜28を設ける構成例を説明したが、本開示はこれに限定されない。例えば、第2Cu配線部22上に、界面Cuバリア膜のみを設ける構成にしてもよい。

## 【0126】

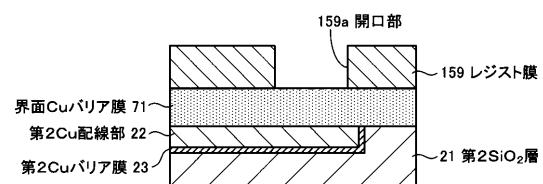

図35に、その一例(変形例1)を示す。図35は、変形例1の半導体装置4の接合界面Sj付近の概略構成断面図である。なお、図35に示すこの例の半導体装置4において、図3に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

## 【0127】

この例の半導体装置4は、図35に示すように、第1半導体部材10と、第2半導体部材70とを備える。なお、この例の半導体装置4における第1半導体部材10の構成は、上記第1の実施形態(図3)のそれと同様の構成であるので、ここでは、第1半導体部材10の説明は省略する。

## 【0128】

第2半導体部材70は、第2半導体基板(不図示)、第2SiO<sub>2</sub>層21、第2Cu配線部22、第2Cuバリア膜23、界面Cuバリア膜71(界面バリア膜、界面バリア部)、第2Cu接合部26、及び、第2Cuバリア層27を有する。なお、この例の第2半導体部材70において、界面Cuバリア膜71以外の構成は、上記第1の実施形態の第2半導体部材20の対応する構成と同様の構成である。

## 【0129】

界面Cuバリア膜71(Cu拡散防止膜)は、第2SiO<sub>2</sub>層21、第2Cu配線部22及び第2Cuバリア膜23上に設けられ、かつ、第2Cuバリア層27の側部を覆うよ

10

20

30

40

50

うに設けられる。それゆえ、この例では、界面Cuバリア膜71は、Cu接合部から層間絶縁膜へのCuの拡散を防止するだけでなく、上記第1の実施形態の第2半導体部材20の第2Cu拡散防止膜24及び第2層間絶縁膜25と同様の役割も兼ねる。

【0130】

なお、界面Cuバリア膜71は、上記第1の実施形態の界面Cuバリア膜28と同様に、例えは、SiN、SiON、SiCN、有機系樹脂等の材料で形成することができる。

【0131】

この例の第2半導体部材70は、例えは、次のようにして作製することができる。まず、上記図5で説明した第1の実施形態の第1半導体部材10の作製工程と同様にして、第2SiO<sub>2</sub>層21上に、第2Cuバリア膜23、及び、第2Cu配線部22をこの順で形成する。次いで、第2SiO<sub>2</sub>層21、第2Cu配線部22及び第2Cuバリア膜23上に、厚さが約5～500nmの界面Cuバリア膜71を形成する。

10

【0132】

次いで、図36に示すように、界面Cuバリア膜71上にレジスト膜159を形成する。その後、フォトリソグラフィ技術を用いて、レジスト膜159に対してパターニング処理を施し、第2Cu接合部26の形成領域のレジスト膜159を除去して開口部159aを形成する。これにより、レジスト膜159の開口部159aに界面Cuバリア膜71が露出する。その後は、上記図13～16で説明した上記第1の実施形態の第2半導体部材20の作製工程と同様にして、この例の第2半導体部材70を作製する。

【0133】

20

この例の構成では、第1Cu接合部16の接合界面Sj側の面領域のうち第2Cu接合部26と接合しない面領域は、界面Cuバリア膜71と接触した状態となる。それゆえ、この例の構成においても、各Cu接合部のCuが外部の酸化膜に拡散することができないので、第1の実施形態と同様の効果が得られる。

【0134】

[変形例2]

上記第2の実施形態では、第1半導体部材30及び第2半導体部材40のいずれにも、Cuシード層を設ける例(図18参照)を説明したが、本開示はこれに限定されない。少なくとも、Cu接合部の接合側の表面面積が大きい方の半導体部材にCuシード層を設ければよい。例えは、図18に示す半導体装置2では、第1半導体部材30の第1Cu接合部16と、第1Cuバリア層17との間のみにCuシード層を設ければよい。

30

【0135】

この場合にも、接合時のアニール処理により、第1半導体部材30のCuシード層中の例えはMn、Mg、Ti、Al等の金属材料が、接合界面Sjを挟んで対向する第2半導体部材40の第2層間絶縁膜25中の酸素と反応する。その結果、この例においても、上記第2の実施形態と同様に、第1半導体部材30の第1Cu接合部16と、第2半導体部材40の第2層間絶縁膜25とが対向する接合界面Sjの領域に界面バリア膜が形成され、第1の実施形態と同様の効果が得られる。

【0136】

40

[変形例3]

上記第3の実施形態では、第2半導体部材60において、第2Cuバリア層61の界面層部61bを第2層間絶縁膜25の接合側表面に埋め込むように形成する例を説明したが、本開示はこれに限定されない。例えは、界面層部61bを、第2層間絶縁膜25の接合側表面上に設ける構成にしてもよい。

【0137】

図37に、その一例(変形例3)を示す。図37は、変形例3の半導体装置5の接合界面Sj付近の概略構成断面図である。また、図37に示すこの例の半導体装置5において、図25に示す第3の実施形態の半導体装置3と同様の構成には、同じ符号を付して示す。

【0138】

50

この例の半導体装置 5 は、図 3 7 に示すように、第 1 半導体部材 1 0 と、第 2 半導体部材 8 0 とを備える。なお、この例の半導体装置 5 における第 1 半導体部材 1 0 の構成は、上記第 3 の実施形態（図 2 5）のそれと同様の構成であるので、ここでは、第 1 半導体部材 1 0 の説明は省略する。

【 0 1 3 9 】

第 2 半導体部材 8 0 は、第 2 半導体基板（不図示）、第 2 SiO<sub>2</sub> 層 2 1、第 2 Cu 配線部 2 2、第 2 Cu バリア膜 2 3、第 2 Cu 拡散防止膜 2 4、第 2 層間絶縁膜 8 1、第 2 Cu 接合部 2 6、第 2 Cu バリア層 6 1、及び、界面 Cu バリア膜 8 2 を有する。

【 0 1 4 0 】

なお、この例の第 2 半導体部材 8 0 において、第 2 半導体基板（不図示）、第 2 SiO<sub>2</sub> 層 2 1、第 2 Cu 配線部 2 2、第 2 Cu バリア膜 2 3、及び、第 2 Cu 拡散防止膜 2 4 の構成は、上記第 3 の実施形態の第 2 半導体部材 6 0 の対応する構成と同様の構成である。また、この例の第 2 Cu 接合部 2 6、及び、第 2 Cu バリア層 6 1 の構成は、上記第 3 の実施形態の第 2 半導体部材 6 0 の対応する構成と同様の構成である。

【 0 1 4 1 】

この例では、第 2 Cu バリア層 6 1 の界面層部 6 1 b は、第 2 層間絶縁膜 8 1 の接合側表面上に設けられる。それゆえ、第 2 層間絶縁膜 8 1 の表面には、上記第 3 の実施形態のように凹部 2 5 b は形成されない。

【 0 1 4 2 】

さらに、この例では、界面 Cu バリア膜 8 2 が、第 2 層間絶縁膜 8 1 の表面上に形成され、かつ、第 2 Cu バリア層 6 1 の界面層部 6 1 b の側部（側面）を覆うように設けられる。また、この際、界面 Cu バリア膜 8 2 の膜厚と界面層部 6 1 b の膜厚とを略同じにして、界面 Cu バリア膜 8 2 の接合界面 S j 側の表面と、界面層部 6 1 b の接合界面 S j 側の表面とが略面一となるようにする。なお、界面 Cu バリア膜 8 2 は、上記第 1 の実施形態の界面 Cu バリア膜 2 8 と同様に、例えば、SiN、SiON、SiCN、有機系樹脂等の材料で形成することができる。

【 0 1 4 3 】

この例では、接合界面 S j において、第 1 Cu 接合部 1 6 と第 2 Cu 接合部 2 6 との接合領域以外の領域では、第 1 Cu 接合部 1 6 は、第 2 Cu バリア層 6 1 の界面層部 6 1 b 及び / 又は界面 Cu バリア膜 8 2 と接触した状態となる。それゆえ、この例の構成においても、各 Cu 接合部の Cu が層間絶縁膜に拡散することを防止することができるので、第 1 の実施形態と同様の効果が得られる。

【 0 1 4 4 】

なお、この例では、界面 Cu バリア膜 8 2 を設けない構成にしてもよい。この場合、第 2 Cu バリア層 6 1 の界面層部 6 1 b の側部の周囲には空隙が形成されるが、この空隙により、各 Cu 接合部の Cu が層間絶縁膜に拡散することを防止することができるので、第 1 の実施形態と同様の効果が得られる。ただし、接合界面 S j の接合強度の観点では、図 3 7 に示すように、界面層部 6 1 b の側部を覆うように界面 Cu バリア膜 8 2 を設けることが好ましい。

【 0 1 4 5 】

【 变形例 4 】

上記各種実施形態及び各種変形例では、各接合部の電極膜を Cu 膜で構成する例を説明したが、本開示はこれに限定されない。接合部を、例えば、Al、W、Ti、TiN、Ta、TaN、Ru 等で形成された金属膜、又は、これらの積層膜で構成していてもよい。

【 0 1 4 6 】

例えば、上記第 1 の実施形態において、接合部の電極材料として Al（アルミニウム）を用いることができる。この場合には、界面 Cu バリア膜 2 8 を、上記第 1 の実施形態と同様に、例えば、SiN、SiON、SiCN、樹脂等の材料で形成することができる。また、この場合、Al 接合部を被覆するメタルバリア層は、Al 接合部側から Ti 膜及び TiN 膜をこの順で積層した多層膜（Ti / TiN 積層膜）で構成することが好ましい。

10

20

30

40

50

## 【0147】

また、例えば、上記第2の実施形態の構成においても、接合部の電極材料としてA1を用いることができる。ただし、この場合には、A1は酸素と反応しやすい材料であるので、界面バリア膜を生成するためのシード層(Cuシード層)を設ける必要がない。

## 【0148】

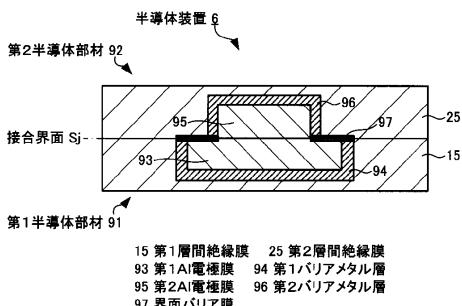

ここで、図38に、上記第2の実施形態の構成において、接合部をA1で形成した場合の半導体装置の接合界面Sj付近の概略構成断面を示す。なお、図38では、説明を簡略化するため、A1接合部付近の構成のみを示し、配線部の構成は省略する。また、図38に示す半導体装置6において、図18に示す第2の実施形態の半導体装置2と同様の構成には、同じ符号を付して示す。

10

## 【0149】

この例の半導体装置6は、図38に示すように、第1半導体部材91と、第2半導体部材92と、界面バリア膜97とを備える。第1半導体部材91は、第1層間絶縁膜15と、その接合側表面に埋め込むようにして形成された第1A1接合部93と、第1層間絶縁膜15及び第1A1接合部93間に設けられた第1バリアメタル層94とを有する。また、第2半導体部材92は、第2層間絶縁膜25と、その接合側表面に埋め込むようにして形成された第2A1接合部95と、第2層間絶縁膜25及び第2A1接合部95間に設けられた第2バリアメタル層96とを有する。

## 【0150】

そして、図38に示す例においても、第1半導体部材91と第2半導体部材92との接合時に行うアニール処理により、第1A1接合部93内のA1の一部が、接合界面Sjを挟んで対向する第2半導体部材92の第2層間絶縁膜25中の酸素と反応する。その結果、第1A1接合部93と、第2層間絶縁膜25とが対向する接合界面Sjの領域には、界面バリア膜97が形成される。それゆえ、この構成例においても、第1の実施形態と同様に、第1半導体部材91及び第2半導体部材92間の接合強度を増大させることができ、より信頼性の高い接合界面を有する半導体装置6を得ることができる。

20

## 【0151】

さらに、例えば、上記第1の実施形態において、接合部の電極材料として例えばW(タンゲステン)を用いることができる。この場合には、界面Cuバリア膜28を、上記第1の実施形態と同様に、例えば、SiN、SiON、SiCN、樹脂等の材料で形成することができる。また、この場合、W接合部を被覆するメタルバリア層は、W接合部側からTi膜及びTiN膜をこの順で積層した多層膜(Ti/TiN積層膜)で構成することが好ましい。なお、Wは酸素と反応し難い(界面バリア膜を自己生成し難い)金属材料であるので、上記第2の実施形態の構成の接合部にWを用いることは難しい。

30

## 【0152】

## [変形例5]

上記各種実施形態及び各種変形例では、信号が供給される金属膜同士を、接合界面Sjで接合する例を説明したが、本開示はこれに限定されない。信号が供給されない金属膜同士を接合界面Sjで接合する場合も、上記各種実施形態及び各種変形例で説明したCu-Cu接合技術を適用することができる。

40

## 【0153】

例えば、ダミー電極同士を接合する場合にも、上記各種実施形態及び各種変形例で説明したCu-Cu接合技術を適用することができる。また、例えば、固体撮像素子において、センサ部とロジック回路部との間で金属膜同士を接合して、遮光膜を形成する場合にも、上記各種実施形態及び各種変形例で説明したCu-Cu接合技術を適用することができる。

## 【0154】

## [参考例1]

上記第2の実施形態では、第1Cu接合部16の接合界面Sj側表面の寸法(表面面積)と、第2Cu接合部26のそれとが異なる例を説明した。しかしながら、上記第2の実

50

施形態で説明した Cu - Cu 接合技術は、第 1 Cu 接合部の接合界面 Sj 側の表面形状及び寸法と、第 2 Cu 接合部のそれらとが同じである半導体装置にも適用可能である。

#### 【0155】

図 39 に、その一例（参考例 1）を示す。なお、図 39 は、この例の半導体装置 100 の接合界面 Sj 付近の概略構成断面図である。また、図 39 に示すこの例の半導体装置 100 において、図 18 に示す第 2 の実施形態の半導体装置 2 と同様の構成には、同じ符号を付して示す。

#### 【0156】

この例の半導体装置 100 は、図 39 に示すように、第 1 半導体部材 101 と、第 2 半導体部材 40 と、界面 Cu バリア膜 105 を備える。なお、この例の半導体装置 100 における第 2 半導体部材 40 の構成は、上記第 2 の実施形態（図 18）のそれと同様の構成であるので、ここでは、第 2 半導体部材 40 の説明は省略する。

10

#### 【0157】

第 1 半導体部材 101 は、第 1 半導体基板（不図示）、第 1 SiO<sub>2</sub> 層 11、第 1 Cu 配線部 12、第 1 Cu バリア膜 13、第 1 Cu 拡散防止膜 14、第 1 層間絶縁膜 15、第 1 Cu 接合部 102、第 1 Cu バリア層 103、及び、第 1 Cu シード層 104 を有する。

#### 【0158】

なお、この例では、第 1 Cu 接合部 102 の接合界面 Sj 側の表面形状及び寸法を、第 2 Cu 接合部 26 のそれらと同じにする。それ以外の第 1 半導体部材 101 の構成は、上記第 2 の実施形態の第 1 半導体部材 30 の対応する構成と同様の構成である。

20

#### 【0159】

そして、この例においても、上記第 2 の実施形態と同様に、第 1 半導体部材 101 の第 1 Cu 接合部 102 側の表面と、第 2 半導体部材 40 の第 2 Cu 接合部 26 側の表面とを接合することにより、半導体装置 100 が作製される。この際、両 Cu 接合部間に、接合アライメントずれが発生すると、接合時のアニール処理により、各 Cu シード層中の例えば Mn、Mg、Ti、Al 等の金属材料が接合界面 Sj を挟んで対向する層間絶縁膜の酸素と選択的に反応する。この結果、図 39 に示すように、第 1 Cu 接合部 102 と第 2 層間絶縁膜 25 とが対向する接合界面 Sj の領域、及び、第 2 Cu 接合部 26 と第 1 層間絶縁膜 15 とが対向する接合界面 Sj の領域にそれぞれ、界面 Cu バリア膜 105 が形成される。

30

#### 【0160】

上述のように、この例の半導体装置 100 においても、一方の半導体部材の Cu 接合部と、他方の半導体部材の層間絶縁膜とが対向する接合界面 Sj の領域には、界面 Cu バリア膜 105 が設けられる。それゆえ、この例においても、第 2 の実施形態と同様の効果が得られる。

#### 【0161】

#### [参考例 2]

上記参考例 1 では、第 1 Cu 接合部の接合界面 Sj 側の表面形状及び寸法と、第 2 Cu 接合部のそれらとが同じである半導体装置に、上記第 2 の実施形態で説明した Cu - Cu 接合技術を適用する例を説明した。ここでは、参考例 1 の半導体装置 100 にさらに、上記第 1 の実施形態で説明した Cu - Cu 接合技術を組み合わせた構成例を説明する。

40

#### 【0162】

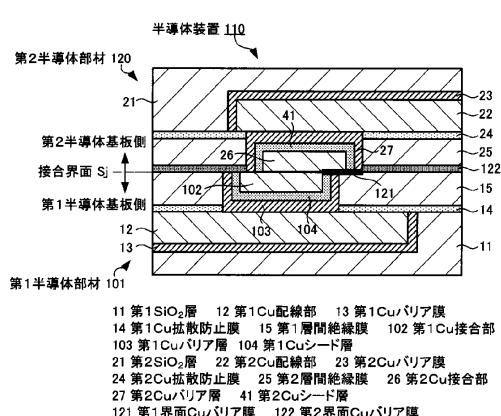

図 40 に、その一例（参考例 2）を示す。なお、図 40 は、この例の半導体装置 110 の接合界面 Sj 付近の概略構成断面図である。また、図 40 に示すこの例の半導体装置 110 において、図 39 に示す参考例 1 の半導体装置 100 と同様の構成には、同じ符号を付して示す。

#### 【0163】

この例の半導体装置 110 は、図 40 に示すように、第 1 半導体部材 101 と、第 2 半導体部材 120 と、第 1 界面 Cu バリア膜 121 を備える。なお、この例の半導体装置

50

110における第1半導体部材101の構成は、上記参考例1(図39)のそれと同様の構成であるので、ここでは、第1半導体部材101の説明は省略する。

【0164】

第2半導体部材120は、第2半導体基板(不図示)、第2SiO<sub>2</sub>層21、第2Cu配線部22、第2Cuバリア膜23、第2Cu拡散防止膜24、第2層間絶縁膜25、第2Cu接合部26、第2Cuバリア層27、及び、第2Cuシード層41を有する。さらに、第2半導体部材120は、第2界面Cuバリア膜122を有する。

【0165】

図40と図39との比較から明らかなように、この例の第2半導体部材120は、上記参考例1の第2半導体部材40において、第2層間絶縁膜25上に第2界面Cuバリア膜122を設けた構成である。また、この例では、第2Cu接合部26の接合界面Sj側の表面と、第2界面Cuバリア膜122の表面とが略面一となるように、第2界面Cuバリア膜122を形成する。なお、第2界面Cuバリア膜122以外の第2半導体部材120の構成は、上記参考例1の第2半導体部材40の対応する構成と同様である。

【0166】

また、第2界面Cuバリア膜122は、上記第1の実施形態の界面Cuバリア膜28と同様に、例えば、SiN、SiON、SiCN、有機系樹脂等の材料で形成することができる。ただし、Cu膜との密着性という観点では、特に、第2界面Cuバリア膜122をSiNで形成することが好ましい。

【0167】

そして、この例においても、上記第2の実施形態と同様に、第1半導体部材101の第1Cu接合部102側の表面と、第2半導体部材120の第2Cu接合部26側の表面とを接合することにより、半導体装置110が作製される。この際、両Cu接合部間に、接合アライメントずれが発生すると、接合時のアニール処理により、各Cuシード層中の例えばMn、Mg、Ti、Al等の金属材料が接合界面Sjを挟んで対向する層間絶縁膜の酸素と選択的に反応する。この結果、一方の半導体部材のCu接合部と、他方の半導体部材の層間絶縁膜とが対向する接合界面Sj領域に、第1界面Cuバリア膜121が形成される。

【0168】

ただし、この例では、上述のように、第2半導体部材120の接合界面Sjの表面に第2界面Cuバリア膜122を設ける。それゆえ、この例では、第1Cu接合部102と第2層間絶縁膜25とが対向する接合界面Sjの領域、及び、第2Cu接合部26と第1層間絶縁膜15とが対向する接合界面Sjの領域の一方に、第1界面Cuバリア膜121が形成される。また、第1Cu接合部102と第2層間絶縁膜25とが対向する接合界面Sjの領域、及び、第2Cu接合部26と第1層間絶縁膜15とが対向する接合界面Sjの領域の他方に、第2界面Cuバリア膜122が配置される。図40に示す例では、前者の接合界面Sjの領域に、第2界面Cuバリア膜122が設けられ、後者の接合界面Sjの領域に、第1界面Cuバリア膜121が設けられる。

【0169】

上述のように、この例の半導体装置110においても、一方の半導体部材のCu接合部と、他方の半導体部材の層間絶縁膜とが対向する接合界面Sjの領域には、第1界面Cuバリア膜121又は第2界面Cuバリア膜122が設けられる。それゆえ、この例においても、第1及び第2の実施形態と同様の効果が得られる。

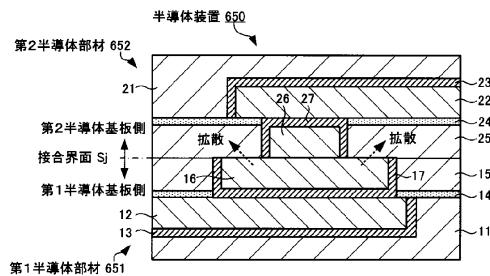

【0170】

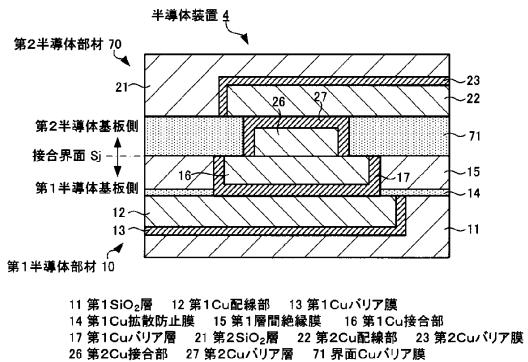

<5.第4の実施形態>

通常、Cu接合部の面積が互いに異なる第1半導体部材及び第2半導体部材を貼り合わせてCu-Cu接合を行う場合、一方の半導体部材のCu接合部と、他方の半導体部材の層間絶縁膜とが接触する。図41に、その接合例における接合界面付近の概略断面図を示す。なお、図41に示す半導体装置650において、図3に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

10

20

30

40

50

## 【0171】

この場合、図41に示すように、第2Cu接合部26より面積の大きな第1Cu接合部16から第2層間絶縁膜25にCuが拡散して(図41中の点線矢印)、接合界面Sjにおける電気特性が劣化し、Cu接合部及び半導体装置650の信頼性が損なわれる。それに対して、上記各種実施形態では、第1Cu接合部16と第2層間絶縁膜25との接合界面に界面バリア膜を形成して、第1Cu接合部16から第2層間絶縁膜25へのCuの拡散を防止することができ、上記問題を解消することができる。

## 【0172】

また、上述した接合界面におけるCuの拡散を防止する別の手法としては、第1半導体部材及び第2半導体部材の少なくとも一方の接合界面側の層間絶縁膜の表面をCu接合部の接合側表面より後退させた状態で、両者を貼り合わせる手法も考えられる。すなわち、第1半導体部材及び第2半導体部材の少なくとも一方のCu接合部を接合界面側に突出させた状態で、両者を貼り合わせる手法も考えられる。

10

## 【0173】

図42に、第1半導体部材及び第2半導体部材の両方のCu接合部を接合界面側に突出させた状態で両者を貼り合わせた場合の、接合界面付近の概略断面図を示す。なお、図42に示す半導体装置660において、図3に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

## 【0174】

この場合には、第1半導体部材661及び第2半導体部材662の接合界面Sj(第1層間絶縁膜663と第2層間絶縁膜664との間)に隙間ができる。これにより、第2層間絶縁膜664と第1Cu接合部16との間には空隙が形成され、第1Cu接合部16から第2層間絶縁膜664へのCuの拡散が防止される。しかしながら、この場合には、図42に示すように、接合界面Sjの隙間に外気(白抜き矢印)が浸入して第1Cu接合部16の表面を汚染し、これにより、接合界面Sjにおける電気特性が劣化し、Cu接合部及び半導体装置の信頼性が損なわれる。

20

## 【0175】

そこで、第4の実施形態では、第2層間絶縁膜と第1Cu接合部との間に空隙を形成した構成を有する半導体装置において、上述した外気の影響を防止できる構成例を説明する。

30

## 【0176】

## [半導体装置の構成]

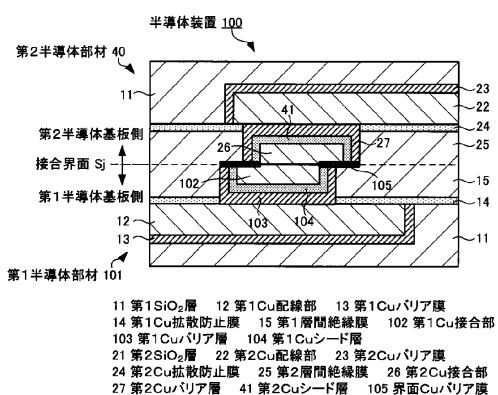

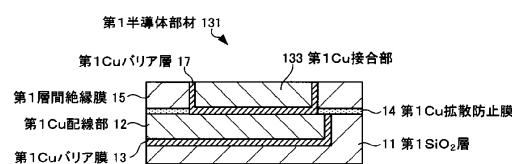

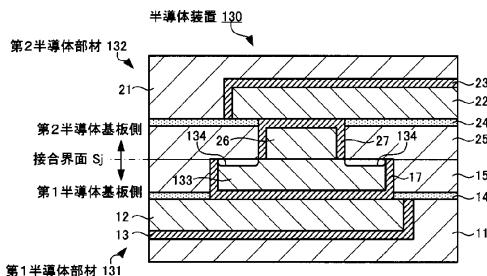

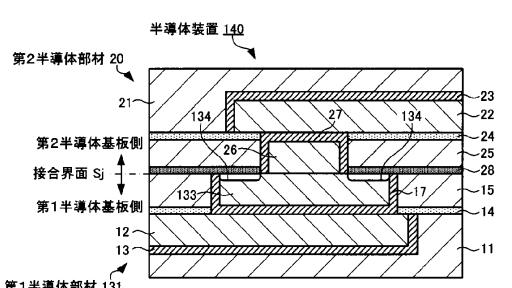

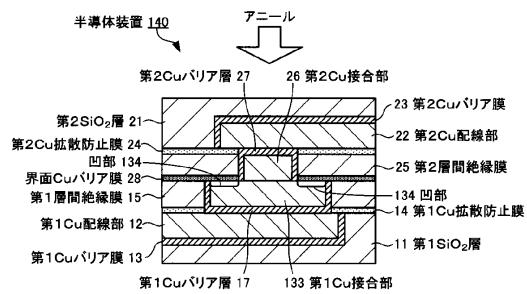

図43及び44に、第4の実施形態に係る半導体装置の概略構成を示す。図43は、第4の実施形態に係る半導体装置の接合界面付近の概略断面図であり、図44は、各Cu接合部と接合界面に画成される空隙との配置関係を示す接合界面付近の概略上面図である。なお、図43及び44では、説明を簡略化するため、1つの接合界面付近の構成のみを示す。また、図43に示す本実施形態の半導体装置130において、図3に示す第1の実施形態の半導体装置1と同様の構成には、同じ符号を付して示す。

## 【0177】

半導体装置130は、図43に示すように、第1半導体部材131(第1半導体部)と、第2半導体部材132(第2半導体部)とを備える。

40

## 【0178】

第1半導体部材131は、第1半導体基板(不図示)、第1SiO<sub>2</sub>層11、第1Cu配線部12、第1Cuバリア膜13、第1Cu拡散防止膜14、第1層間絶縁膜15、第1Cu接合部133、及び、第1Cuバリア層17を有する。

## 【0179】

図43と図3との比較から明らかなように、本実施形態の第1半導体部材131は、第1の実施形態の第1半導体部材10の接合界面Sj側の表面領域において、第2層間絶縁膜25と対向する第1Cu接合部16の表面領域に凹部を設けた構成となる。それ以外の第1半導体部材131の構成は、上記第1の実施形態の第1半導体部材10の対応する構

50

成と同様である。

【0180】

第2半導体部材132は、第2半導体基板(不図示)、第2SiO<sub>2</sub>層21、第2Cu配線部22、第2Cuバリア膜23、第2Cu拡散防止膜24、第2層間絶縁膜25、及び、第2Cu接合部26を有する。

【0181】

図43と図3との比較から明らかなように、本実施形態の第2半導体部材132は、第1の実施形態の第2半導体部材20において、界面Cuバリア膜28を省略した構成となる。それ以外の第2半導体部材132の構成は、上記第1の実施形態の第2半導体部材20の対応する構成と同様である。

10

【0182】

本実施形態の半導体装置130では、図43に示すように、第1半導体部材131の接合界面Sj側の表面領域において、第2半導体部材132の第2層間絶縁膜25と対向する第1Cu接合部133の表面領域に凹部134を設ける。これにより、第1半導体部材131の第1Cu接合部133と、第2半導体部材132の第2層間絶縁膜25とが対向する接合界面Sjの領域に空隙が形成され、第1Cu接合部133が、第2層間絶縁膜25と直接接触しない構造を形成することができる。

【0183】

すなわち、本実施形態の半導体装置130では、第1Cu接合部133の凹部134と、凹部134と対向する第2半導体部材132の接合界面Sj側の表面領域部(面領域部)とにより界面バリア部が構成される。また、本実施形態では、図43に示すように、第1Cu接合部133の凹部134と第2層間絶縁膜25の接合界面Sj側の表面とにより画成された空隙が、その周辺の各種膜により密封された状態になる。

20

【0184】

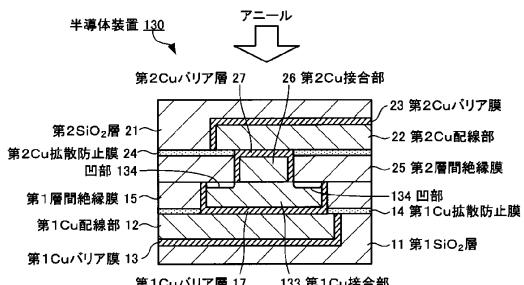

[半導体装置の製造手法]

次に、本実施形態の半導体装置130の製造手法を、図45～48を参照しながら説明する。なお、図45及び46には、各工程で作製される半導体部材のCu接合部付近の概略断面を示し、図47及び48には、第1半導体部材131と第2半導体部材132との接合処理の様子を示す。

30

【0185】

まず、本実施形態では、図5～10で説明した第1の実施形態の第1半導体部材10の作製工程と同様にして、第1半導体部材131を作製する(図45の状態)。

【0186】

また、本実施形態では、図5～10で説明した第1の実施形態の第1半導体部材10の作製工程と同様にして、第2半導体部材132を作製する(図46の状態)。ただし、この際、第2層間絶縁膜25に、第2Cu接合部26及び第2Cuバリア層27の形成領域に対応する開口部を形成する工程(図7の工程に対応)では、開口部の開口径を約1～95μm程度とする。

【0187】

次いで、第1半導体部材131の第1Cu接合部133側の表面、及び、第2半導体部材132の第2Cu接合部26側の表面に対して還元処理を施し、各Cu接合部の表面の酸化膜(酸化物)を除去して、各Cu接合部の表面に清浄なCuを露出させる。なお、この際、還元処理としては、例えば蟻酸等の薬液を用いたウェットエッティング処理、又は、例えばAr、NH<sub>3</sub>、H<sub>2</sub>等のプラズマを用いたドライエッティング処理が用いられる。

40

【0188】

次いで、図47に示すように、第1半導体部材131の第1Cu接合部133側の表面と、第2半導体部材132の第2Cu接合部26側の表面とを接触させる(貼り合わせる)。

【0189】

そして、第1半導体部材131と第2半導体部材132とを貼り合わせた状態で、例え

50

ばホットプレートやR T A装置等の加熱装置(アニール装置)を用いて貼り合わせ部材をアニールして、第1Cu接合部133と第2Cu接合部26とを接合する(図48の状態)。具体的には、例えば、大気圧のN<sub>2</sub>雰囲気中、又は、真空中で約100~400で5分~2時間程度、貼り合わせ部材を加熱する。

【0190】

本実施形態では、図48に示すアニール処理により、第1Cu接合部133のCu膜をさらに引き締める。なお、接合界面Sjにおいて、第1Cu接合部133と第2層間絶縁膜25との接触領域は、他の領域に比べて密着力の弱い領域である。それゆえ、図48に示すアニール処理により、この接触領域では、第1Cu接合部133が収縮して、第1Cu接合部133の表面が接合界面Sjから遠ざかる方向に後退する。この結果、図48に示すように、第1半導体部材131の接合界面Sj側の表面領域において、第2層間絶縁膜25と対向する第1Cu接合部133の表面領域に凹部134が形成される。

10

【0191】

すなわち、図48に示すアニール処理により、第1Cu接合部133及び第2層間絶縁膜25間の接合界面Sjに空隙が形成されるとともに、該空隙が、その周辺の各種膜により、半導体装置130内に密封された構造が形成される。なお、図48に示すアニール処理において、凹部134を形成するためには、例えば、各半導体部材の作製時に緻密な膜質のCu接合部を形成するために行ったアニール処理のアニール温度より高い温度でアニールすることが好みしい。

20

【0192】

本実施形態では、上述のようにして、Cu-Cu接合処理を行う。なお、上述した接合工程以外の半導体装置130の製造工程は、従来の例えば固体撮像装置等の半導体装置の製造手法(例えば特開2007-234725号公報参照)と同様ににすることができる。

【0193】

上述のように、本実施形態の半導体装置130では、第1Cu接合部133及び第2層間絶縁膜25間の接合界面Sjに空隙を形成し、両者が直接接触しない構造を形成する。それゆえ、本実施形態においても、第1の実施形態と同様に、第1Cu接合部133から第2層間絶縁膜25へのCuの拡散を防止することができる。なお、接合界面Sjに形成される空隙の領域は接合界面Sjの全領域に比べて十分小さいので、本実施形態の構成における接合界面Sjの密着性能は、上記各種実施形態のそれと同程度になる。

30

【0194】

また、本実施形態の半導体装置130では、第1Cu接合部133及び第2層間絶縁膜25間の接合界面Sjに形成された空隙が、その周辺の各種膜により密封された状態となる。それゆえ、本実施形態では、Cu接合部への外気の浸入を防止することができ、半導体装置130の信頼性を確保することができる。

【0195】

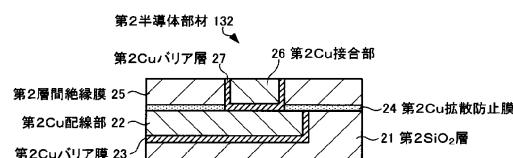

<6.第5の実施形態>

第5の実施形態では、第1半導体部材の第1Cu接合部と、第2半導体部材の第2層間絶縁膜との間の接合界面に空隙を設けた半導体装置の別の構成例を説明する。

【0196】

40

[半導体装置の構成]

図49及び50に、第5の実施形態に係る半導体装置の概略構成を示す。図49は、第5の実施形態に係る半導体装置の接合界面付近の概略断面図であり、図50は、各Cu接合部及び界面Cuバリア膜と接合界面に画成される空隙との間の配置関係を示す接合界面付近の概略上面図である。なお、図49及び50では、説明を簡略化するため、1つの接合界面付近の構成のみを示す。また、図49に示す本実施形態の半導体装置140において、図43に示す第4の実施形態の半導体装置130と同様の構成には、同じ符号を付して示す。

【0197】

半導体装置140は、図49に示すように、第1半導体部材131(第1半導体部)と

50

、第2半導体部材20(第2半導体部)とを備える。

【0198】

第1半導体部材131の構成は、第4の実施形態(図43)のそれと同様の構成である。すなわち、第1半導体部材131の構成は、第1の実施形態(図3)の第1半導体部材10の接合界面Sj側の表面領域において、第2半導体部材20の第2層間絶縁膜25と対向する第1Cu接合部133の表面領域に凹部134を設けた構成となる。一方、第2半導体部材20の構成は、第1の実施形態(図3)のそれと同様の構成であり、第2層間絶縁膜25の接合界面Sj側の表面に、界面Cuバリア膜28が設けられた構成となる。

【0199】

本実施形態の半導体装置140では、上述のように、第1半導体部材131の接合界面Sj側の表面領域において、第2半導体部材20の界面Cuバリア膜28と対向する第1Cu接合部133の表面領域に凹部134を設ける。これにより、第1半導体部材131の第1Cu接合部133と、第2半導体部材20の界面Cuバリア膜28とが対向する接合界面Sjに空隙が形成される。また、本実施形態では、図49に示すように、第1Cu接合部133の凹部134と界面Cuバリア膜28の接合界面Sj側の表面とにより画成された空隙が、その周辺の各種膜により密封された状態になる。

10

【0200】

すなわち、本実施形態においても、第1Cu接合部133の凹部134と、凹部134と対向する第2半導体部材20の接合界面Sj側の表面領域部(面領域部)とにより界面バリア部が構成される。そして、本実施形態では、この界面バリア部に画成される空隙、及び、界面Cuバリア膜28により、第1Cu接合部133から第2層間絶縁膜25へのCuの拡散が防止される。

20

【0201】

[半導体装置の製造手法]

次に、本実施形態の半導体装置140の製造手法を、図51～54を参照しながら説明する。なお、図51及び52には、各工程で作製される半導体部材のCu接合部付近の概略断面を示し、図53及び54には、第1半導体部材131と第2半導体部材20との接合処理の様子を示す。

【0202】

まず、本実施形態では、図5～10で説明した第1の実施形態の第1半導体部材10の作製工程と同様にして、第1半導体部材131を作製する(図51の状態)。

30

【0203】

また、本実施形態では、図11～16で説明した第1の実施形態の第2半導体部材20の作製工程と同様にして、第2半導体部材20を作製する(図52の状態)。ただし、本実施形態では、界面Cuバリア膜28(例えばSiN膜、SiCN膜等)の膜厚は、約10～100nmとし、CVD法又はスピンドル法により界面Cuバリア膜28を形成する。また、本実施形態において、第2層間絶縁膜25に、第2Cu接合部26及び第2Cuバリア層27の形成領域に対応する開口部を形成する工程(図13の工程)では、開口部の開口径を約4～100μm程度とする。

40

【0204】

次いで、第1半導体部材131の第1Cu接合部133側の表面、及び、第2半導体部材20の第2Cu接合部26側の表面に対して還元処理を施し、各Cu接合部の表面の酸化膜(酸化物)を除去して、各Cu接合部の表面に清浄なCuを露出させる。なお、この際、還元処理としては、例えば蟻酸等の薬液を用いたウェットエッチング処理、又は、例えばAr、NH<sub>3</sub>、H<sub>2</sub>等のプラズマを用いたドライエッチング処理が用いられる。

【0205】

次いで、図53に示すように、第1半導体部材131の第1Cu接合部133側の表面と、第2半導体部材20の第2Cu接合部26側の表面とを接触させる(貼り合わせる)。

【0206】

50

そして、第1半導体部材131と第2半導体部材20とを貼り合わせた状態で、例えばホットプレートやRTA装置等の加熱装置（アニール装置）を用いて貼り合わせ部材をアニールして、第1Cu接合部133と第2Cu接合部26とを接合する（図54の状態）。具体的には、例えば、大気圧のN<sub>2</sub>雰囲気中、又は、真空中で約100～400で5分～2時間程度、貼り合わせ部材を加熱する。

#### 【0207】

本実施形態においても、図54に示すアニール処理により、上記第4の実施形態と同様に、第1Cu接合部133のCu膜をさらに引き締める。この際、接合界面Sjにおいて、第1Cu接合部133と界面Cuバリア膜28との接触領域では、該領域の第1Cu接合部133が収縮し、第1Cu接合部133の表面が接合界面Sjから遠ざかる方向に後退する。この結果、図54に示すように、第1半導体部材131の接合界面Sj側の表面領域において、界面Cuバリア膜28と対向する第1Cu接合部133の表面領域に凹部134が形成される。10

#### 【0208】

すなわち、図54に示すアニール処理により、第1Cu接合部133及び界面Cuバリア膜28間の接合界面Sjに空隙が形成されるとともに、該空隙が、その周辺の各種膜により、半導体装置140内に密封された構造が形成される。なお、図54に示すアニール処理において、凹部134を形成するためには、例えば、各半導体部材の作製時に緻密な膜質のCu接合部を形成するために行ったアニール処理のアニール温度より高い温度でアニールすることが好ましい。20

#### 【0209】

本実施形態では、上述のようにして、Cu-Cu接合処理を行う。なお、上述した接合工程以外の半導体装置140の製造工程は、従来の例えば固体撮像装置等の半導体装置の製造手法（例えば特開2007-234725号公報参照）と同様ににすることができる。

#### 【0210】

上述のように、本実施形態の半導体装置140では、第1Cu接合部133及び界面Cuバリア膜28間の接合界面Sjの領域に空隙を形成し、両者が直接接触しない構造を形成する。また、本実施形態では、第1Cu接合部133の凹部134と対向する領域に界面Cuバリア膜28が形成される。それゆえ、本実施形態では、第1Cu接合部133から第2層間絶縁膜25へのCuの拡散をより確実に防止することができる。30

#### 【0211】

また、本実施形態の半導体装置140では、第1Cu接合部133及び界面Cuバリア膜28間の接合界面Sjに形成された空隙が、その周辺の各種膜により密封された状態となる。それゆえ、本実施形態では、上記第4の実施形態と同様に、Cu接合部への外気の浸入を防止することができ、半導体装置140の信頼性を確保することができる。

#### 【0212】

なお、本実施形態では、第1の実施形態の半導体装置1（図3）に、上記第4の実施形態で説明した界面バリア部の形成技術を適用した例を説明したが、本開示はこれに限定されない。例えば、第2の実施形態の半導体装置2（図18）や第3の実施形態の半導体装置3（図25）に、上記第4の実施形態で説明した界面バリア部の形成技術を適用してもよい。さらに、例えば、上記各種変形例の半導体装置（図35～38等）に、上記第4の実施形態で説明した、界面バリア部の形成技術を適用してもよい。40

#### 【0213】

また、上記第4の実施形態で説明した界面バリア部の形成技術は上記各種参考例の半導体装置（図39及び49）にも適用可能である。ただし、この場合には、接合界面Sjにおいて、第2層間絶縁膜と対向する、第1Cu接合部の表面領域だけでなく、第1層間絶縁膜と対向する、第2Cu接合部の表面領域にも凹部が形成される。

#### 【0214】

##### <7. 各種応用例>

上記各種実施形態及び各種変形例で説明した半導体装置、及び、その製造手法（Cu-50

Cu接合手法)は、製造時に2枚の基板を貼り合わせてCu-Cu接合処理を必要とする各種電子機器に適用可能である。特に、上述した各種実施形態及び上記各種変形例のCu-Cu接合手法は、例えば、固体撮像装置の製造に好適である。

【0215】

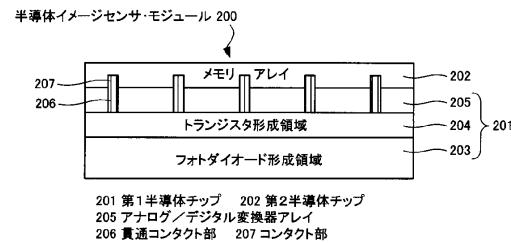

[応用例1]

図55に、上記各種実施形態及び各種変形例で説明した半導体装置、及び、その製造手法が適用可能な半導体イメージセンサ・モジュールの構成例を示す。図55に示す半導体イメージセンサ・モジュール200は、第1半導体チップ201と、第2半導体チップ202とを接合して構成される。

【0216】

第1半導体チップ201は、フォトダイオード形成領域203と、トランジスタ形成領域204と、アナログ/デジタル変換器アレイ205とを内蔵する。そして、フォトダイオード形成領域203上に、トランジスタ形成領域204、及び、アナログ/デジタル変換器アレイ205はこの順で積層される。

10

【0217】

また、アナログ/デジタル変換器アレイ205には、貫通コンタクト部206が形成される。貫通コンタクト部206は、その一方の端部が、アナログ/デジタル変換器アレイ205の第2半導体チップ202側の表面に露出するように形成される。

【0218】

一方、第2半導体チップ202は、メモリアレイで構成され、その内部には、コンタクト部207が形成される。コンタクト部207は、その一方の端部が、第2半導体チップ202の第1半導体チップ201側の表面に露出するように形成される。

20

【0219】

そして、貫通コンタクト部206とコンタクト部207とを突き合わせた状態で、加熱圧着することにより、第1半導体チップ201と第2半導体チップ202とが接合され、半導体イメージセンサ・モジュール200が作製される。このような構成の半導体イメージセンサ・モジュール200では、単位面積当たりの画素数を増やすことができるとともに、その厚さを薄くすることができる。

【0220】

この例の半導体イメージセンサ・モジュール200では、例えば第1半導体チップ201と第2半導体チップ202との接合工程において、上記各種実施形態及び各種変形例のCu-Cu接合手法を適用することができる。この場合には、第1半導体チップ201及び第2半導体チップ202間の接合界面の信頼性をより向上させることができる。

30

【0221】

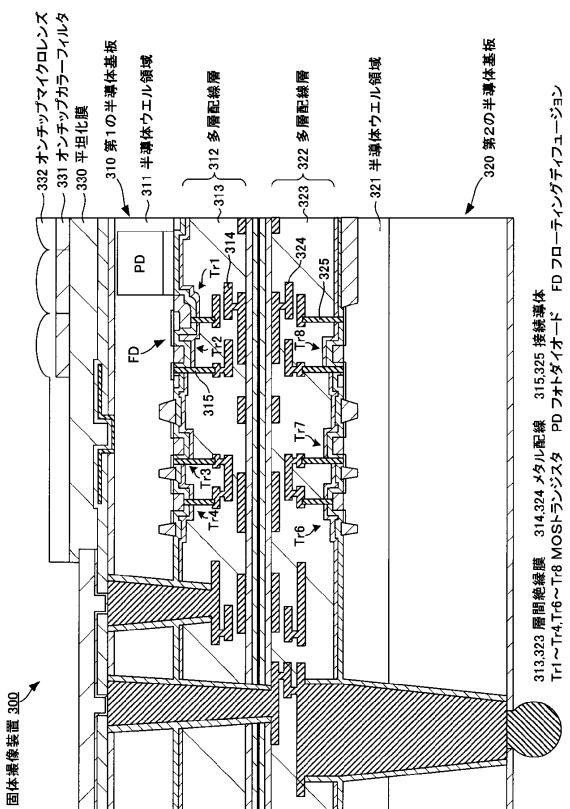

[応用例2]

図56に、上記各種実施形態及び各種変形例で説明した半導体装置、及び、その製造手法が適用可能な裏面照射型の固体撮像装置の要部の概略断面図を示す。

【0222】

図56に示す固体撮像装置300は、半製品状態の画素アレイを備えた第1の半導体基板310と、半製品状態のロジック回路を備えた第2の半導体基板320とを接合して構成される。なお、図56に示す固体撮像装置300では、第1の半導体基板310の第2の半導体基板320側とは反対側の表面上に、平坦化膜330、オンチップカラーフィルタ331、及び、オンチップマイクロレンズ332がこの順で積層される。

40

【0223】

第1の半導体基板310は、P型の半導体ウエル領域311、及び、多層配線層312を有し、平坦化膜330側に、半導体ウエル領域311が配置される。半導体ウエル領域311内には、例えばフォトダイオード(PD)、フローティングディフュージョン(FD)、画素を構成するMOSトランジスタ(Tr1, Tr2)、及び、制御回路を構成するMOSトランジスタ(Tr3, Tr4)が形成される。また、多層配線層312内には、層間絶縁膜313を介して形成された複数のメタル配線314、及び、メタル配線31

50

4と対応するMOSトランジスタとを接続するために層間絶縁膜313に形成された接続導体315が形成される。

【0224】

一方、第2の半導体基板320は、例えばシリコン基板の表面に形成された半導体ウエル領域321と、半導体ウエル領域321の第1の半導体基板310側に形成された多層配線層322とを有する。半導体ウエル領域321には、ロジック回路を構成するMOSトランジスタ(Tr6, Tr7, Tr8)が形成される。また、多層配線層322内には、層間絶縁膜323を介して形成された複数のメタル配線324、及び、メタル配線324と対応するMOSトランジスタとを接続するために層間絶縁膜323に形成された接続導体325が形成される。

10

【0225】

上述した構成の裏面照射型の固体撮像装置300にも、上述した本開示に係る各種実施形態及び上記各種変形例のCu-Cu接合技術を適用することができる。

【0226】

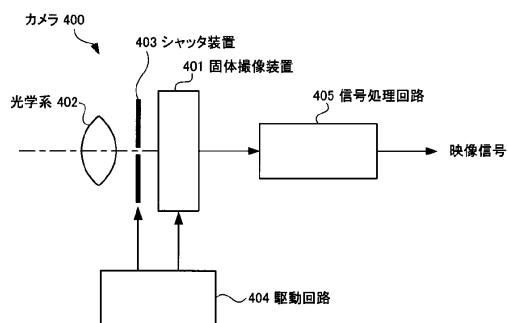

【応用例3】

上記各種実施形態及び各種変形例のCu-Cu接合技術を適用した固体撮像装置は、例えば、デジタルカメラやビデオカメラ等のカメラシステム、撮像機能を有する携帯電話、又は、撮像機能を備えた他の機器などの電子機器に適用することができる。応用例3では、電子機器の一構成例として、カメラを例に挙げ説明する。

【0227】

20

図57に、応用例3に係るカメラの概略構成を示す。なお、図57には、静止画像又は動画を撮影することのできるビデオカメラの構成例を示す。

【0228】

この例のカメラ400は、固体撮像装置401と、固体撮像装置401の受光センサ部に入射光を導く光学系402と、固体撮像装置401及び光学系402間に設けられたシャッタ装置403と、固体撮像装置401を駆動する駆動回路404とを備える。さらに、カメラ400は、固体撮像装置401の出力信号を処理する信号処理回路405を備える。

【0229】

固体撮像装置401は、上述した本開示に係る各種実施形態及び各種変形例のCu-Cu接合技術を用いて作製される。その他の各部の構成及び機能は次の通りである。

30

【0230】

光学系(光学レンズ)402は、被写体からの像光(入射光)を固体撮像装置401の撮像面(不図示)上に結像させる。これにより、固体撮像装置401内に、一定期間、信号電荷が蓄積される。なお、光学系402は、複数の光学レンズを含む光学レンズ群で構成してもよい。また、シャッタ装置403は、入射光の固体撮像装置401への光照射期間及び遮光期間を制御する。

【0231】

駆動回路404は、固体撮像装置401、及び、シャッタ装置403に駆動信号を供給する。そして、駆動回路404は、供給した駆動信号により、固体撮像装置401の信号処理回路405への信号出力動作、及び、シャッタ装置403のシャッタ動作を制御する。すなわち、この例では、駆動回路404から供給される駆動信号(タイミング信号)により、固体撮像装置401から信号処理回路405への信号転送動作を行う。

40

【0232】

信号処理回路405は、固体撮像装置401から転送された信号に対して、各種の信号処理を施す。そして、各種信号処理が施された信号(映像信号)は、メモリなどの記憶媒体(不図示)に記憶される、又は、モニタ(不図示)に出力される。

【0233】

なお、本開示は、以下のような構成を取ることもできる。

接合界面側の表面に形成された第1金属膜を有する第1半導体部と、

前記接合界面で前記第1金属膜と接合されかつ前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜を有し、前記接合界面で前記第1半導体部と貼り合わせて設けられた第2半導体部と、

前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア部と

を備える半導体装置。

( 2 )

前記第2半導体部が、前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア膜を有し、

10

前記界面バリア膜により前記界面バリア部が構成される

( 1 ) 記載の半導体装置。

( 3 )

前記第2半導体部が、前記第2金属膜の側部を覆うように設けられた絶縁膜を有し、

前記界面バリア膜が、前記絶縁膜の前記接合界面側の表面に形成される

( 2 ) に記載の半導体装置。

( 4 )

前記界面バリア膜が、SiN、SiON、SiCN、及び、有機系樹脂材料のいずれかで形成される

( 2 ) に記載の半導体装置。

20

( 5 )

前記第1半導体部が、前記第1金属膜の側部を覆うように設けられた第1酸化膜と、該第1酸化膜及び前記第1金属膜間に設けられかつ所定の金属材料を含むシード層とを有し、

前記第2半導体部が、前記第2金属膜の側部を覆うように設けられた第2酸化膜を有し、

前記界面バリア膜が、前記所定の金属材料の酸化膜で構成される

( 2 ) に記載の半導体装置。

( 6 )

前記所定の金属材料が、Mn、Mg、Ti、及び、Alのいずれかである

30

( 5 ) に記載の半導体装置。

( 7 )

前記第2半導体部が、前記第2金属膜の側部及び前記第2金属膜の前記接合界面とは反対側の表面を覆うように設けられたバリア本体部、並びに、該バリア本体部の前記接合界面側の端部から前記接合界面に沿って延在して形成された界面層部を含むバリアメタル層を有し、

前記界面バリア部が、前記バリアメタル層の前記界面層部で構成される

( 1 ) 又は ( 2 ) に記載の半導体装置。

( 8 )

前記バリアメタル層が、Ti、Ta、Ru、TiN、TaN、及び、RuNのいずれかで形成される

40

( 7 ) に記載の半導体装置。

( 9 )

前記第1半導体部の前記接合界面側の面領域のうち、前記第1金属膜の前記第2金属膜と接合しない面領域に凹部が設けられ、

前記界面バリア部が、前記第1金属膜の前記凹部と、前記凹部と対向する前記第2半導体部の前記接合界面側の面領域部とにより構成され、前記界面バリア部に前記凹部及び前記面領域部により画成されかつ密封された空隙が形成される

( 1 ) ~ ( 8 ) のいずれか一項に記載の半導体装置。

( 10 )

50

前記第2半導体部が、前記第2金属膜の側部を覆うように設けられた絶縁膜を有し、前記凹部と対向する前記第2半導体部の前記接合界面側の面領域部が前記絶縁膜で構成される

(9)に記載の半導体装置。

(11)

前記第2半導体部が、前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア膜を有し、

前記凹部と対向する前記第2半導体部の前記接合界面側の面領域部が前記界面バリア膜で構成される

(9)に記載の半導体装置。

10

(12)

前記第1金属膜及び第2金属膜がともに、Cu膜である

(1)～(11)のいずれか一項に記載の半導体装置。

(13)

接合界面側の表面に形成された第1金属膜を有する第1半導体部と、前記接合界面で前記第1金属膜と接合されかつ前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜を有し、前記接合界面で前記第1半導体部と貼り合わせて設けられた第2半導体部と、前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に設けられた界面バリア部とを有する半導体装置と、

20

前記半導体装置の出力信号を処理する信号処理回路と

を備える電子機器。

(14)

接合界面側の表面に形成された第1金属膜を有する第1半導体部を作製するステップと

、

前記接合界面側の表面面積が前記第1金属膜の前記接合界面側の表面面積より小さい第2金属膜を有する第2半導体部を作製するステップと、

前記第1半導体部の前記第1金属膜側の表面と前記第2半導体部の前記第2金属膜側の表面とを貼り合わせて、前記第1金属膜と前記第2金属膜とを接合するとともに、前記第1金属膜の前記接合界面側の面領域のうち前記第2金属膜と接合しない面領域を含む領域に界面バリア部を設けるステップと

30

を含む半導体装置の製造方法。

【符号の説明】

【0234】

1, 130…半導体装置、10, 131…第1半導体部材、11…第1SiO<sub>2</sub>層、12…第1Cu配線部、13…第1Cuバリア膜、14…第1Cu拡散防止膜、15…第1層間絶縁膜、16, 133…第1Cu接合部、17…第1Cuバリア層、20, 132…第2半導体部材、21…第2SiO<sub>2</sub>層、22…第2Cu配線部、23…第2Cuバリア膜、24…第2Cu拡散防止膜、25…第2層間絶縁膜、26…第2Cu接合部、27…第2Cuバリア層、28…界面Cuバリア膜、134…凹部

40

【図1】

(a)

(b)

【図2】

【図5】

【図6】

【図7】

【図8】

【図3】

【図4】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図23】

【図24】

接合

【図25】

11 第1SiO<sub>2</sub>層 12 第1Cu配線部 13 第1Cuパリア膜

14 第1Cu拡散防止膜 15 第1層間絶縁膜 16 第1Cu接合部

17 第1Cuパリア層 21 第2SiO<sub>2</sub>層 22 第2Cu配線部

23 第2Cu配線部 24 第2Cu拡散防止膜

25 第2層間絶縁膜 26 第2Cu接合部

61 第2Cuパリア層 61a パリア本体部 61b 界面層部

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【 図 4 1 】

11 第1SiO<sub>2</sub>層 12 第1Cu配線部 13 第1Cu/バリア膜

14 第1Cu拡散防止膜 15 第1層間絶縁膜 16 第1Cu接合部

17 第1Cu/バリア層 21 第2SiO<sub>2</sub>層 22 第2Cu配線部

23 第2Cu/バリア膜 24 第2Cu拡散防止膜 25 第2層間絶縁膜

26 第2Cu接合部 27 第2Cu/バリア層

【 図 4 2 】

11 第1SiO<sub>2</sub>層 12 第1Cu配線部 13 第1Cuパリア膜

14 第1Cu拡散防止膜 663 第1層間絶縁膜 16 第1Cu接合部

17 第1Cuパリア層 21 第2SiO<sub>2</sub>層 22 第2Cu配線部

23 第2Cuパリア膜 24 第2Cu拡散防止膜 664 第2層間絶縁膜

26 第2Cu接合部 27 第2Cuパリア層

【 図 4 5 】

【図46】

【 47 】

### 【図4-3】

11 第1SiO<sub>2</sub>層 12 第1Cu配線部 13 第1Cuバリア膜

14 第1Cu拡散防止膜 15 第1層間絶縁膜 133 第1Cu接合部

134 回部 17 第1Cuバリア層 21 第2SiO<sub>2</sub>層 22 第2Cu配線部

23 第2Cuバリア膜 24 第2Cu拡散防止膜 25 第2層間絶縁膜

26 第2Cu接合部 27 第2Cuバリア層

【 図 4 4 】

【 図 4 8 】

〔図49〕

11 第1SiO<sub>2</sub>層 12 第1Cu配線部 13 第1Cuバリア膜

14 第1Cu拡散防止膜 15 第1層間絶縁膜 133 第1Cu接合部

134 凹部 17 第1Cuバリア層 21 第2SiO<sub>2</sub>層 22 第2Cu配線部

23 第2Cuバリア膜 24 第2Cu拡散防止膜 25 第2層間絶縁膜

26 第2Cu接合部 27 第2Cuバリア層 28 面界Cuバリア膜

【図50】

【図51】

【図52】

【図53】

【図54】

【図55】

【図56】

【図5-7】

【図5-8】

---

フロントページの続き

(56)参考文献 特開2011-044655(JP,A)

特開2011-049270(JP,A)

特開2010-129693(JP,A)

特開2006-173637(JP,A)

国際公開第2010/013728(WO,A1)

特開2011-054637(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/768

H01L 23/522

H01L 27/14

H04N 5/369