(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H03L 7/08 (2006.01)

(45) 공고일자

2007년08월03일

(11) 등록번호

10-0746143

(24) 등록일자

2007년07월30일

(21) 출원번호 10-2001-0016631

(22) 출원일자 2001년03월29일

심사청구일자 2006년03월29일

(65) 공개번호

10-2002-0055344

(43) 공개일자

2002년07월08일

(30) 우선권주장 00311746.2 2000년12월28일 유럽특허청(EPO)(EP)

(73) 특허권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

티티피컴 리미티드

영국 에스지8 6이이 로이스톤 허트포드셔 멜보른 캠브리지 로드 멜보른 사이언스 파크

(72) 발명자 야마와끼 다이조

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루빌딩 가부시키가이

샤 히타치세이사쿠쇼 지적소유권본부 내

다나카 사또시

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루빌딩 가부시키가이

샤 히타치세이사쿠쇼 지적소유권본부 내

하야시 노리오

일본 도쿄도 고다이라시 조스이혼쵸 5초메 22-1 히타치 초엘 에스아이

시스템즈 내

와따나베 가즈오

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루빌딩 가부시키가이

샤 히타치세이사쿠쇼 지적소유권본부 내

헨쇼 로버트 애슬

영국 에스지8 6이이 허트포드셔 로이스톤 멜보른 캠브리지로드 멜보른

사이언스 파크 티티피컴 리미티드 내

(74) 대리인

구영창

장수길

(56) 선행기술조사문헌

EP0856946 A

US4115745 AUS4458561 A

EP0326940 A

심사관 : 강윤석

전체 청구항 수 : 총 43 항

## (54) P L L 회로 및 무선 통신 단말기기

---

### (57) 요약

고속 수렴 가능한, IF 신호를 RF 신호로 변환하는 PLL 회로와, PLL 회로를 이용한 무선 통신 단말 기기를 제공한다.

PLL 회로의 전류 출력형 위상 비교기(100)의 출력에, LPF(103) 충전용의 정전류원(101)과, 방전용의 정전류원(200)과, 고속 충전용의 정전류원(201)을 접속한다. 상기 PLL 회로의 수렴 주파수가 낮은 경우에는, 정전류원(101)을 이용해서 VCO(104)의 입력 전위를 0V에서 상승시켜 수렴시킨다. 그 수렴 주파수가 높은 경우에는, 정전류원(201)을 이용해서 상기 입력 전위를 일단 최대 전위로 한다. 그 후, 정전류원(200)을 이용하여 상기 입력 전위를 최대 전압까지 하강시켜 수렴시킨다. 수렴 주파수에 의해서 상기 동작을 선택함으로써, PLL 회로의 최대 수렴 시간을 단축할 수 있다.

### 내포도

도 1

### 특허청구의 범위

#### 청구항 1.

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 상기 전류 출력형 위상 비교기의 제 2 입력 신호를 출력하는 믹서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 제 1 및 제 2 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 제 1 스위치와,

상기 전류 출력형 위상 비교기와 제 2 기준 전압 간에 접속된 제 2 스위치와,

상기 제 1 및 제 2 정전류원의 온-오프를 제어하고, 상기 제 1 스위치와 상기 제 2 스위치의 단락 및 개방을 제어하는 제어 기기를 포함하는 PLL 회로.

#### 청구항 2.

제 1 항에 있어서,

상기 제 1 기준 전압은 0V이고,

상기 제 2 기준 전압은 전원 공급 전압이고,

상기 제 1 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하고,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받는 PLL 회로.

### 청구항 3.

제 2 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 제 1 및 제 2 정전류원이 오프 상태로, 상기 제 1 스위치가 단락되어 있고, 상기 제 2 스위치가 개방되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 제 1 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 제 1 스위치를 개방하고, 상기 제 1 정전류원을 턴온하며,

상기 제 2 수단은 상기 제 1 스위치를 개방하고, 상기 제 2 스위치를 단락하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 턴온하면서 상기 제 2 스위치를 개방하는 PLL 회로.

### 청구항 4.

제 3 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일한 PLL 회로.

### 청구항 5.

제 1 항에 있어서,

상기 제 1 기준 전압은 전원 공급 전압이고,

상기 제 2 기준 전압은 0V이고,

상기 제 1 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받으며,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 PLL 회로.

### 청구항 6.

제 5 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 제 1 및 제 2 정전류원이 오프 상태로, 상기 제 1 스위치가 단락되어 있고, 상기 제 2 스위치가 개방되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 제 1 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 제 1 스위치를 개방하고, 상기 제 1 정전류원을 턴온하며,

상기 제 2 수단은 상기 제 1 스위치를 개방하고, 상기 제 2 스위치를 단락하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 턴온하면서 상기 제 2 스위치를 개방하는 PLL 회로.

### 청구항 7.

제 6 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일한 PLL 회로.

### 청구항 8.

제 1 항에 있어서,

상기 제 1 스위치는 상기 VCO의 입력 전압으로부터 독립된 신호에 의해 제어되며, 상기 제 2 스위치는 상기 VCO의 입력 전압으로부터 독립된 신호에 의해 제어되는 PLL 회로.

### 청구항 9.

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 상기 전류 출력형 위상 비교기의 제 2 입력 신호를 출력하는 빅서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 가변 전류원 및 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 스위치와,

상기 가변 전류원의 온-오프, 출력 전류값 및 상기 정전류원의 온-오프를 제어하고, 상기 스위치의 단락 및 개방을 제어하는 제어기를 포함하는 PLL 회로.

### 청구항 10.

제 9 항에 있어서,

상기 기준 전압은 0V이고,

상기 가변 전류원은 상기 전류 출력형 위상 비교기의 출력단에 전류를 출력하고,

상기 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받는 PLL 회로.

### 청구항 11.

제 10 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 가변 전류원 및 상기 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 가변 전류원이 제 1 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며,

상기 제 2 수단은 상기 가변 전류원이 제 2 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며, 일정 시간 경과 후에, 상기 정전류원을 턴온하면서 상기 가변 전류원을 턴오프하는 PLL 회로.

## 청구항 12.

제 11 항에 있어서,

상기 제 1 정전류값과 상기 정전류의 출력 전류값은 서로 동일하고, 상기 제 2 정전류값은 상기 제 1 정전류값과 상기 정전류의 출력 전류값의 적어도 2배 이상인 PLL 회로.

## 청구항 13.

제 9 항에 있어서,

상기 기준 전압은 전원 공급 전압이고,

상기 가변 전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 전류를 공급받고,

상기 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 PLL 회로.

## 청구항 14.

제 13 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 가변 전류원 및 상기 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 가변 전류원이 제 1 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며,

상기 제 2 수단은 상기 가변 전류원이 제 2 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며, 일정 시간 경과 후에, 상기 정전류원을 턴온하면서 상기 가변 전류원을 턴오프하는 PLL 회로.

## 청구항 15.

제 14 항에 있어서,

상기 제 1 정전류값과 상기 정전류의 출력 전류값은 서로 동일하며, 상기 제 2 정전류값은 상기 제 1 정전류값과 상기 정전류의 출력 전류값의 적어도 2배 이상인 PLL 회로.

## 청구항 16.

제 9 항에 있어서,

상기 스위치는 상기 VCO의 입력 전압으로부터 독립된 신호에 의해 제어되는 PLL 회로.

## 청구항 17.

기저 대역 회로와,

상기 기저 대역 회로로부터 제 1 기저 대역 신호를 공급받는 변조기와,

상기 변조기의 출력부에 접속된 PLL 회로와,

상기 PLL 회로의 출력부에 접속된 전력 증폭기와,

상기 기저 대역 회로에 제 2 기저 대역 신호를 출력하는 수신기 회로와,

안테나와,

상기 안테나, 상기 수신기 회로의 입력부 및 상기 전력 증폭기의 출력부와 접속된 선택기를 포함하는 무선 이동국으로서,

상기 기저 대역 회로는 상기 무선 이동국의 동작을 제어하는 제어 신호를 출력하며,

상기 PLL 회로는,

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 상기 전류 출력형 위상 비교기의 제 2 입력 신호를 출력하는 막서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 제 1 및 제 2 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 제 1 스위치와,

상기 전류 출력형 위상 비교기와 제 2 기준 전압 간에 접속된 제 2 스위치와,

상기 제 1 및 제 2 정전류원의 온-오프를 제어하고, 상기 제 1 스위치와 상기 제 2 스위치의 단락 및 개방을 제어하는 제어 기기를 포함하는 무선 이동국.

## 청구항 18.

제 17 항에 있어서,

상기 제 1 스위치는 상기 VCO의 입력 전압으로부터 독립된 신호에 의해 제어되며, 상기 제 2 스위치는 상기 VCO의 입력 전압으로부터 독립된 신호에 의해 제어되는 무선 이동국.

### 청구항 19.

전류 출력형 위상 비교기와,

저역 통과 필터와,

VCO를 포함하는 PLL 회로로서,

상기 PLL 회로의 수렴 주파수가 설정 주파수보다 낮은 경우에는, 상기 PLL 회로는 상기 수렴 주파수에 대응하는 제 1 수렴 전압보다 낮은 입력 전압으로부터 상기 제 1 수렴 전압까지 PLL 피드백 루프에 의해 상기 수렴 주파수를 수렴시키고,

상기 PLL 회로의 수렴 주파수가 상기 설정 주파수보다 높은 경우에는, 상기 PLL 회로는 제 2 수렴 전압보다 높은 입력 전압으로부터 상기 제 2 수렴 전압까지 상기 PLL 피드백 루프에 의해 상기 수렴 주파수를 수렴시키는 PLL 회로.

### 청구항 20.

전류 출력형 위상 비교기와,

저역 통과 필터와,

VCO를 포함하는 PLL 회로로서,

상기 PLL 회로의 수렴 주파수가 설정 주파수보다 높은 경우에는, 상기 PLL 회로는 상기 수렴 주파수에 대응하는 제 1 수렴 전압보다 높은 입력 전압으로부터 상기 제 1 수렴 전압까지 PLL 피드백 루프에 의해 상기 수렴 주파수를 수렴시키고,

상기 PLL 회로의 수렴 주파수가 설정 주파수보다 낮은 경우에는, 상기 PLL 회로는 제 2 수렴 전압보다 낮은 입력 전압으로부터 상기 제 2 수렴 전압까지 상기 PLL 피드백 루프에 의해 상기 수렴 주파수를 수렴시키는 PLL 회로.

### 청구항 21.

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 제 2 입력 신호를 출력하는 믹서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 제 1, 제 2, 제 3 정전류원과,

상기 전류 출력형 위상 비교기와 기준 전압 간에 접속된 스위치와,

상기 제 1, 제 2, 제 3 정전류원의 온-오프를 제어하고, 상기 스위치의 단락 및 개방을 제어하는 제어 수단을 포함하는 PLL 회로.

## 청구항 22.

제 21 항에 있어서,

상기 기준 전압은 OV이고,

상기 제 1 및 제 3 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하고,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받는 PLL 회로.

## 청구항 23.

제 21 항에 있어서,

상기 기준 전압은 전원 공급 전압이고,

상기 제 1 및 제 3 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받고,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 PLL 회로.

## 청구항 24.

제 22 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 제 1, 제 2, 제 3 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 스위치를 개방하고, 상기 제 1 정전류원을 터온하며,

상기 제 2 수단은 상기 스위치를 개방하고, 상기 제 3 정전류원을 터온하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 터온하면서 상기 제 3 정전류원을 터오프하는 PLL 회로.

## 청구항 25.

제 24 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일하고, 상기 제 3 정전류원의 출력 전류값은 상기 제 1 및 제 2 정전류원의 출력 전류값의 적어도 2배 이상인 PLL 회로.

## 청구항 26.

제 23 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 제 1, 제 2, 제 3 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 스위치를 개방하고, 상기 제 1 정전류원을 턴온하며,

상기 제 2 수단은 상기 스위치를 개방하고, 상기 제 3 정전류원을 턴온하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 턴온하면서 상기 제 3 정전류원을 턴오프하는 PLL 회로.

### 청구항 27.

제 26 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일하고, 상기 제 3 정전류원의 출력 전류값은 상기 제 1 및 제 2 정전류원의 출력 전류값의 적어도 2배 이상인 PLL 회로.

### 청구항 28.

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 제 2 입력 신호를 출력하는 디서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 제 1 및 제 2 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 제 1 스위치와,

상기 전류 출력형 위상 비교기와 제 2 기준 전압 간에 접속된 제 2 스위치와,

상기 제 1 및 제 2 정전류원의 온-오프를 제어하고, 상기 제 1 스위치와 상기 제 2 스위치의 단락 및 개방을 제어하는 제어수단을 포함하는 PLL 회로.

### 청구항 29.

제 28 항에 있어서,

상기 제 1 기준 전압은 0V이고,

상기 제 2 기준 전압은 전원 공급 전압이고,

상기 제 1 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하고,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받는 PLL 회로.

### 청구항 30.

제 28 항에 있어서,

상기 제 1 기준 전압은 전원 공급 전압이고,

상기 제 2 기준 전압은 0V이고,

상기 제 1 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받고,

상기 제 2 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 PLL 회로.

### 청구항 31.

제 29 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 제 1 및 제 2 정전류원이 오프 상태로, 상기 제 1 스위치가 단락되어 있고, 상기 제 2 스위치가 개방되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 제 1 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 제 1 스위치를 개방하고, 상기 제 1 정전류원을 턴온하며,

상기 제 2 수단은 상기 제 1 스위치를 개방하고, 상기 제 2 스위치를 단락하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 턴온하면서 상기 제 2 스위치를 개방하는 PLL 회로.

### 청구항 32.

제 31 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일한 PLL 회로.

### 청구항 33.

PLL 회로로서,

비동작 상태에서, 제 1 및 제 2 정전류원이 오프 상태로, 제 1 스위치가 단락되어 있고, 제 2 스위치가 개방되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 제 1 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 제 1 스위치를 개방하고, 상기 제 1 정전류원을 턴온하며,

상기 제 2 수단은 상기 제 1 스위치를 개방하고, 상기 제 2 스위치를 단락하며, 일정 시간 경과 후에, 상기 제 2 정전류원을 턴온하면서 상기 제 2 스위치를 개방하는 PLL 회로.

### 청구항 34.

제 33 항에 있어서,

상기 제 1 및 제 2 정전류원의 출력 전류값은 서로 동일한 PLL 회로.

### 청구항 35.

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 제 2 입력 신호를 출력하는 띡서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 가변 전류원 및 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 스위치와,

상기 가변 전류원의 온-오프, 출력 전류값 및 상기 정전류원의 온-오프를 제어하고, 상기 스위치의 단락 및 개방을 제어하는 제어 수단을 포함하는 PLL 회로.

### 청구항 36.

제 35 항에 있어서,

상기 기준 전압은 0V이고,

상기 가변 전류원은 상기 전류 출력형 위상 비교기의 출력단에 전류를 출력하고,

상기 정전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 정전류를 공급받는 PLL 회로.

### 청구항 37.

제 36 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 가변 전류원 및 상기 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 가변 전류원이 제 1 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며,

상기 제 2 수단은 상기 가변 전류원이 제 2 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며, 일정 시간 경과 후에, 상기 정전류원을 턴온하면서 상기 가변 전류원을 턴오프하는 PLL 회로.

### 청구항 38.

제 37 항에 있어서,

상기 제 1 정전류값과 상기 정전류의 출력 전류값은 서로 동일하고, 상기 제 2 정전류값은 상기 제 1 정전류값과 상기 정전류의 출력 전류값의 적어도 2배 이상인 PLL 회로.

### 청구항 39.

제 35 항에 있어서,

상기 기준 전압은 전원 공급 전압이고,

상기 가변 전류원은 상기 전류 출력형 위상 비교기의 출력단으로부터 전류를 공급받고,

상기 정전류원은 상기 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 PLL 회로.

#### 청구항 40.

제 39 항에 있어서,

상기 PLL 회로는, 비동작 상태에서, 상기 가변 전류원 및 상기 정전류원이 오프 상태로, 상기 스위치가 단락되어 있으며, 제 1 및 제 2 수단이 상기 비동작 상태로부터 동작 상태로 전이하는데 이용되고, 또한, 상기 PLL 회로의 수렴 주파수가, 상기 스위치의 단락 회로에서의 상기 VCO의 출력 주파수와 설정 주파수 사이의 주파수라는 조건을 충족시키는 경우에는, 상기 제 1 수단이 이용되고, 상기 조건을 충족시키지 못하는 경우에는, 상기 제 2 수단이 이용되는 식으로 구현되고,

상기 제 1 수단은 상기 가변 전류원이 제 1 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며,

상기 제 2 수단은 상기 가변 전류원이 제 2 정전류값을 출력하도록 상기 스위치를 개방하고 상기 가변 전류원을 턴온하며, 일정 시간 경과 후에, 상기 정전류원을 턴온하면서 상기 가변 전류원을 턴오프하는 PLL 회로.

#### 청구항 41.

제 39 항에 있어서,

상기 제 1 정전류값과 상기 정전류의 출력 전류값은 서로 동일하며, 상기 제 2 정전류값은 상기 제 1 정전류값과 상기 정전류의 출력 전류값의 적어도 2배 이상인 PLL 회로.

#### 청구항 42.

기저 대역 회로와,

상기 기저 대역 회로로부터 제 1 기저 대역 신호를 공급받는 변조기와,

상기 변조기의 출력부에 접속된 PLL 회로와,

상기 PLL 회로의 출력부에 접속된 전력 증폭기와,

상기 기저 대역 회로에 제 2 기저 대역 신호를 출력하는 수신기 회로와,

안테나와,

상기 안테나, 상기 수신기 회로의 입력부 및 상기 전력 증폭기의 출력부와 접속된 선택기를 포함하는 무선 이동국으로서,

상기 기저 대역 회로는 상기 무선 이동국의 동작을 제어하는 제어 신호를 출력하며,

상기 PLL 회로는,

주파수 변조된 제 1 입력 신호와 제 2 입력 신호 간의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 저역 통과 필터와,

상기 저역 통과 필터의 출력단에 접속된 VCO와,

상기 VCO의 출력단에 접속되어 상기 VCO의 출력 주파수를 변환하여 제 2 입력 신호를 출력하는 딱서와,

상기 전류 출력형 위상 비교기의 출력단에 접속된 제 1 및 제 2 정전류원과,

상기 전류 출력형 위상 비교기와 제 1 기준 전압 간에 접속된 제 1 스위치와,

상기 전류 출력형 위상 비교기와 제 2 기준 전압 간에 접속된 제 2 스위치와,

상기 제 1 및 제 2 정전류원의 온-오프를 제어하고, 상기 제 1 스위치와 상기 제 2 스위치의 단락 및 개방을 제어하는 제어

수단을 포함하는 무선 이동국.

### 청구항 43.

기저 대역 회로와,

상기 기저 대역 회로로부터 제 1 기저 대역 신호를 공급받는 변조기와,

상기 변조기의 출력부에 접속된 PLL 회로와,

상기 PLL 회로의 출력부에 접속된 전력 증폭기와,

상기 기저 대역 회로에 제 2 기저 대역 신호를 출력하는 수신기 회로와,

안테나와,

상기 안테나, 상기 수신기 회로의 입력부 및 상기 전력 증폭기의 출력부와 접속된 선택기를 포함하는 무선 이동국으로서,

상기 기저 대역 회로는 상기 무선 이동국의 동작을 제어하는 제어 신호를 출력하며,

상기 PLL 회로는,

전류 출력형 위상 비교기와,

저역 통과 필터와,

VCO를 포함하고,

상기 PLL 회로의 수령 주파수가 설정 주파수보다 낮은 경우에는, 상기 PLL 회로는 상기 수령 주파수에 대응하는 제 1 수

령 전압보다 낮은 입력 전압으로부터 상기 제 1 수령 전압까지 PLL 피드백 루프에 의해 상기 수령 주파수를 수령시키고,

상기 PLL 회로의 수령 주파수가 상기 설정 주파수보다 높은 경우에는, 상기 PLL 회로는 제 2 수령 전압보다 높은 입력 전

압으로부터 상기 제 2 수령 전압까지 상기 PLL 피드백 루프에 의해 상기 수령 주파수를 수령시키는 무선 이동국.

### 명세서

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, IF(중간 주파수) 신호를 RF(무선 주파수) 신호로 주파수를 변환하는 PLL 회로의 수렴의 고속화에 적용하기 유효한 기술에 관한 것이다.

이동체 통신 단말에 이용되는 송신기에는 몇 개의 방식이 있다. 가장 일반적인 것은, 기저 대역 신호를 변조기에서 IF(중간 주파수) 신호로 변환하여, 그것을 안테나로부터 송신해야 하는 주파수로 믹서에서 변환하는 믹서 방식이다. 이 외에, 그 방식의 믹서 대신에 PLL 회로를 이용해서 주파수를 변환하는 PLL 방식이 있다. PLL 방식은, 정진폭 변조밖에 취급할 수 없다는 결점은 있지만, 송신 잡음을 믹서 방식에 비해서 대폭 줄일 수 있다는 장점이 있고, 주로 GSM(Global System for Mobile communications) 시스템의 무선 통신 단말 기기에 이용되고 있다. 그 상세한 동작 원리는, 예를들면, IEEE journal of solid-state circuits Vol. 32, No. 12, pp. 2089-2096, "A 2.7-V GSM RF Transceiver IC"에 기재되어 있다.

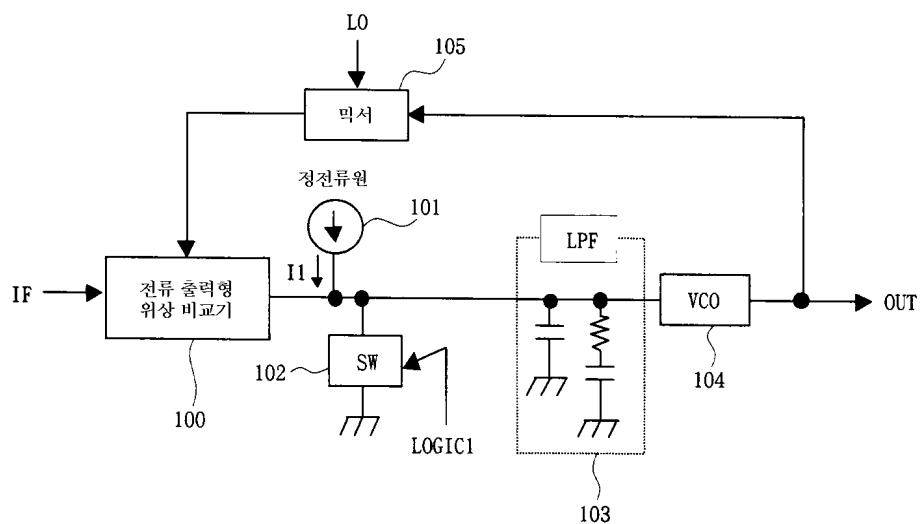

도 12는, 그 PLL 방식에서 이용되는 PLL 회로의 한 예를 도시한 도면이다. 그 PLL 회로는, 전류 출력형 위상 비교기(100)와, 정전류원(101)과, 믹서기(105)와, 저역 통과 필터(LPF)(103)와, 전압 제어 발진기(104)와, 스위치(SW)(102)로 구성된다. 이하의 설명에 있어서, VCO(104)는 플러스의 감도를 가지는 것으로 가정한다. LPF(103)에는, 일반적으로, 도 12에 도시하는 바와 같은 수동 소자로 이루어지는 2차 LPF가 사용된다. 또한, SW(102)에는 제어 신호 LOGIC(1)이 0의 경우에 SW(102)는 개방 상태로 되고, LOGIC(1)이 1인 경우에 SW(102)는 접지에 단락(短絡)한다.

전류 출력형 위상 비교기(100)에는, 위상 주파수 비교기가 아닌 고속 동작 가능한 믹서형의 위상 비교기가 이용된다. 이것에 의해, 송신기의 주파수 구성의 자유도를 올릴 수 있다. 위상 비교기의 결점은, 2개의 입력 주파수 차가 큰 경우에, 출력 전압이 LPF(103)에 의해서 억압되어 VCO(104)에 전달되지 않는 것이다. 즉, 수렴 초기 단계에서의 VCO(104)의 출력 주파수에 의해서는 그 PLL 회로가 수렴될 수 없다. 이 결점을 해소하기 위해서, 정전류원(101)과 SW(102)가 접속되어 있다. 그 PLL 회로가 수렴하기 전에 필히 SW(102)를 접지에 접속하여 VCO(104)의 입력 전위를 접지 전위로 설정한다. 그 후, SW(102)를 개방하여 수렴을 개시한다. 전류 출력형 위상 비교기(100)의 출력이 VCO(104)에 전달되지 않은 경우에도, 정전류원(101)이 LPF(103)의 용량을 충전함으로써, VCO(104)의 입력 전위가 상승한다. 이에 따라, 전류 출력형 위상 비교기(100)의 2개의 입력 주파수는 근접해 갈 수 있다. 그 입력 주파수가 충분히 근접하면, 전류 출력형 위상 비교기(100)의 출력이 VCO(104)의 입력에 전달되어, 수렴이 가능하게 된다.

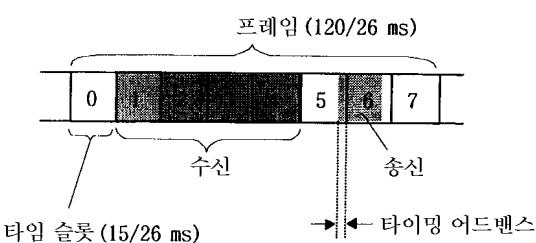

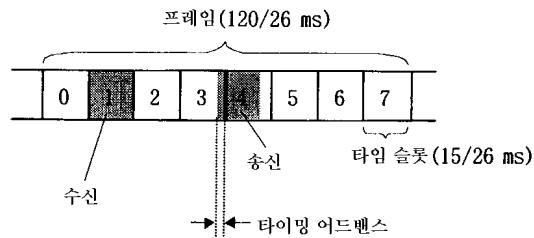

GSM 시스템에는 TDMA (Time Division Multiple Access) 방식이 이용되고 있다. 한 프레임은 120/26ms이고, 15/26ms의 8개의 타임 슬롯으로 구성된다. 한 슬롯을 수신에, 다른 한 슬롯을 송신에 사용한다. 도 13은, 단말의 송수신 타이밍을 도시한 한 예이다. 이 예에서는, 타임 슬롯(1)을 수신으로, 타임 슬롯(4)을 송신으로 할당한다. 송수신 간격은 2개의 타임 슬롯 만큼이다. 단, 단말에서 기지국으로의 전파전송 지연을 고려해서, 송신은 최대 3024/13μs의 타이밍 어드밴스 만큼 조속히 행해진다.

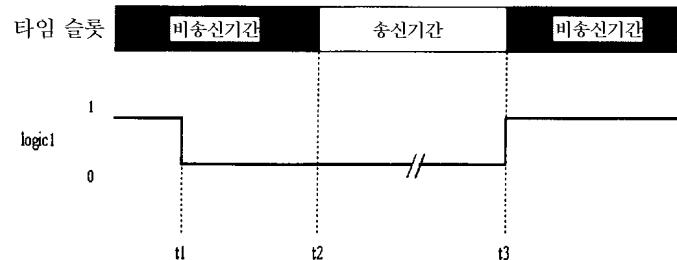

상기 PLL 방식이, 전술의 GSM의 TDMA 동작에 따라서 어떻게 동작하는가를, 상기 종래의 PLL 회로와, 도 14에 도시하는 타이밍 차트를 이용해서 설명한다. 설명의 편의를 위해서, 전류 출력형 위상 비교기(100)의 입력 중심 주파수를 270MHz, 믹서(105)에 입력되는 국부발진 신호 LO의 주파수를 1180MHz로 한다. 또한, VCO(104)의 입력 감도는 플러스이고, 입력 전위가 0V일 때의 출력 주파수를 850MHz로 한다. 단말이 송신 타이밍에 없을 경우, LOGIC(1)에는 1이 입력되며, 전류 출력형 위상 비교기(100)의 출력은 0V가 된다. 이에 따라, LPF(103)의 용량에 축적된 전하가 방전되어, VCO(104)의 입력 전위도 또한 0V가 된다. 따라서, VCO(104)의 출력 주파수는 850MHz가 된다. 시각 t1이 되면, LOGIC(1)에는 0이 입력되어, SW(102)는 개방 상태로 된다. 이 때의 믹서(105)의 출력 주파수는, 850MHz와 1180MHz의 합과 차, 즉, 2030MHz와 330MHz이다. 합성분은, LPF(103)로 억압되어 수렴에 기여하지 않기 때문에, 여기에서는 차성분만을 고려한다. 따라서, 전류 출력형 위상 비교기(100)의 출력 주파수는, 330-270=60MHz가 된다. GSM 시스템에 이용되는 경우, 일반적으로 PLL 회로의 영역은 약 1MHz로 설계되어 있기 때문에, 믹서(105)의 출력 신호는 LPF(103)로 충분히 억압되어, 상기 용량으로의 전하 축적에 기여하지 않는다. 즉, 피드백이 끊긴 상태가 된다. 그러나, 정전류원(101)에서의 정전류에 의해 그 용량에 전하가 축적되어, VCO(104)의 입력 전위는 상승한다. 그 결과, VCO(104)의 출력 주파수는 850MHz로부터 상승해 간다. VCO(104)의 출력 주파수가, 예를들면, 908MHz로 상승한 경우를 고려한다. 이 때, 전류 출력형 위상 비교기(100)의 출력 주파수 2MHz가

된다. 따라서, LPF(103)에서의 억압도가 감소하여, 전하 축적에 기여할 수 있다. 즉, 피드백이 회복된다. 피드백이 회복된 것에 의해 PLL 회로는 최종적으로 수렴하여, VCO(104)의 출력 주파수는  $1180 - 270 = 910\text{MHz}$ 가 된다. 수렴은 송신 기간이 시작되는 시각 t2보다도 빨리 완료해야 한다. 송신 기간이 종료하는 시각 t3에 LOGIC(1)에는 1이 입력되어, 다시 VCO(104)의 입력전위를 0V로 하고, 다음의 송신 기간에 대비한다.

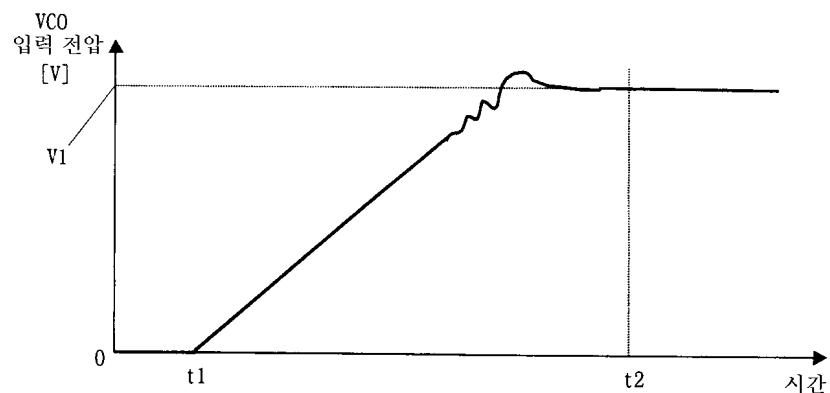

도 15는, 상기 수렴 과정에 있어서의 VCO(104)의 입력 전위의 변화를 나타낸 한 예이다. 시각 t1까지는, 그 입력 전위는 0V이다. 시각 t1에 SW(102)가 개방되고, 입력 전위가 직선적으로 상승을 시작한다. 상승의 기울기는, 주로 정전류원(101)의 출력 전류 I1과, LPF(103)의 총용량 C에 의해 결정되어, I1/C에서 주어진다. 그 후, 피드백을 회복하여 수렴을 완료한다. VCO(104)의 감도를 Kv, 그 입력 전위가 0V일 때의 VCO(104)의 출력 주파수를 f0, 수렴 시의 VCO(104)의 출력 주파수를 f1로 하면, 수렴 시의 그 입력 전위 V1는 수학식 1로 주어진다.

### 수학식 1

$$V1 = (f1 - f0) / Kv$$

PLL 회로의 수렴 시간 ts는, 그 출력 전류 I1에 의해서 그 총용량 C가 V1에 충전되는 시간에 근사할 수 있기 때문에, ts는 수학식 2로 주어된다.

### 수학식 2

$$ts = (f1 - f0) / Kv \cdot C / I1$$

따라서, f1이 높은 수록 수렴 시간이 길게 된다. 예를들면 GSM 시스템에서는, 송신 주파수의 최고 주파수 915MHz로 수렴할 때에 가장 수렴 시간이 길게 된다.

최근, 고속 데이터 통신 서비스의 요구가 급속히 증가되어 왔다. 그것에 따라서, GMS 시스템에 있어서도 종래의 데이터 레이트를 개선하는 방식이 몇 개 제안되어, 실용을 위한 검토가 행해지고 있다. 그 하나가 GPRS (General Packet Radio Service)이다. GPRS는, 도 16에 도시된 바와 같이 복수의 타임 슬롯을 송신 혹은 수신에 할당하는 것으로 데이터 레이트를 높이는 방식이다. 도 13과 도 16을 비교하면 명백한 바와 같이, GPRS에서는 상기 PLL 회로가 수렴에 사용할 수 있는 시간이 종래의 GSM에 비해 약 반이다. 여기서, 상기 PLL 회로의 수렴 시간을 단축할 필요성이 대두되었다.

### 발명이 이루고자 하는 기술적 과제

이와 같이, 종래의 PLL 회로의 수렴 시간 ts는 수학식 2로 주어된다. ts를 단축하는데는, 수학식 2에 포함되는 파라미터를 변경할 필요가 있다. 일반적으로, VCO(014)는 모듈 부품으로서 공급되기 때문에, 그 특성치, (f0)과 (Kv)는 고정치이다. 또한, I1/C는 이하의 1), 2)에 설명하는 제한에 의해 자유롭게 변경하는 것이 곤란하다. 1) 전류 출력형 위상 비교기(100)의 출력 전류와 C의 비는, 시스템 파라미터인 변조 대역폭이나 허용 잡음량에 의해서 결정된다. 2) 그 출력 전류와 I1의 비에 의해 PLL 회로의 수렴 안정성이 결정된다. 즉, 종래의 PLL 회로의 경우, 상술의 제한을 만족하면서, 수렴 시간을 단축하는 것은 곤란하다.

그래서, 본 발명의 목적은, 상술의 제한을 만족하면서, 종래의 PLL 회로의 최대 수렴 시간을 단축하는 것이다.

본 발명의 상기 및 그 외의 목적과 신규 특징은, 본 명세서의 기술 및 첨부 도면으로부터 명확하게 될 것이다.

### 발명의 구성

본 출원에 있어서 개시되는 발명 중에 대표적인 것의 개요를 간단히 설명하면, 다음과 같다.

상기 목적을 달성하기 위해서, 본 발명의 PLL 회로는, 적어도 전류 출력형 위상 비교기와, 저역 통과 필터와, VCO를 포함하는 PLL 회로이고, 수렴 개시 전에는 VCO의 입력 전위를 0V로 하고, PLL 회로의 수렴 주파수가 설정 주파수보다도 낮은 경우에는, 입력 전위를 0V로부터 수렴 전위까지 PLL 피드백 루프에 의해 수렴시키고, 그 수렴 주파수가 그 설정 주파수보다도 높은 경우에는, 우선 그 입력 전위를 0V로부터 전원 전압까지 PLL 피드백 루프를 사용하지 않고 상승시키고, 그 후, 입력 전위를 전원 전압에서부터 수렴 전위까지 PLL 피드백 루프에 의해 수렴시키는 것이다.

또한, 상기 목적을 달성하기 위한 다른 동작으로서, 본 발명의 PLL 회로는, 적어도 전류 출력형 위상 비교기와, 저역 통과 필터과, VCO를 포함하는 PLL 회로이고, 수렴 개시전에 그 VCO의 입력 전위를 전원 전압으로 하고, PLL 회로의 수속 주파수가 설정 주파수보다도 높은 경우에는, 입력 전위를 전원 전압에서부터 수렴 전위까지 PLL 피드백 루프에 의해 수렴시키고, 수렴 주파수가 설정 주파수보다도 낮은 경우에는, 우선 입력 전위를 전원 전압에서 0V까지 PLL 피드백 루프를 사용하지 않고 하강시키고, 그 후, 입력 전위를 0V에서 수렴 전위까지 PLL 피드백 루프에 의해 수렴시키는 것이다.

또한, 상기 목적을 달성하기 위해서, 본 발명의 PLL 회로의 구성은, 제1의 입력 신호와 제2의 입력 신호의 위상차에 비례한 신호를 출력하는 전류 출력형 위상 비교기와, 전류 출력형 위상 비교기의 출력단에 접속된 LPF와, LPF의 출력단에 접속된 VCO와, VCO의 출력단에 접속되어 제2의 신호를 출력하는 믹서와, 전류 출력형 위상 비교기의 출력단에 정전류를 출력하는 제1과 제2의 정전류원과, 전류 출력형 위상 비교기의 출력단으로부터 정전류를 흡수하는 제3의 정전류원과, 전류 출력형 위상 비교기와 접지 사이에 접속된 제1의 스위치를 가지며, 제1, 제2, 제3의 정전류원의 온 오프와 제1의 스위치의 개방, 단락을 제어하는 수단을 가지는 것이다.

또한, 상기 목적을 달성하기 위한 다른 구성으로서, 본 발명의 PLL 회로에 있어서, 제2의 정전류원을 전류 출력형 위상 비교기의 출력단과 전원 전위 사이에 접속된 제2의 스위치로 치환하여, 제2의 스위치의 온 오프를 제어하는 수단을 추가하는 것이다.

또한, 상기 목적을 달성하기 위한 다른 구성으로서, 본 발명의 PLL 회로에 있어서, 제1과 제2의 정전류원을 가변 전류원으로 치환하여, 가변 전류원의 온 오프와 출력 전류치를 제어하는 수단을 추가하는 것이다.

또한, 본 발명의 무선 통신 단말 기기는, 기저 대역 회로와, 기저 대역 회로로부터 제1의 기저 대역 신호가 입력되는 변조기와, 변조기의 출력에 접속된 PLL 회로와, PLL 회로의 출력에 접속된 전력 증폭기와, 기저 대역 회로에 제2의 기저 대역 신호를 출력하는 수신 회로와, 안테나와, 안테나와 수신 회로의 입력과, 전력 증폭기의 출력이 접속되는 안테나 스위치를 가지고, 기저 대역 회로는 무선 통신 단말기의 동작의 제어 신호를 출력하는 무선 통신 단말 기기에 있어서, PLL 회로가, 상기 기재의 PLL 회로로 이루어진 것을 특징으로 하는 것이다. 또한, 셀렉터는 안테나 스위치 혹은 듀플렉서이다.

이하, 본 발명의 실시의 형태를 도면을 이용해서 상세히 설명한다. 또한, 실시의 형태를 설명하기 위한 도면에 있어서, 동일 부재에는 동일의 부호를 붙여, 그 반복의 설명은 생략한다. 또한, 종래의 기술에서 설명한 내용과 중복되는 부분에 대한 설명도 생략한다.

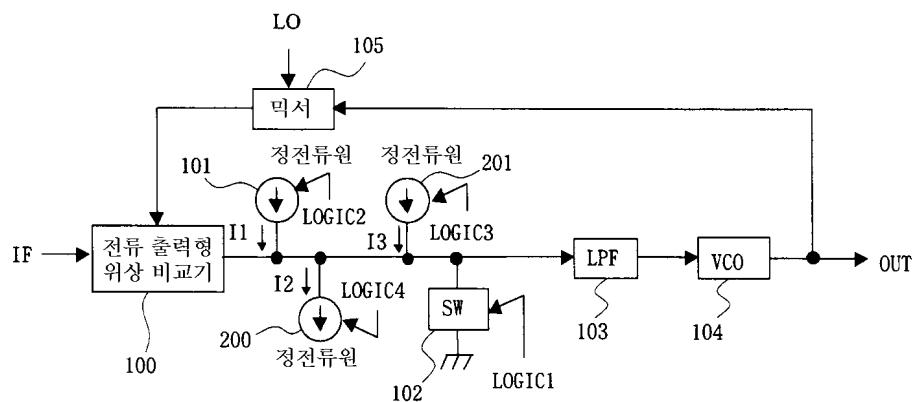

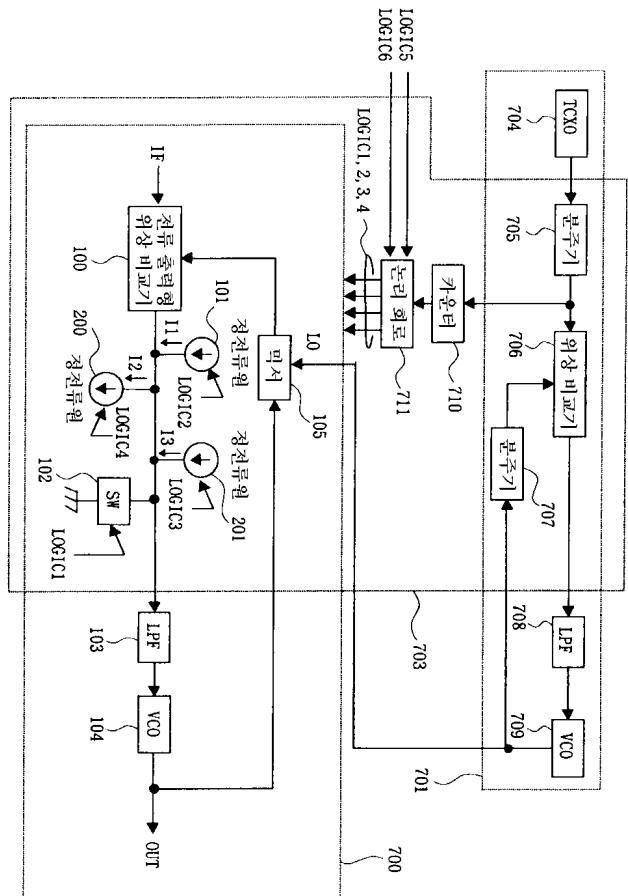

도 1은, 본 발명의 PLL 회로의 제1의 실시의 형태를 도시한 구성도이다.

본 발명에 관한 PLL 회로는, 전류 출력형 위상 비교기(100)와, 정전류원(101, 200, 201)과, 믹서(105)와, LPF(103)와, VCO(104)와, SW(102)로 구성된다. 정전류원(101)과 (200)의 출력 전류는 같은 값이다( $I_1=I_2$ ). 또한, 정전류원(201)의 출력 전류  $I_3$ 은, 정전류원(101)과 (200) 보다도 큰 값, 예를들면 50배의 값이다. 이하의 설명에 있어서, VCO(104)는 플러스의 감도를 가지는 것으로 가정한다. SW(102)에는 제어 신호 LOGIC(1)가 제공된다. LOGIC(1)이 0인 경우에 SW(102)는 개방 상태로 되어, LOGIC(1)이 1인 경우에 SW(102)는 접지로 단락된다. 또한, 정전류원(101, 200, 201)에는 각각 제어 신호 LOGIC(2, 3, 4)가 제공된다. LOGIC(2, 3, 4)이 0인 경우에 LOGIC이 입력되는 정전류원은 각각 오프되어, 1인 경우에 각각 온이 된다.

전류 출력형 위상 비교기(100), 믹서(105), SW(102), LPF(103), VCO(104)의 동작은, 상술의 종래의 PLL 회로와 같다.

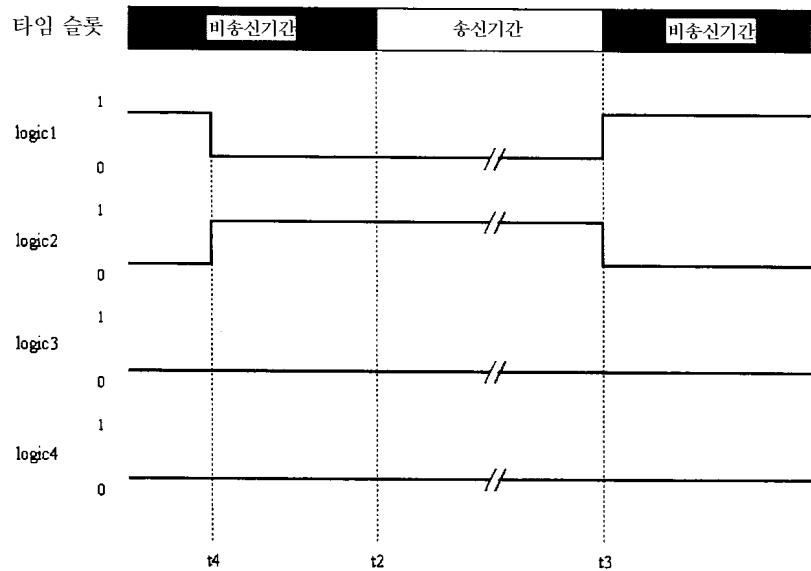

PLL 회로에는 2개의 동작 모드가 있다. 동작 모드의 한 예를 도 2, 3, 4, 5 및 6을 이용해서 설명한다. 도 2는, 정전류원(200, 201)을 이용하지 않는 동작 모드(1)의 타이밍 차트이다. 비송신 기간의 시각  $t_4$ 에 있어서, LOGIC(1)을 1에서 0으로 해서 SW(102)를 단락 상태로부터 개방 상태로 한다. 또한, LOGIC(2)를 0에서 1로 해서 정전류원(101)을 오프에서 온으로 한다. LOGIC(3, 4)은 항상 0이고, 정전류원(200, 201)은 항상 오프로 한다. 동작 모드(1)에 있어서의 PLL 회로의 동작은, 상술의 종래의 PLL 회로의 동작과 같고, 수렴 주파수가 높은 수록 수렴 시간이 길게 된다. 송신 기간이 종료하면, LOGIC(1)은 0에서 1로 하여 SW(102)를 개방 상태로부터 단락 상태로 한다. 또한, LOGIC(2)는 1에서 0으로 해서 정전류원(101)은 온에서 오프로하여, 다음의 송신 기간에 대비한다.

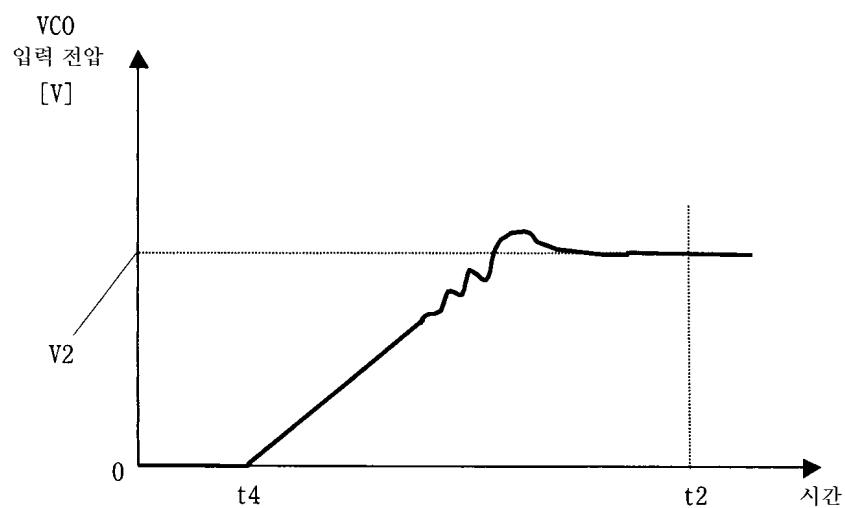

도 3은, 동작 모드(1)에 있어서의 VCO(104)의 입력 전위의 변화를 도시한 한 예이다. 수렴 과정은 종래의 PLL 회로와 마찬가지이다.

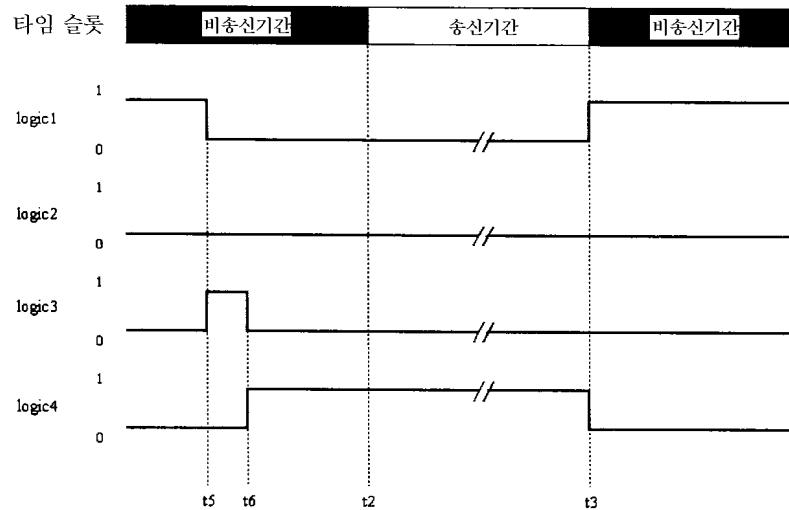

도 4는, 정전류원(101)을 이용하지 않은 동작 모드(2)의 타이밍 차트이다. LOGIC(2)은 항상 0으로서, 정전류원(101)을 항상 오프로 한다. 비송신 기간의 시각 t5에 있어서, LOGIC(1)을 1에서 0으로 하여 SW(102)를 단락 상태로부터 개방상태로 한다. 또한, LOGIC(3)을 0에서 1로 해서 정전류원(201)을 오프에서 온으로 한다. 정전류원(201)의 출력 대전류에 의해 LPF(103)의 용량이 고속 충전되어 VCO(104)의 입력 전위가 최대 전위까지 급상승한다. 이 최대 전위는, 정전류원(201)의 전원 전압에 의해서 결정된다. 그 후, 시각 t6에 있어서 LOGIC(3)을 1에서 0으로 해서, 정전류원(201)을 온에서 오프로 한다. 또한, LOGIC(4)를 0에서 1로 해서, 정전류원(200)을 오프에서 온으로 한다. 정전류원(200)에 의해서 LPF(103)에 축적된 전하가 방전되어, VCO(104)의 입력 전위는 최대 전위로부터 하강되어 가고, 최종적으로 수렴 주파수에 수렴한다. 이 경우, 수렴 주파수가 높은 수록 수렴 시간이 짧게 된다. 송신 기간이 종료하면, LOGIC(1)은 0에서 1로 하여 SW(102)를 개방 상태로부터 단락 상태로 한다. 또한, LOGIC(4)는 1에서 0으로 하여 정전류원(200)을 온에서 오프로 하여, 다음의 송신 기간에 대비한다.

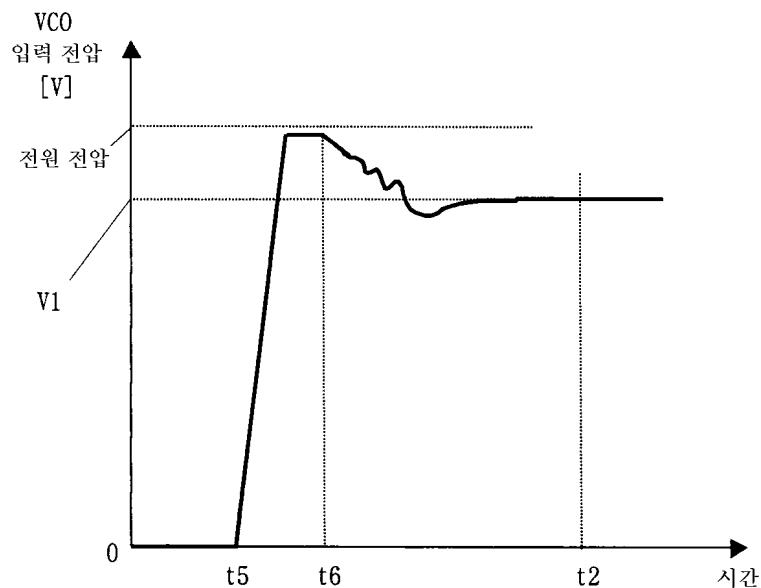

도 5는, 동작 모드(2)에 있어서의 VCO(104)의 입력 전위의 변화를 도시한 한 예이다. 시각 t5까지는, 입력 전위는 0V이다. 시각 t5에 SW(102)가 개방되고, 입력 전위가 직선적으로 상승을 시작한다. 상승의 기울기는, 주로 정전류원(201)의 출력 전류 I3과, LPF(103)의 총용량 C에 의해 결정되며, I3/C에서 주어진다. 상술과 같이 I3은 I1의, 예를들면 50배로 크기 때문에, 상승의 기울기는 동작 모드(1)에 서의 I1에 의해서 결정되는 기울기 I1/C의 50배가 된다. 즉, 매우 급속히 입력 전위가 최대 전위까지 상승한다. 시각 t6이 되면, 정전류원(201)이 오프되어 정전류원(200)이 동작을 시작한다. 정전류원(200)에 의해 입력 전위는 직선적으로 하강을 시작한다. 하강의 기울기는, 주로 정전류원(200)의 출력 전류 I2와, C에 의해 결정되어, I2/C로 부여된다. 그 후, PLL 회로는 피드백을 회복해서 수렴을 완료한다. 동작 모드(1)에서의 수렴 시간 ts1은, 종래의 PLL 회로와 같은 주어진다. 동작 모드(2)에서의 수렴 시간 ts2은,  $td=t6-t5$ , 입력 전위가 최대 전위일 때의 VCO(104)의 출력 주파수를 f2로 하면 수학식 3으로 주어진다.

### 수학식 3

$$ts2 = (f2 - f1) / Kv \cdot C/I2 + td$$

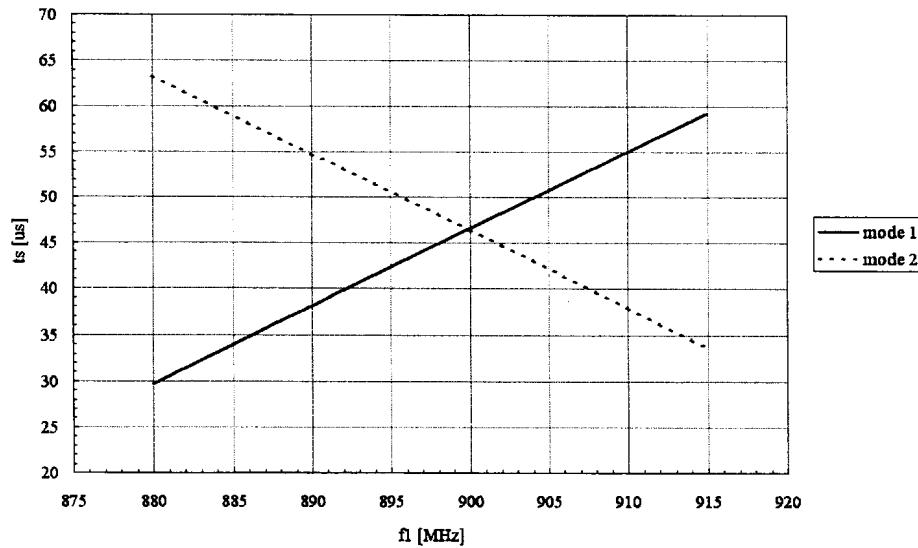

도 6는,  $Kv=35\text{MHz/V}$ ,  $C=16\text{nF}$ ,  $I1=I2=0.54\text{mA}$ ,  $f0=845\text{MHz}$ ,  $f2=943\text{MHz}$ ,  $td=10\mu\text{s}$ 의 경우의, 수렴 시간 ts의 수렴 주파수 f1의 존성을 동작 모드(1, 2)에 대해서 도시한 것이다. GSM 시스템의 경우를 상정해서, f1은  $880\text{MHz}$ 에서  $915\text{MHz}$ 로 계산을 하였다. 또한, 수렴 시간의 계산에는, 수학식 2와 3을 이용한다. 도면으로부터 알 수 있듯이, 동작 모드(1)만을 이용하는 종래의 PLL 회로의 최대 수렴 시간은 약  $60\mu\text{s}$ 이다. 그러나, f1이  $900\text{MHz}$  이하에서는 동작 모드(1)을,  $900\text{MHz}$  이상으로는 동작 모드(2)를 이용하면, 최대 수렴 시간은 약  $47\mu\text{s}$ 로 단축할 수 있다.

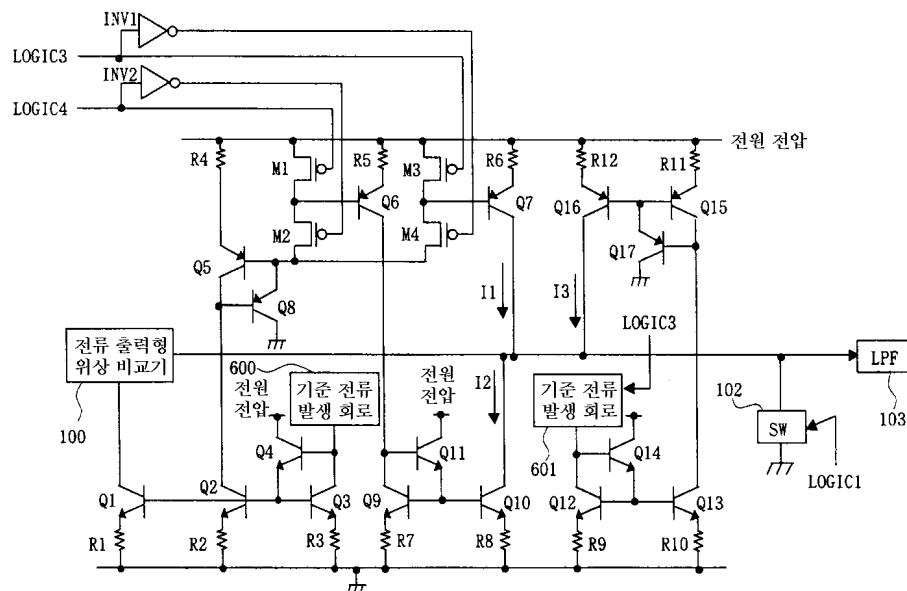

도 7은, 정전류원(101, 200, 201)의 실시예를 도시하는 회로도이다. 그 회로는, 기준 전류 발생 회로(600, 601), 5개의 전류 미로 회로, PMOS 트랜지스터(M1-M4) 및 인버터(INV1, INV2)로 구성된다. 5개의 전류 미로 회로는 각각 (Q1-Q4, R1-R3), (Q5-Q8, R4-R6), (Q9-Q11, R7, R8), (Q12-Q14, R9, R10), (Q15-Q17, R11, R12)로 구성된다. 기준 전류 발생 회로(600, 601)는, 밴드캡 리퍼런스(BGR) 회로에서 발생하는 온도 보상된 기준 전위에서 정전류를 생성해서 출력하는 회로이다.

기준 전류 발생 회로(600)의 출력 전류로부터, 도 1의 I1과 I2가 생성된다. 또한, 기준 전류 발생 회로(601)로부터는 I3이 생성된다. I1, I2의 온 오프 제어는, (M1-M4, INV1, INV2)로 이루어지는 스위치 회로에 의해서 실현된다. 예를들면, LOGIC(3)이 1의 경우, M3의 소스-드레인 사이는 오픈이 되어, M4의 소스-드레인 사이는 쇼트된다. 따라서, Q5와 Q7의 베이스 사이가 쇼트되기 때문에 Q7의 콜렉터로부터 I1이 출력된다. LOGIC(3)이 0인 경우는, Q7의 베이스가 전원 전압으로 되기 때문에 Q7의 콜렉터 전류는 거의 0이 된다. I3의 온 오프 제어는, 기준 전류 발생 회로(601)의 온 오프에 의해서 행해진다.

전류 출력형 위상 비교기(100)의 바이어스 전류도 또한, 기준 전류 발생 회로(600)으로부터 생성된다. 상술과 같이, 전류 출력형 위상 비교기(100)의 출력 전류와 I1, I2의 비에 의해서 PLL 회로의 수렴 안정성을 결정한다. I1, I2 및 그 바이어스 전류를 동일한 기준 전류로부터 생성하는 것으로, 그 출력 전류와 I1, I2의 비의 변동을 저감할 수 있다.

예를들면, 도 7에 있어서, LOGIC(3)에서 제어되는 I3은 I1, I2에 비해서 8배의 전류가 흐른다. 이 8배는, 전류 미리 회로의 에미터 저항비에 기준 전류원으로부터 출력되는 전류치를 건 것의 비이다. 구체적으로는,  $(R11/R12) \times (R9/R10) \times 601$ 이 발생하는 전류치와,  $(R4/R6) \times (R2/R3) \times 600$ 이 발생하는 전류치의 비가 8:1로 되어 있다.

이상과 같은 구성에 있어서,  $0.35\mu\text{m}$  BiCMOS 프로세스를 이용한 예로는, 상기 종래의 PLL 회로에 비해 약 6%의 회로 면적의 증가만으로 본 발명에 관한 PLL 회로의 제1의 실시의 형태를 실현되어 있다.

도 8은, LOGIC(1, 2, 3, 4)의 생성 회로의 실시예를 도시하는 회로도이다. 그 회로는, 제1의 실시의 형태의 PLL 회로(700)와, 제1의 실시의 형태의 맵서(105)에 입력되는 LO 신호를 생성하기 위한 PLL 회로(701)와, 카운터(710)와, 논리 회로(711)로 구성된다. 또한, PLL 회로(701)는, 온도 보상형 수정 발진기 (TXCO) (704)와, 분주기(705, 707)와, 위상 비교기(706)와, LPF(708)와, VCO(709)로 구성된다. 점선(703)으로 둘러싸인 회로는 동일 IC 내에 제조된 회로이다. TCXO (704)는, 온도 보상된 주파수 정밀도가 높은 기준 신호원으로서 이용되어, 예를들면,  $13\text{MHz}$ 의 신호를 출력한다. 분주비는, 예를들면  $1/65$ 로,  $200\text{MHz}$ 의 신호를 출력한다. 분주기(705)의 출력 신호가 카운터(710)에 입력되기 때문에, 카운터(710)의 입력과 출력의 사이에는, 분주기(705)의 출력 신호의 주기의 정수배의 지연이 생긴다. 따라서, 그 지연을 이용하여 도 4에 있어서의 t5에서 t6으로의 지연을 실현할 수 있다. 논리 회로(711)는, 카운터(710)의 출력 신호와 그 IC 외부에서 입력되는 LOGIC(5, 6)으로부터 LOGIC(1, 2, 3, 4)를 생성하여, PLL 회로(700)로 출력한다. LOGIC(5)은 도 2, 4에 있어서의 t4, t5를 결정하기 위한 신호이고, LOGIC(6)은, 상술의 동작 모드를 결정하기 위한 신호이다.

다음에, 본 발명에 관한 PLL 회로의 제2의 실시의 형태를 설명한다.

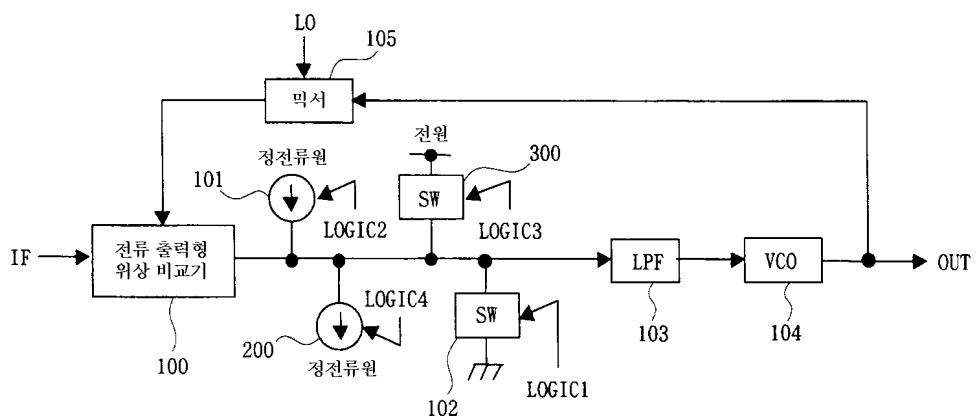

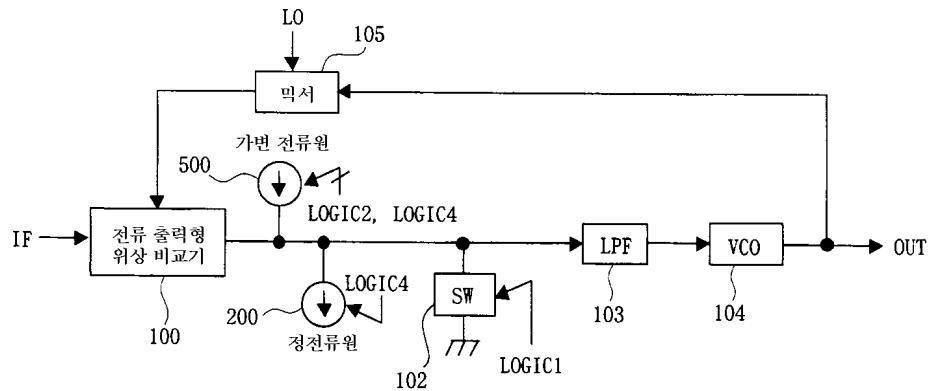

도 9는, 본 발명의 PLL 회로의 제2의 실시의 형태를 도시한 구성도이다. 그 PLL 회로는, 제1의 실시의 형태에 있어서, 정전류원(201)을 전원 전압에 접속된 SW(300)로 치환한 것을 특징으로 하는 회로이다. SW(300)와 LOGIC IC(3) 이외의 회로의 동작은 제1의 실시의 형태와 같다. SW(300)는, 도 4의 시각 t5에서 t6의 사이에만 온으로 된다. 이에 따라, LPF (103)의 입력 단자와 전원이 단락되어, LPF(103)의 용량이 전원으로부터의 전류로 최대 전위까지 고속 충전된다.

다음에, 본 발명에 관한 PLL 회로의 제3의 실시의 형태를 설명한다.

도 10은, 본 발명의 PLL 회로의 제3의 실시의 형태를 도시한 구성도이다. 그 PLL 회로는, 제1의 실시의 형태에 있어서, 정전류원(101, 102)을 가변 전류원(500)으로 치환한 것을 특징으로 하는 회로이다. 가변 전류원(500)은, LOGIC(2, 4)에 의해 온 오프 제어와 출력 전류치 제어가 가능하다. 가변 전류원(500), LOGIC(2, 4)에 의해, 제1의 실시의 형태의 정전류원 (101, 201)과 LOGIC(2, 3)과 같은 기능을 실현한다.

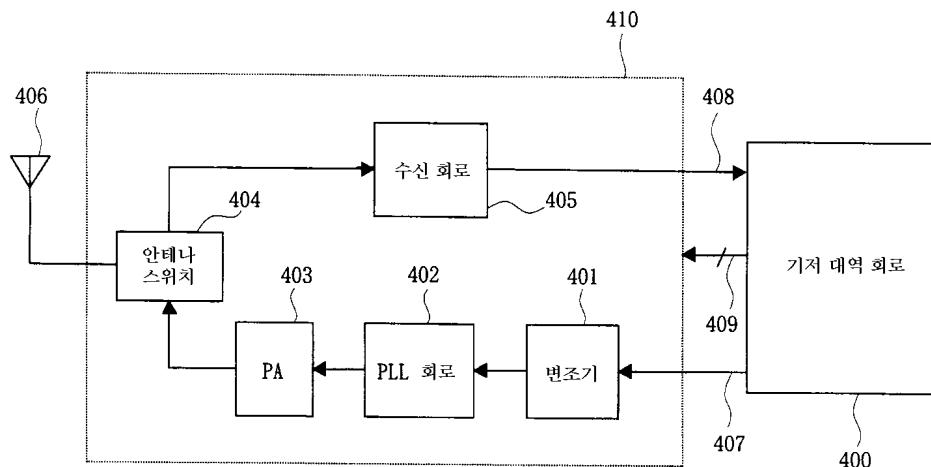

본 발명에 관한 무선 통신 단말기기의 한 예를 도 11에 도시한다. 이 무선 통신 단말 기기는, 기저 대역 회로(400)와, 변조기(401)와, 본 발명에 관한 PLL 회로(402)와, 전력 증폭기(PA)(403)로 구성되는 송신계와, 안테나 스위치(404)와, 안테나(406)와, 수신 회로(405)로 구성된다.

기저 대역 회로(400)는, 음성 신호와 데이터 신호에 기초해서 변조기(401)에 기저 대역 신호(407)를 출력하여, 수신회로 (405)로부터 입력되는 기저 대역 신호(408)에 기초해서 음성 신호와 데이터 신호를 재생한다. 또한, 이 무선 통신 단말기기는 구성하는 회로(410)를 제어하기 위한 제어 신호(409)를 출력한다. 변조기(401)에 있어서, 기저 대역(407)에 기초해서 IF 대의 변조 신호가 생성된다. 변조기(401)의 출력 신호는 PLL 회로(402)에 입력되어, 주파수 변환이 실시된 후, PA (403)에 출력된다. PA(403)에 있어서, 신호는 전력이 증폭되어, 안테나 스위치(404)를 통해서 안테나(406)로부터 송신된다. 안테나 스위치(404)에 의해, 송신 시에는 안테나(406)와 PA(403)가 접속되고, 수신 시에는 안테나(406)와 수신 회로 (405)가 접속된다. 안테나(406)로 수신된 신호는, 수신 회로(405)에 입력되고, 복조가 행해져, 기저 대역 신호(408)가 출력된다.

따라서, 본 실시의 형태에 의하면, PLL 회로의 전류 출력형 위상 비교기(100)의 출력에, LPF(103) 출전용의 정전류원 (101)과, 방전용의 정전류원(200)과 고속 충전용의 정전류원(201)을 접속함으로서, PLL 회로의 수렴 주파수가 낮은 경우에는 정전류원(101)을 이용해서 VCO(104)의 입력 전위를 OV에서부터 상승시켜서 수렴시키고, 수렴 주파수가 높은 경우에는 정전류원(201)을 이용해서 입력 전위를 일단 최대 단위로 하고, 그 후, 정전류원(200)을 이용해서 입력 전위를 최대 전위로부터 하강시켜서 수렴시키는 바와 같이, 수렴 주파수에 의해 상기 동작을 선택함으로써, PLL 회로의 최대 수렴 시간을 단축할 수 있다.

이상, 본 발명자에 의해서 이루어진 발명을 그 실시의 형태에 기초해서 구체적으로 설명했지만, 본 발명은 상기 실시의 형태에 제한된 것이 아니고, 그 요지를 벗어나지 않는 범위내에서 당연히 여러 가지로 변경할 수 있다.

## 발명의 효과

본 출원에 있어서 개시된 발명 안에, 대표적인 것에 의해서 얻어지는 효과를 간단히 설명하면, 다음과 같다.

본 출원에 의하면, 종래의 PLL 회로에 2개의 정전류원을 추가하는 것만으로, 최대 수렴 시간을 약 절반으로 단축할 수 있는 효과가 있다.

### 도면의 간단한 설명

도 1은 본 발명의 PLL 회로의 제1의 실시의 형태를 도시하는 구성도.

도 2는 본 발명의 PLL 회로의 동작 모드(1)를 도시하는 타이밍 차트.

도 3은 본 발명의 PLL 회로의 동작 모드(1)에 있어서의 VCO 입력 전위를 도시하는 특성도.

도 4는 본 발명의 PLL 회로의 동작 모드(2)를 도시하는 타이밍 차트.

도 5는 본 발명의 PLL 회로의 동작 모드(2)에 있어서의 VCO 입력 전위를 도시하는 특성도.

도 6은 본 발명과 종래의 PLL 회로의 수렴 시간 비교를 도시하는 특성도.

도 7은 본 발명의 PLL 회로의 정전류원의 실시예를 도시하는 회로도.

도 8은 본 발명의 PLL 회로의 LOGIC의 생성 회로의 실시예를 도시하는 회로도.

도 9는 본 발명의 PLL 회로의 제2의 실시의 형태를 도시하는 구성도.

도 10은 본 발명의 PLL 회로의 제3의 실시의 형태를 도시하는 구성도.

도 11은 본 발명의 PLL 회로를 이용한 무선 통신 단말기기의 한 예를 도시하는 구성도.

도 12는 종래의 PLL 회로를 도시하는 구성도.

도 13은 GSM 시스템용 무선 통신 단말 기기의 송수신 타이밍을 도시하는 설명도.

도 14는 종래의 PLL 회로의 동작을 도시하는 타이밍 차트.

도 15는 종래의 PLL 회로의 VCO 입력 전위를 도시하는 특성도.

도 16은 GPRS 시스템용 무선 통신 단말 기기의 송수신 타이밍을 도시하는 설명도.

<도면의 주요부분에 대한 부호의 설명>

100 : 전류 출력형 위상 비교기

101, 200, 201 : 정전류원

102, 300 : 스위치(SW)

103 : 저역 통과 필터(LPF)

104 : 전압 제어 발진기(VCO)

105 : 믹서

400 : 기저 대역 회로

401 : 변조기

402 : PLL 회로

403 : 전력 증폭기(PA)

404 : 안테나 스위치

405 : 수신 회로

406 : 안테나

407, 408 : 기저 대역 신호

409 : 제어 신호

500 : 가변 전류원

도면

도면1

## 도면2

## 도면3

## 도면4

## 도면5

도면6

도면7

## 도면8

## 도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16