(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7371344号**

**(P7371344)**

(45)発行日 令和5年10月31日(2023.10.31)

(24)登録日 令和5年10月23日(2023.10.23)

(51)国際特許分類

|        |                  |        |       |   |

|--------|------------------|--------|-------|---|

| H 03 B | 5/32 (2006.01)   | H 03 B | 5/32  | H |

| H 01 L | 21/822 (2006.01) | H 01 L | 27/04 | A |

| H 01 L | 27/04 (2006.01)  | H 01 L | 27/04 | E |

|        |                  | H 01 L | 27/04 | U |

|        |                  | H 01 L | 27/04 | H |

請求項の数 13 (全34頁) 最終頁に続く

(21)出願番号 特願2019-69775(P2019-69775)

(22)出願日 平成31年4月1日(2019.4.1)

(65)公開番号 特開2020-170885(P2020-170885)

A)

(43)公開日 令和2年10月15日(2020.10.15)

審査請求日 令和4年2月21日(2022.2.21)

(73)特許権者 000002369

セイコーホームズ株式会社

東京都新宿区新宿四丁目1番6号

(74)代理人 100104710

弁理士 竹腰 昇

(74)代理人 100090479

弁理士 井上 一

(74)代理人 100124682

弁理士 黒田 泰

(74)代理人 100166523

弁理士 西河 宏晃

(74)代理人 100187539

弁理士 藍原 由和

(72)発明者 澤田 光章

長野県諏訪市大和3丁目3番5号 セイ

最終頁に続く

(54)【発明の名称】 集積回路装置、発振器、電子機器及び移動体

**(57)【特許請求の範囲】****【請求項1】**

振動子の一端に電気的に接続される第1パッドと、

前記振動子の他端に電気的に接続される第2パッドと、

前記第1パッド及び前記第2パッドに電気的に接続され、前記振動子を発振させることで発振信号を生成する発振回路と、

前記発振信号に基づいてクロック信号を出力する出力回路と、

温度センサーからの温度検出信号に基づいて、前記発振回路の発振周波数の温度補償を行う温度補償回路と、

電源電圧が供給される電源パッドと、

前記電源電圧に基づいて第1レギュレーター電源電圧を生成して、前記温度補償回路に供給する第1レギュレーターと、

前記電源電圧に基づいて第2レギュレーター電源電圧を生成して、前記発振回路に供給する第2レギュレーターと、

前記電源パッドと前記第1レギュレーターとを接続し、前記電源電圧を前記第1レギュレーターに供給する第1電源線と、

前記第1電源線とは分離して設けられ、前記電源パッドと前記第2レギュレーターとを接続し、前記電源電圧を前記第2レギュレーターに供給する第2電源線と、

を含み、

前記発振回路は、集積回路装置の第1辺、前記第1辺に交差する第2辺、前記第1辺の

10

20

対辺である第3辺及び前記第2辺の対辺である第4辺のうちの前記第1辺に沿って配置され、

前記第1パッド及び前記第2パッドは、平面視において、前記第1辺に沿って前記発振回路内に配置され、

前記第1辺から前記第3辺に向かう方向を第1方向としたときに、前記温度補償回路は、前記発振回路の前記第1方向に配置され、前記第1レギュレーターは、前記温度補償回路の前記第1方向に配置され、

前記第2レギュレーター、前記電源パッド及び前記出力回路は、前記第2辺に沿って配置され、

前記第2レギュレーターは、前記第1レギュレーターに比べて前記電源パッドの近くに配置され、

前記第1電源線の配線幅は前記第2電源線の配線幅よりも細いことを特徴とする集積回路装置。

#### 【請求項2】

請求項1に記載の集積回路装置において、

グランド電圧が供給されるグランドパッドを含み、

前記グランドパッド及び前記第1レギュレーターは、前記第3辺に沿って配置されることを特徴とする集積回路装置。

#### 【請求項3】

請求項2に記載の集積回路装置において、

前記第1レギュレーターに基準電圧を供給する基準電圧生成回路を含み、

前記基準電圧生成回路は、前記グランドパッドと前記第1レギュレーターとの間に配置されることを特徴とする集積回路装置。

#### 【請求項4】

請求項1乃至3のいずれか一項に記載の集積回路装置において、

前記出力回路は、前記第2辺と前記第3辺とが交差するコーナー部に配置されることを特徴とする集積回路装置。

#### 【請求項5】

請求項1乃至4のいずれか一項に記載の集積回路装置において、

前記温度補償回路を制御する制御回路を含み、

前記制御回路は、前記第2辺から前記第4辺に向かう方向を第2方向としたときに、前記温度補償回路の前記第2方向に配置されることを特徴とする集積回路装置。

#### 【請求項6】

請求項1乃至4のいずれか一項に記載の集積回路装置において、

前記温度センサーは、前記第2辺から前記第4辺に向かう方向を第2方向としたときに、前記発振回路の前記第2方向に配置されることを特徴とする集積回路装置。

#### 【請求項7】

請求項6に記載の集積回路装置において、

前記温度センサーは、前記第1辺と前記第4辺が交差するコーナー部に配置されることを特徴とする集積回路装置。

#### 【請求項8】

請求項1乃至7のいずれか一項に記載の集積回路装置において、

前記クロック信号を出力するクロックパッドを含み、

前記クロックパッドは、前記出力回路内に配置されることを特徴とする集積回路装置。

#### 【請求項9】

請求項1乃至8のいずれか一項に記載の集積回路装置において、

前記発振回路は、前記第1辺に沿った方向を長手方向として配置されることを特徴とする集積回路装置。

#### 【請求項10】

請求項1乃至9のいずれか一項に記載の集積回路装置において、

10

20

30

40

50

前記出力回路は、前記第2辺に沿った方向を長手方向として配置されることを特徴とする集積回路装置。

【請求項11】

請求項1乃至10のいずれか一項に記載の集積回路装置と、

前記振動子と、

を含むことを特徴とする発振器。

【請求項12】

請求項1乃至10のいずれか一項に記載の集積回路装置と、

前記クロック信号により動作する処理装置と、

を含むことを特徴とする電子機器。

10

【請求項13】

請求項1乃至10のいずれか一項に記載の集積回路装置と、

前記クロック信号により動作する処理装置と、

を含むことを特徴とする移動体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路装置、発振器、電子機器及び移動体等に関する。

【背景技術】

【0002】

20

従来より、水晶振動子等の振動子を発振させる発振回路を有する集積回路装置が知られている。特許文献1には、このような集積回路装置のレイアウト配置について開示されている。特許文献1には、振動子が接続されるパッドや、電源が供給されるパッドや、電源線のレイアウト配置手法について開示されている。特許文献1の集積回路装置では、集積回路装置の対向する2つの辺のそれぞれに、振動子に接続される2つのパッドのそれぞれが配置されている。これらの2つのパッドはXエパッド、Xオパッドとも呼ばれる。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2018-98428号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0004】

振動子に接続される2つのパッド間の距離が遠くなると、これらのパッドと発振回路を接続する信号線の配線長が長くなってしまう。このようにパッドと発振回路を接続する信号線の配線長が長くなると、信号線の寄生抵抗や寄生容量が増加し、発振特性を劣化させてしまうおそれがある。また高周波信号経路で発生する放射ノイズ等のノイズについては低減することが望ましい。

【課題を解決するための手段】

【0005】

40

本発明の一態様は、振動子の一端に電気的に接続される第1パッドと、前記振動子の他端に電気的に接続される第2パッドと、前記第1パッド及び前記第2パッドに電気的に接続され、前記振動子を発振させることで発振信号を生成する発振回路と、前記発振信号に基づいてクロック信号を出力する出力回路と、を含み、前記発振回路は、集積回路装置の第1辺、前記第1辺に交差する第2辺、前記第1辺の対辺である第3辺及び前記第2辺の対辺である第4辺のうちの前記第1辺に沿って配置され、前記第1パッド及び前記第2パッドは、平面視において、前記第1辺に沿って前記発振回路内に配置され、前記出力回路は、前記第2辺に沿って配置される集積回路装置に係する。

【図面の簡単な説明】

【0006】

50

- 【図 1】本実施形態の集積回路装置の構成例。

- 【図 2】本実施形態の集積回路装置の詳細な構成例。

- 【図 3】集積回路装置のレイアウト配置例。

- 【図 4】集積回路装置での電流経路を示す模式図。

- 【図 5】集積回路装置での高周波信号の信号経路を示す模式図。

- 【図 6】集積回路装置の他のレイアウト配置例。

- 【図 7】発振回路の構成例。

- 【図 8】出力回路の構成例。

- 【図 9】L V D S のドライバー回路の説明図。

- 【図 10】P E C L のドライバー回路の説明図。 10

- 【図 11】H C S L のドライバー回路の説明図。

- 【図 12】C M O S のドライバー回路の説明図。

- 【図 13】L V D S の差動出力信号の信号波形例。

- 【図 14】P E C L の差動出力信号の信号波形例。

- 【図 15】発振回路、出力回路で発生するノイズの説明図。

- 【図 16】レギュレーターの構成例。

- 【図 17】レギュレーターの他の構成例。

- 【図 18】基準電圧生成回路の構成例。

- 【図 19】温度センサーの構成例。

- 【図 20】温度補償回路の構成例。 20

- 【図 21】発振器の第 1 の構造例。

- 【図 22】発振器の第 2 の構造例。

- 【図 23】電子機器の構成例。

- 【図 24】移動体の構成例。

- 【発明を実施するための形態】

- 【0 0 0 7】

- 以下、本実施形態について説明する。なお、以下に説明する本実施形態は、特許請求の範囲の記載内容を不当に限定するものではない。また本実施形態で説明される構成の全てが必須構成要件であるとは限らない。

- 【0 0 0 8】 30

1. 集積回路装置

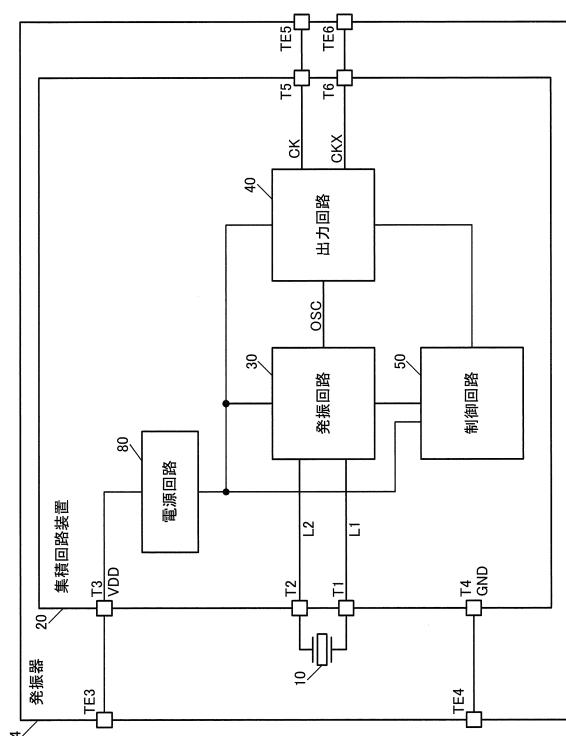

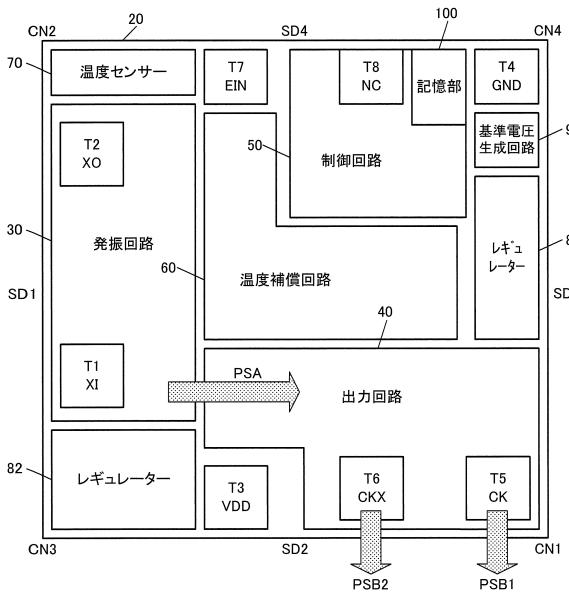

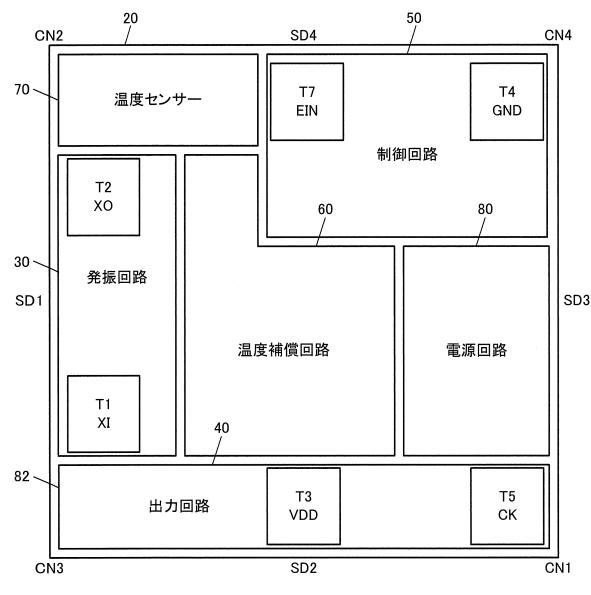

- 図 1 に本実施形態の集積回路装置 20 の構成例を示す。本実施形態の集積回路装置 20 は、パッド T 1、T 2 と発振回路 30 と出力回路 40 を含む。また本実施形態の発振器 4 は振動子 10 と集積回路装置 20 を含む。振動子 10 は集積回路装置 20 に電気的に接続されている。例えば振動子 10 及び集積回路装置 20 を収納するパッケージの内部配線、ボンディングワイヤー又は金属バンプ等を用いて、振動子 10 と集積回路装置 20 は電気的に接続されている。

- 【0 0 0 9】

- 振動子 10 は、電気的な信号により機械的な振動を発生する素子である。振動子 10 は、例えば水晶振動片などの振動片により実現できる。例えば振動子 10 は、カット角が A T カットや S C カットなどの厚みすべり振動する水晶振動片などにより実現できる。例えば振動子 10 は、恒温槽を備えない温度補償型水晶発振器 (T C X O) に内蔵されている振動子であってもよいし、恒温槽を備える恒温槽型水晶発振器 (O C X O) に内蔵されている振動子であってもよい。なお本実施形態の振動子 10 は、例えば厚みすべり振動型以外の振動片や、水晶以外の材料で形成された圧電振動片などの種々の振動片により実現できる。例えば振動子 10 として、S A W (Surface Acoustic Wave) 共振子や、シリコン基板を用いて形成されたシリコン製振動子としてのM E M S (Micro Electro Mechanical Systems) 振動子等を採用してもよい。 40

- 【0 0 1 0】

- 集積回路装置 20 は、I C (Integrated Circuit) と呼ばれる回路装置である。例えば

- 50

集積回路装置 20 は、半導体プロセスにより製造される IC であり、半導体基板上に回路素子が形成された半導体チップである。

#### 【 0 0 1 1 】

集積回路装置 20 は、パッド T 1、T 2 と発振回路 30 と出力回路 40 を含む。また集積回路装置 20 は、電源パッド T 3 とグランドパッド T 4 とクロックパッド T 5、T 6 と制御回路 50 と電源回路 80 を含むことができる。パッドは集積回路装置 20 の端子である。例えばパッド領域では、絶縁層であるパッシベーション膜から金属層が露出しており、例えばこの露出した金属層によりパッドが構成される。

#### 【 0 0 1 2 】

パッド T 1 は、振動子 10 の一端に電気的に接続され、パッド T 2 は、振動子 10 の他端に電気的に接続される。例えば振動子 10 及び集積回路装置 20 を収納するパッケージの内部配線、ボンディングワイヤー又は金属バンプ等を用いて、振動子 10 と集積回路装置 20 のパッド T 1、T 2 は電気的に接続される。パッド T 1 は第 1 パッドであり、パッド T 2 は第 2 パッドである。パッド T 1、T 2 は信号線 L 1、L 2 を介して発振回路 30 に電気的に接続される。信号線 L 1、L 2 はパッド T 1、T 2 と発振回路 30 を接続する配線である。

10

#### 【 0 0 1 3 】

電源パッド T 3 は、電源電圧 VDD が供給されるパッドである。例えば外部の電源供給デバイスから電源パッド T 3 に電源電圧 VDD が供給される。グランドパッド T 4 は、グランド電圧である GND が供給されるパッドである。GND は VSS と呼ぶこともでき、グランド電圧は例えば接地電位である。本実施形態ではグランドを、適宜、GND と記載する。クロックパッド T 5、T 6 は、発振回路 30 の発振信号 OSC に基づき生成されたクロック信号 CK、CKX が出力されるパッドである。ここでは差動クロック信号を構成するクロック信号 CK、CKX が出力されている。クロック信号 CK、CKX は、差動クロック信号を構成する第 1 クロック信号、第 2 クロック信号と呼ぶことができる。なお差動ではないシングルエンドの CMOS やクリップドサイン波の信号形式でクロック信号が出力されてもよい。電源パッド T 3、グランドパッド T 4、クロックパッド T 5、T 6 は、各々、発振器 4 の外部接続用の外部端子 TE 3、TE 4、TE 5、TE 6 に電気的に接続される。例えばパッケージの内部配線、ボンディングワイヤー又は金属バンプ等を用いて電気的に接続される。そして発振器 4 の外部端子 TE 3、TE 4、TE 5、TE 6 は外部デバイスに電気的に接続される。

20

#### 【 0 0 1 4 】

発振回路 30 は振動子 10 を発振させる回路である。例えば発振回路 30 は、パッド T 1 及びパッド T 2 に電気的に接続され、振動子 10 を発振させることで発振信号 OSC を生成する。例えば発振回路 30 は、パッド T 1、T 2 に接続される信号線 L 1 及び信号線 L 2 を介して振動子 10 を駆動して、振動子 10 を発振させる。例えば発振回路 30 は、パッド T 1、T 2 との間に設けられた発振用の駆動回路などを含む。例えば発振回路 30 は、駆動回路を実現するバイポーラトランジスターなどのトランジスターと、キャパシターや抵抗などの能動素子により実現できる。駆動回路は、発振回路 30 のコア回路であり、駆動回路が、振動子 10 を電流駆動又は電圧駆動することで、振動子 10 を発振させる。発振回路 30 としては、例えばピアース型、コルピツ型、インバーター型又はハートレー型などの種々のタイプの発振回路を用いることができる。また発振回路 30 に、可変容量回路を設け、この可変容量回路の容量の調整により、発振周波数を調整できるようにしてもよい。可変容量回路は、バラクターなどの可変容量素子により実現できる。可変容量回路は、例えばパッド T 1 が接続される信号線 L 1 に電気的に接続される。発振回路 30 は、パッド T 1 が接続される信号線 L 1 に電気的に接続される第 1 可変容量回路と、パッド T 2 が接続される信号線 L 2 に電気的に接続される第 2 可変容量回路を有していてもよい。なお本実施形態における接続は電気的な接続である。電気的な接続は、電気信号が伝達可能に接続されていることであり、電気信号による情報の伝達が可能となる接続である。電気的な接続は能動素子等を介した接続であってもよい。

30

40

50

**【 0 0 1 5 】**

出力回路 4 0 は、発振回路 3 0 からの発振信号 O S C に基づいてクロック信号 C K 、 C K X を出力する。例えば出力回路 4 0 は、発振回路 3 0 からの発振信号 O S C をバッファリングしてクロック信号 C K 、 C K X を出力する。例えば出力回路 4 0 は、発振信号 O S C の波形整形、電圧レベルのレベルシフトなども行うことができる。出力回路 4 0 は、例えば種々の信号形式でクロック信号 C K 、 C K X を外部に出力することができる。例えば出力回路 4 0 は、 L V D S ( Low Voltage Differential Signaling ) 、 P E C L ( Positive Emitter Coupled Logic ) 、 H C S L ( High Speed Current Steering Logic ) 、又は差動の C M O S ( Complementary MOS ) などの信号形式で、クロック信号 C K 、 C K X を外部に出力する。例えば出力回路 4 0 は、 L V D S 、 P E C L 、 H C S L 及び差動の C M O S のうちの少なくとも 2 つの信号形式でクロック信号を出力可能な回路であってもよい。この場合には出力回路 4 0 は、制御回路 5 0 により設定された信号形式でクロック信号を出力することになる。なお出力回路 4 0 が出力するクロック信号の信号形式は、差動の信号形式には限定されず、例えばシングルエンドの C M O S やクリップドサイン波などの差動ではない信号形式であってもよい。この場合には、クロック信号 C K X の出力は不要になる。

10

**【 0 0 1 6 】**

制御回路 5 0 は種々の制御処理を行う。例えば制御回路 5 0 は集積回路装置 2 0 の全体の制御を行う。例えば集積回路装置 2 0 の動作シーケンスを制御する。また制御回路 5 0 は発振回路 3 0 の制御のための各種の処理を行う。また制御回路 5 0 は出力回路 4 0 や電源回路 8 0 の制御を行うこともできる。制御回路 5 0 は、例えばゲートアレイ等の自動配置配線による A S I C ( Application Specific Integrated Circuit ) の回路により実現できる。

20

**【 0 0 1 7 】**

電源回路 8 0 は、電源パッド T 3 からの電源電圧 V D D が供給されて、集積回路装置 2 0 の内部回路用の種々の電源電圧を内部回路に供給する。例えば電源電圧 V D D そのものを供給したり、外部からの電源電圧 V D D をレギュレートした電源電圧を供給する。なお図 1 の構成の場合に集積回路装置 2 0 は温度補償機能を有していないなくてもよい。この場合には発振器 4 は S P X O ( Simple Packaged Crystal Oscillator ) の発振器になる。

30

**【 0 0 1 8 】**

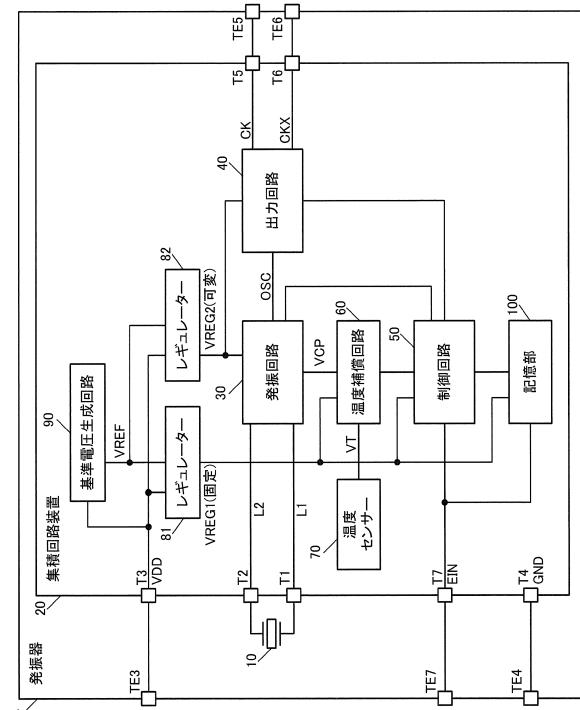

図 2 に集積回路装置 2 0 の詳細な構成例を示す。図 2 では図 1 の構成に加えて、温度補償回路 6 0 、温度センサー 7 0 、レギュレーター 8 1 、 8 2 、基準電圧生成回路 9 0 、記憶部 1 0 0 、パッド T 7 が更に設けられている。

**【 0 0 1 9 】**

温度センサー 7 0 は、温度を検出するセンサーである。具体的には温度センサー 7 0 は、環境の温度に応じて変化する温度依存電圧を、温度検出電圧 V T として出力する。例えば温度センサー 7 0 は、温度依存性を有する回路素子を利用して温度検出電圧 V T を生成する。具体的には温度センサー 7 0 は、 P N 接合の順方向電圧が有する温度依存性を用いることで、温度に依存して電圧値が変化する温度検出電圧 V T を出力する。 P N 接合の順方向電圧としては、例えばバイポーラトランジスターのベース・エミッター間電圧などを用いることができる。

40

**【 0 0 2 0 】**

温度補償回路 6 0 は、発振回路 3 0 の発振周波数の温度補償を行う。例えば温度補償回路 6 0 は、温度センサー 7 0 からの温度検出電圧 V T に基づいて温度補償電圧 V C P を生成し、温度補償電圧 V C P を発振回路 3 0 に出力することで、発振回路 3 0 の発振周波数の温度補償を行う。例えば温度補償回路 6 0 は、発振回路 3 0 が有する可変容量回路に対して、当該可変容量回路の容量制御電圧となる温度補償電圧 V C P を出力することで、温度補償を行う。温度補償は、温度変動による発振周波数の変動を抑制して補償する処理である。

**【 0 0 2 1 】**

50

例えば温度補償回路 60 は、多項式近似によるアナログ方式の温度補償を行う。例えば振動子 10 の周波数温度特性を補償する温度補償電圧 VCP が多項式により近似される場合に、温度補償回路 60 は、当該多項式の係数情報に基づいてアナログ方式の温度補償を行う。アナログ方式の温度補償は、例えばアナログ信号である電流信号や電圧信号の加算処理等により実現される温度補償である。例えば、高次の多項式により温度補償電圧 VCP が近似される場合、多項式の 0 次係数、1 次係数、高次係数が、それぞれ 0 次補正データ、1 次補正データ、高次補正データとして記憶部 100 に記憶される。例えば不揮発性メモリーにより実現される記憶部 100 に記憶される。高次係数は例えば 1 次より大きい高次の次数の係数であり、高次補正データは、高次係数に対応する補正データである。例えば 5 次多項式により温度補償電圧 VCP が近似される場合には、多項式の 0 次係数、1 次係数、2 次係数、3 次係数、4 次係数、5 次係数が、0 次補正データ、1 次補正データ、2 次補正データ、3 次補正データ、4 次補正データ、5 次補正データとして記憶部 100 に記憶される。そして温度補償回路 60 は、0 次補正データ～5 次補正データに基づいて温度補償を行う。なお、2 次補正データ又は 4 次補正データに基づく温度補償については省略してもよい。また多項式近似の次数は任意であり、例えば 3 次の多項式近似を行ったり、5 次よりも大きい次数の多項式近似を行うようにしてもよい。また 0 次補正を温度センサー 70 が行うようにしてもよい。また温度センサー 70 を集積回路装置 20 に設けずに、温度補償回路 60 が、外部から入力された温度検出電圧などの温度検出信号に基づいて温度補償を行うようにしてもよい。

#### 【0022】

制御回路 50 は温度補償回路 60 を制御する。また制御回路 50 は、発振回路 30、出力回路 40、レギュレーター 81、82 又は記憶部 100 の制御を行うともできる。例えば制御回路 50 はレジスターを有しており、振動子 10 を発振させてクロック信号 CK、CKX を出力する通常動作の開始時に、記憶部 100 に記憶された情報が読み出されて、制御回路 50 のレジスターに転送されて記憶される。そしてレジスターに記憶された情報に基づいて、種々の制御信号が生成され、集積回路装置 20 の各回路に出力されて、各回路が制御される。従って、通常動作時においては制御回路 50 は高速な動作を行う必要がないため、制御回路 50 が発生するノイズは低くなる。なお集積回路装置 20 は、温度補償がオンになる第 1 モードと、温度補償がオフになる第 2 モードを有していてもよい。この場合に制御回路 50 は、第 1 モードと第 2 モードの切り替え制御を行うことができる。

#### 【0023】

基準電圧生成回路 90 は、電源電圧 VDD に基づいて基準電圧 VREF を生成する。例えば電源電圧変動や温度変動があった場合にも定電圧となる基準電圧 VREF を生成する。基準電圧生成回路 90 は、例えばバンドギャップ電圧に基づき基準電圧 VREF を生成するバンドギャップリファレンス回路などにより実現できる。

#### 【0024】

レギュレーター 81 は、電源電圧 VDD に基づいてレギュレート電源電圧 VREG1 を生成する。レギュレーター 81 は第 1 レギュレーターであり、レギュレート電源電圧 VREG1 は第 1 レギュレート電源電圧である。例えばレギュレーター 81 は、電源パッド T3 からの電源電圧 VDD と基準電圧生成回路 90 からの基準電圧 VREF に基づいてレギュレート電源電圧 VREG1 を生成する。電源電圧変動や温度変動があった場合にも定電圧となる基準電圧 VREF を用いることで、VDD > VREG1 となる電源電圧であって、電源電圧変動や温度変動があった場合にも定電圧となるレギュレート電源電圧 VREG1 を生成できる。そしてレギュレーター 81 は、生成したレギュレート電源電圧 VREG1 を温度補償回路 60 に供給する。またレギュレーター 81 は、レギュレート電源電圧 VREG1 を制御回路 50 にも供給する。なおレギュレーター 81 とは別のレギュレーターを設けて、当該レギュレーターによりレギュレート電源電圧を制御回路 50 に供給してもよい。

#### 【0025】

レギュレーター 82 は、電源電圧 VDD に基づいてレギュレート電源電圧 VREG2 を

10

20

30

40

50

生成する。レギュレーター 8 2 は第 2 レギュレーターであり、レギュレート電源電圧 V R E G 2 は第 2 レギュレート電源電圧である。例えばレギュレーター 8 2 は、電源パッド T 3 からの電源電圧 V D D と基準電圧生成回路 9 0 からの基準電圧 V R E F に基づいてレギュレート電源電圧 V R E G 2 を生成する。電源電圧変動や温度変動があった場合にも定電圧となる基準電圧 V R E F を用いることで、V D D > V R E G 2 となる電源電圧であって、電源電圧変動や温度変動があった場合にも定電圧となるレギュレート電源電圧 V R E G 2 を生成できる。そしてレギュレーター 8 2 は、生成したレギュレート電源電圧 V R E G 2 を出力回路 4 0 に供給する。またレギュレーター 8 2 は、レギュレート電源電圧 V R E G 2 を発振回路 3 0 にも供給する。なおレギュレーター 8 2 とは別のレギュレーターを設けて、当該レギュレーターによりレギュレート電源電圧を発振回路 3 0 に供給してもよい。

#### 【 0 0 2 6 】

そしてレギュレーター 8 1 は、例えば固定電圧のレギュレート電源電圧 V R E G 1 を生成する。一方、レギュレーター 8 2 は、例えば電圧が可変に設定されるレギュレート電源電圧 V R E G 2 を生成する。例えば記憶部 1 0 0 が電圧設定情報を記憶し、レギュレーター 8 2 は、記憶部 1 0 0 に記憶される電圧設定情報に基づき電圧が可変に設定されるレギュレート電源電圧 V R E G 2 を生成する。これにより出力回路 4 0 や発振回路 3 0 の電源電圧レベルを可変に設定できるようになる。例えば消費電力の低減よりも、位相ジッターによる位相ノイズの低減を重視する機種においては、レギュレート電源電圧 V R E G 2 を高い電圧に設定する。一方、位相ノイズの低減よりも消費電力の低減を重視する機種においては、レギュレート電源電圧 V R E G 2 を低い電圧に設定する。

#### 【 0 0 2 7 】

パッド T 7 は外部入力信号 E I N が入力されるパッドである。パッド T 7 は発振器 4 の外部端子 T E 7 に電気的に接続される。例えば周波数制御信号、アウトプットイネーブル信号又はスタンバイ信号が、外部入力信号 E I N として、パッド T 7 を介して入力される。制御回路 5 0 は、パッド T 7 から入力された周波数制御信号、アウトプットイネーブル信号又はスタンバイ信号に基づいて、周波数制御、アウトプットイネーブル制御又はスタンバイ制御の処理を行う。なおテストモードにおいて、振動子 1 0 のテスト用の信号を、パッド T 7 を介して入力できるようにしてよい。この場合にはパッド T 7 と信号線 L 1 を接続するためのスイッチ回路を設け、パッド T 7 から入力されたテスト用信号を、スイッチ回路及び信号線 L 1 を介して振動子 1 0 の一端に入力する。これにより振動子 1 0 のオーバードライブ等のテスト、検査が可能になる。また記憶部 1 0 0 が不揮発性メモリーにより実現される場合に、不揮発性メモリーへの情報の書き込み時ににおいて、パッド T 7 を介してメモリー書き込み用の高電圧を入力して、記憶部 1 0 0 である不揮発性メモリーに供給するようにしてよい。

#### 【 0 0 2 8 】

記憶部 1 0 0 は、各種の情報を記憶する回路であり、半導体メモリーなどにより実現できる。具体的には記憶部 1 0 0 は、不揮発性メモリーにより実現できる。不揮発性メモリーとしては、例えばデータの電気的な消去が可能な E E P R O M (Electrically Erasable Programmable Read-Only Memory) や、F A M O S (Floating gate Avalanche injection MOS)などを用いた O T P (One Time Programmable) のメモリーなどを用いることができる。或いは不揮発性メモリーは、ヒューズセルを用いたメモリーであってもよい。そして記憶部 1 0 0 は、電圧設定情報を記憶し、レギュレーター 8 2 は、記憶部 1 0 0 に記憶された電圧設定情報に基づき電圧が可変に設定されるレギュレート電源電圧 V R E G 2 を生成する。例えば不揮発性メモリーなどにより実現される記憶部 1 0 0 に電圧設定情報が記憶され、レギュレーター 8 2 が有する可変抵抗の抵抗値を、電圧設定情報に基づき設定することで、レギュレート電源電圧 V R E G 2 の電圧が可変に設定される。また温度補償回路 6 0 が多項式近似による温度補償を行う場合に、不揮発性メモリーなどにより実現される記憶部 1 0 0 は、多項式近似の係数情報を記憶する。例えば記憶部 1 0 0 は、多項式近似の係数情報として、上述した 0 次補正データ、1 次補正データ、高次補正データを記憶する。このような電圧設定情報や係数情報は、例えば集積回路装置 2 0 や

10

20

30

40

50

発振器 4 の製造時や出荷時において、不揮発性メモリーなどにより実現される記憶部 100 に書き込まれて記憶される。これにより、集積回路装置 20 や発振器 4 の機種に応じて、レギュレート電源電圧 VREG2 の電圧値を設定したり、温度補償の係数情報を設定できるようになる。

#### 【0029】

##### 2. レイアウト配置

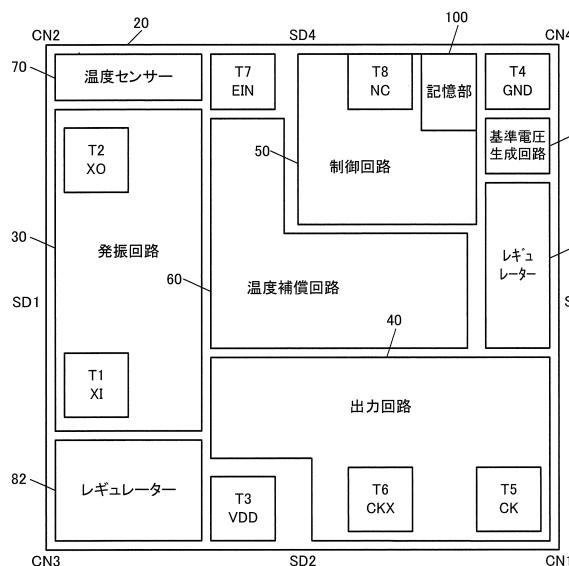

図 3 に本実施形態の集積回路装置 20 のレイアウト配置例を示す。図 3 のレイアウト配置例では、図 2 や図 1 で説明した各回路の回路配置領域が示されている。回路配置領域は、回路を構成する回路素子や回路素子間を接続する配線が配置される領域である。回路素子は、トランジスターなどの能動素子や、抵抗、キャパシターなどの受動素子である。また図 3 ~ 図 6 のレイアウト配置例では、集積回路装置 20 の回路素子が形成される基板に直交する方向の平面視での配置例が示されている。

10

#### 【0030】

集積回路装置 20 は辺 SD1、SD2、SD3、SD4 を有する。辺 SD1、SD2、SD3、SD4 は、各々、第 1 辺、第 2 辺、第 3 辺、第 4 辺である。辺 SD1、SD2、SD3、SD4 は、集積回路装置 20 である矩形の半導体チップの辺に対応する。例えば辺 SD1、SD2、SD3、SD4 は半導体チップの基板の辺である。半導体チップはシリコンダイとも呼ばれる。辺 SD2 は辺 SD1 に交差する辺である。ここで交差は例えば直交である。辺 SD3 は辺 SD1 の対辺である。辺 SD4 は辺 SD2 の対辺である。辺 SD1 及び辺 SD3 は、辺 SD2 及び辺 SD4 と交差する。ここで辺 SD1 から辺 SD3 に向かう方向を DR1 とし、辺 SD2 から辺 SD4 に向かう方向を DR2 とする。また方向 DR1 の反対方向を方向 DR3 とし、方向 DR2 の反対方向を方向 DR4 とする。方向 DR1、DR2、DR3、DR4 は、各々、第 1 方向、第 2 方向、第 3 方向、第 4 方向である。また図 3 において CN1 は辺 SD2 と辺 SD3 が交差するコーナー部であり、CN2 は辺 SD1 と辺 SD4 が交差するコーナー部である。コーナー部 CN1、CN2 は対向するコーナー部になる。また CN3 は辺 SD1 と辺 SD2 が交差するコーナー部であり、CN4 は辺 SD3 と辺 SD4 が交差するコーナー部である。コーナー部 CN3、CN4 は対向するコーナー部になる。

20

#### 【0031】

そして本実施形態の集積回路装置 20 は図 1、図 2、図 3 に示すように、振動子 10 に電気的に接続されるパッド T1、T2 と、パッド T1、T2 に電気的に接続され、振動子 10 を発振させることで発振信号 OSC を生成する発振回路 30 と、発振信号 OSC に基づいてクロック信号 CK、CKX を出力する出力回路 40 を含む。そして図 3 に示すように発振回路 30 は、集積回路装置 20 の辺 SD1 に沿って配置される。例えば発振回路 30 の辺 SD1 側の辺が、集積回路装置 20 の辺 SD1 に沿うように発振回路 30 が配置される。例えば発振回路 30 の長手方向に沿った辺が、辺 SD1 に沿うように配置される。例えば回路が集積回路装置 20 の辺に沿って配置されるとは、例えば回路と辺との間に他の回路が存在しないように回路が配置されることである。例えば辺から所定幅の領域に回路が配置される。また辺に向かう方向と反対方向に他の回路が位置する場合に、他の回路と辺との間に回路が配置される。

30

#### 【0032】

またパッド T1、T2 は、集積回路装置 20 の辺 SD1 に沿って配置される。具体的にはパッド T1、T2 は、平面視において、辺 SD1 に沿って発振回路 30 内に配置される。例えば回路素子が形成される基板に直交する方向での平面視において、発振回路 30 の回路配置領域内に、パッド T1、T2 が配置される。例えば発振回路 30 の回路配置領域において、辺 SD1 に近い位置に、方向 DR2 に沿ってパッド T1、T2 が配置される。例えばパッドが集積回路装置 20 の辺に沿って配置されるとは、例えばパッドと辺との間に他のパッドが存在しないようにパッドが配置されることである。例えば辺から所定幅の領域にパッドが配置される。

40

#### 【0033】

50

そして出力回路 4 0 は、集積回路装置 2 0 の辺 S D 2 に沿って配置される。例えば出力回路 4 0 の辺 S D 2 側の辺が、集積回路装置 2 0 の辺 S D 2 に沿うように出力回路 4 0 が配置される。例えば出力回路 4 0 の長手方向に沿った辺が、辺 S D 2 に沿うように配置される。別の言い方をすれば、発振回路 3 0 は辺 S D 1 に近い領域に配置され、出力回路 4 0 は辺 S D 2 に近い領域に配置される。

#### 【 0 0 3 4 】

振動子接続用のパッド T 1、T 2 は、図 1、図 2 に示すように信号線 L 1、L 2 を介して発振回路 3 0 に接続される。従って、パッド T 1、T 2 間の距離が遠くなると、パッド T 1、T 2 と発振回路 3 0 を接続する信号線 L 1、L 2 の配線長が長くなってしまう。そして、このように信号線 L 1、L 2 の配線長が長くなると、信号線 L 1、L 2 の寄生抵抗や寄生容量が増加し、振動子 1 0 の発振特性が劣化するなどの問題が発生する。例えば負性抵抗の劣化や発振振幅の減少等の問題が発生してしまう。

#### 【 0 0 3 5 】

この点、図 3 では発振回路 3 0 が辺 S D 1 に沿って配置され、パッド T 1、T 2 も辺 S D 1 に沿って配置される。即ち発振回路 3 0 、パッド T 1、T 2 は共に、辺 S D 1 に近い位置に配置される。更に具体的にはパッド T 1、T 2 は発振回路 3 0 の回路配置領域内に配置される。従って、パッド T 1、T 2 と発振回路 3 0 をショートパスで接続できるようになり、信号線 L 1、L 2 の配線長を短くできる。具体的にはパッド T 1、T 2 は、後述の図 7 に示す発振回路 3 0 のコア回路である駆動回路 3 2 に接続されており、本実施形態によればパッド T 1、T 2 と駆動回路 3 2 を接続する信号線 L 1、L 2 の配線長を短くできる。一例としては図 3 において駆動回路 3 2 はパッド T 1 とパッド T 2 の間に配置される。例えばパッド T 1 の方向 D R 2 であってパッド T 2 の方向 D R 4 に、発振回路 3 0 の駆動回路 3 2 が配置されている。即ち、発振回路 3 0 の駆動回路 3 2 とパッド T 1、T 2 とが、平面視において、発振回路 3 0 の回路配置領域内に配置されており、回路配置領域内において隣り合って配置される。従って、パッド T 1、T 2 と駆動回路 3 2 をショートパスで接続できるようになる。そして、このようにパッド T 1、T 2 と駆動回路 3 2 をショートパスで接続することで、信号線 L 1、L 2 の配線長が短くなり、信号線 L 1、L 2 の寄生抵抗や寄生容量を低減できる。従って、信号線 L 1、L 2 の配線長が長くなってしまうことに起因する発振特性の劣化を防止できるようになる。またパッド T 1、T 2 を、発振回路 3 0 内に配置するようにすれば、パッド T 1、T 2 用のパッド配置領域を別個に設けることなく、発振回路 3 0 の回路配置領域を有効利用して、パッド T 1、T 2 を配置できるようになるため、効率的なレイアウト配置が可能になる。

#### 【 0 0 3 6 】

また図 3 では発振回路 3 0 は、辺 S D 1 に沿って配置され、出力回路 4 0 は、辺 S D 1 に交差する辺 S D 2 に沿って配置される。従って発振回路 3 0 と出力回路 4 0 の距離を近づけることが可能になり、高周波信号経路を短くした信号伝搬が可能になる。

#### 【 0 0 3 7 】

例えば振動子 1 0 を 1 0 0 M H z 以上というような高い発振周波数で発振させた場合に、発振回路 3 0 が出力する発振信号 O S C の周波数やクロック信号 C K、C K X の周波数も高くなる。そして高い周波数の信号である高周波信号が、長い配線長の信号線により伝搬すると、信号線から大きな放射ノイズが発生してしまう。また長い配線長の信号線は、発振信号 O S C の特性にも悪影響を与えるおそれがある。

#### 【 0 0 3 8 】

この点、図 3 では、発振回路 3 0 を辺 S D 1 に沿って配置し、出力回路 4 0 を辺 S D 2 に沿って配置することで、発振回路 3 0 と出力回路 4 0 とを短いパスで接続できるようになる。従って、高周波信号が伝播する信号線の配線長を短くでき、当該信号線から発生する放射ノイズを低減できる。また高周波信号が伝播する信号線の配線長が短くなることと、当該信号線の寄生抵抗や寄生容量が発振信号の特性に対して与える悪影響も低減できるようになる。

#### 【 0 0 3 9 】

10

20

30

40

50

また発振回路 3 0 が辺 S D 1 の近傍に配置され、出力回路 4 0 が辺 S D 2 の近傍に配置されることで、発振回路 3 0 の方向 D R 1 側であって出力回路 4 0 の方向 D R 2 側の領域を、例えば温度補償回路 6 0 や制御回路 5 0 の配置領域として利用できるようになる。従って、集積回路装置 2 0 の回路ブロックの効率的なレイアウト配置が可能になり、回路面積を縮小化できるため、集積回路装置 2 0 の小規模化を実現できる。

#### 【 0 0 4 0 】

また出力回路 4 0 は高周波信号についてのバッファリングや駆動を行うため、大きなノイズを発生するノイズ源になると共に、高温を発生する熱源になる。図 3 ではこのようなノイズ源及び熱源となる出力回路 4 0 が辺 S D 2 に沿って配置される。従って、出力回路 4 0 を、辺 S D 2 の近くに寄せて配置できるため、例えばノイズ源や熱源から遠ざけたい回路を、例えば辺 S D 2 の対辺の辺 S D 4 に配置できるようになる。例えば温度センサー 7 0 を、出力回路 4 0 が配置される辺 S D 2 の対辺である辺 S D 4 側に配置することで、出力回路 4 0 からの熱が温度センサー 7 0 での温度検出に及ぼす悪影響を低減できる。これにより温度補償回路 6 0 の温度補償の高精度化等を実現できる。また基準電圧生成回路 9 0 を辺 S D 4 側に配置することで、出力回路 4 0 からのノイズが基準電圧生成回路 9 0 での基準電圧 V R E F の生成に及ぼす悪影響を低減できる。例えば出力回路 4 0 からのノイズにより、基準電圧生成回路 9 0 で生成される基準電圧 V R E F が変動すると、レギュレーター 8 1、8 2 が生成するレギュレート電源電圧 V R E G 1、V R E G 2 も変動してしまう。この結果、温度補償回路 6 0 の温度補償や発振回路 3 0 の発振動作に悪影響を与える、位相ノイズが増加するなどの問題が発生する。出力回路 4 0 を辺 S D 2 に沿って配置することで、出力回路 4 0 と基準電圧生成回路 9 0 との距離を離すことが可能になり、このような問題の発生を防止できるようになる。

#### 【 0 0 4 1 】

また図 3 では出力回路 4 0 は、集積回路装置 2 0 の辺 S D 2 と辺 S D 3 とが交差するコーナー部 C N 1 に配置される。例えば出力回路 4 0 の第 1 辺が集積回路装置 2 0 の辺 S D 2 に沿うと共に出力回路 4 0 の第 2 辺が集積回路装置 2 0 の辺 S D 3 に沿うように、出力回路 4 0 が配置される。即ち出力回路 4 0 の第 1 辺と第 2 边とが交差するコーナー部の位置が、集積回路装置 2 0 のコーナー部 C N 1 の位置になるように、出力回路 4 0 が配置される。

#### 【 0 0 4 2 】

このようにすれば出力回路 4 0 を、集積回路装置 2 0 のコーナー部 C N 1 に寄せて配置できるようになるため、コンパクトで効率的なレイアウト配置が可能になり、集積回路装置 2 0 の小規模化を実現できる。また上述のように出力回路 4 0 は、高周波信号についてのバッファリングや駆動を行うため、大きなノイズを発生するノイズ源になると共に、高温を発生する熱源になる。この点、図 3 では出力回路 4 0 がコーナー部 C N 1 に配置されるため、例えば温度センサー 7 0 については、出力回路 4 0 が配置されるコーナー部 C N 1 に対向するコーナー部 C N 2 に配置できるようになる。従って、出力回路 4 0 と温度センサー 7 0 との距離を最大限に離すことが可能になり、出力回路 4 0 からの熱が温度センサー 7 0 の温度検出結果に悪影響を与えて温度補償の精度が劣化してしまう事態を防止できる。また基準電圧生成回路 9 0 については、出力回路 4 0 が配置されるコーナー部 C N 1 とは異なるコーナー部 C N 4 の付近に配置できるようになる。従って、出力回路 4 0 と基準電圧生成回路 9 0 との距離を離すことが可能になり、出力回路 4 0 からのノイズが基準電圧 V R E F の生成に悪影響を与えて位相ノイズの増加などの問題が発生するのを防止できるようになる。

#### 【 0 0 4 3 】

また集積回路装置 2 0 は、温度センサー 7 0 からの温度検出電圧 V T に基づいて、発振回路 3 0 の発振周波数の温度補償を行う温度補償回路 6 0 を含む。そして辺 S D 1 から辺 S D 3 に向かう方向を D R 1 とし、辺 S D 2 から辺 S D 4 に向かう方向を D R 2 としたときに、温度補償回路 6 0 は、発振回路 3 0 の方向 D R 1 であって、出力回路 4 0 の方向 D R 2 に配置される。即ち発振回路 3 0 の方向 D R 1 側の回路配置領域であって、出力回路

10

20

30

40

50

4 0 の方向 D R 2 側の回路配置領域に、温度補償回路 6 0 が配置される。

#### 【 0 0 4 4 】

このようにすれば、発振回路 3 0 の方向 D R 1 であって出力回路 4 0 の方向 D R 2 にあるスペースを有効活用して、温度補償回路 6 0 を配置できるようになる。例えば温度補償回路 6 0 は、多項式近似によるアナログ方式の温度補償を行う回路であるため、回路面積が大きくなる。この点、辺 S D 1 に沿って配置される発振回路 3 0 の方向 D R 1 側であって、辺 S D 2 に沿って配置される出力回路 4 0 の方向 D R 2 側の領域は、空きスペースとなるため、このスペースに、回路面積が大きな温度補償回路 6 0 を配置することで、効率的なレイアウト配置が可能になる。これにより集積回路装置 2 0 の小面積化を実現できる。また発振回路 3 0 の方向 D R 1 に温度補償回路 6 0 を配置することで、温度補償回路 6 0 からの温度補償電圧 V C P をショートバスで発振回路 3 0 に入力して、発振周波数を制御できるようになる。10

#### 【 0 0 4 5 】

また集積回路装置 2 0 は、温度補償回路 6 0 を制御する制御回路 5 0 を含む。そして制御回路 5 0 は、温度補償回路 6 0 の方向 D R 2 に配置される。別の言い方をすると、温度補償回路 6 0 は、出力回路 4 0 と制御回路 5 0 の間に配置される。そして制御回路 5 0 は、例えば辺 S D 4 に沿って配置される。例えば出力回路 4 0 は、温度補償回路 6 0 と辺 S D 2 との間に配置され、制御回路 5 0 は、温度補償回路 6 0 と辺 S D 4 との間に配置される。また発振回路 3 0 は、温度補償回路 6 0 と辺 S D 1 との間に配置される。即ち温度補償回路 6 0 を中心として、辺 S D 1 の方向に発振回路 3 0 が配置され、辺 S D 2 の方向に出力回路 4 0 が配置され、辺 S D 4 の方向に制御回路 5 0 が配置される。20

#### 【 0 0 4 6 】

このように制御回路 5 0 を配置すれば、温度補償回路 6 0 を制御する制御回路 5 0 を、温度補償回路 6 0 の方向 D R 2 において、例えば温度補償回路 6 0 に隣り合うように配置できる。従って制御回路 5 0 からの制御信号をショートバスで温度補償回路 6 0 に入力できるようになる。また辺 S D 1 に沿って発振回路 3 0 が配置され、辺 S D 2 に沿って出力回路 4 0 が配置される場合に、辺 S D 4 に沿ったスペースを有効活用して、例えば自動配置配線により制御回路 5 0 を配置できるようになり、効率的なレイアウト配置が可能になる。これにより集積回路装置 2 0 の小規模化を図れるようになる。また外部入力信号 E I N が入力されるパッド T 7 が辺 S D 4 に沿って配置される場合に、このパッド T 7 の近くに制御回路 5 0 を配置できるようになる。従って、周波数制御信号、アウトプットイネーブル信号又はスタンバイ信号などの外部入力信号 E I N をショートバスで制御回路 5 0 に入力できるようになる。30

#### 【 0 0 4 7 】

また集積回路装置 2 0 は、発振周波数の温度補償を行う温度補償回路 6 0 と、温度補償回路 6 0 にレギュレート電源電圧 V R E G 1 を供給するレギュレーター 8 1 を含む。そしてレギュレーター 8 1 は、温度補償回路 6 0 の方向 D R 1 に配置される。具体的にはレギュレーター 8 1 は、辺 S D 3 に沿って配置される。例えば温度補償回路 6 0 と辺 S D 3 の間にレギュレーター 8 1 が配置される。このようにすれば、レギュレーター 8 1 が生成したレギュレート電源電圧 V R E G 1 をショートバスで温度補償回路 6 0 に入力できるようになり、レギュレート電源電圧 V R E G 1 の供給用の電源線の寄生抵抗や寄生容量を低減することが可能になる。従って、レギュレーター 8 1 により安定化したレギュレート電源電圧 V R E G 1 が、ノイズ等の影響で変動してしまうのを抑制できるようになる。この結果、レギュレート電源電圧 V R E G 1 が変動して、温度補償回路 6 0 の温度補償の精度が劣化して、クロック周波数の精度が低下するなどの事態を防止できるようになる。40

#### 【 0 0 4 8 】

また集積回路装置 2 0 は、レギュレーター 8 1 に基準電圧 V R E F を供給する基準電圧生成回路 9 0 と、グランド電圧が供給されるグランドパッド T 4 を含む。そして基準電圧生成回路 9 0 は、グランドパッド T 4 とレギュレーター 8 1 の間に配置される。例えばレギュレーター 8 1 の方向 D R 2 に基準電圧生成回路 9 0 が配置され、基準電圧生成回路 9

10

20

30

40

50

0 の方向 D R 2 にグランドパッド T 4 が配置される。具体的には、レギュレーター 8 1 に隣り合うように基準電圧生成回路 9 0 が配置され、基準電圧生成回路 9 0 に隣り合うようにグランドパッド T 4 が配置される。例えばレギュレーター 8 1、基準電圧生成回路 9 0 及びグランドパッド T 4 は、辺 S D 3 に沿って配置され、グランドパッド T 4 は例えば集積回路装置 2 0 のコーナー部 C N 4 に配置される。

#### 【 0 0 4 9 】

このような配置によれば、グランドパッド T 4 と基準電圧生成回路 9 0 との距離や、基準電圧生成回路 9 0 とレギュレーター 8 1 との距離を短くすることが可能になる。従って、グランドパッド T 4 からのグランド電圧をショートパスで基準電圧生成回路 9 0 に供給できるようになる。また基準電圧生成回路 9 0 が生成した基準電圧 V R E F をショートパスでレギュレーター 8 1 に供給できるようになる。これにより基準電圧生成回路 9 0 は、安定した電位のグランド電圧を基準にして、基準電圧 V R E F を生成できるようになるため、安定した電位の基準電圧 V R E F をレギュレーター 8 1 等に供給できるようになる。またレギュレーター 8 1 は、安定した電位の基準電圧 V R E F をレギュレーター 8 1 等に供給できるようになる。これにより、レギュレート電源電圧 V R E G 1 を生成できるようになるため、安定した電位のレギュレート電源電圧 V R E G 1 を、温度補償回路 6 0 等に供給できるようになる。クロック周波数の精度が低下するなどの事態が発生するのを、効果的に防止できるようになる。

10

#### 【 0 0 5 0 】

また集積回路装置 2 0 は、温度センサー 7 0 と、温度センサー 7 0 からの温度検出電圧 V T に基づいて温度補償を行う温度補償回路 6 0 を含む。そして温度センサー 7 0 は、発振回路 3 0 の方向 D R 2 に配置される。例えば温度センサー 7 0 は、発振回路 3 0 と辺 S D 4 との間に配置される。具体的には温度センサー 7 0 は、発振回路 3 0 の方向 D R 2 側において発振回路 3 0 に隣り合うように配置される。

20

#### 【 0 0 5 1 】

このようにすれば、発振回路 3 0 内に配置されるパッド T 2 と温度センサー 7 0 との距離を近づけることができ、例えばパッド T 2 に隣り合うように温度センサー 7 0 を配置できる。また発振回路 3 0 内に配置されるパッド T 1 と温度センサー 7 0 との距離も近づけることが可能になる。例えば温度センサー 7 0 は、理想的には振動子 1 0 の温度自体を検出することが望ましい。しかしながら、図 3 では温度センサー 7 0 は集積回路装置 2 0 に内蔵されているため、振動子 1 0 の直ぐ近くにおいて振動子 1 0 の温度をダイレクトに検出することはできない。この点、パッド T 2 と振動子 1 0 は、パッケージの内部配線、ボンディングワイヤー又は金属バンプ等を用いて電気的に接続されており、内部配線、ボンディングワイヤー、金属バンプは金属により形成されている。従って、振動子 1 0 の温度は、当該金属により熱伝導されて、パッド T 2 に伝達されるようになる。従って、パッド T 2 の近くに温度センサー 7 0 が配置されることで、振動子 1 0 の温度を、温度センサー 7 0 を用いて、より適切に検出することが可能になる。これにより温度検出の精度を向上できるため、温度補償の精度も向上できるようになり、クロック周波数の高精度化等を実現できるようになる。また発振回路 3 0 の方向 D R 2 側に温度センサー 7 0 が配置されることで、辺 S D 2 に沿って配置される出力回路 4 0 と温度センサー 7 0 との距離を離すことが可能になる。従って、出力回路 4 0 からの熱が温度センサー 7 0 の温度検出結果に悪影響を与えて温度補償の精度が劣化してしまう事態を防止できるようになり、クロック周波数の高精度化等を実現できるようになる。

30

#### 【 0 0 5 2 】

また図 3 では、温度センサー 7 0 は、集積回路装置 2 0 の辺 S D 1 と辺 S D 4 が交差するコーナー部 C N 2 に配置される。具体的には温度センサー 7 0 の例えば短辺が辺 S D 1 に沿うと共に、温度センサー 7 0 の例えば長辺が辺 S D 4 に沿うように、温度センサー 7 0 が配置される。例えばコーナー部 C N 2 に最も近い位置に温度センサー 7 0 が配置される。このようにすれば、辺 S D 2 に沿って配置される出力回路 4 0 から離れた位置に温度

40

50

センサー 7 0 を配置できるようになる。例えば出力回路 4 0 がコーナー部 C N 1 に配置される場合に、コーナー部 C N 1 に対向するコーナー部 C N 2 に温度センサー 7 0 を配置できるようになる。これにより、出力回路 4 0 と温度センサー 7 0との距離を最大限に離すことが可能となる。従って、出力回路 4 0 からの熱が温度センサー 7 0 の温度検出結果に悪影響を与えて温度補償の精度が劣化してしまう事態を防止できるようになり、クロック周波数の高精度化等を実現できるようになる。

#### 【 0 0 5 3 】

また集積回路装置 2 0 は、クロック信号 C K、C K X を出力するクロックパッド T 5、T 6 を含む。そしてクロックパッド T 5、T 6 は、出力回路 4 0 内に配置される。例えば平面視において出力回路 4 0 の回路配置領域内にクロックパッド T 5、T 6 が配置される。例えばクロックパッド T 5、T 6 は、出力回路 4 0 の回路配置領域において、辺 S D 2 に近い位置に、方向 D R 1 に沿って配置される。例えばクロックパッド T 5 については、集積回路装置 2 0 のコーナー部 C N 1 に配置される。

10

#### 【 0 0 5 4 】

このようにクロックパッド T 5、T 6 を、出力回路 4 0 内に配置するようすれば、クロックパッド T 5、T 6 用のパッド配置領域を別個に設けることなく、出力回路 4 0 の回路配置領域を有効利用して、クロックパッド T 5、T 6 を配置できるようになるため、効率的なレイアウト配置が可能になる。また辺 S D 1 に沿って配置される発振回路 3 0 からの発振信号 O S C が、辺 S D 2 に沿って配置される出力回路 4 0 に入力され、出力回路 4 0 が、発振信号 O S C に基づくクロック信号 C K、C K X を、出力回路 4 0 内に設けられたクロックパッド T 5、T 6 を介して出力できるようになる。従って、高周波信号がショートバスの信号経路で伝搬されるようになるため、放射ノイズの発生も低減できるようになる。

20

#### 【 0 0 5 5 】

また集積回路装置 2 0 は、電源パッド T 3 とグランドパッド T 4 を含み、電源パッド T 3 は辺 S D 2 に沿って配置され、グランドパッド T 4 は辺 S D 4 に沿って配置される。例えば電源パッド T 3 は辺 S D 2 の中央部付近に配置され、例えばレギュレーター 8 2 と出力回路 4 0 の間に配置される。グランドパッド T 4 は、辺 S D 4 の端部付近に配置され、具体的には辺 S D 4 と辺 S D 3 が交差するコーナー部 C N 4 に配置される。

30

#### 【 0 0 5 6 】

例えば出力回路 4 0 では、後述の図 8 で説明するように、最終段の出力ドライバー 4 6 が電源電圧 V D D に基づいて動作して、クロック信号 C K、C K X を出力する。例えば出力ドライバー 4 6 は、V D D からの電流による電流駆動などを行うため、多くの電流を消費する。このため、V D D の電源線に多くの電流が流れてしまう。この点、辺 S D 2 に沿って電源パッド T 3 を配置することで、辺 S D 2 に沿って配置される出力回路 4 0 の近くに電源パッド T 3 が配置されるようになる。そして出力回路 4 0 の近くに電源パッド T 3 が配置されることで、電源パッド T 3 からの電源線をショートバスで出力回路 4 0 に接続できるようになる。従って、出力回路 4 0 の出力ドライバー 4 6 の駆動によって、V D D の電源線に多くの電流が流れても、電圧降下等を最小限に抑えることができ、出力回路 4 0 の近くに配置された電源パッド T 3 から電流を適切に供給できるようになる。またグランドパッド T 4 が辺 S D 4 に沿って配置されることで、辺 S D 4 の近くに配置される基準電圧生成回路 9 0 等に対して、低インピーダンスでグランド電圧を供給できるようになり、適切な基準電圧 V R E F の生成等を実現できるようになる。

40

#### 【 0 0 5 7 】

また発振回路 3 0 は、辺 S D 1 に沿った方向を長手方向として配置される。例えば発振回路 3 0 の長辺が、辺 S D 1 に沿った方向である方向 D R 2 に沿うように、発振回路 3 0 が配置される。このようにすれば、発振回路 3 0 の短辺の方向は、辺 S D 1 に沿った方向 D R 2 に交差する方向になる。即ち発振回路 3 0 の短辺の方向は、方向 D R 1 になる。従って、辺 S D 1 から所定幅の領域に発振回路 3 0 が配置されるようになる。即ち、辺 S D 1 から、発振回路 3 0 の短辺の長さに対応する所定幅の領域に、発振回路 3 0 を配置でき

50

るようになり、効率的なレイアウト配置が可能になる。

**【 0 0 5 8 】**

また出力回路 4 0 は、辺 S D 2 に沿った方向を長手方向として配置される。例えば出力回路 4 0 の長辺が、辺 S D 2 に沿った方向である方向 D R 1 に沿うように、出力回路 4 0 が配置される。このようにすれば、出力回路 4 0 の短辺の方向は、辺 S D 2 に沿った方向 D R 1 に交差する方向になる。即ち出力回路 4 0 の短辺の方向は、方向 D R 2 になる。従って、辺 S D 2 から所定幅の領域に出力回路 4 0 が配置されるようになる。即ち、辺 S D 2 から、出力回路 4 0 の短辺の長さに対応する所定幅の領域に、出力回路 4 0 を配置できるようになり、効率的なレイアウト配置が可能になる。

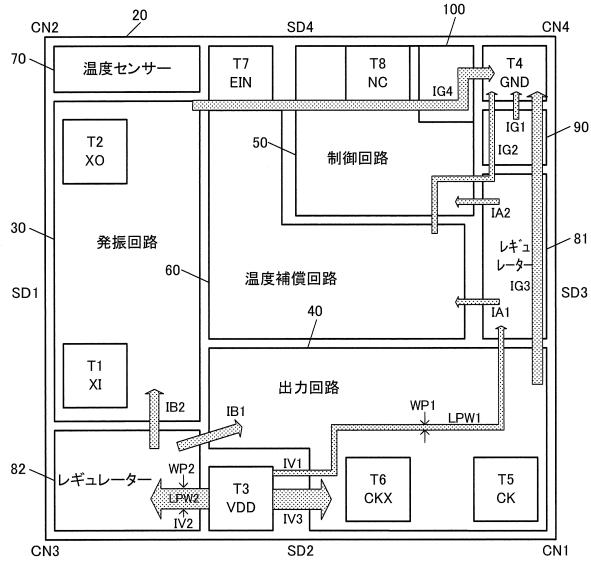

**【 0 0 5 9 】**

図 4 は集積回路装置 2 0 での電流経路を示す模式図である。図 4 において矢印の太さは流れる電流の大きさを模式的に表している。

**【 0 0 6 0 】**

例えば出力回路 4 0 や発振回路 3 0 にレギュレーター 8 2 を供給するレギュレーター 8 2 に対しては、電源パッド T 3 から電流 I V 2 が流れる。温度補償回路 6 0 、制御回路 5 0 にレギュレーター 8 1 を供給しているレギュレーター 8 1 に対しては、電源パッド T 3 から電流 I V 1 が流れる。そして I V 2 > I V 1 の関係が成り立っている。また出力回路 4 0 に対しては電源パッド T 3 から電流 I V 3 が流れ、I V 3 > I V 1 になっている。即ち、高周波数の発振動作や高周波数の信号のバッファリングや駆動には、多くの電流が消費されるため、電源パッド T 3 からレギュレーター 8 2 に流れる電流 I V 2 は多くなり、レギュレーター 8 2 から出力回路 4 0 、発振回路 3 0 に流れる電流 I B 1 、I B 2 も多くなる。また出力回路 4 0 では、後述の図 8 に示すように出力ドライバー 4 6 において多くの電流が流れるため、電源パッド T 3 から出力回路 4 0 に流れる電流 I V 3 も多くなる。このため本実施形態では、電源パッド T 3 の近くにレギュレーター 8 2 、出力回路 4 0 、発振回路 3 0 を配置している。例えばレギュレーター 8 2 、電源パッド T 3 、出力回路 4 0 は辺 S D 2 に沿って配置される。そしてレギュレーター 8 2 の方向 D R 2 に発振回路 3 0 が配置される。これにより電流が流れる経路での寄生抵抗を小さくでき、低インピーダンスでの電流供給が可能になる。

**【 0 0 6 1 】**

また図 4 に示すように、電源パッド T 3 からの電源電圧 V D D は、電源線 L P W 1 を介してレギュレーター 8 1 に供給され、電源線 L P W 2 を介してレギュレーター 8 2 に供給される。L P W 1 は第 1 電源線であり、L P W 2 は第 2 電源線である。そして電源線 L P W 1 を介して供給された電源電圧 V D D に基づいて、レギュレーター 8 1 から温度補償回路 6 0 、制御回路 5 0 に対して電流 I A 1 、I A 2 が流れる。また電源線 L P W 2 を介して供給された電源電圧 V D D に基づいて、レギュレーター 8 2 から出力回路 4 0 、発振回路 3 0 に電流 I B 1 、I B 2 が流れる。このように図 4 では、電源パッド T 3 からの電源電圧 V D D を、分離された別個の電源線 L P W 1 、L P W 2 を介して、各々、レギュレーター 8 1 、8 2 に供給している。

**【 0 0 6 2 】**

このときに本実施形態では、電源パッド T 3 とレギュレーター 8 1 とを接続する電源線 L P W 1 の配線幅 W P 1 を、電源パッド T 3 とレギュレーター 8 2 とを接続する電源線 L P W 2 の配線幅 W P 2 よりも細くしている。即ち、レギュレーター 8 2 に接続される電源線 L P W 2 の配線幅 W P 2 を太くする一方で、レギュレーター 8 1 に接続される電源線 L P W 1 の配線幅 W P 1 を細くしている。そして電源線 L P W 2 の配線幅 W P 2 を太くすることで、電源パッド T 3 からの大電流を低インピーダンスでレギュレーター 8 2 に供給できるようになる。一方、電源線 L P W 1 の配線幅 W P 1 を細くすることで、電源線 L P W 1 でのインピーダンスが、電源線 L P W 2 でのインピーダンスよりも高くなる。このようなインピーダンス分離を行うことで、大電流が流れる電源線 L P W 2 側でのノイズが、電源線 L P W 1 側に伝わらなくなり、レギュレーター 8 1 に供給される電源電圧 V D D のノイズを低減できるようになる。これにより低ノイズの電源での温度補償回路 6 0 の動作が

10

20

30

40

50

可能になり、電源ノイズを原因とする温度補償の精度の劣化を抑制できるようになる。即ち、電源パッドT 3からレギュレーター8 2には大電流が流れ、発生するノイズも大きくなる。そしてレギュレーター8 1に接続される電源線L PW 1の配線幅WP 1を細くすることで、電源線L PW 1のインピーダンスが高くなり、レギュレーター8 2側で発生した電源ノイズが、レギュレーター8 1に伝達されるのが抑制される。レギュレーター8 1から温度補償回路6 0、制御回路5 0に流れる電流は小電流であるため、電源線L PW 1のインピーダンスが高くなってしまっても、大きな問題は生じない。そしてレギュレーター8 2側の電源ノイズが、レギュレーター8 1側に伝達されないことで、レギュレーター8 1が温度補償回路6 0に供給するレギュレート電源電圧V REG 1も低ノイズになり、電源ノイズを原因とする温度補償の精度の劣化等を防止できるようになる。なお、電源線L PW 1の配線幅WP 1及び電源線L PW 2の配線幅WP 2は、必ずしも均一でなくてもよい。この場合、配線幅WP 1の平均値が配線幅WP 2の平均値より小さければよい。

#### 【0063】

また図4に示すように、グランドパッドT 4に対しては、基準電圧生成回路9 0、温度補償回路6 0、出力回路4 0、発振回路3 0から、各々、電流IG 1、IG 2、IG 3、IG 4が流れる。そして基準電圧生成回路9 0は、グランド電圧を基準に基準電圧V REFを生成しているため、電源ノイズ等によりグランド電圧が変動してしまうと、基準電圧V REFも変動してしまう。このように基準電圧V REFが変動してしまうと、温度補償回路6 0での温度補償の精度も劣化してしまう。例えばレギュレーター8 1は、基準電圧生成回路9 0からの基準電圧V REFに基づいてレギュレート電源電圧V REG 1を生成しており、基準電圧V REFが変動すると、レギュレート電源電圧V REG 1も変動してしまう。これにより、レギュレート電源電圧V REG 1に基づき動作する温度補償回路6 0の温度補償の精度も劣化してしまう。またアナログ回路が使用する基準電流は、基準電圧V REFに基づき生成される。従って、基準電圧V REFが変動して、基準電流が変動すると、多項式近似によるアナログ方式の温度補償を行う温度補償回路6 0での当該温度補償の精度も劣化してしまう。

#### 【0064】

この点、本実施形態では、基準電圧生成回路9 0は、他の回路に比べてグランドパッドT 4の近くに配置されている。例えばグランドパッドT 4とレギュレーター8 1との間に基準電圧生成回路9 0が配置されており、例えばグランドパッドT 4に隣り合うように基準電圧生成回路9 0が配置されている。従って、グランドパッドT 4と基準電圧生成回路9 0を接続するグランドの電源線の配線長を短くでき、電線線の経路でのインピーダンスを低減できる。従って、基準電圧生成回路9 0でのグランド電圧の変動を低減でき、低ノイズの基準電圧V REFが生成されるようになるため、温度補償回路6 0の温度補償の高精度化を実現できるようになる。

#### 【0065】

図5は集積回路装置2 0での高周波信号の信号経路を模式的に示す図である。発振回路3 0で生成された高周波の発振信号OSCは、図5のPSAに示す経路で出力回路4 0に入力される。そして発振信号OSCに基づき生成されたクロック信号CK、CKXはPSB 1、PSB 2に示す経路でクロックパッドT 5、T 6から出力される。そして本実施形態では、発振回路3 0を辺SD 1に沿って配置すると共に出力回路4 0を辺SD 2に沿って配置することで、図5に示すようなショートパスの経路で、高周波信号を伝達してクロックパッドT 5、T 6からクロック信号CK、CKXを出力できるようになる。従って、高周波信号が短い経路で伝達されるようになり、高周波信号を原因とする放射ノイズの発生を抑制できるようになる。

#### 【0066】

図6に集積回路装置2 0のレイアウト配置の他の例を示す。図6の集積回路装置2 0は、発振回路3 0、出力回路4 0、制御回路5 0、温度補償回路6 0、温度センサー7 0、電源回路8 0を含む。また集積回路装置2 0は、振動子接続用のパッドT 1、T 2、電源パッドT 3、グランドパッドT 4、クロックパッドT 5、外部入力信号用のパッドT 7を

含む。図6は、図1の構成に対して温度補償回路60や温度センサー70を更に設けた構成になっている。またクロック信号CKは、差動の信号形式ではなく、例えばシングルエンドのCMOSやクリップドサイン波の信号形式で、クロックパッドT5から出力される。

#### 【0067】

図6の集積回路装置20においても、発振回路30は辺SD1に沿って配置され、パッドT1、T2は、辺SD1に沿って発振回路30内に配置される。そして出回路40が辺SD2に沿って配置される。例えば発振回路30は、辺SD1に沿った方向を長手方向として配置され、出回路40は、辺SD2に沿った方向を長手方向として配置される。また温度補償回路60は、発振回路30の方向DR1であって、出回路40の方向DR2に配置される。そして制御回路50は、温度補償回路60の方向DR2に配置される。なお電源回路80は、温度補償回路60の方向DR1に配置される。例えば電源回路80は、出回路40の方向DR2に配置される。また温度センサー70は、発振回路30の方向DR2に配置される。具体的には温度センサー70は、辺SD1と辺SD4が交差するコーナー部CN2に配置される。またクロック信号CKを出力するクロックパッドT5は、出回路40内に配置される。例えばクロックパッドT5は、辺SD2と辺SD3が交差するコーナー部CN1に配置される。また電源パッドT3は、辺SD2に沿って配置され、グランドパッドT4は、辺SD4に沿って配置される。例えば電源パッドT3は、辺SD2の中央部付近の領域に配置され、グランドパッドT4は、辺SD4と辺SD3が交差するコーナー部CN4に配置される。

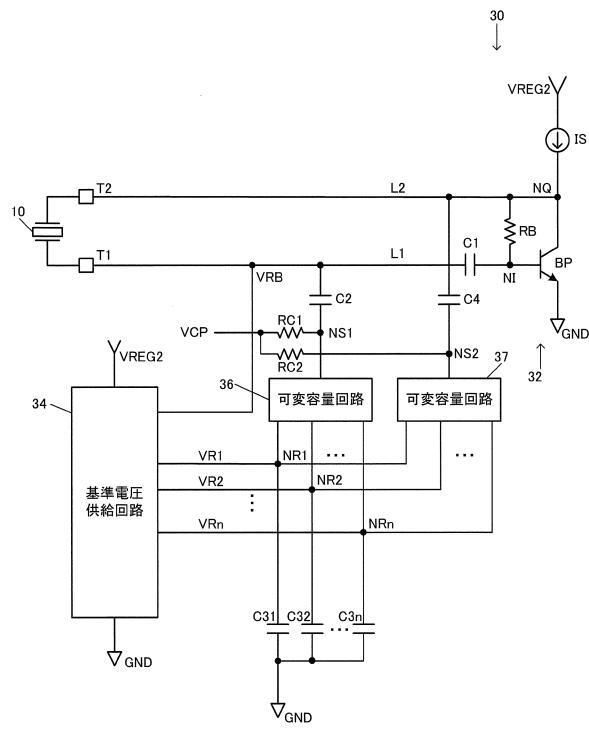

#### 【0068】

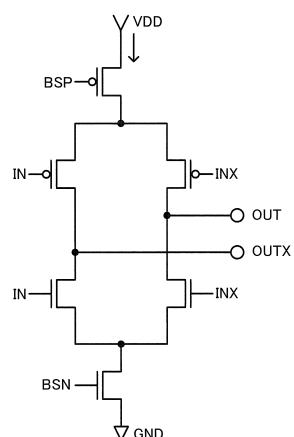

##### 3. 発振回路

図7に発振回路30の構成例を示す。図7の発振回路30は、駆動回路32と、DCカット用のキャパシターC1、C2と、基準電圧供給回路34と、可変容量回路36を含む。また発振回路30は、DCカット用のキャパシターC4と、可変容量回路37を含むことができる。なおキャパシターC4と可変容量回路37は必須の構成要素ではなく、これらを設けない変形実施も可能である。また可変容量回路36及び可変容量回路37とGNDノードとの間にはキャパシターC31～C3nが設けられている。

#### 【0069】

駆動回路32は、振動子10を駆動して発振させる回路である。駆動回路32は、電流源ISと、バイポーラトランジスターBPと、抵抗RBを含む。電流源ISはVREG2の電源ノードとバイポーラトランジスターBPとの間に設けられ、バイポーラトランジスターBPに定電流を供給する。バイポーラトランジスターBPは、振動子10を駆動するトランジスターであり、ベースノードが、駆動回路32の入力ノードNIとなり、コレクターノードが、駆動回路32の出力ノードNQとなっている。抵抗RBはバイポーラトランジスターBPのコレクターノードとベースノードの間に設けられる。

#### 【0070】

DCカット用のキャパシターC1は、駆動回路32の入力ノードNIと信号線L1との間に設けられる。このようなキャパシターC1を設けることで、発振信号のDC成分がカットされ、AC成分だけが駆動回路32の入力ノードNIに伝達されるようになり、バイポーラトランジスターBPを適正に動作させることができになる。なお、DCカット用のキャパシターC1は、駆動回路32の出力ノードNQと信号線L1との間に設けてよい。

#### 【0071】

基準電圧供給回路34は、可変容量回路36及び可変容量回路37に基準電圧VR1～VRnを供給する。基準電圧供給回路34は、例えばVREG2のノードとGNDのノードの間に直列に設けられた複数の抵抗を含み、VREG2の電圧を分割した電圧を基準電圧VR1～VRnとして出力する。

#### 【0072】

また基準電圧供給回路34は、信号線L1にバイアス電圧設定用の基準電圧VRBを供給する。これにより信号線L1での発振信号の振幅中心電圧を基準電圧VRBに設定できるようになる。なお信号線L2での発振信号の振幅中心電圧は、例えばバイポーラトラン

ジスター B P のベース・エミッター間電圧と、抵抗 R B に流れるベース電流に基づき設定される。

#### 【 0 0 7 3 】

D C カット用のキャパシター C 2 は、一端が信号線 L 1 に電気的に接続され、他端が温度補償電圧 V C P の供給ノード N S 1 に電気的に接続される。温度補償電圧 V C P は抵抗 R C 1 を介して供給ノード N S 1 に供給される。可変容量回路 3 6 は、一端が供給ノード N S 1 に電気的に接続されて、温度補償電圧 V C P が供給される。また基準電圧供給回路 3 4 は、可変容量回路 3 6 の他端の供給ノード N R 1 ~ N R n に、基準電圧 V R 1 ~ V R n を供給する。そして基準電圧 V R 1 ~ V R n の供給ノード N R 1 ~ N R n と、G N D ノードとの間にキャパシター C 3 1 ~ C 3 n が設けられる。D C カット用のキャパシター C 4 は、一端が信号線 L 2 に電気的に接続され、他端が温度補償電圧 V C P の供給ノード N S 2 に電気的に接続される。温度補償電圧 V C P は抵抗 R C 2 を介して供給ノード N S 2 に供給される。可変容量回路 3 7 は、一端が供給ノード N S 2 に電気的に接続されて、温度補償電圧 V C P が供給される。また基準電圧供給回路 3 4 は、可変容量回路 3 7 の他端の供給ノード N R 1 ~ N R n に、基準電圧 V R 1 ~ V R n を供給する。10

#### 【 0 0 7 4 】

可変容量回路 3 6 は n 個の可変容量素子を含む。n は 2 以上の整数である。n 個の可変容量素子は、例えば M O S 型の可変容量素子であり、n 個のトランジスターにより構成される。そして n 個のトランジスターのゲートには基準電圧 V R 1 ~ V R n が供給される。また n 個のトランジスターの各トランジスターのソース及びドレインが短絡され、短絡されたソース及びドレインが接続される供給ノード N S 1 に対して、温度補償電圧 V C P が供給される。そして D C カット用のキャパシター C 2 の容量は、可変容量回路 3 6 の容量に比べて十分に大きな容量になっている。このような構成の可変容量回路 3 6 を用いることで、広い温度補償電圧 V C P の電圧範囲において、可変容量回路 3 6 のトータルの容量の容量変化の直線性を確保できるようになる。なお可変容量回路 3 7 の構成は可変容量回路 3 6 と同様の構成であるため、詳細な説明は省略する。20

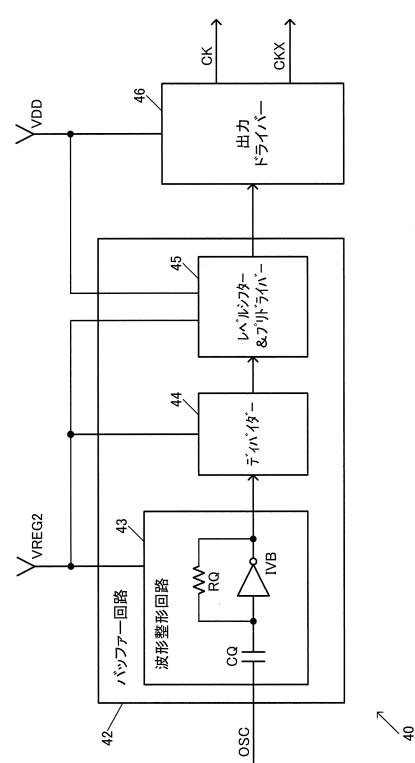

#### 【 0 0 7 5 】

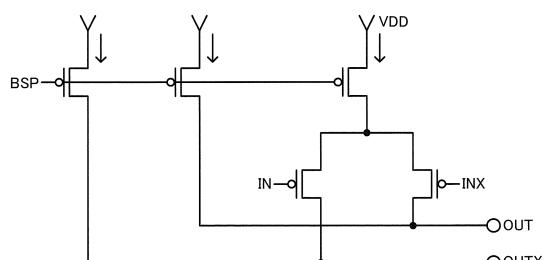

##### 4 . 出力回路

図 8 に出力回路 4 0 の構成例を示す。出力回路 4 0 は、発振信号 O S C のバッファリングなどを行うバッファー回路 4 2 と、発振信号 O S C に基づくクロック信号 C K 、 C K X の出力及び駆動を行う出力ドライバー 4 6 を含む。バッファー回路 4 2 は、例えば波形整形回路 4 3 、ディバイダー 4 4 、レベルシフター & プリドライバー 4 5 を含むことができる。波形整形回路 4 3 は、発振信号 O S C の波形整形を行って、発振信号 O S C に対応する矩形波の信号を出力する回路であり、インバーター I V B と、インバーター I V B の出力端子と入力端子の間に設けられる帰還用の抵抗 R Q を含む。ディバイダー 4 4 は、クロック分周を行う回路であり、ディバイダー 4 4 を設けることで、発振信号 O S C の周波数を分周した周波数のクロック信号 C K 、 C K X を出力できるようになる。レベルシフター & プリドライバー 4 5 は、V R E G 2 の電源電圧レベルから V D D の電源電圧レベルへのレベルシフトや、出力ドライバー 4 6 を駆動するプリドライブを行なう回路である。例えばバッファー回路 4 2 の波形整形回路 4 3 及びディバイダー 4 4 には、レギュレート電源電圧 V R E G 2 が供給され、レベルシフター & プリドライバー 4 5 には、レギュレート電源電圧 V R E G 2 及び電源電圧 V D D が供給される。一方、出力ドライバー 4 6 には電源電圧 V D D が供給される。30

#### 【 0 0 7 6 】

出力ドライバー 4 6 は、L V D S のドライバー回路、P E C L のドライバー回路、H C S L のドライバー回路、及び差動の C M O S のドライバー回路のうちの少なくとも 1 つのドライバー回路を含むことができる。なお、これらの複数のドライバー回路を出力ドライバー 4 6 に設ける場合に、複数のドライバー回路を構成するトランジスターの一部を、複数のドライバー回路の間で共用してもよい。

#### 【 0 0 7 7 】

10

20

30

40

50

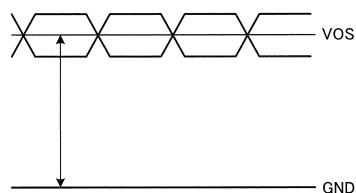

図9はL V D Sのドライバー回路の構成例である。このドライバー回路は、例えば3.5 mAの駆動電流を流す電流源用のP型のトランジスターと、差動の入力信号IN、INXが入力されて差動の出力信号OUT、OUTXを出力する差動部を構成するP型及びN型のトランジスターと、GND側に設けられるN型のトランジスターを有する。出力信号OUT、OUTXはクロック信号CK、CKXに対応する。図13はL V D Sの差動出力信号の信号波形例である。L V D Sの差動出力信号は、GNDを基準にした電圧VOSを中心電圧とする、振幅が例えば0.35Vの信号である。

#### 【0078】

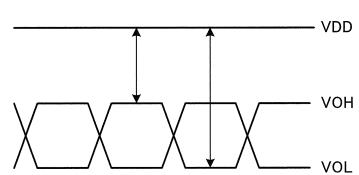

図10はP E C Lのドライバー回路の構成例である。このドライバー回路は、例えば1.5.25mAの駆動電流を流すP型のトランジスターと、差動部を構成する2つのP型のトランジスターと、出力信号OUT、OUTXのノードに5.7mAのバイアス電流を流すバイアス電流回路を構成する2つのP型のトランジスターを有する。このドライバー回路は、実際にはL V - P E C L (Low Voltage Positive Emitter Coupled Logic)と呼ばれるが、本実施形態では単にP E C Lと記載する。図14はP E C Lの差動出力信号の信号波形例である。P E C Lの差動出力信号は、高電位側の電圧がV OHとなり、低電位側の電圧がV OLとなる振幅の信号である。V OHは、V DDを基準にして負電位側に例えば0.9525Vとなる電圧であり、V OLは、V DDを基準にして負電位側に例えば1.715Vとなる電圧である。P E C Lでは、受信側においてテブナン終端又はY終端などが行われる。

#### 【0079】

図11はH C S Lのドライバー回路の構成例である。このドライバー回路は、例えば1.5mAの駆動電流を流すP型のトランジスターと、差動部を構成する2つのP型のトランジスターを有する。H C S Lの差動出力信号は、例えば0.4Vを中心電圧とした1.15V以下の振幅の信号である。図12は差動のC M O Sのドライバー回路の構成例である。このドライバー回路は、V DDとGNDの間に直列に設けられ、ゲートに入力信号INが入力されるP型のトランジスター及びN型のトランジスターと、V DDとGNDの間に直列に設けられ、ゲートに入力信号INXが入力されるP型のトランジスター及びN型のトランジスターを含む。このC M O Sのドライバー回路の差動出力信号は、V DD ~ GNDとなる電圧範囲のフルスイングの信号になる。

#### 【0080】

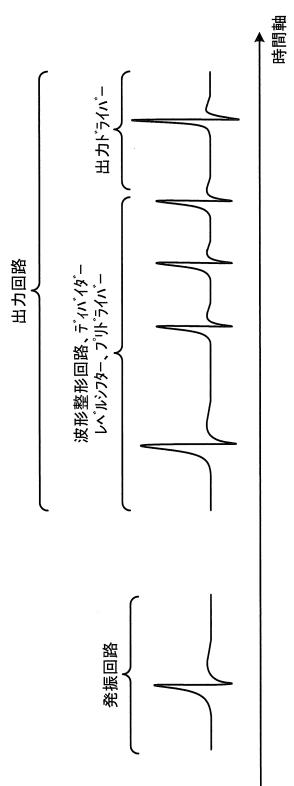

図15は、発振回路30、出力回路40で発生するノイズを模式的に説明する図である。例えばP L L回路等を有しない源振の発振器4では、発振回路30のノイズ成分の周波数と出力回路40のノイズ成分の周波数は同一周波数になる。即ちノイズスペクトルにおいて同一周波数にノイズが現れる。しかしながら、図15に示すように、出力回路40の各回路で発生するノイズは異なるタイミングで発生し、発振回路30に比べて、ノイズの発生要素が多い。従って、ノイズ成分の周波数が同じであっても、スプリアス強度は強くなり、出力回路40は多くのノイズを発生するノイズ源となる。

#### 【0081】

この点、本実施形態では、出力回路40を辺S D 2に沿って配置し、辺S D 2の対辺である辺S D 4に配置されるグランドパッドT4と出力回路40との間の距離を離している。これにより、例えば出力回路40で発生した電源ノイズ等のノイズが、グランド電圧に及ぼす悪影響を低減できるようになる。例えば基準電圧供給回路34は、グランド電圧を基準に基準電圧V R E Fを生成するが、出力回路40で発生したノイズが、グランド電圧に重畠されるのが抑制されるようになる。これにより、基準電圧V R E Fの変動も抑制でき、例えば温度補償回路60の温度補償の精度が劣化するのが抑制され、クロック信号の位相ノイズの低減が可能になる。

#### 【0082】

また本実施形態では、温度補償回路60等にレギュレート電源電圧V R E G 1を供給するレギュレーター81と、出力回路40等にレギュレート電源電圧V R E G 2を供給するレギュレーター82とを、別個に設けている。また図4で説明したように、レギュレータ

10

20

30

40

50

– 8 1 に電源電圧 V D D を供給する電源線 L P W 1 の配線幅 W P 1 を細くして、インピーダンスを高くしている。これによりレギュレーター 8 2 側で発生した電源ノイズが、レギュレーター 8 1 側に及ぶのが抑制され、温度補償回路 6 0 の温度補償の高精度化や位相ノイズの低減などを実現できるようになる。

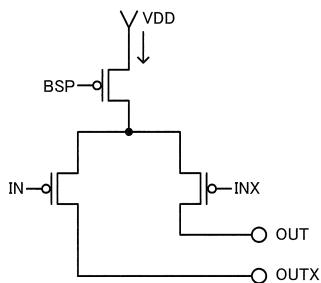

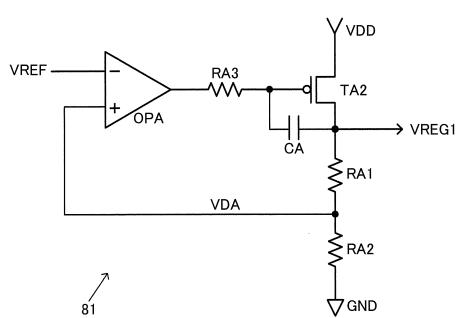

#### 【 0 0 8 3 】

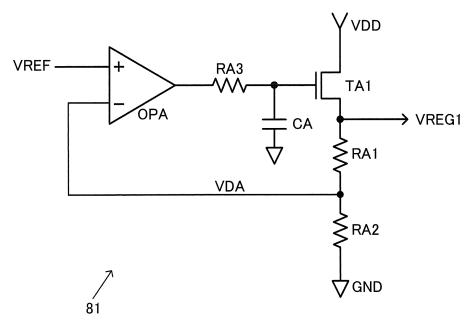

##### 5 . レギュレーター

図 1 6 にレギュレーター 8 1 の構成例を説明する。レギュレーター 8 1 は、V D D ノードと G N D ノードの間に直列に設けられた駆動用の N 型のトランジスター T A 1 及び抵抗 R A 1、R A 2 と、演算増幅器 O P A を含む。またレギュレーター 8 1 は、演算増幅器 O P A の出力端子側に設けられた抵抗 R A 3 及びキャパシター C A を含むことができる。演算増幅器 O P A の非反転入力端子には、基準電圧 V R E F が入力され、反転入力端子には、レギュレート電源電圧 V R E G 1 を抵抗 R A 1、R A 2 により電圧分割した電圧 V D A が入力される。そして演算増幅器 O P A の出力端子が、抵抗 R A 3 を介してトランジスター T A 1 のゲートに入力され、トランジスター T A 1 のドレンノードからレギュレート電源電圧 V R E G 1 が出力される。図 1 7 では、図 1 6 とは異なり、駆動用のトランジスターが P 型のトランジスター T A 2 となっており、演算増幅器 O P A の反転入力端子に基準電圧 V R E F が入力され、非反転入力端子に電圧 V D A が入力される。また図 1 7 では位相補償用のキャパシター C A の接続構成も図 1 6 とは異なっている。

10

#### 【 0 0 8 4 】

レギュレーター 8 2 の回路構成も、図 1 7 のレギュレーター 8 1 と同様の回路構成になる。但し、レギュレーター 8 2 では、図 1 6、図 1 7 の抵抗 R A 1、R A 2 の少なくとも 1 つが可変抵抗になっている。そしてトランジスター T A 1、T A 2 のドレンノードからレギュレート電源電圧 V R E G 2 が出力される。例えばレギュレーター 8 2 では、不揮発性メモリーにより実現される記憶部 1 0 0 に記憶される電圧設定情報に基づいて、抵抗 R A 1 及び抵抗 R A 2 の少なくとも一方の抵抗値が可変に設定される。これにより電圧が可変のレギュレート電源電圧 V R E G 2 が出力されるようになる。

20

#### 【 0 0 8 5 】

即ち、レギュレーター 8 1 では、抵抗 R A 1、R A 2 が例えば固定の抵抗値の抵抗となることで、固定電圧のレギュレート電源電圧 V R E G 1 を出力することになる。一方、レギュレーター 8 2 では、抵抗 R A 1、R A 2 の少なくとも一方が可変抵抗になることで、可変のレギュレート電源電圧 V R E G 2 を出力できるようになる。なおレギュレーター 8 1 においても抵抗 R A 1、R A 2 の抵抗値を可変に設定できるようにしてもよい。例えば製造や出荷時においてプロセス変動に対するレギュレート電源電圧 V R E G 1 の変動を補償するための抵抗値の調整ができるようになる。この場合にはレギュレーター 8 2 の方がレギュレーター 8 1 よりも、抵抗値の調整範囲が広くなり、レギュレート電源電圧の調整範囲も広くなる。

30

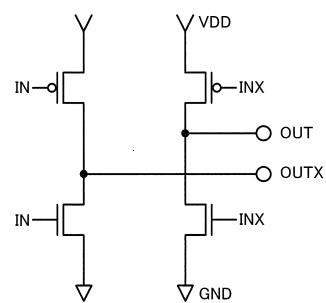

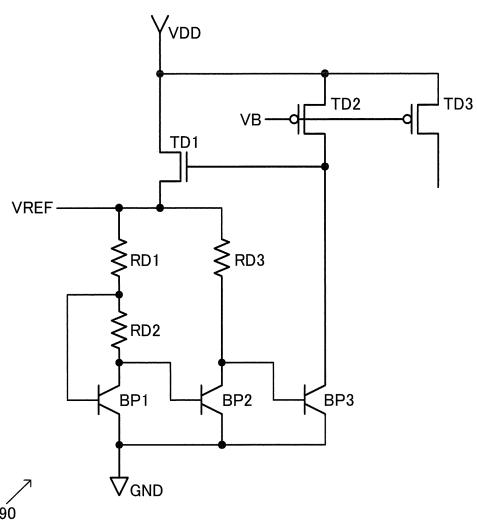

#### 【 0 0 8 6 】

##### 6 . 基準電圧生成回路、温度センサー、温度補償回路

図 1 8 に基準電圧生成回路 9 0 の構成例を示す。基準電圧生成回路 9 0 は、V D D ノードと G N D ノードの間に設けられる N 型のトランジスター T D 1、抵抗 R D 1、R D 2、R D 3、バイポーラトランジスター B P 1、B P 2 を含む。また基準電圧生成回路 9 0 は、バイアス電圧 B S がゲートに入力される P 型のトランジスター T D 1、T D 2 と、トランジスター T D 2 のドレンノードと G N D ノードとの間に設けられるバイポーラトランジスター B P 3 を含む。基準電圧生成回路 9 0 は、バンドギャップリファレンス回路であり、バンドギャップ電圧による基準電圧 V R E F を生成して出力する。例えば P N P 型のバイポーラトランジスター B P 1、B P 2 のベース・エミッター間電圧を V B E 1、V B E 2 とし、 $V B E = V B E 1 - V B E 2$  とする。基準電圧生成回路 9 0 は、例えば  $V R E F = K \times V B E + V B E 2$  となる基準電圧 V R E F を出力する。K は抵抗 R D 1、R D 2 の抵抗値により設定される。例えば V B E 2 は負の温度特性を有し、V B E は正の温度特性を有するため、抵抗 R D 1、R D 2 の抵抗値を調整することで、温度依存性のな

40

50

い定電圧の基準電圧 V R E F を生成できるようになる。そして生成される基準電圧 V R E F はグランド電圧を基準とした定電圧になる。なお基準電圧生成回路 9 0 は図 1 8 の構成に限定されず、例えばトランジスターの仕事関数差電圧を用いて基準電圧 V R E F を生成する回路などの種々の構成の回路を用いることができる。

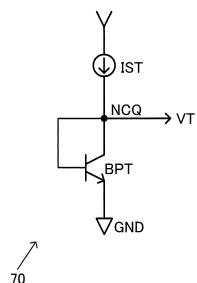

#### 【 0 0 8 7 】

図 1 9 に温度センサー 7 0 の構成例を示す。温度センサー 7 0 は、電源ノードと G N D ノードとの間に直列に設けられた電流源 I S T 、バイポーラトランジスター B P T を含む。バイポーラトランジスター B P T のコレクターノードとベースノードが接続されており、ダイオード接続になっている。これにより、温度センサー 7 0 の出力ノード N C Q から、温度依存性を有する温度検出電圧 V T が出力されるようになる。例えばベース・エミッタ間電圧の温度依存性により発生する負の温度特性の温度検出電圧 V T が出力されるようになる。なお温度センサー 7 0 の構成は図 1 9 の構成に限定されず、種々の変形実施が可能である。例えば温度センサー 7 0 の出力ノード N C Q とバイポーラトランジスター B P T のコレクターノードの間に抵抗を設けると共に、バイポーラトランジスター B P T のエミッターノードと G N D ノートの間に可変抵抗を設ける。このような構成にすることで、温度センサー 7 0 を用いて温度補償の 0 次補正を実現できるようになる。

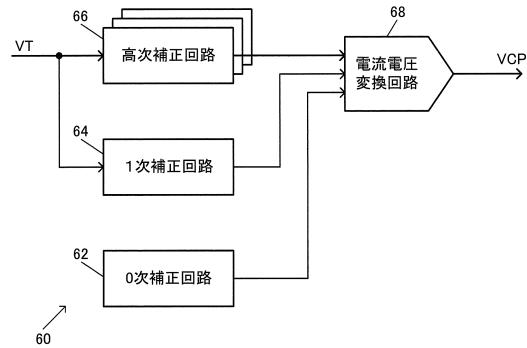

#### 【 0 0 8 8 】

図 2 0 に温度補償回路 6 0 の構成例を示す。温度補償回路 6 0 は、0 次補正回路 6 2 、1 次補正回路 6 4 、高次補正回路 6 6 、電流電圧変換回路 6 8 を含む。なお例えば 3 次補正、4 次補正、5 次補正などを行う場合には、高次補正回路 6 6 として、3 次補正回路、4 次補正回路、5 次補正回路などの複数の補正回路が設けられることになる。高次補正回路 6 6 は関数発生回路とも呼ばれ、温度補償電圧 V C P の特性を近似する多項式に対応する関数電流を発生する。例えば多項式は温度を变数とする関数である。

#### 【 0 0 8 9 】

温度補償回路 6 0 は、多項式近似によるアナログ方式の温度補償を行う。具体的には温度補償回路 6 0 は、温度を变数とする関数である多項式の近似によって温度補償電圧 V C P を生成して出力する。このために図 2 の記憶部 1 0 0 は、温度補償電圧 V C P の特性を近似する多項式の 0 次係数、1 次係数、高次係数を、0 次補正データ、1 次補正データ、高次補正データとして記憶する。そして 0 次補正回路 6 2 、1 次補正回路 6 4 、高次補正回路 6 6 は、記憶部 1 0 0 に記憶された 0 次補正データ、1 次補正データ、高次補正データに基づいて、0 次補正電流信号、1 次補正電流信号、高次補正電流信号を出力する。0 次補正電流信号、1 次補正電流信号、高次補正電流信号は、関数電流の 0 次成分信号、1 次成分信号、高次成分信号と言うことができる。そして 1 次補正回路 6 4 、高次補正回路 6 6 には、温度に対してリニアに変化する温度検出電圧 V T に基づいて、1 次補正電流信号、高次補正電流信号を生成して出力する。電流電圧変換回路 6 8 は、0 次補正電流信号、1 次補正電流信号、高次補正電流信号の加算処理を行うと共に電流電圧変換を行って、温度補償電圧 V C P を出力する。これにより多項式近似によるアナログ方式の温度補償が実現される。

#### 【 0 0 9 0 】

なお上述のように温度センサー 7 0 を用いて温度補償の 0 次補正を行う場合には、0 次補正回路 6 2 の構成は省略できる。この場合に温度検出電圧 V T のオフセット電圧の変動に起因する温度検出電圧特性のズレを補正するために、例えば 5 次の多項式近似の温度補償を行う温度補償回路 6 0 に、2 次補正回路や 4 次補正回路を設けるようにしてもよい。

#### 【 0 0 9 1 】

##### 7 . 発振器

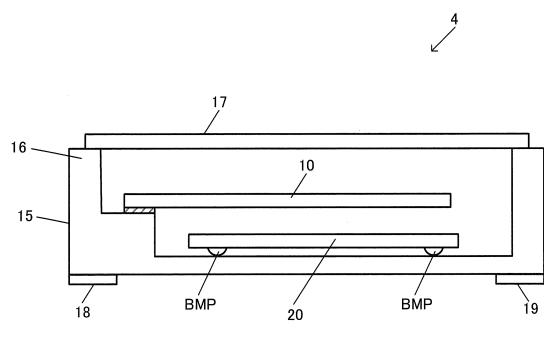

次に本実施形態の発振器 4 の構造例を説明する。図 2 1 に発振器 4 の第 1 の構造例を示す。発振器 4 は、振動子 1 0 と、集積回路装置 2 0 と、振動子 1 0 及び集積回路装置 2 0 を収容するパッケージ 1 5 を有する。パッケージ 1 5 は、例えばセラミック等により形成され、その内側に収容空間を有しており、この収容空間に振動子 1 0 及び集積回路装置 2 0 が収容されている。収容空間は気密封止されており、望ましくは真空に近い状態である

10

20

30

40

50

減圧状態になっている。パッケージ 15 により、振動子 10 及び集積回路装置 20 を衝撃、埃、熱、湿気等から好適に保護することができる。

#### 【 0 0 9 2 】

パッケージ 15 はベース 16 とリッド 17 を有する。具体的にはパッケージ 15 は、振動子 10 及び集積回路装置 20 を支持するベース 16 と、ベース 16 との間に収容空間を形成するようにベース 16 の上面に接合されたリッド 17 とにより構成されている。そして振動子 10 は、ベース 16 の内側に設けられた段差部に端子電極を介して支持されている。また集積回路装置 20 は、ベース 16 の内側底面に配置されている。具体的には集積回路装置 20 は、能動面がベース 16 の内側底面に向くように配置されている。能動面は集積回路装置 20 の回路素子が形成される面である。また集積回路装置 20 のパッドにバンプ B M P が形成されている。そして集積回路装置 20 は、導電性のバンプ B M P を介してベース 16 の内側底面に支持される。導電性のバンプ B M P は例えば金属バンプであり、このバンプ B M P やパッケージ 15 の内部配線や端子電極などを介して、振動子 10 と集積回路装置 20 が電気的な接続される。また集積回路装置 20 は、バンプ B M P やパッケージ 15 の内部配線を介して、発振器 4 の外部端子 18、19 に電気的に接続される。外部端子 18、19 は、パッケージ 15 の外側底面に形成されている。外部端子 18、19 は、外部配線を介して外部デバイスに接続される。外部配線は、例えば外部デバイスが実装される回路基板に形成される配線などである。これにより外部デバイスに対してクロック信号などを出力できるようになる。

10

#### 【 0 0 9 3 】

なお図 21 では、集積回路装置 20 の能動面が下方に向くように集積回路装置 20 がフリップ実装されているが、本実施形態はこのような実装には限定されない。例えば集積回路装置 20 の能動面が上方に向くように集積回路装置 20 を実装してもよい。即ち能動面が振動子 10 に対向するように集積回路装置 20 を実装する。

20

#### 【 0 0 9 4 】

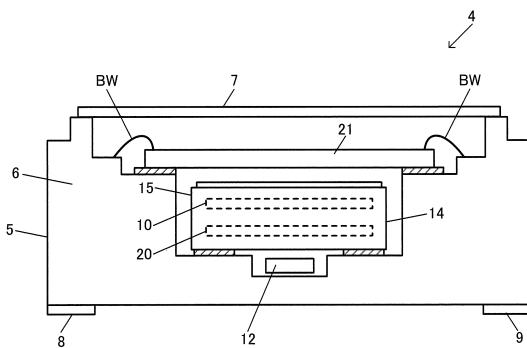

図 22 に発振器 4 の第 2 の構造例を示す。図 22 の発振器 4 は、振動子 10 と集積回路装置 20 と集積回路装置 21 を含む。また発振器 4 は、振動子 10 及び集積回路装置 20 を収容するパッケージ 15 と、パッケージ 15 及び集積回路装置 21 を収容するパッケージ 5 を含む。パッケージ 15、パッケージ 5 は、各々、第 1 パッケージ、第 2 パッケージである。第 1 パッケージ、第 2 パッケージは第 1 容器、第 2 容器と言うこともできる。

30

#### 【 0 0 9 5 】

そして本実施形態では、パッケージ 15 に収容される集積回路装置 20 が第 1 温度補償処理を行い、パッケージ 5 に収容される集積回路装置 21 が第 2 温度補償処理を行う。例えば振動子 10 及び集積回路装置 20 がパッケージ 15 に収容されることで、例えばアナログ方式の第 1 温度補償処理を行う温度補償型の発振器 14 が構成される。そして、アナログ方式の第 1 温度補償処理を行う発振器 14 と、デジタル方式の第 2 温度補償処理を行う集積回路装置 21 とがパッケージ 5 に収容されることで、高精度のクロック信号を生成する発振器 4 が構成される。集積回路装置 21 は、デジタル方式で微調整の第 2 温度補償処理を行う補正 I C と呼ぶこともできる。

#### 【 0 0 9 6 】

具体的にはパッケージ 5 は、例えばセラミック等により形成され、その内側に収容空間を有している。この収容空間に、振動子 10 及び集積回路装置 20 がパッケージ 15 に収容された発振器 14 と、集積回路装置 21 とが収容されている。収容空間は気密封止されており、望ましくは真空に近い状態である減圧状態になっている。パッケージ 5 により、集積回路装置 21 及び発振器 14 を衝撃、埃、熱、湿気等から好適に保護することができる。

40

#### 【 0 0 9 7 】

パッケージ 5 はベース 6 とリッド 7 を有する。具体的にはパッケージ 5 は、発振器 14 及び集積回路装置 21 を支持するベース 6 と、ベース 6 との間に収容空間を形成するようにベース 6 の上面に接合されたリッド 7 とにより構成されている。ベース 6 は、その内側

50

に、上面に開口する第1凹部と、第1凹部の底面に開口する第2凹部を有する。集積回路装置21は、第1凹部の底面に支持されている。例えば集積回路装置21は、端子電極を介して底面の段差部に支持されている。また発振器14は、第2凹部の底面に支持されている。例えば発振器14は、端子電極を介して底面の段差部に支持されている。またベース6は、第2凹部の底面に開口する第3凹部を有しており、この第3凹部に回路部品12が配置される。配置される回路部品12としては、例えばコンデンサーや温度センサーなどを想定できる。

#### 【0098】

集積回路装置21は、例えばポンディングワイヤーBWや、段差部に形成された端子電極や、パッケージ5の内部配線を介して、発振器14の端子に電気的に接続される。これにより発振器14からのクロック信号や温度検出信号を集積回路装置21に入力できるようになる。また集積回路装置21は、ポンディングワイヤーBWや、段差部に形成された端子電極や、パッケージ5の内部配線を介して、発振器4の外部端子8、9に電気的に接続される。外部端子8、9は、パッケージ5の外側底面に形成されている。外部端子8、9は、外部配線を介して外部デバイスに接続される。外部配線は、例えば外部デバイスが実装される回路基板に形成される配線などである。これにより外部デバイスに対してクロック信号などを出力できるようになる。なお発振器14の端子と外部端子8、9を電気的に接続するようにしてもよい。

10

#### 【0099】

なお図22では発振器14の上方向に集積回路装置21を配置しているが、発振器14の下方向に集積回路装置21を配置するようにしてもよい。ここで上方向はパッケージ5の底面からリッド7に向かう方向であり、下方向はその反対方向である。また発振器14の側方に集積回路装置21を設けてもよい。即ち発振器4の上面視において発振器14と集積回路装置21とが並ぶように配置する。

20

#### 【0100】

次に集積回路装置21について説明する。集積回路装置21は、発振器14で生成されたクロック信号である第1クロック信号が、基準クロック信号として入力されるクロック信号生成回路を含む。そしてクロック信号生成回路が生成したクロック信号が、発振器4の出力クロック信号として外部に出力される。例えば集積回路装置21のクロック信号生成回路は、発振器14からの第1クロック信号が基準クロック信号として入力されるフラクショナル-N型のPLL回路により構成される。このPLL回路は、第1クロック信号である基準クロック信号と、PLL回路の出力クロック信号を分周回路により分周したフィードバッククロック信号との位相比較を行う。そしてデルタシグマ変調回路を用いて小数の分周比を設定することで、フラクショナル-N型のPLL回路が実現される。また集積回路装置21が含む制御回路が、温度補償データに基づいて、PLL回路に設定される分周比データの補正処理を行うことで、第2温度補償処理が実現される。なお発振器14において行われる第1温度補償処理は、例えば多項式近似の温度補償処理により実現される。またクロック信号生成回路を、ダイレクトデジタルシンセサイザーにより構成してもよい。この場合には、第1クロック信号を基準クロック信号として動作するダイレクトデジタルシンセサイザーに対して、温度補償データにより補正された周波数制御データを入力することで、第2温度補償処理が実現される。

30

#### 【0101】

図22の発振器4によれば、振動子10を発振させる集積回路装置20が第1温度補償処理を行うことで、第1集積回路装置である集積回路装置20から出力される第1クロック信号の周波数温度特性での周波数変動量を小さくできる。そして第2集積回路装置である集積回路装置21が、集積回路装置20からの第1クロック信号に基づいてクロック信号を生成する際に第2温度補償処理を行う。このように集積回路装置20により第1温度補償処理を行った後に、集積回路装置21により第2温度補償処理を行うことで、温度計測結果の揺らぎなどを原因とする周波数のマイクロジャンプを小さくすることなどが可能になり、発振器4のクロック周波数の高精度化等を実現できるようになる。また図22の

40

50

発振器 4 では、集積回路装置 2 0 に設けられる温度センサーを用いて第 1 温度補償処理を行うと共に、この温度センサーの温度検出信号が、集積回路装置 2 0 から出力されて集積回路装置 2 1 に入力されるようにしてもよい。そして集積回路装置 2 1 が、入力された温度検出信号に基づいて第 2 温度補償処理を行ってもよい。このようにすれば、集積回路装置 2 0 での第 1 温度補償処理と、集積回路装置 2 1 での第 2 温度補償処理を、同じ温度センサーからの温度検出信号に基づいて行うことが可能になるため、より適正な温度補償処理を実現できるようになる。この場合に集積回路装置 2 0 に内蔵される温度センサーと振動子 1 0 との距離は、当該温度センサーと集積回路装置 2 1 との距離よりも短くなる。従って、デジタル方式の温度補償処理を行うことで発熱量が多い集積回路装置 2 1 と、振動子 1 0 との距離を離すことができ、集積回路装置 2 1 の発熱が温度センサーの温度検出結果に及ぼす悪影響を低減できる。従って、振動子 1 0 についての温度を、集積回路装置 2 0 に内蔵される温度センサーを用いて、より正確に計測することが可能になる。

#### 【 0 1 0 2 】

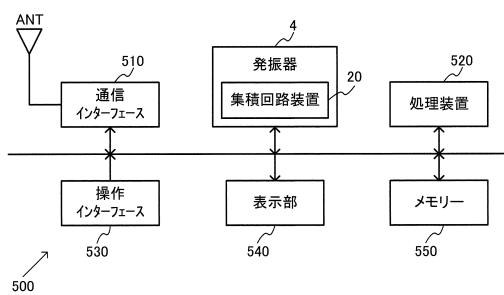

##### 8 . 電子機器、移動体

図 2 3 に、本実施形態の集積回路装置 2 0 を含む電子機器 5 0 0 の構成例を示す。電子機器 5 0 0 は、本実施形態の集積回路装置 2 0 と、集積回路装置 2 0 の発振回路 3 0 の発振信号に基づくクロック信号により動作する処理装置 5 2 0 を含む。具体的には電子機器 5 0 0 は、本実施形態の集積回路装置 2 0 を有する発振器 4 を含み、処理装置 5 2 0 は、発振器 4 からのクロック信号に基づいて動作する。また電子機器 5 0 0 は、アンテナ A N T、通信インターフェース 5 1 0、操作インターフェース 5 3 0、表示部 5 4 0、メモリー 5 5 0 を含むことができる。なお電子機器 5 0 0 は図 2 3 の構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【 0 1 0 3 】

電子機器 5 0 0 は、例えば基地局又はルーター等のネットワーク関連機器、距離、時間、流速又は流量等の物理量を計測する高精度の計測機器、生体情報を測定する生体情報測定機器、或いは車載機器などである。生体情報測定機器は例えば超音波測定装置、脈波計又は血圧測定装置等である。車載機器は自動運転用の機器等である。また電子機器 5 0 0 は、頭部装着型表示装置や時計関連機器などのウェアラブル機器、ロボット、印刷装置、投影装置、スマートフォン等の携帯情報端末、コンテンツを配信するコンテンツ提供機器、或いはデジタルカメラ又はビデオカメラ等の映像機器などであってもよい。

#### 【 0 1 0 4 】

また電子機器 5 0 0 としては、5 G などの次世代移動通信システムに用いられる機器がある。例えば次世代移動通信システムの基地局、リモートディオヘッド( R R H )又は携帯通信端末などの種々の機器に本実施形態の集積回路装置 2 0 を用いることができる。次世代移動通信システムでは、時刻同期等のために高精度のクロック周波数が要望されており、高精度のクロック信号を生成できる本実施形態の集積回路装置 2 0 の適用例として好適である。

#### 【 0 1 0 5 】

通信インターフェース 5 1 0 は、アンテナ A N T を介して外部からデータを受信したり、外部にデータを送信する処理を行う。プロセッサーである処理装置 5 2 0 は、電子機器 5 0 0 の制御処理や、通信インターフェース 5 1 0 を介して送受信されるデータの種々のデジタル処理などを行う。処理装置 5 2 0 の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。操作インターフェース 5 3 0 は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイなどにより実現できる。表示部 5 4 0 は、各種の情報を表示するものであり、液晶や有機 E L などのディスプレイにより実現できる。メモリー 5 5 0 は、データを記憶するものであり、その機能は R A M や R O M などの半導体メモリーにより実現できる。

#### 【 0 1 0 6 】

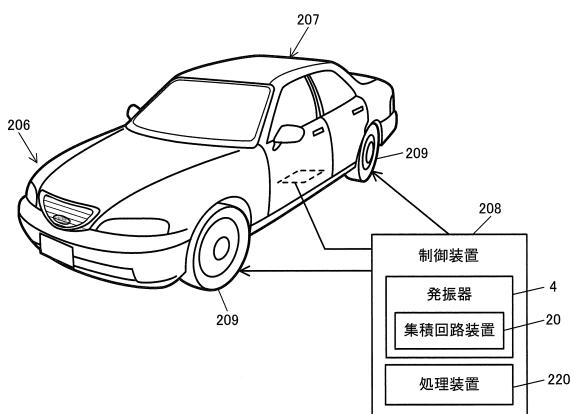

図 2 4 に、本実施形態の集積回路装置 2 0 を含む移動体の例を示す。移動体は、本実施

10

20

30

40

50

形態の集積回路装置 20 と、集積回路装置 20 の発振回路 30 の発振信号に基づくクロック信号により動作する処理装置 220 を含む。具体的には移動体は、本実施形態の集積回路装置 20 を有する発振器 4 を含み、処理装置 220 は、発振器 4 からのクロック信号に基づいて動作する。本実施形態の集積回路装置 20 は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器を備えて、地上や空や海上を移動する機器・装置である。図 24 は移動体の具体例としての自動車 206 を概略的に示している。自動車 206 には、本実施形態の集積回路装置 20 が組み込まれる。具体的には、移動体である自動車 206 は、制御装置 208 を含み、制御装置 208 は、本実施形態の集積回路装置 20 を含む発振器 4 と、発振器 4 により生成されたクロック信号に基づき動作する処理装置 220 を含む。制御装置 208 は、例えば車体 207 の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪 209 のブレーキを制御する。例えば制御装置 208 により、自動車 206 の自動運転を実現してもよい。なお本実施形態の集積回路装置 20 が組み込まれる機器は、このような制御装置 208 には限定されず、自動車 206 等の移動体に設けられるメーターパネル機器やナビゲーション機器などの種々の車載機器に組み込むことが可能である。

#### 【0107】

以上に説明したように本実施形態の集積回路装置は、振動子の一端に電気的に接続される第 1 パッドと、振動子の他端に電気的に接続される第 2 パッドと、第 1 パッド及び第 2 パッドに電気的に接続され、振動子を発振させることで発振信号を生成する発振回路と、発振信号に基づいてクロック信号を出力する出力回路を含む。発振回路は、集積回路装置の第 1 辺、第 1 辺に交差する第 2 辺、第 1 辺の対辺である第 3 辺及び第 2 辺の対辺である第 4 辺のうちの第 1 辺に沿って配置される。そして第 1 パッド及び第 2 パッドは、平面視において、第 1 辺に沿って発振回路内に配置され、出力回路は、第 2 边に沿って配置される。

#### 【0108】

本実施形態によれば集積回路装置は、振動子に電気的に接続される第 1 パッド及び第 2 パッドと、発振信号を生成する発振回路と、発振信号に基づいてクロック信号を出力する出力回路を含む。そして発振回路は、集積回路装置の第 1 辺に沿って配置され、第 1 パッド及び第 2 パッドは、第 1 辺に沿って発振回路内に配置され、出力回路は第 2 边に沿って配置される。このように発振回路が第 1 边に沿って配置され、出力回路が第 1 边に交差する第 2 边に沿って配置されることで、放射ノイズ等のノイズによる悪影響を低減できる。また第 1 パッド及び第 2 パッドが第 1 边に沿って発振回路内に配置されることで、例えば第 1 パッド、第 2 パッドに接続される第 1 信号線、第 2 信号線の寄生抵抗や寄生容量に起因する発振特性の劣化等を抑制でき、高精度のクロック信号を生成できるようになる。従って、放射ノイズなどのノイズを低減しながら発振信号に基づく高精度のクロック信号を生成できる集積回路装置の提供が可能になる。

#### 【0109】

また本実施形態では、出力回路は、第 2 边と第 3 辺とが交差するコーナー部に配置されてもよい。

#### 【0110】

このようにすれば、出力回路を、集積回路装置のコーナー部に寄せて配置できるようになるため、コンパクトで効率的なレイアウト配置が可能になる。

#### 【0111】

また本実施形態では、温度センサーからの温度検出電圧に基づいて、発振回路の発振周波数の温度補償を行う温度補償回路を含み、第 1 边から第 3 辺に向かう方向を第 1 方向とし、第 2 边から第 4 边に向かう方向を第 2 方向としたときに、温度補償回路は、発振回路の第 1 方向であって、出力回路の第 2 方向に配置されてもよい。

#### 【0112】

このようにすれば、発振回路の第 1 方向であって出力回路の第 2 方向の領域を有効活用

10

20

30

40

50

して、温度補償回路を配置できるようになる。

**【0113】**

また本実施形態では、温度補償回路を制御する制御回路を含み、制御回路は、温度補償回路の第2方向に配置されてもよい。

**【0114】**

このようにすれば、温度補償回路を制御する制御回路を、温度補償回路の第2方向において近くに配置できるようになり、制御回路からの制御信号をショートパスで温度補償回路に入力することが可能になる。

**【0115】**

また本実施形態では、温度補償回路にレギュレート電源電圧を供給するレギュレーターを含み、レギュレーターは、温度補償回路の第1方向に配置されてもよい。 10

**【0116】**

このようにすれば、レギュレーターが生成したレギュレート電源電圧をショートパスで温度補償回路に入力できるようになり、レギュレート電源電圧を供給する電源線の寄生抵抗や寄生容量を低減することなどが可能になる。

**【0117】**

また本実施形態では、1レギュレーターに基準電圧を供給する基準電圧生成回路と、グランド電圧が供給されるグランドパッドと、を含み、基準電圧生成回路は、グランドパッドとレギュレーターとの間に配置されてもよい。

**【0118】**

このようにすれば、グランドパッドからのグランド電圧をショートパスで基準電圧生成回路に供給できるようになり、基準電圧生成回路は、安定した電位のグランド電圧を基準にして、基準電圧を生成できるようになる。 20

**【0119】**

また本実施形態では、温度センサーと、温度センサーからの温度検出電圧に基づいて、発振回路の発振周波数の温度補償を行う温度補償回路と、を含み、第1辺から第3辺に向かう方向を第1方向とし、第2辺から第4辺に向かう方向を第2方向としたときに、温度センサーは、発振回路の第2方向に配置されてもよい。

**【0120】**

このようにすれば、発振回路内に配置される第1パッド又は第2パッドと温度センサーとの距離を近づけることができ、振動子の温度を、温度センサーを用いて、より適切に検出できるようになる。 30

**【0121】**

また本実施形態では、温度センサーは、第1辺と第4辺が交差するコーナー部に配置されてもよい。

**【0122】**

このようにすれば、第2辺に沿って配置される出力回路から離れた位置に温度センサーを配置できるようになり、出力回路からの熱が温度センサーの温度検出結果に悪影響を与えてしまうのを抑制できる。

**【0123】**

また本実施形態では、クロック信号を出力するクロックパッドを含み、クロックパッドは、出力回路内に配置されてもよい。 40

**【0124】**

このようにすれば、出力回路の回路配置領域を有効利用して、クロックパッドを配置できるようになるため、効率的なレイアウト配置が可能になる。

**【0125】**

また本実施形態では、電源電圧が供給される電源パッドと、グランド電圧が供給されるグランドパッドと、を含み、電源パッドは、第2辺に沿って配置され、グランドパッドは、第4辺に沿って配置されてもよい。

**【0126】**

10

20

30

40

50

このようにすれば、電源パッドを出力回路の近くに配置できるようになり、出力回路により発生する電源ノイズの悪影響を低減できる。またグランドパッドについては出力回路から遠い位置に配置されるようになり、グランド電圧の変動による悪影響を低減できる。

#### 【0127】

また本実施形態では、発振回路は、第1の辺に沿った方向を長手方向として配置されてもよい。

#### 【0128】

このようにすれば第1辺から所定幅の領域に発振回路を配置できるようになり、効率的なレイアウト配置が可能になる。

#### 【0129】

また本実施形態では、出力回路は、第2辺に沿った方向を長手方向として配置されてもよい。

#### 【0130】

このようにすれば第2辺から所定幅の領域に出力回路を配置できるようになり、効率的なレイアウト配置が可能になる。

#### 【0131】

また本実施形態は、上記に記載の集積回路装置と、振動子を含む発振器に関係する。

#### 【0132】

また本実施形態は、上記に記載の集積回路装置と、クロック信号により動作する処理装置を含む電子機器に関係する。

10

#### 【0133】

また本実施形態は、上記に記載の集積回路装置と、クロック信号により動作する処理装置を含む移動体に関係する。

#### 【0134】

なお、上記のように本実施形態について詳細に説明したが、本開示の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本開示の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本開示の範囲に含まれる。また集積回路装置、発振器、電子機器、移動体の構成・動作等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

20

#### 【符号の説明】

#### 【0135】

T 1、T 2、T 7 …パッド、T 3 …電源パッド、T 4 …グランドパッド、

T 5、T 6 …クロックパッド、L 1、L 2 …信号線、C N 1 ~ C N 4 …コーナー部、

S D 1、S D 2、S D 3、S D 4 …辺、D R 1、D R 2、D R 3、D R 4 …方向、

T E 3、T E 4、T E 5、T E 6、T E 7 …外部端子、L P W 1、L P W 2 …電源線、

C K、C K X …クロック信号、O S C …発振信号、V C P …温度補償電圧、

V R E G 1、V R E G 2 …レギュレート電源電圧、E I N …外部入力信号、

V R E F …基準電圧、V T …温度検出電圧、V R 1 ~ V R n、V R B …基準電圧、

C 1、C 2、C 3 1 ~ C 3 n、C 4、C A …キャパシター、I S、I S T …電流源、

B P、B P 1、B P 2、B P 3、B P T …バイポーラトランジスター、

R A 1 ~ R A 3、R B、R C 1、R C 2、R D 1 ~ R D 3、R Q …抵抗、

O P A …演算増幅器、T A 1、T A 2、T D 1、T D 2、T D 3 …トランジスター、

4 …発振器、5 …パッケージ、6 …ベース、7 …リッド、8、9 …外部端子、

10 …振動子、12 …回路部品、14 …発振器、15 …パッケージ、

16 …ベース、17 …リッド、18、19 …外部端子、

20、21 …集積回路装置、30 …発振回路、32 …駆動回路、

34 …基準電圧供給回路、36、37 …可変容量回路、40 …出力回路、

30

40

50

4 2 ... バッファー回路、4 3 ... 波形整形回路、4 4 ... ディバイダー、

4 5 ... レベルシフター & プリドライバー、4 6 ... 出力ドライバー、

5 0 ... 制御回路、6 0 ... 温度補償回路、6 2 ... 0次補正回路、6 4 ... 1次補正回路、

6 6 ... 高次補正回路、6 8 ... 電流電圧変換回路、7 0 ... 温度センサー、

8 0 ... 電源回路、8 1、8 2 ... レギュレーター、

9 0 ... 基準電圧生成回路、1 0 0 ... 記憶部、

2 0 6 ... 自動車、2 0 7 ... 車体、2 0 8 ... 制御装置、2 0 9 ... 車輪、

2 2 0 ... 处理装置、5 0 0 ... 電子機器、5 1 0 ... 通信インターフェース、

5 2 0 ... 处理装置、5 3 0 ... 操作インターフェース、5 4 0 ... 表示部、

5 5 0 ... メモリー

10

【四面】

【図1】

【図2】

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図 1 5】

【図 1 6】

10

20

【図 1 7】

30

【図 1 8】

40

50

【図 19】

【図 20】

10

【図 21】

【図 22】

20

【図 23】

【図 24】

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 01 L      27/04      V

コーエプソン株式会社内

(72)発明者 井伊 巨樹

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 板坂 洋佑

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 及川 尚人

(56)参考文献 特開2016-025452 (JP, A)

特開2018-098428 (JP, A)

特開平05-048003 (JP, A)

特開2007-067967 (JP, A)

特開2016-134738 (JP, A)

特開2017-175202 (JP, A)

特開2006-191517 (JP, A)

特開2006-054269 (JP, A)

中国特許出願公開第107681980 (CN, A)

特開2016-134889 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 03 B      5 / 30 - 5 / 42

H 01 L      21 / 822