(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7175703号**

**(P7175703)**

(45)発行日 令和4年11月21日(2022.11.21)

(24)登録日 令和4年11月11日(2022.11.11)

(51)国際特許分類

|        |                |        |             |

|--------|----------------|--------|-------------|

| H 04 N | 5/365(2011.01) | H 04 N | 5/365       |

| H 04 N | 5/225(2006.01) | H 04 N | 5/225 3 0 0 |

| H 04 N | 5/232(2006.01) | H 04 N | 5/232 4 1 1 |

| H 04 N | 5/243(2006.01) | H 04 N | 5/243       |

| H 04 N | 5/378(2011.01) | H 04 N | 5/232 2 9 0 |

請求項の数 19 (全26頁) 最終頁に続く

(21)出願番号 特願2018-196072(P2018-196072)

(22)出願日 平成30年10月17日(2018.10.17)

(65)公開番号 特開2020-65175(P2020-65175A)

(43)公開日 令和2年4月23日(2020.4.23)

審査請求日 令和3年10月4日(2021.10.4)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281弁理士法人大塚国際特許事務所

三本杉 英昭

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 鈴木 明

最終頁に続く

(54)【発明の名称】 撮像装置及びその制御方法、プログラム、記憶媒体

**(57)【特許請求の範囲】****【請求項1】**

光電変換を行う複数の画素が行列状に配置された画素領域と、

前記画素領域の各画素列に並列に複数配置され、同じ画素列に配置された異なる複数画素の信号がそれぞれ出力される複数の列出力線と、

前記複数の列出力線に1対1で接続された複数の列回路と、

前記複数の列回路の特性差に基づいて画像データを補正する補正手段と、

同じ画素列に配置された前記複数の列出力線のうちの第1の列出力線に画像データ生成用の信号を出し、前記同じ画素列に配置された前記複数の列出力線のうちの前記第1の列出力線とは異なる第2の列出力線に前記補正手段による補正データ生成用の信号を出力するように制御する制御手段と、

を有することを特徴とする撮像装置。

**【請求項2】**

前記制御手段は、前記第1の列出力線に第1のモードにより得られる画像データ生成用の信号を出し、前記第2の列出力線に前記第1のモードとは異なる第2のモードに対応する補正データ生成用の信号を出力するように制御することを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記制御手段は、さらに前記第2の列出力線に前記第2のモードにより得られる画像データ生成用の信号を出力するように制御するとともに、前記補正手段が前記第2のモード

に対応する補正データを用いて前記第2のモードにより得られた画像データを補正するように制御することを特徴とする請求項2に記載の撮像装置。

**【請求項4】**

前記第1のモードと前記第2のモードは、ISO感度が異なることを特徴とする請求項2または3に記載の撮像装置。

**【請求項5】**

前記第1のモードと前記第2のモードは、AD変換のbit数が異なることを特徴とする請求項2乃至4のいずれか1項に記載の撮像装置。

**【請求項6】**

前記第1のモードと前記第2のモードは、列方向の画素の混合数が異なることを特徴とする請求項2乃至5のいずれか1項に記載の撮像装置。 10

**【請求項7】**

前記第1のモードと前記第2のモードは、行方向の画素の混合数が異なることを特徴とする請求項2乃至6のいずれか1項に記載の撮像装置。

**【請求項8】**

前記画像データ生成用の信号と前記補正データ生成用の信号は、異なる出力部を介して出力されることを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。

**【請求項9】**

前記列回路は、前記列回路ごとにゲインが設定されることを特徴とする請求項1乃至8のいずれか1項に記載の撮像装置。 20

**【請求項10】**

前記画像データ生成用の信号の出力期間と前記補正データ生成用の信号の出力期間は重複することを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

**【請求項11】**

前記画像データ生成用の信号の出力期間と前記補正データ生成用の信号の出力期間は重複しないことを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

**【請求項12】**

前記制御手段は、前記画像データ生成用の信号または前記補正データ生成用の信号の出力期間のいずれかにおいて、使用しない前記列回路をオフするように制御することを特徴とする請求項1乃至11のいずれか1項に記載の撮像装置。 30

**【請求項13】**

前記制御手段は、前記第1または第2の列出力線のいずれかを用いて画素の信号を読み出すモードと、前記第1および第2の列出力線を用いて画素の信号を読み出すモードとを有することを特徴とする請求項1乃至12のいずれか1項に記載の撮像装置。

**【請求項14】**

前記補正手段は、前記補正データ生成用の信号を用いて得られた補正值を用いて前記画像データを補正するモードと、前記補正データ生成用の信号を用いないで得られた補正值を用いて前記画像データを補正するモードとを有することを特徴とする請求項1乃至13のいずれか1項に記載の撮像装置。

**【請求項15】**

前記補正手段は、撮像素子に内蔵されることを特徴とする請求項1乃至14のいずれか1項に記載の撮像装置。

**【請求項16】**

前記補正データ生成用の信号は、前記画素領域において、光電変換素子からの信号を転送しない読み出しにより得られることを特徴とする請求項1乃至15のいずれか1項に記載の撮像装置。

**【請求項17】**

光電変換を行う複数の画素が行列状に配置された画素領域と、前記画素領域の各画素列に並列に複数配置され、同じ画素列に配置された異なる複数画素の信号がそれぞれ出力される複数の列出力線と、前記複数の列出力線に1対1で接続された複数の列回路と、を備

10

20

30

40

50

える撮像装置を制御する方法であって、

前記複数の列回路の特性差に基づいて画像データを補正する補正工程と、

同じ画素列に配置された前記複数の列出力線のうちの第1の列出力線に画像データ生成用

の信号を出力し、前記同じ画素列に配置された前記複数の列出力線のうちの前記第1の列

出力線とは異なる第2の列出力線に前記補正工程による補正データ生成用の信号を出力す

るように制御する制御工程と、

を有することを特徴とする撮像装置の制御方法。

【請求項18】

請求項17に記載の制御方法をコンピュータに実行させるためのプログラム。

【請求項19】

請求項17に記載の制御方法をコンピュータに実行させるためのプログラムを記憶した

コンピュータが読み取り可能な記憶媒体。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置及びその制御方法に関する。

【背景技術】

【0002】

撮像装置に使用されるCMOSセンサー等の撮像素子では、画素の不均一性による垂直

方向、水平方向のシェーディングが存在する。特に、水平方向においては、列毎の読み出

し回路、メモリの不均一性あるいはメモリから出力線を介して信号が出力されるまでの距

離に応じてシェーディングが存在する。例えば、特許文献1には、撮像素子が出力する信

号を撮像装置が有する補正機能によって補正することで均一化する撮像装置が開示されて

いる。

20

【先行技術文献】

【特許文献】

【0003】

【文献】特開2010-263553号公報

【発明の概要】

【発明が解決しようとする課題】

30

【0004】

しかしながら、上述の特許文献に開示された従来技術では、ゲイン制御などの撮像素子

の駆動条件が変わった場合や、静止画や動画などの駆動モードの違いに対応するために列

毎の補正值を駆動条件毎に予め記憶する必要がある。この場合、記憶するためのROMな

どの容量を圧迫するなどのシステム負荷が生じる。また、撮影条件が変化したときに補正

値を生成する場合には、生成するために画像撮影を中断する必要があり、動画などではフ

レームがブラックアウトするという問題もある。

【0005】

本発明は上述した課題に鑑みてなされたものであり、その目的は、装置の負荷の増加を

抑制しつつ、撮影画像の画質を向上させることができる撮像装置を提供することである。

40

【課題を解決するための手段】

【0006】

本発明に係わる撮像装置は、光電変換を行う複数の画素が行列状に配置された画素領域

と、前記画素領域の各画素列に並列に複数配置され、同じ画素列に配置された異なる複数

画素の信号がそれぞれ出力される複数の列出力線と、前記複数の列出力線に1対1で接続

された複数の列回路と、前記複数の列回路の特性差に基づいて画像データを補正する補正

手段と、同じ画素列に配置された前記複数の列出力線のうちの第1の列出力線に画像データ

生成用の信号を出力し、前記同じ画素列に配置された前記複数の列出力線のうちの前記

第1の列出力線とは異なる第2の列出力線に前記補正手段による補正データ生成用の信号

を出力するように制御する制御手段と、を有することを特徴とする。

50

**【発明の効果】****【0007】**

本発明によれば、装置の負荷の増加を抑制しつつ、撮影画像の画質を向上させることができる撮像装置を提供することが可能となる。

**【図面の簡単な説明】****【0008】**

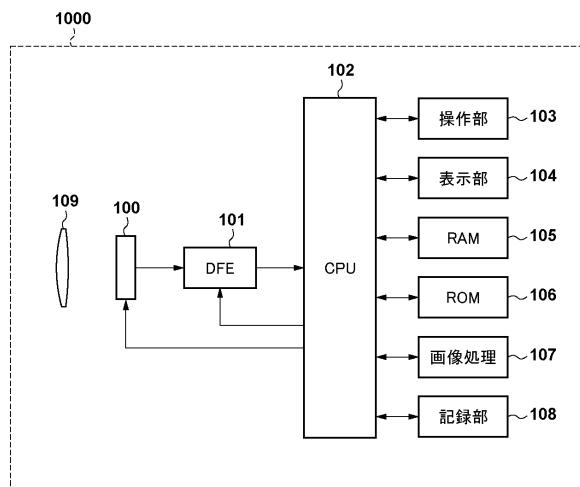

【図1】本発明の第1の実施形態に係わる撮像装置の構成を示す図。

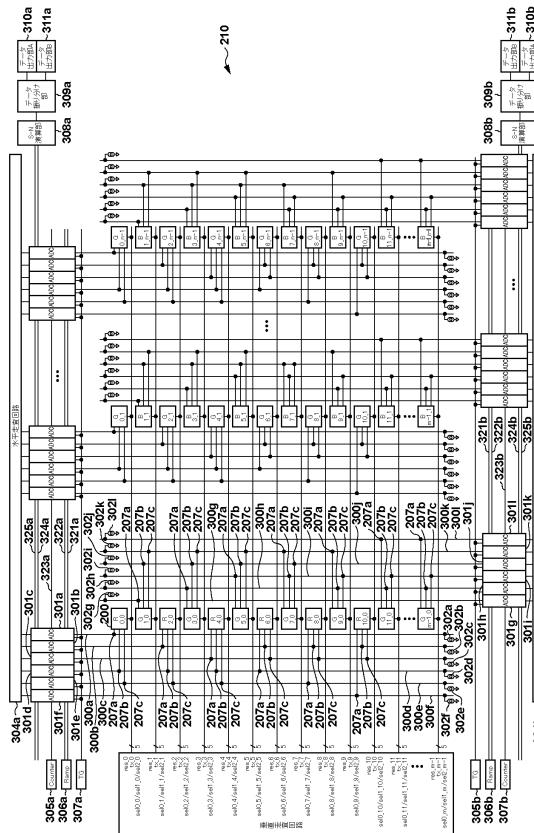

【図2A】第1の実施形態における像素子の構成を示す図。

【図2B】第1の実施形態における像素子の構成を示す図。

【図2C】第1の実施形態における像素子の構成を示す図。

【図2D】第1の実施形態における像素子の構成を示す図。

【図2E】第1の実施形態における像素子の構成を示す図。

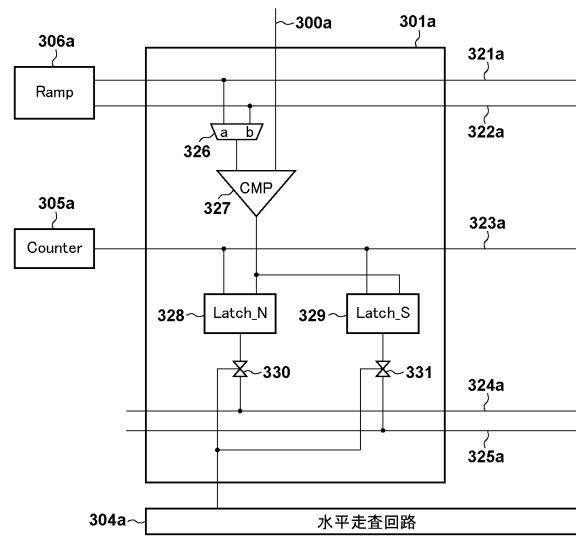

【図3】第1の実施形態におけるDFEの構成を示す図。

【図4】第1の実施形態に係わる撮像装置の動作を示すフローチャート。

【図5】第1の実施形態における撮像装置の動作の概念を示す図。

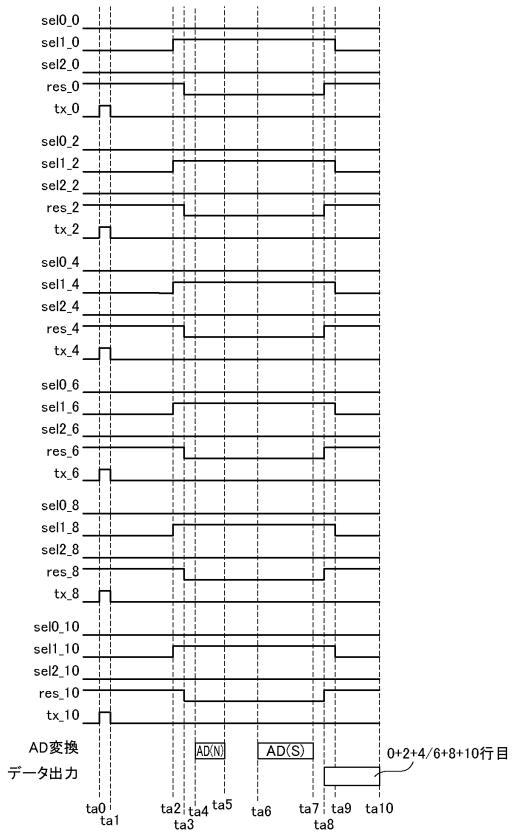

【図6A】第1の実施形態における像素子の動作を示すタイミングチャート。

【図6B】第1の実施形態における像素子の動作を示すタイミングチャート。

【図7】第1の実施形態における像素子の動作の概念を示す図。

【図8】第1の実施形態における像素子の動作の概念を示す図。

【図9】第1の実施形態におけるDFEの動作の概念を示す図。

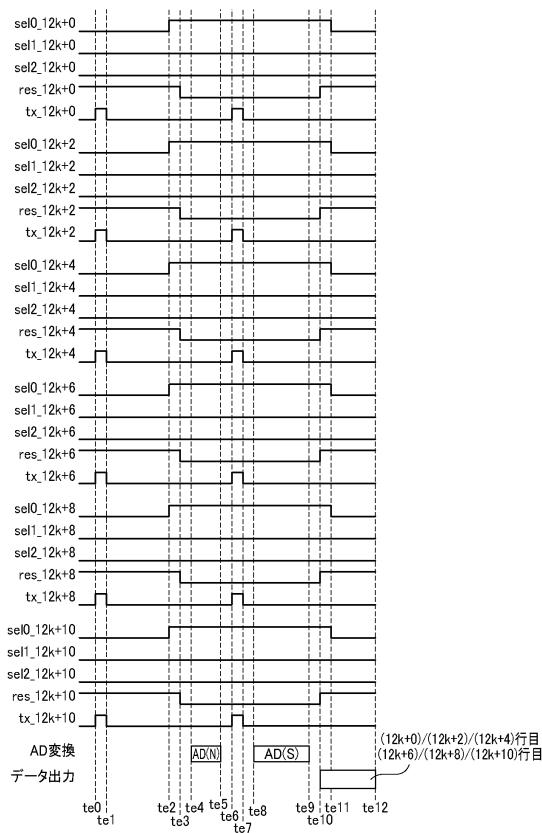

【図10A】第1の実施形態における像素子の動作を示すタイミングチャート。

【図10B】第1の実施形態における像素子の動作を示すタイミングチャート。

【図10C】第1の実施形態における像素子の動作を示すタイミングチャート。

【図11】第1の実施形態におけるDFEの動作の概念を示す図。

【図12】第2の実施形態に係わる撮像装置の構成を示す図。

【図13】第2の実施形態における像素子の構成を示す図。

【図14】第2の実施形態における画像補正回路の構成を示す図。

**【発明を実施するための形態】****【0009】**

以下、本発明の実施形態について、添付図面を参照して詳細に説明する。

**【0010】****<第1の実施形態>**

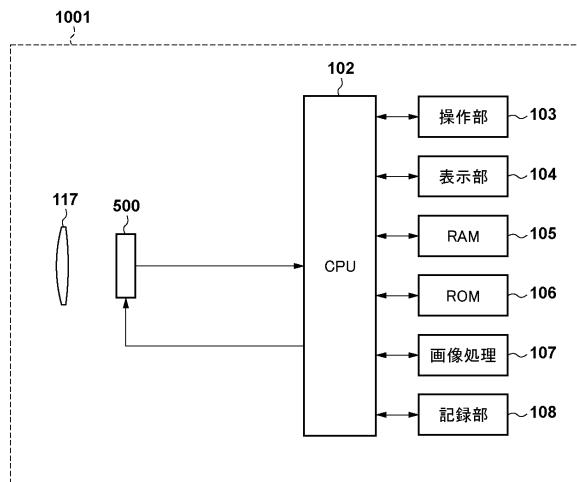

図1は、本発明の第1の実施形態に係わる撮像装置の構成を示すブロック図である。本実施形態の撮像装置1000は、例えばデジタルカメラであり、静止画像撮影機能及び動画像撮影機能を有している。撮像装置1000は、撮像装置1000を統括的に制御するCPU(Central Processing Unit)102、及び撮影レンズ109を通過した光学像が結像される像素子100を有する。

**【0011】**

像素子100は、これに結像された光学像を電気信号(アナログ画素信号)に変換後、所定の量子化ビット数に応じてデジタル画像データに変換して出力する。DFE(Digital Front End)101は、像素子100からデータを受信し、後述する画像への列回路ごとの特性差に基づいて画像データを補正する補正処理を行い、CPU102へデータを送信する。

**【0012】**

RAM(Random Access Memory)105は、像素子100から出力される画像データ及び画像処理部107で処理された画像データを記憶するための画像メモリである。RAM105は、CPU102のワークメモリとしても用いられる。本実施形態では、画像メモリ及びワークメモリとしてRAM105を用いるが、アクセス速度に問題ないものであれば、他のメモリを用いてもよい。

**【0013】**

10

20

30

40

50

R O M ( R e a d O n l y M e m o r y ) 1 0 6 には、 C P U 1 0 2 で動作するプログラムが格納される。本実施形態では、 R O M 1 0 6 としてフラッシュ R O M が用いられるが、 アクセス速度に問題がないものであれば、他のメモリを用いてもよい。

#### 【 0 0 1 4 】

画像処理部 1 0 7 は、本実施形態における静止画像及び動画像の補正処理や、画像の圧縮処理等を行う。操作部 1 0 3 は、撮像装置 1 0 0 0 を起動するメインスイッチや、ユーザーが撮像装置 1 0 0 0 に静止画や動画の撮影命令を行う撮影スイッチを含み、撮像条件等を設定する際にも用いられる。表示部 1 0 4 は、 C P U 1 0 2 の制御下で、画像データに応じた静止画像又は動画像の表示を行うとともに、メニュー等の表示を行う。

#### 【 0 0 1 5 】

記録部 1 0 8 は、例えば不揮発性メモリ又はハードディスクであり、画像データ等が記録される。本実施形態において記録部 1 0 8 は、装置に内蔵される形で記載されているが、コネクタ等を介した着脱可能なメモリーカードなどの外部記録媒体でもよい。

#### 【 0 0 1 6 】

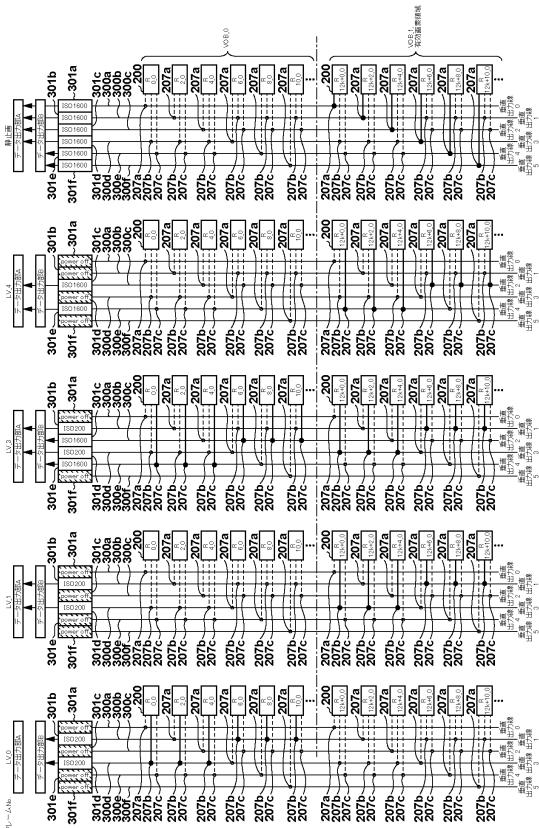

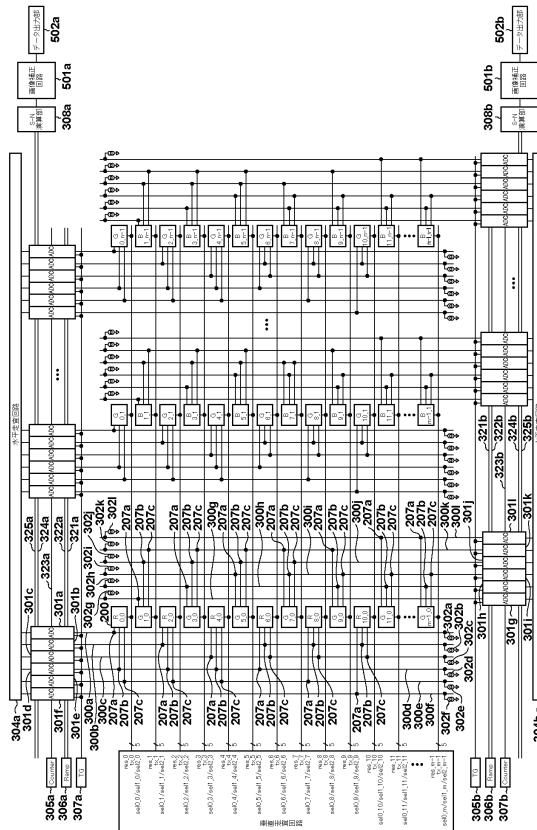

図 2 A ~ 図 2 E は、撮像素子 1 0 0 の回路構成の一例を示す図である。図 2 A に示すように光電変換素子を有する画素 2 0 0 が画素 R 0 \_ 0 ~ B m - 1 \_ n - 1 ( m, n は任意の整数 ) のように行列状に複数配置されている。画素 2 0 0 に示す R は赤色、 G は緑色、 B は青色のカラーフィルタが各画素に配置されることを意味する。また、 R ( G , B ) p - q は、画素部 2 1 0 における第 p 行第 q 列の画素であることを示す。

#### 【 0 0 1 7 】

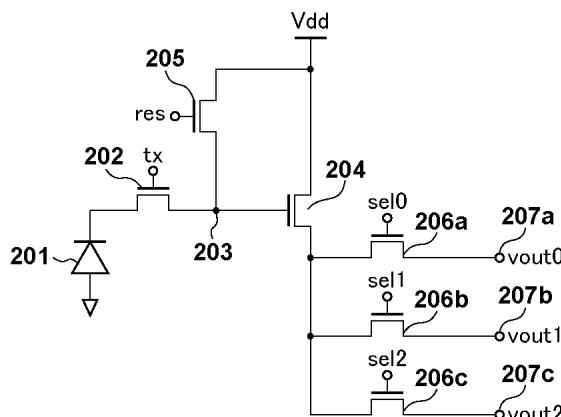

ここで、画素 2 0 0 の 1 画素毎の構成について図 2 B を用いて説明する。フォトダイオード ( P D ) 2 0 1 は、入射した光信号を光電変換し、露光量に応じた電荷を蓄積する。制御信号 t x をハイレベルにすることにより転送ゲート 2 0 2 がオン ( 導通状態 ) になり、 P D 2 0 1 に蓄積されている電荷がフローティングディフュージョン部 ( F D 部 ) 2 0 3 に転送される。 F D 部 2 0 3 は、増幅 M O S トランジスタ 2 0 4 のゲートに接続されている。増幅 M O S トランジスタ 2 0 4 は、 P D 2 0 1 から F D 部 2 0 3 に転送されてきた電荷量に応じた電圧信号を出力する。

#### 【 0 0 1 8 】

リセットスイッチ 2 0 5 は、 F D 部 2 0 3 や P D 2 0 1 の電荷をリセットするためのスイッチである。制御信号 r e s をハイレベルにすることによりリセットスイッチ 2 0 5 がオン ( 導通状態 ) になり、 F D 部 2 0 3 がリセットされる。また、 P D 2 0 1 の電荷をリセットする場合には、制御信号 t x 及び制御信号 r e s を同時にハイレベルにすることにより、転送ゲート 2 0 2 及びリセットスイッチ 2 0 5 を両方オンし、 F D 部 2 0 3 経由で P D 2 0 1 をリセットする。

#### 【 0 0 1 9 】

画素選択スイッチ 2 0 6 a ~ 2 0 6 c は、それぞれ制御信号 s e l 0 ~ s e l 2 をハイレベルとすることによりオン ( 導通状態 ) になり、増幅 M O S トランジスタ 2 0 4 と画素 2 0 0 の出力端子 v o u t 0 ( 2 0 7 a ) ~ v o u t 2 ( 2 0 7 c ) とを接続する。これにより、増幅 M O S トランジスタ 2 0 4 で電圧に変換された画素信号が画素 2 0 0 の出力端子 v o u t 0 ( 2 0 7 a ) ~ v o u t 2 ( 2 0 7 c ) に出力される。

#### 【 0 0 2 0 】

本実施形態の撮像素子では、後述する制御により、駆動条件によって行毎に s e l 0 ~ s e l 2 のいずれかがオンになり、出力端子 v o u t 0 ( 2 0 7 a ) ~ v o u t 2 ( 2 0 7 c ) のいずれかから画素信号が出力される。

#### 【 0 0 2 1 】

図 2 A に戻り、垂直走査回路 3 0 3 は、制御信号 r e s , t x , s e l 0 ~ 2 等を各画素 2 0 0 に供給する。これらの制御信号は、それぞれ各画素 2 0 0 の端子 r e s , t x , s e l 0 ~ 2 に供給される。各画素の出力端子 v o u t 0 ( 2 0 7 a ) ~ v o u t 2 ( 2 0 7 c ) は、列出力線 3 0 0 a ~ 3 0 0 1 に接続される。画素 R 0 \_ 0 が配置される列 ( 0 列目 ) を例に説明すると、図 2 A に示すように 0 行目の画素 R 0 \_ 0 から 1 1 行目の画

10

20

30

40

50

素 G 1 1 \_ 0までの画素と列出力線 3 0 0 a ~ 3 0 0 1との接続パターンが、12行目以降の画素において繰り返される。この接続パターンは、各列同様である。

#### 【 0 0 2 2 】

列出力線 3 0 0 a ~ 3 0 0 1は、それぞれ A D 变換器 ( A D C ) 3 0 1 a ~ 3 0 1 1の入力へ接続される。A D 变換器 3 0 1 a ~ 3 0 1 1は、画素 2 0 0 から出力される光信号とノイズ信号をアナログ - デジタル变換する。列出力線 3 0 0 a ~ 3 0 0 1には、それ電流源 3 0 2 a ~ 3 0 2 1が接続されている。電流源 3 0 2 a ~ 3 0 2 1と列出力線 3 0 0 a ~ 3 0 0 1に接続された画素部 2 0 0 の增幅 M O S トランジスタ 2 0 4によってソースフォロア回路が構成される。

#### 【 0 0 2 3 】

A D 变換器 3 0 1 aを例として、A D 变換器の構成を図 2 C に示す。A D 变換器 3 0 1 aは、比較器 3 2 7 、 L a t c h \_ N 3 2 8 、 L a t c h \_ S 3 2 9 、スイッチ 3 3 0 , 3 3 1 を有する。列出力線 3 0 0 aにより出力される信号は比較器 3 2 7 に入力される。ランプ信号発生器 3 0 6 aからは、信号線 3 2 1 aおよび信号線 3 2 2 aを介してランプ信号 A とランプ信号 B が出力され、セレクタ 3 2 6 で選択されたランプ信号が比較器 3 2 7 に入力される。

#### 【 0 0 2 4 】

図 2 A に示す T G 3 0 7 a から出力される制御信号によりセレクタ 3 2 6 が制御され、A D 变換器毎にどちらのランプ信号を使用するかが選択される。すなわち、該当する A D 变換器が画像信号の A D 变換に使用される場合にはランプ信号 A が選択され、補正データ信号の A D 变換に使用される場合にはランプ信号 B が選択される。

#### 【 0 0 2 5 】

L a t c h \_ N 3 2 8 はノイズレベル ( N 信号 ) を保持するための記憶素子であり、L a t c h \_ S 3 2 9 は信号レベル ( S 信号 ) を保持するための記憶素子である。カウンタ 3 0 5 a から信号線 3 2 3 aを介して出力されるカウンタ値が L a t c h \_ N 3 2 8 と L a t c h \_ S 3 2 9 に入力される。

#### 【 0 0 2 6 】

L a t c h \_ N 3 2 8 は比較器 3 2 7 から反転出力が入力された場合のカウンタ値を N 信号のデジタル信号値として保持し、L a t c h \_ S 3 2 9 は比較器 3 2 7 から反転出力が入力された場合のカウンタ値を S 信号のデジタル信号値として保持する。

#### 【 0 0 2 7 】

L a t c h \_ N 3 2 8 に保持された N 信号と、L a t c h \_ S 3 2 9 に保持された S 信号はスイッチ 3 3 0 , 3 3 1 を介してそれぞれ共通出力線 3 2 4 a , 3 2 5 a を介して図 2 A に示す S - N 演算部 3 0 8 a に出力される。

#### 【 0 0 2 8 】

スイッチ 3 3 0 , 3 3 1 は水平走査回路 3 0 4 a からの制御信号で制御される。この S - N 演算部 3 0 8 a または 3 0 8 b へのデジタル信号の出力は A D 变換器毎に順次行われ、水平転送と呼ぶ。

#### 【 0 0 2 9 】

S - N 演算部 3 0 8 a , 3 0 8 b は、入力された S 信号から N 信号を減算する。この動作により列回路に起因するノイズ成分をキャンセルした画像データまたは補正值生成用の補正データが生成される。

#### 【 0 0 3 0 】

S - N 演算部 3 0 8 a , 3 0 8 b から出力されたデータは、データ振り分け部 3 0 9 a , 3 0 9 b に入力される。データ振り分け部 3 0 9 a , 3 0 9 b ではデータの振り分け、並び替え等を行い、データをデータ出力部 A 3 1 0 a , 3 1 0 b またはデータ出力部 3 1 1 a , 3 1 1 b へ出力する。

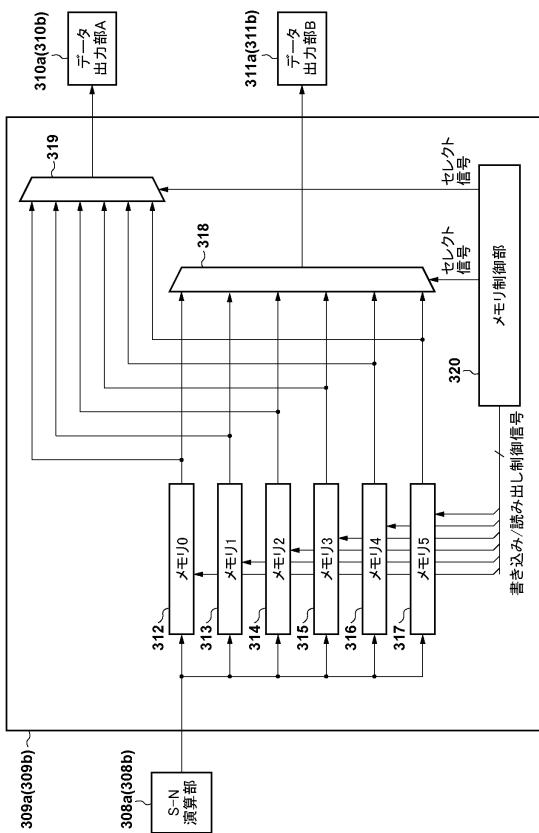

#### 【 0 0 3 1 】

図 2 D にデータ振り分け部 3 0 9 a , 3 0 9 b の構成を示す。入力されたデータは、メモリ制御部 3 2 0 から出力される書き込み制御信号に従い、A D 变換器毎にメモリ 0 ( 3

10

20

30

40

50

12)～メモリ5(317)に書き込まれる。画素R0\_0が配置される列を例にすると、AD変換器301a～301fにおいてAD変換されたデータは、データ振り分け部309aに含まれるメモリ0(312)～メモリ5(317)にそれぞれ書き込まれる。また、AD変換器301g～301lにおいてAD変換されたデータは、データ振り分け部309bに含まれるメモリ0(312)～メモリ5(317)にそれぞれ書き込まれる。

#### 【0032】

メモリ制御部320はセレクタ318, 319とメモリ0(312)～メモリ5(317)からのデータ読み出しを制御する。すなわち、データ出力部310a, 310bまたはデータ出力部311a, 311bへデータをメモリ毎に順次出力する。データ出力部310a, 310bまたはデータ出力部311a, 311bは、S L V S (Scalable Low Voltage Signaling)等の伝送方式により、撮像素子100の外部へデータを出力する。

10

#### 【0033】

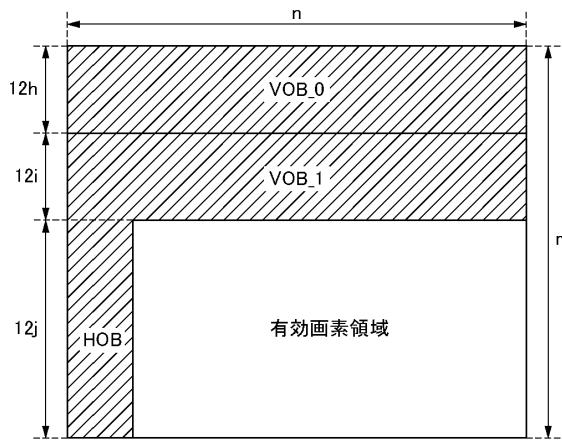

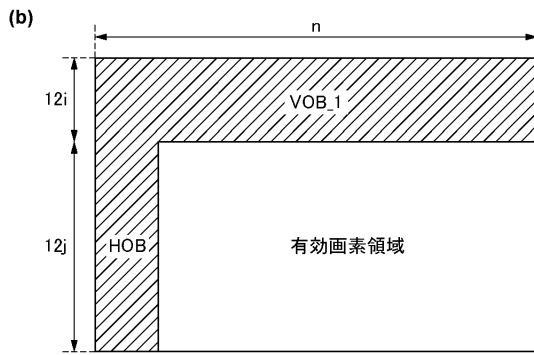

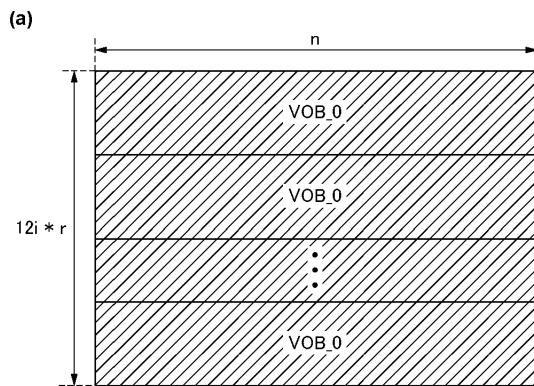

ここで、図2Eを用いて撮像素子100における画素領域の構成について説明する。図2Eに示すように、遮光された画素が複数配置された遮光画素領域V0B\_0, V0B\_1, H0Bと、被写体を撮影する有効画素が複数配置された有効画素領域を有する。水平方向(行方向)にn列、垂直方向(列方向)にm行の画素が配置されている。

#### 【0034】

また、垂直方向(列方向)には遮光画素領域V0B\_0は12h(hは0より大きい整数)行、遮光画素領域V0B\_1は12i(iは0より大きい整数)行、有効画素領域は12j(jは0より大きい整数)行の画素がそれぞれ配置されている。垂直方向については、図2Aに示す0行目から11行目の画素列出力線接続パターンが繰り返し続くため、各領域が12の倍数となっている。

20

#### 【0035】

また、遮光画素領域V0B\_0は後述する補正データの読み出し時に使用され、遮光画素領域V0B\_1, H0B、有効画像領域は画像データの読み出し時に使用される。遮光画素領域V0B\_0, V0B\_1, H0B、有効画像領域の各々から信号を読み出すための垂直走査動作や画素列出力線の電気的な接続を決定する制御信号s e l 0 ~ 2が独立に垂直走査回路303によって制御される。

#### 【0036】

30

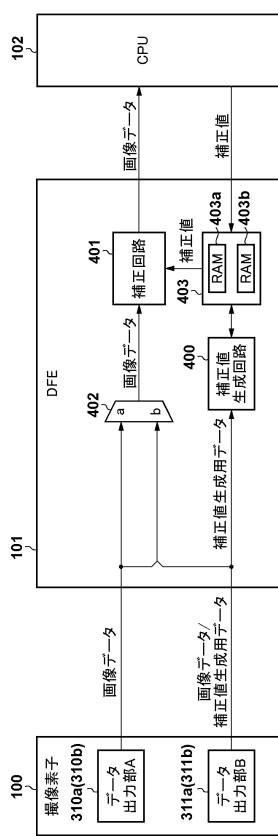

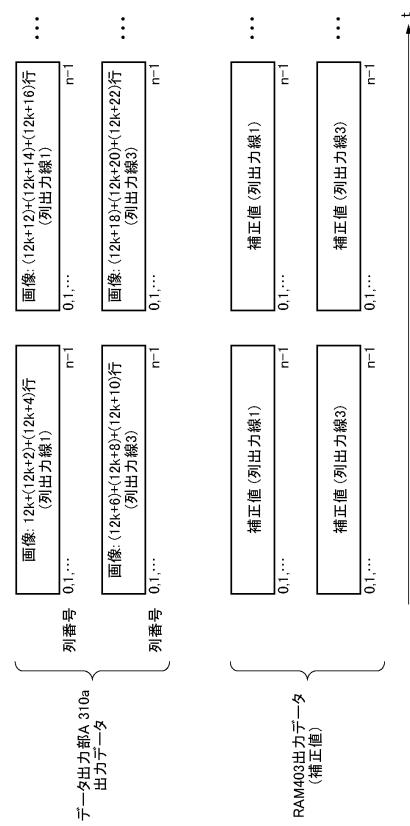

次に、図3を用いてDFE101の構成について説明する。図3に撮像素子100、CPU102との接続を含めたDFE101の構成を示す。データ出力部310a, 310bから出力されるデータは、セレクタ402へ入力される。一方、データ出力部311a, 311bから出力されるデータは補正值生成回路400へ入力される。また、データ出力部310a, 310bから出力されるデータと、データ出力部311a, 311bから出力されるデータは1フレームの画像データとしてまとめられ、セレクタ402へ入力される。セレクタ402は撮影モード毎にCPU102から設定される設定に基づき制御される。セレクタ402の出力は補正回路401へ入力される。

#### 【0037】

補正值生成回路400は、データ出力部311a, 311bから出力されるデータから列回路(列出力線、AD変換器等)毎の補正值を生成し、RAM403へ格納する。RAM403は、RAM403aとRAM403bを有する。いずれか一方のRAMに画像の補正值を格納し、補正に使用する。補正に使用していない側のRAMでは補正值生成や保持が行われ、またはパワーダウンされる。また、RAM403aまたはRAM403bは、CPU102から送信される補正值を書き込む機能を有する。

40

#### 【0038】

補正回路401は、列回路毎にRAM403から出力される補正值を画像データから減算し、オフセット補正を行う。その後CPU102に対してデータを出力する。

#### 【0039】

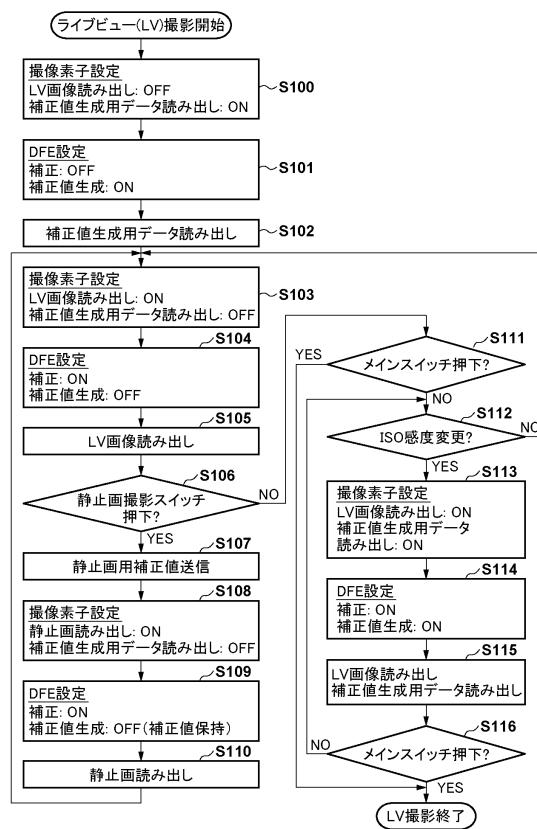

次に、第1の実施形態における撮像装置の動作について説明する。図4は、第1の実施

50

形態における撮像装置 100 の撮影動作を説明するためのフローチャートである。なお、以下では例として R 画素のみについて説明を行う。G 画素、B 画素の動作については R 画素と同様であるため、説明を省略する。

#### 【0040】

ユーザーが図 1 に示した操作部 103 のメインスイッチを押下すると、ライブビュー (LV) 撮影が開始される。LV 撮影が開始されると、ステップ S100において、CPU 102 は撮像素子 100 に対して LV 画像データを補正するための補正データを読み出す設定を行う。CPU 102 は垂直走査回路 303 に対して、遮光領域 VOB\_0 の制御信号 res, tx, sel0~2 等のパルス設定を行う。

#### 【0041】

また、ランプ信号発生器 306a により生成するランプ信号 B の傾きとして、補正データを読み出す場合の傾き（例えば撮影感度 ISO200 で撮影するための傾き）を設定する。また TG307a に対して、AD 変換器 301d, 301b をオン状態、その他の AD 変換器 (301a, 301c, 301e, 301f) はオフ状態にする設定を行う。また、AD 変換器 301d, 301b のセレクタ 326 にランプ信号 B を選択する設定を行う。また、データ出力部 310a をオフにし、データ出力部 311a をオンにする設定を行う。本実施形態では、オフにした回路は消費電力がオン時より低くなる構成とする。

#### 【0042】

次にステップ S101 において DFE101 の設定を行う。ここでは、補正值を生成するための設定を行う。補正值生成回路 400 に補正值を生成する設定を行う。また、RAM 403 に対して、補正值生成のために使用する RAM を RAM403a にする設定を行う。

#### 【0043】

次にステップ S102 において、補正データの読み出しを行う。なお、このときの各構成要素の状態を示す概念図を図 5 のフレーム No. LV\_0 に示す。

#### 【0044】

補正データ読み出し時（出力期間）の撮像素子 100 の動作について、図 6A を用いて説明する。

#### 【0045】

時刻 ta0 において、制御信号 tx\_0, 2, 4, 6, 8, 10 が H になり、転送スイッチ 202 がオンになる。このとき、リセットスイッチ 205 の制御信号 res\_0, 2, 4, 6, 8, 10 は H になっている。そして、フォトダイオード 201 に蓄積された電荷は、転送スイッチ 202、リセットスイッチ 205 を介して電源 208 に転送され、フォトダイオード 201 はリセットされる。

#### 【0046】

時刻 ta1 において、制御信号 tx\_0, 2, 4, 6, 8, 10 を L とし、フォトダイオード 201 における電荷の蓄積が開始される。

#### 【0047】

所定の時間だけ電荷の蓄積を行った後の時刻 ta2 において、選択スイッチ 206 の制御信号 sel1\_0, 2, 4, 6, 8, 10 が H になり、増幅MOSトランジスタ 204 のソースが列出力線に接続される。

#### 【0048】

時刻 ta3 において、リセットスイッチ 205 の制御信号 res\_0, 2, 4, 6, 8, 10 を L とすることで FD 部 203 のリセットを解除する。このとき、FD 部 203 の電位に応じたリセット信号レベルの電位が増幅MOSトランジスタ 204 を介して列出力線 300b, 300d に出力され、AD 変換器 301b, 301d に入力される。

#### 【0049】

このときの、画素と列出力線の接続を示す概念図を図 7 に示す。フレーム No. LV\_0 に示すように、0, 2, 4 行目が列出力線 300d (列出力線 3) に接続され、6, 8, 10 行目が列出力線 300b (列出力線 1) に接続されることになる。同一列出力線に

10

20

30

40

50

接続された画素信号は混合（加算）された状態で A D 変換器において A D 変換される。

#### 【 0 0 5 0 】

なお、図 7において画素からの列出力線への接続線が破線で記載されているものは、制御信号 s e 1 が L となっており、列出力線へ接続されていないものとする。また、以下の説明において、列出力線 3 0 0 a ~ 3 0 0 f をそれぞれ列出力線 0 ~ 5 と便宜的に呼ぶこととする。

#### 【 0 0 5 1 】

各画素 2 0 0 の出力端子 v o u t 1 にはノイズレベルが出力され、列出力線 3 0 0 b には 6 , 8 , 1 0 行目の画素のノイズレベルの混合（加算）信号が出力され、列出力線 3 0 0 d には 0 , 2 , 4 行目の画素のノイズレベルの混合信号が出力される。

10

#### 【 0 0 5 2 】

次に、時刻 t a 4 において、T G 3 0 7 a は A D 変換器 3 0 1 b , 3 0 1 d を駆動し、A D 変換を開始する。ここで各列出力線に出力されるノイズレベルの混合信号が A D 変換される。A D 変換開始とともにカウンタ 3 0 5 a がカウント値のインクリメント動作を開始する。列出力線 3 0 0 b , 3 0 1 d の信号レベルとセレクタ 3 2 6 から出力されるランプ信号レベルを比較器 3 2 7 で比較し、一致した時点のカウンタ値を L a t c h \_ N 3 2 8 に格納することで A D 変換が行われる。

#### 【 0 0 5 3 】

時刻 t a 5 において、A D 変換が終了すると、A D 変換器 3 0 1 b , 3 0 1 d はそれぞれ A D 変換されたノイズレベルを保持する。

20

#### 【 0 0 5 4 】

次に、時刻 t a 6 において、T G 3 0 7 a は再び A D 変換器 3 0 1 b , 3 0 1 d を駆動し、A D 変換を開始する。すなわち各列出力線に出力されるノイズレベルの混合信号が A D 変換される。時刻 t a 7 において、A D 変換が終了すると、A D 変換器 3 0 1 b , 3 0 1 d は、それぞれ A D 変換されたノイズレベルを保持する。

#### 【 0 0 5 5 】

ここで保持されるノイズレベルと最初のノイズレベルとは、r e s \_ 0 , 2 , 4 , 6 , 8 , 1 0 を L にしてリセット解除した状態からの時間（タイミング）が異なっている。本実施形態では、この時間に関連する 2 回取得されたノイズレベルの違いを列回路（列出力線、A D 変換器等）毎の固有の列オフセットノイズとして、補正対象とする。

30

#### 【 0 0 5 6 】

その後、時刻 t a 8 において、制御信号 r e s \_ 0 , 2 , 4 , 6 , 8 , 1 0 を H とし、再び F D 部 2 0 3 をリセット状態とする。また、撮像素子 1 0 0 の外部へのデータ出力を開始する。水平走査回路 3 0 4 は水平走査を開始し、各列の A D 変換器 3 0 1 b , 3 0 1 d の 1 回目の N 信号と 2 回目の N 信号を S - N 演算部 3 0 8 a へ順次転送する。

#### 【 0 0 5 7 】

S - N 演算部 3 0 8 a で列毎に 2 回目の N 信号から 1 回目の N 信号が減算され、データ振り分け部 3 0 9 a を経由してデータ出力部 3 1 1 a からデータを出力する。

#### 【 0 0 5 8 】

時刻 t a 9 において、制御信号 s e 1 \_ 0 , 2 , 4 , 6 , 8 , 1 0 が L になり、その後、時刻 t a 1 0 において全列のデータ出力が終了すると、データ出力の 1 転送単位が終了する。

40

#### 【 0 0 5 9 】

本実施形態では、図 8 ( a ) に示すように遮光画素領域 V O B \_ 0 に対して図 6 A に示す補正データ読み出し動作を所定回数繰り返すことにより、補正データを出力する。

#### 【 0 0 6 0 】

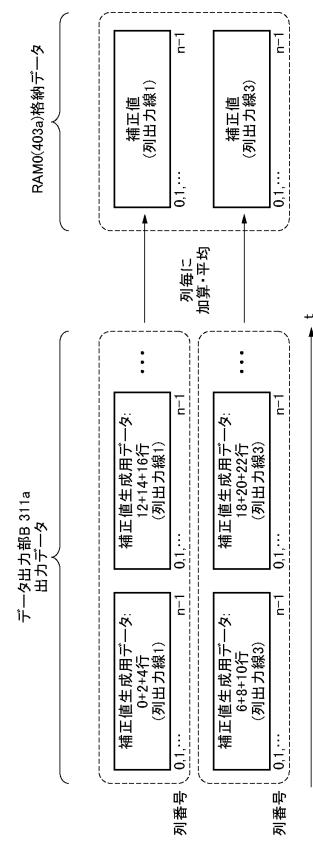

次に、ステップ S 1 0 2 における D F E 1 0 1 の動作（図 5 の L V \_ 0 フレーム）について説明する。

#### 【 0 0 6 1 】

撮像素子 1 0 0 のデータ出力部 3 1 1 a から補正データが出力され、補正值生成回路 4

50

00に入力される。図9に示すように補正值生成回路400には、列出力線300b, 300d(列出力線1, 3)をそれぞれ経由したデータが順次入力される。

#### 【0062】

補正值生成回路400は各列出力線の列毎に、RAM403aへデータを一時格納しながら加算する。所定の行数加算後に平均し、補正值としてRAM403aへ格納する。DFE101で補正值の生成が終了すると、ステップS103へ進む。

#### 【0063】

ステップS103において、CPU102は撮像素子100に対してLV画像データを読み出す設定を行う。CPU102は垂直走査回路303に対して、遮光画素領域VOB\_1と有効画素領域の制御信号res, tx, sel0~2等のパルス設定を行う。

10

#### 【0064】

また、ランプ信号発生器306aにより生成するランプ信号Aの傾きとして、LV画像データを読み出すときの傾き(例えば撮影感度ISO200で撮影するための傾き)を設定する。またTG307aに対して、AD変換器301d, 301bをオン状態、他のAD変換器(301a, 301c, 301e, 301f)はオフ状態にする設定を行う。

#### 【0065】

また、AD変換器301d, 301bのセレクタ326にランプ信号Aを選択する設定を行う。また、データ出力部311aをオフにし、データ出力部310aをオンにする設定を行う。

#### 【0066】

次にステップS104においてDFE101の設定を行う。ここでは、LV画像データを補正するための設定を行う。セレクタ402をaに設定し、データ出力部310aからのデータのみを選択する。また、RAM403に対して、補正のために使用するRAMをRAM403aにする設定を行う。

20

#### 【0067】

次にステップS105において、LV画像データの読み出しを行う。なお、このときの各構成要素の状態を示す概念図を図5のフレームNo.LV\_1に示す。

#### 【0068】

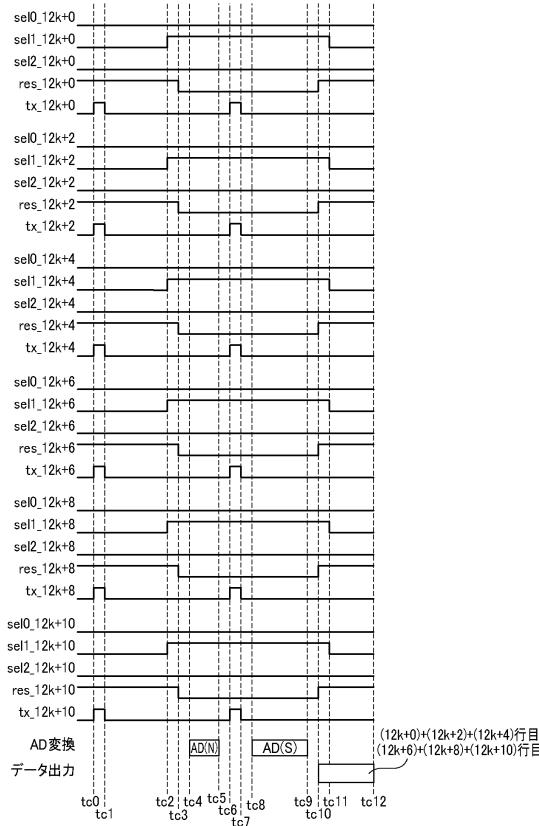

LV画像データ読み出し時の撮像素子100の動作について、図10Bを用いて説明する。

30

#### 【0069】

時刻tc0において、制御信号tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10(kはhより大きい整数)がHになり、転送スイッチ202がオンになる。このとき、res\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10はHになっている。そして、フォトダイオード201に蓄積された電荷は、転送スイッチ202、リセットスイッチ205を介して電源208に転送され、フォトダイオード201はリセットされる。

#### 【0070】

時刻tc1において、制御信号tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10をLとし、フォトダイオード201における光電荷の蓄積が開始される。

40

#### 【0071】

所定の時間だけ光電荷の蓄積を行った後の時刻tc2において、選択スイッチ206の制御信号sel1\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10がHになる。そして、増幅MOSトランジスタ204のソースが列出力線に接続される。

#### 【0072】

時刻tc3において、リセットスイッチ205の制御信号res\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10をLとすることでFD部203のリセットを解除する。このとき、FD部203の電位に応じたリセット信号レベルの

50

電位が増幅MOSトランジスタ204を介して列出力線300b, 300d(列出力線1, 3)に出力され、AD変換器301b, 301dに入力される。

#### 【0073】

このときの、画素と列出力線の接続を示す概念図を図7に示す。フレームNo. LV\_1に示すように、12k+0, 12k+2, 12k+4行目が列出力線300d(列出力線3)に接続され、12k+6, 12k+8, 12k+10行目が列出力線300b(列出力線1)に接続されることになる。同一列出力線に接続された画素信号は混合(加算)された状態でAD変換器においてAD変換される。

#### 【0074】

各画素200の出力端子vout1にはノイズレベルが出力され、列出力線300bには6, 8, 10行目の画素のノイズレベルの混合(加算)信号が出力され、列出力線300dには0, 2, 4行目の画素のノイズレベルの混合信号が出力される。

10

#### 【0075】

次に、時刻t\_c4において、TG307aはAD変換器301b, 301dを駆動し、AD変換を開始する。ここで各列出力線に出力されるノイズレベルの混合信号がAD変換される。AD変換開始とともにカウンタ305aがカウント値のインクリメント動作を開始する。列出力線300b, 300dの信号レベルとセレクタ326から出力されるランプ信号レベルを比較器327で比較し、一致した時点のカウンタ値をLatch\_N328に格納することでAD変換が行われる。

20

#### 【0076】

時刻t\_c5において、AD変換が終了すると、AD変換器301b, 301dはそれぞれAD変換されたノイズレベルを保持する。

#### 【0077】

時刻t\_c6において、垂直走査回路303は、制御信号tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10をHにする。それに伴って、12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10行目の画素200の転送ゲート202がオンされる。

#### 【0078】

そして、各画素のPD201に蓄積されている信号電荷(光電荷)が増幅MOSトランジスタ204で構成されるソースフォロアのゲートに転送される。ソースフォロアは転送された信号電荷に見合う分だけリセットレベルから電位が変動して信号レベルが確定する。

30

#### 【0079】

このとき、各画素200の出力端子vout1には信号レベルが出力され、列出力線300dには12k+0, 12k+2, 12k+4行目の画素の信号レベルの混合(加算)信号が出力される。また、列出力線300bには12k+6, 12k+8, 12k+10行目の画素の信号レベルの混合信号が出力される。

#### 【0080】

その後、時刻t\_c7において、制御信号tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10をLにし、PD201からの転送を完了する。

#### 【0081】

次に、時刻t\_c8において、TG307aはAD変換器301b, 301dを駆動し、AD変換を開始する。すなわち各列出力線に出力される信号レベルの混合信号がAD変換される。時刻t\_c9において、AD変換が終了されると、AD変換器301b, 301dは、それぞれAD変換された信号レベルを保持する。

40

#### 【0082】

その後、時刻t\_c10において、制御信号res\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10をHとし、再びFD部203をリセット状態とする。また、撮像素子100の外部へのデータ出力を開始する。水平走査回路304は水平走査を開始し、各列のAD変換器301b, 301dのN信号とS信号をS-N演算部308aへ順次転送する。

50

**【 0 0 8 3 】**

S - N 演算部 3 0 8 a で列毎に S 信号から N 信号が減算され、データ振り分け部 3 0 9 a を経由してデータ出力部 3 1 0 a からデータを出力する。

**【 0 0 8 4 】**

時刻 t c 1 1 において、制御信号 s e l 1 \_ 1 2 k + 0 , 1 2 k + 2 , 1 2 k + 4 , 1 2 k + 6 , 1 2 k + 8 , 1 2 k + 1 0 が L になる。その後、時刻 t c 1 2 において全列のデータ出力が終了すると、データ出力の 1 転送単位が終了する。

**【 0 0 8 5 】**

本実施形態では、図 8 ( b ) に示すように垂直方向 ( 列方向 ) において、遮光画素領域 V O B \_ 1 、有効画素領域に対して図 1 0 B に示す L V 画像データ読み出し動作を行い、垂直方向に 3 画素の信号を混合することにより、 L V 画像データを出力する。10

**【 0 0 8 6 】**

次に、ステップ S 1 0 5 における D F E 1 0 1 の動作 ( 図 5 の L V \_ 1 フレーム ) について説明する。

**【 0 0 8 7 】**

撮像素子 1 0 0 のデータ出力部 3 1 0 a から L V 画像データが出力され、補正回路 4 0 1 へ入力される。図 1 1 に示すように補正回路 4 0 1 には、列出力線 3 0 0 b , 3 0 0 d ( 列出力線 1 , 3 ) をそれぞれ経由した画像データが順次入力される。

**【 0 0 8 8 】**

補正回路 4 0 1 は R A M 4 0 3 a に格納されている補正值を、入力される画像データの列との対応が合うタイミングで受信し、各列出力線の列毎に画像データから補正值を減算する。その後、 C P U 1 0 2 に対して画像データを出力する。20

**【 0 0 8 9 】**

C P U 1 0 2 は入力された L V 画像データを画像処理部 1 0 7 へ転送し、画像処理部 1 0 7 内で不図示の現像回路での現像を行い、表示部 1 0 4 でライブビュー画像として表示を開始する。

**【 0 0 9 0 】**

その後、ステップ S 1 0 6 において、 C P U 1 0 2 は、操作部 1 0 3 の静止画撮影スイッチが押下されたか否かを判断する。静止画撮影スイッチが押下されていない場合には ( ステップ S 1 0 6 の N O ) 、ステップ S 1 1 1 へ進む。30

**【 0 0 9 1 】**

ステップ S 1 1 1 では、 C P U 1 0 2 は、メインスイッチが押下されているか否かを判断し、メインスイッチが押下されている場合には ( ステップ S 1 1 1 の Y E S ) 、撮影を終了する。メインスイッチが押下されていない場合には ( ステップ S 1 1 1 の N O ) 、ステップ S 1 1 2 に進む。

**【 0 0 9 2 】**

ステップ S 1 1 2 では、 C P U 1 0 2 は次のフレームで I S O 感度を変更するか否かを判断する。本実施形態ではユーザーが操作部 1 0 3 を操作して I S O 感度を変更するものとし、変更されない場合 ( ステップ S 1 1 2 の N O ) はステップ S 1 0 3 に戻る。 I S O 感度が変更された場合 ( ステップ S 1 1 2 の Y E S ) はステップ S 1 1 3 へ進む。40

**【 0 0 9 3 】**

なお、本実施形態では I S O 感度をユーザーが決定する構成としたが、それに限定されるものではない。撮影した L V 画像から明るさを検知し、所定の判断で C P U 1 0 2 が自動で I S O 感度を変更する構成でもよい。

**【 0 0 9 4 】**

ステップ S 1 1 3 において、 C P U 1 0 2 は撮像素子 1 0 0 に対して L V 画像データを補正するための補正データを読み出す設定を行う。 C P U 1 0 2 は垂直走査回路 3 0 3 に対して、遮光画素領域 V O B \_ 0 の制御信号 r e s , t x , s e l 0 ~ 2 等のパルス設定を行う。

**【 0 0 9 5 】**1020304050

また、ランプ信号発生器 306a により生成するランプ信号 B の傾きとして、補正データを読み出すときの傾き（例えば撮影感度 ISO1600 で撮影するための傾き）を設定する。

#### 【0096】

また、CPU102 は垂直走査回路 303 に対して、遮光画素領域 VOB\_1 と有効画素領域の制御信号 res, tx, sel0~2 等のパルス設定を行う。

#### 【0097】

また、ランプ信号発生器 306a により生成するランプ信号 A の傾きとして、LV 画像データを読み出すときの傾き（例えば撮影感度 ISO200 で撮影するための傾き）を設定する。

10

#### 【0098】

また TG307a に対して、AD 変換器 301b, 301c, 301d, 301e をオン状態、その他の AD 変換器（301a, 301f）はオフ状態にする設定を行う。また、AD 変換器 301b, 301d にはセレクタ 326 にランプ信号 A を選択する設定を行う。AD 変換器 301c, 301e にはセレクタ 326 にランプ信号 B を選択する設定を行う。また、データ出力部 310a、データ出力部 311a をオンにする設定を行う。

#### 【0099】

次にステップ S114において DFE101 の設定を行う。ここでは、補正值を生成するための設定を行う。補正值生成回路 400 に補正值を生成する設定を行う。また、RAM403 に対して、補正值生成のために使用する RAM を RAM403b にする設定を行う。

20

#### 【0100】

また、LV 画像データを補正するための設定を行う。セレクタ 402 を a に設定し、データ出力部 310a からのデータのみを選択する。また、RAM403 に対して、補正のために使用する RAM を RAM403a にする設定を行う。

#### 【0101】

次にステップ S115において、補正データの読み出しと LV 画像データの読み出しを行う。なお、このときの各構成要素の状態を示す概念図を図 5 のフレーム No. LV\_3 に示す。

30

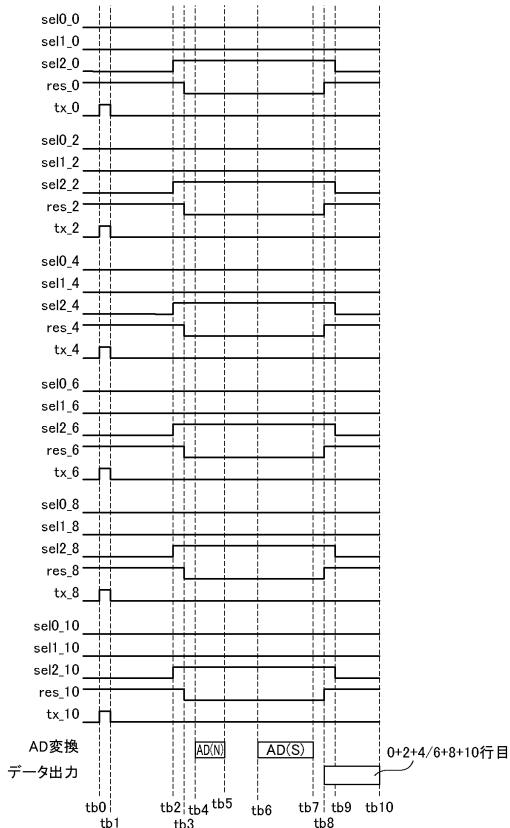

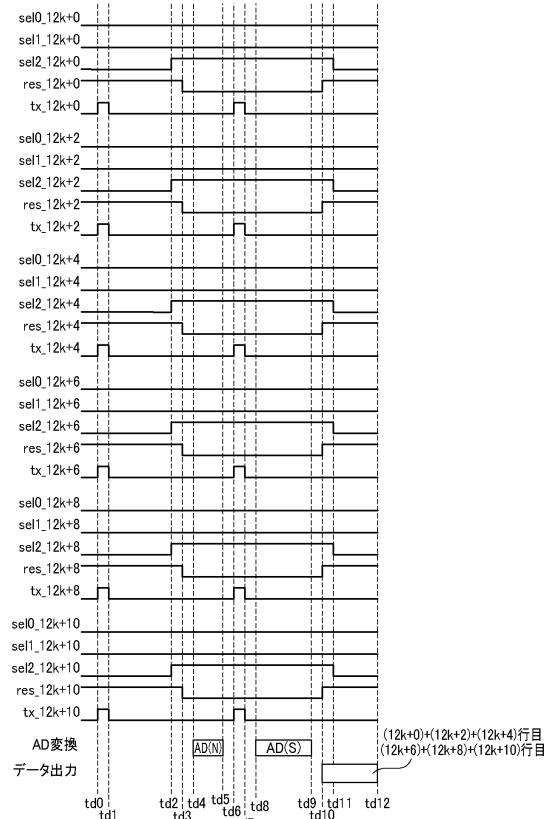

#### 【0102】

このときの補正データの読み出しにおける撮像素子 100 の動作を、図 6B に示す。前述した図 6A の補正データ読み出し時の動作と異なるのは、制御信号 sel2\_0, 2, 4, 6, 8, 10 を駆動する点であり、他は図 6A と同様であるため説明を省略する。

#### 【0103】

このときの、画素と列出力線の接続を示す概念図を再び図 7 を用いて説明する。フレーム No. LV\_3 に示すように、0, 2, 4 行目が列出力線 300e（列出力線 4）に接続され、6, 8, 10 行目が列出力線 300c（列出力線 2）に接続されることになる。同一列出力線に接続された画素信号は混合（加算）された状態で AD 変換器において AD 変換される。

40

#### 【0104】

また、同時に LV 画像データの読み出しを行う。このときの LV 画像データの読み出しは前述した図 10A と同様であるため、説明を省略する。

#### 【0105】

次に、ステップ S115における DFE101 の動作（図 5 の LV\_3 フレーム）について説明する。このフレームでは、画像データと補正データの読み出し期間が重複する。

#### 【0106】

撮像素子 100 のデータ出力部 311a から補正データが出力され、補正值生成回路 400 に入力される。補正值生成回路 400 には、列出力線 300c, 300e（列出力線 2, 4）をそれぞれ経由した補正データが順次入力される。

#### 【0107】

50

補正值生成回路 400 は各列出力線の列毎に、RAM403b へ補正データを一時格納しながら加算する。所定の行数の加算後に平均し、補正值として RAM403b へ格納する。

#### 【0108】

また、LV 画像の補正については、前述したステップ S105 の動作と同様のため、説明を省略する。DFE101 で補正值の生成と LV 画像の補正が終了すると、ステップ S116 へ進む。

#### 【0109】

ステップ S116 では、CPU102 は、メインスイッチが押下されているか否かを判断し、メインスイッチが押下されている場合には（ステップ S116 の YES）、撮影を終了する。メインスイッチが押下されていない場合には（ステップ S116 の NO）、ステップ S112 に進む。ステップ S112 において、さらに ISO 感度が変更されないと判断された場合には、ステップ S103 へ進む。

10

#### 【0110】

ステップ S103 において、CPU102 は撮像素子 100 に対して LV 画像データを読み出す設定を行う。CPU102 は垂直走査回路 303 に対して、遮光画素領域 VOB\_1 と有効画素領域の制御信号 res, tx, sel0~2 等のパルス設定を行う。

#### 【0111】

また、ランプ信号発生器 306a により生成されるランプ信号 A の傾きとして、LV 画像データを読み出すときの傾き（例えば撮影感度 ISO1600 で撮影するための傾き）を設定する。また TG307a に対して、AD 変換器 301e, 301c をオン状態、その他の AD 変換器（301a, 301b, 301d, 301f）をオフ状態にする設定を行う。

20

#### 【0112】

また、AD 変換器 301e, 301c のセレクタ 326 に対してランプ信号 A を選択する設定を行う。また、データ出力部 311a をオフにし、データ出力部 310a をオンにする設定を行う。

#### 【0113】

次にステップ S104 において DFE101 の設定を行う。ここでは、LV 画像データを補正するための設定を行う。セレクタ 402 を a に設定し、データ出力部 310a からの画像データのみを選択する。また、RAM403 に対して、補正のために使用する RAM を RAM403a にする設定を行う。

30

#### 【0114】

次にステップ S105 において、LV 画像データの読み出しを行う。なお、このときの各構成要素の状態を示す概念図を図 5 のフレーム No. LV\_4 に示す。

#### 【0115】

このときの補正データ読み出し時の撮像素子 100 の動作を、図 10B に示す。前述した図 6A の補正データ読み出し時の動作と異なるのは、制御信号 sel2\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10 を駆動する点であり、他は図 10A と同様であるため説明を省略する。

40

#### 【0116】

このときの、画素と列出力線の接続を示す概念図を再び図 7 を用いて説明する。フレーム No. LV\_4 に示すように、12k+0, 12k+2, 12k+4 行目が列出力線 300e（列出力線 4）に接続され、12k+6, 12k+8, 12k+10 行目が列出力線 300c（列出力線 2）に接続されることになる。同一列出力線に接続された画素信号は混合（加算）された状態で AD 変換器において AD 変換される。

#### 【0117】

次に、ステップ S105 における DFE101 の動作（図 5 の LV\_4 フレーム）について説明する。

#### 【0118】

50

撮像素子 100 のデータ出力部 310a から LV 画像データが output され、補正回路 401 へ入力される。図 11 に示すように補正回路 401 には、列出力線 300c, 300e (列出力線 2, 4) をそれぞれ経由した画像データが順次入力される。

#### 【0119】

補正回路 401 は RAM 403b に格納されている補正值を、入力される画像データの列と対応するタイミングで受信し、各列出力線の列毎に画像データから補正值を減算する。その後、CPU 102 に対して画像データを出力する。

#### 【0120】

CPU 102 は入力された LV 画像データを画像処理部 107 へ転送し、画像処理部 107 内で不図示の現像回路での現像を行い、表示部 104 へライブビュー画像として表示する動作を開始する。

10

#### 【0121】

その後ステップ S106 へ進む。ステップ S106 において静止画撮影スイッチが押下されていた場合 (ステップ S106 の YES) には、ステップ S107 へ進む。

#### 【0122】

ステップ S107 では、CPU 102 は静止画用の補正データを DFE101 に送信する。ここでは、静止画撮影は ISO1600 で行われるものとする。CPU 102 は ROM106 に格納される、列出力線 300a ~ 300f (列出力線 0 ~ 5) の列毎の ISO1600 に対応する補正值を DFE101 の RAM 403 へ送信する。ここでは LV 画像データの補正に使用していない RAM 403a に書き込まれる。なお、このときの各構成要素の状態を示す概念図を図 5 のフレーム No. LV\_5 に示す。その後ステップ S108 へ進む。

20

#### 【0123】

ステップ S108 において、CPU 102 は撮像素子 100 に対して静止画画像データを読み出す設定を行う。CPU 102 は垂直走査回路 303 に対して、遮光画素領域 VOB\_1 と有効画素領域の制御信号 res, tx, sel0 ~ 2 等のパルス設定を行う。

#### 【0124】

また、ランプ信号発生器 306a により生成するランプ信号 A の傾きとして、静止画画像データを読み出すときの傾き (例えば撮影感度 ISO1600 で撮影するための傾き) を設定する。また TG307a に対して、AD 変換器 301a ~ 301f をオン状態にする設定を行う。

30

#### 【0125】

また、AD 変換器 301a ~ 301f のセレクタ 326 にランプ信号 A を選択する設定を行う。また、データ出力部 310a、データ出力部 311a をオンにする設定を行う。

#### 【0126】

次にステップ S109 において DFE101 の設定を行う。ここでは、静止画画像データを補正するための設定を行う。セレクタ 402 を b に設定し、データ出力部 310a とデータ出力部 311a からのデータを選択する。また、RAM 403 に対して、補正のために使用する RAM を RAM 403a にする設定を行う。また、RAM 403b に格納される補正值は保持する設定を行う。

40

#### 【0127】

次にステップ S110 において、静止画画像データの読み出しを行う。なお、このときの各構成要素の状態を示す概念図を図 5 のフレーム No. 静止画に示す。

#### 【0128】

静止画画像データの読み出しにおける撮像素子 100 の動作について、図 10C を用いて説明する。

#### 【0129】

時刻 te0 において、制御信号 tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10 が H になり、転送スイッチ 202 がオンになる。このとき、res\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+1

50

0はHになっている。そして、フォトダイオード201に蓄積された電荷は、転送スイッチ202、リセットスイッチ205を介して電源208に転送され、フォトダイオード201はリセットされる。

#### 【0130】

時刻 $t_{e1}$ において、制御信号 $tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ をLとし、フォトダイオード201における光電荷の蓄積が開始される。

#### 【0131】

所定の時間だけ光電荷の蓄積を行った後の時刻 $t_{e2}$ において、選択スイッチ206の制御信号 $se10\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ がHになる。そして、増幅MOSトランジスタ204のソースが列出力線に接続される。10

#### 【0132】

時刻 $t_{e3}$ において、リセットスイッチ205の制御信号 $res\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ をLとすることでFD部203のリセットを解除する。このとき、FD部203の電位に応じたリセット信号レベルの電位が増幅MOSトランジスタ204を介して列出力線300a～300fに出力され、AD変換器301a～301fに入力される。

#### 【0133】

このときの、画素と列出力線の接続を示す概念図を再び図7を用いて説明する。フレームNo.静止画に示すように、 $12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ 行目がそれぞれ列出力線300a～300f(列出力線0～5)に接続されることになる。20

#### 【0134】

各画素200の出力端子 $vout_0$ にはノイズレベルが出力され、列出力線300a～300fには $12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ 行目の画素のノイズレベルが出力される。

#### 【0135】

次に、時刻 $t_{e4}$ において、TG307aはAD変換器301a～301fを駆動し、AD変換を開始する。ここで各列出力線に出力されるノイズレベルがAD変換される。AD変換開始にカウンタ305aがカウント値のインクリメント動作を開始する。列出力線300a～300fの信号レベルとセレクタ326から出力されるランプ信号レベルを比較器327で比較し、一致した時点のカウンタ値をLateh\_N328に格納することによりAD変換が行われる。30

#### 【0136】

時刻 $t_{e5}$ において、AD変換が終了されると、AD変換器301a～301fはそれぞれAD変換されたノイズレベルを保持する。

#### 【0137】

時刻 $t_{e6}$ において、垂直走査回路303は、制御信号 $tx\_12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ をHにする。それに伴って、 $12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ 行目の画素200の転送ゲート202がオンされる。40

#### 【0138】

そして、各画素のPD201に蓄積されている信号電荷(光電荷)が増幅MOSトランジスタ204で構成されるソースフォロアのゲートに転送される。ソースフォロアは転送された信号電荷に見合う分だけリセットレベルから電位が変動して信号レベルが確定する。

#### 【0139】

このとき、各画素200の出力端子 $vout_0$ には信号レベルが出力され、列出力線300a～300fには $12k+0, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ 行目の画素の信号レベルが出力される。50

**【0140】**

その後、時刻  $t_{e7}$ において、制御信号  $t_{x\_12k+0}, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ をLにし、PD201からの転送を完了する。

**【0141】**

次に、時刻  $t_{e8}$ において、TG307aはAD変換器301b, 301dを駆動し、AD変換を開始する。すなわち各列出力線に出力される信号レベルがAD変換される。時刻  $t_{e9}$ において、AD変換が終了されると、AD変換器301b, 301dは、それぞれAD変換された信号レベルを保持する。

**【0142】**

その後、時刻  $t_{e10}$ において  $r_{es\_12k+0}, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ をHとし、再びFD部203をリセット状態とする。また、撮像素子100の外部へのデータ出力を開始する。水平走査回路304は水平走査を開始し、各列のAD変換器301b, 301dのN信号とS信号をS-N演算部308aへ順次転送する。10

**【0143】**

S-N演算部308aで列毎にS信号からN信号が減算され、データ振り分け部309aを経由して、データ出力部311aから静止画画像データが出力される。

**【0144】**

時刻  $t_{e11}$ において制御信号  $s_{el0\_12k+0}, 12k+2, 12k+4, 12k+6, 12k+8, 12k+10$ がLになる。その後、時刻  $t_{e12}$ において全列のデータ出力が終了すると、データ出力の1転送単位が終了する。20

**【0145】**

本実施形態では、図8(b)に示すように、垂直方向(列方向)において、遮光画素領域VOB\_1、有効画素領域に対して図10Cに示す静止画画像データ読み出し動作を行うことにより、静止画画像データを出力する。

**【0146】**

次に、ステップS110におけるDFE101の動作(図5の静止画フレーム)について説明する。

**【0147】**

撮像素子100のデータ出力部310a、データ出力部311aから静止画画像データが出力され、補正回路401へ入力される。補正回路401には、列出力線300a～300f(列出力線0～5)をそれぞれ経由した静止画画像データが順次入力される。30

**【0148】**

補正回路401はRAM403aに格納されている補正值を、入力される静止画画像データの列と対応が合うタイミングで受信し、各列出力線の列毎に静止画画像データから補正值を減算する。その後、CPU102に対して静止画画像データを出力する。

**【0149】**

CPU102は入力された静止画画像データを画像処理部107へ転送し、画像処理部107内で不図示の現像回路での現像を行い、記録部108へ静止画として記録する。静止画撮影が終了すると、ステップS103に進む。

**【0150】**

上記の動作により、動画撮影においてISO感度などの撮影モードが変わった場合でも、動画(LV画像)フレームが消失することなく、撮影モードに対応した補正を画像に適用することができる。また、撮影直前に補正值を生成するため、必要な撮影モード毎の補正值を記憶する必要がない。

**【0151】**

なお、本実施形態では、ISO感度に関連してAD変換器のゲインを変更した場合に、補正值を取得する構成としたが、これに限定されるものではない。例えば、内蔵アンプのゲインなどが変更された場合にも適用できる。また、AD変換のbit数、垂直方向/水平方向の画素混合数などの撮影モードが切り替わった場合などにも適用することができる。50

**【0152】**

また、本実施形態ではオフセット補正を行う構成としたが、ゲイン補正など列回路に起因する補正であれば適用可能である。

**【0153】**

<第2の実施形態>

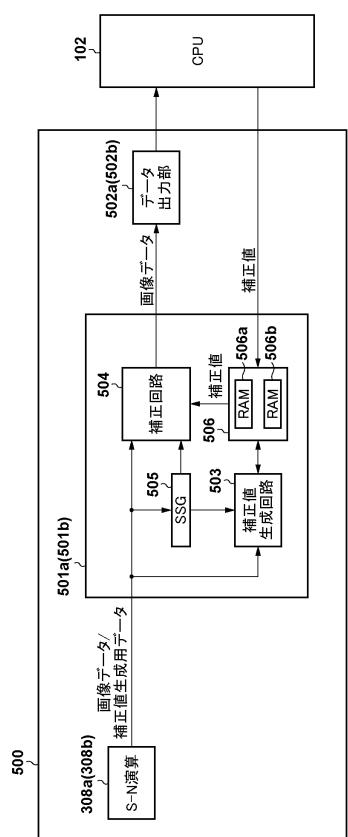

以下、図12を参照して、本発明の第2の実施形態に係わる撮像装置について説明する。図12は、本実施形態における撮像装置の構成を示すブロック図である。本実施形態における撮像装置1001は、撮像素子500を有する。また、第1の実施形態で説明した撮像装置1000と比較して、DFE101を持たず、撮像素子500から直接CPU102にデータが送信される。それ以外は撮像装置1000と同様であるため、説明を省略する。10

**【0154】**

図13は、撮像素子500の構成を示す図である。画像補正回路501a, 501bは、S-N演算部308a, 308bから出力される補正データに基づいて補正值を生成し、画像データを補正する。データ出力部502a, 502bはS L V S (Scalable Low Voltage Signaling)等の伝送方式である。

**【0155】**

画像補正回路501a, 501bから出力された画像データは、データ出力部502a, 502bから撮像素子500の外部へ出力される。画像補正回路501a, 501b、データ出力部502a, 502b以外の構成は撮像素子100と同様であるため、説明を省略する。20

**【0156】**

次に、図14を用いて画像補正回路501の構成について説明する。図14は、CPU102との接続を含めた画像補正回路501の構成を示す図である。S-N演算部308a(308b)から入力されたデータは、補正值生成回路503、補正回路504へ入力される。SSG505はTG307a(307b)からの不図示の制御信号に基づいて、入力データの種別とデータ数をカウントし、補正值生成回路503と補正回路504に対して、補正值生成と補正のタイミング制御を行う。

**【0157】**

補正值生成回路503はSSG505のタイミング制御信号に基づき、入力されるデータが補正データである場合に、列回路(列出力線、AD変換器等)毎の補正值を生成し、RAM506へ格納する。RAM506は、RAM506aとRAM506bを有する。いずれか一方のRAMに読み出しを行う画像の補正值を格納し、補正に使用する。補正に使用していない側のRAMでは補正值生成や保持が行われるか、またはパワーダウンされる。また、RAM506aまたはRAM506bは、CPU102から送信される補正值を書き込む機能を有する。30

**【0158】**

補正回路504は、SSG505のタイミング制御信号に基づき、入力されるデータが画像データである場合に、列回路毎にRAM506から出力される補正值を画像データから減算し、オフセット補正を行う。その後CPU102に対してデータを出力する。40

**【0159】**

本実施形態の画像補正回路501a(501b)は、補正值生成回路503と補正回路504がSSG505でタイミング制御されて処理を実行する以外、第1の実施形態で説明したDFE101の機能と同様である。DFE101では、画像データと補正データが撮像素子100から分かれて入力されるが、画像補正回路501a(501b)ではSSG505でデータの判別とデータ数カウントを実施している。画像補正回路501a(501b)、補正回路504、RAM506の動作内容は、DFE101の補正值生成回路400、補正回路401、RAM403と同様である。

**【0160】**

本実施形態の撮像装置1001の動作は、第1の実施形態における図4の動作に対して

10

20

30

40

50

、 D F E 1 0 1 で行っている動作が画像補正回路 5 0 1 a ( 5 0 1 b ) に変更されるのみであるため、説明を省略する。

【 0 1 6 1 】

上記の動作により、動画撮影において I S O 感度などの撮影モードが変わった場合でも動画フレームが消失することなく、撮影モードに対応した補正を画像に適用することができる。

【 0 1 6 2 】

本実施形態では、撮像素子外に補正值を生成するためのデータを出力する必要がないため、撮像素子のデータ出力インターフェース ( I / F ) に関して画像データの出力レートを制限することがない。また、撮像素子外へ出力する場合と比べて出力 I / F をパワーダウンできるので、消費電力を削減することができる。10

【 0 1 6 3 】

以上、本発明の好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されず、その要旨の範囲内で種々の変形及び変更が可能である。

【 0 1 6 4 】

( その他の実施形態 )

また本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現できる。また、1 以上の機能を実現する回路 ( 例えば、A S I C ) によっても実現できる。20

【 符号の説明 】

【 0 1 6 5 】

1 0 0 : 撮像素子、1 0 1 : D F E 、1 0 2 : C P U 、1 0 4 : 表示部、1 0 7 : 画像処理部、1 0 9 : 撮影レンズ、1 0 0 0 : 撮像装置

【四面】

【 四 1 】

【図2A】

【図2B】

【図2C】

10

20

30

40

50

【図 2 D】

【図 2 E】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6 A】

10

20

【図 6 B】

【図 7】

30

40

50

【図 8】

【図 9】

【図 10 A】

【図 10 B】

10

20

30

40

50

【図10C】

【 図 1 1 】

【図12】

【図13】

【図 1 4】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 0 4 N      5/378

(56)参考文献      特開2017-200135(JP, A)

国際公開第2015/107575(WO, A1)

特開2017-195642(JP, A)

特開2012-080195(JP, A)

特開2018-078401(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 0 4 N      5 / 3 0 - 5 / 3 7 8

H 0 4 N      5 / 2 2 2 - 5 / 2 5 7