(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4069408号

(P4069408)

(45) 発行日 平成20年4月2日(2008.4.2)

(24) 登録日 平成20年1月25日(2008.1.25)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 J |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 2 D |

|             |              |                  | G09G | 3/20 | 6 2 1 F |

|             |              |                  | G09G | 3/20 | 6 2 4 B |

請求項の数 9 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2002-101837 (P2002-101837)

(22) 出願日

平成14年4月3日(2002.4.3)

(65) 公開番号

特開2003-295824 (P2003-295824A)

(43) 公開日

平成15年10月15日(2003.10.15)

審査請求日

平成17年3月25日(2005.3.25)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100080953

弁理士 田中 克郎

(74) 代理人 100093861

弁理士 大賀 真司

(72) 発明者 宮澤 貴士

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 濱本 穎広

最終頁に続く

(54) 【発明の名称】電子回路及びその駆動方法、及び電子装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電子素子と、

前記電子素子に供給する電流量を導通状態に応じて制御する第1のトランジスタと、少なくとも前記第1のトランジスタを通過するプログラミング電流を電圧に変換して、前記第1のトランジスタの第1のゲート端子に印加される電圧値を第1の電圧値に設定するための電流-電圧変換を行う電流-電圧変換手段と、

前記第1のゲート端子に印加される電圧値を前記第1の電圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるように設定された第2の電圧値に変化させる電圧調整手段と、を備え、

前記電圧調整手段は、容量素子と前記容量素子と電圧源との間に接続された第2のトランジスタと、を含み、

前記第2のトランジスタを介して前記容量素子と前記電圧源とが電気的に接続されることにより、前記第1のゲート端子に印加される電圧値は、前記第1の電圧値から前記第2の電圧値に変化すること、

を特徴とする電子回路。

## 【請求項 2】

電子素子と、

前記電子素子に直列に接続された第1のトランジスタと、

容量素子と、

10

20

前記容量素子と電圧源との間に接続された第2のトランジスタと、を備え、

第1の期間において、前記第1のトランジスタの第1のゲート端子に印加される電圧値

は第1の電圧値に設定され、

第2の期間において、前記第2のトランジスタを介して前記容量素子と前記電圧源とが

電気的に接続されることにより、前記第1のゲート端子に印加される電圧値は前記第1の

電圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるよ

うに設定された第2の電圧値に変化すること、

を特徴とする電子回路。

【請求項3】

請求項1又は2に記載の電子回路において、

10

前記プログラミング電流はデータ信号に基づいて設定されること、

を特徴とする電子回路。

【請求項4】

請求項1乃至3のいずれかに記載の電子回路において、

前記電子素子は電気光学素子であること、

を特徴とする電子回路。

【請求項5】

請求項1乃至4のいずれかに記載の電子回路において、

前記容量素子は、第1の電極と第2の電極とを含み、

前記第1の電極は、前記第1のゲート端子に接続され、

前記第2の電極は、前記第2のトランジスタに接続されていること、

を特徴とする電子回路。

20

【請求項6】

請求項1乃至5のうち何れか1項に記載の電子回路を備えた電子装置。

【請求項7】

電子素子と、前記電子素子に直列に接続された第1のトランジスタと、容量素子と、前

記容量素子と電圧源との間に接続された第2のトランジスタと、を備えた電子回路の駆動

方法であって、

第1の期間において、前記第1のトランジスタの第1のゲート端子に印加される電圧値

を第1の電圧値に設定し、

30

第2の期間において、前記第2のトランジスタを介して前記容量素子と前記電圧源とを

電気的に接続することにより、前記第1のゲート端子に印加される電圧値を前記第1の電

圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるよ

うに設定された第2の電圧値に変化させること、

を特徴とする電子回路の駆動方法。

【請求項8】

請求項7に記載の電子回路の駆動方法において、

前記容量素子は、第1の電極と第2の電極とを有し、

前記第2の期間において、前記第2のトランジスタを介して前記第2の電極と前記電圧

源とが電気的に接続されること、

40

を特徴とする電子回路の駆動方法。

【請求項9】

請求項7又は8記載の電子回路の駆動方法において、

前記電子素子は電気光学素子であること、

を特徴とする電子回路の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は電子素子の駆動制御技術に関する。

【0002】

50

**【従来の技術】**

データ信号に応じた電圧をゲート端子に印加することによりトランジスタの導通状態を制御して有機EL素子に供給する電流量を設定する方式では、トランジスタの閾値電圧等のバラツキの影響を受ける。一般に、多数の有機EL素子を備える表示装置の駆動には、各々の有機EL素子を駆動するための薄膜トランジスタが用いられるが、シリコンベースのトランジスタに比べて薄膜トランジスタの特性のバラツキが顕著であるため、中間階調を得るための電流量を正確に有機EL素子に供給することは困難である。このようなトランジスタの特性のバラツキを補償する方法として、電流プログラム方式が提案されている。

**【0003】**

電流プログラム方式は発光階調に応じて電流出力回路から供給される電流（プログラミング電流）に応じた電荷量を保持キャパシタに保持し、有機EL素子へ供給される順バイアス電流（駆動電流）を供給する駆動トランジスタのゲート端子を当該保持キャパシタに充電された電圧によって制御する方式であり、このため、トランジスタの閾値電圧等の特性のバラツキを補償して、プログラミング電流値とほぼ同じ値の駆動電流で有機EL素子を駆動できる特徴がある。このように、電流値に応じて発光階調を設定する一連の操作は「電流プログラミング」と称されている。

**【0004】****【発明が解決しようとする課題】**

しかし、電流プログラム方式では、保持キャパシタへの電荷の蓄積に電流を用いるため、小電流でプログラミングを行うと配線容量の影響でプログラミングに時間を要するという問題がある。

**【0005】**

そこで、本発明は低階調レベルでのデータの書き込み遅延を低減し、画素回路の高速駆動を可能とする電子回路及びその駆動方法、電子装置、電気光学装置及び電子機器を提案することを課題とする。

**【0006】****【課題を解決するための手段】**

本発明に係る電子回路は、電子素子と、前記電子素子に供給する電流量を導通状態に応じて制御する第1のトランジスタと、少なくとも前記第1のトランジスタを通過するプログラミング電流を電圧に変換して、前記第1のトランジスタの第1のゲート端子に印加される電圧値を第1の電圧値に設定するための電流-電圧変換を行う電流-電圧変換手段と、前記第1のゲート端子に印加される電圧値を前記第1の電圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるように設定された第2の電圧値に変化させる電圧調整手段と、を備え、前記電圧調整手段は、容量素子と前記容量素子と電圧源との間に接続された第2のトランジスタと、を含み、前記第2のトランジスタを介して前記容量素子と前記電圧源とが電気的に接続されることにより、前記第1のゲート端子に印加される電圧値は、前記第1の電圧値から前記第2の電圧値に変化すること、を特徴とする。

本発明に係る電子回路は、電子素子と、前記電子素子に直列に接続された第1のトランジスタと、容量素子と、前記容量素子と電圧源との間に接続された第2のトランジスタと、を備え、第1の期間において、前記第1のトランジスタの第1のゲート端子に印加される電圧値は第1の電圧値に設定され、第2の期間において、前記第2のトランジスタを介して前記容量素子と前記電圧源とが電気的に接続されることにより、前記第1のゲート端子に印加される電圧値は前記第1の電圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるように設定された第2の電圧値に変化すること、を特徴とする。

前記プログラミング電流はデータ信号に基づいて設定される。

前記電子素子は電気光学素子である。

前記容量素子は、第1の電極と第2の電極とを含み、前記第1の電極は、前記第1のゲート端子に接続され、前記第2の電極は、前記第2のトランジスタに接続されている。

10

20

30

40

50

本発明に係る電子装置は、上記電子回路を備える。

本発明に係る電子回路の駆動方法は、電子素子と、前記電子素子に直列に接続された第1のトランジスタと、容量素子と、前記容量素子と電圧源との間に接続された第2のトランジスタと、を備えた電子回路の駆動方法であって、第1の期間において、前記第1のトランジスタの第1のゲート端子に印加される電圧値を第1の電圧値に設定し、第2の期間において、前記第2のトランジスタを介して前記容量素子と前記電圧源とを電気的に接続することにより、前記第1のゲート端子に印加される電圧値を前記第1の電圧値から前記第1の電圧値に比して前記第1のトランジスタの前記導通状態を減ずるように設定された第2の電圧値に変化させること、を特徴とする。

前記容量素子は、第1の電極と第2の電極とを有し、前記第2の期間において、前記第2のトランジスタを介して前記第2の電極と前記電圧源とが電気的に接続される。

前記電子素子は電気光学素子である。

また、上記の課題を解決するため、本発明の電子回路は、電子素子に電流を供給するトランジスタと、前記トランジスタのゲート端子に印加する電圧値に対応した電荷量を保持する電荷保持手段とを備え、前記電荷保持手段は第1の容量素子を含み、前記第1の容量素子は可変電圧供給手段に接続可能である。

#### 【0007】

かかる構成により、可変電圧供給手段から供給される電圧変化を第1の容量素子を介してゲート端子に伝達することで、トランジスタの導通状態を制御することができる。

#### 【0008】

ここで、「電荷保持手段」とは電荷蓄積機能を有する回路素子一般をいい、特に限定されるものではない。

#### 【0009】

また、「可変電圧供給手段」とは可変電圧を供給するための手段をいい、供給電圧レベルを任意に可変できる可変電圧源だけでなく、電圧レベルの異なる複数の電圧源の電源出力をスイッチを介して切換出力する場合も含むものとする。

#### 【0010】

また、「電子素子」とは電子回路を構成する回路素子一般をいい、特に限定されるものではない。

#### 【0011】

好ましくは、前記第1の容量素子は前記可変電圧供給手段から供給される電圧変化を前記ゲート端子に伝達することで、前記トランジスタの導通状態を制御する。

#### 【0012】

可変電圧供給手段の電圧変化を容量カッピングを介してゲート端子に伝達することで、ゲート端子の電位変化を迅速に制御することができる。

#### 【0013】

好ましくは、前記第1の容量素子の一方の電極を前記トランジスタのゲート端子に接続し、他方の電極を少なくとも1つのスイッチング素子を介して前記可変電圧供給手段に接続可能とする。

#### 【0014】

かかる構成により、可変電圧供給手段からの電圧変化をスイッチング素子を介して容量素子に伝達することができる。

#### 【0015】

好ましくは、前記電荷保持手段は、さらに第2の容量素子を含み、前記第2の容量素子の一方の電極は前記ゲート端子に接続され、他方の電極は電源線に接続可能である。

#### 【0016】

かかる構成により、第2の容量素子に蓄積された電圧によって、トランジスタのゲート端子の電圧を調整することができる。

#### 【0017】

好ましくは、前記トランジスタは、少なくとも1つのスイッチング素子を介して電流出力

10

20

30

40

50

回路に接続することが可能とする。

【0018】

ここで、電流出力回路とは、データ信号に対応して出力電流値が定められる電流源をいう。電子素子として有機EL素子などの電流駆動型発光素子を例にとると、データ信号は発光階調に対応する。

【0019】

好ましくは、前記第2の容量素子は、前記トランジスタを通過して前記電流出力回路から出力される出力電流に応じた電荷を保持する一方、前記トランジスタのドレイン端子若しくはソース端子から前記出力電流と同程度の電流を出力させるために前記ゲート端子に印加される電圧を調整する。

10

【0020】

電子素子として、例えば、電気光学素子が好ましく、特に、電流駆動型発光素子が好適である。電気光学素子とは、電気的作用により自発光し、若しくは外部から供給される光の光学的状態を変化させる素子一般をいい、液晶素子、電気泳動素子、エレクトロルミネンス素子、電子放出素子などを含む。また、電流駆動型発光素子とは、外部からの電流供給により発光する素子をいい、エレクトロルミネンス素子などがこれに該当する。

【0021】

好ましくは、前記出力電流の値は前記電子素子の発光階調に対応して設定する。電流出力回路からの出力電流の値を発光階調に対応して設定することで、表示階調を制御することができる。

20

【0022】

本発明の電子回路は、電子素子と、前記電子素子に供給する電流量を、導通状態に応じて制御するトランジスタと、少なくとも前記トランジスタを通過する電流を電圧に変換して、前記トランジスタのゲート端子に印加される電圧値の初期値を設定するための電流-電圧変換を行う電流-電圧変換手段と、前記電流-電圧変換後において、前記ゲート端子に印加される電圧値を調整する電圧調整手段とを備える。

【0023】

かかる構成により、電流-電圧変換手段によって、トランジスタから電子素子への電流供給を促す一方で、電圧調整手段によって、トランジスタの導通状態を制御し、電子素子への供給電流量を調整することができる。

30

【0024】

ここで、「電流-電圧変換手段」とはトランジスタを通過した電流信号を、トランジスタを駆動するための電圧信号に変換するための回路素子一般をいう。

【0025】

また、「電圧調整手段」とはトランジスタのゲート端子の電圧を調整するための回路素子一般をいう。

【0026】

好ましくは、前記電流-電圧変換時に前記トランジスタを通過する電流はデータ信号に基づいて設定される電流値である。

40

【0027】

好ましくは、前記電圧調整手段は、前記電流-電圧変換時における前記トランジスタの導通状態を減ずるように前記トランジスタのゲート端子に印加される電圧値を調整する。

【0028】

好ましくは、前記電圧調整手段は、可変電圧供給手段から供給される電圧変化を容量カッティングを通じて前記ゲート端子に印加し、前記トランジスタの導通状態を制御する。

【0029】

電子素子の例として、電気光学素子、電流駆動型発光素子、有機EL素子などが挙げられる。

【0030】

本発明の電子装置は本発明の電子回路を備える。

50

**【 0 0 3 1 】**

ここで、「電子装置」とは、特に限定されるものではないが、本発明の電子回路を回路素子として含んで構成される装置一般をいう。

**【 0 0 3 2 】**

本発明の電気光学装置は、複数のデータ線と複数の走査線との交差部に対応して配置された複数の単位回路を含む電気光学装置であって、前記複数のデータ線を介して前記単位回路に供給するデータ信号の送出を制御するデータ線駆動回路と、前記複数の走査線を介して前記単位回路に供給する走査信号の送出を制御する走査線駆動回路とを備え、前記単位回路は、電気光学素子と、前記電気光学素子に駆動電流を供給する駆動トランジスタと、前記単位回路に供給された前記データ信号を電荷量として保持する機能を少なくとも有する電荷保持手段とを備え、前記電荷保持手段は、第1の容量素子を含み、前記第1の容量素子の一方の電極は前記駆動トランジスタのゲート端子に接続され、他方の電極は可変電圧供給手段に接続可能である。

**【 0 0 3 3 】**

かかる構成により、データ線駆動回路から単位回路に供給される電流を電荷保持によって保持し、トランジスタから電気光学素子に供給される駆動電流の供給を促す一方で、第1の容量素子を介して可変電圧供給手段からゲート端子に供給される電圧変化によって、トランジスタの導通状態を制御し、電気光学素子に供給される駆動電流の供給量を制御することができる。

**【 0 0 3 4 】**

ここで、「電気光学装置」とは、電気的作用により自発光し、若しくは外部から供給される光の光学的状態を変化させて表示画像を生成するための表示装置をいう。

**【 0 0 3 5 】**

好ましくは、前記可変電圧供給手段から出力された電圧の値の変化を、前記第1の容量素子を介して前記ゲート端子に伝達可能とする。

**【 0 0 3 6 】**

好ましくは、前記第1の容量素子は少なくとも1つのスイッチング素子を介して前記可変電圧供給手段に接続可能とする。

**【 0 0 3 7 】**

好ましくは、前記電荷保持手段は、さらに第2の容量素子を含み、前記第2の容量素子の一方の電極は前記ゲート端子に接続され、他方の電極は電源線に接続可能とする。

**【 0 0 3 8 】**

好ましくは、前記トランジスタは、少なくとも1つのスイッチング素子を介してデータ線駆動回路に接続することが可能である。

**【 0 0 3 9 】**

好ましくは、前記第2の容量素子は、前記トランジスタを通過して前記データ線駆動回路から出力される出力電流に応じた電荷を保持する一方、前記トランジスタのドレイン端子若しくはソース端子から前記出力電流と同程度の電流を出力させるために前記ゲート端子に印加される電圧を調整する。

**【 0 0 4 0 】**

好ましくは、前記データ信号としての電流を出力する電流输出回路を備える。

**【 0 0 4 1 】**

電子素子の例として、電気光学素子、電流駆動型発光素子、有機EL素子などが挙げられる。

**【 0 0 4 2 】**

本発明の電気光学装置は、複数のデータ線と複数の走査線との交差部に対応して配置された複数の単位回路を含む電気光学装置であって、前記複数のデータ線を介して前記単位回路に供給するデータ信号の送出を制御するデータ線駆動回路と、前記複数の走査線を介して前記単位回路に供給する走査信号の送出を制御する走査線駆動回路とを備え、前記単位回路は、電子素子と、前記電子素子に供給する電流量を、導通状態に応じて制御するトランジスタと、前記トランジスタのゲート端子に接続される電源線とを有する電荷保持手段とを有する。

10

20

30

40

50

ンジスタと、少なくとも前記トランジスタを通過する電流を電圧に変換して、前記トランジスタのゲート端子に印加される電圧値の初期値を設定するための電流 - 電圧変換を行う電流 - 電圧変換手段と、前記電流 - 電圧変換後において、前記ゲート端子に印加される電圧値を調整する電圧調整手段とを備える。

## 【0043】

好ましくは、前記電流 - 電圧変換時に前記トランジスタを通過する電流は、前記データ信号に基づいて設定される電流値である。

## 【0044】

好ましくは、前記電圧調整手段は、前記電流 - 電圧変換時における前記トランジスタの導通状態を減ずるように前記トランジスタのゲート端子に印加される電圧値を調整する。

10

## 【0045】

好ましくは、前記電圧調整手段は、可変電圧供給手段から供給される電圧変化を容量カップリングを通じて前記ゲート端子に印加し、前記トランジスタの導通状態を制御する。

## 【0046】

電子素子の例として、電気光学素子、電流駆動型発光素子、有機EL素子などが挙げられる。

## 【0047】

本発明の電子機器は、本発明の電気光学装置を備えて構成される。

## 【0048】

このような電子機器として、電気光学装置をディスプレイとして備える機器であれば特に限定されるものではなく、携帯電話、ビデオカメラ、パーソナルコンピュータ、ヘッドマウントディスプレイ、プロジェクタ、ファックス装置、デジタルカメラ、PDA、電子手帳などを含む。

20

## 【0049】

本発明の電子回路の駆動方法は、保持キャパシタの一方の電極をトランジスタのゲート端子に接続した状態で、データ線を介して供給されるデータ信号を当該トランジスタのドレイン端子とソース端子間を通過させることにより前記保持キャパシタに電荷を蓄積し、前記データ信号を前記ゲート端子に印加されるべき電圧の初期値に変換する変換ステップと、前記保持キャパシタに充電された電圧により前記ゲート端子の印加電圧を調整し、前記トランジスタから出力される電流を電子素子に供給する供給ステップと、可変電圧供給手段の電圧変化を容量カップリングを介して前記ゲート端子に伝達し、前記トランジスタの導通状態を調整する調整ステップとを含む。

30

## 【0050】

好ましくは、前記データ信号は電流である。

## 【0051】

好ましくは、前記調整ステップにおいて、前記ゲート端子に一方の電極が接続する容量素子の他方の電極に可変電圧供給手段からの電圧変化を供給する。

## 【0052】

電子素子の例として、電気光学素子、電流駆動型発光素子、有機EL素子などが挙げられる。

40

## 【0053】

好ましくは、前記調整ステップにおいて、表示階調に対応した発光期間経過後、前記トランジスタの導通状態をオフに調整する。

## 【0054】

## 【発明の実施の形態】

発明の実施の形態1.

以下、各図を参照して本実施の形態について説明する。

## 【0055】

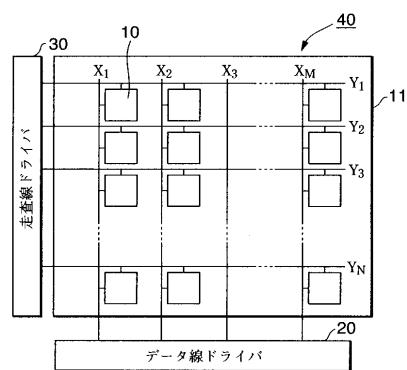

図4は電気光学装置40の主要部分におけるブロック図である。ここでは、電気光学装置40として、アクティブマトリクス駆動型有機ELディスプレイを例示して説明する。電

50

気光学装置 40 は、透明ガラス基板上に N 行 M 列のマトリクス状に配置された画素回路 10 を含むアレイ基板 11 と、同基板上に形成された M 本のデータ線線  $X_1, X_2, \dots, X_M$  を介して列方向に並ぶ画素回路群にプログラミング電流を供給するデータ線ドライバ 20 と、同基板上に形成された N 本の走査線線  $Y_1, Y_2, \dots, Y_N$  を介して行方向に並ぶ画素回路群を線順次走査し、プログラミング電流の供給を選択的にアクティブにする走査線ドライバ 30 を備えて構成されている。

#### 【 0 0 5 6 】

尚、データ線はソース線と、データ線ドライバはソースドライバと、走査線はゲート線と、走査線ドライバはゲートドライバと、画素回路は単位回路或いは単に画素と称することもできる。

10

#### 【 0 0 5 7 】

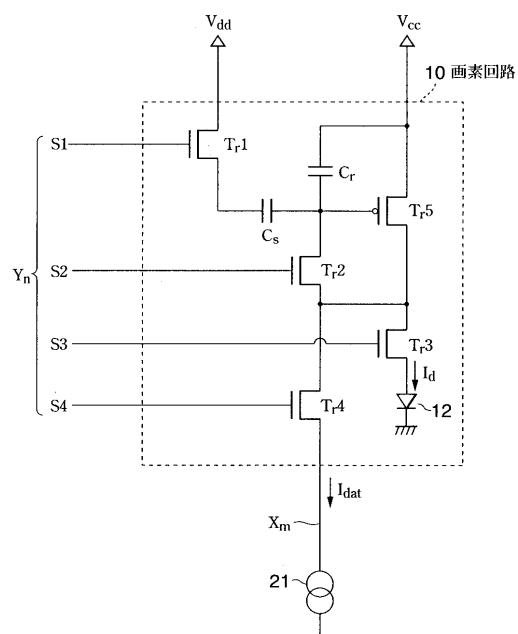

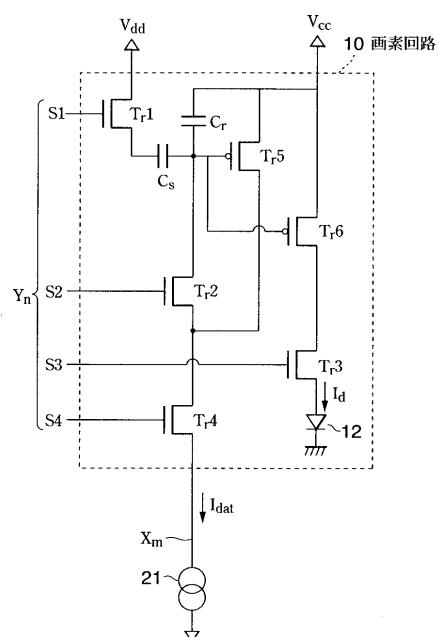

図 1 はアレイ基板 11 上において、n 行 m 列 (1 n N, 1 m M) の位置に配置されている画素回路 10 の回路構成図である。画素回路 10 は電流駆動型発光素子として機能する有機 EL 素子 12 と、走査線  $Y_N$  から出力される信号を受けてスイッチング動作を行うスイッチングトランジスタ  $T_{r1} \sim T_{r4}$  と、外部回路からプログラミング電流の供給を受けて所定量の電荷を蓄積する保持キャパシタ  $C_r$  と、保持キャパシタ  $C_r$  から電圧供給を受けて 1 フレーム期間にわたり有機 EL 素子 12 に駆動電流  $I_d$  を供給する駆動トランジスタ  $T_{r5}$  と、可変電圧源  $V_{dd}$  からの電圧供給を容量カップリングにより駆動トランジスタ  $T_{r5}$  のゲート電極に伝達し、有機 EL 素子 12 への駆動電流  $I_d$  の供給を制御するキャパシタ  $C_s$  とを含んで構成されている。また、データ線  $X_m$  は定電流源 21 に接続しており、走査線  $Y_N$  は 4 本のサブ走査線  $S_1 \sim S_4$  から構成されている。定電流源 21 から出力される電流はデータ信号とも称され、その電流値は各画素回路 10 の発光階調に対応して定めれる。

20

#### 【 0 0 5 8 】

上記の構成において、サブ走査線  $S_1 \sim S_4$  の各々はスイッチングトランジスタ  $T_{r1} \sim T_{r4}$  のゲート電極に接続しており、Y ドライバ 30 から出力される信号の H レベル / L レベルに対応してスイッチングトランジスタ  $T_{r1} \sim T_{r4}$  のオン / オフ制御を行う。スイッチングトランジスタ  $T_{r1} \sim T_{r4}$  は n チャンネル型 FET から構成されており、H レベルの信号によりオン状態（開状態）となる。スイッチングトランジスタ  $T_{r1}$  はサブ走査線  $S_1$  からの信号に対応して、可変電圧源  $V_{dd}$  からの電圧をキャパシタ  $C_s$  に供給するためのスイッチング素子であり、そのドレイン端子は可変電圧源  $V_{dd}$  に接続される一方、ソース端子はキャパシタ  $C_s$  に接続している。スイッチングトランジスタ  $T_{r2}$  及び  $T_{r4}$  はサブ走査線  $S_2, S_4$  からの H レベルの信号によりオン状態となり、データ線  $X_m$  を介して定電流電源 22 から供給されるプログラミング電流  $I_{dat}$  の値に対応した電荷を保持キャパシタ  $C_r$  に蓄積するためのスイッチング素子である。保持キャパシタ  $C_r$  はプログラミング電流  $I_{dat}$  の値に対応した電荷を保持するため、記憶キャパシタと称することもできる。スイッチングトランジスタ  $T_{r2}$  のドレイン端子はキャパシタ  $C_s$ 、保持キャパシタ  $C_r$  及び駆動トランジスタ  $T_{r5}$  のゲート端子に接続される一方、ソース端子はスイッチングトランジスタ  $T_{r4}$  及び  $T_{r3}$  のドレイン端子に接続されている。スイッチングトランジスタ  $T_{r3}$  はサブ走査線  $S_3$  からの H レベルの信号によりオン状態となり、駆動トランジスタ  $T_{r5}$  から出力される駆動電流  $I_d$  を有機 EL 素子 12 に注入するためのスイッチング素子であり、そのソース端子は有機 EL 素子 12 の陽極に直列接続される一方、そのドレイン端子は駆動トランジスタ  $T_{r5}$  のドレイン端子と  $T_{r2}$  のソース端子に接続されている。駆動トランジスタ  $T_{r5}$  は p チャンネル型 FET から構成され、そのソース端子は定電圧電源  $V_{cc}$  に接続されている。定電圧電源  $V_{cc}$  は駆動トランジスタ  $T_{r5}$  をピンチオフ領域で動作させるために必要かつ十分なバイアス電圧に設定されている。

30

#### 【 0 0 5 9 】

尚、スイッチングトランジスタ  $T_{r1} \sim T_{r4}$  は、リーク電流が多いと不必要なときに画素が点灯する可能性があるため、オフ状態におけるリーク電流が少ないと要求される。オフ・リークは LDD 構造によって抑えることができるが、p チャンネル型 FET よりも

40

50

nチャネル型FETの方がその効果が大きい。よって、スイッチングトランジスタTr1～Tr4はnチャネル型、駆動トランジスタTr5はpチャネル型が好ましいが、この組み合わせに限られるものではない。

#### 【0060】

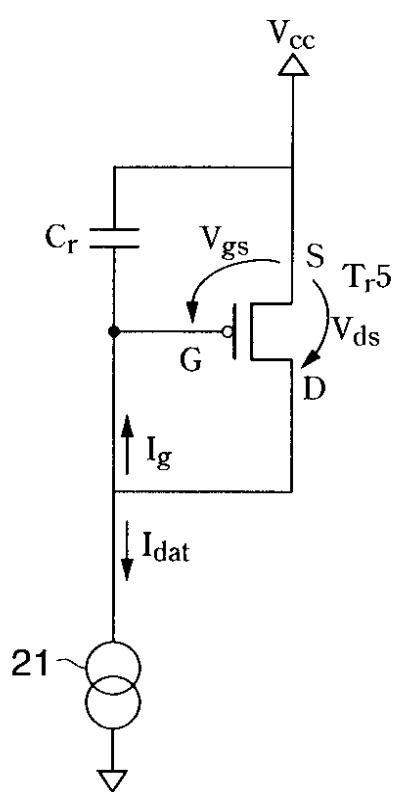

図5は画素回路10を駆動するための1フレーム期間内における各信号のタイミングチャートである。1フレーム期間は画素回路10への電流プログラムを行うプログラミング期間と、有機EL素子12へ駆動電流 $I_d$ を供給する発光期間と、有機EL素子への駆動電流 $I_d$ の供給を停止する非発光期間とを含む。毎秒60フレームの画像を表示する場合には、1フレーム期間は約16.7msである。プログラミング期間においては、サブ走査線S1, S3の信号がLレベルに立ち下がる一方で、サブ走査線S2, S4の信号がHレベルに立ち上がる。これにより、スイッチングトランジスタTr1, Tr3はオフ状態(閉状態)になる一方、スイッチングトランジスタTr2, Tr4はオン状態となる。また、定電流電源22からは画素回路10に対してプログラミング電流 $I_{dat}$ の供給を開始する。このときの画素回路10における等価回路は図2のようになる。

#### 【0061】

同図において、駆動トランジスタTr5のゲート/ソース間の電圧 $V_{gs}$ は当初、負にバイアスされており、そのチャネルに流れる過渡的なドレイン電流は定電流電源21から供給されるプログラミング電流 $I_{dat}$ と、ゲート電極に回り込む電流 $I_g$ の和となる。プログラミング電流 $I_{dat}$ の値は表示階調に対応してその大きさが定められるが、本実施形態においては、画素回路10へのデータの書き込み遅延をできるだけ低減するため、プログラミング電流 $I_{dat}$ の値をやや大きめに設定している。ゲート電極に回り込む電流 $I_g$ によって保持キャパシタCrには電荷が蓄積されることになるが、その電荷量(若しくは電圧値)はプログラミング電流 $I_{dat}$ に応じた値となる。本実施形態においては、電流プログラミングを通じて保持キャパシタCrに蓄積された電圧によって、駆動トランジスタTr5のゲート端子に印加される初期電圧が定まるため、保持キャパシタCrは電流-電圧変換手段として機能する。このように、電流プログラミングによって保持キャパシタCrに所定の電荷を蓄積する操作をデータの書き込みと称する。スイッチングトランジスタTr2がオン状態となることで、駆動トランジスタTr5のゲート/ドレイン間は導通状態にあるため、プログラミング終了時点において、ゲート/ソース間の電圧 $V_{gs}$ と、ドレイン/ソース間の電圧 $V_{ds}$ とは等しくなっている。

#### 【0062】

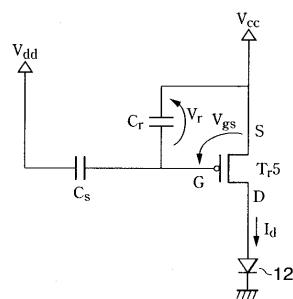

保持キャパシタCrへのデータの書き込みが終了したならば、発光期間に入り、サブ走査線S1, S3の信号をLレベルからHレベルに立ち上げる一方で、サブ走査線S2, S4の信号をHレベルからLレベルに立ち下げる。これにより、スイッチングトランジスタTr1, Tr3はオフ状態からオン状態に遷移する一方、スイッチングトランジスタTr2, Tr4はオン状態からオフ状態へ遷移する。また、同期間ににおいて定電流電源21から画素回路10に供給されるプログラミング電流 $I_{dat}$ は0に停止され、可変電圧源 $V_{dd}$ の出力電圧は一定のまま保持される。このときの画素回路10における等価回路は図3のようになる。同図において、電流プログラミングの際に保持キャパシタCrに充電された電圧によって、駆動トランジスタTr5がオン状態となり、同トランジスタから駆動電流が出力される。このときの駆動電流の値は、プログラミング電流 $I_{dat}$ にほぼ等しい。従つて、発光期間において駆動トランジスタTr5が有機EL素子12を駆動するための駆動電流 $I_d$ はプログラミング電流 $I_{dat}$ にほぼ等しくなる。本実施形態においては、プログラミング電流 $I_{dat}$ の値を通常の値よりもやや大きめに設定してあるため、発光期間は通常の値よりもやや短めに設定する必要がある。

#### 【0063】

階調表示に必要な期間、有機EL素子12を駆動したならば、非発光期間に移る。非発光期間においては、可変電圧源 $V_{dd}$ の電圧を $V_{dd}$ だけ変化させる一方で、サブ走査線S1～S4に出力される各々の信号のオン/オフ状態を維持したままにする。可変電圧源 $V_{dd}$ の電圧を $V_{dd}$ だけ変化させると、キャパシタCsの容量カップリングによりキャパシタ

10

20

30

40

50

電圧  $V_r$  の電圧値が変化し、駆動トランジスタ  $T_r 5$  が output する駆動電流  $I_d$  の値を制御することができる。つまり、キャパシタ  $C_s$  は駆動トランジスタ  $T_r 5$  のゲート端子の電圧を調整するための電圧調整手段として機能する。いま、同図に示す向きにキャパシタ電圧  $V_r$  の向きを定めると、キャパシタ電圧  $V_r$  は下式のように記述できる。

$$V_r = V_{cc} - V_{th} - C_s \cdot V_{dd} / (C_s + C_r + C_g) \quad \dots (1)$$

一方、駆動トランジスタ  $T_r 5$  のチャネルを流れる駆動電流  $I_d$  は下式のように記述できることが知られている。

$$I_d = (V_{gs} - V_{th})^2 \quad \dots (2)$$

ここで、 $= (W \mu C_{ox}) / (2L)$  であり、W はチャネル幅、L はチャネル長、 $\mu$  は移動度、 $C_{ox}$  は単位面積当たりのゲート酸化膜容量、 $V_{gs}$  はゲート / ソース間の電圧であり、その向きは同図に示す通りである。 $V_r = -V_{gs}$  であるから、(2) 式に (1) 式を代入することにより、 $V_{gs}$  を消去し、 $= C_s / (C_s + C_r + C_g)$  とすれば、下式が得られる。

$$I_d = (V_{dd} - V_{cc})^2 \quad \dots (3)$$

ここで、 $V_{dd} = V_{cc} /$  とすれば、駆動電流  $I_d$  を 0 にすることができる。有機 E L 素子 12 の発光を停止することができる。つまり、発光期間においては、 $V_{dd} = 0$  とする一方、非発光期間においては、 $V_{dd} = V_{cc} /$  とすることで、駆動トランジスタ  $T_r 5$  による駆動電流  $I_d$  の供給をオン / オフ制御することができる。

#### 【0064】

このように、本実施形態によれば、プログラミング電流  $I_{dat}$  の値をやや大きめに設定することで、データの書き込み遅延を低減することができる。さらに、有機 E L 素子 12 への駆動電流  $I_d$  の供給停止は容量カッピングを用いて制御するため、駆動電流  $I_d$  の供給停止を速やかに行うことができる。駆動電流  $I_d$  の供給を停止するための他の手段として、例えば、保持キャパシタ  $C_r$  の蓄積電荷を引き抜くための電流経路を別途設け、かかる電流経路から当該蓄積電荷を引き抜けば、駆動トランジスタ  $T_r 5$  のゲート電極に印加される電圧を調整できるため、駆動電流  $I_d$  の供給を停止することができるが、電荷の引き抜きに時間を要するため、高速動作に不向きというデメリットがある。これに対し、容量カッピングを利用すれば、駆動トランジスタ  $T_r 5$  のゲート電圧を瞬時に制御できるため、高速動作に優れているというメリットがある。

#### 発明の実施の形態 2 .

図 6 は第 2 の実施形態における画素回路 10 の回路構成図である。同図において、トランジスタ  $T_r 5$  及び  $T_r 6$  は各々のゲート電極同士及びソース電極同士が相互に接続しており、カレントミラー回路を構成している。カレントミラー回路においては、各々のトランジスタを流れる電流比は利得係数の比に等しい。このため、トランジスタ  $T_r 5$  及び  $T_r 6$  のチャネル長、チャネル幅、ゲート酸化膜容量等のデバイスパラメータを適当に設計することで、両者の電流比を  $k : 1$  とすることができる。図中、スイッチングトランジスタ  $T_r 1 \sim T_r 4$ 、キャパシタ  $C_s$ 、及び保持キャパシタ  $C_r$  の各々の動作は実施形態 1 と同様であり、詳細な説明は省略する。また、トランジスタ  $T_r 5$  及び  $T_r 6$  は p チャンネル型 F E T である。上記の構成において、プログラミング期間における画素回路 10 の等価回路は図 2 と同じ構成になり、発光期間及び非発光期間における画素回路 10 の等価回路は図 3 と同じ構成になる（但し、本実施形態においては、図 3 に記載のトランジスタ  $T_r 5$  をトランジスタ  $T_r 6$  に置き換えた構成となる。）。ここで、 $k > 1$  となるようにトランジスタ  $T_r 5$  及び  $T_r 6$  の利得係数を設定すれば、プログラミング期間におけるトランジスタ  $T_r 5$  による保持キャパシタ  $C_r$  への電荷の蓄積を高速に行うことができ、プログラミング期間を短縮することができる。

#### 【0065】

尚、上記の説明では、データ信号の供給を線順次操作で行っていたが、これに限らず、例えば、点順次走査或いは相展開方式で行ってもよい。また、上述のトランジスタ  $T_r 1 \sim T_r 6$  の全部又は一部について、F E T に替えてバイポーラトランジスタや、他のスイッチング素子で代用してもよい。また、上記の例では、アクティブマトリクス駆動方式を前

10

20

30

40

50

提に説明したが、これに限らず、パッシブマトリクス駆動方式を利用してもよい。また、上記の説明では有機E-Lディスプレイの例を説明したが、LEDや、FEDなどの電流駆動型発光素子を用いた電気光学装置にも適用できる。

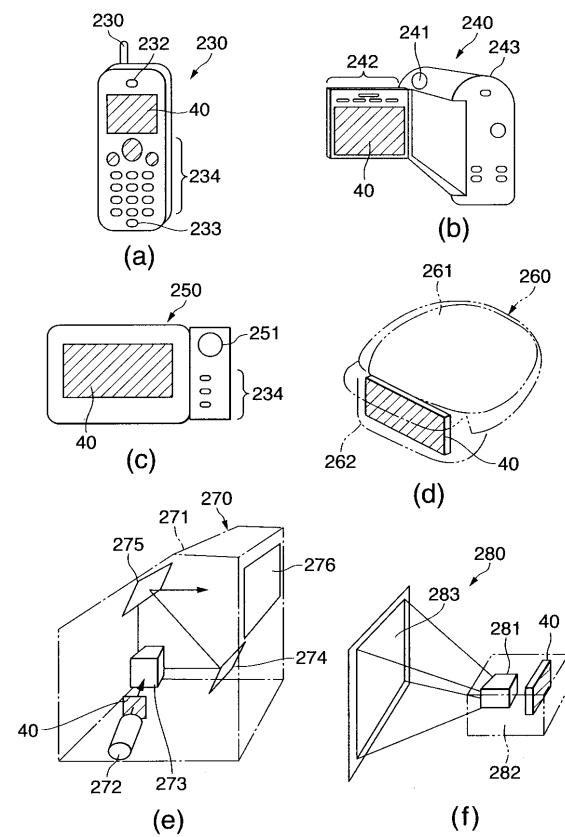

【0066】

図7に本発明の電気光学装置40を適用可能な電子機器の例を挙げる。同図(a)は携帯電話への適用例であり、携帯電話230は、アンテナ部231、音声出力部232、音声入力部233、操作部234、及び本発明の電気光学装置40を備えている。このように本発明の電気光学装置40を携帯電話230の表示部として利用可能である。同図(b)はビデオカメラへの適用例であり、ビデオカメラ240は、受像部241、操作部242、音声入力部243、及び本発明の電気光学装置40を備えている。このように本発明の電気光学装置は、ファインダーや表示部として利用可能である。同図(c)は携帯型パソコンへの適用例であり、コンピュータ250は、カメラ部251、操作部252、及び本発明の電気光学装置40を備えている。このように本発明の電気光学装置は、表示部として利用可能である。

10

【0067】

同図(d)はヘッドマウントディスプレイへの適用例であり、ヘッドマウントディスプレイ260は、バンド261、光学系収納部262及び本発明の電気光学装置40を備えている。このように本発明の電気光学装置は画像表示源として利用可能である。同図(e)はリア型プロジェクターへの適用例であり、プロジェクター270は、筐体271に、光源272、合成光学系273、ミラー274、ミラー275、スクリーン276、及び本発明の電気光学装置40を備えている。このように本発明の電気光学装置は画像表示源として利用可能である。同図(f)はフロント型プロジェクターへの適用例であり、プロジェクター280は、筐体282に光学系281及び本発明の電気光学装置40を備え、画像をスクリーン283に表示可能になっている。このように本発明の電気光学装置は画像表示源として利用可能である。上記例に限らず本発明の電気光学装置40は、アクティブマトリクス型の表示装置を適用可能なあらゆる電子機器に適用可能である。例えば、この他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、DSP装置、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、POS端末、ワープローション、テレビ電話、ワードプロセッサ、電卓、ページャ、カーナビゲーション装置などに備えられている電気光学装置にも適用可能である。

20

【0068】

【発明の効果】

本発明によれば、トランジスタのゲート端子の電圧を容量カップリングを用いて制御することによって、電子素子へ供給される電流の出力を瞬時に制御できるため、電子回路の高速駆動を可能にすることができる。

【図面の簡単な説明】

【図1】実施形態1に係わる画素回路の回路構成図である。

【図2】電流プログラミング時における画素回路の等価回路である。

【図3】発光期間における画素回路の等価回路である。

【図4】有機E-Lディスプレイの主要回路構成図である。

30

【図5】画素回路を駆動するための各信号のタイミングチャートである。

【図6】実施形態2に係わる画素回路の回路構成図である。

【図7】電気光学装置を備えた電子機器の例である。

【符号の説明】

10...画素回路

11...アレイ基板

20...データ線ドライバ

21...定電流源

30...走査線ドライバ

Tr1~Tr4...スイッチングトランジスタ

40

50

Tr5 ... 駆動トランジスタ

Cr ... 保持キャパシタ

Cs ... キャパシタ

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 D

H 05 B 33/14 A

(56)参考文献 国際公開第 01 / 006484 (WO, A1)

特開2003-140612 (JP, A)

特開平10-319908 (JP, A)

特開2001-042822 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/30, 3/20