(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6259936号

(P6259936)

(45) 発行日 平成30年1月10日(2018.1.10)

(24) 登録日 平成29年12月15日(2017.12.15)

(51) Int.Cl.

F 1

|        |        |           |        |       |         |

|--------|--------|-----------|--------|-------|---------|

| G 11 C | 19/28  | (2006.01) | G 11 C | 19/28 | 2 3 0   |

| G 02 F | 1/133  | (2006.01) | G 02 F | 1/133 | 5 5 0   |

| G 09 G | 3/20   | (2006.01) | G 09 G | 3/20  | 6 2 2 E |

| G 09 G | 3/3266 | (2016.01) | G 09 G | 3/20  | 6 2 1 M |

| G 09 G | 3/36   | (2006.01) | G 09 G | 3/20  | 6 8 0 G |

請求項の数 16 (全 48 頁) 最終頁に続く

(21) 出願番号

特願2017-1501(P2017-1501)

(22) 出願日

平成29年1月9日(2017.1.9)

(62) 分割の表示

特願2013-34158(P2013-34158)

の分割

原出願日

平成25年2月25日(2013.2.25)

(65) 公開番号

特開2017-107632(P2017-107632A)

(43) 公開日

平成29年6月15日(2017.6.15)

審査請求日

平成29年1月9日(2017.1.9)

(31) 優先権主張番号

特願2012-42864(P2012-42864)

(32) 優先日

平成24年2月29日(2012.2.29)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 梅崎 敦司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 後藤 彰

(56) 参考文献 米国特許出願公開第2005/0220

262 (U.S., A 1)

特開2004-078172 (JP, A

)特開2007-123861 (JP, A

)

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

10

20

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、 10

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続されることを特徴とする表示装置。

#### 【請求項2】

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、 20

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、 30

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、 40

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲ 50

ーと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第1のトランジスタのW/L（Wはチャネル幅、Lはチャネル長）は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きいことを特徴とする表示装置。 10

### 【請求項3】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、 20

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、 30

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、 40

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と電気的に接続され、 50

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と電気的に接続されることを特徴とする表示装置。

【請求項4】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、10

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、20

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、30

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第1のトランジスタのW/L（Wはチャネル幅、Lはチャネル長）は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、40

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と電気的に接続され、

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記50

第1の配線と電気的に接続されることを特徴とする表示装置。

**【請求項 5】**

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力されることを特徴とする表示装置。

**【請求項 6】**

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続

10

20

30

40

50

され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きいことを特徴とする表示装置。

#### 【請求項7】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

10

20

30

40

50

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、 10

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、 20

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と電気的に接続され、

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と電気的に接続されることを特徴とする表示装置。

#### 【請求項8】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、 30

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と電気的に接続され、 40

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソ 50

ース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第7のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と電気的に接続され、

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と電気的に接続されることを特徴とする表示装置。

#### 【請求項9】

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソ

10

20

30

40

50

ース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続されることを特徴とする表示装置。

【請求項10】

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

10

20

30

40

50

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きいことを特徴とする表示装置。

【請求項11】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され

、前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され

、前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と直接接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と直接接続され

、前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と直接接続されることを特徴とする表示装置。

【請求項12】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

10

20

30

40

50

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され

、前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され

、前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と直接接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と直接接続され

、前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と直接接続されることを特徴とする表示装置。

### 【請求項13】

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され

10

20

30

40

50

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力されることを特徴とする表示装置。

**【請求項14】**

ゲートドライバを有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

10

20

30

40

50

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きいことを特徴とする表示装置。

【請求項15】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

10

20

30

40

50

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と直接接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と直接接続され

、

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と直接接続されることを特徴とする表示装置。

10

【請求項16】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、第7のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と直接接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と直接接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の電源線と直接接続され

、

前記第2のトランジスタのソース又はドレインの他方は、第2の電源線と直接接続され

、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと直接接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと直接接続され、

前記第3のトランジスタのゲートは、第2の配線と直接接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第6のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと直接接続され、

前記第5のトランジスタのソース又はドレインの他方は、第3の配線と直接接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第2の電源線と直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートと直接接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと直接接続され、

前記第7のトランジスタのゲートは、前記第2の配線と直接接続され、

前記第2の配線には、第1のクロック信号が入力され、

前記第3の配線には、第2のクロック信号が入力され、

前記第1のトランジスタのW/L (Wはチャネル幅、Lはチャネル長)は、前記第3のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第5のトランジスタのW/Lよりも大きく、

前記第1のトランジスタのW/Lは、前記第6のトランジスタのW/Lよりも大きく、

20

30

40

50

前記第1のトランジスタのW/Lは、前記第7のトランジスタのW/Lよりも大きく、

前記第2のトランジスタのW/Lは、前記第4のトランジスタのW/Lよりも大きく、

前記画素は、第8のトランジスタと、第9のトランジスタと、発光素子と、を有し、

前記第8のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのソース又はドレインの一方と直接接続され、

前記第9のトランジスタのソース又はドレインの他方は、前記発光素子と直接接続され、

前記第8のトランジスタのゲート又は前記第9のトランジスタのゲートの一方は、前記第1の配線と直接接続されることを特徴とする表示装置。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明の一態様は、半導体装置及び表示装置等に関する。

【背景技術】

【0002】

近年、同じの極性のトランジスタで構成されるシフトレジスタ回路の開発が活発に進められている（特許文献1参照）。特許文献1のシフトレジスタ回路は、Nチャネル型のトランジスタで構成されている。そして、クロック信号がハイレベルになったときに、そのクロック信号を出力することにより、ハイレベルの信号を順次出力する。しかし、特許文献1のシフトレジスタ回路は、クロック信号を出力するため、ロウレベルの信号を順次出力することができない。

20

【0003】

また、特許文献1のシフトレジスタがPチャネル型のトランジスタで構成した場合、ロウレベルの信号を順次出力することができるようになるものの、ハイレベルの信号を順次出力することができなくなる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004-103226号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、Nチャネル型のトランジスタで構成されたシフトレジスタ回路において、ロウレベルの信号を順次出力することが求められている。また、Pチャネル型のトランジスタで構成されたシフトレジスタ回路において、ハイレベルの信号を順次出力することが求められている。

【0006】

そこで、本発明の一態様は、Nチャネル型のトランジスタで構成され、ロウレベルの信号を順次出力するための回路を提供することを課題の一とする。また、本発明の一態様は、Pチャネル型のトランジスタで構成され、ハイレベルの信号を順次出力するための回路を提供することを課題の一とする。また、本発明の一態様は、回路規模を小さくすることを課題の一とする。また、本発明の一態様は、消費電力を小さくすることを課題の一とする。

40

【課題を解決するための手段】

【0007】

本発明の一態様は、ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第3の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第2のトランジスタと、ソース及びドレインの一方が第4の配線と電気的に接続され、ソース及びドレインの他方が第2のトランジスタのゲートと電気

50

的に接続された第3のトランジスタと、ソース及びドレインの一方が第5の配線と電気的に接続され、ソース及びドレインの他方が第3のトランジスタのゲートと電気的に接続され、ゲートが第6の配線と電気的に接続された第4のトランジスタと、第1の端子が第3の配線と電気的に接続され、第2の端子が第1のトランジスタのゲートと電気的に接続された第1のスイッチと、を有する半導体装置である。

#### 【0008】

なお、上記本発明の一態様は、第1の端子が第1の配線と電気的に接続され、第2の端子が第1のトランジスタのゲートと電気的に接続された第2のスイッチを有していてもよい。

#### 【0009】

なお、上記本発明の一態様は、第1の端子が第3の配線と電気的に接続され、第2の端子が第2のトランジスタのゲートと電気的に接続された第3のスイッチを有していてもよい。

#### 【0010】

なお、上記本発明の一態様において、第1乃至第4のトランジスタは、チャネル形成領域に酸化物半導体を含んでいてもよい。

#### 【発明の効果】

#### 【0011】

本発明の一態様は、Nチャネル型のトランジスタで構成され、ロウレベルの信号を順次出力するための回路を提供することができる。また、本発明の一態様は、Pチャネル型のトランジスタで構成され、ハイレベルの信号を順次出力するための回路を提供することができる。また、本発明の一態様は、回路規模を小さくすることができる。また、本発明の一態様は、消費電力を小さくすることができる。

#### 【図面の簡単な説明】

#### 【0012】

【図1】本発明に係る基本回路を説明する図。

【図2】本発明に係る順序回路を説明する図。

【図3】本発明に係るシフトレジスタ回路を説明する図。

【図4】本発明に係るシフトレジスタ回路を説明する図。

【図5】本発明に係る順序回路を説明する図。

【図6】本発明に係る順序回路を説明する図。

【図7】本発明に係る順序回路を説明する図。

【図8】本発明に係る順序回路を説明する図。

【図9】本発明に係る順序回路を説明する図。

【図10】本発明に係る基本回路及び順序回路を説明する図。

【図11】本発明に係る基本回路を説明する図。

【図12】本発明に係る表示装置を説明する図。

【図13】本発明に係る表示装置を説明する図。

【図14】本発明に係るトランジスタを説明する図。

【図15】本発明に係る電子機器を説明する図。

#### 【発明を実施するための形態】

#### 【0013】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明の構成は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

#### 【0014】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、信号波形、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケ

10

20

30

40

50

ールに限定されない。

【0015】

なお、本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0016】

（実施の形態1）

本実施の形態では、本発明の一態様に係る、基本回路、順序回路、及びシフトレジスタ回路について説明する。

【0017】

まず、本実施の形態の基本回路（半導体装置又は駆動回路ともいう）について説明する。

10

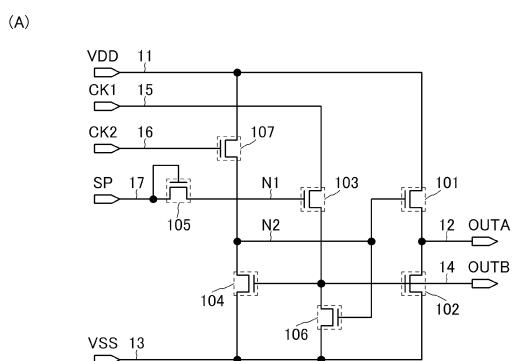

【0018】

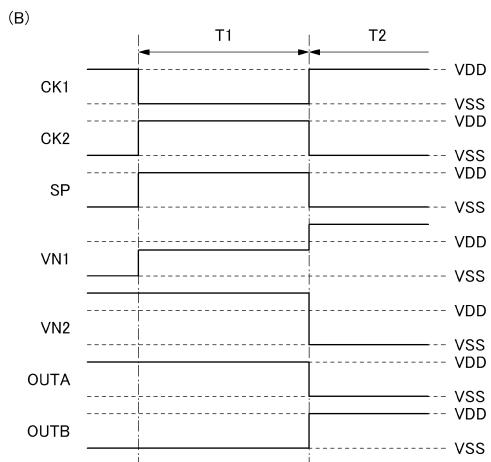

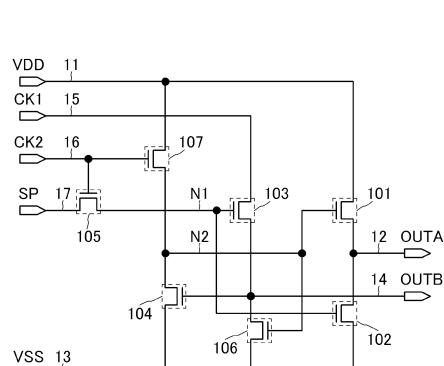

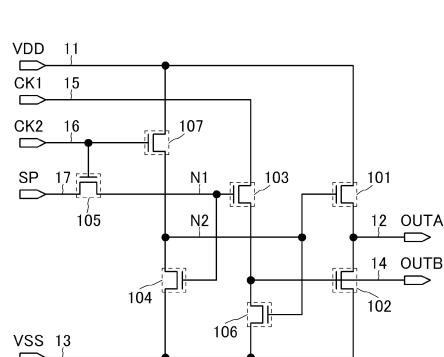

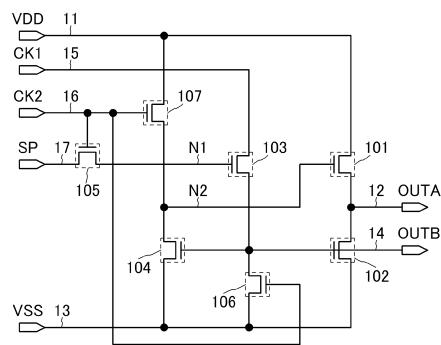

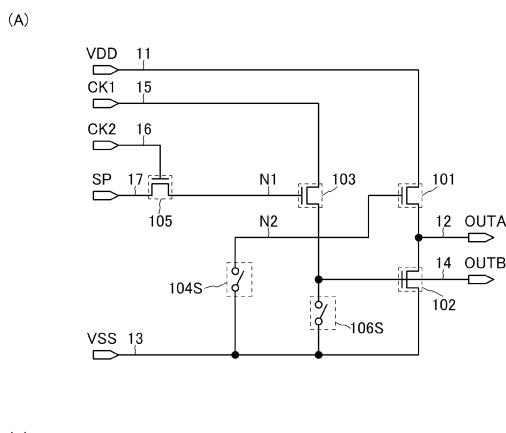

図1（A）は、本実施の形態の基本回路の回路図である。図1（A）の基本回路は、トランジスタ101乃至トランジスタ105を有する。

【0019】

なお、本発明の一態様において、トランジスタの極性はNチャネル型でもよいし、Pチャネル型でもよい。ただし、トランジスタ101乃至トランジスタ105の極性は同じ極性であることが好ましい。本実施の形態では、トランジスタ101乃至トランジスタ105がNチャネル型であるとして説明する。

【0020】

20

なお、本発明の一態様において、トランジスタとしては、チャネル形成領域にシリコン又はゲルマニウムなどの半導体を含むトランジスタを用いることができる。また、トランジスタとしては、チャネル形成領域に酸化物半導体又は窒化物半導体などの半導体を含むトランジスタを用いることができる。なお、前述した半導体は、非晶質、微結晶、多結晶又は単結晶である領域を有する。

【0021】

なお、本発明の一態様において、トランジスタとしては、薄膜トランジスタ（TFT）を用いることができる。また、トランジスタとしては、半導体基板又はSOI基板を用いて形成される、MOS型トランジスタ、接合型トランジスタ又はバイポーラトランジスタ等を用いることができる。

30

【0022】

次に、図1（A）の基本回路の接続関係について説明する。

【0023】

トランジスタ101の第1の端子（ソース及びドレンの一方ともいう）は配線11と接続され、トランジスタ101の第2の端子（ソース及びドレンの他方ともいう）は配線12と接続される。トランジスタ102の第1の端子は配線13と接続され、トランジスタ102の第2の端子は配線12と接続され、トランジスタ102のゲートは配線14と接続される。トランジスタ103の第1の端子は配線15と接続され、トランジスタ103の第2の端子は配線14と接続される。トランジスタ104の第1の端子は配線13と接続され、トランジスタ104の第2の端子はトランジスタ101のゲートと接続され、トランジスタ104のゲートは配線14と接続される。トランジスタ105の第1の端子は配線17と接続され、トランジスタ105の第2の端子はトランジスタ103のゲートと接続され、トランジスタ105のゲートは配線16と接続される。

40

【0024】

なお、トランジスタ103のゲートとトランジスタ105の第2の端子との接続箇所をノードN1と示す。また、トランジスタ101のゲートとトランジスタ104の第2の端子との接続箇所をノードN2と示す。

【0025】

なお、本明細書等において、接続とは電気的な接続を意味しており、電流、電圧、電位、信号又は電荷等を供給又は伝送可能な状態に相当する。よって、「接続されている」とは

50

、直接接続されている状態に加えて、例えば配線、導電膜、抵抗、ダイオード、トランジスタ、スイッチング素子などの素子を介して間接的に接続している状態も、その範疇に含む。

**【0026】**

次に、配線11乃至配線17の信号又は電位等について説明する。

**【0027】**

配線11には電位VDDが供給される。配線12からは信号OUTAが出力される。配線13には電位VSSが供給される。配線14からは信号OUTBが出力される。配線15には信号CK1が入力される。配線16には信号CK2が入力される。配線17には信号SPが入力される。

10

**【0028】**

なお、電位VDD及び電位VSSは一定の電位である。また、電位VDDは電位VSSよりも高い電位である。

**【0029】**

なお、信号OUTA、信号OUTB、信号CK1、信号CK2及び信号SPはハイレベルとロウレベルとを有するデジタル信号である。

**【0030】**

なお、配線11乃至配線17の信号又は電位等は上述したものに限定されない。配線11には配線12の電位を上昇させるための信号又は電位等が供給されなければならない。配線13には配線12の電位を下降させるための信号若しくは電位等、及びノーブル又はトランジスタ101をオフにするための信号若しくは電位等が供給されなければならない。配線15には配線14の電位を上昇させるための信号若しくは電位等、トランジスタ102をオンにするための信号若しくは電位等、及びノーブル又はトランジスタ104をオンにするための信号若しくは電位等が入力されなければならない。配線16にはトランジスタ105のオン又はオフを制御するための信号が入力されなければならない。配線17にはトランジスタ103をオンにするための信号又は電位等が入力されなければならない。

20

**【0031】**

なお、本明細書等において、信号が入力された配線を信号線と呼んでもよい。また、電位が供給された配線を電源線と呼んでもよい。

**【0032】**

なお、本発明の一態様において、配線は信号又は電位等を伝達する機能を有する。例えば、配線15は信号CK1を伝達する機能を有する。

30

**【0033】**

次に、図1(A)の基本回路の動作について説明する。

**【0034】**

図1(B)は、図1(A)の基本回路の動作を説明するためのタイミングチャートである。図1(B)のタイミングチャートは、信号CK1、信号CK2、信号SP、ノードN1の電位VN1、ノードN2の電位VN2、信号OUTA及び信号OUTBを示す。

**【0035】**

なお、便宜上、信号SP、信号CK1及び信号CK2のハイレベルの電位を電位VDD、ロウレベルの電位を電位VSSとして説明する。

40

**【0036】**

なお、便宜上、ノードN1の電位VN1の初期値を電位VSS、ノードN2の電位VN2の初期値を電位VDDとトランジスタ101の閾値電圧との和を超えた電位として説明する。

**【0037】**

なお、便宜上、期間T1と期間T2とに分けて説明する。

**【0038】**

期間T1では、信号SPがハイレベルになり、信号CK1がロウレベルになり、信号CK2がハイレベルになる。

50

**【0039】**

トランジスタ105がオンになることで、配線17の信号S PがノードN 1に供給される。期間T 1では信号S Pがハイレベルであるため、ノードN 1の電位が上昇する。ノードN 1の電位がトランジスタ105のゲートの電位（例えば電位V D D）からトランジスタ105の閾値電圧を引いた電位まで上昇すると、トランジスタ105がオフになる。よって、ノードN 1が浮遊状態になる。

**【0040】**

トランジスタ103がオンになることで、信号C K 1が配線14に供給される。期間T 1では信号C K 1がロウレベルであるため、配線14の電位が電位V S Sになる。つまり、信号O U T Bがロウレベルになる。

10

**【0041】**

トランジスタ104がオフになることで、ノードN 2が浮遊状態になる。よって、ノードN 2の電位が電位V D Dとトランジスタ101の閾値電圧との和を超えた電位に維持される。

**【0042】**

トランジスタ101がオンになり、トランジスタ102がオフになることで、配線11の電位V D Dが配線12に供給される。よって、配線12の電位が電位V D Dになる。つまり、信号O U T Aがハイレベルになる。

**【0043】**

期間T 2では、信号S Pがロウレベルになり、信号C K 1がハイレベルになり、信号C K 2がロウレベルになる。

20

**【0044】**

トランジスタ105がオフになることで、ノードN 1が浮遊状態になる。

**【0045】**

トランジスタ103がオンになることで、配線15の信号C K 1が配線14に供給される。期間T 2では信号C K 1がハイレベルであるため、配線14の電位が上昇する。このとき、ノードN 1が浮遊状態であり、またトランジスタ103がノードN 1と配線14との間の電位差を保持している。よって、配線14の電位の上昇に伴って、ノードN 1の電位も上昇する。ノードN 1の電位がトランジスタ103の第1の端子の電位（例えば電位V D D）とトランジスタ103の閾値電圧との和を超えた電位となれば、配線14の電位が電位V D Dになる。つまり、信号O U T Bがハイレベルになる。

30

**【0046】**

トランジスタ104がオンになることで、配線13の電位V S SがノードN 2に供給される。よって、ノードN 2の電位が電位V S Sになる。

**【0047】**

トランジスタ101がオフになり、トランジスタ102がオンになることで、配線13の電位V S Sが配線12に供給される。よって、配線12の電位が電位V S Sになる。つまり、信号O U T Aがロウレベルになる。

**【0048】**

以上のとおり、信号O U T Aは期間T 1においてハイレベルになり、期間T 2においてロウレベルになる。また、信号O U T Bは、期間T 1においてロウレベルになり、期間T 2においてハイレベルになる。

40

**【0049】**

次に、図1(A)の基本回路を用いた順序回路について説明する。

**【0050】**

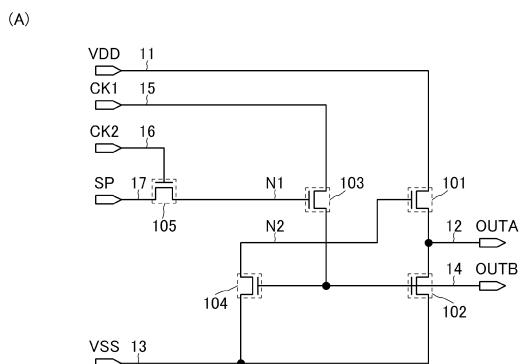

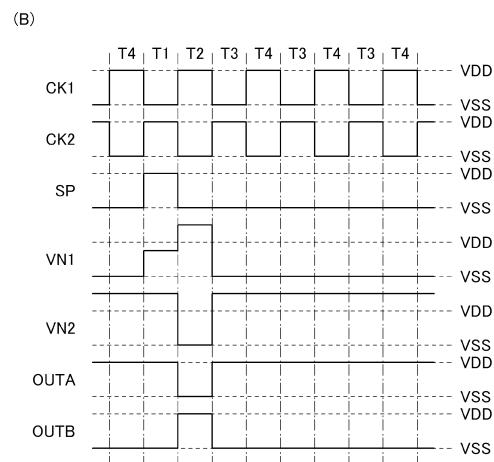

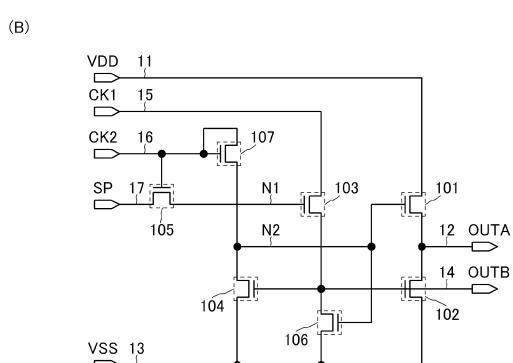

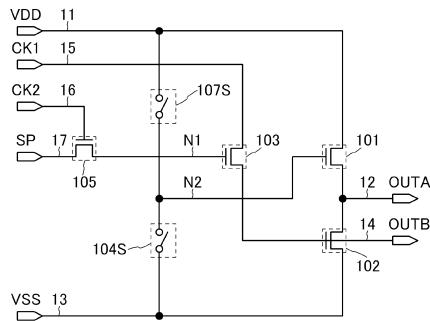

図2(A)は、本実施の形態の順序回路の回路図である。図2(A)の順序回路は、トランジスタ101乃至トランジスタ107を有する。

**【0051】**

なお、トランジスタ106及びトランジスタ107はトランジスタ101と同じ極性であることが好ましい。本実施の形態では、トランジスタ106及びトランジスタ107がN

50

チャネル型であるものとして説明する。

**【0052】**

なお、図2(A)の順序回路のトランジスタ106は設けなくてもよい。また、図2(A)の順序回路のトランジスタ107は設けなくてもよい。

**【0053】**

次に、図2(A)の順序回路の接続関係について説明する。

**【0054】**

トランジスタ101乃至トランジスタ105の接続関係は図1(A)の基本回路と同じであるため、その説明を省略する。トランジスタ106の第1の端子は配線13と接続され、トランジスタ106の第2の端子は配線14と接続され、トランジスタ106のゲートはノードN2と接続される。トランジスタ107の第1の端子は配線11と接続され、トランジスタ107の第2の端子はノードN2と接続され、トランジスタ107のゲートは配線16と接続される。

10

**【0055】**

次に、図2(A)の順序回路の動作について説明する。

**【0056】**

図2(B)は、図2(A)の順序回路の動作を説明するためのタイミングチャートである。図2(B)のタイミングチャートは、信号CK1、信号CK2、信号SP、ノードN1の電位VN1、ノードN2の電位VN2、信号OUTA及び信号OUTBを示す。

**【0057】**

なお、便宜上、信号SP、信号CK1及び信号CK2のハイレベルの電位を電位VDD、ロウレベルの電位を電位VSSとして説明する。

20

**【0058】**

なお、便宜上、ノードN1の電位VN1の初期値を電位VSS、ノードN2の電位VN2の初期値を電位VDDとトランジスタ101の閾値電圧との和を超えた電位として説明する。

**【0059】**

なお、便宜上、期間T1、期間T2、期間T3及び期間T4に分けて説明する。

**【0060】**

期間T1では、信号SPがハイレベルになり、信号CK1がロウレベルになり、信号CK2がハイレベルになる。

30

**【0061】**

トランジスタ105がオンになることで、配線17の信号SPがノードN1に供給される。期間T1では信号SPがハイレベルであるため、ノードN1の電位が上昇する。ノードN1の電位がトランジスタ105のゲートの電位(例えば電位VDD)からトランジスタ105の閾値電圧を引いた電位まで上昇すると、トランジスタ105がオフになる。よって、ノードN1が浮遊状態になる。

**【0062】**

トランジスタ103がオンになり、トランジスタ106がオンになることで、配線15の信号CK1及び配線13の電位VSSが配線14に供給される。期間T1では信号CK1がロウレベルであるため、配線14の電位が電位VSSになる。つまり、信号OUTBがロウレベルになる。

40

**【0063】**

トランジスタ107がオフになり、トランジスタ104がオフになることで、ノードN2が浮遊状態になる。よって、ノードN2の電位がトランジスタ101の第1の端子の電位(例えば電位VDD)とトランジスタ101の閾値電圧との和を超えた電位に維持される。

**【0064】**

なお、ノードN2の電位VN2の初期値が電位VSSであれば、トランジスタ107がオンになり、配線11の電位VDDがノードN2に供給される。

50

**【 0 0 6 5 】**

トランジスタ 101 がオンになり、トランジスタ 102 がオフになることで、配線 11 の電位 VDD が配線 12 に供給される。よって、配線 12 の電位が電位 VDD になる。つまり、信号 OUTA がハイレベルになる。

**【 0 0 6 6 】**

期間 T2 では、信号 SP がロウレベルになり、信号 CK1 がハイレベルになり、信号 CK2 がロウレベルになる。

**【 0 0 6 7 】**

トランジスタ 105 がオフになるため、ノード N1 が浮遊状態になる。

**【 0 0 6 8 】**

トランジスタ 103 がオンになり、トランジスタ 106 がオフになることで、配線 15 の信号 CK1 が配線 14 に供給される。期間 T2 では信号 CK1 がハイレベルであるため、配線 14 の電位が上昇する。このとき、ノード N1 が浮遊状態であり、またトランジスタ 103 のゲートとトランジスタ 103 の第 2 の端子との間にはノード N1 と配線 14 との電位差が保持されている。よって、配線 14 の電位の上昇に伴って、ノード N1 の電位も上昇する。ノード N1 の電位がトランジスタ 103 の第 1 の端子の電位（例えば電位 VDD）とトランジスタ 103 の閾値電圧との和を超えた電位まで上昇すれば、配線 14 の電位が電位 VDD になる。つまり、信号 OUTB がハイレベルになる。

10

**【 0 0 6 9 】**

トランジスタ 107 がオフになり、トランジスタ 104 がオンになることで、配線 13 の電位 VSS がノード N2 に供給される。よって、ノード N2 の電位が電位 VSS になる。

20

**【 0 0 7 0 】**

トランジスタ 101 がオフになり、トランジスタ 102 がオンになることで、配線 13 の電位 VSS が配線 12 に供給される。よって、配線 12 の電位が電位 VSS になる。つまり、信号 OUTA がロウレベルになる。

**【 0 0 7 1 】**

期間 T3 では、信号 SP がロウレベルになり、信号 CK1 がロウレベルになり、信号 CK2 がハイレベルになる。

**【 0 0 7 2 】**

トランジスタ 105 がオンになることで、配線 17 の信号 SP がノード N1 に供給される。期間 T3 では信号 SP がロウレベルであるため、ノード N1 の電位が電位 VSS になる。

30

**【 0 0 7 3 】**

トランジスタ 103 がオフになり、トランジスタ 106 がオンになることで、配線 13 の電位 VSS が配線 14 に供給される。よって、配線 14 の電位が電位 VSS になる。つまり、信号 OUTB がロウレベルになる。

**【 0 0 7 4 】**

トランジスタ 107 がオンになり、トランジスタ 104 がオフになることで、配線 11 の電位 VDD がノード N2 に供給される。よって、ノード N2 の電位が上昇する。ノード N2 の電位がトランジスタ 107 のゲートの電位（例えば電位 VDD）からトランジスタ 107 の閾値電圧を引いた電位まで上昇すると、トランジスタ 107 がオフになる。よって、ノード N2 が浮遊状態になる。

40

**【 0 0 7 5 】**

トランジスタ 101 がオンになり、トランジスタ 102 がオフになることで、配線 11 の電位 VDD が配線 12 に供給される。よって、配線 12 の電位が上昇する。このとき、ノード N2 が浮遊状態であり、トランジスタ 101 のゲートとトランジスタ 101 の第 2 の端子との間にはノード N2 と配線 12 との間の電位差が保持されている。よって、配線 12 の電位の上昇に伴って、ノード N2 の電位も上昇する。ノード N2 の電位がトランジスタ 101 の第 1 の端子の電位（例えば電位 VDD）とトランジスタ 101 の閾値電圧との和を超えた電位まで上昇すれば、配線 12 の電位が電位 VDD になる。つまり、信号 OU

50

T A がハイレベルになる。

**【0076】**

期間 T 4 では、信号 S P がロウレベルになり、信号 C K 1 がハイレベルになり、信号 C K 2 がロウレベルになる。

**【0077】**

トランジスタ 105 がオフになることで、ノード N 1 が浮遊状態になる。よって、ノード N 1 の電位が期間 T 3 における電位に維持される。

**【0078】**

トランジスタ 103 がオフになり、トランジスタ 106 がオンになることで、配線 13 の電位 V SS が配線 14 に供給される。よって、配線 14 の電位が電位 V SS になる。つまり、信号 OUT B がロウレベルになる。10

**【0079】**

トランジスタ 107 がオフになり、トランジスタ 104 がオフになることで、ノード N 2 が浮遊状態になる。よって、ノード N 2 の電位が期間 T 3 における電位に維持される。

**【0080】**

トランジスタ 101 がオンになり、トランジスタ 102 がオフになることで、配線 11 の電位 V DD が配線 12 に供給される。よって、配線 12 の電位が電位 V DD になる。つまり、信号 OUT A がハイレベルになる。

**【0081】**

以上のとおり、信号 OUT A は、期間 T 2 においてロウレベルになり、期間 T 1 、期間 T 3 及び期間 T 4 においてハイレベルになる。また、信号 OUT B は、期間 T 2 においてハイレベルになり、期間 T 1 、期間 T 3 及び期間 T 4 においてロウレベルになる。20

**【0082】**

次に、図 2 (A) の順序回路を用いたシフトレジスタ回路について説明する。

**【0083】**

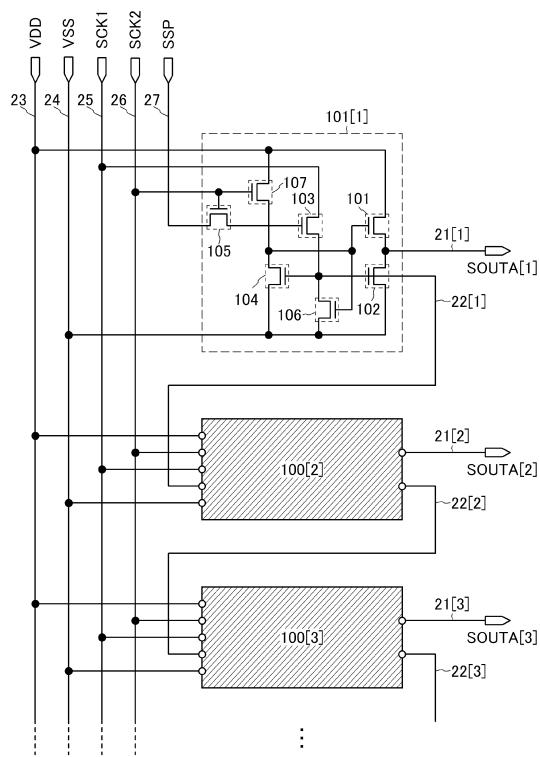

図 3 は、本実施の形態のシフトレジスタ回路の回路図である。図 3 のシフトレジスタ回路は、N (N は自然数) 個 (N 段ともいう) の順序回路 100 を有する。ただし、図 3 には、1 段目乃至 3 段目の順序回路 (順序回路 100 [1] 、順序回路 100 [2] 、順序回路 100 [3] と示す) のみを示す。

**【0084】**

なお、N 個の順序回路 100 としては、各々、図 2 (A) の順序回路を用いている。30

**【0085】**

次に、図 3 のシフトレジスタ回路の接続関係について説明する。

**【0086】**

図 3 のシフトレジスタ回路は、N 本の配線 21 、N 本の配線 22 、配線 23 、配線 24 、配線 25 、配線 26 及び配線 27 と接続される。

**【0087】**

具体的には、i (i は 2 乃至 N のいずれか一) 段目の順序回路 100 (順序回路 100 [i] と示す) において、トランジスタ 101 の第 2 の端子が配線 21 [i] と接続される。トランジスタ 102 のゲートが配線 22 [i] と接続される。トランジスタ 105 の第 1 の端子が配線 22 [i - 1] と接続される。トランジスタ 101 の第 1 の端子が配線 23 と接続される。トランジスタ 102 の第 1 の端子が配線 24 と接続される。トランジスタ 103 の第 1 の端子が配線 25 と配線 26 の一方と接続される。トランジスタ 107 のゲートが配線 25 と配線 26 の他方と接続される。40

**【0088】**

すなわち、順序回路 100 [i] においては、配線 21 [i] が配線 12 に対応する。配線 22 [i] が配線 14 に対応する。配線 23 が配線 11 に対応する。配線 24 が配線 13 に対応する。配線 25 及び配線 26 の一方が配線 15 に対応する。配線 25 及び配線 26 の他方が配線 16 に対応する。配線 22 [i - 1] が配線 17 に対応する。

**【0089】**

なお、順序回路 100 [ i - 1 ] 又は順序回路 100 [ i + 1 ] においては、トランジスタ 103 の第 1 の端子が配線 25 と配線 26 との他方と接続される。トランジスタ 107 のゲートが配線 25 と配線 26 との一方と接続される。つまり、トランジスタ 103 の第 1 の端子及びトランジスタ 107 のゲートの接続先は、奇数段目と偶数段目とにおいて入れ替わる。

#### 【0090】

なお、順序回路 100 [ 1 ] においては、トランジスタ 105 の第 1 の端子が配線 27 と接続されるところが、 i 段目の順序回路 100 と異なる。

#### 【0091】

次に、配線 21 乃至配線 27 の信号又は電位等について説明する。

10

#### 【0092】

配線 21 からは信号 SOUTA が出力される。配線 22 からは信号 SOUTB が出力される。配線 23 には電位 VDD が供給される。配線 24 には電位 VSS が供給される。配線 25 には信号 SCK1 が入力される。配線 26 には信号 SCK2 が入力される。配線 27 には信号 SSP が入力される。

#### 【0093】

なお、信号 SOUTA は信号 OUTA に対応する。信号 SOUTB は信号 OUTB に対応する。信号 SCK1 は信号 CK1 又は信号 CK2 に対応する。信号 SCK2 は信号 CK1 又は信号 CK2 に対応する。信号 SSP は信号 SP に対応する。

#### 【0094】

次に、図 3 のシフトレジスタ回路の動作について説明する。

20

#### 【0095】

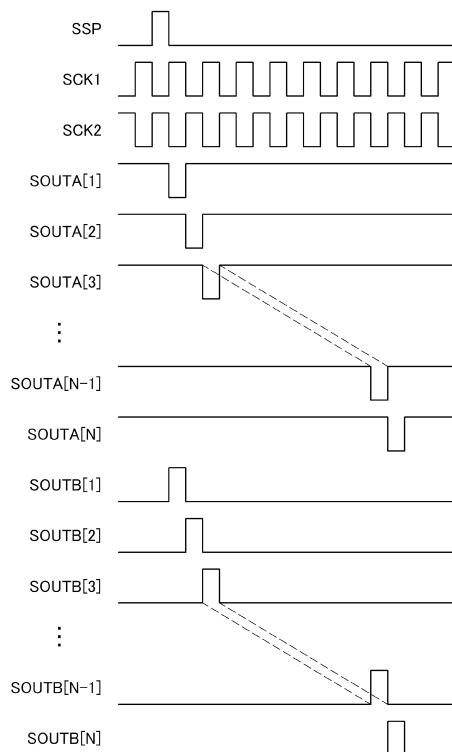

図 4 は、図 3 のシフトレジスタ回路の動作を説明するためのタイミングチャートである。図 4 のタイミングチャートは、信号 SSP 、信号 SCK1 、信号 SCK2 、信号 SOUTA [ 1 ] 乃至信号 SOUTA [ 3 ] 、信号 SOUTA [ N - 1 ] 、信号 SOUTA [ N ] 、信号 SOUTB [ 1 ] 乃至信号 SOUTB [ 3 ] 、信号 SOUTB [ N - 1 ] 、信号 SOUTB [ N ] を示す。

#### 【0096】

信号 SOUTB [ i - 1 ] がハイレベルになると、順序回路 100 [ i ] が期間 T1 における動作を行う。よって、信号 SOUTA [ i ] がハイレベルになり、信号 SOUTB [ i ] がロウレベルになる。

30

#### 【0097】

その後、信号 SCK1 及び信号 SCK2 が反転すると、順序回路 100 [ i ] が期間 T2 における動作を行う。よって、信号 SOUTA [ i ] がロウレベルになり、信号 SOUTB [ i ] がハイレベルになる。

#### 【0098】

その後、再び信号 SOUTB [ i - 1 ] がハイレベルになるまで、信号 SCK1 及び信号 SCK2 が反転する毎に、順序回路 100 [ i ] が期間 T3 における動作と期間 T4 における動作とを繰り返す。よって、信号 SOUTA [ i ] がハイレベルになり、信号 SOUTB [ i ] がロウレベルになる。

40

#### 【0099】

なお、順序回路 100 [ 1 ] は、信号 SSP がハイレベルになると期間 T1 における動作を行うところが、順序回路 100 [ i ] と異なる。

#### 【0100】

以上のとおり、信号 SOUTA [ 1 ] 乃至信号 SOUTA [ N ] は、信号 SSP がハイレベルになった後に、順次ロウレベルになる。また、信号 SOUTB [ 1 ] 乃至信号 SOUTB [ N ] は、信号 SSP がハイレベルになった後に、順次ハイレベルになる。

#### 【0101】

次に、トランジスタ 101 乃至トランジスタ 107 の機能について説明する。

#### 【0102】

50

トランジスタ101乃至トランジスタ107のそれぞれは第1の端子の接続先と第2の端子の接続先との導通又は非導通を制御する機能を有する。また、第1の端子の接続先の信号又は電位等を第2の端子の接続先に供給する機能を有する。例えば、トランジスタ102は配線13と配線12との導通又は非導通を制御する機能を有する。また、電位VSSを配線12に供給する機能を有する。

#### 【0103】

また、トランジスタ101及びトランジスタ103はゲートの接続先と第2の端子の接続先との間の電位差を保持する機能を有する。例えば、トランジスタ101はノードN2と配線12との間の電位差を保持する機能を有する。

#### 【0104】

また、トランジスタ105及びトランジスタ107は第1の端子の接続先と第2の端子との接続先を導通にした後に、第1の端子の接続先と第2の端子の接続先とを非導通にする機能を有する。また、第1の端子の接続先の信号又は電位等を第2の端子の接続先に供給した後に、第1の端子の接続先の信号又は電位等の供給を止める機能を有する。例えば、トランジスタ105は配線17とノードN1とを導通にした後に、配線17とノードN1とを非導通にする機能を有する。また、信号SPをノードN1に供給した後に、信号SPの供給を止める機能を有する。

#### 【0105】

また、トランジスタ101は配線12に電位を上昇させるための信号又は電位等を供給する機能を有する。トランジスタ102は配線12に電位を下降させるための信号又は電位等を供給する機能を有する。トランジスタ103は配線14に電位を上昇させるための信号又は電位等を供給する機能を有する。トランジスタ104はノードN2にトランジスタ101をオフにするための信号又は電位等を供給する機能を有する。トランジスタ105はノードN1にトランジスタ103をオンにするための信号又は電位等を供給する機能を有する。トランジスタ106は配線14に電位を下降させるための信号又は電位等を供給する機能を有する。トランジスタ107はノードN2にトランジスタ101をオンにするための信号又は電位等を供給する機能を有する。

#### 【0106】

なお、本発明の一態様において、トランジスタを、第1の端子と第2の端子との間の導通又は非導通を制御する機能を有するスイッチに置き換えてよい。トランジスタの第1の端子がスイッチの第1の端子、トランジスタの第2の端子がスイッチの第2の端子に対応する。また、必要に応じて、トランジスタのゲートがスイッチの制御端子に対応する。

#### 【0107】

次に、トランジスタ101乃至トランジスタ107のW/L (W:チャネル幅、L:チャネル長)について説明する。

#### 【0108】

トランジスタ101のW/Lは、トランジスタ102乃至トランジスタ107のW/Lよりも大きいことが好ましい。また、トランジスタ102のW/Lはトランジスタ104のW/Lよりも大きいことが好ましい。また、トランジスタ103のW/Lはトランジスタ105のW/Lよりも大きいことが好ましい。また、トランジスタ104のW/Lはトランジスタ106のW/Lよりも大きいことが好ましい。

#### 【0109】

ところで、トランジスタ101乃至トランジスタ107としてPチャネル型のトランジスタを用いる場合には、配線11には電位VSSを供給し、配線13には電位VDDを供給することが好ましい。また、信号CK1、信号CK2及び信号SPを反転することが好ましい。すると、信号OUTA及び信号OUTBも反転する。また、トランジスタ101乃至トランジスタ107としてPチャネル型のトランジスタを用いる場合には、上述した説明において、「上昇」を「下降」に置き換え、「下降」を「上昇」に置き換えればよい。

#### 【0110】

次に、本実施の形態の基本回路、順序回路、及びシフトレジスタ回路が奏する効果につい

10

20

30

40

50

て説明する。

**【0111】**

Nチャネル型のトランジスタで構成された回路において、ロウレベルの信号をシフトさせることができる。また、Pチャネル型のトランジスタで構成された回路において、ハイレベルの信号をシフトさせることができる。

**【0112】**

また、少ないトランジスタ数で信号OUTA及び信号SOUTAのような信号を生成することができる。

**【0113】**

また、トランジスタ107及びトランジスタ104の双方がオンになる期間をなくすことができるため、配線11と配線13との間に生じる電流を小さくすることができる。よって、消費電力の削減を図ることができる。10

**【0114】**

また、トランジスタ101及びトランジスタ102の双方がオンになる期間をなくすことができるため、配線11と配線13との間に生じる電流を小さくすることができる。よって、消費電力の削減を図ることができる。

**【0115】**

また、信号CK1がハイレベルである期間において、トランジスタ103及びトランジスタ106の双方がオンになる期間をなくすことができるため、配線15と配線13との間に生じる電流を小さくすることができる。よって、消費電力の削減を図ることができる。20

**【0116】**

また、期間T3において、トランジスタ105がオンになることで、ロウレベルである信号SPをノードN1に供給することができる。よって、ノードN1の電位を電位VSSに維持しやすくすることができ、誤動作を防止することができる。

**【0117】**

また、期間T3において、トランジスタ107がオンになることで、電位VDDをノードN2に供給することができる。よって、ノードN2の電位を高い電位に維持しやすくすることができ、誤動作を防止することができる。

**【0118】**

また、期間T3及び期間T4において、トランジスタ106がオンになることで、配線13の電位VSSを配線14に供給することができる。よって、配線14の電位を電位VSSに維持しやすくすることができ、誤動作を防止することができる。30

**【0119】**

本実施の形態は、他の実施の形態等と適宜組み合わせて実施することが可能である。

**【0120】**

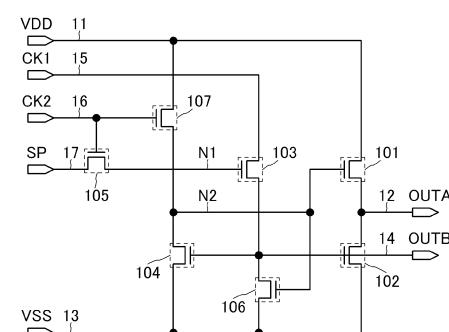

(実施の形態2)

本実施の形態では、実施の形態1とは異なる、基本回路、順序回路及びシフトレジスタ回路について説明する。ただし、実施の形態1と共に通するところは共通の符号を示し、その説明を省略する。

**【0121】**

なお、本実施の形態では、図2(A)の順序回路に変更を加えた図面を用いて本実施の形態の基本回路、順序回路及びシフトレジスタ回路について説明することができる。ただし、本実施の形態で述べる構成は、図2(A)の順序回路だけでなく、実施の形態1で述べた他の、基本回路、順序回路及びシフトレジスタ回路にも適用することができる。40

**【0122】**

なお、本実施の形態の基本回路、順序回路及びシフトレジスタ回路は、実施の形態1で述べた効果と同様の効果を奏する。

**【0123】**

まず、トランジスタ105の実施の形態1とは異なる接続関係について説明する。

**【0124】**

トランジスタ105の第1の端子を配線11、配線12、配線16、配線17又はノードN2と接続し、トランジスタ105の第2の端子をノードN1と接続し、トランジスタ105のゲートを配線17と接続してもよい。

**【0125】**

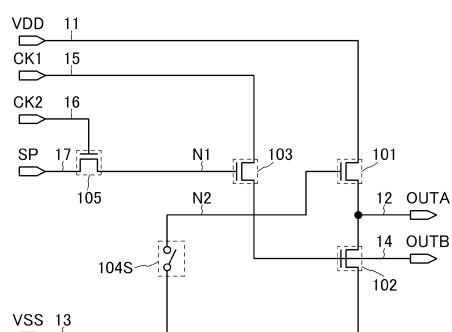

図5(A)は、トランジスタ105の第1の端子を配線17と接続し、トランジスタ105の第2の端子をノードN1と接続し、トランジスタ105のゲートを配線17と接続した順序回路の回路図である。

**【0126】**

次に、トランジスタ107の実施の形態1とは異なる接続関係について説明する。

**【0127】**

トランジスタ107の第1の端子を配線16と接続し、トランジスタ107の第2の端子をノードN2と接続し、トランジスタ107のゲートを配線16と接続してもよい。また、トランジスタ107の第1の端子を配線11と接続し、トランジスタ107の第2の端子をノードN2と接続し、トランジスタ107のゲートを配線11と接続してもよい。

**【0128】**

図5(B)は、トランジスタ107の第1の端子を配線16と接続し、トランジスタ107の第2の端子をノードN2と接続し、トランジスタ107のゲートを配線16と接続した順序回路の回路図である。

**【0129】**

次に、トランジスタ104の実施の形態1とは異なる接続関係について説明する。

10

**【0130】**

トランジスタ104の第1の端子を配線13と接続し、トランジスタ104の第2の端子をノードN2と接続し、トランジスタ104のゲートをノードN1又は配線17と接続してもよい。

**【0131】**

図6(A)は、トランジスタ104の第1の端子を配線13と接続し、トランジスタ104の第2の端子をノードN2と接続し、トランジスタ104のゲートをノードN1と接続した順序回路の回路図である。

**【0132】**

次に、トランジスタ102の実施の形態1とは異なる接続関係について説明する。

20

**【0133】**

トランジスタ102の第1の端子を配線13と接続し、トランジスタ102の第2の端子を配線12と接続し、トランジスタ102のゲートをノードN1又は配線17と接続してもよい。

**【0134】**

図6(B)は、トランジスタ102の第1の端子を配線13と接続し、トランジスタ102の第2の端子を配線12と接続し、トランジスタ102のゲートをノードN1と接続した順序回路の回路図である。

**【0135】**

次に、トランジスタ106の実施の形態1とは異なる接続関係について説明する。

30

**【0136】**

トランジスタ106の第1の端子を配線13と接続し、トランジスタ106の第2の端子を配線14と接続し、トランジスタ106のゲートを配線16と接続してもよい。こうすれば、トランジスタ106がオンになる時間を短くするとともに、期間T3において配線13の電位VSSを配線14に供給することができるため、配線14の電位を安定して維持することができる。

**【0137】**

図7(A)は、トランジスタ106の第1の端子を配線13と接続し、トランジスタ106の第2の端子を配線14と接続し、トランジスタ106のゲートを配線16と接続した順序回路の回路図である。

40

50

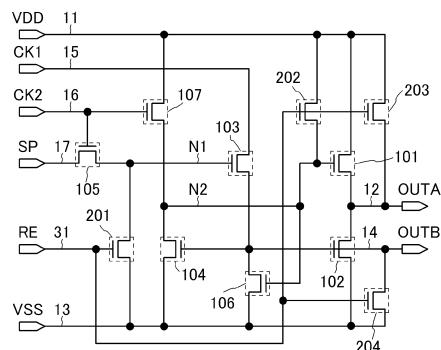

**【 0 1 3 8 】**

次に、トランジスタ201、トランジスタ202、トランジスタ203及びトランジスタ204を設けた構成について説明する。

**【 0 1 3 9 】**

図7(B)は、トランジスタ201、トランジスタ202、トランジスタ203及びトランジスタ204を設けた順序回路の回路図である。トランジスタ201の第1の端子は配線13と接続され、トランジスタ201の第2の端子はノードN1と接続され、トランジスタ201のゲートは配線31と接続される。トランジスタ202の第1の端子は配線11と接続され、トランジスタ202の第2の端子はノードN2と接続され、トランジスタ202のゲートは配線31と接続される。トランジスタ203の第1の端子は配線11と接続され、トランジスタ203の第2の端子は配線12と接続され、トランジスタ203のゲートは配線31と接続される。トランジスタ204の第1の端子は配線13と接続され、トランジスタ204の第2の端子は配線14と接続され、トランジスタ204のゲートは配線31と接続される。10

**【 0 1 4 0 】**

配線31には信号REが入力される。信号REはハイレベルとロウレベルとを有するデジタル信号である。ただし、配線31にはトランジスタ201乃至トランジスタ204の導通又は非導通を制御するための信号が入力されればよい。

**【 0 1 4 1 】**

なお、順序回路100[i]において、配線31は配線22[i+1]に対応する。ただし、配線31が配線22[i+2]又は配線22[i+3]のように配線22[i+n](nは自然数)と対応してもよい。20

**【 0 1 4 2 】**

信号REがハイレベルになると、トランジスタ201乃至トランジスタ204がオンになる。トランジスタ201及びトランジスタ204がオンになることで、配線13の電位VSSがノードN1及び配線14に供給される。よって、ノードN1及び配線14の電位が電位VSSになる。また、トランジスタ202及びトランジスタ203がオンになることで、配線11の電位VDDがノードN2及び配線12に供給される。よって、ノードN2及び配線12の電位が電位VDD又は電位VSSより高い電位になる。30

**【 0 1 4 3 】**

一方、信号REがロウレベルになると、トランジスタ201乃至トランジスタ204がオフになる。

**【 0 1 4 4 】**

信号REのタイミングの一例について説明する。配線31が配線22[i+1]に対応している場合には、信号REは信号OUTB[i+1]に対応する。よって、信号REは期間T2の後(例えば期間T2の直後の期間T3)においてハイレベルになり、それ以外の期間ではロウレベルになる。よって、期間T2の後に、順序回路を初期化することができる。

**【 0 1 4 5 】**

なお、トランジスタ201乃至トランジスタ204から選択された1つ、2つ又は3つのトランジスタのみを設けてもよい。40

**【 0 1 4 6 】**

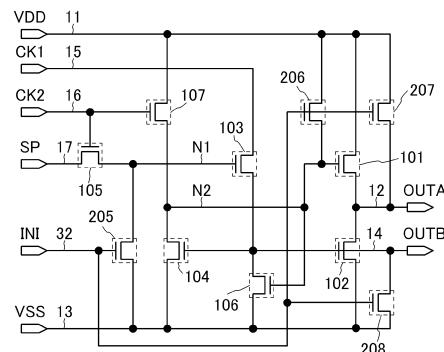

次に、トランジスタ205、トランジスタ206、トランジスタ207及びトランジスタ208を設けた構成について説明する。

**【 0 1 4 7 】**

図8(A)は、トランジスタ205、トランジスタ206、トランジスタ207及びトランジスタ208を設けた順序回路の回路図である。トランジスタ205乃至トランジスタ208の接続関係は、ゲートが配線32と接続されているところが、トランジスタ201乃至トランジスタ204と異なる。

**【 0 1 4 8 】**

なお、N個の順序回路100の全て又は少なくとも2つにおいて、トランジスタ205乃至トランジスタ208のゲートの接続先は共通である。

【0149】

配線32には信号INIが入力される。信号INIはハイレベルとロウレベルとを有するデジタル信号である。ただし、配線32にはトランジスタ205乃至トランジスタ208の導通又は非導通を制御するための信号が入力されなければならない。

【0150】

信号INIがハイレベルになると、トランジスタ205乃至トランジスタ208がオンになる。トランジスタ205及びトランジスタ208がオンになるとにより、配線13の電位VSSがノードN1及び配線14に供給される。よって、ノードN1及び配線14の電位が電位VSSになる。また、トランジスタ206及びトランジスタ207がオンになるとにより、配線11の電位VDDがノードN2及び配線12に供給される。よって、ノードN2及び配線12の電位が電位VDD又は電位VSSよりも高い電位になる。10

【0151】

一方、信号INIがロウレベルになると、トランジスタ205乃至トランジスタ208がオフになる。

【0152】

信号INIのタイミングの一例について説明する。信号SSPがハイレベルになる期間よりも前に、信号INIがハイレベルになる。よって、1段目の順序回路100が期間T1における動作を行う前に、各順序回路100を初期化することができる。よって、誤動作の防止を図ることができる。20

【0153】

なお、信号OUTB[N]がハイレベルになった後であり、且つ信号SSPがハイレベルになる前において、信号INIがハイレベルになることが好ましい。また、電源投入後であり、且つ信号SSPがハイレベルになる前において、信号INIがハイレベルになってもよい。

【0154】

なお、トランジスタ207の第1の端子を配線13と接続してもよい。

【0155】

なお、トランジスタ205乃至トランジスタ208のゲートを配線27と接続してもよい。つまり、信号INIとして信号SSPを用いてもよい。30

【0156】

なお、トランジスタ205乃至トランジスタ208から選択された1つ、2つ又は3つのトランジスタのみを設けてもよい。

【0157】

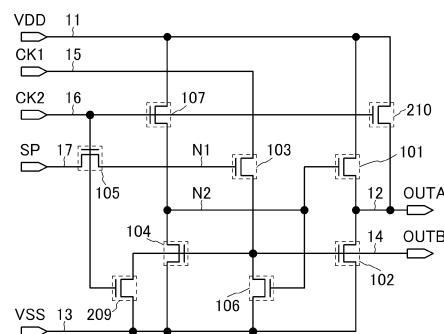

次に、トランジスタ209及びトランジスタ210を設けた構成について説明する。

【0158】

図8(B)は、トランジスタ209及びトランジスタ210を設けた順序回路の回路図である。トランジスタ209の第1の端子は配線13と接続され、トランジスタ209の第2の端子は配線14と接続され、トランジスタ209のゲートは配線16と接続される。トランジスタ210の第1の端子は配線11と接続され、トランジスタ210の第2の端子は配線12と接続され、トランジスタ210のゲートは配線16と接続される。40

【0159】

信号CK2がハイレベルになると、トランジスタ209及びトランジスタ210がオンになる。トランジスタ209がオンになると、配線13の電位VSSが配線14に供給される。トランジスタ210がオンになると、配線11の電位VDDが配線12に供給される。

【0160】

一方、信号CK2がロウレベルになると、トランジスタ209及びトランジスタ210がオフになる。50

**【 0 1 6 1 】**

信号 C K 2 は、期間 T 1 及び期間 T 3 においてハイレベルになり、期間 T 2 及び期間 T 4 においてロウレベルになる。よって、期間 T 1 及び期間 T 3 において、配線 1 3 の電位 V S S が配線 1 4 に供給され、配線 1 1 の電位 V D D が配線 1 2 に供給される。特に、期間 T 3 において信号 C K 2 がハイレベルになることにより、配線 1 3 の電位 V S S が配線 1 4 に定期的に供給され、配線 1 1 の電位 V D D が配線 1 2 に定期的に供給される。よって、配線 1 4 及び配線 1 2 の電位を維持しやすくなる。

**【 0 1 6 2 】**

なお、トランジスタ 2 0 9 及びトランジスタ 2 1 0 の一方のみを設けてもよい。

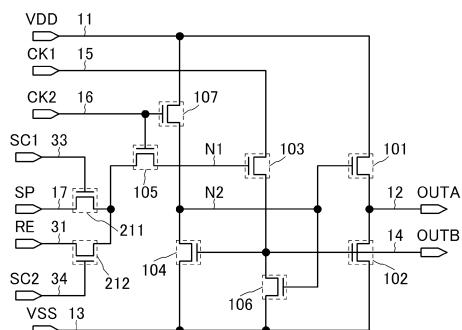

**【 0 1 6 3 】**

次に、トランジスタ 2 1 1 及びトランジスタ 2 1 2 を設けた構成について説明する。

**【 0 1 6 4 】**

図 9 ( A ) は、トランジスタ 2 1 1 及びトランジスタ 2 1 2 を設けた順序回路の回路図である。トランジスタ 2 1 1 の第 1 の端子は配線 1 7 と接続され、トランジスタ 2 1 1 の第 2 の端子はトランジスタ 1 0 5 の第 1 の端子と接続され、トランジスタ 2 1 1 のゲートは配線 3 3 と接続される。トランジスタ 2 1 2 の第 1 の端子は配線 3 1 と接続され、トランジスタ 2 1 2 の第 2 の端子はトランジスタ 1 0 5 の第 1 の端子と接続され、トランジスタ 2 1 2 のゲートは配線 3 4 と接続される。

**【 0 1 6 5 】**

なお、N 個の順序回路 1 0 0 の全て又は少なくとも 2 つにおいて、トランジスタ 2 1 1 のゲートの接続先は共通であり、またトランジスタ 2 1 2 のゲートの接続先は共通である。

**【 0 1 6 6 】**

配線 3 3 には信号 S C 1 が入力される。信号 S C 1 はハイレベルとロウレベルとを有するデジタル信号である。ただし、配線 3 3 にはトランジスタ 2 1 1 の導通又は非導通を制御するための信号又は電位等が入力されていればよい。また、配線 3 4 には信号 S C 2 が入力される。信号 S C 2 はハイレベルとロウレベルとを有するデジタル信号である。ただし、配線 3 4 にはトランジスタ 2 1 2 の導通又は非導通を制御するための信号又は電位等が入力されていればよい。

**【 0 1 6 7 】**

信号 S C 1 がハイレベルになり、信号 S C 2 がロウレベルになると、トランジスタ 2 1 1 がオンになり、トランジスタ 2 1 2 がオフになる。トランジスタ 2 1 1 がオンになると、配線 1 7 の信号 S P がトランジスタ 1 0 5 の第 1 の端子に供給される。

**【 0 1 6 8 】**

一方、信号 S C 1 がロウレベルになり、信号 S C 2 がハイレベルになると、トランジスタ 2 1 1 がオフになり、トランジスタ 2 1 2 がオンになる。トランジスタ 2 1 2 がオンになると、配線 3 1 の信号 R E がトランジスタ 1 0 5 の第 1 の端子に供給される。

**【 0 1 6 9 】**

信号 S C 1 及び信号 S C 2 のタイミングの一例について説明する。シフトレジスタ回路のシフト方向を順序回路 1 0 0 [ 1 ] から順序回路 1 0 0 [ N ] の方向とする場合には、信号 S C 1 がハイレベルになり、信号 S C 2 がロウレベルになる。また、シフトレジスタ回路のシフト方向を順序回路 1 0 0 [ N ] から順序回路 1 0 0 [ 1 ] の方向とする場合には、信号 S C 1 がロウレベルになり、信号 S C 2 がハイレベルになる。

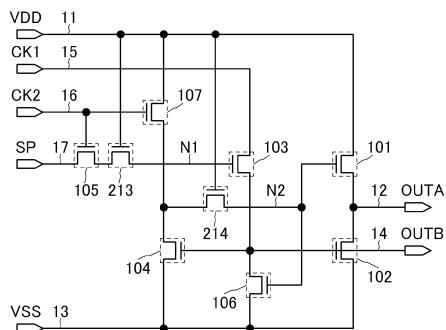

**【 0 1 7 0 】**

次に、トランジスタ 2 1 3 及びトランジスタ 2 1 4 を設けた構成について説明する。

**【 0 1 7 1 】**

図 9 ( B ) は、トランジスタ 2 1 3 及びトランジスタ 2 1 4 を設けた順序回路の回路図である。トランジスタ 2 1 3 の第 1 の端子はトランジスタ 1 0 5 の第 2 の端子と接続され、トランジスタ 2 1 3 の第 2 の端子はトランジスタ 1 0 3 のゲートと接続され、トランジスタ 2 1 3 のゲートは配線 1 1 と接続される。トランジスタ 2 1 4 の第 1 の端子はトランジスタ 1 0 7 の第 2 の端子と接続され、トランジスタ 2 1 4 の第 2 の端子はトランジスタ 1

10

20

30

40

50

01のゲートと接続され、トランジスタ214のゲートは配線11と接続される。

**【0172】**

トランジスタ213を有することにより、トランジスタ103のゲートの電位が上昇しすぎることを防止することができる。よって、トランジスタ103の劣化の抑制又は絶縁破壊の防止等を図ることができる。

**【0173】**

また、トランジスタ214を有することにより、トランジスタ101のゲートの電位が上昇しすぎることを防止することができる。よって、トランジスタ101の劣化の抑制又は絶縁破壊の防止等を図ることができます。また、トランジスタ106のV<sub>gs</sub>を小さくすることができるため、トランジスタ106の劣化の抑制を図ることができます。 10

**【0174】**

なお、トランジスタ213のゲートを配線12、配線16、配線17、トランジスタ101のゲート等と接続してもよい。また、トランジスタ213の第1の端子を配線17と接続し、トランジスタ213の第2の端子をトランジスタ105の第1の端子と接続してもよい。

**【0175】**

なお、トランジスタ214のゲートを配線12、配線16等と接続してもよい。また、トランジスタ214の第1の端子を配線11と接続し、トランジスタ214の第2の端子をトランジスタ107の第1の端子と接続してもよい。

**【0176】**

なお、トランジスタ106のゲートをトランジスタ104の第2の端子と接続してもよい。

**【0177】**

なお、トランジスタ213及びトランジスタ214の一方のみを設けてもよい。

**【0178】**

次に、トランジスタの一部をスイッチに置き換えた構成について説明する。

**【0179】**

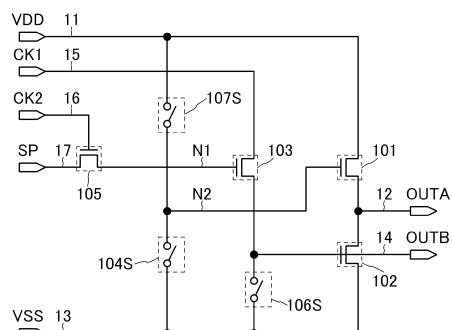

図10(A)は、トランジスタ104、トランジスタ106及びトランジスタ107としてスイッチを用いた順序回路の回路図である。スイッチ104S、スイッチ106S及びスイッチ107Sは、各々、トランジスタ104、トランジスタ106及びトランジスタ107に対応する。また、スイッチ104Sの第1の端子は配線13と接続され、スイッチ104Sの第2の端子はトランジスタ101のゲートと接続される。スイッチ106Sの第1の端子は配線13と接続され、スイッチ106Sの第2の端子は配線14と接続される。スイッチ107Sの第1の端子は配線11と接続され、スイッチ107Sの第2の端子はトランジスタ101のゲートと接続される。 30

**【0180】**

期間T1において、スイッチ104Sがオフになり、スイッチ106Sがオンになり、スイッチ107Sがオンになる。また、期間T2において、スイッチ104Sがオンになり、スイッチ106Sがオフになり、スイッチ107Sがオフになる。また、期間T3において、スイッチ104Sがオフになり、スイッチ106Sがオンになり、スイッチ107Sがオンになる。また、期間T4において、スイッチ104Sがオフになり、スイッチ106Sがオンになり、スイッチ107Sがオフになる。 40

**【0181】**

なお、スイッチ104Sは期間T1においてオンになってもよい。また、スイッチ106Sは期間T3及び期間T4の一方においてオフになってもよい。また、スイッチ107Sは期間T4においてオンになってもよい。

**【0182】**

なお、図10(B)は、トランジスタ104としてスイッチ104Sを用いた基本回路の回路図である。また、図11(A)は、図10(B)の基本回路にスイッチ106Sを設けた基本回路の回路図である。また、図11(B)は、図10(B)の基本回路にスイッ 50

チ 1 0 7 S を設けた基本回路の回路図である。

【 0 1 8 3 】

次に、トランジスタ 2 0 1 乃至トランジスタ 2 1 4 の機能について説明する。

【 0 1 8 4 】

トランジスタ 2 0 1 乃至トランジスタ 2 1 4 のそれぞれは、第 1 の端子の接続先と第 2 の端子の接続先との導通又は非導通を制御する機能を有する。また、第 1 の端子の接続先の信号又は電位等を第 2 の端子の接続先に供給する機能を有する。例えば、トランジスタ 2 0 1 は配線 1 3 とノード N 1 との導通又は非導通を制御する機能を有する。また、電位 V SS をノード N 1 に供給する機能を有する。

【 0 1 8 5 】

10

また、トランジスタ 2 1 3 及びトランジスタ 2 1 4 は第 1 の端子の接続先と第 2 の端子との接続先を導通にした後に、第 1 の端子の接続先と第 2 の端子の接続先とを非導通にする機能を有する。また、第 1 の端子の接続先の信号又は電位等を第 2 の端子の接続先に供給した後に、第 1 の端子の接続先の信号又は電位等の供給を止める機能を有する。例えば、トランジスタ 2 1 3 はトランジスタ 1 0 5 の第 2 の端子とトランジスタ 1 0 3 のゲートとを導通にした後に、トランジスタ 1 0 5 の第 2 の端子とトランジスタ 1 0 3 のゲートとを非導通にする機能を有する。また、トランジスタ 1 0 5 の第 2 の端子の電位をノード N 1 に供給した後に、トランジスタ 1 0 5 の第 2 の端子の電位の供給を止める機能を有する。

【 0 1 8 6 】

ところで、トランジスタ 2 0 1 乃至トランジスタ 2 1 4 は、トランジスタ 1 0 1 と同じ極性であることが好ましい。

20

【 0 1 8 7 】

また、トランジスタ 1 0 1 の W / L はトランジスタ 2 0 1 乃至トランジスタ 2 1 4 の W / L よりも大きいことが好ましい。

【 0 1 8 8 】

本実施の形態は、他の実施の形態等と適宜組み合わせて実施することが可能である。

【 0 1 8 9 】

( 実施の形態 3 )

本実施の形態では、本発明の一態様に係る表示装置について説明する。

【 0 1 9 0 】

30

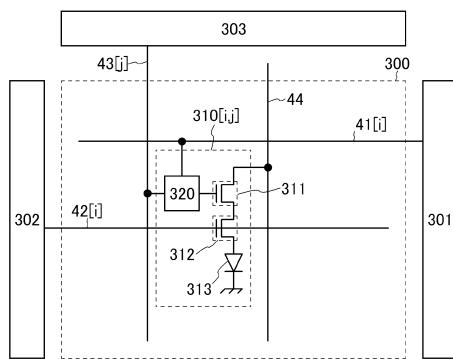

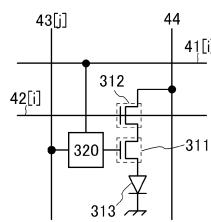

図 1 2 ( A ) は、本実施の形態の表示装置の回路図である。図 1 2 ( A ) の表示装置は、画素部 3 0 0 と、ゲートドライバ 3 0 1 と、ゲートドライバ 3 0 2 と、ソースドライバ 3 0 3 と、を有する。画素部 3 0 0 は、複数の画素 3 1 0 を有する。複数の画素 3 1 0 のそれぞれは、トランジスタ 3 1 1 と、トランジスタ 3 1 2 と、表示素子 3 1 3 と、回路 3 2 0 と、を有する。なお、ゲートドライバ 3 0 2 として、実施の形態 1 及び実施の形態 2 のシフトレジスタ回路を用いることができる。

【 0 1 9 1 】

なお、本発明の一態様において、表示素子としては、液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 E L ( E l e c t r o L u m i n e s c e n c e ) 素子、有機 E L 素子等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

40

【 0 1 9 2 】

次に、図 1 2 ( A ) の表示装置の接続関係について説明する。

【 0 1 9 3 】

ゲートドライバ 3 0 1 は N 本の配線 4 1 と接続される。ゲートドライバ 3 0 2 は N 本の配線 4 2 と接続される。ソースドライバ 3 0 3 は M ( M は自然数 ) 本の配線 4 3 と接続される。なお、図 1 2 ( A ) には、N 本の配線 4 1 のうち i 本目の配線 4 1 ( 配線 4 1 [ i ] と示す ) 、N 本の配線 4 2 のうち i 本目の配線 4 2 ( 配線 4 2 [ i ] と示す ) 、M 本の配線 4 3 のうち j ( j は 1 ~ M のいずれか一 ) 本目の配線 4 3 ( 配線 4 3 [ j ] と示す ) の

50

みを示す。

**【0194】**

複数の画素310のうちi行目、j列目に属する画素310（画素310[i, j]と示す）は、配線41[i]、配線42[i]、配線43[j]及び配線44と接続される。

**【0195】**

画素310[i, j]において、トランジスタ311の第1の端子は配線44と接続され、トランジスタ311のゲートは回路320と接続される。トランジスタ312の第1の端子はトランジスタ311の第2の端子と接続され、トランジスタ312の第2の端子は表示素子313と接続され、トランジスタ312のゲートは配線42[i]と接続される。また、回路320は配線43[j]、配線41[i]と接続される。

10

**【0196】**

なお、配線44には電圧が入力される。配線44は表示素子313に流れる電流を供給する機能を有する。

**【0197】**

なお、ゲートドライバ302として実施の形態1及び実施の形態2のシフトレジスタ回路を用いる場合、N本の配線42がN本の配線21に対応する。例えば、配線42[i]が配線21[i]に対応する。

**【0198】**

次に、図12(A)の表示装置の動作について説明する。

**【0199】**

ゲートドライバ301は、N本の配線41に順次ハイレベルの信号を出力する。ゲートドライバ302は、N本の配線42に順次ロウレベルの信号を出力する。ソースドライバ303はビデオ信号をM本の配線43に出力する。

20

**【0200】**

例えば、画素310[i, j]では、ゲートドライバ301がハイレベルの信号を配線41[i]に出力すると、配線43[j]のビデオ信号が書き込まれる。このビデオ信号はソースドライバ303が配線43[j]に出力したビデオ信号である。その後、画素310[i, j]は、再びゲートドライバ301がハイレベルの信号を配線41[i]に出力するまでビデオ信号を保持し、該ビデオ信号に応じた表示を行う。

**【0201】**

具体的には、ゲートドライバ301がハイレベルの信号を配線41[i]に出力すると、ビデオ信号は回路320に入力される。回路320はビデオ信号にトランジスタ311のしきい値電圧及び/又は移動度等に応じた補正を施し、補正を施したビデオ信号をトランジスタ311にゲートに供給する。すると、トランジスタ311は補正を施したビデオ信号に応じた電流を供給することができるようになる。ただし、回路320にビデオ信号が入力される期間、回路320がビデオ信号に補正を施すための期間、及び/又は回路320にビデオ信号が入力される前の初期化期間等においては、トランジスタ311の電流は不正な値となっていることが多い。この電流が表示素子に供給されてしまうと、階調がずれたり、黒浮きが生じたりすることがある。そこで、上述した期間においては、ゲートドライバ302が配線42[i]にロウレベルの信号を出力することにより、トランジスタ312をオフにする。

30

**【0202】**

なお、ゲートドライバ302として実施の形態1及び実施の形態2のシフトレジスタ回路を用いる場合、ゲートドライバ302が配線42[1]乃至配線42[N]に出力する信号が信号SOUTA[1]乃至信号SOUTA[N]に対応する。例えば、ゲートドライバ302が配線42[i]に出力する信号が信号SOUTA[i]に対応する。

40

**【0203】**

なお、図12(B)に示すように、トランジスタ311とトランジスタ312との接続箇所を入れ替えてよい。

**【0204】**

50

ゲートドライバ302として実施の形態1及び実施の形態2のシフトレジスタ回路を用いることにより、ゲートドライバ302を画素のトランジスタと同じ極性のトランジスタで構成することが可能になる。よって、ゲートドライバ301だけでなく、ゲートドライバ302を画素部300と同じ基板に形成することができる。

#### 【0205】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0206】

##### (実施の形態4)

本実施の形態では、本発明の一態様に係る表示装置の画素及び駆動回路の断面構成について、EL表示装置を例に挙げて説明する。

10

#### 【0207】

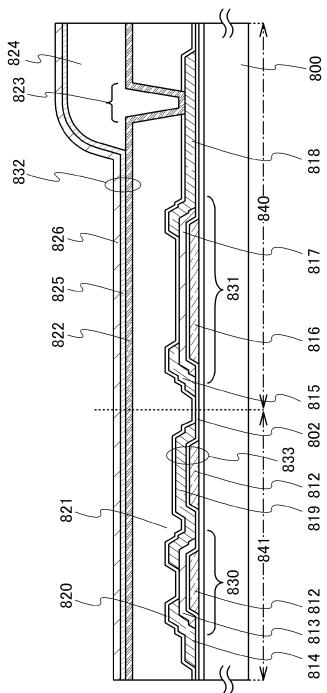

図13は、本実施の形態の表示装置の断面図であり、画素840及び駆動回路841の断面図を示す。

#### 【0208】

画素840は、発光素子832と、発光素子832に電流を供給する機能を備えるトランジスタ831とを有する。なお、画素840は、発光素子832及びトランジスタ831に加えて、画像信号の画素840への入力を制御するトランジスタ、及びノ/又は画像信号の電位を保持する容量素子など、各種の半導体素子を有していてもよい。

#### 【0209】

駆動回路841は、トランジスタ830と、トランジスタ830のゲート電圧を保持するための容量素子833とを有する。駆動回路841は、実施の形態1又は実施の形態2の基本回路、順序回路及びシフトレジスタ回路等に対応する。具体的には、トランジスタ830は、トランジスタ101等に相当する。なお、駆動回路841は、トランジスタ830及び容量素子833に加えて、トランジスタや容量素子などの各種の半導体素子を有していてもよい。

20

#### 【0210】

トランジスタ831は、絶縁表面を有する基板800上に、ゲートとして機能する導電膜816と、導電膜816上のゲート絶縁膜802と、導電膜816と重なる位置においてゲート絶縁膜802上に位置する半導体膜817と、ソース端子またはドレイン端子として機能し、半導体膜817上に位置する導電膜815及び導電膜818とを有する。導電膜816は走査線としても機能する。

30

#### 【0211】

トランジスタ830は、絶縁表面を有する基板800上に、ゲートとして機能する導電膜812と、導電膜812上のゲート絶縁膜802と、導電膜812と重なる位置においてゲート絶縁膜802上に位置する半導体膜813と、ソース端子またはドレイン端子として機能し、半導体膜813上に位置する導電膜814及び導電膜819とを有する。

#### 【0212】

容量素子833は、絶縁表面を有する基板800上に、導電膜812と、導電膜812上のゲート絶縁膜802と、導電膜812と重なる位置においてゲート絶縁膜802上に位置する導電膜819とを有する。

40

#### 【0213】

導電膜814、導電膜815、導電膜818、導電膜819上には、絶縁膜820及び絶縁膜821が、順に積層されるように設けられている。そして、絶縁膜821上には、陽極として機能する導電膜822が設けられている。導電膜822は、絶縁膜820及び絶縁膜821に形成されたコンタクトホール823を介して、導電膜818に接続されている。

#### 【0214】

導電膜822の一部が露出するような開口部を有した絶縁膜824が、絶縁膜821上に設けられている。導電膜822の一部及び絶縁膜824上には、EL層825と、陰極として機能する導電膜826とが、順に積層するように設けられている。導電膜822と、

50

E L 層 8 2 5 と、導電膜 8 2 6 とが重なっている領域が、発光素子 8 3 2 に相当する。

**【 0 2 1 5 】**

なお、本発明の一態様において、トランジスタは、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの半導体が半導体膜に用いられていてもよいし、酸化物半導体などのワイドギャップ半導体が半導体膜に用いられていてもよい。

**【 0 2 1 6 】**

トランジスタの半導体膜に、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの半導体が用いられる場合、一導電性を付与する不純物元素を上記半導体膜に添加して、ソース端子またはドレイン端子として機能する不純物領域を形成する。例えば、リンまたはヒ素を上記半導体膜に添加することで、n型の導電性を有する不純物領域を形成することができる。また、例えば、ホウ素を上記半導体膜に添加することで、p型の導電性を有する不純物領域を形成することができる。10

**【 0 2 1 7 】**

また、トランジスタの半導体膜に、酸化物半導体が用いられる場合、ドーパントを上記半導体膜に添加して、ソース端子またはドレイン端子として機能する不純物領域を形成してもよい。ドーパントの添加は、イオン注入法を用いることができる。ドーパントは、例えばヘリウム、アルゴン、キセノンなどの希ガスや、窒素、リン、ヒ素、アンチモンなどの15族元素などを用いることができる。例えば、窒素をドーパントとして用いた場合、不純物領域中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下であることが望ましい。20

**【 0 2 1 8 】**

なお、シリコン半導体としては、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハーに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

**【 0 2 1 9 】**

なお、酸化物半導体としては、少なくともインジウム(I n)あるいは亜鉛(Z n)を含むことが好ましい。特にI nとZ nを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(G a)を有することが好ましい。また、スタビライザーとしてスズ(S n)を有することが好ましい。また、スタビライザーとしてハフニウム(H f)を有することが好ましい。また、スタビライザーとしてアルミニウム(A l)を有することが好ましい。30

**【 0 2 2 0 】**

また、他のスタビライザーとして、ランタノイドである、ラントラン(L a)、セリウム(C e)、プラセオジム(P r)、ネオジム(N d)、サマリウム(S m)、ユウロピウム(E u)、ガドリニウム(G d)、テルビウム(T b)、ジスプロシウム(D y)、ホルミウム(H o)、エルビウム(E r)、ツリウム(T m)、イッテルビウム(Y b)、ルテチウム(L u)のいずれか一種または複数種を含んでいてもよい。

**【 0 2 2 1 】**

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、I n - Z n系酸化物、S n - Z n系酸化物、A l - Z n系酸化物、Z n - M g系酸化物、S n - M g系酸化物、I n - M g系酸化物、I n - G a系酸化物、I n - G a - Z n系酸化物(I G Z Oとも表記する)、I n - A l - Z n系酸化物、I n - S n - Z n系酸化物、S n - G a - Z n系酸化物、A l - G a - Z n系酸化物、S n - A l - Z n系酸化物、I n - H f - Z n系酸化物、I n - L a - Z n系酸化物、I n - C e - Z n系酸化物、I n - P r - Z n系酸化物、I n - N d - Z n系酸化物、I n - S m - Z n系酸化物、I n - E u - Z n系酸化物、I n - G d - Z n系酸化物、I n - T b - Z n系酸化物、I n - D y - Z n系酸化物、I n - H o - Z n系酸化物、I n - E r - Z n系酸化物、I n - T m - Z n系酸化物、I n - Y b - Z n系酸化物、I n - L u - Z n系酸化物、I n - S n - G a - Z n系酸4050

化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。また、上記酸化物半導体は、珪素を含んでいてもよい。

#### 【0222】

なお、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素を含んでいてもよい。In-Ga-Zn系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高いため、トランジスタに用いる半導体材料としては好適である。

#### 【0223】

10

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$ あるいは $In : Ga : Zn = 2 : 2 : 1 (= 2/5 : 2/5 : 1/5)$ の原子比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1/3 : 1/3 : 1/3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1/3 : 1/6 : 1/2)$ あるいは $In : Sn : Zn = 2 : 1 : 5 (= 1/4 : 1/8 : 5/8)$ の原子比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0224】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

20

#### 【0225】

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、i型（真性半導体）又はi型に限りなく近い。そのため、上記酸化物半導体を用いたトランジスタは、オフ電流が著しく低いという特性を有する。また、酸化物半導体のバンドギャップは、2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。水分または水素などの不純物濃度が十分に低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体膜を用いることにより、トランジスタのオフ電流を下げることができる。

#### 【0226】

具体的に、高純度化された酸化物半導体を半導体膜に用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu m$ でチャネル長が $10 \mu m$ の素子であっても、ソース端子とドレイン端子間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} A$ 以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で除した数値に相当するオフ電流密度は、 $100 zA / \mu m$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流密度の測定を行った。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流密度を測定した。その結果、トランジスタのソース端子とドレイン端子間の電圧が3Vの場合に、数十 $yA / \mu m$ という、さらに低いオフ電流密度が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

30

#### 【0227】

なお、本明細書等において、オフ電流とは、nチャネル型トランジスタにおいては、ドレイン端子をソース端子とゲートよりも高い電位とした状態において、ソース端子の電位を基準としたときのゲートの電位が0以下であるときに、ソース端子とドレイン端子の間に流れる電流のことを意味する。また、pチャネル型トランジスタにおいては、オフ電流と

40

50

は、ドレイン端子をソース端子とゲートよりも低い電位とした状態において、ソース端子の電位を基準としたときのゲートの電位が0以上であるときに、ソース端子とドレイン端子の間に流れる電流のことを意味する。

#### 【0228】

なお、例えば、酸化物半導体膜は、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含むターゲットを用いたスパッタ法により形成することができる。In-Ga-Zn系酸化物半導体膜をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Ga:Zn = 1:1:1、4:2:3、3:1:2、1:1:2、2:1:3、または3:1:4で示されるIn-Ga-Zn系酸化物のターゲットを用いる。前述の原子数比を有するIn-Ga-Zn系酸化物のターゲットを用いて酸化物半導体膜を成膜することで、多結晶または後述するCACが形成されやすくなる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

#### 【0229】

なお、酸化物半導体膜としてIn-Zn系酸化物の材料を用いる場合、用いるターゲットの組成は、原子数比で、In:Zn = 50:1~1:2(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 25:1~1:4)、好ましくはIn:Zn = 20:1~1:1(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 10:1~1:2)、さらに好ましくはIn:Zn = 1.5:1~1.5:1(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 3:4~1.5:2)とする。例えば、In-Zn系酸化物である酸化物半導体膜の形成に用いるターゲットは、原子数比がIn:Zn:O = X:Y:Zのとき、Z > 1.5X+Yとする。Znの比率を上記範囲に収めることで、移動度の向上を実現することができる。

#### 【0230】

そして、具体的に酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて形成すればよい。成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としてもよい。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0231】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素(水酸基を含む)が多量に含まれていることがある。水分または水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体膜に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)雰囲気下で、加熱処理を施す。

#### 【0232】

酸化物半導体膜に加熱処理を施すことで、酸化物半導体膜中の水分または水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えばよい。例えば、500、3分間以上6分間以下

10

20

30

40

50

程度で行えればよい。加熱処理に R T A 法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

#### 【 0 2 3 3 】

なお、上記加熱処理により、酸化物半導体膜から酸素が脱離し、酸化物半導体膜内に酸素欠損が形成される場合がある。よって、本発明の一態様では、酸化物半導体膜と接するゲート絶縁膜などの絶縁膜として、酸素を含む絶縁膜を用いる。そして、酸素を含む絶縁膜を形成した後、加熱処理を施すことで、上記絶縁膜から酸化物半導体膜に酸素が供与されるようにする。上記構成により、ドナーとなる酸素欠損を低減し、酸化物半導体膜に含まれる酸化物半導体の、化学量論的組成を満たすことができる。その結果、酸化物半導体膜を i 型に近づけることができ、酸素欠損によるトランジスタの電気的特性のばらつきを軽減し、電気的特性の向上を実現することができる。10

#### 【 0 2 3 4 】

なお、酸素を酸化物半導体膜に供与するための加熱処理は、窒素、超乾燥空気、または希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは 200 以上 400 以下、例えば 250 以上 350 以下）で行う。上記ガスは、水の含有量が 20 ppm 以下、好ましくは 1 ppm 以下、より好ましくは 10 ppb 以下であることが望ましい。

#### 【 0 2 3 5 】

酸化物半導体膜は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

#### 【 0 2 3 6 】

好ましくは、酸化物半導体膜は、 C A A C - O S ( C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜とする。20

#### 【 0 2 3 7 】

なお、当該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡（T E M : T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ）による観察像では、 C A A C - O S 膜に含まれる非晶質部と結晶部との境界、結晶部と結晶部との境界は明確ではない。また、T E M によって C A A C - O S 膜には明確な粒界（グレインバウンダリーともいう。）は確認できない。そのため、 C A A C - O S 膜は、粒界に起因する電子移動度の低下が抑制される。

#### 【 0 2 3 8 】

C A A C - O S 膜に含まれる結晶部は、c 軸が C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85° 以上 95° 以下の範囲も含まれることとする。また、単に平行と記載する場合、-5° 以上 5° 以下の範囲も含まれることとする。30

#### 【 0 2 3 9 】

なお、 C A A C - O S 膜において、結晶部の分布が一様でなくともよい。例えば、 C A A C - O S 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、 C A A C - O S 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。40

#### 【 0 2 4 0 】

C A A C - O S 膜に含まれる結晶部の c 軸は、 C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、 C A A C - O S 膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、 C A A C - O S 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。50

**【0241】**

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

**【0242】**

なお、酸化物半導体膜を構成する酸素の一部は窒素で置換されてもよい。

**【0243】**

次いで、本発明の一態様に係るトランジスタの、具体的な構成の一例について説明する。

**【0244】**

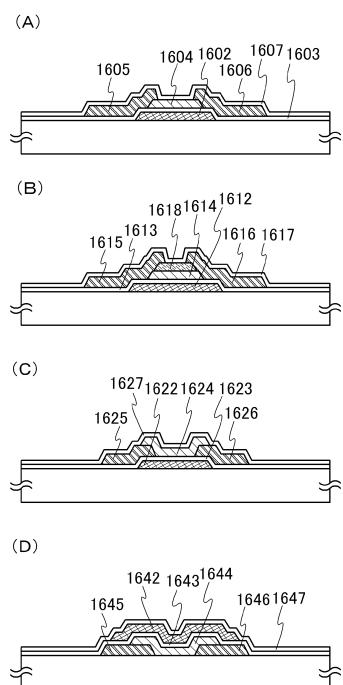

図14(A)に示すトランジスタは、チャネルエッチ構造の、ボトムゲート型である。

**【0245】**

図14(A)に示すトランジスタは、絶縁表面上に形成されたゲート電極(ゲート)1602と、ゲート電極1602上のゲート絶縁膜1603と、ゲート絶縁膜1603上においてゲート電極1602と重なっている半導体膜1604と、半導体膜1604上に形成された導電膜1605、導電膜1606とを有する。さらに、トランジスタは、半導体膜1604、導電膜1605及び導電膜1606上に形成された絶縁膜1607を、その構成要素に含めてもよい。

10

**【0246】**

なお、図14(A)に示したトランジスタは、半導体膜1604と重なる位置において絶縁膜1607上に形成されたバックゲート電極を、更に有してもよい。

**【0247】**

図14(B)に示すトランジスタは、チャネル保護構造の、ボトムゲート型である。

20

**【0248】**

図14(B)に示すトランジスタは、絶縁表面上に形成されたゲート電極1612と、ゲート電極1612上のゲート絶縁膜1613と、ゲート絶縁膜1613上においてゲート電極1612と重なっている半導体膜1614と、半導体膜1614上に形成されたチャネル保護膜1618と、半導体膜1614上に形成された導電膜1615、導電膜1616とを有する。さらに、トランジスタは、チャネル保護膜1618、導電膜1615及び導電膜1616上に形成された絶縁膜1617を、その構成要素に含めてもよい。

**【0249】**

なお、図14(B)に示したトランジスタは、半導体膜1614と重なる位置において絶縁膜1617上に形成されたバックゲート電極を、更に有してもよい。

30

**【0250】**

チャネル保護膜1618を設けることによって、半導体膜1614のチャネル形成領域となる部分に対する、後の工程における、エッティング時のプラズマやエッティング剤による膜減りなどのダメージを防ぐことができる。従ってトランジスタの信頼性を向上させることができる。

**【0251】**

図14(C)に示すトランジスタは、ボトムコンタクト構造の、ボトムゲート型である。

**【0252】**

図14(C)に示すトランジスタは、絶縁表面上に形成されたゲート電極1622と、ゲート電極1622上のゲート絶縁膜1623と、ゲート絶縁膜1623上の導電膜1625、導電膜1626と、ゲート絶縁膜1623上においてゲート電極1622と重なっており、なおかつ導電膜1625、導電膜1626上に形成された半導体膜1624とを有する。さらに、トランジスタは、導電膜1625、導電膜1626、及び半導体膜1624上に形成された絶縁膜1627を、その構成要素に含めてもよい。

40

**【0253】**

なお、図14(C)に示したトランジスタは、半導体膜1624と重なる位置において絶縁膜1627上に形成されたバックゲート電極を、更に有してもよい。

**【0254】**

図14(D)に示すトランジスタは、ボトムコンタクト構造の、トップゲート型である。

50

## 【0255】

図14(D)に示すトランジスタは、絶縁表面上に形成された導電膜1645、導電膜1646と、絶縁表面及び導電膜1645、導電膜1646上に形成された半導体膜1644と、半導体膜1644、導電膜1645及び導電膜1646上に形成されたゲート絶縁膜1643と、ゲート絶縁膜1643上において半導体膜1644と重なっているゲート電極1642とを有する。さらに、トランジスタは、ゲート電極1642上に形成された絶縁膜1647を、その構成要素に含めてよい。

## 【0256】

本実施の形態のトランジスタを実施の形態1及び実施の形態2の基本回路、順序回路及びシフトレジスタ回路を構成するトランジスタ、並びに実施の形態3の表示装置を構成するトランジスタに用いることができる。特に、酸化物半導体を用いたトランジスタは移動度が高く、オフ電流が小さい。よって、実施の形態1及び実施の形態2の基本回路、順序回路及びシフトレジスタ回路、並びに実施の形態3の表示装置を高速に動作させることができる。また、各ノードから漏れる電荷量を小さくすることができる。10

## 【0257】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0258】

## (実施の形態5)

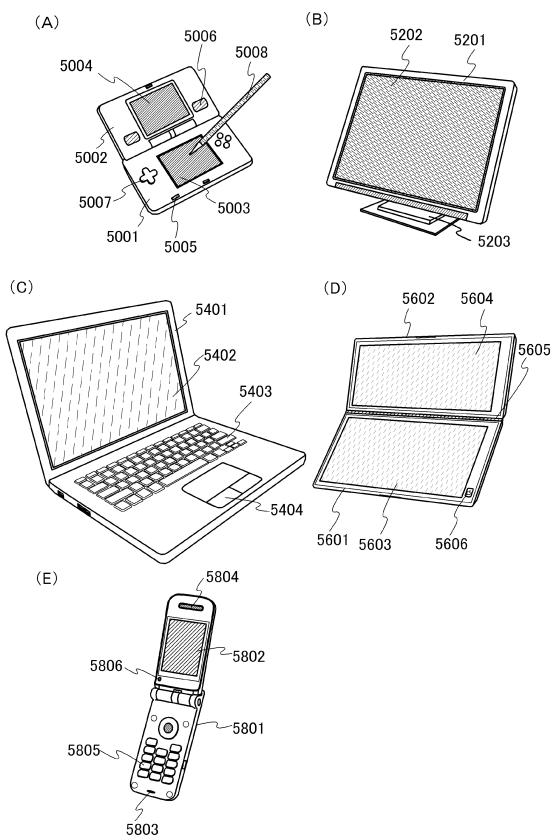

本発明の一態様に係る、基本回路、順序回路、シフトレジスタ回路及び表示装置等は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る、基本回路、順序回路、シフトレジスタ回路及び表示装置等を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図15に示す。20

## 【0259】

図15(A)は携帯型ゲーム機であり、筐体5001、筐体5002、表示部5003、表示部5004、マイクロホン5005、スピーカー5006、操作キー5007、スタイルス5008等を有する。なお、図15(A)に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。30

## 【0260】

図15(B)は表示機器であり、筐体5201、表示部5202、支持台5203等を有する。なお、表示機器には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

## 【0261】

図15(C)はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。40

## 【0262】

図15(D)は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602との間の角度は、接続部5605により可動となっている。第1表示部5603における映像の切り替えを、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としてもよい。50

## 【0263】

図15(E)は携帯電話であり、筐体5801、表示部5802、音声入力部5803、音声出力部5804、操作キー5805、受光部5806等を有する。受光部5806において受信した光を電気信号に変換することで、外部の画像を取り込むことができる。

## 【0264】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

## 【符号の説明】

## 【0265】

|         |        |    |

|---------|--------|----|

| 1 1     | 配線     |    |

| 1 2     | 配線     | 10 |

| 1 3     | 配線     |    |

| 1 4     | 配線     |    |

| 1 5     | 配線     |    |

| 1 6     | 配線     |    |

| 1 7     | 配線     |    |

| 2 1     | 配線     |    |

| 2 2     | 配線     |    |

| 2 3     | 配線     |    |

| 2 4     | 配線     |    |

| 2 5     | 配線     | 20 |

| 2 6     | 配線     |    |

| 2 7     | 配線     |    |

| 3 1     | 配線     |    |

| 3 2     | 配線     |    |

| 3 3     | 配線     |    |

| 3 4     | 配線     |    |

| 4 1     | 配線     |    |

| 4 2     | 配線     |    |

| 4 3     | 配線     |    |

| 4 4     | 配線     | 30 |

| 1 0 0   | 順序回路   |    |

| 1 0 1   | トランジスタ |    |

| 1 0 2   | トランジスタ |    |

| 1 0 3   | トランジスタ |    |

| 1 0 4   | トランジスタ |    |

| 1 0 4 S | スイッチ   |    |

| 1 0 5   | トランジスタ |    |

| 1 0 6   | トランジスタ |    |

| 1 0 6 S | スイッチ   |    |

| 1 0 7   | トランジスタ | 40 |

| 1 0 7 S | スイッチ   |    |

| 2 0 1   | トランジスタ |    |

| 2 0 2   | トランジスタ |    |

| 2 0 3   | トランジスタ |    |

| 2 0 4   | トランジスタ |    |

| 2 0 5   | トランジスタ |    |

| 2 0 6   | トランジスタ |    |

| 2 0 7   | トランジスタ |    |

| 2 0 8   | トランジスタ |    |

| 2 0 9   | トランジスタ | 50 |

|         |          |    |

|---------|----------|----|

| 2 1 0   | トランジスタ   |    |

| 2 1 1   | トランジスタ   |    |

| 2 1 2   | トランジスタ   |    |

| 2 1 3   | トランジスタ   |    |

| 2 1 4   | トランジスタ   |    |

| 3 0 0   | 画素部      |    |

| 3 0 1   | ゲートドライバ  |    |

| 3 0 2   | ゲートドライバ  |    |

| 3 0 3   | ソースドライバ  |    |

| 3 1 0   | 画素       | 10 |

| 3 1 1   | トランジスタ   |    |

| 3 1 2   | トランジスタ   |    |

| 3 1 3   | 表示素子     |    |

| 3 2 0   | 回路       |    |

| 8 0 0   | 基板       |    |

| 8 0 2   | ゲート絶縁膜   |    |

| 8 1 2   | 導電膜      |    |

| 8 1 3   | 半導体膜     |    |

| 8 1 4   | 導電膜      |    |

| 8 1 5   | 導電膜      | 20 |

| 8 1 6   | 導電膜      |    |

| 8 1 7   | 半導体膜     |    |

| 8 1 8   | 導電膜      |    |

| 8 1 9   | 導電膜      |    |

| 8 2 0   | 絶縁膜      |    |

| 8 2 1   | 絶縁膜      |    |

| 8 2 2   | 導電膜      |    |

| 8 2 3   | コンタクトホール |    |

| 8 2 4   | 絶縁膜      |    |

| 8 2 5   | E L 層    | 30 |

| 8 2 6   | 導電膜      |    |

| 8 3 0   | トランジスタ   |    |

| 8 3 1   | トランジスタ   |    |

| 8 3 2   | 発光素子     |    |

| 8 3 3   | 容量素子     |    |

| 8 4 0   | 画素       |    |

| 8 4 1   | 駆動回路     |    |

| 1 6 0 2 | ゲート電極    |    |

| 1 6 0 3 | ゲート絶縁膜   |    |

| 1 6 0 4 | 半導体膜     | 40 |

| 1 6 0 5 | 導電膜      |    |

| 1 6 0 6 | 導電膜      |    |

| 1 6 0 7 | 絶縁膜      |    |

| 1 6 1 2 | ゲート電極    |    |

| 1 6 1 3 | ゲート絶縁膜   |    |

| 1 6 1 4 | 半導体膜     |    |

| 1 6 1 5 | 導電膜      |    |

| 1 6 1 6 | 導電膜      |    |

| 1 6 1 7 | 絶縁膜      |    |

| 1 6 1 8 | チャネル保護膜  | 50 |

|         |             |    |

|---------|-------------|----|

| 1 6 2 2 | ゲート電極       |    |

| 1 6 2 3 | ゲート絶縁膜      |    |

| 1 6 2 4 | 半導体膜        |    |

| 1 6 2 5 | 導電膜         |    |

| 1 6 2 6 | 導電膜         |    |

| 1 6 2 7 | 絶縁膜         |    |

| 1 6 4 2 | ゲート電極       |    |

| 1 6 4 3 | ゲート絶縁膜      |    |

| 1 6 4 4 | 半導体膜        |    |

| 1 6 4 5 | 導電膜         | 10 |

| 1 6 4 6 | 導電膜         |    |

| 1 6 4 7 | 絶縁膜         |    |

| 5 0 0 1 | 筐体          |    |

| 5 0 0 2 | 筐体          |    |

| 5 0 0 3 | 表示部         |    |

| 5 0 0 4 | 表示部         |    |

| 5 0 0 5 | マイクロホン      |    |

| 5 0 0 6 | スピーカー       |    |

| 5 0 0 7 | 操作キー        |    |

| 5 0 0 8 | スタイラス       | 20 |

| 5 2 0 1 | 筐体          |    |

| 5 2 0 2 | 表示部         |    |

| 5 2 0 3 | 支持台         |    |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キーボード       |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          |    |

| 5 6 0 2 | 筐体          |    |

| 5 6 0 3 | 表示部         | 30 |

| 5 6 0 4 | 表示部         |    |

| 5 6 0 5 | 接続部         |    |

| 5 6 0 6 | 操作キー        |    |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 表示部         |    |

| 5 8 0 3 | 音声入力部       |    |

| 5 8 0 4 | 音声出力部       |    |

| 5 8 0 5 | 操作キー        |    |

| 5 8 0 6 | 受光部         |    |

| C K 1   | 信号          | 40 |

| C K 2   | 信号          |    |

| N 1     | ノード         |    |

| N 2     | ノード         |    |

| S C 1   | 信号          |    |

| S C 2   | 信号          |    |

| S C K 1 | 信号          |    |

| S C K 2 | 信号          |    |

| T 1     | 期間          |    |

| T 2     | 期間          |    |

| T 3     | 期間          | 50 |

T 4 期間

V N 1 電位

V N 2 電位

V D D 電位

V S S 電位

S P 信号

S S P 信号

O U T A 信号

O U T B 信号

S O U T A 信号

S O U T B 信号

R E 信号

I N I 信号

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(A)

(B)

【図8】

(A)

(B)

【図9】

(A)

(B)

【図10】

(A)

(B)

【図11】

(B)

【図12】

(B)

【図13】

【図14】

## 【図 1 5】

---

フロントページの続き

|                |                         |                |               |                |

|----------------|-------------------------|----------------|---------------|----------------|

| (51)Int.Cl.    | F I                     |                |               |                |

| <b>G 0 9 G</b> | <b>3/3225 (2016.01)</b> | <b>G 0 9 G</b> | <b>3/20</b>   | <b>6 1 1 A</b> |

|                |                         | <b>G 0 9 G</b> | <b>3/3266</b> |                |

|                |                         | <b>G 0 9 G</b> | <b>3/36</b>   |                |

|                |                         | <b>G 0 9 G</b> | <b>3/3225</b> |                |

|                |                         | <b>G 0 9 G</b> | <b>3/20</b>   | <b>6 7 0 E</b> |

(58)調査した分野(Int.Cl., DB名)

|                |                    |

|----------------|--------------------|

| <b>G 1 1 C</b> | <b>1 9 / 2 8</b>   |

| <b>G 0 2 F</b> | <b>1 / 1 3 3</b>   |

| <b>G 0 9 G</b> | <b>3 / 2 0</b>     |

| <b>G 0 9 G</b> | <b>3 / 3 2 2 5</b> |

| <b>G 0 9 G</b> | <b>3 / 3 2 6 6</b> |

| <b>G 0 9 G</b> | <b>3 / 3 6</b>     |