(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-506710

(P2006-506710A)

(43) 公表日 平成18年2月23日(2006.2.23)

(51) Int.C1.

**G06F 17/50** (2006.01)

F 1

G06F 17/50 664Z

G06F 17/50 654G

G06F 17/50 654K

テーマコード(参考)

5B046

審査請求 未請求 予備審査請求 未請求 (全 22 頁)

|               |                              |          |                                                                                                             |

|---------------|------------------------------|----------|-------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2004-551788 (P2004-551788) | (71) 出願人 | 502317817<br>ソニックス インコーポレイテッド<br>アメリカ合衆国 カリフォルニア州 94<br>040 マウンテン ビュー ウエスト<br>エル カミノ レアル 2440 スウェ<br>ート 620 |

| (86) (22) 出願日 | 平成15年11月5日 (2003.11.5)       | (74) 代理人 | 100082005<br>弁理士 熊倉 賴男                                                                                      |

| (85) 翻訳文提出日   | 平成17年7月7日 (2005.7.7)         | (74) 代理人 | 100067013<br>弁理士 大塚 文昭                                                                                      |

| (86) 國際出願番号   | PCT/US2003/035336            | (74) 代理人 | 100074228<br>弁理士 今城 俊夫                                                                                      |

| (87) 國際公開番号   | W02004/044749                | (74) 代理人 | 100086771<br>弁理士 西島 孝喜                                                                                      |

| (87) 國際公開日    | 平成16年5月27日 (2004.5.27)       |          |                                                                                                             |

| (31) 優先権主張番号  | 10/293,734                   |          |                                                                                                             |

| (32) 優先日      | 平成14年11月12日 (2002.11.12)     |          |                                                                                                             |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                             |

最終頁に続く

(54) 【発明の名称】構成可能なハードウェアを分解し、検証する方法及び装置

## (57) 【要約】

本発明は、構成可能なハードウェアを分解し、検証するための方法及び装置を含む。1つの実施において、この方法は、ハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、該ユニットの組の各々についてテストベンチを作成し、ハードウェア・システム設計を検証する前に該ユニットの組の各々を検証するステップを含む。

**【特許請求の範囲】****【請求項 1】**

ハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、前記ユニットの組の各々についてテストベンチを作成し、前記ハードウェア・システムを検証する前に、前記ユニットの組の各々を検証する、ステップを含むことを特徴とするコンピュータにより実施される方法。

**【請求項 2】**

前記ユニットの組が構成可能なハードウェア・ライブラリにおいて定義され、前記システムが構成データ・ストレージ・ユニットにおいて指定されることを特徴とする請求項1に記載のコンピュータにより実施される方法。 10

**【請求項 3】**

前記構成データが階層言語で表され、前記構成可能なハードウェア・ライブラリがハードウェア設計言語(HDL)で表されることを特徴とする請求項2に記載のコンピュータにより実施される方法。

**【請求項 4】**

前記テストベンチが、各ユニット接続に取り付けられたモデルを含み、前記モデルは、前記ユニットのパラメータに従って該ユニットとの間でデータを送受信することを特徴とする請求項1に記載のコンピュータにより実施される方法。

**【請求項 5】**

1つ又はそれ以上の階層レベルからなる構成可能なハードウェア・システム設計階層の第1のレベルにおける1つ又はそれ以上のユニットの組を、前記ハードウェア・システム設計階層の最も低いレベルの1つ又はそれ以上のユニットの組に自動的に分解し、 20

前記ハードウェア・システム設計階層の各階層レベルのユニットを、前記最も低いレベルから前記第1のレベルまで連続的に個別に検証し、テストベンチが一連のレベルの各々の各ユニットについて動的に構築されるようになる、

ステップを含むことを特徴とするコンピュータにより実施される方法。

**【請求項 6】**

前記自動的に分解するステップが、構成データ及び構成可能なハードウェア・ライブラリのコンテンツに基づいていることを特徴とする請求項5に記載のコンピュータにより実施される方法。 30

**【請求項 7】**

前記構成データが、前記構成可能なハードウェア・システム設計レベルの組の各々のユニットについてのパラメータを指定することを特徴とする請求項6に記載のコンピュータにより実施される方法。

**【請求項 8】**

前記構成可能なハードウェア・ライブラリが、前記階層レベルの組の各々のユニットを定義することを特徴とする請求項6に記載のコンピュータにより実施される方法。

**【請求項 9】**

構成データの組を、構成可能なハードウェア・ライブラリから選択された対応する構成可能なユニットの定義にマッピングし、1つ又はそれ以上の構成可能なハードウェア・ユニットの組を生成し、 40

前記構成データに基づいて、前記構成可能なハードウェア・ユニットの組の各々についてテストベンチを動的に生成し、

対応するテストベンチを用いて前記構成可能なハードウェア・ユニットの組の各々について検証し、

検証された前記構成可能なハードウェア・ユニットの組を構成可能なハードウェア・システム内に統合し、

前記構成可能なハードウェア・システムを検証する、ステップを含むことを特徴とするコンピュータにより実施される方法。

**【請求項 10】**

10

20

30

40

50

前記テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項 9 に記載のコンピュータにより実施される方法。

【請求項 1 1】

前記対応する構成可能なユニットの定義がハードウェア設計言語（HDL）で表されることを特徴とする請求項 9 に記載のコンピュータにより実施される方法。

【請求項 1 2】

前記構成データがツール制御言語（TCL）で表され、該構成データは、前記構成可能なハードウェア・ユニットの組の各々についてのパラメータを定義することを特徴とする請求項 9 に記載のコンピュータにより実施される方法。 10

【請求項 1 3】

前記テストベンチが前記ユニットの各通信経路に接続されたモデルを含むことを特徴とする請求項 9 に記載のコンピュータにより実施される方法。

【請求項 1 4】

構成データ及び構成可能なハードウェア・ライブラリに基づいて、より高いレベルの構成可能なハードウェア設計階層からなるシステムから分解された、より低いレベルの構成可能なハードウェア設計階層からなる個々のユニットについて、1つ又はそれ以上のテストベンチの組を構築し、 20

システム・テストベンチを構築し、

前記個々のユニットを検証した後で前記システムを検証する、

ステップを含むことを特徴とするコンピュータにより実施される方法。

【請求項 1 5】

前記システムは前記システム・テストベンチを用いて検証され、前記個々のユニットは前記テストベンチの組を用いて検証されることを特徴とする請求項 1 4 に記載のコンピュータにより実施される方法。

【請求項 1 6】

前記テストベンチの組及び前記システム・テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、 30

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項 1 4 に記載のコンピュータにより実施される方法。

【請求項 1 7】

前記構成可能なハードウェア・ライブラリが、前記システム内に含まれる前記ユニットを定義し、前記構成データが該システムのパラメータを指定することを特徴とする請求項 1 4 に記載のコンピュータにより実施される方法。

【請求項 1 8】

ハードウェア・システムを自動的に生成、分解、及び検証するための生成及び検証ユニットと、 40

ハードウェア・システム設計を定義するための構成データを含み、前記生成及び検証ユニットに結合された構成データ・ストレージ・ユニットと、

ハードウェア・システムを統合し、分解するための構成可能なハードウェア・ユニットの定義を格納するための、前記生成及び検証ユニットに結合された構成可能なハードウェア・ライブラリと、

を備えることを特徴とする装置。

【請求項 1 9】

前記構成可能なハードウェア・ユニットの定義が、ハードウェア設計言語（HDL）で表されることを特徴とする請求項 1 8 に記載の装置。

【請求項 2 0】

10

20

30

40

50

前記構成データが階層言語で表されることを特徴とする請求項18に記載の装置。

【請求項21】

前記生成及び検証ユニットが、ハードウェア設計階層内にユニット及びシステムを生成するための生成モジュールと、前記ユニット及び前記システムを分解するための分解モジュールと、該ユニット及び該システムについてテストベンチを構築し、該ユニット及び該システムを検証するための検証モジュールとを含むことを特徴とする請求項18に記載の装置。

【請求項22】

前記ユニット及びシステムがHDLで表されることを特徴とする請求項21に記載の装置。

10

【請求項23】

機械によって実行されるとき、前記機械に、

ハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、

前記ユニットの組の各々についてテストベンチを作成し、

前記ハードウェア・システム設計を検証する前に前記ユニットの組の各々を検証する、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

【請求項24】

前記ユニットの組が構成可能なハードウェア・ライブラリにおいて定義され、前記システムが構成データ・ストレージ・ユニットにおいて指定されることを特徴とする請求項23に記載の機械可読媒体。

20

【請求項25】

前記構成データが階層言語で表され、前記構成可能なハードウェア・ライブラリがハードウェア設計言語(HDL)で表されることを特徴とする請求項24に記載の機械可読媒体。

【請求項26】

前記テストベンチが、各ユニット接続に取り付けられたモデルを含み、前記モデルは、前記ユニットのパラメータに従って該ユニットとの間でデータを送受信することを特徴とする請求項23に記載の機械可読媒体。

30

【請求項27】

機械によって実行されるとき、前記機械に、

1つ又はそれ以上の階層レベルからなる構成可能なハードウェア・システム設計階層の第1のレベルにおける1つ又はそれ以上のユニットの組を、前記ハードウェア・システム設計階層の最も低いレベルの1つ又はそれ以上のユニットの組に自動的に分解し、

前記ハードウェア・システム設計階層の各階層レベルのユニットを、前記最も低いレベルから前記第1のレベルまで連続的に個別に検証し、テストベンチが一連のレベルの各々の各ユニットについて動的に構築されるようになる、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

【請求項28】

前記自動的に分解するステップが、構成データ及び構成可能なハードウェア・ライブラリのコンテンツに基づいていることを特徴とする請求項27に記載の機械可読媒体。

40

【請求項29】

前記構成データが、前記構成可能なハードウェア・システム設計レベルの組の各々のユニットについてのパラメータを指定することを特徴とする請求項28に記載の機械可読媒体。

【請求項30】

前記構成可能なハードウェア・ライブラリが、前記階層レベルの組の各々のユニットを定義することを特徴とする請求項28に記載の機械可読媒体。

【請求項31】

機械によって実行されるとき、前記機械に、

構成データの組を、構成可能なハードウェア・ライブラリから選択された対応する構成

50

可能なユニットの定義にマッピングし、1つ又はそれ以上の構成可能なハードウェア・ユニットの組を生成し、

前記構成データに基づいて、前記構成可能なハードウェア・ユニットの組の各々についてテストベンチを動的に生成し、

対応するテストベンチを用いて前記構成可能なハードウェア・ユニットの組の各々について検証し、

検証された前記構成可能なハードウェア・ユニットの組を構成可能なハードウェア・システム内に統合し、

前記構成可能なハードウェア・システムを検証する、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

10

#### 【請求項 3 2】

前記テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項 3 1 に記載の機械可読媒体。

#### 【請求項 3 3】

前記対応する構成可能なユニットの定義がハードウェア設計言語（HDL）で表されることを特徴とする請求項 3 1 に記載の機械可読媒体。

#### 【請求項 3 4】

前記構成データがツール制御言語（TCL）で表され、該構成データは、前記構成可能なハードウェア・ユニットの組の各々についてのパラメータを定義することを特徴とする請求項 3 1 に記載の機械可読媒体。

20

#### 【請求項 3 5】

前記テストベンチが前記ユニットの各通信経路に接続されたモデルを含むことを特徴とする請求項 3 1 に記載の機械可読媒体。

#### 【請求項 3 6】

機械によって実行されるとき、前記機械に、

構成データ及び構成可能なハードウェア・ライブラリに基づいて、より高いレベルの構成可能なハードウェア設計階層からなるシステムから分解された、より低いレベルの構成可能なハードウェア設計階層からなる個々のユニットについて1つ又はそれ以上のテストベンチの組を構築し、

30

システム・テストベンチを構築し、

前記個々のユニットを検証した後で前記システムを検証する、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

#### 【請求項 3 7】

前記システムは前記システム・テストベンチを用いて検証され、前記個々のユニットは前記テストベンチの組を用いて検証されることを特徴とする請求項 3 6 に記載の機械可読媒体。

#### 【請求項 3 8】

前記テストベンチの組及び前記システム・テストベンチ上で実行される試験を生成し、

40

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項 3 6 に記載の機械可読媒体。

#### 【請求項 3 9】

前記構成可能なハードウェア・ライブラリが、前記システム内に含まれる前記ユニットを定義し、前記構成データが該システムのパラメータを指定することを特徴とする請求項 3 6 に記載の機械可読媒体。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

50

本発明は、ハードウェアの検証に関する。より具体的には、本発明は、構成可能なハードウェアを検証することに関する。

【背景技術】

【0002】

「構成可能なハードウェア」又は「パラメータ化されたハードウェア」とは、パラメータ又は属性の組についての特定の値を用いて、設計作成時に自動的にカスタマイズされるハードウェア・システムを説明するものである。こうしたハードウェアは、パラメータの設定によって、実行時における変更もサポートする。構成可能なハードウェア・システムは、一般に、汎用コンピュータ・システム上で動作するソフトウェアより優れた性能を提供し、回路のサイズとコストを増大させることなく、従来の特定用途向け集積回路（ASIC）より大きな柔軟性をもたらす。10

【0003】

従来のハードウェア・システムにおいては、システム及びそのコンポーネントを試験することによって、システムの機能を検証することが必要である。一般に、システムの機能を検証する複雑さは、該システムを構成するコンポーネントの数と共に増大する。したがって、従来の手法は、各々のユニットを個別に手作業で検証し、次に「分かっている優れたユニット」をシステム内に組み立てるというものである。ハードウェアが階層構造に配列されている場合には、階層内の各レベルについて検証を行わなければならない。システムを組み立てる前に個々のユニットの各々が検証された場合、検証システム機能が、各コンポーネントの能力ではなく、コンポーネント間の相互作用に関する潜在的な問題に主眼を置くことができる。20

【0004】

このタイプの従来の階層分解を用いて、構成可能なハードウェア・システムを検証することができる。しかしながら、構成可能なハードウェア・システムの各インスタンスが異なるため、構成パラメータはその都度修正され、システム及びそのコンポーネントを手作業で検証しなければならない。システム及びそのコンポーネントを繰り返し手作業で検証するコストにより、多くの場合、構成可能なハードウェアの利点が相殺される。

【発明の開示】

【0005】

本発明は、構成可能なハードウェアを分解し、検証するための方法及び装置を含む。1 30

この実施において、この方法は、ハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、該ユニットの組の各々についてテストベンチを作成し、ハードウェア・システム設計を検証する前に該ユニットの組の各々を検証するステップを含む。

【発明を実施するための最良の形態】

【0006】

本発明が、同じ参照番号が類似した要素を示す添付図面の図において、制限としてでなく、例として示される。

構成可能なハードウェアを分解し、検証するための方法及び装置が説明される。この説明において、「1つの実施形態」又は「実施形態」への言及は、言及される特徴が、本発明の少なくとも1つの実施形態に含まれることを意味することに注意されたい。さらに、この説明における「1つの実施形態」への別個の言及は、必ずしも同じ実施形態を指すとは限らず、そのように述べられ、当業者には容易に明らかである場合を除いて、こうした実施形態のいずれも相互排他的なものである。したがって、本発明は、ここに記載される実施形態のいずれの種々の組み合わせ及び/又は統合を含むことができる。40

【0007】

ここに、ブロック図が本発明の例示的な実施形態を示す。また、ここに、フロー図が本発明の例示的な実施形態の作動を示す。フロー図の動作が、ブロック図に示される例示的な実施形態と関連して説明される。しかしながら、フロー図の動作は、ブロック図と関連して説明されるもの以外の本発明の実施形態によって実行でき、ブロック図に関連して説明される実施形態が、フロー図と関連して説明されたものと異なる動作を実行できること50

を理解すべきである。

### 【0008】

#### 概要

本発明の1つの実施形態において、生成及び検証ユニットが、構成データ及び構成可能なハードウェア・ライブラリに基づいて、構成可能なハードウェア・システムを生成する。構成可能なハードウェア・システムは、多数のユニットから構成される。本発明の1つの実施形態において、生成及び検証ユニットは、構成可能なハードウェア・システムを、システム設計を構成するユニットに階層的に分解する。構成データが各ユニットに適用されるので、ユニット自体を変えることなく、各ユニットを、システムの外側で取り外し、検証し、又は分析することができる。生成及び検証ユニットは、各ユニットについて、テ

10

### 【0009】

#### 例示的なアーキテクチャ

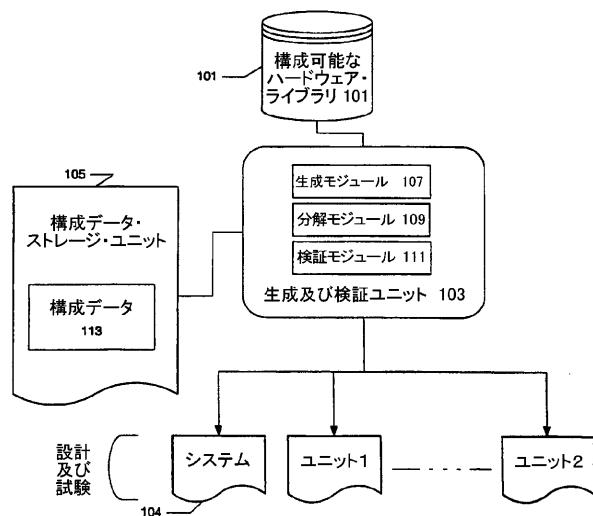

図1は、本発明の1つの実施形態による構成可能なハードウェアを分解し、検証するためのブロック図である。図1は、生成及び検証ユニット103を含み、この生成及び検証ユニット103は、生成モジュール107、分解モジュール109、及び検証モジュール111をさらに含む。生成及び検証ユニット103は、構成可能なハードウェア・ライブラリ101及び構成データ・ストレージ・ユニット105に接続される。構成データ・ストレージ・ユニット105は、構成データ113を含む。生成及び検証ユニット103は、構成可能なハードウェア・システム104及びその構成要素ユニット（ユニット1-Nとして示されている）を生成する。

20

### 【0010】

構成可能なハードウェア・システムの設計階層において、「システム」という用語は、ユニットの詳細が隠されている特定の階層レベルにおけるユニットの構成を指す。したがって、構成可能なハードウェア・システム設計階層の特定のレベルにおいて、ユニットは、分割できないコンポーネントである。しかしながら、より低い階層レベルにおいては、より高いレベルからのユニットは、それらの詳細及び内部コンポーネントが露出されている。例えば、図1を参照すると、ある設計階層レベルにおいて、システム104は、ユニット1-Nについての詳細が隠されている、より大きなシステムの「ブラックボックス」ユニットと見なされる。しかしながら、より低い設計階層レベルにおいては、システム104は、ユニット1-Nを含むものとして見なされ、そこではユニット接続の詳細が露出されている。より低いレベルの構成可能なハードウェア・システム設計階層においてさえ、ユニット1-Nの内部詳細が露出されている。最も低い階層レベルにおいては、ユニットを分解することができない。システム104及びユニット1-Nの生成が、図4において以下により詳細に説明される。

30

### 【0011】

構成データ・ストレージ・ユニット105は、構成可能なハードウェア・システムを階層的に説明する構成データ113を含む。例えば、構成データ113は、関連する全ての階層レベルにおいて、システム及びユニット・パラメータを指定する。エンド・ユーザは構成データ113における大部分のパラメータを設定するが、生成及び検証ユニット103が、ハードウェアの統合及び/又は分解プロセスの際に一部のパラメータを設定する。本発明の実施形態によると、構成データ113は、何らかの適切な電子設計自動化スクリプト言語によって表すことができる。本発明の1つの実施形態において、構成データ113は、ツール制御言語（TCL）のスクリプト言語で表される。特に、構成データ113は、システム設計名、システム・レベルのパラメータ、ユニット・レベル名及びパラメータ、ユニット・レベルの接続パラメータ（例えば、単一バンドル内のワイヤ数、ハンドシェーリング・プロトコル、パイプライン動作など）、及びユニットのインスタンスを特定の接続にバインドするためのインターフェース・ステートメントを定義するTCLテキストファイルを含むことができる。本発明の代替的な実施形態において、このシステム情報は、拡張可能マークアップ言語（XML）形式又はリレーションナル・データベースで表す

40

50

ことができる。

【0012】

いざれかの特定のハードウェア・ユニットの多数のインスタンスをハードウェア・システム内に含ませることができるので、各ユニットのインスタンスは、構成データ113において固有に名前が付けられる。さらに、同じユニットの異なるインスタンスを異なるように構成することができる。例えば、FIFOの1つのインスタンスは、10バイトの深さを有するように構成することができ、FIFOの別のインスタンスは、100バイトの深さを有するように構成することができる。

構成可能なハードウェア・ライブラリ101は、システムのハードウェア・コンポーネントの可能な構成の全てを記載する。例えば、構成可能なハードウェア・ライブラリ101は、深さ、幅、及び他の構成可能なパラメータを含む、FIFOの可能な構成の全てを記載することができる。本発明の1つの実施形態において、構成可能なハードウェア・ライブラリは、構成データ113をどのように解釈するかを説明する前処理ステートメントが組み込まれたハードウェア記述言語(HDL)コード(例えば、Verilog又はVHDL)を含む。

【0013】

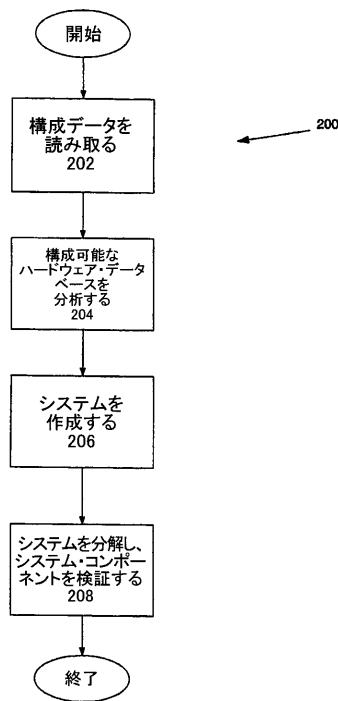

図2は、本発明の実施形態による、構成可能なハードウェア・システムの作成、分解、及び検証を示すフロー図である。フロー図200の動作が、図1のブロック図と関連して説明される。プロセス・ブロック202において、構成データが読み取られる。例えば、図1に示される本発明の実施形態によると、生成及び検証ユニット103の生成モジュール107が、構成データ・ストレージ・ユニット105から構成データ113を読み取る。上述のように、構成データ113は、構成可能なハードウェア・システムを階層的に定義するTCLファイルとすることができる。制御は、ブロック204に続く。

ブロック204において、構成可能なハードウェア・ライブラリが分析される。例えば、生成モジュール107は、構成データ113を分析し、構成データ113によって定義されるハードウェア・システムを生成するのに必要なハードウェア・コンポーネントの可能な構成を決定する。制御はブロック206に続く。

【0014】

ブロック206に示されるように、構成可能なハードウェア・システムが作成される。例えば、生成モジュール107は、構成データ113及び構成可能なハードウェア・ライブラリ101に基づいて構成可能なハードウェア・システムを作成する。ブロック206の動作が、図3に関連してさらに説明される。制御は、ブロック208に続く。

ブロック208において、システムが分解され、該システム及びそのコンポーネントが検証される。例えば、分解モジュール109及び検証モジュール111は、システム・コンポーネントを分解し、検証する。ブロック208における動作が、図5の説明において以下により詳細に説明される。

【0015】

階層システム設計のいざれのレベルにおいても、ハードウェアを生成し、検証するために、フロー図200に説明された動作を繰り返すことができることが、当業者には明らかであろう。例えば、特定の階層レベルにおいてシステムを検証するために、システムのコンポーネントの全てを検証しなければならない。このことは、より低いレベルのシステムの検証を必要とし、そのことが、さらに低いレベルのシステムの検証を必要とすることがある。最も低いレベルのシステムが検証されると、より高いレベルのシステムを順に検証することができる。したがって、いざれの設計レベルにおいても、システム及び/又はコンポーネントを作成し、検証するために、フロー図200に述べられた動作を繰り返すことができる。

【0016】

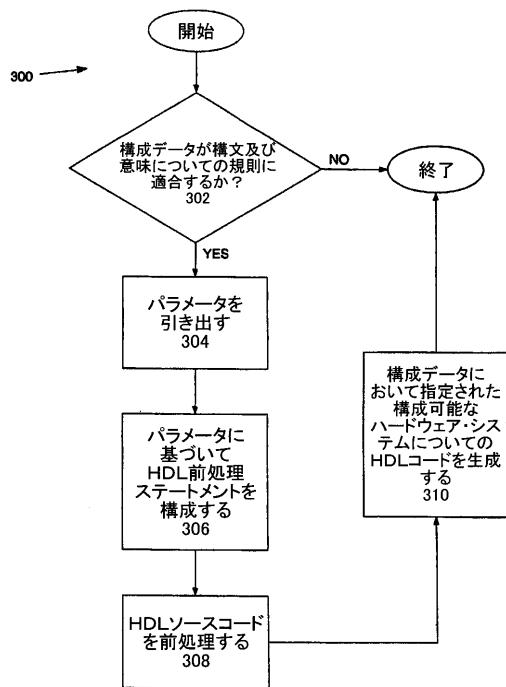

図3は、本発明の実施形態による、システムの作成を示すフロー図である。フロー図300の動作が、図1に示される例示的な実施形態に関連して説明される。決定ブロック302において、構成データが、構文及び意味についての規則に適合するかどうかが決定さ

10

20

30

40

50

れる。例えば、統合モジュール 109 は、構成データ・ストレージ・ユニット 105 からの構成データが、構文及び意味についての規則に適合するかどうかを決定する。より特定的な例として、構成データ 113 が T C L テキストファイルで表される実施形態において、統合モジュール 109 は、T C L ファイルが、構成可能なハードウェア・ライブラリによって用いられる H D L の構文及び意味規則に適合するかどうかを決定する。1 つの実施形態において、統合モジュール 109 は、高レベルの言語プログラム（例えば、C++、Python、又は Java プログラム）を用いて、構文及び意味について T C L ファイルを分析する。構成データ・ファイルが構文及び意味規則に適合する場合には、制御はブロック 304 に続く。他の場合には、フローは、エラー報告書で終了する。制御はブロック 304 に続く。

10

#### 【 0 0 1 7 】

ブロック 304 において、パラメータが引き出される。例えば、統合モジュール 109 は、構成データ 113 からシステム・パラメータを引き出す。より特定的な例として、1 つの実施形態において、統合モジュール 109 は、構成可能なハードウェア・システムを定義する T C L ファイルを分析することによって、システムのパラメータを引き出す。例えば、システム・パラメータは、内部通信経路に必要とする最小帯域幅を指定することができる。この設定から、システム内の種々の接続ポイントで用いられるワイヤの数を指定するためのパラメータが、構成データ内に規則に従って引き出される。制御はブロック 306 に続く。

20

ブロック 306 に示されるように、引き出されたパラメータに基づいて、前処理ステートメントが構成される。例えば、本発明の1つの実施形態において、統合モジュール 109 は、指定され、引き出されたパラメータによって影響される、H D L コードの前処理ステートメント（構成可能なハードウェア・ライブラリ 101 に格納されている）を構成する。これを行う際、統合モジュール 109 は、特定の値又は制御構造を、H D L コードに組み込まれたプリプロセッサ・ステートメントに与える。制御はブロック 308 に続く。

#### 【 0 0 1 8 】

ブロック 308 に示されるように、H D L ソースコードが前処理される。例えば、統合モジュール 109 は、引き出されたパラメータに従って構成された H D L ソースコードを前処理する。本発明の1つの実施形態において、統合モジュール 109 は、組み込まれた H D L ソースコードを前処理するためのマクロ言語プリプロセッサ（例えば、C プリプロセッサ、M4 プリプロセッサ、又は S I M P L E プリプロセッサ）を含む。

30

ブロック 310 において、構成データにおいて指定された、構成可能なハードウェア・システムのための H D L コードが生成される。例えば、統合モジュール 109 は、構成可能なハードウェア・ライブラリ 101 からの H D L コードを用いて、構成データ 113 において指定された、システムのための H D L コードを生成する。ブロック 310 から、制御が終了する。

#### 【 0 0 1 9 】

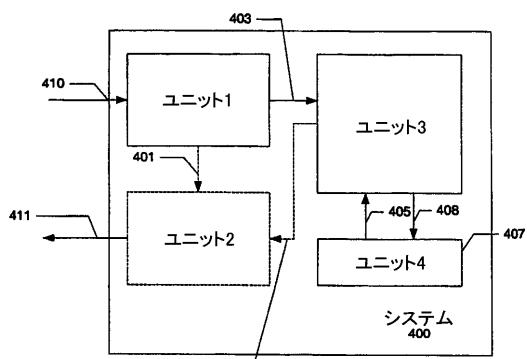

図 4 は、本発明の実施形態によるシステム設計の概念ブロック図である。上述のように、本発明の実施形態によると、図 3 の動作は、H D L コードで表されたシステム設計を生成する。図 4 は、こうしたシステムのグラフ表示を提供する。図 4 は、ユニット 1、ユニット 2、ユニット 3、及びユニット 4 からなるシステム 400 を含む。システム 400 において、ユニット 1 は、通信経路 410 によってシステム 400 の外部のシステムに通信する。ユニット 1 は、通信経路 401 によってユニット 2 に、通信経路 403 によってユニット 3 に結合される。ユニット 2 は、通信経路 411 を通してシステム 400 の外部のシステムと通信する。ユニット 3 は、通信経路 405 及び 408 によってユニット 4 に接続される。ユニット 3 はまた、通信経路 409 によってユニット 2 にも接続される。

40

#### 【 0 0 2 0 】

破線で示されるユニット 2 は、システム 400 における任意のユニットである。接続経路 401 及び 409 もまた任意的である。所定のレベルのシステム設計階層については、システムの外部の要因が、任意のユニットの機能（例えば、設計階層における、より高い

50

レベルのシステム)を必要とするかどうかが分からぬ場合には、ユニット(又は接続経路)は任意的である。例えば、2つの異なるモードで作動するようにシステム400を構成できるとすると、その機能が第2のモードによってではなく第1のモードによって要求される場合、ユニット2は任意的である。

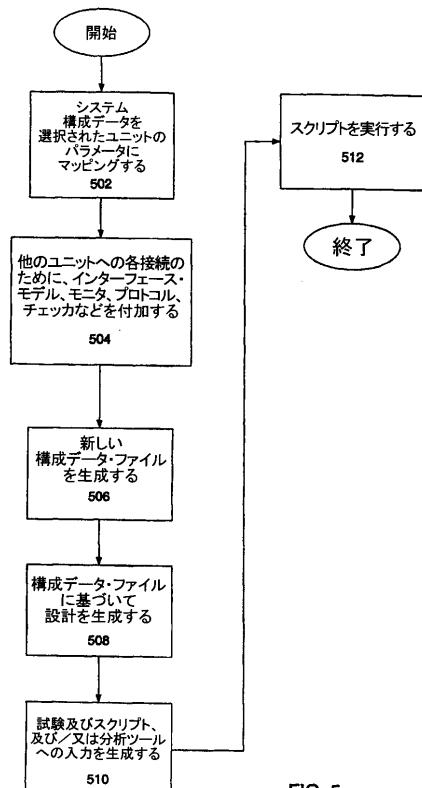

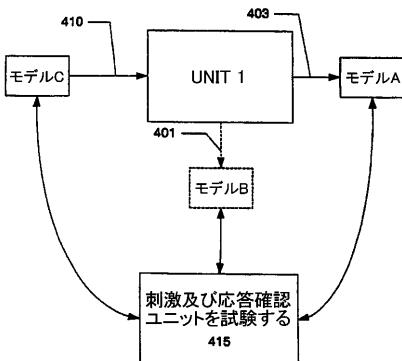

図5及び図6は、本発明の実施形態に従って、システム400がどのように分解され、検証されるかを示す。図5は、本発明の実施形態による、構成可能なハードウェア・システムを分解し、検証するための動作を示すフロー図である。図6は、本発明の実施形態に従って、ユニットを検証するためのテストベンチを示すブロック図である。図5及び図6は、図4の例示的なシステム及び図1の例示的な実施形態に関連して説明される。

#### 【0021】

図5のフロー図を参照すると、ブロック502において、構成データ113が、選択されたユニットのパラメータにマッピングされる。例えば、分解モジュール109は、システム400を定義する構成データ113を、システム400のユニット(例えば、ユニット1)のパラメータにマッピングする。より特定的な例として、分解モジュール109は、構成データ113を分析し、システム400の要件を満たすために、ユニット1のパラメータをどのように構成すべきかを決定する。制御はブロック504に続く。

#### 【0022】

ブロック504において、他のユニットへの各接続のために、インターフェース・モデル、モニタ、及び/又はプロトコル・チェックが、該ユニットに付加される。例えば、検証モジュール111は、構成データ113を分析し、選択されたユニット(例えば、ユニット1)のための接続を決定する。各接続(例えば、通信経路)のために、構成モジュール109は、モデルを、インターフェース・ドライバ・モデル、インターフェース・モニタ、及び/又はプロトコル・チェックを含み得るユニットに結合させる。この動作は、図6に概念的に示される。図6において、モデルAは、通信経路403を通してユニット1に接続され、モデルBは、通信経路401を通して該ユニット1に接続される。モデルCは、通信経路410を通してユニット1に接続される。試験刺激及び応答確認ユニット415が、モデルA、B、及びCに接続される。試験刺激及び応答確認ユニット415は、動作の試験を監視し、これを容易にする。テストベンチにおいて、モデルは、情報を検証されるユニットとの間で送受信するために用いられる。例えば、モデルA及びBは、ユニット1のパラメータに従って(例えば、特定の通信経路のために定義された特定の通信プロトコルに従って)、該ユニット1からデータの流れを受信する。同様に、モデルCは、ユニット1のパラメータに従って、データをユニット1に伝送する。ユニットとの間で伝送される特定のデータは、該ユニットを検証するために用いられる試験によって決定される。ブロック504から、制御はブロック506に続く。

#### 【0023】

ブロック506において、構成データが生成される。例えば、分解モジュール109は、構成データ113を生成し、選択されたユニットのパラメータを指定する。本発明の1つの実施形態によると、図1の説明において上述されたように、分解モジュール109は、TCLファイルの形態で構成データ113を生成する。代替的な実施形態によると、分解モジュール109は、XMLファイルの形態で構成データ113を生成する。

ブロック508において、構成データ113に基づいた設計が生成される。例えば、生成モジュール107は、構成可能なハードウェア・ライブラリ101を用い、構成データ113に基づいて構成可能なハードウェア・システム設計を生成する。この動作は、図3の説明において上記により詳細に説明されている。1つの実施形態において、設計は、HDLコードで表される。制御はブロック510に続く。

#### 【0024】

ブロック510において、試験及びスクリプト、及び/又は分析ツールへの入力が生成される。例えば、検証モジュール111は、試験及び/又は分析ツールへの入力を実行するために試験及びスクリプトを生成する。ブロック510から、制御はブロック512に継続する。試験を生成する際に、検証モジュール111は、特定のユニットの機能を検証

10

20

30

40

50

するのに周知の既存の試験を用いることができ、或いはユニット構成の分析に基づいてカスタマイズされた試験を生成することができる。これらの試験は、試験される構成されたユニットの機能を実行し、検証する。本発明の実施形態によると、検証モジュール111は、ユニットのいずれかの構成を検証することができる試験を生成する。この実施形態において、試験は、試験が始まる前ではなく試験を行っている間に、構成データ113を読み取り、これに応じてそれらの刺激を修正する。検証モジュール111はまた、試験を自動的に実行するためのスクリプトを生成することもできる。

#### 【0025】

試験の付加的な形態又は代替的な形態として、検証モジュール111は、設計の静的分析を行う分析ツールに設計を提供する。例えば、本発明の1つの実施形態によると、検証モジュール111は、HDLコードで表されたユニット設計を、エラーについてHDLコードを分析する静的検証ツールに提供する。1つの実施形態において、静的検証ツールは、HDLコードの分析に基づいて、警告及び/又はエラー・メッセージを生成する。

ロック512に示されるように、スクリプトが実行される。例えば、検証モジュール111は、選択されたユニットを自動的に試験し、検証するスクリプトを実行する。図5のフロー図に記載される動作を繰り返し、設計階層内のどのレベルにおいても、ユニット/システムを検証できることが、当業者には明らかであろう。

#### 【0026】

図1を参照すると、生成及び検証ユニット103、構成可能なハードウェア・ライブラリ101、及び構成データ・ストレージ・ユニット105は、1つ又はそれ以上のプロセッサ、特定用途向け集積回路(ASIC)、メモリ、及び/又は本発明の実施形態による動作を実行するための命令が格納される機械可読媒体を含む、従来のコンピューティング・プラットフォームの形態で実装することができる。機械可読媒体は、機械(例えば、コンピュータ)によって読み取り可能な形態で情報を提供する(すなわち、格納及び/又は伝送する)何らかの機構を含む。例えば、機械可読媒体は、読み取り専用メモリ(ROM)、ランダム・アクセス・メモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ素子、電気、光、音響、又は他の形態の伝搬信号(例えば、搬送波、赤外線信号、デジタル信号など)などを含む。1つの実施形態において、図1に示されるユニットは、プロセッサ上で動作し、ここに説明される動作を実行する機械可読媒体である。しかしながら、代替的な実施形態において、図1のユニットは、ここに説明される動作を実行するための他のタイプの論理(例えば、デジタル論理)である。代替的に、本発明の1つの実施形態によると、生成及び検証ユニット103、構成可能なハードウェア・ライブラリ101、及び構成データ・ストレージ・ユニット105は、1つ又はそれ以上の別個のコンピュータ・システムを含むことができる。本発明の実施形態によると、図1に示されるコンポーネントは、多数のネットワーク化コンピュータにわたって分散させ、これを遠隔制御し、操作できることも理解すべきである。

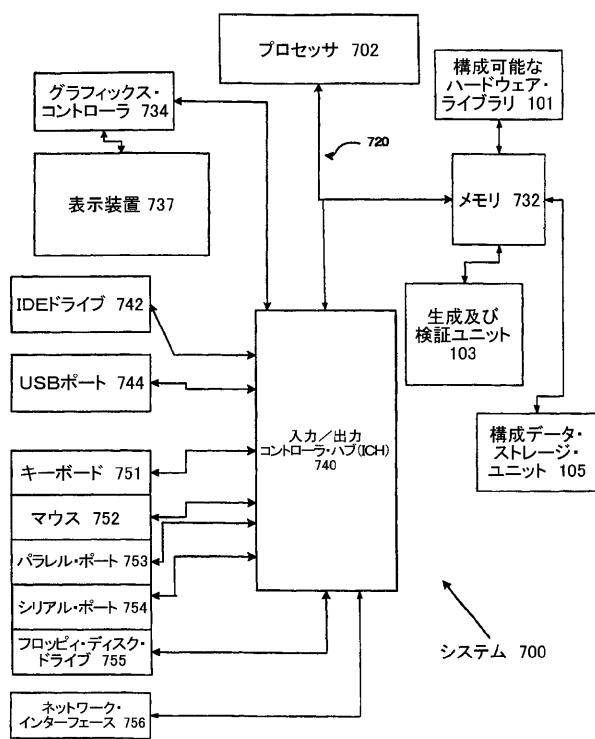

#### 【0027】

図7は、本発明の実施形態による、構成可能なハードウェアを分解し、検証するための例示的なシステムを示す。図7に示されるように、コンピュータ・システム700は、プロセッサ702を含む。コンピュータ・システム700は、メモリ732、プロセッサ・バス710、及び入力/出力コントローラ・ハブ(ICH)740を含むこともできる。プロセッサ702、メモリ732、及びICH740は、プロセッサ・バス710に結合される。プロセッサ702は、いずれかの適切なプロセッサ・アーキテクチャを含むこともできる。本発明の他の実施形態については、コンピュータ・システム700は、1つ、2つ、3つ、又はそれ以上のプロセッサを含むことができ、そのいずれも本発明の実施形態に従った命令の組を実行することができる。

#### 【0028】

メモリ732は、データ及び/又は命令を格納し、例えば、動的ランダム・アクセス・メモリ(DRAM)のような何らかの適切なメモリを含むことができる。本発明の1つの実施形態において、構成可能なハードウェア・ライブラリ101、生成及び検証ユニット

103、及び構成データ・ストレージ・ユニット105は、メモリ732に格納される。しかしながら、これらを、IDEドライブ742、メモリ732、及び/又は他の適切な記憶装置のいずれか又は全てに格納することもできる。本発明の実施形態によると、グラフィックス・コントローラ734が、表示装置737上の情報の表示を制御する。

入力/出力コントローラ・ハブ(ICH)740は、コンピュータ・システム700のために、I/O装置又は周辺コンポーネントへのインターフェースを提供する。ICH740は、いずれかの適切なインターフェース・コントローラを含み、プロセッサ702、メモリ732、及び/又はICH740と通信状態の何らかの適切な装置又はコンポーネントへの何らかの適切な通信リンクを提供する。本発明の1つの実施形態については、ICH740は、各インターフェースのために適切なアービトレーション及びバッファリングを提供する。

10

#### 【0029】

本発明の1つの実施形態については、ICH740は、例えばデータ及び/又は命令を格納するための、例えばハードディスク・ドライブ(HDD)又はコンパクト・ディスク読み取り専用メモリ(CD ROM)ドライブのような、1つ又はそれ以上の適切なIntegrated drive electronics(IDE)ドライバ742、1つ又はそれ以上のUSBポート744を介する1つ又はそれ以上の適切なuniversal serial bus(USB)へのインターフェースを提供する。本発明の1つの実施形態については、ICH740は、キーボード751、マウス752、フロッピィ・ディスク・ドライブ755、1つ又はそれ以上のパラレル・ポート753を介する1つ又はそれ以上の適切な装置(例えば、プリンタ)、及び1つ又はそれ以上のシリアル・ポート754を介する1つ又はそれ以上の適切な装置へのインターフェースも提供する。本発明の1つの実施形態については、ICH740は、コンピュータ・システム700が他のコンピュータ及び/又は装置と通信できるネットワーク・インターフェース756を提供することもできる。

20

#### 【0030】

したがって、コンピュータ・システム700は、ここに説明される方法のいずれか1つ又は全てを具体化する命令の組(すなわち、ソフトウェア)が格納される機械可読媒体を含む。例えば、ソフトウェアは、メモリ732及び/又はプロセッサ702内に完全に又は少なくとも部分的に常駐することができる。

30

本発明は、幾つかの実施形態に関して説明されたが、当業者であれば、本発明が説明された実施形態に制限されるものでないことを理解するであろう。添付の特許請求の範囲の精神及び範囲内の修正及び変更によって、本発明の方法及び装置を実行することができる。したがって、説明は、本発明を制限するものとしてではなく、例示的なものとみなすべきである。

#### 【図面の簡単な説明】

#### 【0031】

【図1】本発明の1つの実施形態による、構成可能なハードウェアを分解し、検証するためのブロック図である。

【図2】本発明の1つの実施形態による、構成可能なハードウェアを作成し、検証するためのシステムを示すブロック図である。

40

【図3】本発明の実施形態による、システムの作成を示すフロー図である。

【図4】本発明の実施形態による、システム設計の概念ブロック図である。

【図5】本発明の実施形態による、構成可能なハードウェア・システムを分解し、検証するための動作を示すフロー図である。

【図6】本発明の実施形態による、ユニットを検証するためのテストベンチを示すブロック図である。

【図7】本発明の実施形態による、構成可能なハードウェアを分解し、検証するための例示的なシステムを示す。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

**FIG. 5**

【 四 6 】

FIG. 6

〔 四 7 〕

**FIG. 7**

**【手続補正書】**

【提出日】平成17年7月14日(2005.7.14)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

構成可能なハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、

前記ユニットの組の各々についてテストベンチを作成し、

前記構成可能なハードウェア・システムを検証する前に、前記ユニットの組の各々を検証する、

ステップを含み、

前記構成可能なハードウェア・システムが、パラメータの組について指定された値を用いることによって設計作成時にカスタマイズされ、該構成可能なハードウェア・システムの第1のインスタンスの機能が、該構成可能なハードウェア・システムの第2のインスタンスのものと異なることを特徴とするコンピュータにより実施される方法。

**【請求項2】**

前記ユニットの組が構成可能なハードウェア・ライブラリにおいて定義され、前記構成可能なハードウェア・システムが構成データ・ストレージ・ユニットにおいて指定されることを特徴とする請求項1に記載のコンピュータにより実施される方法。

**【請求項3】**

前記構成データが階層言語で表され、前記構成可能なハードウェア・ライブラリがハードウェア設計言語(HDL)で表されることを特徴とする請求項2に記載のコンピュータにより実施される方法。

**【請求項4】**

前記テストベンチが、各ユニット接続に取り付けられたモデルを含み、前記モデルは、前記ユニットのパラメータに従って該ユニットとの間でデータを送受信することを特徴とする請求項1に記載のコンピュータにより実施される方法。

**【請求項5】**

1つ又はそれ以上の階層レベルからなる構成可能なハードウェア・システム設計階層の第1のレベルにおける1つ又はそれ以上のユニットの組を、前記ハードウェア・システム設計階層の最も低いレベルの1つ又はそれ以上のユニットの組に自動的に分解し、

前記ハードウェア・システム設計階層の各階層レベルのユニットを、前記最も低いレベルから前記第1のレベルまで連続的に個別に検証し、テストベンチが一連のレベルの各々の各ユニットについて動的に構築されるようになる、

ステップを含み、

前記構成可能なハードウェア・システムが設計作成時にカスタマイズされたようになったことを特徴とするコンピュータにより実施される方法。

**【請求項6】**

前記自動的に分解するステップが、構成データ及び構成可能なハードウェア・ライブラリのコンテンツに基づいていることを特徴とする請求項5に記載のコンピュータにより実施される方法。

**【請求項7】**

前記構成データが、前記構成可能なハードウェア・システム設計レベルの組の各々のユニットについてのパラメータを指定することを特徴とする請求項6に記載のコンピュータにより実施される方法。

**【請求項8】**

前記構成可能なハードウェア・ライブラリが、前記階層レベルの組の各々のユニットを定義することを特徴とする請求項6に記載のコンピュータにより実施される方法。

【請求項9】

構成データの組を、構成可能なハードウェア・ライブラリから選択された対応する構成可能なユニットの定義にマッピングし、1つ又はそれ以上の構成可能なハードウェア・ユニットの組を生成し、

前記構成データに基づいて、前記構成可能なハードウェア・ユニットの組の各々についてテストベンチを動的に生成し、

対応するテストベンチを用いて前記構成可能なハードウェア・ユニットの組の各々について検証し、

検証された前記構成可能なハードウェア・ユニットの組を構成可能なハードウェア・システム内に統合し、

設計作成環境における機能論理検証の際に、前記構成可能なハードウェア・システムを検証する、

ステップを含むことを特徴とするコンピュータにより実施される方法。

【請求項10】

前記テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項9に記載のコンピュータにより実施される方法。

【請求項11】

前記対応する構成可能なユニットの定義がハードウェア設計言語(HDL)で表されることを特徴とする請求項9に記載のコンピュータにより実施される方法。

【請求項12】

前記構成データがツール制御言語(TCL)で表され、該構成データは、前記構成可能なハードウェア・ユニットの組の各々についてのパラメータを定義することを特徴とする請求項9に記載のコンピュータにより実施される方法。

【請求項13】

前記テストベンチが前記ユニットの各通信経路に接続されたモデルを含むことを特徴とする請求項9に記載のコンピュータにより実施される方法。

【請求項14】

コンピュータにより実施される機能論理検証の方法であって、

構成データ及び構成可能なハードウェア・ライブラリに基づいて、より高いレベルの構成可能なハードウェア設計階層からなる構成可能なハードウェア・システムから分解された、より低いレベルの構成可能なハードウェア設計階層からなる個々のユニットについて1つ又はそれ以上のテストベンチの組を構築し、

システム・テストベンチを構築し、

前記個々のユニットを検証した後で前記構成可能なハードウェア・システムを検証する、

ステップを含むことを特徴とするコンピュータにより実施される方法。

【請求項15】

前記システムは前記システム・テストベンチを用いて検証され、前記個々のユニットは前記テストベンチの組を用いて検証されることを特徴とする請求項14に記載のコンピュータにより実施される方法。

【請求項16】

前記テストベンチの組及び前記システム・テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項14に記載のコンピュータにより実施され

る方法。

【請求項 17】

前記構成可能なハードウェア・ライブラリが、前記システム内に含まれる前記ユニットを定義し、前記構成データが該システムのパラメータを指定することを特徴とする請求項14に記載のコンピュータにより実施される方法。

【請求項 18】

構成可能なハードウェア・システムを自動的に生成、分解、及び検証するための生成及び検証ユニットと、

構成可能なハードウェア・システム設計を定義するための構成データを含み、前記生成及び検証ユニットに結合された構成データ・ストレージ・ユニットと、

ハードウェア・システムを統合し、分解するための構成可能なハードウェア・ユニットの定義を格納するための、前記生成及び検証ユニットに結合された構成可能なハードウェア・ライブラリと、

を備えることを特徴とする装置。

【請求項 19】

前記構成可能なハードウェア・ユニットの定義が、ハードウェア設計言語（HDL）で表されることを特徴とする請求項18に記載の装置。

【請求項 20】

前記構成データが階層言語で表されることを特徴とする請求項18に記載の装置。

【請求項 21】

前記生成及び検証ユニットが、ハードウェア設計階層内にユニット及びシステムを生成するための生成モジュールと、前記ユニット及び前記システムを分解するための分解モジュールと、該ユニット及び該システムについてテストベンチを構築し、該ユニット及び該システムを検証するための検証モジュールとを含むことを特徴とする請求項18に記載の装置。

【請求項 22】

前記ユニット及びシステムがHDLで表されることを特徴とする請求項21に記載の装置。

【請求項 23】

機械によって実行されるとき、前記機械に、

構成可能なハードウェア・システムを1つ又はそれ以上のユニットの組に自動的に分解し、

前記ユニットの組の各々についてテストベンチを作成し、

前記構成可能なハードウェア・システム設計を検証する前に前記ユニットの組の各々を検証する、

ステップを含む動作を実行させる命令を提供し、

前記構成可能なハードウェア・システムが、パラメータの組について指定された値を用いることによって設計作成時にカスタマイズされ、該構成可能なハードウェア・システムの第1のインスタンスの機能が、該構成可能なハードウェア・システムの第2のインスタンスのものと異なることを特徴とする機械可読媒体。

【請求項 24】

前記ユニットの組が構成可能なハードウェア・ライブラリにおいて定義され、前記システムが構成データ・ストレージ・ユニットにおいて指定されることを特徴とする請求項23に記載の機械可読媒体。

【請求項 25】

前記構成データが階層言語で表され、前記構成可能なハードウェア・ライブラリがハードウェア設計言語（HDL）で表されることを特徴とする請求項24に記載の機械可読媒体。

【請求項 26】

前記テストベンチが、各ユニット接続に取り付けられたモデルを含み、前記モデルは、

前記ユニットのパラメータに従って該ユニットとの間でデータを送受信することを特徴とする請求項23に記載の機械可読媒体。

【請求項27】

機械によって実行されるとき、前記機械に、

1つ又はそれ以上の階層レベルからなる構成可能なハードウェア・システム設計階層の第1のレベルにおける1つ又はそれ以上のユニットの組を、前記ハードウェア・システム設計階層の最も低いレベルの1つ又はそれ以上のユニットの組に自動的に分解し、

前記ハードウェア・システム設計階層の各階層レベルのユニットを、前記最も低いレベルから前記第1のレベルまで連続的に個別に検証し、テストベンチが一連のレベルの各々の各ユニットについて動的に構築されるようになる、

ステップを含む動作を実行させる命令を提供し、

前記構成可能なハードウェア・システムが設計作成時にカスタマイズされたことを特徴とする機械可読媒体。

【請求項28】

前記自動的に分解するステップが、構成データ及び構成可能なハードウェア・ライブラリのコンテンツに基づいていることを特徴とする請求項27に記載の機械可読媒体。

【請求項29】

前記構成データが、前記構成可能なハードウェア・システム設計レベルの組の各々のユニットについてのパラメータを指定することを特徴とする請求項28に記載の機械可読媒体。

【請求項30】

前記構成可能なハードウェア・ライブラリが、前記階層レベルの組の各々のユニットを定義することを特徴とする請求項28に記載の機械可読媒体。

【請求項31】

機械によって実行されるとき、前記機械に、

構成データの組を、構成可能なハードウェア・ライブラリから選択された対応する構成可能なユニットの定義にマッピングし、1つ又はそれ以上の構成可能なハードウェア・ユニットの組を生成し、

前記構成データに基づいて、前記構成可能なハードウェア・ユニットの組の各々についてテストベンチを動的に生成し、

対応するテストベンチを用いて前記構成可能なハードウェア・ユニットの組の各々について検証し、

検証された前記構成可能なハードウェア・ユニットの組を構成可能なハードウェア・システム内に統合し、

設計作成環境における機能論理検証の際に、前記構成可能なハードウェア・システムを検証する、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

【請求項32】

前記テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項31に記載の機械可読媒体。

【請求項33】

前記対応する構成可能なユニットの定義がハードウェア設計言語(HDL)で表されることを特徴とする請求項31に記載の機械可読媒体。

【請求項34】

前記構成データがツール制御言語(TCL)で表され、該構成データは、前記構成可能なハードウェア・ユニットの組の各々についてのパラメータを定義することを特徴とする請求項31に記載の機械可読媒体。

【請求項35】

前記テストベンチが前記ユニットの各通信経路に接続されたモデルを含むことを特徴とする請求項31に記載の機械可読媒体。

**【請求項36】**

機械によって実行されるとき、前記機械に、

構成データ及び構成可能なハードウェア・ライブラリに基づいて、より高いレベルの構成可能なハードウェア設計階層からなる構成可能なハードウェア・システムから分解された、より低いレベルの構成可能なハードウェア設計階層からなる個々のユニットについて1つ又はそれ以上のテストベンチの組を構築し、

システム・テストベンチを構築し、

前記個々のユニットを検証した後で前記システムを検証する、

ステップを含む動作を実行させる命令を提供する機械可読媒体。

**【請求項37】**

前記システムは前記システム・テストベンチを用いて検証され、前記個々のユニットは前記テストベンチの組を用いて検証されることを特徴とする請求項36に記載の機械可読媒体。

**【請求項38】**

前記テストベンチの組及び前記システム・テストベンチ上で実行される試験を生成し、

前記試験を実行するためのスクリプトを生成し、

分析ツールへの入力を生成する、

ステップをさらに含むことを特徴とする請求項36に記載の機械可読媒体。

**【請求項39】**

前記構成可能なハードウェア・ライブラリが、前記システム内に含まれる前記ユニットを定義し、前記構成データが該システムのパラメータを指定することを特徴とする請求項36に記載の機械可読媒体。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                            | International application No.<br>PCT/US03/35336   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------|------------------------------------------------------------------------------------|-----------------------|---|----------------------------------------------------------------------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------|------|---|-----------------------------------------------------|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC(7) : G06F 11/30,15/00;G21C 17/00<br>US CL : 702/182<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 702/182 702/57-59,85,117-123,189;714/733,738;716/4,5,7,12,703/23,25;324/763,765                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Please See Continuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left;">Category *</th> <th style="text-align: left;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td>X</td> <td>US 2002/0091979 A1 (Cooke et al.) 11 July 2002, see entire document.</td> <td>1-39</td> </tr> <tr> <td>A</td> <td>Thaker et al., 'Register-Transfer Level Fault Modeling and Test Evaluation Techniques for VLSI Circuits', January 2000, IEEE Publication, pages 940-949.</td> <td>1-39</td> </tr> <tr> <td>A</td> <td>Lin et al., 'A Functional Test Planning System for Validation of DSP Circuits Modeled in VHDL', March 1998, IEEE Publication, pages 172-177.</td> <td>1-39</td> </tr> <tr> <td>A</td> <td>US 5,801,956 A (Kawamura et al.) 01 September 1998.</td> <td>1-39</td> </tr> </tbody> </table> |                                                                                                                                                            |                                                   | Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 2002/0091979 A1 (Cooke et al.) 11 July 2002, see entire document. | 1-39 | A | Thaker et al., 'Register-Transfer Level Fault Modeling and Test Evaluation Techniques for VLSI Circuits', January 2000, IEEE Publication, pages 940-949. | 1-39 | A | Lin et al., 'A Functional Test Planning System for Validation of DSP Circuits Modeled in VHDL', March 1998, IEEE Publication, pages 172-177. | 1-39 | A | US 5,801,956 A (Kawamura et al.) 01 September 1998. | 1-39 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                         | Relevant to claim No.                             |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2002/0091979 A1 (Cooke et al.) 11 July 2002, see entire document.                                                                                       | 1-39                                              |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Thaker et al., 'Register-Transfer Level Fault Modeling and Test Evaluation Techniques for VLSI Circuits', January 2000, IEEE Publication, pages 940-949.   | 1-39                                              |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Lin et al., 'A Functional Test Planning System for Validation of DSP Circuits Modeled in VHDL', March 1998, IEEE Publication, pages 172-177.               | 1-39                                              |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 5,801,956 A (Kawamura et al.) 01 September 1998.                                                                                                        | 1-39                                              |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            | <input type="checkbox"/> See patent family annex. |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubt on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                            |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| Date of the actual completion of the international search<br>12 February 2004 (12.02.2004)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date of mailing of the international search report<br><b>20 FEB 2004</b>                                                                                   |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (703)305-3230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Authorized officer<br><br>Lissi Marquis<br>Telephone No. (703) 308-2260 |                                                   |            |                                                                                    |                       |   |                                                                      |      |   |                                                                                                                                                          |      |   |                                                                                                                                              |      |   |                                                     |      |

Form PCT/ISA/210 (second sheet) (July 1998)

|                                    |                |

|------------------------------------|----------------|

| <b>INTERNATIONAL SEARCH REPORT</b> | PCT/US03/35336 |

|                                    |                |

Continuation of **B. FIELDS SEARCHED** Item 3:

USPAT;US-POPUB;EPO;JPO;DERWENT;IBM\_TDB

HDL,hardware,dardsdrive;test,bench,storage,memory,units,library,file,script,system,vector

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(特許庁注：以下のものは登録商標)

JAVA

(72)発明者 エバート ジェフリー アレン

アメリカ合衆国 カリフォルニア州 94019 ハーフ ムーン ベイ セント ジョセフ アベニュー 415

(72)発明者 ヴェヌゴパラン ラヴィー

アメリカ合衆国 カリフォルニア州 95051 サンタ クララ ホームステッド ロード 3455 #66

(72)発明者 エヴァンズ スコット カールトン

アメリカ合衆国 カリフォルニア州 95051 サンタ クララ ヘイズ アベニュー 252

F ターム(参考) 5B046 AA08 BA02 JA01 KA06