(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년10월06일

(11) 등록번호 10-0985935

(24) 등록일자 2010년09월30일

(51) Int. Cl.

H01L 29/772 (2006.01)

(21) 출원번호 10-2006-7007131

(22) 출원일자(국제출원일자) 2004년10월19일

심사청구일자 2008년01월14일

(85) 번역문제출일자 2006년04월13일

(65) 공개번호 10-2006-0090828

(43) 공개일자 2006년08월16일

(86) 국제출원번호 PCT/US2004/034562

(87) 국제공개번호 WO 2005/043591

국제공개일자 2005년05월12일

(30) 우선권주장

10/689,506 2003년10월20일 미국(US)

(56) 선행기술조사문현

US20050035470 A1\*

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

인터넷 비즈니스 머신즈 코포레이션

미국 10504 뉴욕주 아몬크 뉴오차드 로드

(72) 발명자

치담바라오, 듀레세티

미국, 코네티컷 06883, 웨스턴, 올드 밀 로드 29

도쿠마치, 오며

미국, 뉴욕 12590, 웨이핑거즈 폴즈, 윈쓰롭 코트

32이

첸, 후아지

미국, 코네티컷 06810, 댄버리, 아발론 레이크 로

드 622

(74) 대리인

신영무, 이용미

전체 청구항 수 : 총 10 항

심사관 : 김태훈

(54) Si:C 및 Si:Ge 애피택셜 소스/드레인을 사용하는 고성능의 스트레스 강화 MOSFETs 및 제조 방법

### (57) 요약

반도체 디바이스 및 반도체 디바이스 제조 방법이다. 반도체 디바이스는 pFET 및 nFET용 채널이 포함된다. SiGe 층은 pFET 채널의 소스 및 드레인 영역에서 선택적으로 성장하고, Si:C 층은 nFET 채널의 소스 및 드레인 영역에서 선택적으로 성장한다. SiGe 층 및 Si:Ge 층은 스트레스 성분을 형성하기 위하여 기본적인 Si 층의 격자 네트워크와 일치한다. 일실시예에서, 이는 pFET 채널에서의 압축 성분 및 nFET 채널에서의 인장 성분의 원인이 된다.

대 표 도 - 도1a

## 특허청구의 범위

### 청구항 1

반도체 구조물 제조방법에 있어서,

p형 전계효과트랜지스터(pFET) 채널 및 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계와,

상기 pFET 채널에 pFET 스택을 형성하고 상기 nFET 채널에 nFET 스택을 형성하는 단계와,

상기 pFET 스택과 관련된 소스/드레인 영역에 제1 물질층 -상기 제1 물질층은 상기 pFET 채널 내에 압축 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가지며, 상기 제1 물질층은 상기 nFET 채널 위에 마스크를 배치하고, 상기 pFET 영역을 에칭하고 상기 pFET 채널의 영역내에 상기 제1 물질층을 선택적으로 성장시킴으로써 형성됨- 을 제공하는 단계와,

상기 nFET 스택과 관련된 소스/드레인 영역에 제2 물질층 -상기 제2 물질층은 상기 nFET 채널내에 인장 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가지며, 상기 제2 물질층은 상기 pFET 채널 위에 마스크를 배치하고, 상기 nFET 영역을 에칭하고 상기 nFET 채널의 영역내에 상기 제2 물질층을 선택적으로 성장시킴으로써 형성됨- 을 제공하는 단계와,

상기 pFET 스택의 영역의 에칭 단계 그리고 상기 제1 물질층을 선택적으로 성장시키는 단계 이전에 상기 마스크 아래 및 상기 nFET 스택 위에 보호층을 제공하는 단계와,

상기 nFET 스택의 영역의 에칭 단계 그리고 상기 제2 물질층을 선택적으로 성장시키는 단계 이전에 상기 마스크 아래 및 상기 pFET 스택 위에 보호층을 제공하는 단계

를 포함하는 반도체 구조물 제조 방법.

### 청구항 2

반도체 구조물 제조 방법에 있어서,

p형 전계효과트랜지스터(pFET) 채널 및 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계와,

상기 pFET 채널에 pFET 스택을 형성하고 상기 nFET 채널에 nFET 스택을 형성하는 단계와,

상기 pFET 스택이 형성된 이후, 상기 pFET 스택과 관련된 소스/드레인 영역에 제1 물질층 -상기 제1 물질층은 상기 pFET 채널 내에 압축 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가짐- 을 제공하는 단계와,

상기 nFET 스택이 형성된 이후, 상기 nFET 스택과 관련된 소스/드레인 영역에 제2 물질층 -상기 제2 물질층은 상기 nFET 채널내에 인장 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가짐- 을 제공하는 단계를 포함하며,

상기 제1 물질층은 상기 nFET 채널 위에 마스크를 배치하고 상기 pFET 영역을 에칭하고 상기 pFET 채널의 영역내에 상기 제1 물질층을 선택적으로 성장시킴으로써 형성되며,

상기 제2 물질층은 상기 pFET 채널 위에 마스크를 배치하고 상기 nFET 영역을 에칭하고 상기 nFET 채널의 영역내에 상기 제2 물질층을 선택적으로 성장시킴으로써 형성되며,

상기 제1 물질층 및 제2 물질층 각각은 10에서 100nm 의 두께로 성장되는, 반도체 구조물 제조방법.

### 청구항 3

반도체 구조물 제조방법에 있어서,

p형 전계효과트랜지스터(pFET) 채널 및 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계와,

상기 pFET 채널에 pFET 스택을 형성하고 상기 nFET 채널에 nFET 스택을 형성하는 단계와,

상기 pFET 스택이 형성된 이후, 상기 pFET 스택과 관련된 소스/드레인 영역에 제1 물질층 -상기 제1 물질층은 상기 pFET 채널 내에 압축 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가짐- 을 제공

하는 단계와,

상기 nFET 스택이 형성된 이후, 상기 nFET 스택과 관련된 소스/드레인 영역에 제2 물질층 -상기 제2 물질층은 상기 nFET 채널내에 인장 상태를 형성하도록 상기 기판의 기본 격자 상수와 상이한 격자 상수를 가짐- 을 제공하는 단계를 포함하며,

상기 제1 물질층은 상기 nFET 채널 위에 마스크를 배치하고 상기 pFET 영역을 에칭하고 상기 pFET 채널의 영역 내에 상기 제1 물질층을 선택적으로 성장시킴으로써 형성되며,

상기 제2 물질층은 상기 pFET 채널 위에 마스크를 배치하고 상기 nFET 영역을 에칭하고 상기 nFET 채널의 영역 내에 상기 제2 물질층을 선택적으로 성장시킴으로써 형성되며,

상기 제1 물질층 및 제2 물질층은 상기 기판에 매립되는, 반도체 구조물 제조방법.

#### 청구항 4

반도체 구조물 제조 방법에 있어서,

p형 전계효과트랜지스터(pFET) 채널 및 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계와,

상기 pFET 채널 및 상기 nFET 채널과 각각 관련된 상기 기판 상에 pFET 구조물 및 nFET 구조물을 형성하는 단계 와,

보호층에 의해 덮여진 상기 pFET 구조물 영역 및 상기 nFET 구조물 영역을 에칭하는 단계와,

상기 pFET 스택이 형성되고, pFET 구조물이 보호층에 덮여진 이후에, nFET 구조물을 마스킹하고, 상기 pFET 채널에 압축 스트레스를 제공하기 위하여 상기 pFET 구조물 영역에서 상기 기판의 기본 격자 상수와 상이한 격자 상수를 갖는 제1물질을 형성하는 단계와,

상기 nFET 스택이 형성되고, nFET 구조물이 보호층에 덮여진 이후에, pFET 구조물을 마스킹하고, 상기 nFET 채널에 인장 스트레스를 제공하기 위하여 상기 nFET 구조물 영역에서 상기 기판의 기본 격자 상수와 상이한 격자 상수를 갖는 제2물질을 형성하는 단계와,

상기 nFET 구조물 및 상기 pFET 구조물의 소스 및 드레인 영역을 도핑하는 단계를 포함하는 반도체 구조물 제조 방법.

#### 청구항 5

제4항에 있어서,

상기 제1물질은 SiGe이고 상기 제2물질은 Si:C인 반도체 구조물 제조 방법.

#### 청구항 6

제4항에 있어서,

상기 pFET과 상기 nFET의 상기 소스 및 드레인 영역을 각각 형성하기 위하여 제 위치에서 p형 도핑으로 상기 제1물질을 도핑하고 n형 도핑으로 상기 제2물질을 도핑하는 단계를 더 포함하는 반도체 구조물 제조 방법.

#### 청구항 7

반도체 구조물 제조 방법에 있어서,

p형 전계효과트랜지스터(pFET) 채널 및 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계와,

상기 pFET 채널에 pFET 구조물 및 상기 nFET 채널에 nFET 구조물을 형성하는 단계와,

상기 pFET 스택이 형성된 이후에, 상기 pFET 스택과 관련된 소스/드레인 영역에 상기 pFET 채널에 압축 상태를 형성하기 위하여 상기 기판의 기본 격자 상수와 상이한 격자 상수를 갖는 제1 물질층을 제공하는 단계와,

상기 nFET 스택이 형성된 이후에, 상기 nFET 스택과 관련된 소스/드레인 영역에 상기 nFET 채널에 인장 상태를 형성하기 위하여 상기 기판의 기본 격자 상수와 상이한 격자 상수를 갖는 제2 물질층을 제공하는 단계를 포함하고,

여기서 제1 물질층은 nFET 스택 위에 마스크를 배치하고, 상기 pFET의 영역을 에칭하고, pFET 채널의 영역 내에서 제1 물질층을 선택적으로 성장시키고,

여기서 제2 물질층은 pFET 스택 위에 마스크를 배치하고, 상기 nFET의 영역을 에칭하고, nFET 채널의 영역 내에서 제2 물질층을 선택적으로 성장시키는 반도체 구조물 제조 방법.

#### 청구항 8

반도체 구조물에 있어서,

기판에 형성된 p형 전계효과트랜지스터(pFET) 채널과,

상기 기판에 형성된 n형 전계효과트랜지스터(nFET) 채널과,

상기 기판의 격자 상수와 상이한 격자 상수를 갖는 pFET 채널의 소스 및 드레인 영역의 제1 물질층과,

상기 기판의 격자 상수와 상이한 격자 상수를 갖는 nFET 채널의 소스 및 드레인 영역의 제2 물질층을 포함하는 반도체 구조물.

#### 청구항 9

제8항에 있어서,

상기 제1물질층은 SiGe이고 상기 제2물질층은 Si:C인 반도체 구조물.

#### 청구항 10

제8항에 있어서,

상기 제1물질층 및 상기 제2물질층은 상기 pFET 채널 및 상기 nFET 채널에 각각 상이한 유형의 스트레스를 형성하는 반도체 구조물.

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

## 명세서

### 기술 분야

[0001] 본 발명은 반도체 디바이스 및 제조방법에 관한 것이고, 특히 디바이스를 제조하는 동안 인장(tensile) 스트레스와 압축(compressive) 스트레스를 상기 디바이스에 부과하는 반도체 디바이스 및 제조방법에 관한 것이다.

### 배경기술

[0002] 반도체 디바이스 기판 내의 기계적인 스트레스는 디바이스 성능을 좌우할 수 있다. 즉 반도체 디바이스 내의 스트레스는 반도체 디바이스 특성을 강화시키는 것으로 알려져 있다. 따라서 반도체 디바이스의 특성을 향상시키기 위하여, 인장 스트레스 및/또는 압축 스트레스는 n형 디바이스(예를 들면 NFETs) 및/또는 p형 디바이스(예를 들면 PFETs)의 채널에 형성된다. 그러나 동일한 스트레스 성분, 인장 스트레스 또는 압축 스트레스는 n형 디바이스와 p형 디바이스의 특성에 상이한 영향을 준다.

[0003] 예를 들어 디바이스는, 실리콘 기판의 상부에서 이완되는 다른 애피택셜 성장형 SiGe 층 상에서 애피택셜하게 성장하는 실리콘 층(또는 캡)에 형성될 때 더욱 향상된 성능 특성을 나타낸다는 것이 공지되어 있다. 이러한 시스템에서 실리콘 캡은 쌍축 인장 변형(biaxial tensile strain)을 경험한다. 실리콘 상에서 애피택셜하게 성장할 때, 비이완된 SiGe 층은 상기 실리콘 기판의 격자 상수에 따른 격자 상수를 가질 것이다. (예를 들어 고온 프로세스를 통한) 이완시에, SiGe 격자 상수는 실리콘의 격자 상수보다 큰 고유 격자 상수에 근접한다. 완전히 이완된 SiGe 층은 그의 고유값에 근접한 격자 상수를 갖는다. 실리콘 층이 애피택셜하게 성장할 때, 실리콘 층은 이완된 SiGe 층의 더 큰 격자 상수에 따르고, 이것은 물리적인 쌍축 스트레스(예를 들면 팽창)를 그 위에 형성된 실리콘 층에 인가한다. 팽창된 실리콘 층이 N형 디바이스 성능을 향상시키고 SiGe 층에서의 더 높은 Ge 농도가 P형 디바이스의 성능을 향상시키기 때문에, 실리콘 층에 인가된 이러한 물리적인 스트레스는 그 위에 형성된 디바이스(예를 들면 CMOS 디바이스)에 유익하다.

[0004] 실리콘 기판상의 SiGe의 이완은 부정합 전위(misfit dislocation)의 형성을 통해 발생한다. 완전히 이완된 기판의 경우에, 동일하게 이격된 부정합 전위의 그리드(grid)가 스트레스를 경감시키는 것을 생각할 수 있다. 부정합 전위는 실리콘의 엑스트라 하프 평면(extra half-planes)을 기판에 제공함으로써 SiGe 층의 격자 상수가 고유한 값을 찾는 것을 용이하게 한다. 이 때 SiGe/실리콘 계면을 가로지르는 부정합 변형은 축적되고 SiGe 격자 상수는 점점 더 커지게 된다.

[0005] 그러나 이러한 종래의 접근법과 관련된 문제점은, 전위가 SiGe 층 및 실리콘 기판 층 사이로 침투(threading)하는 것을 방지하면서 표면부에 부정합 전위를 달성하기 위하여 매우 두꺼운(예를 들면 약 5000Å 내지 15000Å의 두께인) 다층 SiGe 버퍼 층을 필요로 하고, 그에 의해 다층 SiGe 층의 표면상에 이완된 SiGe 구조를 달성한다는 것이다. 또한 이러한 접근법은 제조 시간과 제조 비용을 상당히 증가시킨다. 게다가 두꺼운 경사형 SiGe 버퍼 층(graded SiGe buffer layer)은 SOI(silicon-on-insulator) 기판에 용이하게 적용할 수 없다. 이는 SOI의 경우에, SOI의 이점을 유효화시키기 위하여 실리콘 두께가 1500Å 이하여야 하기 때문이다. SiGe 버퍼층 구조는 너무 두껍다.

[0006] 다른 문제점은 SiGe 층과 실리콘 애피택셜 층 사이에 형성된 부정합 전위가 일정하지 않고 상당히 불균일하며 용이하게 제어할 수 없는 불균질 핵생성(heterogeneous nucleation)으로 인하여 용이하게 제어될 수 없다는 것이다. 또한, 부정합 전위 밀도는 부분별로 상당히 다르다. 따라서 불균일한 부정합 전위로 야기된 물리적 스트레스는 실리콘 애피택셜 층에서 상당히 불균일한 경향이 있고, 이러한 불균일 스트레스는 불균일한 성능을 야기하고 가변성(variability)을 더 크게 한다. 게다가 부정합 밀도가 높은 위치들에서, 결함은 디바이스 터미널의

단락 및 다른 현저한 누설 메커니즘을 통해 디바이스 성능을 떨어뜨린다.

[0007] 고유한 신장력이 있는 Si 상에서 Si:C 가 에파택셜하게 성장하는 것은 알려져 있다. Si:C/Si 물질 스택(stack)에서 1% C 함량은 Si:C에서 인장 스트레스 레벨이 500MPa 수준으로 되는 원인이 된다. 비교해 보면, SiGe/Si 시스템에서 약 6% Ge는 500MPa 압축을 야기시키기 위하여 필요하다. 이러한 1% 수준의 C는, Ernst 등이 저술한 VLSI 2002, p92에 나타난 바와 같이, 에파택셜 성장 동안 Si로 합체될 수 있다. Ernst 등의 논문에서, nFETs용 Si/Si:C/Si 층으로 이루어진 채널이 도시되어 있다. 그러나 Ernst 등의 구조물에서, 종래의 변형 Si 접근법에서는, Si:C는 채널에서 층들의 스택(stack)으로 제공된다. 따라서 Ernst 등의 구조물에서, Si:C는 그 자신이 채널의 일부로서 사용된다. 이러한 접근법의 문제점은 이동성이 향상되지 않고 스캐터링(scattering)으로 인한 C 함량에 따라 저해된다는 점이다.

### 발명의 상세한 설명

[0008] 본 발명의 제1특징에서, 반도체 구조물을 제조하는 방법은 p형 전계효과트랜지스터(pFET) 채널과 n형 전계효과트랜지스터(nFET) 채널을 기판에 형성하는 단계를 포함한다. pFET 스택과 nFET 스택은 각각의 채널과 관련된 기판에 형성된다. 제1물질층은 pFET 스택과 관련된 소스/드레인 영역에 제공된다. 제1물질층은 압축 상태를 pFET 채널 내에서 형성하도록 기판의 기본 격자 상수와 상이한 격자 상수를 갖는다. 제2물질층은 nFET 스택과 관련된 소스/드레인 영역에 제공된다. 제2물질층은 인장 상태를 nFET 채널에 형성하도록 기판의 기본 상수 격자와 상이한 격자 상수를 갖는다.

[0009] 본 발명의 다른 특징에서, pFET 채널과 nFET 채널을 기판에 형성하는 단계를 포함하는 반도체 구조물 제조 방법이 제공된다. pFET 구조물 및 nFET 구조물은 pFET 채널 및 nFET 채널과 각각 관련되는 기판상에 형성된다. pFET 구조물 및 nFET 구조물의 영역은 소정 깊이로 식각된다. 상기 층의 기본 격자 상수와 상이한 격자 상수를 갖는 제1물질은 압축 스트레스를 pFET 채널에 제공하도록 pFET 구조물의 식각된 영역에 제공된다. 상기 층의 기본 격자 상수와 상이한 격자 상수를 갖는 제2물질은 인장 스트레스를 nFET 채널에 제공하도록 nFET 구조물의 식각된 영역에 제공된다. nFET 구조물 및 pFET 구조물의 소스 및 드레인 영역을 도핑하는 단계가 제공된다.

[0010] 본 발명의 다른 특징에서, 반도체 구조물은 반도체 기판을 포함하고, pFET 및 nFET는 상기 기판에서 각각의 채널에 형성된다. pFET 채널의 소스 및 드레인 영역에서 제1물질층은 기판의 격자 상수와 상이한 격자 상수를 갖는다. nFET 채널의 소스 및 드레인 영역에서 제2물질층은 기판의 격자 상수와 상이한 격자상수를 갖는다.

### 실시 예

[0014] 본 발명은 CMOS 디바이스의 nFET 채널 부근에 인장 스트레스를 제공하고 pFET 채널 부근에 압축 스트레스를 제공하는 반도체 디바이스 및 제조방법에 관한 것이다. 본 발명의 일실시예에서, 압축 스트레스는 pFET 채널에 상당히 근접하여 발생하는 동시에 세로방향의 인장 스트레스는 nFET 채널에 상당히 근접하여 발생한다. 부가적으로, 본 발명에 있어서 프로세스 및 구조물은 SiGe 및 Si:C 재료 양쪽을 CMOS 기술에 통합하기 위하여 제공된다.

[0015] 예를 들면 고인장성 Si:C 박막은 게이트 영역 하의 채널에서 nFET 구조물에 장력을 세로 방향으로 인가하도록 소스/드레인(S/D) 영역의 실리콘 기판에 제공된다(예를 들면 매립(embedded)된다). 마찬가지로 높은 고압축성 SiGe 박막은 게이트 영역 하의 채널에서 pFET에 압축력을 세로 방향으로 인가하도록 S/D 영역의 실리콘 기판에 제공된다(예를 들면 매립된다). SiGe 층과 유사하게, Si:C 층은 비교적 얇고(임계 두께 이하) 이완되지 않는다. nFET의 트랜지스터 채널영역은 Si:C 층으로부터 스트레스에 의해 변형되지만, pFET의 채널 영역은 SiGe으로부터 압축 스트레스가 제공된다.

[0016] SiGe 층은 pFET의 S/D 영역에 매립되기 때문에, 저 저항 실리사이드가 여전히 형성될 수 있다. 흥미롭게도 매립된(예를 들면 하부 표면 또는 동일평면상의 표면의) Si:C 박막은 박막 표면이 자유롭지 않기 때문에 상부 표면의 Si:C 대응부보다 더 큰 스트레스를 부과할 수 있다. 본 발명에서는, 매립되거나 또는 표면과 동일 평면이거나 또는 용기되었거나, Si:C의 상이한 두께와 돌출부(protrusions)가 고려될 수 있다. SiGe 층에서 Ge조성의 농도를 조정함으로써, pFET 채널에서 압축 스트레스를 조정 가능하다는 점은 이해될 수 있다. 유사하게 Si:C 층에서 C의 농도를 조정함으로써 nFET에서 인장 스트레스를 조정하는 것이 가능하다. 이것은 이러한 물질들의 격자 상수에 기인한다.

[0017] 본 발명에서 Si:C는 적당한 스트레스를 갖고, C 조성의 적당한 양을 포함하며, 에파택셜하고 선택적으로 성장할 수 있다는 것을 알 수 있다. 또한 본 발명에서 Si:C는 채널 하부에서 직접 구축되는 스택층으로서 이용되지는 않지만, 장력을 갖고 따라서 채널 영역에서 장력을 부과하는 nFET S/D 영역을 위한 대체 물질로서 사용될 수 있

다. 따라서 이러한 Si:C 박막은, SiGe가 pFET 채널에 압축 스트레스를 인가하는 반면 nFET 채널에 인장 스트레스를 인가한다.

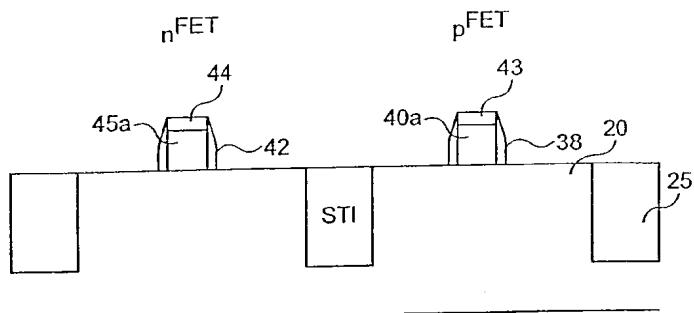

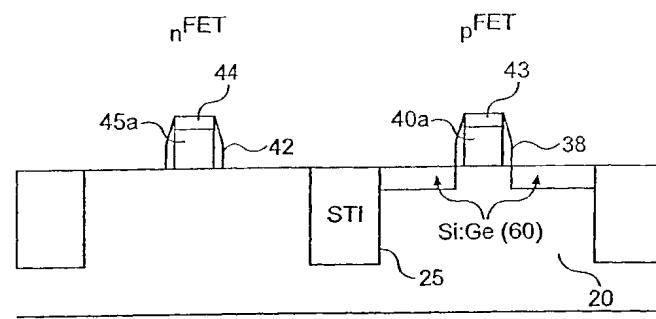

[0018] 도 1a 내지 도 1e는 본 발명의 실시예에 따라서 디바이스를 형성하기 위한 제조 프로세스를 나타낸다. 도 1a에서, SOI(20) 등이 제공된다. 층(20)은, 예를 들면 패드 산화(pad oxidation), 패드 질화 증착(pad nitride deposition), 리소그라피 기반 패턴(lithography based patterning), 배몰 산화층(buried oxide)까지 하방으로 질소, 산소 및 하부의 실리콘으로 구성된 스택의 활성이온식각(reactive ion etching; RIE), 에지 산화(edge oxidation), 선형 증착(linear deposition), 필 증착(fill deposition) 및 화학기계적 연마(chemical mechanical polish)의 일반적인 기술을 이용하여 STI(shallow trench isolation) 형상(25)을 형성하도록 패턴된다. STI 형성 프로세스는 기술 분야에서 잘 알려져 있다. 이 후에, 상기 패드 질화물은 제거된다. 예를 들어 게이트 유전체 및 폴리 실리콘(poly silicon)을 포함하는 게이트 스택은 잘 알려진 방법을 통해 상기 구조물에 형성되어 pFET 및 nFET를 형성한다. TEOS 캡(43, 44)에는 주지의 방법으로 pFET 및 nFET이 형성된다.

[0019] 도 1a를 계속 참조하면, 스페이서(spacer)는 잘 알려진 임의의 프로세스를 사용하여 pFET 스택 및 nFET 스택에 각각 형성된다. 예를 들면 스페이서(38)는 pFET 스택(40a)의 측벽에 형성되고, 스페이서(42)는 nFET 스택(45a)의 측벽에 형성된다. 상기 스페이서는 예를 들면 산화물 스페이서 또는 질화물 스페이서일 수 있다.

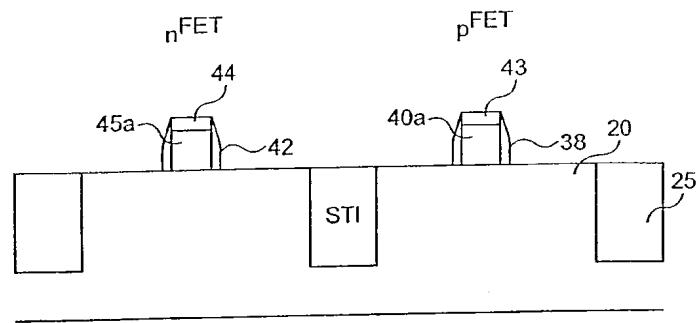

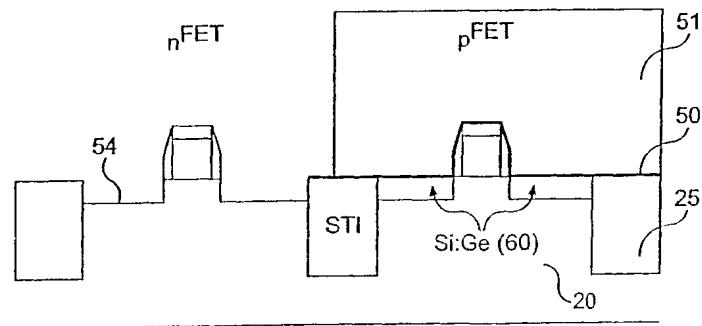

[0020] 도 1b에서, 박형 라이너(thin liner; 50)는 예를 들면 pFET 스택, nFET 스택 및 이들의 S/D 영역을 포함하는 구조물의 상부에 블랭킷 증착된다. 일실시예에서 박형 라이너(50)는  $\text{Si}_3\text{N}_4$  라이너 또는 하드 마스크(hard mask)의 물질에 따른 임의의 질화물 또는 산화물 기반 재료이다. 상기 박형 라이너의 두께 범위는 약 5 내지 20nm이다. 박형 라이너(50)는 보호층으로서 역할을 할 수 있다. 이후에, 하드 마스크(51)는 nFET 스택(45a) 및 그것의 S/D 영역의 상부에 형성된다.

[0021] pFET 스택(40a) 부근의 영역은 라이너(50)까지 식각된다. 이후에, 라이너(50)는 식각되고, S/D 영역(52)은 스택(40a) 부근에 형성(식각)된다. S/D 영역(52)의 깊이는 상기 SOI 층의 두께에 따라 약 20 내지 100nm이다. 고압 축성 선택적 애피택셜 SiGe 층(60)은, 도 1c에 나타난 바와 같이 pFET 스택(40a)의 영역(52)에서 성장하여 S/D 식각 영역(52)을 완전히 채운다. SiGe 층(60)은 비록 본 발명에 의해 다른 두께가 예측가능하지만, 약 10 내지 100nm 두께로 성장할 수 있다. 일실시예에서 상기 SiGe층은 상기 게이트 산화층의 표면 이상의 두께로 성장된다. 상기 하드 마스크 및 상기 라이너의 잔여부는, 예를 들면 습식 케미칼(wet chemical)과 같은 주지의 프로세스를 사용하여 제거된다. 프로세스 단계 중에 도판트(dopant)는 상기 하드 마스크를 제거하기에 앞서 pFET 스택(40a) 부근의 상기 S/D 영역을 형성하도록 이온 주입된다.

[0022] 독립적으로 상기 SiGe는 통상적으로 상기 SOI보다 더 큰 격자 상수를 갖는다. 즉 상기 SiGe 물질의 격자 상수는 Si의 격자 상수와 일치하지 않는다. 그러나 본 발명에 따른 구조물에서, 상기 SiGe 층의 성장으로 인하여 상기 SiGe 층의 격자 구조는 하부에 있는 Si의 격자 구조와 일치하는 경향이 있을 것이다. 이로 인하여 상기 SiGe 층 및 상기 SiGe 부근의 채널 영역은 압축상태에 있게 된다. 일실시예에서, 상기 SiGe층의 Ge 조성은 Si 조성에 대한 0% 이상의 비율보다 높을 수 있다.

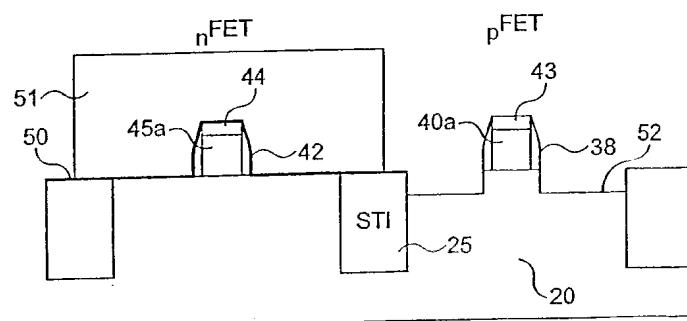

[0023] 계속하여 본 발명의 프로세스를 참조하면, 도 1d에서, 박형 라이너(50)는, 예를 들면 nFET, pFET 및 이들의 S/D 영역을 포함하는 구조물 위에 다시 블랭킷 증착된다. 일실시예에서, 박형 라이너(50)는  $\text{Si}_3\text{N}_4$  라이너 또는 하드 마스크 물질에 따른 임의의 질화물 또는 산화물 물질이다. 상기 박형 라이너의 두께 범위는 약 5 내지 20nm이다. 박형 라이너(50)는 보호층으로서 역할을 할 수 있다.

[0024] 이후에, 마스크(51)는 pFET 스택(40a) 위에 형성되고, nFET 스택(45a) 부근의 영역은 라이너(50)까지 식각된다. 그리고 상기 라이너는 식각되고, S/D 영역(54)은 스택(45a) 부근에 형성(식각)된다. S/D 영역(54)의 깊이는 상기 SOI 층의 두께에 따라서 약 20 내지 100nm이다. 잘 알려진 임의의 프로세스가 영역(54)을 식각하기 위하여 사용될 수 있다.

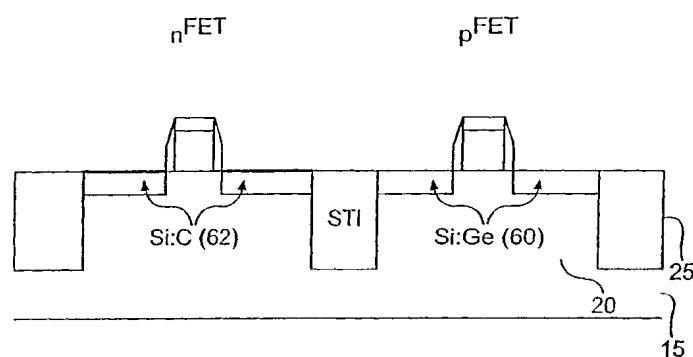

[0025] 고인장성 선택적 애피택셜 Si:C 층은 도 1e에 나타난 바와 같이 nFET 스택(45a)의 영역(45)에서 약 10 내지 100nm 두께로 성장한다. 본 발명에 의해 예측할 수 있는 바와 같이, Si:C 층(62)은 다른 두께로 애피택셜하게 성장할 수 있다. 일실시예에서 C 조성은 Si 조성에 대한 비율로써 0% 내지 4% 일 수 있다. 상기 박형 라이너의 저항부 및 잔여부는, 예를 들면 습식 케미칼을 사용하는 것과 같이 잘 알려진 임의의 프로세스를 사용하여 제거된다.

[0026] 독립적으로 Si:C는 통상적으로 하부에 있는 Si보다 더 작은 격자 상수를 가질 수 있다. 즉 Si:C 물질의 격자 상

수는 Si의 격자 상수와 일치하지 않는다. 그러나 본 발명에 따른 구조물에서, nFET 스택(45a)의 S/D 영역 내에서 Si:C 층의 성장으로 인하여, Si:C 층의 격자 구조는 기본적인 Si의 격자 구조와 일치하려는 경향이 있을 것이다. 이로 인하여 Si:C 층 및 상기 Si:C의 부근의 채널 영역은 인장 스트레스 하에 있게 된다.

[0027] 일실시예에서 상기 Si:C 층 및/또는 SiGe 층은 이러한 층을 리세스(recess)하는 프로세싱 최적화를 위해서, 예를 들면 RIE, 습식 또는 다른 프로세스 또는 이들의 결합에 의해 디바이스 내에 내장될 수 있다. 그리고 Si는 임의의 잘 알려진 프로세스를 사용하여 영역(52, 54) 위에서 선택적으로 성장된다. 이 후에, 소스 및 드레인 임플란팅(source and drain implanting)은 잘 알려진 임의의 프로세스를 이용하여 수행될 수 있다. 다른 프로세스는 디바이스 및 상호연결을 수립하도록 수행될 수 있다.

[0028] 이제 알 수 있는 바와 같이, Si:C 층 및 SiGe 층 양쪽은 디바이스 내에서 내장될 수 있거나 디바이스와 동일 평면이거나 디바이스로부터 융기될 수 있다. 일실시예에서 Si:C 박막 및 SiGe 박막은 10 nm 내지 100nm 두께까지 증착되어, 스트레스(압축 또는 인장)를 MOSFETs에 인가하기 위한 더욱 비용효율적인 방법을 제공한다. 융기되는 실시예에서, Si:C 층 및 SiGe 층은 디바이스의 표면 위로 약 50nm 까지 융기될 수 있다. 또한 다른 두께가 본 발명에 의해 예측되는 것이 인식될 수 있다.

[0029] 또한 pFET 및 nFET의 소스 및 드레인 영역을 각각 형성하기 위하여, 제 위치에서 p형 도핑으로는 SiGe를 도핑하고 n형 도핑으로 Si:C를 도핑하는 것이 또한 가능하다.

[0030] 도 1d 및 도 1e의 프로세스 단계는 도 1b 및 도 1c에 나타난 프로세스 단계에 앞서 동일하게 수행될 수 있다는 것은 기술 분야에서 당업자에 의해 또한 이해되어야 한다. 또한 예를 들면 스탠다드 이온 주입법(standard ion implantation)과 같은, 다른 프로세스 단계는 pFET 및 nFET의 S/D 영역을 형성하도록 수행될 수 있다. 이온 주입법을 통한 S/D 영역의 형성은, 프로세스 동안 마스크로서 작용하는 nFET 영역 및 pFET 영역의 게이트 산화층으로 인하여 자가 정렬한다.

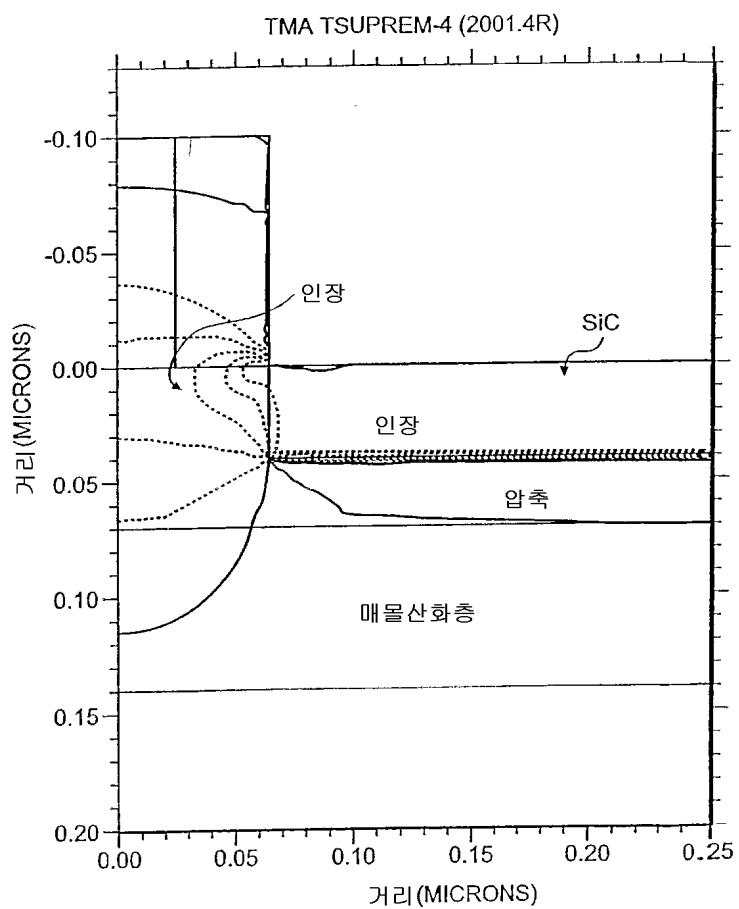

[0031] 도 2는 본 발명에 따른 nFET 디바이스에서 스트레스의 위치를 도시한다. 도 2에 나타난 바와 같이 압축 스트레스는 비이완된 SiGe의 영역을 갖는 pFET 바로 밑에서 나타난다. 더욱 자세하게는 본 발명에 따른 구조물에서, SiGe 층의 격자 구조는 하부에 있는 Si 절연층의 격자 구조와 일치한다. 이로 인하여 SiGe층 및 주변부가 압축 스트레스 하에 있게 된다.

[0032] 도 3은 본 발명에 따른 nFET 디바이스에서 스트레스의 위치를 도시한다. 도 3에 나타난 바와 같이, 인장 스트레스는 nFET의 채널에서 나타난다. 더욱 자세하게는 본 발명에 따른 구조물에서, Si:C 층의 격자 구조는 nFET 채널에서 인장 스트레스 요소를 형성하기 위하여 하부에 있는 Si 절연층(20)의 격자 구조와 일치할 것이다.

### 산업상 이용 가능성

[0033] 본 발명은 실시예로서 설명되었지만, 기술 분야의 당업자들은, 본 발명이 첨부된 청구항의 사상과 요지 내에서 변경될 수 있음을 알 수 있을 것이다. 예를 들면, 본 발명은 벌크(bulk) 구조물에 용이하게 적용될 수 있다.

### 도면의 간단한 설명

[0011] 도 1a 내지 도 1e는 본 발명에 따라서 디바이스를 형성하는 제조 프로세스를 나타낸다.

[0012] 도 2는 본 발명에 따른 pFET 디바이스에서 스트레스의 위치를 도시한다.

[0013] 도 3은 본 발명에 따른 nFET 디바이스에서 스트레스의 위치를 도시한다.

## 도면

## 도면1a

## 도면1b

## 도면1c

도면1d

도면1e

도면2

## 도면3