(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-73044

(P2016-73044A)

(43) 公開日 平成28年5月9日(2016.5.9)

| (51) Int.Cl.                  | F 1                          | テーマコード (参考)                                                  |

|-------------------------------|------------------------------|--------------------------------------------------------------|

| HO2J 7/00 (2006.01)           | HO2J 7/00                    | B 5G503                                                      |

| HO2J 7/02 (2016.01)           | HO2J 7/00                    | 302B                                                         |

| HO2J 7/10 (2006.01)           | HO2J 7/02                    | H                                                            |

|                               | HO2J 7/10                    | B                                                            |

|                               | HO2J 7/10                    | Z                                                            |

| 審査請求 未請求 請求項の数 5 O L (全 12 頁) |                              |                                                              |

| (21) 出願番号                     | 特願2014-198293 (P2014-198293) | (71) 出願人 395011665<br>株式会社オートネットワーク技術研究所<br>三重県四日市市西末広町1番14号 |

| (22) 出願日                      | 平成26年9月29日 (2014.9.29)       | (71) 出願人 000183406<br>住友電装株式会社<br>三重県四日市市西末広町1番14号           |

|                               |                              | (71) 出願人 000002130<br>住友電気工業株式会社<br>大阪府大阪市中央区北浜四丁目5番33号      |

|                               |                              | (74) 代理人 100088672<br>弁理士 吉竹 英俊                              |

|                               |                              | (74) 代理人 100088845<br>弁理士 有田 貴弘                              |

最終頁に続く

(54) 【発明の名称】充放電制御回路

## (57) 【要約】

【課題】直列に接続された複数のキャパシタを全て有効に活用しつつ、環境温度に応じてキャパシタユニットが保持する電圧を制御する。

【解決手段】キャパシタユニットへの充電経路に介挿されたスイッチ素子8と、スイッチ素子の開閉を制御するスイッチ制御部9などが設けられる。スイッチ制御部9は、キャパシタユニットが保持する電圧V4を分圧して出力する一対の抵抗素子Rth, R1を有する第1分圧回路92と、第1分圧回路92から出力される電位V40と所定電位Vref1とを比較した結果に基づいてスイッチ素子8の開閉を制御する比較結果出力回路91とを含む。抵抗素子Rth, R1のそれぞれの抵抗値の温度依存性は相互に異なる。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

互いに直列に接続された複数のキャパシタを有するキャパシタユニットを充放電する充放電制御回路であって、

前記キャパシタの放電を個別に制御する放電制御回路と、

前記キャパシタユニットの充電を前記キャパシタの全てを一括して制御する充電制御回路と

を備え、

前記充電制御回路は、

前記キャパシタユニットへの充電経路に介挿されたスイッチ素子と、

前記スイッチ素子の開閉を制御するスイッチ制御部と

を有し、

前記スイッチ制御部は、

前記キャパシタユニットが保持する電圧を分圧して出力する一対の抵抗素子を有する第1分圧回路と、

前記第1分圧回路から出力される電位と所定電位とを比較した結果に基づいて前記スイッチ素子の開閉を制御する比較結果出力回路と

を含み、

前記一対の抵抗素子のそれぞれの抵抗値の温度依存性は相互に異なる、充放電制御回路

。

10

20

30

**【請求項 2】**

請求項1に記載の充放電制御回路であって、

前記放電制御回路は、

前記複数のキャパシタの各々が保持する電圧を、同一の閾値と比較して、前記複数のキャパシタの各々の放電を個別に制御する、複数の放電部と、

前記キャパシタユニットが保持する前記電圧を、前記キャパシタユニットにおいて直列に接続される前記キャパシタの個数で除した値に分圧して前記閾値として出力する第2分圧回路と

を有する、充放電制御回路。

**【請求項 3】**

請求項1又は請求項2に記載の充放電制御回路であって、

前記所定電位は正值であり、

前記一対の抵抗素子のうち、前記キャパシタユニットの高電位側に接続される第1の抵抗素子の抵抗値は第1の温度係数を有し、

前記一対の抵抗素子のうち、前記キャパシタユニットの低電位側に接続される第2の抵抗素子の抵抗値は前記第1の温度係数よりも高い第2の温度係数を有し、

比較結果出力回路は、前記第1分圧回路から出力された前記電位が前記所定電位を越えることによって前記スイッチ素子を非導通とする、充放電制御回路。

**【請求項 4】**

請求項3に記載の充放電制御回路であって、

前記第1の温度係数は負の温度係数であり、前記第2の温度係数は正の温度係数である、充放電制御回路。

40

**【請求項 5】**

請求項3又は請求項4に記載の充放電制御回路であって、

前記第1分圧回路は、

前記第1の抵抗素子に対して並列に接続され、前記第1の温度係数よりも高い第3の温度係数を有する第3の抵抗素子

を更に有する、充放電制御回路。

**【発明の詳細な説明】****【技術分野】**

50

## 【0001】

この発明は、放電制御回路に関し、例えばキャパシタを用いたサブバッテリ回路を充放電する技術に適用される。

## 【背景技術】

## 【0002】

近年、燃費を上げるためにハイブリッドカーや電気自動車の開発が進んでいる。ガソリン車においてもアイドリングストップ等を実施し、燃費向上が望まれている。

## 【0003】

しかしアイドリングストップ等で一旦エンジンが停止すると、オルタネータによるバッテリの充電が行われなくなる。このため、再度エンジンを点火する際には、バッテリ電圧が急激に低下する、「クランкиング」と呼ばれる現象が発生する。10

## 【0004】

クランкиングが発生してバッテリ電圧が急激に低下すると、自動車のボディECU（電子制御ユニット）が誤って低電圧リセットを掛けてしまう恐れがある。

## 【0005】

このような事態を回避するため、バッテリとは別に、大容量キャパシタなどのサブバッテリを備え、クランкиングに対応する技術が周知である。

## 【0006】

このサブバッテリは例えば、クランкиング対策の他、車両が衝突した際にバッテリが喪失したときの、ドアロック解除用の補助電源としても採用される。20

## 【0007】

サブバッテリで使用されるキャパシタは経年劣化により、静電容量の低下、内部抵抗の上昇が発生する。この経年劣化の進行は一般的にアレニウス則として知られており、環境温度については10~2倍則に従う。

## 【0008】

また、キャパシタの劣化の進行には充電電圧も影響を与える。環境温度が一定であれば、充電電圧が低いほど、劣化しにくい。

## 【0009】

このようなキャパシタを用いたサブバッテリ回路で、キャパシタの劣化を抑制し、環境温度の変化に対応して必要なエネルギーを供給する技術が、下掲の特許文献1に例示されている。30

## 【0010】

具体的には、下掲の特許文献1には、

- (i)主電源たるバッテリから補助電源たるキャパシタユニットへの充電：

- (ii)キャパシタユニットを構成する複数のキャパシタの一部の充電停止：

- (iii)上記(ii)の充電停止、及び充電の再開の判断は、キャパシタユニット近傍の温度に依拠する：

- が記載されている。

## 【0011】

そして上記(i)~(iii)の制御により、環境温度が高いときにはキャパシタユニットへの充電電圧を低くし、以てキャパシタの劣化を抑えつつキャパシタユニットが給電するエネルギーが確保される。40

## 【0012】

また、特許文献2には、組電池を構成する複数の電池毎にバイパス回路を設ける技術が紹介されている。そしてある電池が所定の充電電位を越えた場合に、当該電池に対応するバイパス回路を導通させ、電池同士の充電電圧の不均等が低減されている。

## 【先行技術文献】

## 【特許文献】

## 【0013】

【特許文献1】特開2008-5662号公報

10

20

30

40

50

【特許文献 2】特開平 8 - 19188 号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかし、特許文献 1 に紹介された技術では、(ii)で示されるように、一部のキャパシタが充電されるか否かという段階的な制御が行われる。これは(iii)で示される温度に依拠した制御が容易ではない。換言すると充電の停止 / 再開を設定する温度閾値の設定が難しい。しかも、環境温度が高いときに給電に寄与しないキャパシタが存在することは、キャパシタユニットに設けられたキャパシタを有効に使用できていないことになり、コスト的に不利となる。

10

【0015】

また、特許文献 2 に紹介された技術では、充電する電圧は一意にしか決定できず、温度による充電電圧の変化を行うことは示唆されていない。

【0016】

そこで、本発明は、直列に接続された複数のキャパシタを全て有効に活用しつつ、環境温度に応じてキャパシタユニットが保持する電圧を制御する技術を提供することを目的とする。

【課題を解決するための手段】

【0017】

第 1 の態様は、互いに直列に接続された複数のキャパシタを有するキャパシタユニットを充放電する充放電制御回路である。そして前記キャパシタの放電を個別に制御する放電制御回路と、前記キャパシタユニットの充電を前記キャパシタの全てを一括して制御する充電制御回路とを備える。前記充電制御回路は、前記キャパシタユニットへの充電経路に介挿されたスイッチ素子と、前記スイッチ素子の開閉を制御するスイッチ制御部とを有する。前記スイッチ制御部は、前記キャパシタユニットが保持する電圧を分圧して出力する一対の抵抗素子を有する第 1 分圧回路と、前記第 1 分圧回路から出力される電位と所定電位とを比較した結果に基づいて前記スイッチ素子の開閉を制御する比較結果出力回路とを含む。前記一対の抵抗素子のそれぞれの抵抗値の温度依存性は相互に異なる。

20

【0018】

第 2 の態様は第 1 の態様に係る放電制御回路であって、前記放電制御回路は、前記複数のキャパシタの各々が保持する電圧を、同一の閾値と比較して、前記複数のキャパシタの各々の放電を個別に制御する、複数の放電部と、前記キャパシタユニットが保持する前記電圧を、前記キャパシタユニットにおいて直列に接続される前記キャパシタの個数で除した値に分圧して前記閾値として出力する第 2 分圧回路とを有する。

30

【0019】

第 3 の態様は第 1 の態様又は第 2 の態様に係る放電制御回路であって、前記所定電位は正值であり、前記一対の抵抗素子のうち、前記キャパシタユニットの高電位側に接続される第 1 の抵抗素子の抵抗値は第 1 の温度係数を有し、前記一対の抵抗素子のうち、前記キャパシタユニットの低電位側に接続される第 2 の抵抗素子の抵抗値は前記第 1 の温度係数よりも高い第 2 の温度係数を有し、比較結果出力回路は、前記第 1 分圧回路から出力された前記電位が前記所定電位を越えることによって前記スイッチ素子を非導通とする。

40

【0020】

第 4 の態様は第 3 の態様に係る放電制御回路であって、前記第 1 の温度係数は負の温度係数であり、前記第 2 の温度係数は正の温度係数である。

【0021】

第 5 の態様は第 3 の態様又は第 4 の態様に係る放電制御回路であって、前記第 1 分圧回路は、前記第 1 の抵抗素子に対して並列に接続され、前記第 1 の温度係数よりも高い第 3 の温度係数を有する第 3 の抵抗素子を更に有する。

【発明の効果】

【0022】

50

第1の態様によると、キャパシタユニットの電圧が温度を考慮した電圧に変換されて比較結果出力回路に与えられる。これにより、キャパシタの全てについて、温度を考慮した充電が行われ、以てキャパシタユニットが保持する電圧は環境温度に応じて制御される。しかも直列に接続されたキャパシタの全てが利用される。

#### 【0023】

第2の態様によると、キャパシタユニットを構成して直列に接続される複数のキャパシタ同士の充電電圧を均等化し、充電電圧の不均一による劣化を抑制する。

#### 【0024】

第3の態様によると、キャパシタユニットの電圧は環境温度が高いほど高い電圧へ分圧される。よって、環境温度が高いほど、低いキャパシタユニットの電圧でスイッチ素子が非導通となり、以てキャパシタの各々が保持する電圧を低く設定できる。

10

#### 【0025】

第4の態様によると、第3の態様における第1の抵抗素子と第2の抵抗素子を容易に選定できる。

#### 【0026】

第5の態様によると、キャパシタの電圧から接続点の電位への変換の、微調整が容易である。

#### 【図面の簡単な説明】

#### 【0027】

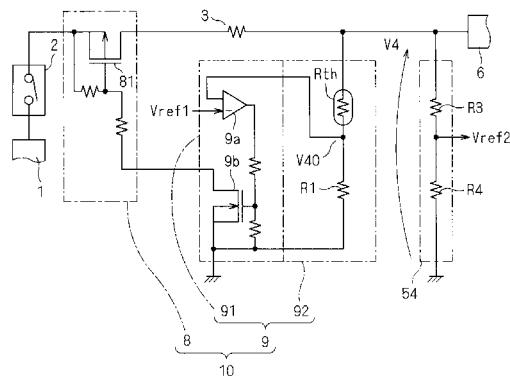

【図1】実施形態に係る構成を示す図である。

20

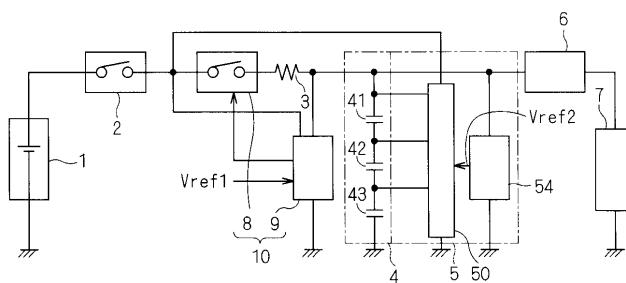

【図2】放電制御回路の一部と、充電制御回路の構成を示す回路図である。

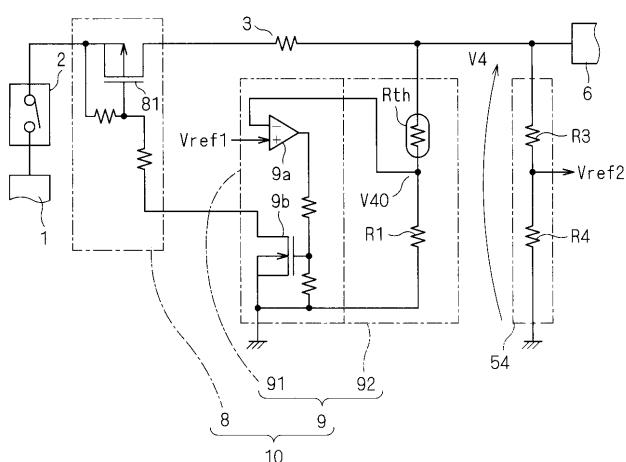

【図3】放電制御部の構成を示す回路図である。

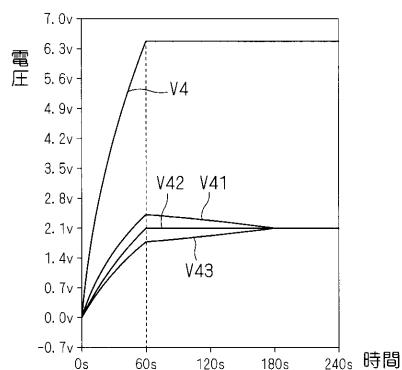

【図4】キャパシタユニットが保持する電圧、キャパシタが保持する電圧の時間依存性を示すグラフである。

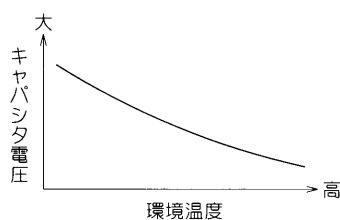

【図5】キャパシタユニットが保持する電圧の、環境温度に対する関係を模式的に示すグラフである。

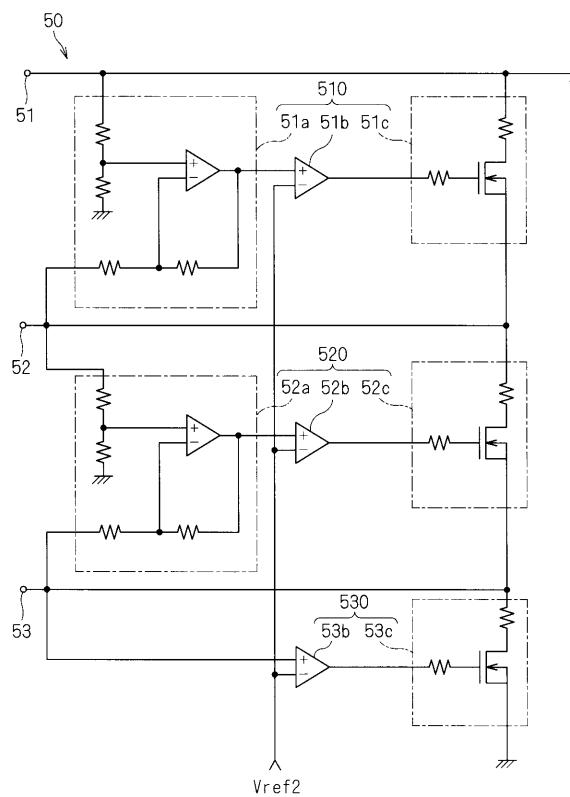

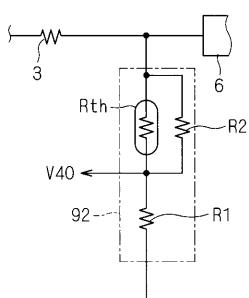

【図6】第1分圧回路の変形の構成を示す回路図である。

【図7】第1分圧回路の他の変形の構成を示す回路図である。

#### 【発明を実施するための形態】

#### 【0028】

以下、実施形態に係る充放電制御回路について説明する。図1は、キャパシタユニット4と、キャパシタユニット4の充放電を制御する充放電制御回路、及びこれらと接続される要素について示す回路図である。

30

#### 【0029】

バッテリ1は、例えば車載用のバッテリであり、不図示のオルタネータ等によって充電される。リレー2は例えばイグニッションリレーであり、エンジン点火に伴って導通する。電流制限抵抗3の一端はリレー2を介してバッテリ1の正極に接続されており、他端はキャパシタユニット4の高電位側に接続される。

#### 【0030】

キャパシタユニット4は電流制限抵抗3の他端と、バッテリ1の負極との間に接続されている。換言すれば、バッテリ1、リレー2、電流制限抵抗3はキャパシタユニット4に対して並列に接続されている。なお、図1ではバッテリ1の負極は接地されている。

40

#### 【0031】

キャパシタユニット4は互いに直列に接続されたキャパシタ41、42、43を有している。キャパシタ41はキャパシタ42よりも、キャパシタ42はキャパシタ43よりも、それぞれ高電位側に設けられる。キャパシタ41の高電位側端は電流制限抵抗3の他端に接続され、キャパシタ43の低電位側端はバッテリ1の負極に接続される。

#### 【0032】

ここではキャパシタユニット4が有するキャパシタの個数として3個の場合が例示されたが、複数であればその個数は適宜選定できる。

50

## 【0033】

充放電制御回路は放電制御回路5と、充電制御回路10とを備える。放電制御回路5は、キャパシタ41, 42, 43の放電を個別に制御する。充電制御回路10は、キャパシタユニット4の充電をキャパシタ41, 42, 43の全てを一括して制御する。充電制御回路10は、スイッチ素子8とスイッチ制御部9とを有している。図2に、放電制御回路5の一部と、充電制御回路10の構成を回路図で示す。

## 【0034】

コンバータ6は、例えば昇圧DC/DCコンバータである。例えばコンバータ6は、キャパシタユニット4が保持する電圧を入力し、これを昇圧して負荷7に与える。負荷7は例えばドアロック解除用のモータである。

10

## 【0035】

スイッチ素子8は、キャパシタユニット4への充電経路(ここではバッテリ1、リレー2、電流制限抵抗3が直列に接続される経路)に介挿される。スイッチ素子8は、例えばPMOSトランジスタ81を含んで構成される(図2参照)。

## 【0036】

スイッチ制御部9は、スイッチ素子8の開閉を制御する。図2を参照して、スイッチ制御部9は、第1分圧回路92と、比較結果出力回路91とを含む。第1分圧回路92は、キャパシタユニット4が保持する電圧V4を分圧して電位V40を出力する機能を有し、一対の抵抗素子Rth, R1を有する。一対の抵抗素子Rth, R1のそれぞれの抵抗値の温度依存性は相互に異なる。

20

## 【0037】

比較結果出力回路91は、電位V40と所定電位Vref1とを比較した結果に基づいて、スイッチ素子8の開閉を制御する。比較結果出力回路91は例えばコンパレータ9a、NMOSトランジスタ9bを含んで構成される。

## 【0038】

以下、リレー2がオンしている状況において説明する。スイッチ素子8がオンしていると、バッテリ1によってキャパシタユニット4へと充電電流が供給される。スイッチ素子8がオフすると、充電電流の供給は遮断される。

## 【0039】

電位V40が所定電位Vref1を越えると、コンパレータ9aの出力は低電位となり、NMOSトランジスタ9bをオフする。NMOSトランジスタ9bがオフすると、PMOSトランジスタ81は、そのゲート電位が上昇してオフする。よってスイッチ素子8が非導通となる。

30

## 【0040】

電位V40が所定電位Vref1以下であれば、コンパレータ9aの出力は高電位となり、NMOSトランジスタ9bがオンしてPMOSトランジスタ81のゲート電位を下げる。これによりPMOSトランジスタ81はオンして、スイッチ素子8が導通する。

## 【0041】

電位V40は第1分圧回路92によってキャパシタユニット4が保持する電圧V4を分圧したものであり、これが比較結果出力回路91に与えられる。これにより、キャパシタ41, 42, 43の全てについて、温度を考慮した充電が行われ、以てキャパシタユニット4が保持する電圧は環境温度に応じて制御される。しかも直列に接続されたキャパシタ41, 42, 43の全てが利用される。

40

## 【0042】

図3は放電制御部50の構成を示す回路図である。放電制御部50は、直列に接続された複数の放電部510, 520, 530と、入力端51, 52, 53とを備える。

## 【0043】

放電部510, 520, 530は、それぞれキャパシタ41, 42, 43に対応して備えられる。放電制御部50において放電部510, 520, 530は、キャパシタユニット4が有するキャパシタ41, 42, 43の個数と同じ個数が設けられる。

50

## 【0044】

ここでは入力端51はキャパシタ41の高電位側に、入力端52はキャパシタ41の低電位側及びキャパシタ42の高電位側に、入力端53はキャパシタ42の低電位側及びキャパシタ43の高電位側に、それぞれ接続される。

## 【0045】

もちろん、放電制御部50は、キャパシタユニット4が有するキャパシタの個数よりも多くの放電部を備えててもよい。しかしキャパシタに対応しない（言ってみれば余剰の）放電部は本実施形態の動作とは直接の関連はない。

## 【0046】

放電部510は差動増幅回路51aとコンパレータ51bと、スイッチ素子51cとを有する。差動増幅回路51aは例えばオペアンプと抵抗素子とを用いて構成できる。差動増幅回路51aは入力端51, 52間の電圧（つまりキャパシタ41が保持する電圧）を、キャパシタユニット4の低電位側（ここでは接地）を基準として出力する。10

## 【0047】

コンパレータ51bは差動増幅回路51aの出力と閾値 $V_{ref}$ とを比較し、その比較結果に基づいてスイッチ素子51cの開閉を制御する。スイッチ素子51cは入力端51, 52の間に接続される。

## 【0048】

具体的には差動増幅回路51aの出力が閾値 $V_{ref}$ を越えればスイッチ素子51cを導通させ、以てキャパシタ41を放電させる。差動増幅回路51aの出力が閾値 $V_{ref}$ 以下であればスイッチ素子51cを非導通とし、以てキャパシタ41の放電を抑制する。通常、差動増幅回路51aを構成するオペアンプの入力抵抗は非常に大きいので、スイッチ素子51cが非導通のときのキャパシタ41の放電量は小さい。20

## 【0049】

放電部520は差動増幅回路52aとコンパレータ52bと、スイッチ素子52cとを有する。差動増幅回路52aは入力端52, 53間の電圧（つまりキャパシタ42が保持する電圧）を、キャパシタユニット4の低電位側を基準として出力する。差動増幅回路52aも差動増幅回路51aと同様にして構成できる。

## 【0050】

コンパレータ52bは差動増幅回路52aの出力と閾値 $V_{ref}$ とを比較し、その比較結果に基づいてスイッチ素子52cの開閉を制御する。スイッチ素子52cは入力端52, 53の間に接続される。よって差動増幅回路52aの出力が閾値 $V_{ref}$ を越えればキャパシタ42が放電し、差動増幅回路52aの出力が閾値 $V_{ref}$ 以下であればキャパシタ42の放電が抑制される。30

## 【0051】

放電部530も放電部510, 520と同様にして、コンパレータ53bとスイッチ素子53cとを有するが、差動増幅回路は必要としない。キャパシタ43の電位はキャパシタユニット4の低電位側を基準としているからである。

## 【0052】

入力端53の電位が、コンパレータ53bによって閾値 $V_{ref}$ とを比較され、その比較結果に基づいてスイッチ素子53cの開閉が制御される。40

## 【0053】

スイッチ素子53cは入力端53と、キャパシタユニット4の低電位側との間に接続されるので、入力端53の電位が閾値 $V_{ref}$ を越えればキャパシタ43が放電し、閾値 $V_{ref}$ 以下であればキャパシタ43の放電が抑制される。

## 【0054】

キャパシタユニットに設けられた（少なくとも一つの）キャパシタを、これに並列に接続されたスイッチ素子の開閉によって、充放電すること自体は公知であるので、これ以上の放電部510, 520, 530の動作の詳細な説明は避ける。

## 【0055】

10

20

30

40

50

このように、放電制御回路 5において、放電部 510, 520, 530は、キャパシタ 41, 42, 43の各々が保持する電圧を、同一の閾値  $V_{ref2}$ と比較して、キャパシタ 41, 42, 43の各々の放電を個別に制御する。よってキャパシタユニット4を構成して直列に接続されるキャパシタ 41, 42, 43同士の充電電圧を均等化し、充電電圧の不均一による劣化を抑制する。

#### 【0056】

但し、上記の説明から理解されるように、キャパシタ 41, 42, 43の放電の有無は、それぞれが保持する電圧と、閾値  $V_{ref2}$ との比較結果に依存する。そしてキャパシタユニット4ではキャパシタ 41, 42, 43が直列に接続されているのであるから、閾値  $V_{ref2}$ はキャパシタユニット4が保持する電圧  $V_4$ の  $1/3$ 倍でなければならない。

10

#### 【0057】

そこで、放電制御回路 5は更に、第2分圧回路 54を有する。第2分圧回路 54は、電圧  $V_4$ を、キャパシタユニット4において直列に接続されるキャパシタ 41, 42, 43の個数  $N$ 個（ここでは  $N = 3$ ）で除した値  $V_4 \times (1/N)$ に分圧して閾値  $V_{ref2}$ として出力する。

#### 【0058】

第2分圧回路 54は具体的には例えば図2を参照して、キャパシタユニット4の高電位側と低電位側との間で直列に接続される一対の抵抗素子  $R_3, R_4$ を含んで構成される。抵抗素子  $R_3, R_4$ はそれぞれキャパシタユニット4の高電位側と低電位側とに配置される。抵抗素子  $R_3$ の抵抗値は抵抗素子  $R_4$ の抵抗値の  $(N - 1)$ 倍に設定される。これにより閾値  $V_{ref2} = V_4 \times (1/N)$ が、抵抗素子  $R_3, R_4$ 同士の接続点から得られることになる。

20

#### 【0059】

図4は、キャパシタユニット4が保持する電圧  $V_4$ 、キャパシタ 41, 42, 43がそれぞれ保持する電圧  $V_{41}, V_{42}, V_{43}$ の時間依存性を示すグラフである。キャパシタユニット4ではキャパシタ 41, 42, 43が直列に接続されているのであるから、 $V_4 = V_{41} + V_{42} + V_{43}$ の関係がある。

#### 【0060】

初期状態として、キャパシタ 41, 42, 43が完全に放電されており、 $V_4 = V_{41} = V_{42} = V_{43} = 0$ となる場合を設定している。また、理解を容易にするために、キャパシタ 41, 42, 43の静電容量  $C_{41}, C_{42}, C_{43}$ を、 $C_{41} < C_{42} < C_{43}$ に設定した。

30

#### 【0061】

時刻 0 s には、リレー 2の導通を開始した時点を採用した。それ以前には  $V_4 = 0$ であるので、スイッチ素子 8は導通し、時刻 0 s 以降、キャパシタユニット4はバッテリ 1によって充電される。

#### 【0062】

上述のように  $C_{41} < C_{42} < C_{43}$ であるので、キャパシタユニット4への充電が行われている間は  $V_{41} > V_{42} > V_{43}$ となっている。

40

#### 【0063】

さて、キャパシタユニット4への充電により、電圧  $V_4$ は上昇し続ける。電圧  $V_4$ が上昇し続ける間は、閾値  $V_{ref2}$ も上昇し続けるので、電圧  $V_{41}, V_{42}, V_{43}$ も上昇し続ける。

#### 【0064】

時刻 60 sにおいて電圧  $V_4$ がほぼ 6.3 Vに達すると、スイッチ制御部 9の機能により、スイッチ素子 8が非導通となる。この後、キャパシタ 41, 42, 43の微少な放電により電圧  $V_4$ が低下すると、再びスイッチ素子 8は導通してキャパシタユニット4への充電が再開される。よってこれ以後、電圧  $V_4$ は振動しつつも 6.3 V近傍で維持される。但し、図4ではこの振動（電圧  $V_{41}, V_{42}, V_{43}$ についても同様）については無

50

視して描いている。

【0065】

このように電圧V4がほぼ6.3Vでほぼ一定値となるので、閾値Vref2は6.3 / 2 = 2.1V程度で一定値となる。このため、時刻60sにおいて電圧2.1V近傍にあった電圧V42はその値を維持し続ける。

【0066】

他方、時刻60sにおいて電圧2.1Vよりも大きな値であった電圧V41は電圧2.1Vに向けて低下する（スイッチ素子51cによるキャパシタ41の放電）。

【0067】

また時刻60sにおいて電圧2.1Vよりも小さな値であった電圧V43は電圧2.1Vに向けて上昇する。これはキャパシタ41が放電されることにより、その蓄積していた電荷がキャパシタ43を充電するからである。

10

【0068】

このようにして、時刻180s付近では、電圧V41, V42, V43のいずれもがほぼ2.1Vに等しくなり、その後もこれらの電圧が維持される。

【0069】

上述の構成において所定電位Vref1がキャパシタユニット4の低電位側（ここでは接地）を基準とした正值とする場合について、より具体的に説明する。抵抗素子Rth, R1のうち、キャパシタユニット4の高電位側に接続される抵抗素子Rthの抵抗値が有する第1の温度係数よりも、低電位側に接続される抵抗素子R1の抵抗値が有する第2の温度係数の方が高い。

20

【0070】

例えば抵抗素子R1は通常の抵抗素子であって、正の温度係数を有する。例えば抵抗素子Rthは負の温度係数を有するタイプのサーミスタを採用する。

【0071】

負の温度係数を有するタイプのサーミスタでは、その環境温度Tthにおける抵抗値Rthは、基準温度T0における抵抗値R0と、サーミスタ係数Bとを用いて、下式のように示されることが公知である。

【0072】

$$R_{th} = R_0 \cdot \exp [B \cdot (1/T_{th} - 1/T_0)]$$

30

【0073】

但し、記号exp[ ]は、括弧内の値の指数関数を示す。

【0074】

よってキャパシタユニット4が保持する電圧V4は環境温度が高いほど高い電位V40へ変換される。よって、環境温度が高いほど、低いキャパシタユニットの電圧でスイッチ素子8が非導通となり、以てキャパシタ41, 42, 43が保持する電圧を低く設定できる。このように環境温度が高いほど、キャパシタが保持する電圧を低くすることが望ましいのは、上述の通りである。

【0075】

図5は上述の動作によって得られる電圧V4の、環境温度に対する関係を模式的に示すグラフである。当該グラフにおいて、環境温度が上昇するほど、キャパシタ電圧は低下することが示されている。

40

【0076】

もちろん、第1の温度係数と、第2の温度係数とはその極性が異なることを前提とするものではない。第1の温度係数よりも第2の温度係数の方が高く、電位V40が所定電位Vref1よりも高いときにスイッチ素子8を非導通させることができればよい。

【0077】

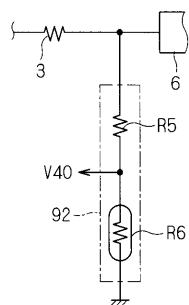

図6は第1分圧回路92の変形を示す回路図である。当該変形にかかる第1分圧回路92は、図2に示された第1分圧回路92に対し、抵抗素子Rth, R1をそれぞれ抵抗素子R5, R6に置換した構成を有している。

50

## 【0078】

抵抗素子 R<sub>t h</sub>, R<sub>1</sub> と類似して、抵抗素子 R<sub>5</sub> の抵抗値が有する第 1 の温度係数よりも、抵抗素子 R<sub>6</sub> の抵抗値が有する第 2 の温度係数の方が高い。但し抵抗素子 R<sub>1</sub> は通常の抵抗素子であって、正の温度係数を有する。例えば抵抗素子 R<sub>6</sub> は正の温度係数を有するタイプのサーミスタを採用する。

## 【0079】

このような場合でも、電圧 V<sub>4</sub> は環境温度が高いほど高い電圧に変換される。よって環境温度が高いほどキャパシタユニット 4 は充電されにくくなり、電圧 V<sub>4</sub> を、ひいては V<sub>4 1</sub>, V<sub>4 2</sub>, V<sub>4 3</sub> を抑制できる。

## 【0080】

あるいは第 1 の温度係数よりも第 2 の温度係数の方が低い構成を採用することもできる。この場合、比較結果出力回路 9<sub>1</sub> として他の構成を、たとえばコンパレータ 9<sub>a</sub> の反転入力端と非反転入力端とを入れ替えるなどの適宜の設計変更を行えばよい。

## 【0081】

図 7 は第 1 分圧回路 9<sub>2</sub> の更なる変形を示す回路図である。当該変形にかかる第 1 分圧回路 9<sub>2</sub> は、図 2 に示された第 1 分圧回路 9<sub>2</sub> に対し、抵抗素子 R<sub>t h</sub> に対して抵抗素子 R<sub>2</sub> を並列に接続した点が特徴である。抵抗素子 R<sub>2</sub> の抵抗値が有する第 3 の温度係数は、抵抗素子 R<sub>t h</sub> の抵抗値が有する第 1 の温度係数よりも高い。

## 【0082】

このようにすれば、環境温度に応じた電圧 V<sub>4</sub> から電位 V<sub>4 0</sub>への変換の、微調整が容易となる。

10

## 【0083】

なお、上記各構成は、相互に矛盾しない限り適宜組合せることができる。

## 【0084】

以上のようにこの発明は詳細に説明されたが、上記した説明は、すべての局面において、例示であって、この発明がそれに限定されるものではない。例示されていない無数の変形例が、この発明の範囲から外れることなく想定され得るものと解される。

20

## 【符号の説明】

## 【0085】

4 キャパシタユニット

30

4<sub>1</sub>, 4<sub>2</sub>, 4<sub>3</sub> キャパシタ

5 放電制御回路

5<sub>1 0</sub>, 5<sub>2 0</sub>, 5<sub>3 0</sub> 放電部

5<sub>4</sub>, 9<sub>2</sub> 分圧回路

8 スイッチ素子

9 スイッチ制御部

R<sub>1</sub>, R<sub>2</sub>, R<sub>t h</sub> 抵抗素子

【図 1】

【図 2】

【図 3】

【図 4】

【図 6】

【図 5】

【図 7】

---

フロントページの続き

(72)発明者 澤野 峻一

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

(72)発明者 生田 勝也

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

F ターム(参考) 5G503 AA04 BB01 BB03 CA11 CB13 DA02