(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3888221号

(P3888221)

(45) 発行日 平成19年2月28日(2007.2.28)

(24) 登録日 平成18年12月8日(2006.12.8)

(51) Int.C1.

F 1

A 6 3 F 7/02 (2006.01)

A 6 3 F 7/02 3 1 5 Z

A 6 3 F 7/02 3 3 4

請求項の数 2 (全 13 頁)

(21) 出願番号 特願2002-130222 (P2002-130222)

(22) 出願日 平成14年5月1日 (2002.5.1)

(62) 分割の表示 特願平10-168956の分割

原出願日 平成10年6月16日 (1998.6.16)

(65) 公開番号 特開2002-369927 (P2002-369927A)

(43) 公開日 平成14年12月24日 (2002.12.24)

審査請求日 平成14年5月2日 (2002.5.2)

(31) 優先権主張番号 特願平9-167789

(32) 優先日 平成9年6月24日 (1997.6.24)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000144522

株式会社三洋物産

愛知県名古屋市千種区今池3丁目9番21号

(74) 代理人 100103045

弁理士 兼子 直久

(72) 発明者 保谷 誠

名古屋市千種区今池3丁目9番21号

株式会社 三洋物産内

(72) 発明者 中嶋 博

名古屋市千種区春岡通7丁目49番地

株式会社 ジェイ・ティ内

(72) 発明者 那須 隆

名古屋市千種区春岡通7丁目49番地

株式会社 ジェイ・ティ内

最終頁に続く

(54) 【発明の名称】制御装置および、その制御装置を備えた遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技機の制御に使用される乱数値を生成するための乱数生成手段と、その乱数生成手段により生成された値を所定の契機に読み出して遊技の制御を行う制御手段とを備えた制御装置において、

前記乱数生成手段は、前記乱数値として使用される生成値を記憶する生成値記憶手段を有し、

前記制御手段は、プログラムに従って所定時間ごとに定期的に実行される定期処理において前記生成値記憶手段に記憶される生成値を所定の契機に読み出して遊技の制御を行うものであって、

前記乱数生成手段と前記制御手段とを備える回路基板と、

その回路基板と遊技機に設けられる所定の装置とを接続するために使用され前記回路基板に設けられるコネクタと、

前記乱数生成手段の乱数の値を更新するために使用される信号を出力する信号出力手段とを備え、

前記乱数生成手段は、

生成可能な上限値の範囲内にて前記乱数値の最大値をいずれの値にも設定可能であって、その設定された最大値に対する情報を記憶して前記生成値記憶手段に記憶される生成値を前記最大値内にするための最大値設定手段と、

その最大値設定手段によって記憶される情報に対応する乱数値の範囲内で前記生成値記

憶手段に記憶される生成値を更新するための生成値更新手段と、

前記生成値記憶手段に記憶された生成値を特定するための情報を記憶する生成済値記憶手段とを有し、

前記生成値記憶手段に前記生成値がその生成値の総個数の n 倍回 ( n は自然数のいずれか ) 記憶される場合に、前記生成済値記憶手段に記憶される情報によって各生成値の生成回数が n 回ずつとされると共に前記更新範囲内の数値順とは異なる生成順序に生成値が生成されるようにし、

更に、前記信号出力手段が出力する信号は前記コネクタを通過しないことを特徴とする制御装置。

**【請求項 2】**

10

請求項 1 記載の制御装置を有し、

前記所定の装置は、図柄を表示する表示装置を制御する表示制御装置を含み、

前記定期処理は、前記表示制御装置に対して動作信号を出力する出力処理を含んで構成されることを特徴とする遊技機。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、パチンコ遊技機などに使用される制御装置およびその制御装置を備えた遊技機に関し、特に、「ぶら下げ基板」等による不正行為を防止することができる制御装置およびその制御装置を備えた遊技機に関するものである。

20

**【0002】**

**【従来の技術】**

遊技機の一種であるパチンコ遊技機は、複数種類の図柄を変動表示可能な表示装置を備えており、遊技領域に打ち込まれた打球が図柄作動ゲートを通過することにより、変動表示を開始するように構成されている。この変動表示が予め定められた図柄の組み合わせと一致して停止すると、大当たりとなって、遊技者に所定の遊技価値が付与され、大量の遊技球が払出可能な状態となる。

**【0003】**

かかる大当たりの発生の有無は、打球が図柄作動ゲートを通過するタイミングで決定される。即ち、1カウントずつ定期的に一定の範囲で(例えば、1カウントずつ、2ms毎に、0から346の範囲で)更新されるカウンタを備え、打球が図柄作動ゲートを通過したときに、そのカウンタの値を読み出し、読み出されたカウンタの値が、例えば「7」などの所定値と一致する場合に、大当たりを発生させている。

30

**【0004】**

**【発明が解決しようとする課題】**

ところが、最近、「ぶら下げ基板」と呼ばれる不正な基板を使用した不正行為が報告されている。この不正行為は、制御基板と表示装置の表示用基板との間等に、不正な基板をぶら下げて(不正な「ぶら下げ基板」を取り付けて)、不当に大当たりを発生させるというものである。具体的には、前記したパチンコ遊技機に設けられる大当たりを決定するためのカウンタと同様の働きをするカウンタ(1カウントずつ定期的に一定の範囲で更新されるカウンタ)を「ぶら下げ基板」内に設け、そのカウンタの値をパチンコ遊技機の電源投入に合わせてリセット(0クリア)することにより、「ぶら下げ基板」内で大当たりの発生タイミングを把握する。そして、その把握した大当たりの発生タイミングに合わせて、「ぶら下げ基板」内で打球の図柄作動ゲート通過信号を不正に生成し、これをパチンコ遊技機の制御基板へ出力して、不当に大当たりを発生させるというものである。遊技場などでは、この「ぶら下げ基板」を用いた不正行為により、多大な被害を被っているという問題点があった。

40

**【0005】**

本発明は上述した問題点を解決することができる制御装置を提供するものである。また「ぶら下げ基板」等による大当たりの発生タイミングの把握を不可能にして、かかる「ぶ

50

ら下げ基板」等を用いた不正行為を防止することができる制御装置を備えた遊技機を提供するものである。

#### 【0006】

##### 【課題を解決するための手段】

この目的を達成するために請求項1記載の制御装置は、遊技機の制御に使用される乱数値を生成するための乱数生成手段と、その乱数生成手段により生成された値を所定の契機に読み出して遊技の制御を行う制御手段とを備えており、前記乱数生成手段は、前記乱数値として使用される生成値を記憶する生成値記憶手段を有し、前記制御手段は、プログラムに従って所定時間ごとに定期的に実行される定期処理において前記生成値記憶手段に記憶される生成値を所定の契機に読み出して遊技の制御を行うものであって、前記乱数生成手段と前記制御手段とを備える回路基板と、その回路基板と遊技機に設けられる所定の装置とを接続するために使用され前記回路基板に設けられるコネクタと、前記乱数生成手段の乱数の値を更新するために使用される信号を出力する信号出力手段とを備え、前記乱数生成手段は、生成可能な上限値の範囲内にて前記乱数値の最大値をいずれの値にも設定可能であって、その設定された最大値に対する情報を記憶して前記生成値記憶手段に記憶される生成値を前記最大値内にするための最大値設定手段と、その最大値設定手段によって記憶される情報に対応する乱数値の範囲内で前記生成値記憶手段に記憶される生成値を更新するための生成値更新手段と、前記生成値記憶手段に記憶された生成値を特定するための情報を記憶する生成済値記憶手段とを有し、前記生成値記憶手段に前記生成値がその生成値の総個数のn倍回（nは自然数のいずれか）記憶される場合に、前記生成済値記憶手段に記憶される情報によって各生成値の生成回数がn回ずつとされると共に前記更新範囲内の数値順とは異なる生成順序に生成値が生成されるようにし、更に、前記信号出力手段が出力する信号は前記コネクタを通過しないことを特徴としている。

#### 【0007】

請求項2記載の遊技機は、請求項1記載の制御装置を有し、前記所定の装置は、図柄を表示する表示装置を制御する表示制御装置を含み、前記定期処理は、前記表示制御装置に対して動作信号を出力する出力処理を含んで構成される。

#### 【0008】

##### 【発明の実施の形態】

以下、本発明の好ましい実施例について、添付図面を参照して説明する。本実施例では、遊技機の一例としてパチンコ遊技機、特に、第1種パチンコ遊技機を用いて説明する。なお、本発明を第3種パチンコ遊技機や他の遊技機に用いることは、当然に可能である。

#### 【0009】

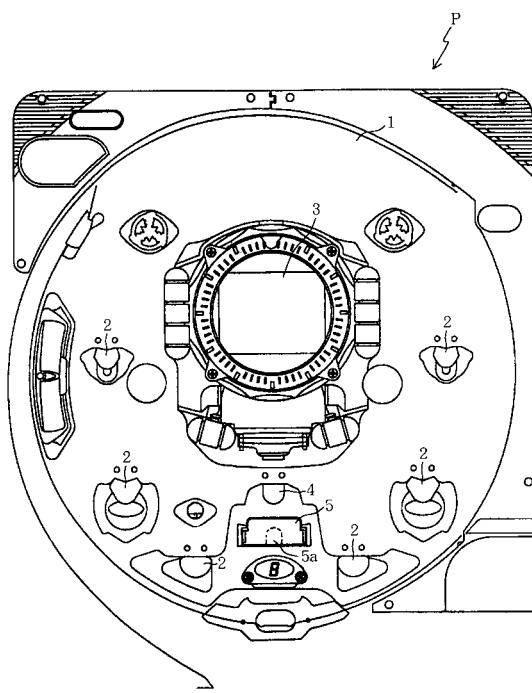

図1は、パチンコ遊技機Pの遊技盤の正面図である。遊技盤1の周囲には、打球が入賞することにより5個から15個の遊技球が払い出される複数の入賞口2が設けられている。また、遊技盤1の中央には、複数種類の識別情報としての図柄などを表示する液晶（LCD）ディスプレイ3が設けられている。このLCDディスプレイ3の表示画面は横方向に3分割されており、3分割された各表示領域において、それぞれ図柄の変動表示が行われる。

#### 【0010】

LCDディスプレイ3の下方には、図柄作動ゲート（第1種始動口）4が設けられている。打球がこの図柄作動ゲート4を通過することにより、前記したLCDディスプレイ3の変動表示が開始される。図柄作動ゲート4の下方には、特定入賞口（大入賞口）5が設けられている。この特定入賞口5は、LCDディスプレイ3の変動後の表示結果が予め定められた図柄の組み合わせの1つと一致する場合に、大当たりとなって、打球が入賞しやすいように所定時間（例えば、30秒経過するまで、あるいは、打球が10個入賞するまで）開放される入賞口である。この特定入賞口5内には、Vゾーン5aが設けられており、特定入賞口5の開放中に、打球がVゾーン5a内を通過すると、継続権が成立して、特定入賞口5の閉鎖後、再度、その特定入賞口5が所定時間（又は、特定入賞口5に打球が所定個数入賞するまで）開放される。この特定入賞口5の開閉動作は、最高で16回（1

10

20

30

40

50

6ラウンド)繰り返し可能にされており、開閉動作の行われ得る状態が、いわゆる所定の遊技価値の付与された状態(特別遊技状態)である。

【0011】

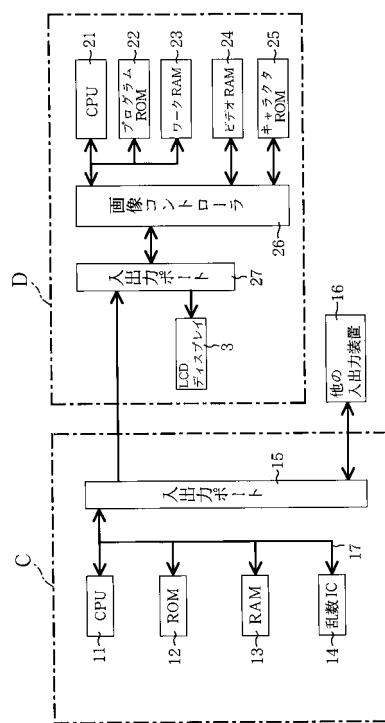

図2は、かかるパチンコ遊技機Pの電気的構成を示したブロック図である。パチンコ遊技機Pの制御部Cは、演算装置であるCPU11と、そのCPU11によって実行される各種の制御プログラムなどを記憶したROM12と、各種のデータ等を一時的に記憶するためのメモリであるRAM13と、パチンコ遊技機Pの制御に使用される乱数を生成し出力する乱数IC14とを備えている。なお、図5のフローチャートに示すリセット割込処理は、ROM12内に記憶されている。

【0012】

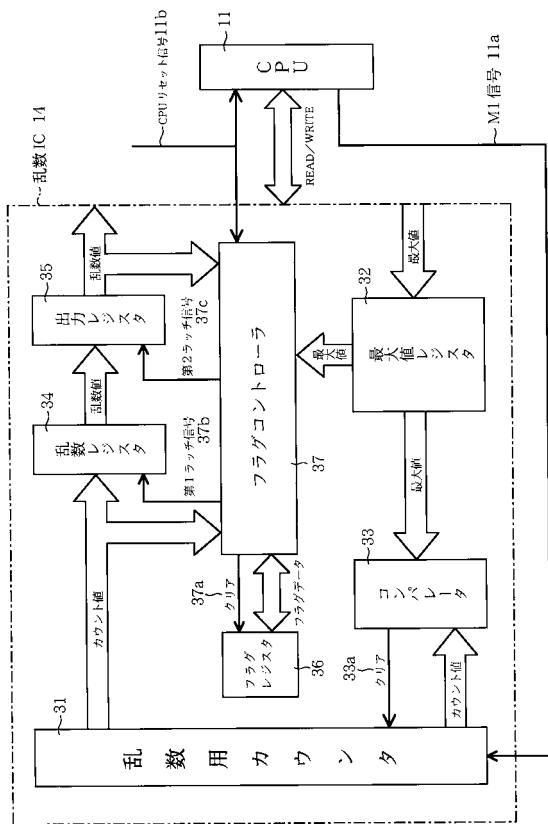

図3は、乱数IC14の電気的構成を示したブロック図である。乱数IC14は、乱数用カウンタ31と、最大値レジスタ32と、コンパレータ33と、乱数レジスタ34と、出力レジスタ35と、フラグレジスタ36と、フラグコントローラ37とを備えている。

【0013】

乱数用カウンタ31は、CPU11から出力されるオペコード・フェッチの信号であるM1信号11aの立ち下がり毎に1カウントずつカウントアップを行う10ビットのカウンタであり、カウント値を「0～1023」の範囲で更新可能にされている。最大値レジスタ32は、その乱数用カウンタ31で更新されるカウント値の最大値+1を記憶するためのレジスタであり、乱数用カウンタ31の更新範囲+1である「1～1024」のいずれかの値が、CPU11によって書き込まれる。コンパレータ33は、最大値レジスタ32の値と乱数用カウンタ31のカウント値とを比較して、両値が一致する場合に、クリア信号33aを乱数用カウンタ31へ出力して、乱数用カウンタ31のカウント値を「0」クリアする。

【0014】

このように乱数用カウンタ31は、M1信号11aが出力される度に、「0」から最大値レジスタ32に記憶された値-1の範囲内で、1カウントずつカウントアップを行うのである。なお、本実施例では、乱数用カウンタ31が「0～346」の範囲でカウント値の更新を行うように、CPU11により最大値レジスタ32に「347」が書き込まれる。

【0015】

乱数レジスタ34は、乱数用カウンタ31が未だ出力レジスタ35にラッチされていない値をカウントする場合に、そのカウント値をラッチするレジスタである。具体的には、乱数レジスタ34は、後述するフラグコントローラ37から出力される第1ラッチ信号37bが入力された時の乱数用カウンタ31のカウント値をラッチする。第1ラッチ信号37bは、乱数用カウンタ31のカウント値に対応するフラグレジスタ36のフラグがオフである場合に、フラグコントローラ37によって出力される。

【0016】

出力レジスタ35は、乱数IC14から乱数値として出力される値をラッチするレジスタであり、フラグコントローラ37から出力される第2ラッチ信号37cが入力された時の乱数レジスタ34の値をラッチする。後述するように、第2ラッチ信号37cは、CPU11に対して2ms毎にリセット割込処理を実行させるためのCPUリセット信号11bを入力することにより、フラグコントローラ37によって出力される。このため出力レジスタ35の値、即ち、乱数IC14の出力乱数値は、CPUリセット信号11bに対応して、2ms毎に切り替えられるのである。なお、CPUリセット信号11bは、図示しないゲートアレイにより、2ms間隔で出力される。

【0017】

フラグレジスタ36は、出力レジスタ35にラッチ済みの値を記憶するためのフラグであり、乱数用カウンタ31の各値に対応する1024ビットのフラグを備えている。例えば、出力レジスタ35に「5」がラッチされた場合には、フラグレジスタ36の5番目のフラグがオンされ、「100」がラッチされた場合には、フラグレジスタ36の100番

10

20

30

40

50

目のフラグがオンされる。一旦オンされたフラグレジスタ 3 6 の各フラグは、フラグコントローラ 3 7 から出力されるクリア信号 3 7 a によって、一斉にオフされる。

【0018】

フラグコントローラ 3 7 は、次の4つの機能を備えたコントローラである。第1は、乱数用カウンタ 3 1 のカウント値を入力して、そのカウント値に対応するフラグレジスタ 3 6 のフラグのオンオフ状態を調べ、かかるフラグがオフされている場合、即ち、入力された乱数用カウンタ 3 1 のカウント値が未だ出力レジスタ 3 5 にラッチされていない値である場合に、第1ラッチ信号 3 7 b を乱数レジスタ 3 4 へ出力する機能である。これにより、そのときの乱数用カウンタ 3 1 のカウント値が乱数レジスタ 3 4 にラッチされる。

【0019】

第2は、CPU11 に対して 2 ms 毎にリセット割込処理を実行させるための CPUリセット信号 1 1 b を入力して、第2ラッチ信号 3 7 c を出力レジスタ 3 5 へ出力する機能である。これにより、乱数レジスタ 3 4 にラッチされている値を、2 ms 毎に出力レジスタ 3 5 にラッチさせることができる。即ち、2 ms 毎に出力レジスタ 3 5 の値（乱数 I C 1 4 の出力乱数値）を切り替えることができる。

【0020】

第3は、第2ラッチ信号 3 7 c により出力レジスタ 3 5 にラッチされた値を入力して、その値に対応するフラグレジスタ 3 6 のフラグをオンする機能である。この機能と第1の機能とが相まって、フラグレジスタ 3 6 のフラグがオフされるまでの間、出力レジスタ 3 5 にラッチ済みの値を、再び乱数レジスタ 3 4 （および出力レジスタ 3 5 ）へラッチさせないようにしている。

【0021】

第4は、前記 CPUリセット信号 1 1 b の回数をカウントして、その回数が最大値レジスタ 3 2 に記憶される値と一致した場合に、フラグレジスタ 3 6 へクリア信号 3 7 a を出力する機能である。このクリア信号 3 7 a により、フラグレジスタ 3 6 のフラグが一斉にオフされる。

【0022】

前記したように、CPUリセット信号 1 1 b を入力する度に出力レジスタ 3 5 にラッチされる値が切り替えられ（第2の機能）、かつ、一度、出力レジスタ 3 5 にラッチされた値は、フラグレジスタ 3 6 のフラグがオフされるまで出力レジスタ 3 5 にはラッチされない（第1～3の機能）。しかも、乱数用カウンタ 3 1 は、M1信号 1 1 a によりカウントの更新を行うので、後述するように、CPUリセット信号 1 1 b の出力間隔である 2 ms のうちに一回り以上のカウントの更新を行っている。よって、出力レジスタ 3 5 の値を切り替える第2ラッチ信号 3 7 c の出力回数が最大値レジスタ 3 2 に記憶されている値と一致するということは、すべての乱数値が出力レジスタ 3 5 にラッチされたということ、即ち、すべての乱数値が乱数 I C 1 4 の乱数値として出力されたということである。従って、かかる場合には、乱数 I C 1 4 からの乱数値の出力を再度繰り返すために、クリア信号 3 7 a をフラグレジスタ 3 6 へ出力して、フラグレジスタ 3 6 のすべてのフラグをオフするのである。

【0023】

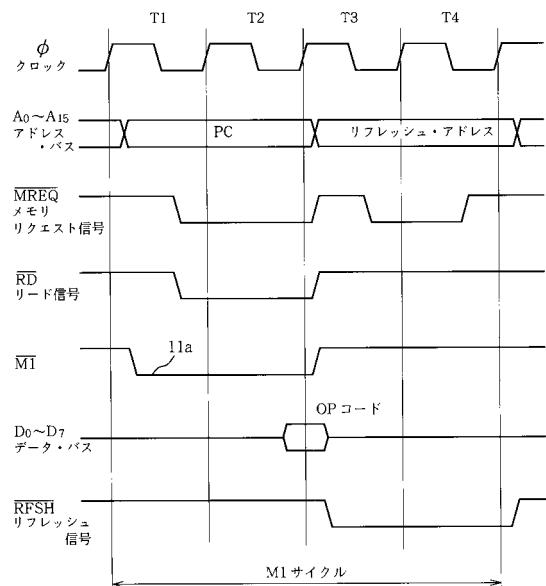

ここで図4を参照して、乱数用カウンタ 3 1 の更新トリガーとなるM1信号 1 1 a について説明する。M1信号 1 1 a は、CPU11 から出力されるオペコードをフェッチするための信号であり、T1クロックの立ち上がりとほぼ同時に立ち下がり、T3クロックの立ち上がり後、ほぼ同時に立ち上がる信号である。M1信号 1 1 a は、CPU11 による各命令の実行時に必ず1回以上出力される。例えば、CPU11 が第1オペコードのみの命令を実行する場合には、その命令の実行時にM1信号 1 1 a は1回出力されるだけであるが、第2オペコードまで有する命令を実行する場合には、その命令の実行時に、M1信号 1 1 a は2回出力される。加えて、1つの命令を構成するマシンサイクル数は、命令によって異なっている。このためM1信号 1 1 a は、CPU11 による命令の実行時に必ず出力されるが、その出力間隔は一定ではない。即ち、CPU11 により実行される命令に

10

20

30

40

50

応じて(パチンコ遊技機Pの遊技状態に応じて)、M1信号11aの出力間隔は変化するのである。

【0024】

しかも、M1信号11aは、CPUリセット信号11bの出力間隔である2msのうちに、約1000回以上出力される信号である。例えば、CPU11の動作クロックを8MHzとすると、1クロックは125nsである。そこで、1命令を実行するための平均クロック数を約16クロックとして計算すると、1命令の実行時間は約2μsとなるので、2msのうちに約1000命令が実行される。このためM1信号11aは、CPUリセット信号11bの出力間隔である2msのうちに、約1000回以上出力されるのである。

【0025】

よって、本実施例では、かかるM1信号11aにより乱数用カウンタ31の値を「0～346」の範囲で更新しているので、出力乱数値をラッチする出力レジスタ35の値が切り替えられる2msの間に、乱数用カウンタ31のカウント値の更新を非等間隔に、かつ、確実に一回り以上行うことができるのである。

【0026】

図2に示すように、これらのCPU11、ROM12、RAM13、乱数IC14は、バスライン17を介して互いに接続されている。バスライン17は、また、入出力ポート15にも接続されており、この入出力ポート15は表示装置Dや他の入出力装置16と接続されている。制御部Cは、入出力ポート15を介して、表示装置Dや他の入出力装置16へ動作コマンドを送り、それら各装置を制御する。LCDディスプレイ3の変動表示や特定入賞口5の開閉動作も、この動作コマンドに基づいて制御される。

【0027】

表示装置Dは、CPU21と、プログラムROM22と、ワークRAM23と、ビデオRAM24と、キャラクタROM25と、画像コントローラ26と、入出力ポート27と、LCDディスプレイ3とを備えている。表示装置DのCPU21は、制御部Cから出力される動作コマンドに応じて、LCDディスプレイ3の表示制御(変動表示)を行うものであり、プログラムROM22には、このCPU21により実行されるプログラムが記憶されている。ワークRAM23は、CPU21によるプログラムの実行時に使用されるワークデータが記憶されるメモリである。

【0028】

ビデオRAM24は、LCDディスプレイ3に表示されるデータが記憶されるメモリであり、このビデオRAM24の内容を書き換えることにより、LCDディスプレイ3の表示内容が変更される。即ち、各表示領域における図柄の変動表示は、ビデオRAM24の内容が書き換えることにより行われる。キャラクタROM25は、LCDディスプレイ3に表示される図柄などのキャラクタデータを記憶するメモリである。画像コントローラ26は、CPU21、ビデオRAM24、入出力ポート27のそれぞれのタイミングを調整して、データの読み書きを介在するとともに、ビデオRAM24に記憶される表示データをキャラクタROM25を参照して所定のタイミングでLCDディスプレイ3に表示させるものである。

【0029】

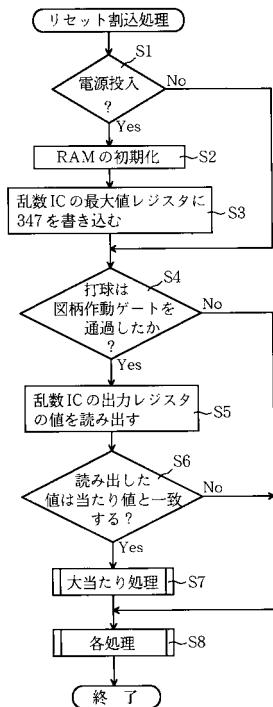

次に、上記のように構成されたパチンコ遊技機Pで実行される各処理を、図5のフローチャートを参照して説明する。図5は、CPUリセット信号11bにより、パチンコ遊技機Pの制御部Cにおいて、2ms毎に実行されるリセット割込処理のフローチャートである。このリセット割込処理により、パチンコ遊技機Pの遊技が制御される。

【0030】

リセット割込処理では、まず、その処理が電源投入後、最初に実行された処理であるか否かが調べられる(S1)。最初に実行された処理であれば(S1: Yes)、RAM13の初期化を行った後に(S2)、乱数の更新範囲の上限を定めるため、乱数IC14の最大値レジスタ32に「347」を書き込む(S3)。これにより乱数IC14の乱数用カウンタ31は「0～346」の範囲でカウントアップを行うので、乱数IC14から出

10

20

30

40

50

力される乱数値は「0～346」となる。

【0031】

S3の処理後、又は、S1の処理において電源投入後2回目以降に実行されたリセット割込処理であると判断された場合には(S1:No)、打球が図柄作動ゲート4を通過していれば(S4:Yes)、乱数IC14の出力乱数値を記憶する出力レジスタ35の値を読み出し(S5)、その読み出した値が当たり値(例えば「7」)の1つと一致するか否かを判断する(S6)。当たり値の1つと一致する場合には(S6:Yes)、大当たりと判定して、大当たり処理を実行する(S7)。大当たり処理では、大当たりコマンドが制御部Cから後述する表示装置Dへ送られて、表示装置Dにより、この大当たりコマンドに基づいて、LCDディスプレイ3の変動表示が大当たりの状態に制御されるのである。

10

【0032】

一方、S4の処理において、打球が図柄作動ゲート4を通過しなかった場合は(S4:No)、乱数IC14の値を読み出すことなく、また、S6の処理において、読み出した乱数IC14の出力レジスタ35の値がいずれの当たり値とも一致しない場合には(S6:No)、ハズレであるので、大当たり処理を行うことなく、S8の処理へ移行する。

【0033】

S8の処理において、パチンコ遊技機Pの遊技状態に応じた各処理を実行した後、今回のリセット割込処理を終了して、次回のリセット割込処理を待機する。

【0034】

ここで、大当たりの判定に用いられる乱数値を出力する乱数IC14の動作について説明する。乱数IC14の乱数用カウンタ31は、CPU11から出力されるM1信号11aの立ち下がり毎にカウントアップを行い、カウント値が最大値レジスタ32に記憶される「347」に達すると、コンパレータ33からクリア信号33aが乱数用カウンタ31へ出力されて、カウント値が「0」クリアされる。よって、乱数用カウンタ31は、M1信号11aにより、「0～346」の範囲でカウントアップを繰り返すのである。

20

【0035】

この乱数用カウンタ31のカウント値は、フラグコントローラ37に入力されている。フラグコントローラ37では、その都度、乱数用カウンタ31のカウント値に対応するフラグレジスタ36のフラグを調べ、そのフラグがオフされていれば、第1ラッチ信号37bを出力して、かかるカウント値を乱数レジスタ34へラッチさせる。

30

【0036】

フラグコントローラ37は、また、リセット割込処理(図5)の実行の契機となるCPUリセット信号11bを入力することにより、第2ラッチ信号37cを出力し、そのタイミングで乱数レジスタ34にラッチされている値を出力レジスタ35へラッチさせる。この出力レジスタ35にラッチされた値が、乱数IC14の出力乱数値として、リセット割込処理のS5の処理により読み出され、大当たりの判定に用いられる(S6)。

【0037】

出力レジスタ35にラッチされた値は、フラグコントローラ37へも出力され、フラグコントローラ37によって、その値に対応するフラグレジスタ36のフラグがオンされる。このフラグのオン操作により、次回からその値の乱数レジスタ34へのラッチが禁止されるので、乱数IC14の出力乱数値として、「0～346」のすべての値を出力するまでに、いずれかの値を2回以上出力してしまうことを防止することができる。

40

【0038】

なお、乱数用カウンタ31をカウントアップさせるM1信号11aは、CPUリセット信号11bの出力間隔である2msの間に、約1000回以上出力されるので、CPUリセット信号11bの出力後、次の信号11bが出力されるまでに、乱数用カウンタ31は一回り以上の更新を行う。よって、出力レジスタ35にラッチされていない値のみを、2ms毎に切り替えて、出力レジスタ35にラッチさせることができる。

【0039】

50

C P U リセット信号 1 1 b の出力回数が最大値レジスタ 3 2 の値である「3 4 7」と一致すると、「0 ~ 3 4 6」の 3 4 7 個のすべての値が 1 回ずつ出力レジスタ 3 5 にラッチされ、乱数値として用いられたことになる。よって、この場合には、フラグコントローラ 3 7 からクリア信号 3 7 a をフラグレジスタ 3 6 へ出力して、フラグレジスタ 3 6 のすべてのフラグを一斉にオフして、乱数値の出力を再び繰り返す。

#### 【0 0 4 0】

以上説明したように、本実施例のパチンコ遊技機 P では、乱数 I C 1 4 から出力される乱数値を用いて大当たりを判定している。この乱数 I C 1 4 から出力される乱数値は、乱数の一様性（連続で取得した場合、同じ値を取得することができなく、しかも、すべての値が同じ確率で取得できる）を備えつつ、ランダムになっている。このランダムな値は、パチンコ遊技機 P の遊技状態に応じて、その出力間隔が変化する M 1 信号 1 1 a に基づいて生成されている。よって、「ぶら下げ基板」では、かかる乱数 I C 1 4 の出力乱数値を把握することができない。従って、「ぶら下げ基板」による大当たりの発生タイミングの把握を不可能にして、「ぶら下げ基板」を用いた不正行為を防止することができる。

#### 【0 0 4 1】

以上、実施例に基づき本発明を説明したが、本発明は上記実施例に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良変形が可能であることは容易に推察できるものである。

#### 【0 0 4 2】

例えば、本実施例では、乱数 I C 1 4 は C P U 1 1 と別体に構成されたが、乱数 I C 1 4 を C P U 1 1 に内蔵しても良い。乱数 I C 1 4 を C P U 1 1 に内蔵することにより、乱数 I C 1 4 自体を交換するといった不正行為を防止することができるので、不正行為の防止効果を一層向上することができる。しかも、乱数 I C 1 4 を C P U に内蔵し、その乱数 I C 1 4 の乱数用カウンタ 3 1 を更新するための信号（本実施例では、M 1 信号 1 1 a）を、C P U 1 1 の外部へ出力しないように構成すれば、C P U 1 1 の外部から乱数用カウンタ 3 1 の更新タイミングが全くわからなくなるので、「ぶら下げ基板」等による出力乱数値の把握を一層困難なものにすることができます。

#### 【0 0 4 3】

また、フラグレジスタ 3 6 のフラグをカウンタに変更しても良い。例えば、乱数用カウンタ 3 1 で更新される各値に対して 2 ビットずつのカウンタを設ければ、各値の出力レジスタ 3 5 へのラッチ回数を 3 回までカウントすることができる。よって、かかる構成を採用することにより、各乱数値が 3 回りする範囲において、乱数の一様性を保つようにすることができる。

#### 【0 0 4 4】

更に、乱数用カウンタ 3 1 のカウントアップを行う信号は、必ずしも M 1 信号 1 1 a に限られるものではなく、第 2 ラッチ信号 3 7 c の出力間隔に、乱数用カウンタ 3 1 の更新を一回り以上行わせることができるスピードの信号であれば、M 1 信号 1 1 a に代えて使用することができる。よって、例えば、C P U 1 1 の動作クロック を M 1 信号 1 1 a に代えて使用することもできる。

#### 【0 0 4 5】

また、かかる信号が高速であるだけでなく、不等間隔に絶えず出力される信号であれば、M 1 信号 1 1 a のように、「ぶら下げ基板」対策を一層効果的なものとすることができます。例えば、C P U 1 1 から出力されるメモリ・リクエスト信号、I O リクエスト信号、リード信号、ライト信号、リフレッシュ信号、ウエイト信号、バス・リクエスト信号、バス・アクノリッジ信号、いずれかのアドレスバス信号、または、いずれかのデータバス信号などを、M 1 信号 1 1 a に代えて使用することができる。更に、これら複数の信号を組み合わせて使用するようにしても良いのである。

#### 【0 0 4 6】

本実施例では、乱数レジスタ 3 4 および出力レジスタ 3 5 は別々のラッチ回路で構成されたが、これらを単一のフリップフロップで構成するようにしても良い。即ち、第 1 ラッ

10

20

30

40

50

チ回路および第2ラッチ回路を单一のフリップフロップで構成しても良い。

【0047】

以下に本発明の変形例を示す。請求項1記載の遊技機用乱数生成回路において、前記カウンタ回路は、1の第2ラッチ信号とその次の第2ラッチ信号との間に、すべての乱数値の更新を一回り以上行うことを特徴とする遊技機用乱数生成回路1。

【0048】

請求項1記載の遊技機用乱数生成回路、または、遊技機用乱数生成回路1において、前記記憶回路は、各乱数値毎に設けられたフラグ( $n=1$ の場合)、または、各乱数値毎に設けられたカウンタ( $n=2$ 以上の整数の場合)により構成されていることを特徴とする遊技機用乱数生成回路2。第2ラッチ回路に記憶された乱数値を直接記憶する場合に比べて、記憶回路の容量を少容量化して、回路コストを低減することができる。

10

【0049】

請求項1記載の遊技機用乱数生成回路、または、遊技機用乱数生成回路1、2において、前記カウンタ回路のカウント値の更新トリガとなる信号は、この遊技機用乱数生成回路の搭載される回路基板が外部装置と接続されるコネクタ上の信号以外の信号で構成されることを特徴とする遊技機用乱数生成回路3。よって、「ぶら下げ基板」等を該コネクタに接続しても、「ぶら下げ基板」等では、カウンタ回路のカウント値の更新トリガを入力することができず、遊技機用乱数生成回路から出力される乱数値を把握することができない。

【0050】

20

請求項1記載の遊技機用乱数生成回路、または、遊技機用乱数生成回路1から3のいずれかにおいて、CPUに内蔵されていることを特徴とする遊技機用乱数生成回路4。遊技機用乱数生成回路をCPUに内蔵することにより、遊技機用乱数生成回路のみの不正な取り替えを防止して、不正行為の防止を強化することができる。また、遊技機用乱数生成回路をCPUに内蔵し、かつ、カウンタ回路のカウント値の更新トリガとなる信号をCPUの内部の信号を用い、その信号をCPUの外部へ出力しないように構成すれば、「ぶら下げ基板」等によるカウンタ回路のカウント値の更新を把握できなくすることができる。

【0051】

請求項1記載の遊技機用乱数生成回路、または、遊技機用乱数生成回路1から4のいずれかにおいて、前記カウンタ回路は、非等間隔に絶えず出力される信号に基づいてカウント値の更新を行うことを特徴とする遊技機用乱数生成回路5。カウンタ回路の更新は非等間隔に絶えず行われるので、「ぶら下げ基板」等による乱数値の把握を一層不可能にすることができる。

30

【0052】

請求項1記載の遊技機用乱数生成回路、または、遊技機用乱数生成回路1から5のいずれかにおいて、前記カウンタ回路は、CPUの動作クロック信号、M1信号(オペコードフェッチ信号)、メモリ・リクエスト信号、I/Oリクエスト信号、リード信号、ライト信号、リフレッシュ信号、ウエイト信号、バス・リクエスト信号、バス・アクリッジ信号、少なくとも1本のアドレスバス信号、または、少なくとも1本のデータバス信号のうち、いずれかの信号に基づいてカウント値を更新することを特徴とする遊技機用乱数生成回路6。これらの信号であれば、該信号の発生回路を別途設ける必要がなく、回路コストを低減することができる。CPUの動作クロック信号を除く上記各信号は、遊技機の制御状態に応じて、いずれも非等間隔に絶えず出力されるので、「ぶら下げ基板」等による乱数値の把握を一層不可能にすることができる。なお、CPUの動作クロック信号も含め、前記した信号のうち、いくつかの信号を組み合わせて使用しても良い。

40

【0053】

【発明の効果】

本発明の制御装置によれば、乱数値として使用される生成値がすべてn回分出力されるまで、n回を超えて出力される生成値を生じさせることなく、しかも、生成値の出力順はランダムにされる。よって、この制御装置を用いた遊技機によればこの制御装置から出力

50

される生成値を「ぶら下げ基板」等では把握することができない。従って、「ぶら下げ基板」等による大当たりの発生タイミングの把握を不可能にして、「ぶら下げ基板」等を用いた不正行為を防止することができるという効果がある。なお、nは自然数のいずれかである。

【図面の簡単な説明】

【図1】 本発明の一実施例であるパチンコ遊技機の遊技盤の正面図である。

【図2】 パチンコ遊技機の電気的構成を示したブロック図である。

【図3】 亂数ICの電気的構成を示したブロック図である。

【図4】 M1サイクル(オペコード・フェッチ・サイクル)のタイミングチャートである。

【図5】 リセット割込処理を示したフローチャートである。

【符号の説明】

|       |                               |    |

|-------|-------------------------------|----|

| 1 1   | 制御部のCPU(制御手段、 <u>信号出力手段</u> ) |    |

| 1 1 a | M1信号                          |    |

| 1 1 b | CPUリセット信号                     |    |

| 1 4   | 乱数IC(乱数生成手段)                  |    |

| 3 1   | 乱数用カウンタ                       |    |

| 3 2   | 最大値レジスタ(最大値設定手段)              |    |

| 3 3   | コンパレータ                        |    |

| 3 3 a | クリア信号                         | 20 |

| 3 4   | 乱数レジスタ                        |    |

| 3 5   | 出力レジスタ(生成値記憶手段)               |    |

| 3 6   | フラグレジスタ(生成済値記憶手段)             |    |

| 3 7   | フラグコントローラ(生成値更新手段)            |    |

| 3 7 a | クリア信号                         |    |

| 3 7 b | 第1ラッチ信号                       |    |

| 3 7 c | 第2ラッチ信号                       |    |

| C     | 制御部(制御装置)                     |    |

| D     | 表示装置(表示制御装置)                  |    |

| P     | パチンコ遊技機(遊技機)                  | 30 |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 山崎 好男

名古屋市千種区春岡通7丁目49番地

株式会社 ジェイ・ティ内

審査官 吉川 康史

(56)参考文献 特開平07-031724 (JP, A)

特開平08-182828 (JP, A)

特開昭62-098819 (JP, A)

特開平02-242327 (JP, A)

特開平06-051957 (JP, A)

特開平01-206718 (JP, A)

登録実用新案第3048805 (JP, U)

(58)調査した分野(Int.Cl., DB名)

A63F 7/02

G06F 7/58