(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 699 12 611 T2 2004.09.16**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 092 160 B1**

(51) Int Cl.<sup>7</sup>: **G01R 19/00**

(21) Deutsches Aktenzeichen: **699 12 611.8**

(86) PCT-Aktenzeichen: **PCT/GB99/02060**

(96) Europäisches Aktenzeichen: **99 928 140.5**

(87) PCT-Veröffentlichungs-Nr.: **WO 00/00834**

(86) PCT-Anmeldetag: **30.06.1999**

(87) Veröffentlichungstag

der PCT-Anmeldung: **06.01.2000**

(97) Erstveröffentlichung durch das EPA: **18.04.2001**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **05.11.2003**

(47) Veröffentlichungstag im Patentblatt: **16.09.2004**

(30) Unionspriorität:

**9813982 30.06.1998 GB**

(84) Benannte Vertragsstaaten:

**AT, BE, CH, CY, DE, DK, ES, FI, FR, GR, IE, IT, LI, LU, MC, NL, PT, SE**

(73) Patentinhaber:

**Delta Electrical Ltd., London, GB**

(72) Erfinder:

**SKERRITT, Robert Charles, Conwy LL30 3HX, GB;

CROSIER, Mark David, Holyhead, Isle of Anglesey

LL65 1PD, GB; MURRAY, Anthony, Martin, Bangor

LL57 2AX, GB; REEDER, Brian Martin, Trearddur

Bay, Isle of Anglesey LL65 2AZ, GB**

(54) Bezeichnung: **FEHLERSTROMERFASSUNGSEINRICHTUNG**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingereicht, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

[0001] Diese Erfindung betrifft eine Reststrom-Korrekturseinrichtung (RCD) zur Verwendung in einem Schaltungsunterbrecher.

[0002] Herkömmlicherweise wird ein Reststrom oder Fehlerstrom unter Verwendung eines Stromtransformators erfasst, der Primärwicklungen aufweist, durch die, für den Fall einer einphasigen Einrichtung, ein Laststrom in entgegengesetzte Richtungen fließt, so dass dann, wenn der zurückfließende Strom wegen eines Stromlecks unterschiedlich zu dem nach außen fließenden Strom ist, ein Ausgangstromsignal in einer Sekundärwicklung des Transformators induziert wird. Für den Fall einer mehrphasigen Einrichtung werden Primärwicklungen des Transformators in sämtliche Phasenleitungen und die Neutralleitung geschaltet. In normalen Situationen, wenn kein Stromleck vorhanden ist, ist der Nettostrom, der in der Sekundärwicklung induziert wird, Null und deshalb wird kein Ausgang erfasst.

[0003] Hochentwickelte Materialien sind für den Kern des Stromtransformators entwickelt worden, die ermöglichen, dass eine beträchtliche Genauigkeit erhalten wird, wenn die Ströme, die in den Primärwicklungen fließen, im Wesentlichen sinusförmig sind. Jedoch werden oft Schaltnetzteile für Computer und andere Geräte verwendet und es besteht eine zunehmende Tendenz, dass ein derartiges Gerät DC Versätze in den Strömen verursacht. Derartige Entwicklungen haben Detektoren, die Stromtransformatoren verwenden, weniger zuverlässig gemacht und mit einer Neigung versehen eine falsche Auslösung bereitzustellen oder ein DC Stromleck nicht zu erfassen.

[0004] Dies ist ein besonderes Problem für den Fall von direktbetätigten elektromechanischen Einrichtungen, bei denen die Sekundärwicklung des Stromtransformators tatsächlich eine Betätigungs vorrichtung ansteuert. Die Situation wird nicht sehr verbessert, wenn eine elektronische Erfassungs- und Verstärkungseinrichtung, die mit der Sekundärwicklung verbunden ist, eingebaut wird, da noch Probleme mit Hochfrequenz-Transienten und DC Versätzen bestehen. Ein sehr kleiner DC Strompegel kann bewirken, dass der Kern gesättigt wird, wodurch die Fähigkeit des Detektors zum Erfassen eines Stromlecks stark verschlechtert wird.

[0005] Ein isolierter Stromnebenschlusswandler zum Messen eines elektrischen Stroms in einer Messseinrichtung für eine mehrphasige Leistung ist in der U.S. Patent Beschreibung 5701253 beschrieben. Die hier offenbare Einrichtung misst einen Strom, der in eine Last hineinfließt, für den Zweck einer Leistungsmessung.

[0006] Es ist eine Aufgabe der vorliegenden Erfindung eine Reststrom-Erfassungseinrichtung bereitzustellen, bei der die voranstehend erwähnten Probleme im Wesentlichen in einer einfachen und effizienten Weise beseitigt werden.

[0007] In Übereinstimmung mit der Erfindung ist

eine Reststrom-Erfassungseinrichtung vorgesehen, wie im Anspruch 1 definiert.

[0008] Vorzugsweise umfasst die Detektoreinrichtung einen Analog-zu-Digital-Wandler für jeden Nebenschluss und ein Prozessor ist vorgesehen, um die digitalen Signale von den Wählern zu empfangen und zu bestimmen, ob ein Stromungleichgewicht existiert.

[0009] Jeder Nebenschluss nimmt vorzugsweise die Form eines zusammengesetzten Streifens mit leitenden Abschnitten an seinen Enden und einem widerstandsbehafteten Abschnitt, der die leitenden Abschnitte untereinander verbindet, an. Derartige zusammengesetzte Streifen können in einer Massenherstellung kostengünstig auf sehr hohe Toleranzen hergestellt werden, was sie für diesen Zweck extrem geeignet macht.

[0010] Der Analog-zu-Digital-Wandler für jeden Nebenschluss kann einen Delta-Sigma-Modulator umfassen, der einen einzelnen digitalen Hochfrequenz-Datenstrom erzeugt, der durch eine Dezimierungsfilterung auf einen Mehrbit-Digitaldatenstrom bei einer niedrigeren Frequenz umgewandelt wird.

[0011] Der Analog-zu-Digital-Wandler für jeden Nebenschluss ist vorzugsweise mit dem Prozessor über eine Isolationsbarriere verbunden, so dass der Wandler auf dem Spannungspegel des Nebenschlusses, den er bedient, schweben kann. Die Dezimierungsfilterung kann effizient in dem Wandler, vollständig in dem Prozessor oder zwischen dem Wandler und dem Prozessor bewirkt werden.

[0012] In den Zeichnungen zeigen:

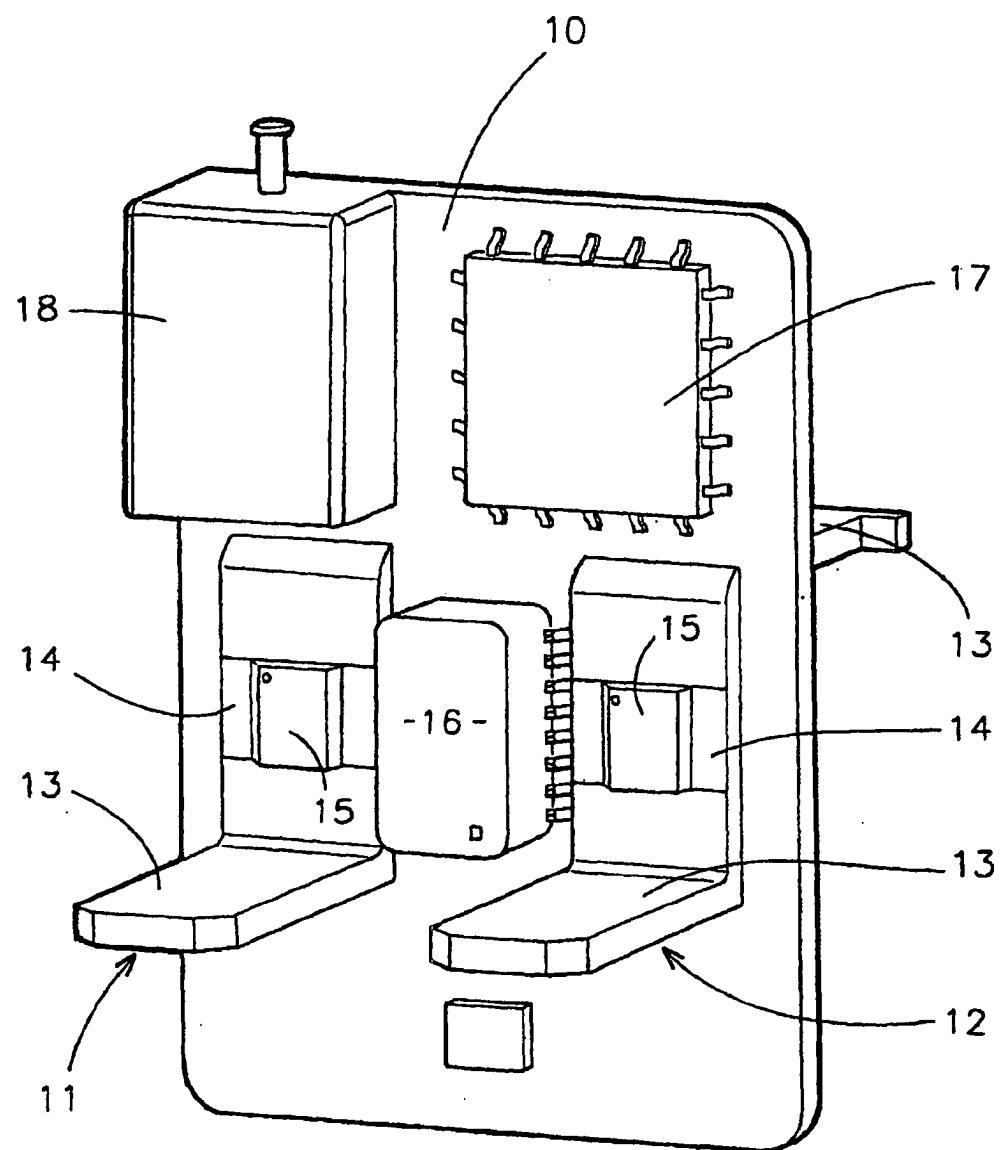

[0013] **Fig. 1** eine diagrammatische perspektivische Ansicht eines Beispiels der Erfindung, wie auf eine dreiphasige Einrichtung angewendet;

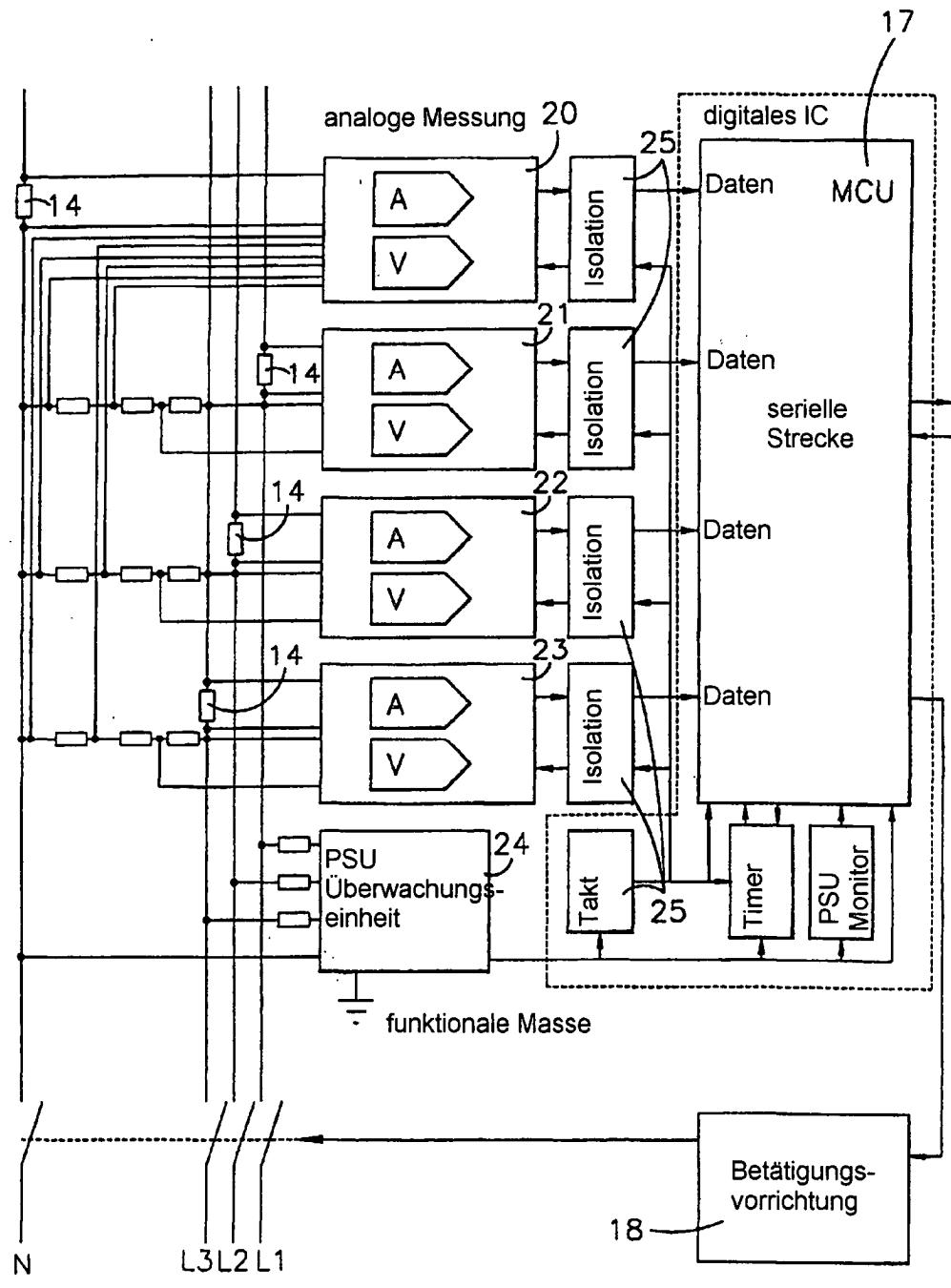

[0014] **Fig. 2** ein Blockdiagramm eines anderen Beispiels der Erfindung, wie auf eine dreiphasige Einrichtung angewendet;

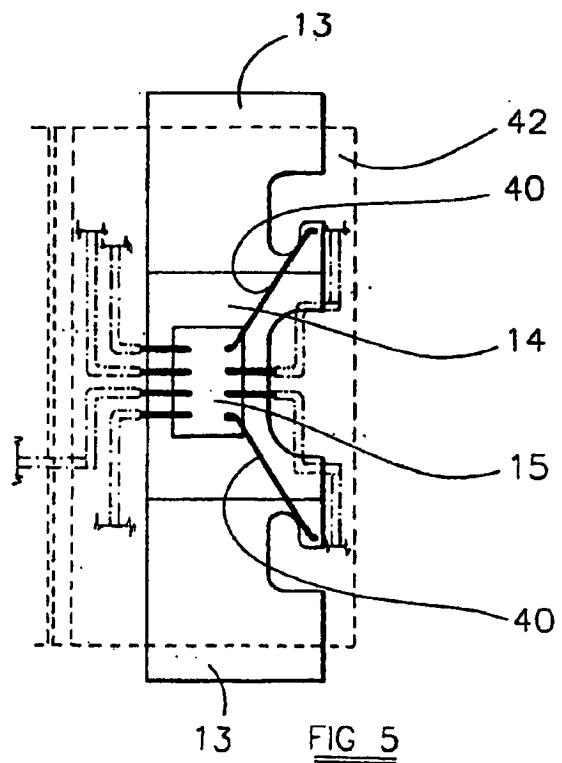

[0015] **Fig. 3** eine perspektivische Ansicht, die eine der Stromerfassungseinrichtungen zeigt;

[0016] **Fig. 4** eine Querschnittsansicht der Stromerfassungseinrichtung der **Fig. 3**;

[0017] **Fig. 5** einen Aufriss der Einrichtung der **Fig. 3**;

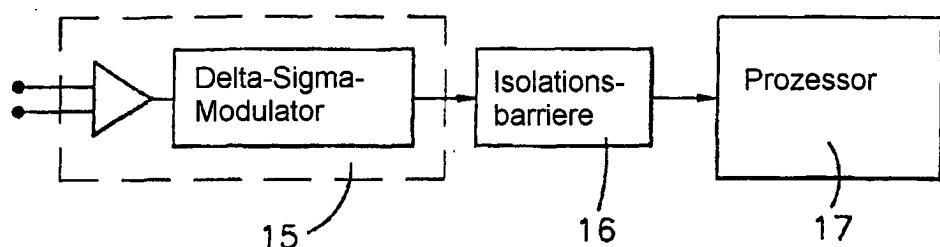

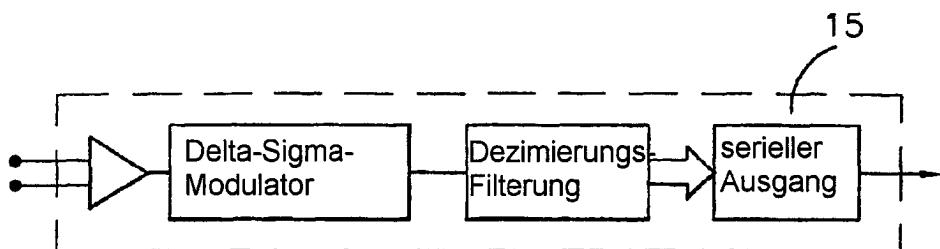

[0018] **Fig. 6** ein Blockdiagramm einer einfachen Form der elektronischen Schaltung einer einzelnen Stromsensoreinrichtung;

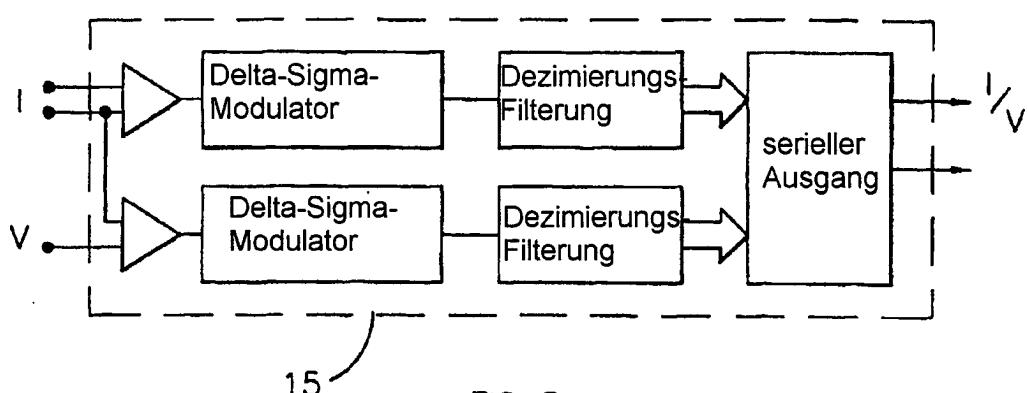

[0019] **Fig. 7** ein Blockdiagramm einer alternativen Ausbildung der elektronischen Schaltung; und

[0020] **Fig. 8** ein Blockdiagramm einer noch anderen Ausbildung der elektronischen Schaltung.

[0021] In der in **Fig. 1** gezeigten Einrichtung haltert ein Substrat **10** zwei zusammengesetzte Leiterstreifen **11, 12**. Jeder von diesen umfasst Endabschnitte **13** aus Kupfer und einen Zwischenabschnitt **14** aus einem widerstandsbehafteten Material wie Manganin. Die Streifen werden gebildet, indem eine Sandwich-Anordnung, gebildet durch eine Elektronenstrahlverschweißung der Kupferabschnitte an gegenüberliegende Seiten des Manganin-Abschnitts, ge-

schnitten werden. Die Nebenschlüsse, die durch die widerstandsbehafteten Abschnitte gebildet werden, die durch dieses Verfahren hergestellt werden, können einen nominellen Widerstand von  $0,2\text{ m}\Omega$  bei einer Toleranz von weniger als 5% aufweisen. Wenn die zwei Nebenschlüsse **14**, die auf einer Einrichtung verwendet werden, von angrenzenden Abschnitten des Sandwich-Materials gepresst werden, stimmen sie auf innerhalb von 2% überein. Eine Kalibrierung der Nebenschlüsse, die in eine Einheit eingebaut sind, bei zwei unterschiedlichen Temperaturen kann größtenteils Nebenschlussfehler beseitigen.

[0022] In dem in **Fig. 1** gezeigten Beispiel gibt es eine getrennte Signalvorverarbeitungseinheit in Form einer anwendungsspezifischen integrierten Schaltung (Application Specific Integrated Circuit, ASIC) **15**, die auf jedem der Nebenschlüsse **14** angebracht und mit den Kupferendabschnitten **13** der zugehörigen Leiterabschnitte verbunden ist. Die zwei ASICs **15** sind über ein Isolationstransformatorfeld **16** mit einem Hauptprozessor **17** verbunden. Die ASICs **15** arbeiten, um die zwei Spannungen über den Nebenschlüssen in einen digitalen Signalstrom umzuwandeln, der über das Isolationstransformatorfeld an den Prozessor **17** kommuniziert wird. Der Hauptprozessor wird programmiert, um ein Ansteuersignal an einer Auslöse-Betätigungs Vorrichtung **18** bereitzustellen.

[0023] Die tatsächliche bevorzugte strukturelle Konfiguration der Sensoren ist in den **Fig. 3** bis **5** gezeigt. Diese zeigen Zuleitungen **40**, die zwei analoge Eingangsanschlüsse des ASIC mit den zwei Kupferendabschnitten verbinden. Andere Zuleitungen verbinden andere Anschlüsse des ASIC **15** mit einem Zuleitungsrahmen, über den sämtliche anderen externen Verbindungen hergestellt werden. **Fig. 5** zeigt mit gestrichelten Linien einen Block **42** eines Verkapselungsmaterials und **Fig. 4** zeigt eine elektrisch isolierende Klebeschicht **41**, mit der die ASIC an dem Zwischenabschnitt **14** des zusammengesetzten Streifens **14, 15** angebracht ist.

[0024] **Fig. 2** zeigt mit näheren elektrischen Einzelheiten eine dreiphasige Einrichtung. In diesem Fall gibt es vier Nebenschlüsse **14**, einer in jeder Phasenleitung und ein vierter in der Neutralleitung. Die ASICs **15** der **Fig. 1** sind als vier getrennte Blöcke **20, 21, 22** und **23** gezeigt und es gibt eine Energiezuführungseinheit **24**, die Energie bzw. Leistung aus den Phasenleitungen auf der Netzseite der Nebenschlüsse **14** zieht und gesteuerte Spannungen an dem Prozessor **17** bereitstellt. Leistung wird an die vier Blöcke **20** bis **23** über Isolationsbarrieren **25** zugeführt, die das Feld **16** bildet. Jeder Block der ASIC umfasst einen Analog-zu-Digital-Wandler in der Form eines Delta-Sigma-Modulators, der einen Einbit-Digitaldatenstrom hoher Frequenz erzeugt. Ein Multiplexer kann in jedem Wandler enthalten sein, so dass der Wandler an dem Prozessor, durch die jeweilige Isolationsbarriere, Signale bereitstellen kann, die sowohl den Strom in dem zugehörigen Nebenschluss als

auch die Spannung an einem Ende davon darstellen. Der Prozessor verwendet diese Signale, um den Strom in jedem Nebenschluss zu überwachen und die Betätigungs Vorrichtung **18** zu betreiben, wenn ein Ungleichgewicht auftritt.

[0025] Es sei darauf hingewiesen, dass die Spannungserfassungsverbindungen zu den ASICs über Widerstandsketten gestellt werden, zwischen jede Phasenleitung und die Neutrale geschaltet sind. Jede derartige Widerstandskette umfasst ein äußeres Paar von Präzisionswiderständen mit einem relativ niedrigen Ohm'schen Wert und einem Zwischenwiderstand mit einem relativ hohen Ohm'schen Wert. Diese Widerstandsketten ermöglichen, dass die RCD mit einer unabhängigen Referenz versehen wird. Wenn der neutrale Analog-zu-Digital-Wandler (ADC) als die gewählte Systemreferenz genommen wird, dann kann die Betriebsssoftware des Hauptprozessors die mehreren Signale, die von den einigen Widerstandsketten abgeleitet werden, verwenden, um jede Phase gegenüber der Neutralreferenz zu kalibrieren.

[0026] Die Zentralverarbeitungseinheit (Central Processing Unit, CPU) ist programmiert, um die erforderlichen Berechnungen auszuführen, um die Existenz eines Ungleichgewichts zu bestimmen, und kann den echten Quadratwurzel-Mittelwert des Reststroms bestimmen, den herkömmliche Einrichtungen insbesondere für den Fall von nicht-sinusförmigen Stromwellenformen nicht richtig bestimmen tun. Die CPU kann programmiert werden, um ihr zu ermöglichen aus den Daten, die sie empfängt, zu bestimmen, ob ein bestimmtes Ereignis tatsächlich ein nicht akzeptables Leck ist, und zwar zuverlässiger als herkömmliche Einrichtungen. Zum Beispiel kann die CPU das historische Betriebsverhalten der Einheit berücksichtigen, wenn die Leckstromschwelle gesetzt wird, und kann Ereignisse ignorieren, die eine erkennbare „Signatur“ aufweisen. In dieser Weise kann eine verbesserte Toleranz gegenüber einem störenden Auslösen erhalten werden.

[0027] Eine Dezimierungsfilterung des Einbit-Datenstroms hoher Frequenz wird benötigt, um jeden Datenstrom auf ein Mehrbit-Digitalsignal bei einer vorgegebenen Abtastrate zu reduzieren. Beispielsweise kann jedes Stromsignal ein 23-Bit Signal bei einer Abtastrate von 64 mal der Netzfrequenz sein, aber eine niedrigere Auflösung bei niedrigeren Abtastraten kann verwendet werden, wenn eine nicht-lineare anstelle einer linearen Umwandlung akzeptabel ist. Die Dezimierungsfilterung ist typischerweise eine Funktion des Prozessors, wobei die vier Datenströme gefiltert werden, die gerade gleichzeitig ausgeführt werden, so dass Abtastwerte für sämtliche vier Nebenschlüsse gleichzeitig abgeleitet werden. Eine Schaltung, die eine derartige Anordnung verwendet, ist in **Fig. 6** gezeigt.

[0028] In einer alternativen Ausführungsform wie in **Fig. 7** gezeigt, kann/können ein oder mehrere Stufen der Dezimierungsfilterung durch eine Hardware aus-

geführt werden, die in der ASIC enthalten ist. Digitale Wörter mit mehreren Bits werden seriell über die Isolationsbarrieren anstelle eines Einbit-Signalstroms übertragen. Die Filterungsstufen können zwischen der ASIC und dem Prozessor aufgesplittet werden.

[0029] Wenn sowohl der Strom als auch die Spannung in dem in **Fig. 2** gezeigten System überwacht werden sollen, kann die Schaltung **15** wie in **Fig. 8** gezeigt sein, mit getrennten Modulations- und Filterungskomponenten für die zwei Signalströme und einer gemeinsamen seriellen Schnittstelle. Alternative getrennte serielle Schnittstellen können verwendet werden.

[0030] Die beschriebenen Anordnungen erlauben, dass eine sehr genaue Erfassung eines Stromungleichgewichts durchgeführt wird, sogar bei der Anwesenheit von Schalttransienten und DC Versätzen. Die Probleme, die sich von einer potentiellen Sättigung des Stromtransformatorkerns ergeben, werden vollständig vermieden.

[0031] Da die CPU tatsächliche Leistungsstrom- und Spannungsdaten von jedem der Blöcke **20** bis **23** empfängt, kann sie programmiert werden, um andere Berechnungen auszuführen, beispielsweise eine Strombeschränkung und einen Leistungsverbrauch. Somit kann eine RCD Einrichtung, die wie voranstehend beschrieben, konstruiert ist, auch die Funktionen eines herkömmlichen Schaltungsunterbrechers und/oder diejenigen eines Leistungsverbrauchs-Messgeräts bereitstellen, ohne das irgendwelche zusätzlichen Erfassungs- oder Analog-zu-Digital-Komponenten benötigt werden.

### Patentansprüche

1. Reststrom-Erfassungseinrichtung, umfassend eine Vielzahl von widerstandsbehafteten Nebenschlüssen (**14**) für eine Verbindung in jeweilige von Phasen- und Neutralleitungen, durch die ein Phasenleitungsstrom an eine Last fließen kann und durch die ein Neutralleitungsstrom von der Last fließen kann, und eine jeweilige Detektoreinrichtung (**15**), die für jeden Nebenschluss (**14**) vorgesehen ist, wobei jede jeweilige Detektoreinrichtung (**15**) auf die Spannung empfindlich ist, die sich über dem Nebenschluss (**14**) entwickelt, um ein Signal bereitzustellen, das den Strom anzeigt, der durch den Nebenschluss (**14**) fließt, wodurch irgendein Ungleichgewicht zwischen den Strömen, die durch die Nebenschlüsse (**14**) fließen, bestimmt werden kann.

2. Einrichtung nach Anspruch 1, bei der die Detektoreinrichtung einen Analog-zu-Digital-Wandler für jeden Nebenschluss (**14**) umfasst und ein Prozessor (**17**) vorgesehen ist, um die digitalen Signale von den Wählern zu empfangen und zu bestimmen, ob ein Stromungleichgewicht existiert.

3. Einrichtung nach Anspruch 1 oder Anspruch 2, bei der jeder Nebenschluss (**14**) die Form eines zu-

sammengesetzten Streifens (**11, 12**) mit leitenden Abschnitten (**13**) an seinen Enden und einem widerstandsbehafteten Abschnitt (**14**), der die leitenden Abschnitte untereinander verbindet, annimmt.

4. Einrichtung nach Anspruch 2 oder Anspruch 3, wenn vom Anspruch 2 abhängig, bei der der Analog-zu-Digital-Wandler für jeden Nebenschluss (**14**) einen Delta-Sigma-Modulator einschließt, der einen Einzeldigitaldatenstrom hoher Frequenz erzeugt, der durch eine Dezimierungsfilterung in einen Mehrbit-Digitaldatenstrom bei einer niedrigeren Frequenz umgewandelt wird.

5. Einrichtung nach Anspruch 2, 3, wenn vom Anspruch 2 abhängig, oder 4, bei der jeder Analog-zu-Digital-Wandler in der Form einer integrierten Schaltung (**15**) ist, die auf einem jeweiligen der widerstandsbehafteten Nebenschlüsse (**14**) angebracht ist.

6. Einrichtung nach Anspruch 5, bei der jede integrierte Schaltung (**15**) analoge Eingangsanschlüsse aufweist, die durch Zuleitungsdrähte (**40**) mit den zwei Kupferendenabschnitten (**13**) der entsprechenden der widerstandsbehafteten Nebenschlüsse (**14**) verbunden sind.

7. Einrichtung nach Anspruch 6, bei der die integrierte Schaltung (**15**) auch einen Anschluss aufweist, der mit einer Spannungsreferenzquelle verbunden ist, und einen zweiten Analog-zu-Digital-Wandler zum Bereitstellen eines Digitalsignalstroms in Abhängigkeit von der Spannung auf einem der Kupferendenabschnitten des zugehörigen der Nebenschlüsse (**14**) einschließt.

8. Reststrom-Erfassungseinrichtung nach irgendeinem der vorangehenden Ansprüche, betreibbar zum Ausführen einer zusätzlichen Funktion als ein herkömmlicher Schaltungsunterbrecher und/oder als herkömmliches Verbrauchsmessgerät.

9. Reststrom-Erfassungseinrichtung nach irgendeinem der vorangehenden Ansprüche, ferner umfassend eine Widerstandskette zum Koppeln zwischen einer Phasenleitung und der Neutralleitung, um die Reststrom-Erfassungseinrichtung mit einer unabhängigen Referenz zu versehen.

10. Reststrom-Erfassungseinrichtung nach Anspruch 9, wobei die Widerstandskette ein äußeres Paar von Widerständen und einen Zwischenwiderstand umfasst, wobei das äußere Paar einen niedrigeren Ohm'schen Wert als der Zwischenwiderstand aufweist.

11. Reststrom-Erfassungseinrichtung nach Anspruch 1, bei der: die Detektoreinrichtung einen Analog-zu-Digi-

tal-Wandler für jeden Nebenschluss (**14**) einschließt; die Einrichtung mit einem Prozessor (**17**) zum Empfangen der digitalen Signale von den Analog-zu-Digital-Wandlern und zum Bestimmen, ob irgendein Stromgleichgewicht existiert, versehen ist; die Einrichtung mit einer Widerstandskette zur Kopplung zwischen einer Phasenleitung und der Neutralleitung versehen ist, um die Einrichtung mit einer unabhängigen Referenz zu versehen, wobei die Widerstandskette ein äußeres Paar von Widerständen und einen Zwischenwiderstand umfasst, wobei das äußere Paar einen niedrigeren Ohm'schen Wert als der Zwischenwiderstand aufweist, wodurch in der Verwendung eine der Phasen- und Neutralleitungen als die unabhängige Referenz genommen werden kann; und der Prozessor (**17**) eine Software umfasst, die zum Empfangen von Spannungssignalen von der Widerstandskette betreibbar ist, um jede der Phasenleitungen gegenüber der Neutralleitung zu kalibrieren.

12. Reststrom-Erfassungseinrichtung nach irgendeinem der Ansprüche 9 bis 11, umfassend jeweilige Widerstandsketten zur Kopplung zwischen jeder Phasenleitung und der Neutralleitung eines Mehrphasensystems.

Es folgen 4 Blatt Zeichnungen

FIG 1

FIG 2

FIG. 3

FIG. 4

FIG. 5

FIG 6

FIG 7

FIG 8