(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-10281

(P2009-10281A)

(43) 公開日 平成21年1月15日(2009.1.15)

| (51) Int.Cl.             | F 1                | テーマコード (参考) |

|--------------------------|--------------------|-------------|

| HO 1 L 27/10 (2006.01)   | HO 1 L 27/10 4 6 1 | 5 F 0 3 8   |

| HO 1 L 21/8247 (2006.01) | HO 1 L 27/10 4 3 4 | 5 F 0 8 3   |

| HO 1 L 27/115 (2006.01)  | HO 1 L 27/10 4 8 1 | 5 F 1 0 1   |

| HO 1 L 29/788 (2006.01)  | HO 1 L 29/78 3 7 1 |             |

| HO 1 L 29/792 (2006.01)  | HO 1 L 27/04 C     |             |

審査請求 未請求 請求項の数 18 O L (全 29 頁) 最終頁に続く

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2007-172235 (P2007-172235) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区大手町二丁目6番2号 |

| (22) 出願日  | 平成19年6月29日 (2007. 6. 29)     | (74) 代理人 | 100080001<br>弁理士 筒井 大和                          |

|           |                              | (72) 発明者 | 川嶋 祥之<br>東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内       |

|           |                              | (72) 発明者 | 石井 泰之<br>東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内       |

|           |                              | (72) 発明者 | 鳥羽 功一<br>東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内       |

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】半導体基板上に不揮発性メモリセルと容量素子とを形成する半導体装置において、容量素子を製造する追加工程を実施することなく、高精度な容量素子を製造できる技術を提供する。

【解決手段】容量素子形成領域に形成される容量素子において、容量素子を形成する上部電極22全体を完全にシリサイド化する。すなわち、例えば、上部電極22全体をコバルトシリサイド膜31から形成する。これにより、上部電極22と容量絶縁膜26の境界で生じる上部電極22の空乏化を抑制することができ、高精度な容量素子を形成することができる。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

(a) 半導体基板と、

(b) 前記半導体基板上の第1領域に形成された不揮発性メモリセルと、

(c) 前記半導体基板上の第2領域に形成された容量素子とを備え、

前記容量素子は、

(c1) 前記半導体基板上に形成された下部電極と、

(c2) 前記下部電極上に形成された容量絶縁膜と、

(c3) 前記容量絶縁膜上に形成された上部電極とを有する半導体装置であって、

前記上部電極の全体は、金属シリサイド膜から形成されていることを特徴とする半導体装置。

10

## 【請求項 2】

請求項1記載の半導体装置であって、

前記金属シリサイド膜は、コバルトシリサイド膜、チタンシリサイド膜、あるいは、ニッケルシリサイド膜のいずれかの膜から形成されていることを特徴とする半導体装置。

## 【請求項 3】

請求項1記載の半導体装置であって、

前記不揮発性メモリセルは、

(b1) 前記半導体基板上に形成された第1ゲート絶縁膜と、

(b2) 前記第1ゲート絶縁膜上に形成されたコントロールゲート電極と、

(b3) 前記コントロールゲート電極の片側の側壁に形成されたメモリゲート電極と、

(b4) 前記コントロールゲート電極と前記メモリゲート電極の間および前記メモリゲート電極と前記半導体基板の間に形成された複数の絶縁膜からなる積層膜とを有し、

前記コントロールゲート電極と前記下部電極とは同一の膜を使用して形成され、

前記積層膜と前記容量絶縁膜とは同一の膜を使用して形成され、

前記メモリゲート電極と前記上部電極とは同一の膜を使用して形成されていることを特徴とする半導体装置。

20

## 【請求項 4】

請求項3記載の半導体装置であって、

前記メモリゲート電極と前記上部電極とは同一のポリシリコン膜を使用して形成され、

前記上部電極は、前記ポリシリコン膜をフルシリサイド化することにより形成された前記金属シリサイド膜から構成され、

前記メモリゲート電極は、前記ポリシリコン膜の一部をシリサイド化していることを特徴とする半導体装置。

30

## 【請求項 5】

請求項3記載の半導体装置であって、

前記積層膜は、第2ゲート絶縁膜と、前記第2ゲート絶縁膜上に形成された電荷蓄積膜と、前記電荷蓄積膜上に形成された第1絶縁膜から形成されていることを特徴とする半導体装置。

40

## 【請求項 6】

請求項5記載の半導体装置であって、

前記電荷蓄積膜は、トラップ準位を有する絶縁膜から形成されていることを特徴とする半導体装置。

## 【請求項 7】

請求項6記載の半導体装置であって、

前記電荷蓄積膜は、窒化シリコン膜から形成されていることを特徴とする半導体装置。

## 【請求項 8】

請求項1記載の半導体装置であって、

前記下部電極には負電圧を印加し、かつ、前記上部電極には正電圧を印加することにより、前記容量素子を動作させることを特徴とする半導体装置。

50

## 【請求項 9】

請求項 1 記載の半導体装置であって、

前記上部電極の面積は前記下部電極の面積よりも小さく、かつ、平面的に前記上部電極が前記下部電極に包含されていることを特徴とする半導体装置。

## 【請求項 10】

( a ) 半導体基板と、

( b ) 前記半導体基板上の第 1 領域に形成された不揮発性メモリセルと、

( c ) 前記半導体基板上の第 2 領域に形成された容量素子とを備え、

前記容量素子は、

( c 1 ) 前記半導体基板上に形成された下部電極と、

( c 2 ) 前記下部電極上に形成された容量絶縁膜と、

( c 3 ) 前記容量絶縁膜上に形成された上部電極とを有し、

前記上部電極は前記下部電極と平面的に重ならない部位を有しており、

前記上部電極の前記下部電極と平面的に重なる部位から前記上部電極の前記下部電極と平面的に重ならない部位への間には段差が形成され、前記段差の側壁にサイドウォールが形成されている半導体装置であって、

前記上部電極のうち表面に前記サイドウォールが形成されている以外の部位は金属シリサイド膜から形成されていることを特徴とする半導体装置。

## 【請求項 11】

請求項 10 記載の半導体装置であって、

前記上部電極と電気的に接続するプラグは、前記上部電極のうち前記下部電極と平面的に重ならない部位に形成されていることを特徴とする半導体装置。

## 【請求項 12】

( a ) 半導体基板と、

( b ) 前記半導体基板上の第 1 領域に形成された不揮発性メモリセルと、

( c ) 前記半導体基板上の第 2 領域に形成された容量素子とを備え、

前記容量素子は、

( c 1 ) 前記半導体基板上に形成された下部電極と、

( c 2 ) 前記下部電極上に形成された容量絶縁膜と、

( c 3 ) 前記容量絶縁膜上に形成された上部電極とを有する半導体装置であって、

前記上部電極を構成する膜は部分的にシリサイド化されており、

前記上部電極のうちシリサイド化されていない膜の膜厚は、前記容量絶縁膜の膜厚の 10 % 以下であることを特徴とする半導体装置。

## 【請求項 13】

( a ) 半導体基板と、

( b ) 前記半導体基板上の第 1 領域に形成された不揮発性メモリセルと、

( c ) 前記半導体基板上の第 2 領域に形成された容量素子とを備え、

前記不揮発性メモリセルは、

( b 1 ) 前記半導体基板上に形成された第 1 ゲート絶縁膜と、

( b 2 ) 前記第 1 ゲート絶縁膜上に形成されたコントロールゲート電極と、

( b 3 ) 前記コントロールゲート電極の片側の側壁に形成されたメモリゲート電極と、

( b 4 ) 前記コントロールゲート電極と前記メモリゲート電極の間および前記メモリゲート電極と前記半導体基板の間に形成された複数の絶縁膜からなる積層膜とを有し、

前記容量素子は、

( c 1 ) 前記半導体基板上に形成された下部電極と、

( c 2 ) 前記下部電極上に形成された容量絶縁膜と、

( c 3 ) 前記容量絶縁膜上に形成された上部電極とを有する半導体装置であって、

前記メモリゲート電極と前記上部電極とは同一の金属膜から形成されていることを特徴とする半導体装置。

## 【請求項 14】

10

20

30

40

50

請求項 1 3 記載の半導体装置であって、

前記コントロールゲート電極と前記下部電極とは同一の金属膜から形成されていることを特徴とする半導体装置。

【請求項 1 5】

半導体基板の第 1 領域上に不揮発性メモリセルを形成し、前記半導体基板の第 2 領域に容量素子を形成する半導体装置の製造方法であって、

( a ) 前記半導体基板上に第 1 ゲート絶縁膜を形成する工程と、

( b ) 前記第 1 ゲート絶縁膜上に第 1 ポリシリコン膜を形成する工程と、

( c ) 前記第 1 ポリシリコン膜を加工することにより、前記第 1 領域に前記不揮発性メモリセルのコントロールゲート電極を形成し、かつ、前記第 2 領域に前記容量素子の下部電極を形成する工程と、

( d ) 前記半導体基板の前記第 1 領域と前記第 2 領域を含む全面に複数の絶縁膜を積層した積層膜を形成する工程と、

( e ) 前記積層膜上に第 2 ポリシリコン膜を形成する工程と、

( f ) 前記第 2 ポリシリコン膜を加工することにより、前記第 1 領域では前記コントロールゲート電極の両側の側壁にだけ前記第 2 ポリシリコン膜を残し、かつ、前記第 2 領域では前記第 2 ポリシリコン膜よりなる前記容量素子の上部電極を形成する工程と、

( g ) 前記コントロールゲート電極の片側の側壁に形成されている前記第 2 ポリシリコン膜を除去することにより、前記コントロールゲート電極のもう一方の片側の側壁に残存する前記第 2 ポリシリコン膜からなるメモリゲート電極を形成する工程と、

( h ) 前記半導体基板に露出している前記積層膜を除去することにより、前記第 1 領域では、前記コントロールゲート電極と前記メモリゲート電極の間および前記メモリゲート電極と前記半導体基板の間に残存する前記積層膜により、第 2 ゲート絶縁膜、前記第 2 ゲート絶縁膜上に形成される電荷蓄積膜および前記電荷蓄積膜上に形成される第 1 絶縁膜を形成し、かつ、前記第 2 領域では、前記上部電極で覆われて残存する前記積層膜よりなる容量絶縁膜を形成する工程と、

( i ) 前記半導体基板の前記第 1 領域と前記第 2 領域を含む全面に金属膜を形成して、前記金属膜と前記コントロールゲート電極、前記金属膜と前記メモリゲート電極および前記金属膜と前記上部電極とを接触する工程と、

( j ) 前記半導体基板に対して熱処理を施すことにより、前記コントロールゲート電極、前記メモリゲート電極および前記上部電極に金属シリサイド膜を形成する工程とを備え、

前記容量素子の前記上部電極のうちシリサイド化されていない膜の膜厚は、前記容量絶縁膜の膜厚の 10 % 以下であることを特徴とする半導体装置の製造方法。

【請求項 1 6】

請求項 1 5 記載の半導体装置の製造方法であって、

前記容量素子の前記上部電極はフルシリサイド化されていることを特徴とする半導体装置の製造方法。

【請求項 1 7】

半導体基板の第 1 領域上に不揮発性メモリセルを形成し、前記半導体基板の第 2 領域に容量素子を形成する半導体装置の製造方法であって、

( a ) 前記半導体基板上に第 1 ゲート絶縁膜を形成する工程と、

( b ) 前記第 1 ゲート絶縁膜上に導体膜を形成する工程と、

( c ) 前記導体膜を加工することにより、前記第 1 領域に前記不揮発性メモリセルのコントロールゲート電極を形成し、かつ、前記第 2 領域に前記容量素子の下部電極を形成する工程と、

( d ) 前記半導体基板の前記第 1 領域と前記第 2 領域を含む全面に複数の絶縁膜を積層した積層膜を形成する工程と、

( e ) 前記積層膜上に金属膜を形成する工程と、

( f ) 前記金属膜を加工することにより、前記第 1 領域では前記コントロールゲート電

10

20

30

40

50

極の両側の側壁にだけ前記金属膜を残し、かつ、前記第2領域では前記金属膜よりなる前記容量素子の上部電極を形成する工程と、

(g) 前記コントロールゲート電極の片側の側壁に形成されている前記金属膜を除去することにより、前記コントロールゲート電極のもう一方の片側の側壁に残存する前記金属膜からなるメモリゲート電極を形成する工程と、

(h) 前記半導体基板に露出している前記積層膜を除去することにより、前記第1領域では、前記コントロールゲート電極と前記メモリゲート電極の間および前記メモリゲート電極と前記半導体基板の間に残存する前記積層膜により、第2ゲート絶縁膜、前記第2ゲート絶縁膜上に形成される電荷蓄積膜および前記電荷蓄積膜上に形成される第1絶縁膜を形成し、かつ、前記第2領域では、前記上部電極で覆われて残存する前記積層膜よりなる容量絶縁膜を形成する工程とを備えることを特徴とする半導体装置の製造方法。

10

【請求項18】

請求項17記載の半導体装置の製造方法であって、

前記導体膜は金属膜であることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、半導体基板上に不揮発性メモリセルと容量素子を形成する技術に適用して有効な技術に関するものである。

【背景技術】

【0002】

特開平7-321234号公報（特許文献1）には、半導体基板上にS R A M (Static Random Access Memory) のメモリセルとメモリセル以外の領域にC M I S F E T (Complementary Metal Insulator Semiconductor Field Effect Transistor) を使用した回路素子群を形成する技術が開示されている。この技術において、周辺領域の回路素子群に容量素子を形成し、この容量素子をゲート電極とローカル配線から形成するとしている。そして、ローカル配線の一部をシリサイド化している。

【特許文献1】特開平7-321234号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

半導体装置として1つの半導体チップにマイコンを形成しているものがある。このマイコンを形成した半導体チップには、C M I S F E T (Complementary Metal Insulator Semiconductor Field Effect Transistor) などの論理回路からなる中央演算処理部（C P U : Central Processing Unit）やメモリあるいはアナログ回路などが形成されている。

【0004】

半導体チップに形成されているメモリとしては、例えば、電気的に書き換え可能な不揮発性メモリが使用される。電気的に書き込み・消去が可能な不揮発性メモリ（不揮発性半導体記憶装置）として、E E P R O M (Electrically Erasable and Programmable Read Only Memory) やフラッシュメモリが広く使用されている。現在広く用いられているE E P R O M やフラッシュメモリに代表されるこれらの不揮発性メモリは、M O S (Metal Oxide Semiconductor) トランジスタのゲート電極下に、酸化シリコン膜で囲まれた導電性の浮遊ゲート電極やトラップ性絶縁膜など電荷蓄積膜を有しており、浮遊ゲート電極やトラップ性絶縁膜での電荷蓄積状態によってトランジスタのしきい値が異なることを利用して情報を記憶する。

40

【0005】

このトラップ性絶縁膜とは、電荷の蓄積可能なトラップ準位を有する絶縁膜をいい、一例として、窒化シリコン膜等があげられる。このようなトラップ性絶縁膜への電荷の注入・放出によってM O S トランジスタのしきい値をシフトさせ記憶素子として動作させる。トラップ性絶縁膜を電荷蓄積膜とする不揮発性メモリをM O N O S (Metal Oxide Nitrid

50

e Oxide Semiconductor) 型トランジスタと呼んでおり、電荷蓄積膜に導電性の浮遊ゲート電極を使用する場合に比べ、離散的なトラップ準位に電荷を蓄積するためにデータ保持の信頼性に優れる。また、データ保持の信頼性に優れているためにトラップ性絶縁膜上下の酸化シリコン膜の膜厚を薄膜化でき、書き込み・消去動作の低電圧化が可能である等の利点を有する。

【0006】

上述したような不揮発性メモリを動作させるために、半導体チップには昇圧回路などの駆動回路が形成されている。この駆動回路には高精度の容量素子が必要とされる。また、マイコンを形成した半導体チップには、アナログ回路も形成されており、このアナログ回路にも高精度の容量素子が必要とされる。したがって、半導体チップには、上述した不揮発性メモリやMISFETの他に容量素子も形成されている。

10

【0007】

この容量素子は、例えば、配線層に形成される。具体的には、配線層間にある絶縁膜を容量絶縁膜とし、かつ、上部電極および下部電極を配線で使用する金属膜より構成するものがある。この容量素子は、例えば、MIM (Metal Insulator Metal) 容量と呼ばれる。このMIM容量によれば、配線用の金属膜を上部電極および下部電極に使用することから、高精度の容量素子を形成することができる。

【0008】

しかし、MIM容量を形成するのは、MIM容量を形成するための追加工程が必要となる。このため、半導体装置のコストが上昇するという問題点がある。そこで、容量素子を製造する追加工程を実施することなく、容量素子を半導体基板上に形成する技術がある。

20

【0009】

例えば、不揮発性メモリセルは、半導体基板上にゲート絶縁膜を介してコントロールゲート電極が形成されており、このコントロールゲート電極の片側の側壁に積層膜を介してサイドウォール状のメモリゲート電極が形成された構造をしている。このような不揮発性メモリセルを製造する工程を使用して容量素子も同時に形成することが行なわれている。具体的には、不揮発性メモリセルのコントロールゲート電極を形成する工程で容量素子の下部電極を形成し、不揮発性メモリの電荷蓄積膜を含む積層膜を形成する工程で、容量素子の容量絶縁膜を形成することが行なわれている。そして、不揮発性メモリセルのメモリゲート電極を形成する工程で容量素子の上部電極を形成することが行なわれている。このようにして、不揮発性メモリセルを形成する工程で容量素子を形成することができるので、容量素子を形成する新たな工程を追加することなく、半導体基板上に容量素子を形成することができる。したがって、半導体基板上に容量素子を形成しても半導体装置の製造コストが上昇することを防止できる。

30

【0010】

ここで、不揮発性メモリセルのコントロールゲート電極およびメモリゲート電極は、通常、不純物を導入したポリシリコン膜が使用されている。このため、容量素子の上部電極および下部電極もポリシリコン膜が使用されることになる。ところが、容量素子の上部電極および下部電極にポリシリコン膜を使用すると、容量素子に電圧を印加した場合に、ポリシリコン膜が空乏化する。ポリシリコン膜が空乏化するということは、空乏化した領域が絶縁膜として機能することになるから、容量絶縁膜の膜厚が空乏化した膜厚の分だけ変動することになる。容量素子の容量は容量絶縁膜の膜厚によって決定されることから、この容量絶縁膜の膜厚が変動することによって、容量素子の容量が変動することになる。すなわち、ポリシリコン膜の空乏化により容量素子の容量が変動し、高精度な容量素子を形成することができない問題点が発生する。

40

【0011】

本発明の目的は、半導体基板上に不揮発性メモリセルと容量素子とを形成する半導体装置において、容量素子を製造する追加工程を実施することなく、高精度な容量素子を製造できる技術を提供することにある。つまり、半導体基板上に不揮発性メモリセルと容量素子とを形成する半導体装置において、半導体装置の製造コストを上昇させることなく、高

50

精度な容量素子を製造できる技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

本発明による半導体装置は、(a)半導体基板と、(b)前記半導体基板上の第1領域に形成された不揮発性メモリセルと、(c)前記半導体基板上の第2領域に形成された容量素子とを備える。そして、前記容量素子は、(c1)前記半導体基板上に形成された下部電極と、(c2)前記下部電極上に形成された容量絶縁膜と、(c3)前記容量絶縁膜上に形成された上部電極とを有する。ここで、前記上部電極の全体は、金属シリサイド膜から形成されていることを特徴とするものである。

10

【0015】

また、本発明による半導体装置の製造方法は、半導体基板の第1領域上に不揮発性メモリセルを形成し、前記半導体基板の第2領域に容量素子を形成するものである。そして、(a)前記半導体基板上に第1ゲート絶縁膜を形成する工程と、(b)前記第1ゲート絶縁膜上に第1ポリシリコン膜を形成する工程と、(c)前記第1ポリシリコン膜を加工することにより、前記第1領域に前記不揮発性メモリセルのコントロールゲート電極を形成し、かつ、前記第2領域に前記容量素子の下部電極を形成する工程とを有する。さらに、(d)前記半導体基板の前記第1領域と前記第2領域を含む全面に複数の絶縁膜を積層した積層膜を形成する工程と、(e)前記積層膜上に第2ポリシリコン膜を形成する工程とを有する。そして、(f)前記第2ポリシリコン膜を加工することにより、前記第1領域では前記コントロールゲート電極の両側の側壁にだけ前記第2ポリシリコン膜を残し、かつ、前記第2領域では前記第2ポリシリコン膜よりなる前記容量素子の上部電極を形成する工程とを有する。さらに、(g)前記コントロールゲート電極の片側の側壁に形成されている前記第2ポリシリコン膜を除去することにより、前記コントロールゲート電極のもう一方の片側の側壁に残存する前記第2ポリシリコン膜からなるメモリゲート電極を形成する工程とを有する。続いて、(h)前記半導体基板に露出している前記積層膜を除去することにより、前記第1領域では、前記コントロールゲート電極と前記メモリゲート電極の間および前記メモリゲート電極と前記半導体基板の間に残存する前記積層膜により、第2ゲート絶縁膜、前記第2ゲート絶縁膜上に形成される電荷蓄積膜および前記電荷蓄積膜上に形成される第1絶縁膜を形成し、かつ、前記第2領域では、前記上部電極で覆われて残存する前記積層膜よりなる容量絶縁膜を形成する工程とを有する。次に、(i)前記半導体基板の前記第1領域と前記第2領域を含む全面に金属膜を形成して、前記金属膜と前記コントロールゲート電極、前記金属膜と前記メモリゲート電極および前記金属膜と前記上部電極とを接触する工程とを有する。その後、(j)前記半導体基板に対して熱処理を施すことにより、前記コントロールゲート電極、前記メモリゲート電極および前記上部電極に金属シリサイド膜を形成する工程とを有する。ここで、前記容量素子の前記上部電極のうちシリサイド化されていない膜の膜厚は、前記容量絶縁膜の膜厚の10%以下であることを特徴とするものである。

20

20

30

30

40

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

不揮発性メモリセルを形成する工程を利用して容量素子を形成することができるので、容量素子を形成する追加工程を実施する必要がなく、半導体装置の製造コストを抑えるこ

50

とができる。このとき、容量素子の上部電極はポリシリコン膜から形成されるが、不揮発性メモリセルの製造工程で実施されるシリサイド工程を利用して、容量素子の上部電極全体を金属シリサイド膜にする。これにより、容量素子の上部電極が空乏化することなく、高精度な容量素子を製造することができる。

【発明を実施するための最良の形態】

【0018】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0019】

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0020】

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0021】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0022】

また、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。なお、図面をわかりやすくするために平面図であってもハッチングを付す場合がある。

【0023】

（実施の形態1）

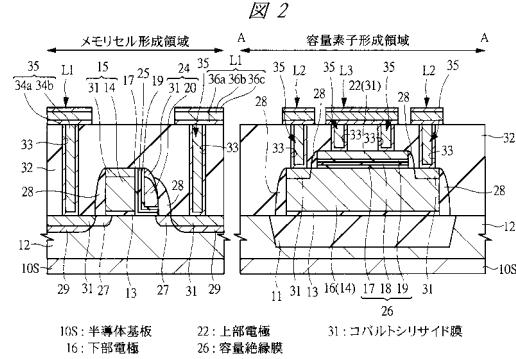

図1は、例えば、マイコンを形成した半導体チップ（半導体基板）CHPを示す平面図であり、半導体チップCHPに形成されたそれぞれの素子のレイアウト構成を示した図である。図1において、半導体チップCHPは、CPU（Central Processing Unit）1、RAM（Random Access Memory）2、アナログ回路3およびフラッシュメモリ4を有している。

【0024】

CPU（回路）1は、中央演算処理部とも呼ばれ、コンピュータなどの心臓部にあたる。このCPU1は、記憶装置から命令を読み出して解読し、それに基づいて多種多様な演算や制御を行なうものであり、処理の高速性が要求される。したがって、CPU1を構成しているMISFETには、半導体チップCHPに形成されている素子の中で、相対的に大きな電流駆動力が必要とされる。すなわち低耐圧MISFETで形成される。

【0025】

RAM（回路）2は、記憶情報をランダムに、すなわち隨時記憶されている記憶情報を読み出したり、記憶情報を新たに書き込んだりすることができるメモリであり、隨時書き込み読み出しができるメモリとも呼ばれる。I CメモリとしてのRAMには、ダイナミック回路を用いたDRAM（Dynamic RAM）とスタティック回路を用いたSRAM（Static RAM）の2種類がある。DRAMは、記憶保持動作が必要な隨時書き込み読み出しメモリであり、SRAMは、記憶保持動作が不要な隨時書き込み読み出しメモリである。これらRAM2も動作の高速性が要求されるため、RAM2を構成しているMISFETには、相対的に大きな電流駆動力が必要とされている。すなわち低耐圧MISFETで形成される。

【0026】

10

20

30

40

50

アナログ回路3は、時間的に連続して変化する電圧や電流の信号、すなわちアナログ信号を扱う回路であり、例えば增幅回路、変換回路、変調回路、発振回路、電源回路などから構成されている。これらアナログ回路3は、半導体チップCHPに形成された素子の中で、相対的に高耐圧のMISFETが使用される。

【0027】

フラッシュメモリ4は、書き込み動作および消去動作とも電気的に書き換え可能な不揮発性メモリの一種であり、電気的消去可能なプログラマブル読み出し専用メモリとも呼ばれる。このフラッシュメモリ4のメモリセルには、メモリセル選択用のMISFETと、記憶(メモリ)用の例えばMONOS(Metal Oxide Nitride Oxide Semiconductor)型FETから構成される。フラッシュメモリの書き込み動作には、例えばホットエレクトロン注入またはファウラーノルドハイム型トンネル現象を利用し、消去動作には、ファウラーノルドハイム型トンネル現象またはホットホール注入を利用する。なお、ホットエレクトロン注入と、ホットホール注入とを逆にしてもよいのは勿論である。

10

【0028】

上述したようなフラッシュメモリ4を動作させるために、半導体チップには昇圧回路などの駆動回路が形成されている。この駆動回路には高精度の容量素子が必要とされる。また、上述したアナログ回路3にも高精度の容量素子が必要とされる。したがって、半導体チップCHPには、上述したフラッシュメモリ4のメモリセルやMISFETの他に容量素子も形成されている。本実施の形態1では、半導体チップCHPに形成される容量素子の構造に特徴の1つがある。この容量素子は、後述するようにフラッシュメモリ4のメモリセルを形成する工程で同時に形成されるので、以下では、半導体チップCHPに形成されるフラッシュメモリ4のメモリセルと、アナログ回路3やフラッシュメモリ4の駆動回路に使用される容量素子とを図示しながら、容量素子の構造について説明する。

20

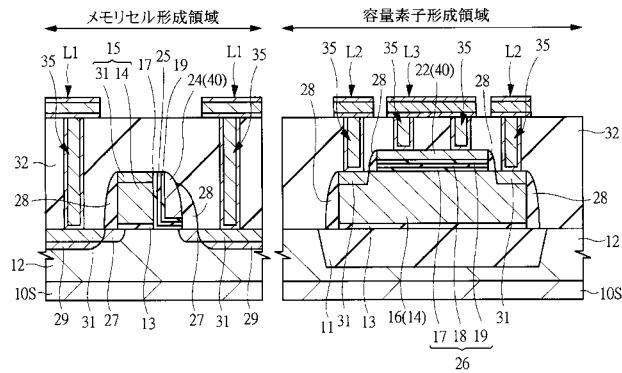

【0029】

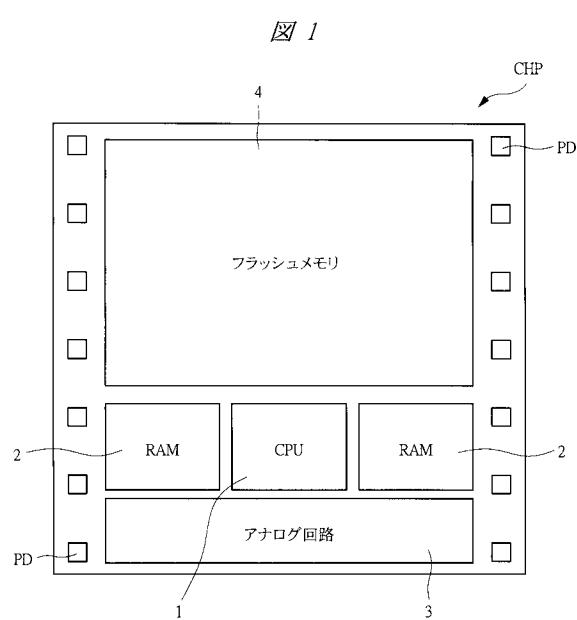

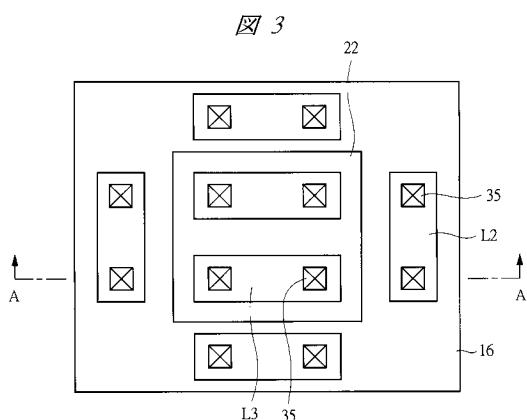

図2は、フラッシュメモリのメモリセルの構造と、アナログ回路などに形成されている容量素子の構造を示す断面図である。図2において、メモリセルは半導体チップのメモリセル形成領域(第1領域)に形成され、容量素子は半導体チップの容量素子形成領域(第2領域)に形成される。

【0030】

まず、フラッシュメモリのメモリセルの構造について説明する。図2に示すように、メモリセル形成領域において、半導体基板10S上にp型ウェル12が形成され、このp型ウェル12上にメモリセルが形成されている。このメモリセルは、メモリセルを選択する選択部と情報を記憶する記憶部から構成されている。まず、メモリセルを選択する選択部の構成について説明する。メモリセルは、半導体基板10S(p型ウェル12)上に形成されたゲート絶縁膜(第1ゲート絶縁膜)13を有しており、このゲート絶縁膜13上にコントロールゲート電極(制御電極)15が形成されている。ゲート絶縁膜13は、例えば、酸化シリコン膜から形成されており、コントロールゲート電極15は、例えば、ポリシリコン膜14とポリシリコン膜14上に形成されているコバルトシリサイド膜31から形成されている。コバルトシリサイド膜31は、コントロールゲート電極15の低抵抗化のために形成されている。このコントロールゲート電極15は、メモリセルを選択する機能を有している。つまり、コントロールゲート電極15によって特定のメモリセルを選択し、選択したメモリセルに対して書き込み動作や消去動作あるいは読み出し動作をするようになっている。

30

【0031】

次に、メモリセルの記憶部の構成について説明する。コントロールゲート電極15の片側の側壁には絶縁膜からなる積層膜を介してメモリゲート電極24が形成されている。メモリゲート電極24は、コントロールゲート電極15の片側の側壁に形成されたサイドウォール状の形状をしており、ポリシリコン膜20とポリシリコン膜20上に形成されているコバルトシリサイド膜31から形成されている。コバルトシリサイド膜31は、メモリゲート電極24の低抵抗化のために形成されている。

40

50

## 【0032】

コントロールゲート電極15とメモリゲート電極24の間およびメモリゲート電極24と半導体基板10Sとの間には、積層膜が形成されている。この積層膜は、半導体基板10S上に形成されている酸化シリコン膜(第2ゲート絶縁膜)17と、酸化シリコン膜17上に形成されている電荷蓄積膜25と、電荷蓄積膜25上に形成されている酸化シリコン膜(第1絶縁膜)19から構成されている。酸化シリコン膜17は、メモリゲート電極24と半導体基板10Sとの間に形成されるゲート絶縁膜として機能する。この酸化シリコン膜17からなるゲート絶縁膜は、トンネル絶縁膜としての機能も有する。例えばメモリセルの記憶部は、半導体基板10Sから酸化シリコン膜17を介して電荷蓄積膜25に電子を注入したり、電荷蓄積膜25に正孔を注入したりして情報の記憶や消去を行なうため、酸化シリコン膜17は、トンネル絶縁膜として機能する。

10

## 【0033】

そして、この酸化シリコン膜17上に形成されている電荷蓄積膜25は、電荷を蓄積する機能を有している。具体的に、本実施の形態1では、電荷蓄積膜25を窒化シリコン膜から形成している。本実施の形態1におけるメモリセルの記憶部は、電荷蓄積膜25に蓄積される電荷の有無によって、メモリゲート電極24下の半導体基板10S内を流れる電流を制御することにより、情報を記憶するようになっている。つまり、電荷蓄積膜25に蓄積される電荷の有無によって、メモリゲート電極24下の半導体基板10S内を流れる電流のしきい値電圧が変化することを利用して情報を記憶している。

20

## 【0034】

本実施の形態1では、電荷蓄積膜25としてトラップ準位を有する絶縁膜を使用している。このトラップ準位を有する絶縁膜の一例として窒化シリコン膜が挙げられるが、窒化シリコン膜に限らず、例えば、酸化アルミニウム膜(アルミナ)などを使用してもよい。電荷蓄積膜25としてトラップ準位を有する絶縁膜を使用する場合、電荷は絶縁膜に形成されているトラップ準位に捕獲される。このようにトラップ準位に電荷を捕獲することにより、絶縁膜中に電荷を蓄積するようになっている。

20

## 【0035】

従来、電荷蓄積膜25としてポリシリコン膜が主に使用されてきたが、電荷蓄積膜25としてポリシリコン膜を使用した場合、電荷蓄積膜25を取り囲む酸化シリコン膜17あるいは酸化シリコン膜19のどこか一部に欠陥があると、電荷蓄積膜25が導体膜であるため、異常リークにより電荷蓄積膜25に蓄積された電荷がすべて抜けてしまうことが起こりうる。

30

## 【0036】

そこで、電荷蓄積膜25として、絶縁体である窒化シリコン膜が使用されてきている。この場合、データ記憶に寄与する電荷は、窒化シリコン膜中に存在する離散的なトラップ準位(捕獲準位)に蓄積される。したがって、電荷蓄積膜25を取り巻く酸化シリコン膜17や酸化シリコン膜19中の一部に欠陥が生じても、電荷は電荷蓄積膜25の離散的なトラップ準位に蓄積されているため、すべての電荷が電荷蓄積膜25から抜け出てしまうことがない。このため、データ保持の信頼性向上を図ることができる。

40

## 【0037】

このような理由から、電荷蓄積膜25として、窒化シリコン膜に限らず、離散的なトラップ準位を含むような膜を使用することにより、データ保持の信頼性を向上することができる。

## 【0038】

次に、コントロールゲート電極15の側壁のうち、一方の片側にはメモリゲート電極24が形成されているが、もう一方の片側には、酸化シリコン膜よりなるサイドウォール28が形成されている。同様に、メモリゲート電極24の側壁のうち、一方の片側にはコントロールゲート電極15が形成されており、もう一方の片側にも酸化シリコン膜よりなるサイドウォール28が形成されている。

50

## 【0039】

サイドウォール 2 8 の直下にある半導体基板 1 0 S 内には、n 型半導体領域である一対の浅い低濃度不純物拡散領域 2 7 が形成されており、この一対の浅い低濃度不純物拡散領域 2 7 に接する外側の領域に一対の深い高濃度不純物拡散領域 2 9 が形成されている。この深い高濃度不純物拡散領域 2 9 も n 型半導体領域であり、高濃度不純物拡散領域 2 9 の表面にはコバルトシリサイド膜 3 1 が形成されている。一対の低濃度不純物拡散領域 2 7 と一対の高濃度不純物拡散領域 2 9 によって、メモリセルのソース領域あるいはドレイン領域が形成される。ソース領域とドレイン領域を低濃度不純物拡散領域 2 7 と高濃度不純物拡散領域 2 9 で形成することにより、ソース領域とドレイン領域を L D D (Lightly Doped Drain) 構造とすることができます。ここで、ゲート絶縁膜 1 3 およびゲート絶縁膜 1 3 上に形成されたコントロールゲート電極 1 5 および上述したソース領域とドレイン領域によって構成されるトランジスタを選択トランジスタと呼ぶことにする。一方、酸化シリコン膜 1 7 、電荷蓄積膜 2 5 および酸化シリコン膜 1 9 からなる積層膜とこの積層膜上に形成されているメモリゲート電極 2 4 、上述したソース領域とドレイン領域によって構成されるトランジスタをメモリトランジスタと呼ぶことにする。これにより、メモリセルの選択部は選択トランジスタから構成され、メモリセルの記憶部はメモリトランジスタから構成されているということができる。このようにして、メモリセルが構成されている。

## 【0040】

次に、メモリセルと接続する配線構造について説明する。メモリセル上には、メモリセルを覆うように層間絶縁膜である酸化シリコン膜 3 2 が形成されている。この酸化シリコン膜 3 2 には、酸化シリコン膜 3 2 を貫通してソース領域やドレイン領域を構成するコバルトシリサイド膜 3 1 に達するコンタクトホール 3 3 が形成されている。コンタクトホール 3 3 の内部には、バリア導体膜であるチタン / 窒化チタン膜 3 4 a が形成され、コンタクトホール 3 3 を埋め込むようにタンゲステン膜 3 4 b が形成されている。このように、コンタクトホール 3 3 にチタン / 窒化チタン膜 3 4 a およびタンゲステン膜 3 4 b を埋め込むことにより、導電性のプラグ 3 5 が形成されている。そして、層間絶縁膜である酸化シリコン膜 3 2 上には、配線 L 1 が形成されており、この配線 L 1 とプラグ 3 5 が電気的に接続されている。配線 L 1 は、例えば、チタン / 窒化チタン膜 3 6 a 、アルミニウム膜 3 6 b およびチタン / 窒化チタン膜 3 6 c の積層膜から形成されている。

## 【0041】

続いて、本実施の形態 1 の特徴の 1 つである容量素子の構造について説明する。図 2 において、半導体基板 1 0 S 上に p 型ウェル 1 2 が形成されており、この p 型ウェル 1 2 に素子分離領域 1 1 が形成されている。素子分離領域 1 1 は、素子を電気的に分離する領域であり、例えば、高耐圧 M I S F E T と低耐圧 M I S F E T とを分離するために形成される。この素子分離領域 1 1 は、さらに、容量素子形成領域にも形成されている。容量素子形成領域に形成されている素子分離領域 1 1 は、この素子分離領域 1 1 上に形成される容量素子を半導体基板 1 0 S から絶縁する機能を有している。すなわち、容量素子は素子分離領域 1 1 上に形成される。

## 【0042】

素子分離領域 1 1 上には、ゲート絶縁膜 1 3 が形成されており、このゲート絶縁膜 1 3 上に容量素子の下部電極 1 6 が形成されている。この下部電極 1 6 はポリシリコン膜 1 4 から形成されている。ここで、下部電極 1 6 はメモリセル形成領域に形成されているコントロールゲート電極 1 5 を構成するポリシリコン膜 1 4 と同一の膜から形成されている。すなわち、後述する製造方法で説明するが、容量素子の下部電極 1 6 は、メモリセルのコントロールゲート電極 1 5 を形成する工程で同時に形成されるのである。

## 【0043】

そして、この下部電極 1 6 上には、容量絶縁膜 2 6 が形成されている。この容量絶縁膜 2 6 は、酸化シリコン膜 1 7 、酸化シリコン膜上に形成されている窒化シリコン膜 1 8 および窒化シリコン膜 1 8 上に形成されている酸化シリコン膜 1 9 から形成されている。つまり、メモリセルのメモリトランジスタを構成する積層膜と同一の膜から形成されている。言い換えれば、メモリセルの酸化シリコン膜、電荷蓄積膜 2 5 (窒化シリコン膜 1 8 )

10

20

30

40

50

および酸化シリコン膜 19 よりなる積層膜が容量素子形成領域においては、容量素子の容量絶縁膜 26 となっているのである。

【0044】

容量絶縁膜 26 上には、上部電極 22 が形成されている。この上部電極 22 は、上部電極 22 全体がコバルトシリサイド膜 31 から形成されている。このように上部電極 22 を完全にフルシリサイド化して金属シリサイド膜から形成するように構成する点が本実施の形態 1 における特徴の 1 つである。この上部電極 22 は、メモリセルのメモリゲート電極 24 を形成する工程で同時に形成される膜である。つまり、メモリセルのメモリゲート電極 24 10 はポリシリコン膜 20 と、このポリシリコン膜 20 上に形成されたコバルトシリサイド膜 31 によって構成されているが、容量素子の上部電極 22 もメモリゲート電極 24 を構成するポリシリコン膜 20 で形成する。その後、メモリゲート電極 24 を構成するポリシリコン膜 20 の一部をシリサイド化する工程で、ポリシリコン膜から構成されている上部電極 22 を完全にシリサイド化する。これにより、容量素子の上部電極 22 をコバルトシリサイド膜 31 から形成することができる。

【0045】

そして、容量絶縁膜 26 および上部電極 22 の側壁にはサイドウォール 28 が形成され、下部電極 16 の側壁にもサイドウォール 28 が形成されている。このサイドウォール 28 は、容量素子に必要なものではなく、メモリセルのサイドウォール 28 を形成する際、付隨的に形成されるものである。

【0046】

このように構成された容量素子は、層間絶縁膜を介して配線と接続されている。この配線と接続する構成について説明する。図 2 に示すように、下部電極 16 の幅は容量絶縁膜 26 の幅および上部電極 22 の幅に比べて大きくなっている。下部電極 16 の表面には、層間絶縁膜である酸化シリコン膜 32 を貫通するプラグ 35 が電気的に接続されている。このプラグ 35 と接続する領域では、下部電極 16 がシリサイド化されている。すなわち、プラグ 35 と接続する下部電極 16 の表面にはコバルトシリサイド膜 31 が形成されている。プラグ 35 は、酸化シリコン膜 32 上に形成された配線 L2 と接続している。一方、上部電極 22 にも酸化シリコン膜 32 を貫通して上部電極 22 に達するプラグ 35 が形成されている。このプラグ 35 は、層間絶縁膜である酸化シリコン膜 32 上に形成されている配線 L3 と電気的に接続されている。

【0047】

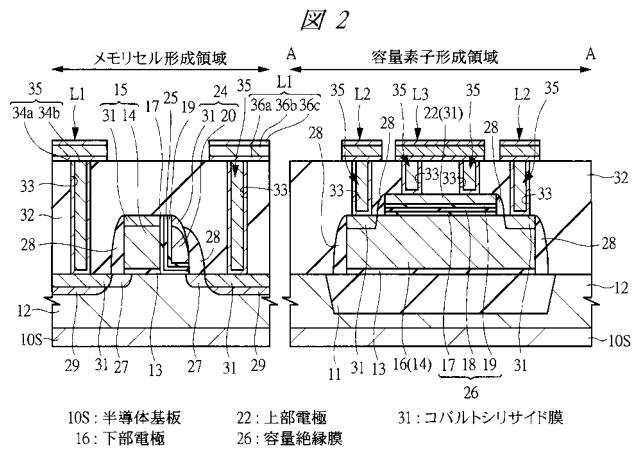

次に、本実施の形態 1 における容量素子を上面から見たレイアウト構成について説明する。図 3 は、本実施の形態 1 における容量素子の平面図を示しており、図 3 の A-A 線で切断した断面が図 2 の容量素子形成領域に対応する。

【0048】

図 3 に示すように、容量素子の下部電極 16 は矩形形状をしており、この下部電極 16 上に容量絶縁膜（図示せず）を介して上部電極 22 が形成されている。上部電極 22 も矩形形状をしており、上部電極 22 の面積は下部電極 16 の面積よりも小さくなっている。したがって、上部電極 22 は平面的に下部電極 16 に包含されるようになっている。このようなレイアウト構成では、実質的な容量素子の容量は、容量絶縁膜の誘電率と膜厚のほか、上部電極 22 と下部電極 16 の平面的に重なっている領域で決まる。つまり、下部電極 16 に内包される上部電極 22 の面積によって、容量素子の容量が決定される。

【0049】

上部電極 22 の面積を下部電極 16 の面積よりも小さくするのは、図 3 に示すように、下部電極 16 と配線 L2 とをプラグ 35 で接続する領域を確保する必要があるからである。このように上部電極 22 の面積を下部電極 16 の面積よりも小さくすることにより、下部電極 16 と配線 L2 との電気的な接続を容易にすることができる。なお、上部電極 22 は、上部電極 22 上に形成されたプラグ 35 を介して配線 L3 と電気的に接続されている。

【0050】

10

20

30

40

50

本実施の形態 1 における容量素子は上記のように構成されており、以下に、その特徴的な構成について説明する。本実施の形態 1 における容量素子の特徴の 1 つは、図 2 にも示すように、上部電極 2 2 を完全にフルシリサイド化して、上部電極 2 2 全体をコバルトシリサイド膜 3 1 から形成している点である。上述したように、容量素子は、メモリセルを形成する工程で形成される。このため、容量素子を独自に形成する工程を追加する必要がなく、半導体装置の製造コストを低減することができる。

#### 【 0 0 5 1 】

しかし、従来、容量素子の上部電極は、ポリシリコン膜から形成している。つまり、メモリセルのメモリゲート電極はポリシリコン膜から形成されているので、このポリシリコン膜を使用する上部電極は、やはりポリシリコン膜から形成される。そして、メモリゲート電極を構成するポリシリコン膜の一部を低抵抗化のためシリサイド化して、ポリシリコン膜上にコバルトシリサイド膜を形成している。このため、容量素子の上部電極もポリシリコン膜上にコバルトシリサイド膜が形成されている構成になっている。しかし、上部電極は完全にシリサイド化されていることはなく、ポリシリコン膜とコバルトシリサイド膜の積層構造をしている。つまり、容量素子は、ポリシリコン膜よりなる下部電極上に容量絶縁膜が形成され、容量絶縁膜上に上部電極が形成された構成をとるが、上部電極がポリシリコン膜とコバルトシリサイド膜の積層膜から構成される。このため、容量絶縁膜と上部電極の一部を構成するポリシリコン膜が接する構造となる。このような構成の容量素子を動作させると、上部電極あるいは下部電極に印加された電圧によってポリシリコン膜が空乏化する。いまの場合、下部電極と容量絶縁膜の境界および上部電極と容量絶縁膜の境界でポリシリコン膜が空乏化することになる。ポリシリコン膜が空乏化すると、空乏化したポリシリコン膜が絶縁膜として機能することになるから、容量絶縁膜の膜厚が空乏化した膜厚の分だけ変動することになる。容量素子の容量は容量絶縁膜の膜厚によって決定されることから、この容量絶縁膜の膜厚が変動することによって、容量素子の容量が変動することになる。すなわち、ポリシリコン膜の空乏化により容量素子の容量が変動し、高精度な容量素子を形成することができない。

#### 【 0 0 5 2 】

そこで、本実施の形態 1 では、図 2 に示すように、容量素子の上部電極 2 2 を完全にシリサイド化したコバルトシリサイド膜 3 1 から構成するようにしている。すなわち、上部電極 2 2 をコバルトシリサイド膜 3 1 の単層膜から構成している。すると、上部電極 2 2 と容量絶縁膜 2 6 の境界では、容量絶縁膜とコバルトシリサイド膜 3 1 が接することになるから空乏化することはない。したがって、上部電極と容量絶縁膜の境界に空乏化した絶縁領域が形成されることもなく、容量変化を低減することができる。このことから、本実施の形態 1 によれば、上部電極 2 2 全体をコバルトシリサイド膜 3 1 から形成することにより、高精度な容量素子を形成することができる。そして、後述するように、上部電極 2 2 全体をコバルトシリサイド化するために、新たな工程を追加する必要はないので、製造コストの増加も抑制できる。つまり、本実施の形態 1 によれば、製造コストを増加させずに、高精度な容量素子を形成できるという顕著な効果を得るのである。

#### 【 0 0 5 3 】

なお、本実施の形態 1 では、上部電極 2 2 全体をコバルトシリサイド膜 3 1 から形成する例について説明しているが、コバルトシリサイド膜 3 1 に限定されるものではなく、様々な金属シリサイド膜を上部電極 2 2 全体に使用することができる。金属シリサイド膜としては、例えば、チタンシリサイド膜やニッケルシリサイド膜を使用することもできる。

#### 【 0 0 5 4 】

次に、本実施の形態 1 における容量素子の動作条件について説明する。図 4 は、本実施の形態 1 における容量素子の各部位に印加する電圧例を示す図である。図 4 に示すように、上部電極 2 2 および下部電極 1 6 には、それぞれ - Vcc (- 5 V) ~ + Vcc (5 V) の範囲の電圧が印加される。また、p 型ウェル 1 2 には、0 V が印加される。このようして、容量素子を動作させることができる。

#### 【 0 0 5 5 】

10

20

30

40

50

ここで、図2に示す容量素子の上部電極22全体はコバルトシリサイド膜31から構成しているが、下部電極16はポリシリコン膜14から形成している。したがって、容量絶縁膜26と上部電極22との間では空乏化が生じないが、容量絶縁膜26と下部電極16の間では、下部電極がポリシリコン膜14から構成されていることから、空乏化が生じることになる。したがって、容量素子の容量変動が生じることが懸念される。確かに、下部電極16に印加する電圧によっては、下部電極16と容量絶縁膜26との間に空乏化が生じて容量変動が生じることになる。その上、上部電極22がポリシリコン膜から構成されていると、さらに、上部電極22と容量絶縁膜26の間でも空乏化が生じて、容量素子の容量変動が大きくなる。しかし、本実施の形態1によれば、上部電極22全体をコバルトシリサイド膜31から形成するように構成しているので、どのような動作電圧を印加しても、上部電極22と容量絶縁膜26の境界では空乏化が生じない。すなわち、本実施の形態1によれば、上部電極22と容量絶縁膜26の境界および下部電極16と容量絶縁膜26の境界の両方でポリシリコン膜の空乏化が生じることを防止できるので、容量素子の容量変化(ばらつき)を半減させることができるのである。

10

## 【0056】

さらに、動作電圧を所定の条件に設定することにより、下部電極16と容量絶縁膜26の間でも空乏化を生じさせないことができる。具体的に説明すると、下部電極16はポリシリコン膜14から形成されているが、このポリシリコン膜14はメモリセルのコントロールゲート電極15にも使用されている。したがって、ポリシリコン膜14には、通常、リンや砒素などのn型不純物が導入されている。この条件のもとでは、下部電極16に正電圧を印加すると、下部電極16を構成するポリシリコン膜14が空乏化することになる。そこで、動作条件として、下部電極16に負電圧を印加し、上部電極22に正電圧を印加するようにすれば、上部電極22と下部電極16の両方で空乏化を防止できる。つまり、上部電極22は全体がコバルトシリサイド膜31から形成されているので、印加する電圧が負電圧であろうと正電圧であろうと関係なく空乏化することはない。このため、下部電極16がn型不純物を導入したポリシリコン膜14であることを考慮して、下部電極16に負電圧を印加し、上部電極22に正電圧を印加するようにすれば、上部電極22と下部電極16の両方で空乏化を防止できるのである。このように動作条件を設定するように回路設計を行なうようにすれば、さらに高精度の容量素子を形成することができる。

20

## 【0057】

30

次に、本実施の形態1における半導体装置の製造方法について、図面を参照しながら説明する。

## 【0058】

40

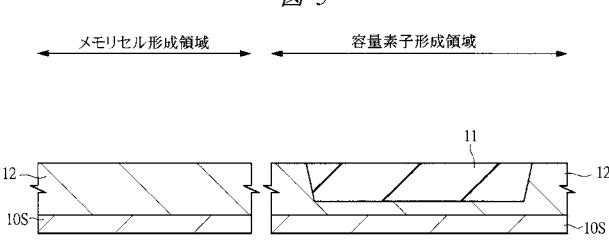

まず、図5に示すように、ホウ素(B)などのp型不純物を導入したシリコン単結晶よりなる半導体基板10Sを用意する。このとき、半導体基板10Sは、略円盤形状をした半導体ウェハの状態になっている。そして、半導体基板10Sの低耐圧MISFET形成領域と高耐圧MISFET形成領域とを分離する素子分離領域を形成する。素子分離領域は、素子が互いに干渉しないようにするために設けられる。この素子分離領域は、例えばLOCOS(local Oxidation of silicon)法やSTI(shallow trench isolation)法を用いて形成することができる。例えば、STI法では、以下のようにして素子分離領域を形成している。すなわち、半導体基板10Sにフォトリソグラフィ技術およびエッティング技術を使用して素子分離溝を形成する。そして、素子分離溝を埋め込むように半導体基板10S上に酸化シリコン膜を形成し、その後、化学的機械的研磨法(CMP; chemical mechanical polishing)により、半導体基板10S上に形成された不要な酸化シリコン膜を除去する。これにより、素子分離溝内にだけ酸化シリコン膜を埋め込んだ素子分離領域を形成することができる。なお、図5においては、メモリセル形成領域では、素子分離領域11が形成されていないが、容量素子形成領域では、素子分離領域11が形成される。

## 【0059】

50

続いて、半導体基板10Sに不純物を導入してp型ウェル12を形成する。p型ウェル

12は、例えばホウ素などのp型不純物をイオン注入法により半導体基板10Sに導入することで形成される。そして、メモリセル形成領域では、p型ウェル12の表面領域に選択トランジスタのチャネル形成用の半導体領域(図示せず)を形成する。このチャネル形成用の半導体領域は、チャネルを形成するしきい値電圧を調整するために形成される。

#### 【0060】

次に、図6に示すように、半導体基板10S上にゲート絶縁膜13を形成する。ゲート絶縁膜13は、例えば、酸化シリコン膜から形成され、例えば熱酸化法を使用して形成することができる。ただし、ゲート絶縁膜13は、酸化シリコン膜に限定されるものではなく種々変更可能であり、例えば、ゲート絶縁膜13を酸窒化シリコン膜(SiON)としてもよい。すなわち、ゲート絶縁膜13と半導体基板10Sとの界面に窒素を偏析させる構造としてもよい。酸窒化シリコン膜は、酸化シリコン膜に比べて膜中における界面準位の発生を抑制したり、電子トラップを低減する効果が高い。したがって、ゲート絶縁膜13のホットキャリア耐性を向上でき、絶縁耐性を向上させることができる。また、酸窒化シリコン膜は、酸化シリコン膜に比べて不純物が貫通しにくい。このため、ゲート絶縁膜13に酸窒化シリコン膜を用いることにより、ゲート電極中の不純物が半導体基板10S側に拡散することに起因するしきい値電圧の変動を抑制することができる。酸窒化シリコン膜を形成するのは、例えば、半導体基板10SをNO、NO<sub>2</sub>またはNH<sub>3</sub>といった窒素を含む雰囲気中で熱処理すればよい。また、半導体基板10Sの表面に酸化シリコン膜からなるゲート絶縁膜13を形成した後、窒素を含む雰囲気中で半導体基板10Sを熱処理し、ゲート絶縁膜13と半導体基板10Sとの界面に窒素を偏析させることによっても同様の効果を得ることができる。

10

20

30

40

#### 【0061】

また、ゲート絶縁膜13は、例えば酸化シリコン膜より誘電率の高い高誘電率膜から形成してもよい。従来、絶縁耐性が高い、シリコン-酸化シリコン界面の電気的・物性的安定性などが優れているとの観点から、ゲート絶縁膜13として酸化シリコン膜が使用されている。しかし、素子の微細化に伴い、ゲート絶縁膜13の膜厚について、極薄化が要求されるようになってきている。このように薄い酸化シリコン膜をゲート絶縁膜13として使用すると、MISFETのチャネルを流れる電子が酸化シリコン膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流が発生してしまう。

#### 【0062】

そこで、酸化シリコン膜より誘電率の高い材料を使用することにより、容量が同じでも物理的膜厚を増加させることができる高誘電体膜が使用されるようになってきている。高誘電体膜によれば、容量を同じにしても物理的膜厚を増加させることができるので、リーキ電流を低減することができる。

#### 【0063】

例えば、高誘電体膜として、ハフニウム酸化物の一つである酸化ハフニウム膜(HfO<sub>2</sub>膜)が使用されるが、酸化ハフニウム膜に変えて、ハフニウムアルミネート膜、HfO<sub>N</sub>膜(ハフニウムオキシナイトライド膜)、HfSiO膜(ハフニウムシリケート膜)、HfSiON膜(ハフニウムシリコンオキシナイトライド膜)、HfAlO膜のような他のハフニウム系絶縁膜を使用することもできる。さらに、これらのハフニウム系絶縁膜に酸化タンタル、酸化ニオブ、酸化チタン、酸化ジルコニアム、酸化ランタン、酸化イットリウムなどの酸化物を導入したハフニウム系絶縁膜を使用することもできる。ハフニウム系絶縁膜は、酸化ハフニウム膜と同様、酸化シリコン膜や酸窒化シリコン膜より誘電率が高いので、酸化ハフニウム膜を用いた場合と同様の効果が得られる。

#### 【0064】

そして、ゲート絶縁膜13上にポリシリコン膜14を形成する。ポリシリコン膜14は、例えば、CVD法を使用して形成することができる。そして、フォトリソグラフィ技術およびイオン注入法を使用して、ポリシリコン膜14中にリンや砒素などのn型不純物を導入する。

#### 【0065】

50

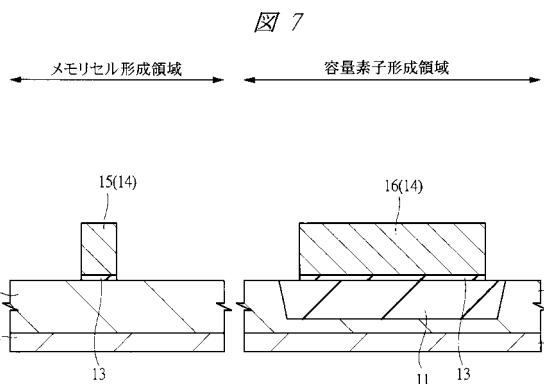

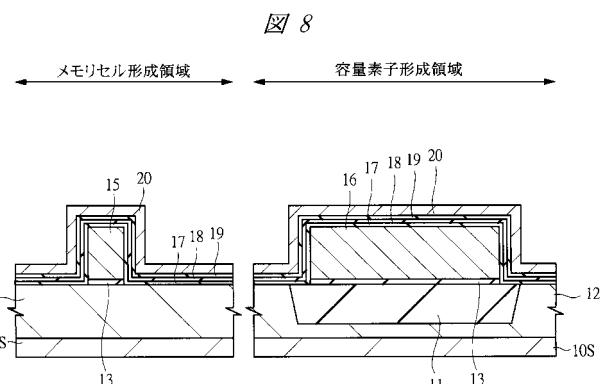

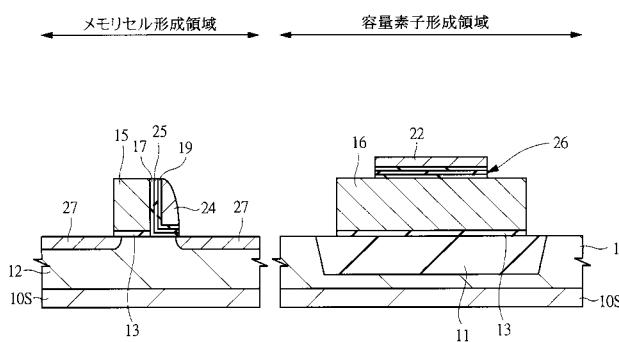

次に、図 7 に示すように、パターニングしたレジスト膜をマスクにしたエッチングによりポリシリコン膜 14 加工して、メモリセル形成領域にコントロールゲート電極 15 を形成し、容量素子形成領域に下部電極 16 を形成する。このコントロールゲート電極 15 は、メモリセルの選択トランジスタのゲート電極である。このように容量素子の下部電極 16 は、メモリセルのコントロールゲート電極 15 を形成する工程で形成されることがわかる。

#### 【0066】

ここで、コントロールゲート電極 15 には、ポリシリコン膜 14 中に n 型不純物が導入されている。このため、コントロールゲート電極 15 の仕事関数値をシリコンの伝導帯近傍 (4.15 eV) の値にすることができるので、n チャネル型 MISFET である選択トランジスタのしきい値電圧を低減することができる。

10

#### 【0067】

続いて、図示はしないが、フォトリソグラフィ技術およびイオン注入法を使用することにより、コントロールゲート電極 15 に整合してリンや砒素などの n 型不純物を導入する。この工程は、後述するようにコントロールゲート電極 15 の側壁に形成するメモリトランジスタのしきい値を調整するために実施されるものである。

#### 【0068】

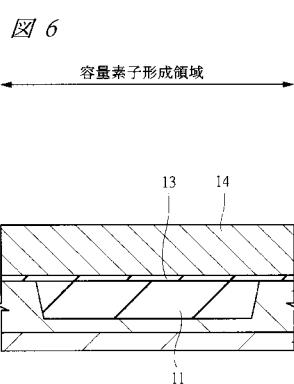

次に、図 8 に示すように、コントロールゲート電極 15 および下部電極 16 上を覆う半導体基板 10S 上に積層膜を形成する。積層膜は、例えば、酸化シリコン膜 17 と、この酸化シリコン膜 17 上に形成される窒化シリコン膜 18 と、窒化シリコン膜 18 上に形成される酸化シリコン膜 19 から形成される (ONO 膜)。これらの積層膜は、例えば、CVD 法を使用して形成することができる。そして、例えば、酸化シリコン膜 17 の膜厚は 5 nm、窒化シリコン膜 18 の膜厚は 10 nm、酸化シリコン膜 19 の膜厚は 5 nm である。

20

#### 【0069】

この積層膜のうち窒化シリコン膜 18 は、メモリセル形成領域において、メモリトランジスタの電荷蓄積膜となる膜である。本実施の形態 1 では、電荷蓄積膜として窒化シリコン膜 18 を使用しているが、電荷蓄積膜としてトランジット準位を有する他の絶縁膜から形成してもよい。例えば、電荷蓄積膜として酸化アルミニウム膜 (アルミナ膜) を使用することもできる。また、積層膜は、容量素子形成領域においては、容量絶縁膜となる。

30

#### 【0070】

そして、積層膜上にポリシリコン膜 20 を形成する。ポリシリコン膜 20 は、例えば、CVD 法を使用することにより形成することができ、ポリシリコン膜 20 の膜厚は、例えば、約 30 nm である。本実施の形態では、例としてポリシリコン膜 20 の膜厚を約 30 nm に設定した場合のプロセス条件を示す。

#### 【0071】

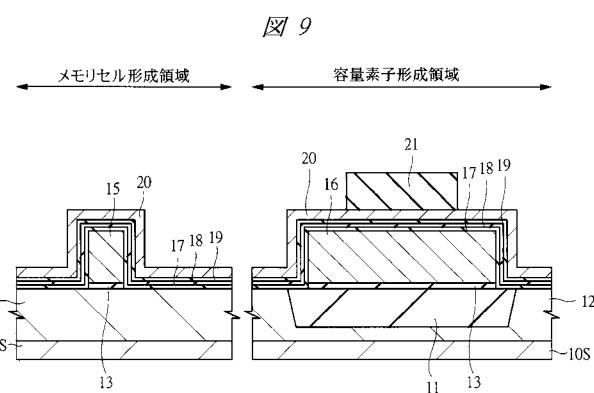

次に、図 9 に示すように、半導体基板 10S 上にレジスト膜 21 を塗布した後、このレジスト膜 21 に対して露光・現像処理を施すことによりパターニングする。パターニングは、容量素子形成領域の上部電極形成領域を覆い、その他の領域を露出するように行なわれる。

40

#### 【0072】

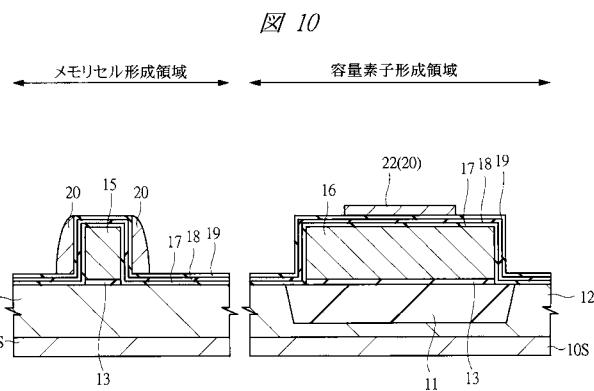

続いて、図 10 に示すように、レジスト膜 21 をマスクにして、ポリシリコン膜 20 を異方性エッチングすることにより、メモリセル形成領域では、コントロールゲート電極 15 の両側の側壁にポリシリコン膜 20 を残す。一方、容量素子形成領域では、レジスト膜 21 で覆われていた領域にだけポリシリコン膜 20 が残存し、この残存したポリシリコン膜 20 により上部電極 22 が形成される。この段階では、上部電極 22 はポリシリコン膜 20 から構成されている。その後、パターニングしたレジスト膜 21 を除去する。

#### 【0073】

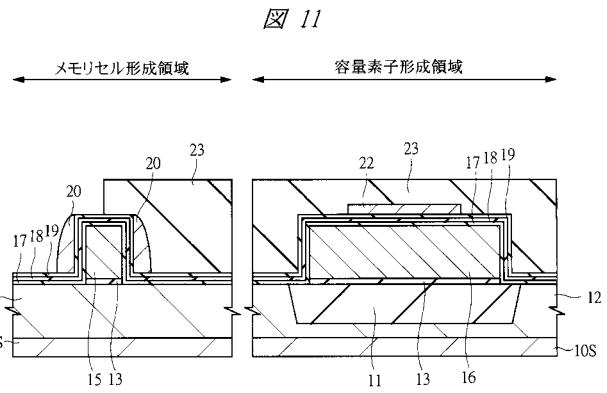

そして、図 11 に示すように、半導体基板 10S 上にレジスト膜 23 を塗布した後、このレジスト膜 23 に対して露光・現像処理を施すことにより、レジスト膜 23 をパターニ

50

ングする。パターニングは、容量素子形成領域を完全に覆う一方、メモリセル形成領域の一部を開口するように行なわれる。具体的には、メモリセル形成領域のうち、コントロールゲート電極 15 の片側の側壁に形成されているポリシリコン膜 20 が露出するように行なわれる。例えば、図 1 1 では、メモリセル形成領域に形成されているコントロールゲート電極 15 の左側の側壁に形成されているポリシリコン膜 20 が露出している。

【0074】

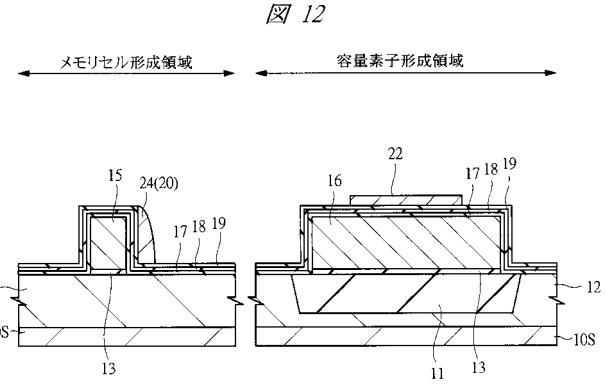

次に、図 1 2 に示すように、パターニングしたレジスト膜 23 をマスクにしたエッチングにより、コントロールゲート電極 15 の左側の側壁に露出しているポリシリコン膜 20 を除去する。このとき、コントロールゲート電極 15 の右側の側壁に形成されているポリシリコン膜 20 は、レジスト膜 23 で覆われているため除去されない。また、容量素子形成領域においても、上部電極 22 はレジスト膜 23 で保護されているため除去されずに残る。その後、パターニングしたレジスト膜 23 を除去する。

10

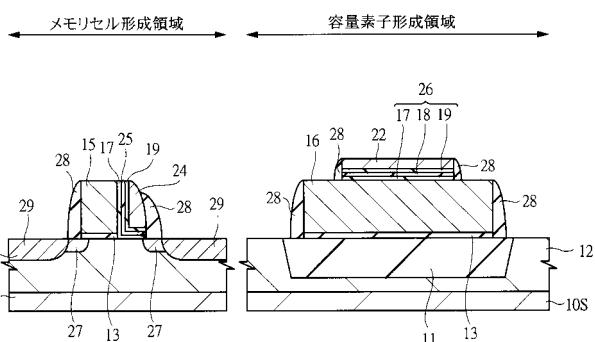

【0075】

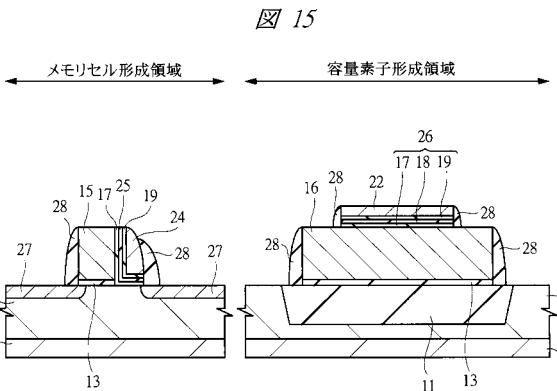

続いて、図 1 3 に示すように、露出する ONO 膜（積層膜）をエッチングすることにより除去する。このようにして、メモリセル形成領域では、コントロールゲート電極 15 の右側の側壁にだけ積層膜（ONO 膜）を介して、サイドウォール形状のメモリゲート電極 24 が形成される。このとき、積層膜（ONO 膜）を構成する窒化シリコン膜 18 が電荷蓄積膜 25 となる。一方、容量素子形成領域では、上部電極 22 で覆われている ONO 膜だけが残存し、この上部電極 22 の下層に形成されている ONO 膜が容量絶縁膜 26 となる。すなわち、容量絶縁膜 26 は、酸化シリコン膜 17、窒化シリコン膜 18 および酸化シリコン膜 19 から構成される。この時点ではメモリセルのメモリゲート電極 24 および容量素子の上部電極 22 はポリシリコン膜から形成されている。

20

【0076】

次に、図 1 4 に示すように、フォトリソグラフィ技術およびイオン注入法を使用することにより、メモリセル形成領域では、コントロールゲート電極 15 とメモリゲート電極 24 に整合した浅い低濃度不純物拡散領域 27 を形成する。浅い低濃度不純物拡散領域 27 は、リンや砒素などの n 型不純物を導入した n 型半導体領域である。

30

【0077】

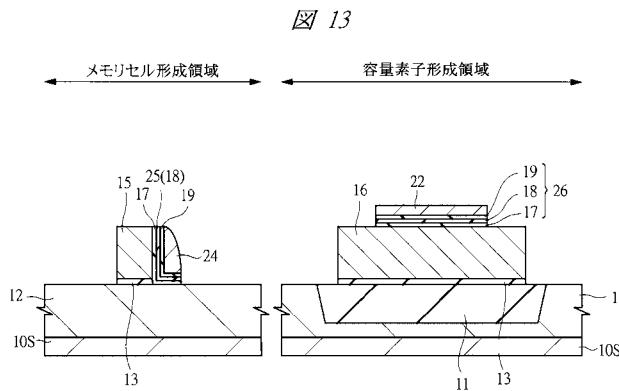

続いて、図 1 5 に示すように、半導体基板 10S 上に酸化シリコン膜を形成する。酸化シリコン膜は、例えば、CVD 法を使用して形成することができる。そして、酸化シリコン膜を異方性エッチングすることにより、サイドウォール 28 を形成する。メモリセル形成領域においては、コントロールゲート電極 15 の左側の側壁およびメモリゲート電極 24 の右側の側壁にサイドウォール 28 が形成される。一方、容量素子形成領域においては、上部電極 22 と容量絶縁膜 26 の側壁および下部電極 16 の側壁にサイドウォール 28 が形成される。これらのサイドウォール 28 は、酸化シリコン膜の単層膜から形成するようにしたが、これに限らず、例えば、窒化シリコン膜と酸化シリコン膜の積層膜からなるサイドウォール 28 を形成してもよい。

【0078】

次に、図 1 6 に示すように、フォトリソグラフィ技術およびイオン注入法を使用することにより、メモリセル形成領域にサイドウォール 28 に整合した深い高濃度不純物拡散領域 29 を形成する。深い高濃度不純物拡散領域 29 は、リンや砒素などの n 型不純物を導入した n 型半導体領域である。この深い高濃度不純物拡散領域 29 と浅い低濃度不純物拡散領域 27 によってメモリセルのソース領域あるいはドレイン領域が形成される。このようにソース領域とドレイン領域を浅い低濃度不純物拡散領域 27 と深い高濃度不純物拡散領域 29 で形成することにより、ソース領域およびドレイン領域を LDD (Lightly Doped Drain) 構造とすることができます。このようにして、高濃度不純物拡散領域 29 を形成した後、1000 度の熱処理を行なう。これにより、導入した不純物の活性化が行なわれる。

40

【0079】

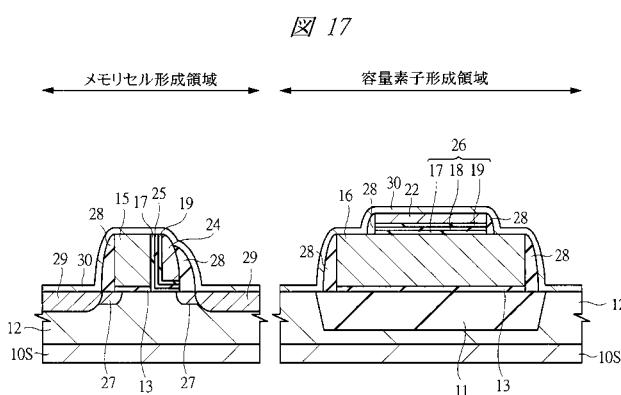

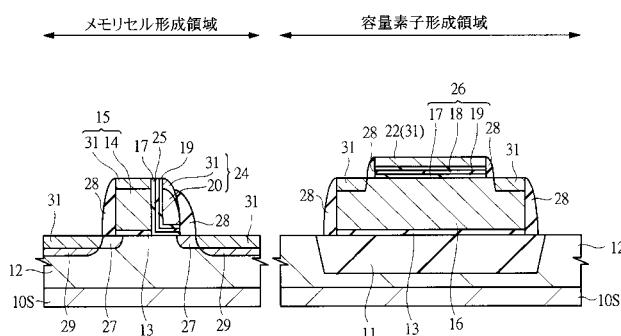

その後、図 1 7 に示すように、半導体基板 10S 上にコバルト膜 30 を形成する。この

50

とき、メモリセル形成領域では、露出しているコントロールゲート電極 15 およびメモリゲート電極 24 に直接接するようにコバルト膜 30 が形成される。同様に、深い高濃度不純物拡散領域 29 にもコバルト膜 30 が直接接する。一方、容量素子形成領域においては、下部電極 16 の一部および上部電極 22 の表面全体にコバルト膜 30 が直接接觸する。このコバルト膜 30 は、例えば、スパッタリング法を使用して形成することができる。コバルト膜 30 の膜厚は、例えば、15 nm である。

#### 【0080】

その後、半導体基板 10S に対して第 1 熱処理を実施する。この第 1 熱処理は、例えば、500 で 1 分間続ける。その後、半導体基板 10S の表面を洗浄する。この洗浄は、APM (Ammonium hydroxide hydrogen Peroxide Mixture cleaning) 洗浄と HPM 洗浄で行なわれる。APM 洗浄は、水酸化アンモニウム (NH<sub>4</sub>OH) / 過酸化水素 (H<sub>2</sub>O<sub>2</sub>) / 純水 (H<sub>2</sub>O) からなる混合薬液であり、パーティクルや有機物に対する除去効果が大きい洗浄である。一方、HPM 洗浄は、塩酸 (HCl) / 過酸化水素 (H<sub>2</sub>O<sub>2</sub>) / 純水 (H<sub>2</sub>O) からなる混合薬液であり、金属類に対する除去効果が大きい洗浄である。続いて、洗浄後、第 2 熱処理を実施する。第 2 熱処理は、例えば、700 で 1 分間続ける。

#### 【0081】

これにより、図 18 に示すように、メモリセル形成領域においては、コントロールゲート電極 15 およびメモリゲート電極 24 を構成するポリシリコン膜 14、20 とコバルト膜 30 を反応させて、コバルトシリサイド膜 31 を形成する。これにより、コントロールゲート電極 15 およびメモリゲート電極 24 はそれぞれポリシリコン膜 14、20 とコバルトシリサイド膜 31 の積層構造となる。コバルトシリサイド膜 31 は、コントロールゲート電極 15 およびメモリゲート電極 24 の低抵抗化のために形成される。同様に、上述した熱処理により、高濃度不純物拡散領域 29 の表面においてもシリコンとコバルト膜 30 が反応してコバルトシリサイド膜 31 が形成される。このため高濃度不純物拡散領域 29 においても低抵抗化を図ることができる。

#### 【0082】

一方、容量素子形成領域では、上部電極 22 とコバルト膜 30 が反応してコバルトシリサイド膜 31 からなる上部電極 22 が形成される。すなわち、上部電極 22 を構成するポリシリコン膜の膜厚が 30 nm で、このポリシリコン膜上に形成されているコバルト膜 30 が 15 nm で、上述した熱処理を施すと、上部電極 22 を構成するポリシリコン膜が完全にシリサイド化 (フルシリサイド化) される。これにより、上部電極 22 全体をコバルトシリサイド膜 31 から形成することができる。また、下部電極 16 とコバルト膜 30 が直接接觸している領域でもシリサイド反応が進行し、コバルトシリサイド膜 31 が形成される。

#### 【0083】

そして、未反応のコバルト膜 30 は、半導体基板 10S 上から除去される。なお、本実施の形態 1 では、コバルトシリサイド膜 31 を形成するように構成しているが、例えば、コバルトシリサイド膜 31 に代えてニッケルシリサイド膜やチタンシリサイド膜を形成するようにしてもよい。

#### 【0084】

以上のようにして、メモリセル形成領域にメモリセルを形成し、容量素子形成領域に上部電極 22 全体をコバルトシリサイド膜 31 から構成した容量素子を形成することができる。

#### 【0085】

次に、配線工程について図 2 を参照しながら説明する。図 2 に示すように、半導体基板 10S の主面上に層間絶縁膜となる酸化シリコン膜 32 を形成する。この酸化シリコン膜 32 は、例えば TEOS (tetra ethyl ortho silicate) を原料とした CVD 法を使用して形成することができる。その後、酸化シリコン膜 32 の表面を、例えば CMP (Chemical Mechanical Polishing) 法を使用して平坦化する。

10

20

30

40

50

## 【0086】

続いて、フォトリソグラフィ技術およびエッチング技術を使用して、酸化シリコン膜32にコンタクトホール33を形成する。このコンタクトホール33はメモリセル形成領域と容量素子形成領域に複数形成される。そして、コンタクトホール33の底面および内壁を含む酸化シリコン膜32上にチタン/窒化チタン膜34aを形成する。チタン/窒化チタン膜34aは、チタン膜と窒化チタン膜の積層膜から構成され、例えばスパッタリング法を使用することにより形成することができる。このチタン/窒化チタン膜34aは、例えば、後の工程で埋め込む膜の材料であるタンゲステンがシリコン中へ拡散するのを防止する、いわゆるバリア性を有する。

## 【0087】

続いて、コンタクトホール33を埋め込むように、半導体基板10Sの正面の全面にタンゲステン膜34bを形成する。このタンゲステン膜34bは、例えばCVD法を使用して形成することができる。そして、酸化シリコン膜32上に形成された不要なチタン/窒化チタン膜34aおよびタンゲステン膜34bを例えればCMP法で除去することにより、プラグ35を形成することができる。

## 【0088】

次に、酸化シリコン膜32およびプラグ35上にチタン/窒化チタン膜36a、銅を含有するアルミニウム膜36b、チタン/窒化チタン膜36cを順次、形成する。これらの膜は、例えばスパッタリング法を使用することにより形成することができる。続いて、フォトリソグラフィ技術およびエッチング技術を使用することにより、これらの膜のパターニングを行い、配線L1、L2、L3を形成する。さらに、配線の上層に配線を形成するが、ここでの説明は省略する。このようにして、最終的に本実施の形態1における半導体装置を形成することができる。

## 【0089】

本実施の形態1によれば、不揮発性メモリセルを形成する工程を利用して容量素子を形成することができるので、容量素子を形成する追加工程を実施する必要がなく、半導体装置の製造コストを抑えることができる。このとき、容量素子の上部電極はポリシリコン膜から形成されるが、不揮発性メモリセルの製造工程で実施されるシリサイド工程を利用して、容量素子の上部電極全体を金属シリサイド膜にしている。これにより、容量素子の上部電極が空乏化することなく、高精度な容量素子を製造することができる。つまり、本実施の形態1によれば、製造コストを上昇させることなく、同一半導体基板上に不揮発性メモリセルと高精度な容量素子を形成することができる。

## 【0090】

本実施の形態1では、図2に示すように、容量素子の上部電極22全体をコバルトシリサイド膜31から構成する点に特徴の1つがある。そして、上部電極22を完全にシリサイド化するために、本実施の形態1では、上部電極22をシリサイド化する前のポリシリコン膜の膜厚を薄く形成している。これにより、ポリシリコン膜を完全にフルシリサイド化することができる。このようにポリシリコン膜を薄く形成する構成は、容量素子の上部電極22を完全にシリサイド化することが目的であるが、さらに、派生的な効果を得ることができる。

## 【0091】

この点について説明する。まず、図2に示すように、容量素子の上部電極22とメモリセルのメモリゲート電極24とは同一のポリシリコン膜を使用している。つまり、容量素子の上部電極22の膜厚を薄くするためにポリシリコン膜の膜厚を薄くすると、メモリゲート電極24を構成するポリシリコン膜20の膜厚も薄くなる。すると、メモリゲート電極24のゲート長(ゲート幅)が小さくなる。メモリゲート電極24のゲート長を小さくすると、メモリトランジスタの読み出し電流を充分に確保できるようになり、メモリトランジスタの性能が向上する。すなわち、容量素子の上部電極22を完全にシリサイド化するためにポリシリコン膜を薄くすると、派生的にメモリトランジスタの性能が向上する効果が得られる。

10

20

30

40

50

## 【0092】

さらに、メモリトランジスタでは、メモリゲート電極24と半導体基板10Sの間に積層膜が形成されている。この積層膜は酸化シリコン膜17、電荷蓄積膜25および酸化シリコン膜19から形成されており、電荷蓄積膜25への電荷の注入によってメモリトランジスタの書き込み動作や消去動作が行なわれる。具体的には、例えば、書き込み状態では、電荷蓄積膜25に電子を注入することにより、メモリトランジスタのしきい値電圧が上昇した状態となっており、消去状態では、電荷蓄積膜25に正孔を注入することにより、メモリトランジスタのしきい値電圧が低下した状態となっている。書き込み方法として、ソース領域(右側の低濃度不純物拡散領域27)からドレイン領域(左側の低濃度不純物拡散領域27)へチャネル電流を流し、そのとき発生するホットエレクトロンを注入する方法を用いた場合、電子は、電荷蓄積膜25のコントロールゲート電極15側に蓄積される。すなわち、電荷蓄積膜25に蓄積される電子は、電荷蓄積膜25の一部領域に局在するようになっている。一方、消去方法としてソース領域側のBTT(Band-To-Band Tunneling)により発生するホットホールを注入する方式を用いた場合、正孔は、電荷蓄積膜25のソース領域側(右側の低濃度不純物拡散領域27側)に蓄積される。したがって、正孔も電荷蓄積膜25の一部領域に局在するようになっている。消去動作では、正孔を電荷蓄積膜25に注入して電荷蓄積膜25に蓄積されている電子と対消滅させることにより、電荷蓄積膜25内の電子を消滅させてしきい値を下げている。しかし、上述したように電子の局在領域と正孔の局在領域が異なることから、電荷蓄積膜25の幅が大きいと効率的に電子と正孔が対消滅しにくくなり、メモリトランジスタの信頼性が低下する。これに対し、本実施の形態1では、ポリシリコン膜20の膜厚を薄くすることにより、メモリゲート電極24のゲート長が短くなることから、メモリゲート電極24下に形成されている電荷蓄積膜25の幅も小さくなる。このことから、電荷蓄積膜25における電子の局在領域と正孔の局在領域が近接することになり、電子と正孔の対消滅が充分に行なわれ、メモリトランジスタの信頼性が向上するという効果が得られる。このように、本実施の形態1によれば、高精度の容量素子を製造できるとともに、メモリセルの性能向上と信頼性向上を実現できる顕著な効果を得ることができる。 10 20

## 【0093】

## (実施の形態2)

前記実施の形態1では、図3に示すように、上部電極22が平面的に下部電極16に包含されるレイアウト例について説明した。本実施の形態2では、容量素子の他のレイアウト例について説明する。 30

## 【0094】

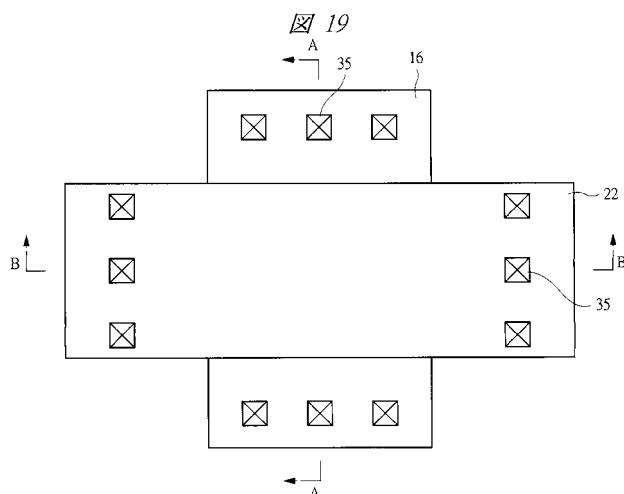

図19は、本実施の形態2における容量素子のレイアウト構成を示す平面図である。図19に示すように、下部電極16と上部電極22とは平面的に重なる部位を有するとともに、平面的に重ならない部位も有している。そして、上部電極22と下部電極16のそれぞれにプラグ35が接続されており、このプラグ35によってそれぞれ上部電極22と下部電極16が配線(図示せず)に接続されている。このように本実施の形態2では、前記実施の形態1のように上部電極22が下部電極16に包含されているのではなく、上部電極22に、下部電極16と平面的に重ならない部位を有し、この部位に接続するようにプラグ35が接続されている点に特徴の1つがある。 40

## 【0095】

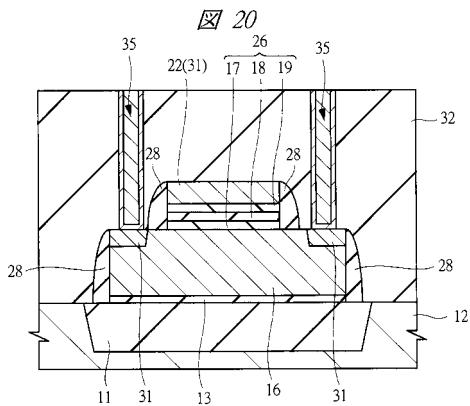

図20は、図19のA-A線で切断した断面図である。図20において、下部電極16上に容量絶縁膜26を介して上部電極22が形成されている。そして、下部電極16上にプラグ35が形成されている。この上部電極22は、前記実施の形態1と同様に、全体がコバルトシリサイド膜31から形成されている。したがって、上部電極22と容量絶縁膜26との間で空乏化が発生しないため、容量素子の容量変動を低減することができ、高精度な容量素子を形成できる点は、前記実施の形態1と同様である。

## 【0096】

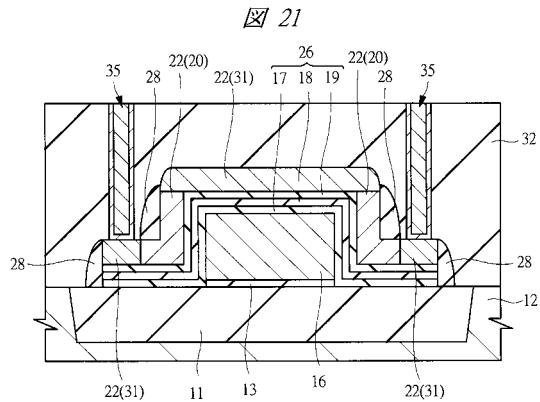

次に、図21は、図19のB-B線で切断した断面図である。図21に示すように、半

導体基板 10S に形成された素子分離領域 11 上に下部電極 16 が形成されており、この下部電極 16 を覆い、かつ、素子分離領域 11 上に延在するように容量絶縁膜 26 が形成されている。すなわち、容量絶縁膜 26 は下部電極 16 上にだけではなく、素子分離領域 11 上にわたって形成されている。そして、この容量絶縁膜 26 上に上部電極 22 が形成されている。上部電極 22 は、容量絶縁膜 26 と同様に、下部電極 16 と平面的に重なりを有する部位だけでなく、下部電極 16 と平面的に重なりを有さない素子分離領域 11 上にわたって形成されている。そして、上部電極 22 の下部電極 16 と平面的に重なる部位から上部電極 22 の下部電極 16 と平面的に重ならない部位への間には段差が形成され、この段差の側壁にサイドウォール 28 が形成されている。

## 【0097】

10

ここで、本実施の形態 2 における特徴の 1 つは、図 21 に示すように、上部電極 22 の下部電極 16 と平面的に重なりを有さない部位でプラグ 35 と接続している点にある。例えば、上部電極 22 の下部電極 16 と平面的に重なりを有する部位で、上部電極 22 とプラグ 35 とを接続すると、以下に示すことが懸念される。上部電極 22 と下部電極 16 が平面的に重なる部位によって容量素子の実質的な容量が形成される。このため、上部電極 22 の下部電極 16 と平面的に重なる部位で、上部電極 22 とプラグ 35 とを接続すると、プラグ 35 を形成するための孔が上部電極 22 を突き抜けるように形成された場合、下層に形成されている容量絶縁膜 26 にダメージを与えることになる。この領域に形成されている容量絶縁膜 26 は、容量素子の実質的な容量を決定しているものであるため、ダメージが与えられると容量素子の特性が劣化することが懸念される。

## 【0098】

20

そこで、本実施の形態 2 では、図 21 に示すように、プラグ 35 と上部電極 22 の電気的な接続を、上部電極 22 の下部電極 16 と平面的に重なりを有さない部位で行なうように構成している。これにより、例えば、プラグ 35 を形成するための孔が上部電極 22 を突き抜けるように形成された場合、上部電極 22 の下層に形成されている容量絶縁膜 26 にダメージを与えることになるが、この領域に形成されている容量絶縁膜 26 は、容量素子の実質的な容量を決定しているものではない。すなわち、この領域に形成されている容量絶縁膜 26 は、下部電極 16 上に形成されているものではなく素子分離領域 11 上に形成されているものであることから、実質的な容量絶縁膜としては機能しないのである。したがって、この領域に形成されている容量絶縁膜 26 にダメージが与えられても、容量素子の特性に悪影響を及ぼすことがないのである。このように本実施の形態 2 によれば、上部電極 22 とプラグ 35 とを接続するレイアウトを工夫することで、容量素子の信頼性を向上することができる。

## 【0099】

30

なお、上部電極 22 は前記実施の形態 1 と同様にシリサイド化が行なわれるが、図 21 に示す本実施の形態 2 における容量素子では、段差に形成されたサイドウォール 28 の影響により、表面をサイドウォール 28 に覆われた上部電極 22 の部位はシリサイド化が行なわれない。つまり、上部電極 22 は、完全にシリサイド化されてシリサイド膜 31 から構成されている部位とサイドウォール 28 に覆われてシリサイド化が行なわれずにポリシリコン膜 20 から構成されている部位が並存することになる。しかし、図 21 を見てもわかるように、実質的に容量を形成する上部電極 22 の大部分は完全にフルシリサイド化されたコバルトシリサイド膜 31 から形成されており、シリサイド化されていない部位はわずかである。したがって、上部電極 22 にシリサイド化されていない部位が存在しても、この部位が容量素子の特性に与える影響はわずかであり問題は生じない。

## 【0100】

40

本実施の形態 2 における容量素子も前記実施の形態 1 で説明した製造方法とほぼ同様の工程を経ることにより形成することができる。例えば、マスクの変更によって容量素子のレイアウト構成を変えることができる。

## 【0101】

50

(実施の形態 3 )

前記実施の形態1では、容量素子の上部電極を完全にシリサイド化して金属シリサイド膜から形成する例について説明したが、本実施の形態3では、容量素子の上部電極を一部シリサイド化し、シリサイド化されていないポリシリコン膜の膜厚を所定値以下にする例について説明する。

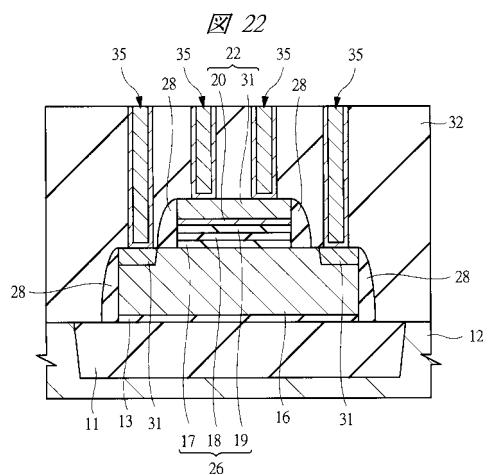

【0102】

図22は、本実施の形態3における容量素子を示す断面図である。図22において、容量素子の上部電極22は、ポリシリコン膜20とコバルトシリサイド膜31の積層膜で形成されている。つまり、上部電極22を構成するポリシリコン膜20をシリサイド化するが、このとき、ポリシリコン膜20のすべてをシリサイド化しなくても、ポリシリコン膜20の残存する膜厚を所定値以下にすることによっても実用に耐えうる充分に高精度な容量素子を形成することができる。

10

【0103】

上部電極22としてポリシリコン膜20が残存することから、容量絶縁膜26と上部電極22の境界では、ポリシリコン膜20と容量絶縁膜26が接触することになる。したがって、容量素子を動作させると、このポリシリコン膜20が空乏化する。このため、容量素子の容量変動が生じる。しかし、ポリシリコン膜20の膜厚を容量絶縁膜26の膜厚の10%以下にすることにより、空乏化する膜厚を容量絶縁膜26の10%以下にすることができる。このため、上部電極22の空乏化に起因した容量変動を問題とならない規定値以下に抑えることができる。この程度の容量変動であれば問題ないので高精度な容量素子を実現することができる。

20

【0104】

具体的に、図22に示すように、容量絶縁膜26は、酸化シリコン膜17、窒化シリコン膜18および酸化シリコン膜19から構成されるが、それぞれの膜厚は、約5nm、約10nm、約5nmである。すなわち、容量絶縁膜26の物理膜厚は約20nmであり、酸化シリコン換算膜厚(EOT)に換算すると、約15nmとなる。このことから、上部電極22の一部を構成するポリシリコン膜20の膜厚を約1.5nm以下にすることにより、空乏化する膜厚を容量絶縁膜26の10%以下にすることができる。

20

【0105】

前記実施の形態1のように上部電極22を完全にシリサイド化してコバルトシリサイド膜31から構成することが、上部電極22の空乏化を抑制する観点から望ましい。しかし、本実施の形態3のように、上部電極22を構成する膜にポリシリコン膜20が残存しても、そのポリシリコン膜20の膜厚を容量絶縁膜26の膜厚(EOT膜厚)の10%以下にすることにより、充分に高精度の容量素子を構成することができる。なお、本実施の形態3における容量素子の製造方法は、前記実施の形態1とほぼ同様である。このとき、上部電極22をシリサイド化する工程で、ポリシリコン膜20が残存する条件で行い、その残存するポリシリコン膜20の膜厚を容量絶縁膜26の膜厚の10%以下にすることで、本実施の形態3における容量素子を製造することができる。

30

【0106】

また、本実施の形態3に開示した技術を、前述の前記実施の形態2に適用することも可能であり、本実施の形態3と同様の効果を得ることができる。

40

【0107】

(実施の形態4)

前記実施の形態1では、容量素子の上部電極全体を金属シリサイド膜から形成する例について説明したが、本実施の形態4では、容量素子の上部電極全体を金属膜から形成する例について説明する。

【0108】

図23は、メモリセル形成領域と容量素子形成領域を示したものであり、容量素子形成領域に本実施の形態4における容量素子を形成している断面図である。この図23は、前記実施の形態1を説明する図2とほぼ同様の構成をしている。異なる点は、容量素子の上部電極22に金属膜40を形成した点である。このように上部電極22全体を金属膜40

50

から構成することによっても、高精度な容量素子を実現することができる。すなわち、金属膜40は空乏化することはないので、上部電極22と容量絶縁膜26の境界での空乏化を防止することができるからである。なお、金属膜としては、窒化タンタル膜(TaN)、窒化チタン膜(TiN)、窒化タンゲスタン膜(WN)または窒化ハフニウム膜(HfN)など、様々な種類の膜を使用することができる。

#### 【0109】

ここで、本実施の形態4における容量素子の製造方法は、前記実施の形態1とほぼ同様である。異なる点は、ポリシリコン膜20の代わりに金属膜40を使用する点である。このとき、容量素子の上部電極22とメモリセルのメモリゲート電極24は同一の膜から形成されるので、メモリゲート電極24も金属膜40から構成されることになる。

10

#### 【0110】

また、図23に示すように、本実施の形態4でも容量素子の下部電極16は、導体膜の1つであるポリシリコン膜14から構成されるが、この下部電極16も金属膜から構成するようにしてもよい。これにより、上部電極22と下部電極16の両方を金属膜から構成することにより、上部電極22の空乏化だけでなく、下部電極16の空乏化も防止することができる。さらに高精度な容量素子を形成することができる。下部電極16を金属膜から構成する場合には、メモリセルのコントロールゲート電極15も金属膜から構成されることになる。以上のように、本実施の形態4においても、製造コストを増加させずに、高精度な容量素子を形成できるという顕著な効果を得ることができる。

20

#### 【0111】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【0112】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

#### 【図面の簡単な説明】

#### 【0113】

【図1】本発明の実施の形態1における半導体チップの構成を示す平面図である。

30

【図2】実施の形態1における不揮発性メモリセルと容量素子とを示す断面図である。

【図3】図2に示す容量素子を上面から見た平面図である。

【図4】容量素子の動作条件を示す図である。

【図5】実施の形態1における半導体装置の製造工程を示す断面図である。

【図6】図5に続く半導体装置の製造工程を示す断面図である。

【図7】図6に続く半導体装置の製造工程を示す断面図である。

【図8】図7に続く半導体装置の製造工程を示す断面図である。

【図9】図8に続く半導体装置の製造工程を示す断面図である。

【図10】図9に続く半導体装置の製造工程を示す断面図である。

【図11】図10に続く半導体装置の製造工程を示す断面図である。

【図12】図11に続く半導体装置の製造工程を示す断面図である。

40

【図13】図12に続く半導体装置の製造工程を示す断面図である。

【図14】図13に続く半導体装置の製造工程を示す断面図である。

【図15】図14に続く半導体装置の製造工程を示す断面図である。

【図16】図15に続く半導体装置の製造工程を示す断面図である。

【図17】図16に続く半導体装置の製造工程を示す断面図である。

【図18】図17に続く半導体装置の製造工程を示す断面図である。

【図19】実施の形態2における容量素子を示す平面図である。

【図20】図19のA-A線で切断した断面図である。

【図21】図19のB-B線で切断した断面図である。

【図22】実施の形態3における容量素子を示す断面図である。

50

【図23】実施の形態4における不揮発性メモリセルと容量素子を示す断面図である。

【符号の説明】

【0 1 1 4】

|       |             |    |

|-------|-------------|----|

| 1     | C P U       |    |

| 2     | R A M       |    |

| 3     | アナログ回路      |    |

| 4     | フラッシュメモリ    |    |

| 1 0   | S 半導体基板     | 10 |

| 1 1   | 素子分離領域      |    |

| 1 2   | p型ウェル       |    |

| 1 3   | ゲート絶縁膜      |    |

| 1 4   | ポリシリコン膜     |    |

| 1 5   | コントロールゲート電極 |    |

| 1 6   | 下部電極        |    |

| 1 7   | 酸化シリコン膜     |    |

| 1 8   | 窒化シリコン膜     |    |

| 1 9   | 酸化シリコン膜     |    |

| 2 0   | ポリシリコン膜     |    |

| 2 1   | レジスト膜       | 20 |

| 2 2   | 上部電極        |    |

| 2 3   | レジスト膜       |    |

| 2 4   | メモリゲート電極    |    |

| 2 5   | 電荷蓄積膜       |    |

| 2 6   | 容量絶縁膜       |    |

| 2 7   | 低濃度不純物拡散領域  |    |

| 2 8   | サイドウォール     |    |

| 2 9   | 高濃度不純物拡散領域  |    |

| 3 0   | コバルト膜       |    |

| 3 1   | コバルトシリサイド膜  | 30 |

| 3 2   | 酸化シリコン膜     |    |

| 3 3   | コンタクトホール    |    |

| 3 4 a | チタン/窒化チタン膜  |    |

| 3 4 b | タンゲステン膜     |    |

| 3 5   | プラグ         |    |

| 3 6 a | チタン/窒化チタン膜  |    |

| 3 6 b | アルミニウム膜     |    |

| 3 6 c | チタン/窒化チタン膜  |    |

| 4 0   | 金属膜         |    |

| C H P | 半導体チップ      | 40 |

| L 1   | 配線          |    |

| L 2   | 配線          |    |

| L 3   | 配線          |    |

| P D   | パッド         |    |

【図 1】

【図 2】

【図 3】

【図 4】

|         |                                 |

|---------|---------------------------------|

| 上部電極22  | $-V_{cc}(-5V) \sim +V_{cc}(5V)$ |

| 下部電極16  | $-V_{cc}(-5V) \sim +V_{cc}(5V)$ |

| p型ウェル12 | 0V                              |

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図19】

【図18】

図18

【図 2 0】

【図 2 1】

【図 2 2】

【図 2 3】

図 23

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 01 L 21/822 (2006.01)

H 01 L 27/04 (2006.01)

(72)発明者 橋本 孝司

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

F ターム(参考) 5F038 AC04 AC05 AC10 AC16 AC17 BG01 DF04 DF05 DF12 EZ13

EZ14 EZ15 EZ16 EZ17 EZ20

5F083 EP18 EP22 EP33 EP63 EP68 ER02 ER11 JA02 JA35 JA39

JA40 MA05 MA06 MA19 NA01 PR05 PR33 PR43 PR52 ZA12

ZA13

5F101 BA45 BB02 BC11 BD07 BD22 BE02 BE05 BE07 BH15 BH16

BH21