(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6080732号

(P6080732)

(45) 発行日 平成29年2月15日(2017.2.15)

(24) 登録日 平成29年1月27日(2017.1.27)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 2 0

請求項の数 1 (全 38 頁)

(21) 出願番号 特願2013-196720 (P2013-196720)

(22) 出願日 平成25年9月24日 (2013.9.24)

(62) 分割の表示 特願2012-238054 (P2012-238054)

分割

原出願日 平成24年10月29日 (2012.10.29)

(65) 公開番号 特開2014-87604 (P2014-87604A)

(43) 公開日 平成26年5月15日 (2014.5.15)

審査請求日 平成27年9月15日 (2015.9.15)

(73) 特許権者 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74) 代理人 100100376

弁理士 野中 誠一

(72) 発明者 坂井 良太

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

審査官 堀 圭史

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

所定のスイッチ信号に起因する抽選処理を実行して、その抽選結果に対応する画像演出を実行する遊技機であって、

前記抽選処理を実行して抽選結果を特定する制御コマンドを出力する主制御手段と、制御コマンドが特定する抽選結果に対応する一連の画像演出を、表示装置を使用して実行する画像制御手段と、を有して構成され、

一連の画像演出は、関連する一連の複数フレーム数の単位画像を連続させて構成される動画を含んで実現され、

前記画像制御手段は、表示装置を駆動する副画像制御手段と、

副画像制御手段の動作を制御して画像演出を実現する主画像制御手段と、を有して構成され、

副画像制御手段は、

動画を構成する動画圧縮データをデコードした伸張データが一時記憶されるムービーバッファと、

外付けRAMか又は内蔵RAMに確保されたメモリ領域であって、ムービーバッファの伸張データに基づいて形成された画像データを一時記憶するフレームバッファと、

自らの動作内容を規定するコマンドリストが一時記憶されるコマンドメモリと、

前記ムービーバッファ、前記フレームバッファ、及び前記コマンドメモリにアクセス可能で、前記コマンドリストに基づいて動作する描画制御手段と、を有し、

10

20

動画の再生を指示するコマンドリストは、初期コマンドリストと、定常コマンドリストとに区分され、

前記初期コマンドリストは、フレームバッファのメモリ領域を特定すると共に、再生すべき動画を特定するムービーIDを含んで構成され、

前記定常コマンドリストは、ムービーIDで特定される動画を構成する単位画像を、表示装置のどの位置に描画するかの指示を含んで構成されており、

前記描画制御手段は、前記初期コマンドリストを受けた後、前記定常コマンドリストを複数回受けことで、前記初期コマンドリストが特定するフレームバッファに一時記憶された画像データを表示装置に出力して、前記初期コマンドリストが特定するムービーIDに対応する動画を表示装置に表示することを特徴とする遊技機。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、遊技動作に起因する抽選処理によって大当たり状態を発生させる遊技機に関し、特に、迫力ある画像演出を安定して実行できる遊技機に関する。

【背景技術】

【0002】

パチンコ機などの弾球遊技機は、遊技盤に設けた図柄始動口と、複数の表示図柄による一連の図柄変動態様を表示する図柄表示部と、開閉板が開閉される大入賞口などを備えて構成されている。そして、図柄始動口に設けられた検出スイッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示図柄が所定時間変動される。その後、7・7・7などの所定の態様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な遊技状態を発生させている。

20

【0003】

このような遊技状態を発生させるか否かは、図柄始動口に遊技球が入賞したことを条件に実行される大当たり抽選で決定されており、上記の図柄変動動作は、この抽選結果を踏まえたものとなっている。例えば、抽選結果が当選状態である場合には、リーチアクションなどと称される演出動作を20秒前後実行し、その後、特別図柄を整列させている。一方、ハズレ状態の場合にも、同様のリーチアクションが実行されることがあり、この場合には、遊技者は、大当たり状態になることを強く念じつつ演出動作の推移を注視することになる。そして、図柄変動動作の終了時に、停止ラインに所定図柄が揃えば、大当たり状態であることが遊技者に保証されたことになる。

30

【発明の概要】

【発明が解決しようとする課題】

【0004】

この種の遊技機では、各種の演出を複雑化かつ豊富化したいところ、特に、画像演出については、その要請が高い。また、不自然な画像演出の出現も可能な限り回避したいところである。

【0005】

この発明は、上記の課題に鑑みてなされたものであって、複雑高度な画像演出を安定して実行できる遊技機を提供することを目的とする。

40

【課題を解決するための手段】

【0006】

上記の目的を達成するため、本発明は、所定のスイッチ信号に起因する抽選処理を実行して、その抽選結果に対応する画像演出を実行する遊技機であって、前記抽選処理を実行して抽選結果を特定する制御コマンドを出力する主制御手段と、制御コマンドが特定する抽選結果に対応する一連の画像演出を、表示装置を使用して実行する画像制御手段と、を有して構成され、一連の画像演出は、関連する一連の複数フレーム数の単位画像を連続させて構成される動画を含んで実現され、前記画像制御手段は、表示装置を駆動する副画像制御手段と、副画像制御手段の動作を制御して画像演出を実現する主画像制御手段と、を

50

有して構成され、副画像制御手段は、動画を構成する動画圧縮データをデコードした伸張データが一時記憶されるムービーバッファと、外付けRAMか又は内蔵RAMに確保されたメモリ領域であって、ムービーバッファの伸張データに基づいて形成された画像データを一時記憶するフレームバッファと、自らの動作内容を規定するコマンドリストが一時記憶されるコマンドメモリと、前記ムービーバッファ、前記フレームバッファ、及び前記コマンドメモリにアクセス可能で、前記コマンドリストに基づいて動作する描画制御手段と、を有し、動画の再生を指示するコマンドリストは、初期コマンドリストと、定常コマンドリストとに区分され、前記初期コマンドリストは、フレームバッファのメモリ領域を特定すると共に、再生すべき動画を特定するムービーIDを含んで構成され、前記定常コマンドリストは、ムービーIDで特定される動画を構成する単位画像を、表示装置のどの位置に描画するかの指示を含んで構成されており、前記描画制御手段は、前記初期コマンドリストを受けた後、前記定常コマンドリストを複数回受けることで、前記初期コマンドリストが特定するフレームバッファに一時記憶された画像データを表示装置に出力して、前記初期コマンドリストが特定するムービーIDに対応する動画を表示装置に表示する。

10

#### 【0007】

本発明のデコード手段や描画指示手段は、主画像制御手段が、コマンドメモリにコマンドリストを書き込んだ後、副画像制御手段に対して、コマンドリストの解析を指示することで機能するのが好ましい。何れにしても、デコード手段を一回機能させたことに対して、描画指示手段を複数回機能させる構成が好適である。

20

#### 【0008】

また、不揮発性メモリは、基点アドレスを指示した後、クロック信号を受ける毎に記憶内容が読み出し可能に構成されるのが好ましい。ここで、前記基点アドレスは、記憶内容が読み出されるデータバスを経由して、描画制御部から不揮発性メモリに伝送されるのが好適である。

#### 【0009】

本発明の不揮発性メモリは、1バイト毎に記憶内容の演算処理が可能に構成され、演算開始アドレスから演算終了アドレスまでの演算結果は、2バイト長で特定可能に構成されているのが好ましい。この場合、前記演算結果は、描画制御部を経由して、主画像制御手段において把握可能に構成されているのが好適である。

30

#### 【0010】

また、本発明のムービーバッファは、描画制御部と分離されたメモリ素子に確保されて、アドレスバス及びデータバスを経由して接続されているのが好適である。コマンドメモリは、描画制御部と同一の電子素子に内蔵されているのが好適であり、フレームバッファは、描画制御部と同一の電子素子の内部に確保されているのが好適である。また、フレームバッファは、描画制御部と分離されたメモリ素子に確保されて、アドレスバス及びデータバスを経由して接続されているのも好適である。

#### 【発明の効果】

#### 【0011】

上記した本発明の遊技機によれば、複雑高度な画像演出を安定して実行することができる。

40

#### 【図面の簡単な説明】

#### 【0012】

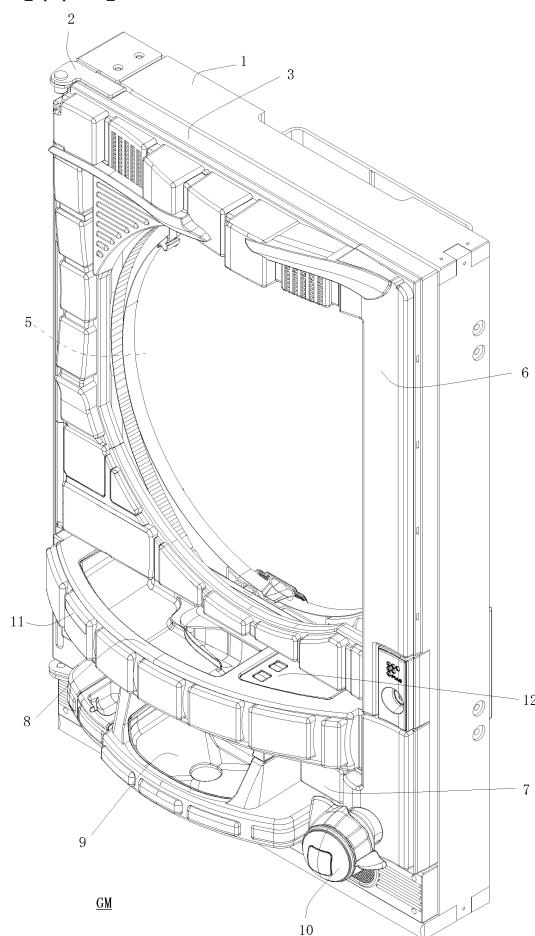

【図1】実施例に示すパチンコ機の斜視図である。

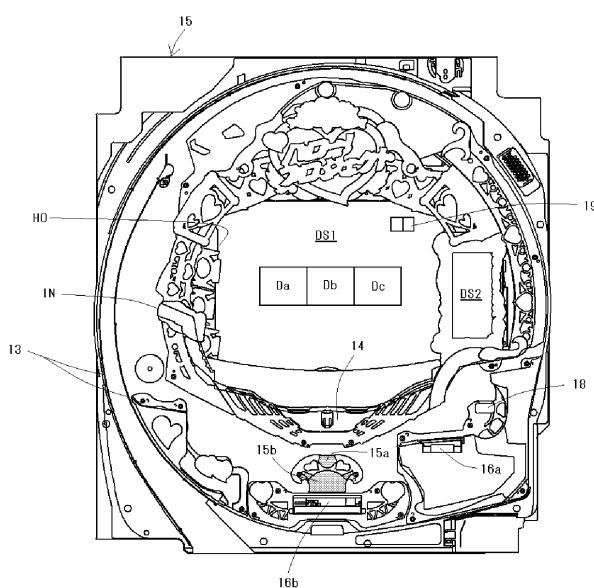

【図2】図1のパチンコ機の遊技盤を図示した正面図である。

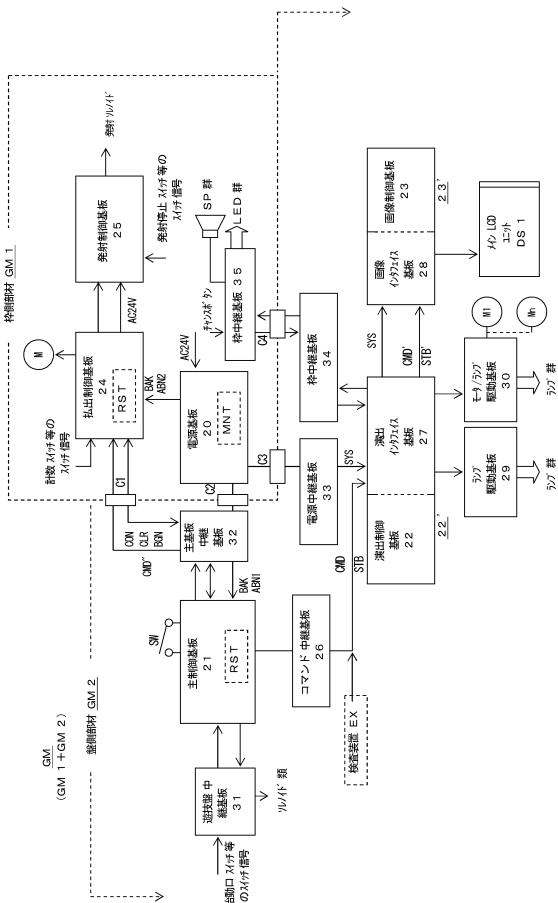

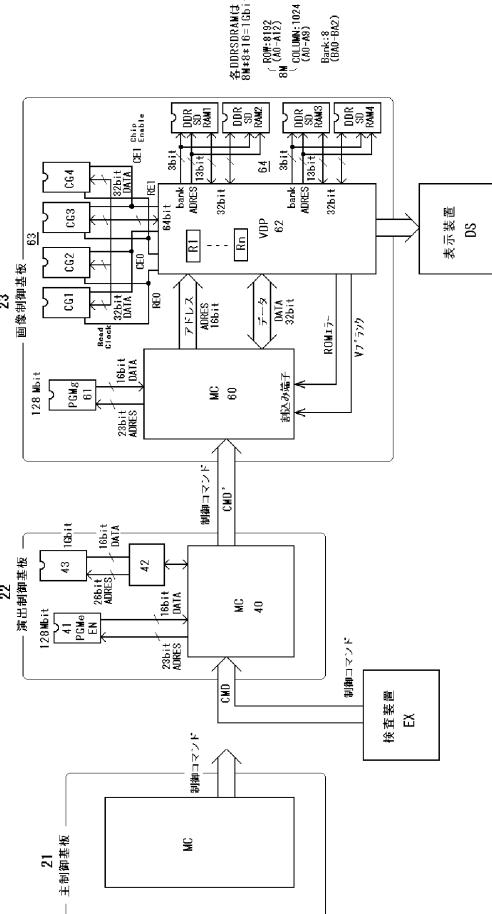

【図3】図1のパチンコ機の全体構成を示すブロック図である。

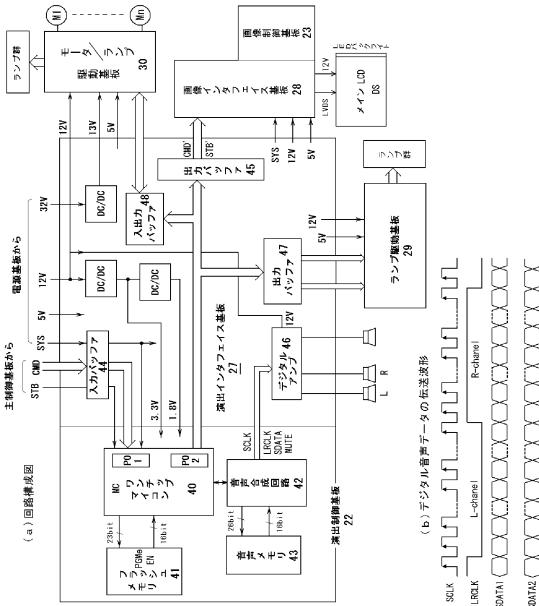

【図4】演出制御部の回路構成を例示するブロック図である。

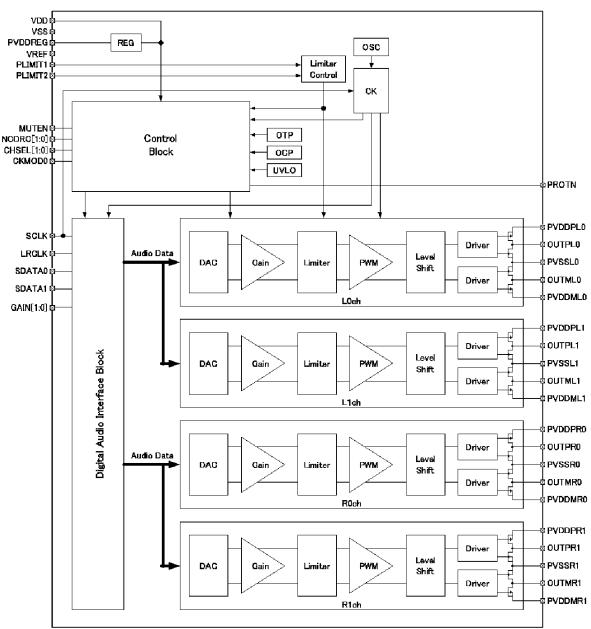

【図5】デジタルアンプの内部構成を例示するブロック図である。

【図6】モータ／ランプ駆動基板の内部構成を例示するブロック図である。

【図7】画像制御部の回路構成を例示するブロック図である。

50

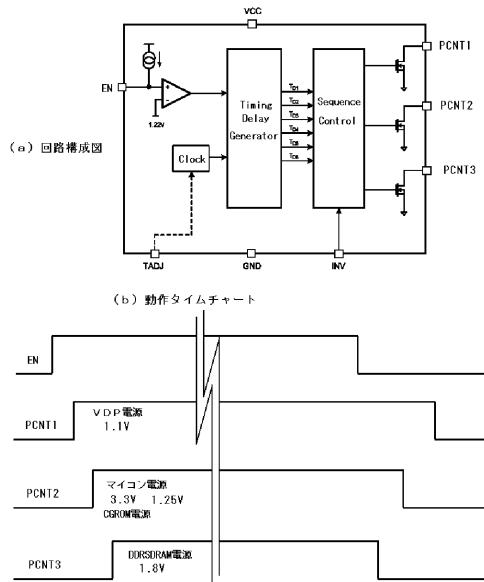

【図8】演出制御部と画像制御部のメモリ構成を概略的に説明する図面である。

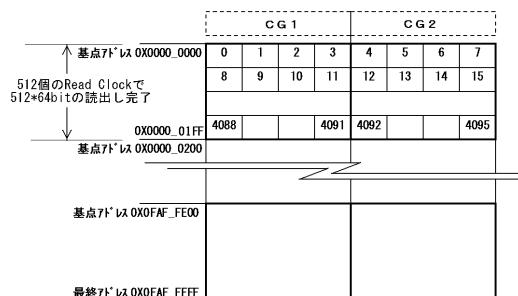

【図9】C G R O Mを構成するメモリ素子を説明する図面である。

【図10】図9メモリ素子のアドレス構成とチェックサム演算の手順を説明する図面である。

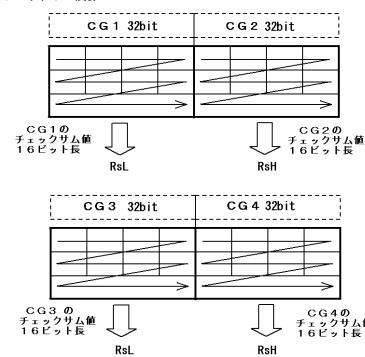

【図11】電源シーケンス回路の内部構成と動作を説明する図面である。

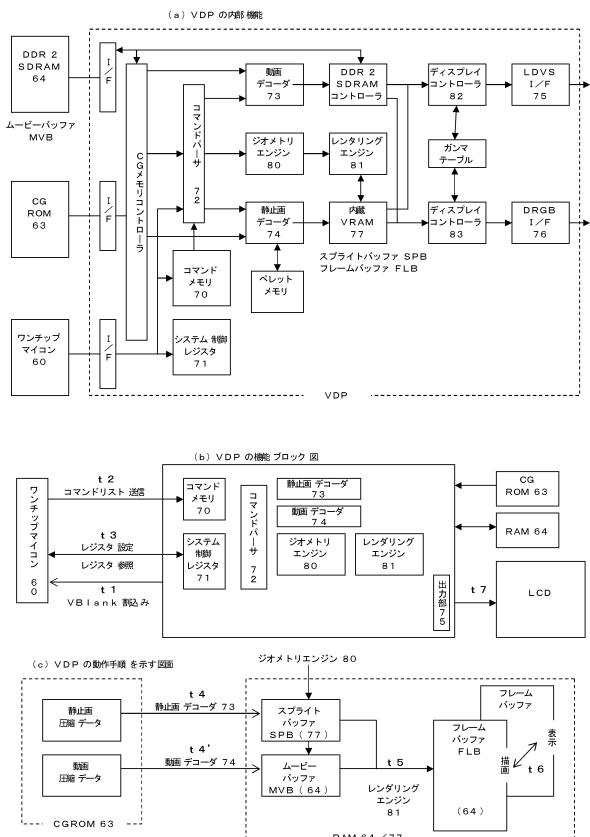

【図12】V D Pの内部構成と内部動作を説明する図面である。

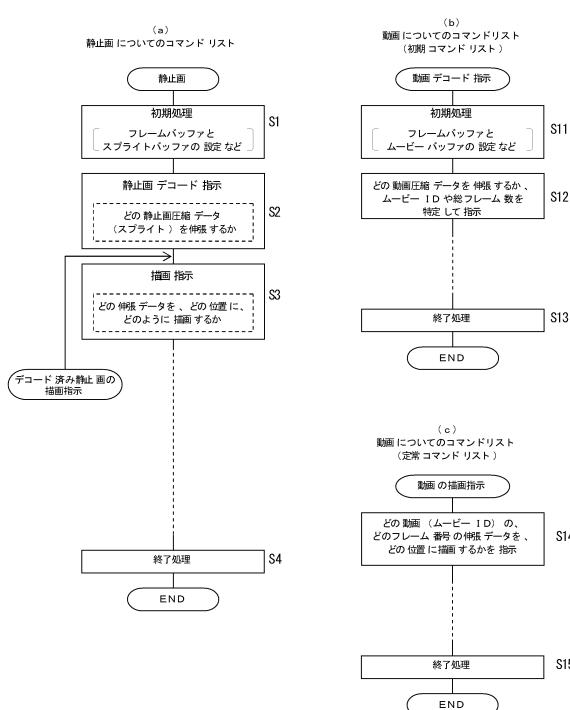

【図13】コマンドリストを説明する図面である。

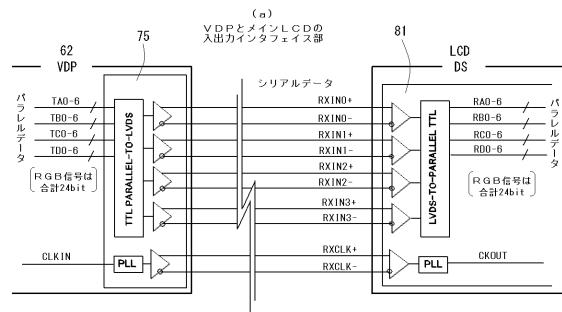

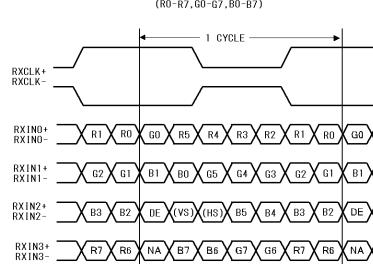

【図14】V D Pと表示装置との接続関係を説明する図面である。

【図15】画像演出動作を示す図面である。

【図16】図15の動作を規定する演出テーブルのデータ構造を示す図面である。 10

【図17】図15の一部を詳細に示す図面である。

【図18】画像演出部の動作を説明するフローチャートである。

【図19】図18の動作を説明するための図面である。

【発明を実施するための形態】

【0013】

以下、実施例に基づいて本発明を詳細に説明する。図1は、本実施例のパチンコ機G Mを示す斜視図である。このパチンコ機G Mは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく、表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。 20

【0014】

ガラス扉6の外周には、L E Dランプなどによる電飾ランプが、略C字状に配置されている。一方、ガラス扉6の上部左右位置と下側には、全3個のスピーカが配置されている。上部に配置された2個のスピーカは、各々、左右チャネルR,Lの音声を出力し、下側のスピーカは重低音を出力するよう構成されている。

【0015】

前面板7には、発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。 30

【0016】

上皿8の外周面には、チャンスボタン11が設けられている。このチャンスボタン11は、遊技者の左手で操作できる位置に設けられており、遊技者は、発射ハンドル10から右手を離すことなくチャンスボタン11を操作できる。このチャンスボタン11は、通常時には機能していないが、ゲーム状態がボタンチャンス状態となると内蔵ランプが点灯されて操作可能となる。なお、ボタンチャンス状態は、必要に応じて設けられるゲーム状態である。

【0017】

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設けられている。 40

【0018】

図2に示すように、遊技盤5の表面には、金属製の外レールと内レールとからなるガイドレール13が環状に設けられ、その略中央には、中央開口H Oが設けられている。そして、中央開口H Oの下方には、不図示の可動演出体が隠蔽状態で収納されており、可動予告演出時には、その可動演出体が上昇して露出状態となることで、所定の信頼度の予告演出を実現している。ここで、予告演出とは、遊技者に有利な大当たり状態が招来することを不確定に報知する演出であり、予告演出の信頼度とは、大当たり状態が招来する確率を意味している。 50

## 【0019】

中央開口HOには、大型の液晶カラーディスプレイ（LCD）で構成された表示装置DSが配置されている。表示装置DSは、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に表示する装置である。この表示装置DSは、中央部に特別図柄表示部Da～Dcと右上部に普通図柄表示部19とを有している。そして、特別図柄表示部Da～Dcでは、大当たり状態の招来を期待させるリーチ演出が実行されることがあり、特別図柄表示部Da～Dc及びその周りでは、適宜な予告演出などが実行される。

## 【0020】

遊技球が落下移動する遊技領域には、第1図柄始動口15a、第2図柄始動口15b、第1大入賞口16a、第2大入賞口16b、普通入賞口17、及び、ゲート18が配設されている。これらの入賞口15～18は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。

10

## 【0021】

第1図柄始動口15aの上部には、導入口INから進入した遊技球がシーソー状又はルーレット状に移動した後に、第1図柄始動口15に入賞可能に構成された演出ステージ14が配置されている。そして、第1図柄始動口15に遊技球が入賞すると、特別図柄表示部Da～Dcの変動動作が開始されるよう構成されている。

## 【0022】

第2図柄始動口15bは、左右一対の開閉爪を備えた電動式チューリップで開閉されるよう構成され、普通図柄表示部19の変動後の停止図柄が当り図柄を表示した場合には、所定時間だけ、若しくは、所定個数の遊技球を検出するまで、開閉爪が開放されるようになっている。

20

## 【0023】

なお、普通図柄表示部19は、普通図柄を表示するものであり、ゲート18を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート18の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止する。

## 【0024】

第1大入賞口16aは、前後方向に進退するスライド盤を有して構成され、第2大入賞口16bは、下端が軸支されて前方に開放する開閉板を有して構成されている。第1大入賞口16aや第2大入賞口16bの動作は、特に限定されないが、この実施例では、第1大入賞口16aは、第1図柄始動口15aに対応し、第2大入賞口16bは、第1図柄始動口15bに対応するよう構成されている。

30

## 【0025】

すなわち、第1図柄始動口15aに遊技球が入賞すると、特別図柄表示部Da～Dcの変動動作が開始され、その後、所定の大当たり図柄が特別図柄表示部Da～Dcに整列すると、第1大当たりたる特別遊技が開始され、第1大入賞口16aのスライド盤が、前方に開放されて遊技球の入賞が容易化される。

## 【0026】

一方、第2図柄始動口15bへの遊技球の入賞によって開始された変動動作の結果、所定の大当たり図柄が特別図柄表示部Da～Dcに整列すると、第2大当たりたる特別遊技が開始され、第2大入賞口16bの開閉板が開放されて遊技球の入賞が容易化される。特別遊技（大当たり状態）の遊技価値は、整列する大当たり図柄などに対応して種々相違するが、何れの遊技価値が付与されるかは、遊技球の入賞タイミングに応じた抽選結果に基づいて予め決定される。

40

## 【0027】

典型的な大当たり状態では、大入賞口16の開閉板が開放された後、所定時間が経過し、又は所定数（例えば10個）の遊技球が入賞すると開閉板が閉じる。このような動作は、最大で例えば15回まで継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部Da～Dcの変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別

50

遊技の終了後のゲームが高確率状態（確変状態）となるという特典が付与される。

#### 【0028】

図3は、上記した各動作を実現するパチンコ機GMの全体回路構成を示すブロック図であり、図4はその一部を詳細に図示したものである。図3に示す通り、このパチンコ機GMは、AC24Vを受けて各種の直流電圧や、電源異常信号ABN1、ABN2やシステムリセット信号（電源リセット信号）SYSなどを出力する電源基板20と、遊技制御動作を中心統括的に担う主制御基板21と、主制御基板21から受けた制御コマンドCMDに基づいてランプ演出及び音声演出を実行する演出制御基板22と、演出制御基板22から受けた制御コマンドCMD'に基づいて表示装置DSを駆動する画像制御基板23と、主制御基板21から受けた制御コマンドCMD"に基づいて払出モータMを制御して遊技球を払い出す払出制御基板24と、遊技者の操作に応答して遊技球を発射させる発射制御基板25と、を中心に構成されている。10

#### 【0029】

但し、この実施例では、主制御基板21が出力する制御コマンドCMDは、コマンド中継基板26と演出インタフェイス基板27を経由して、演出制御基板22に伝送される。また、演出制御基板22が出力する制御コマンドCMD'は、演出インタフェイス基板27と画像インタフェイス基板28を経由して、画像制御基板23に伝送され、主制御基板21が出力する制御コマンドCMD"は、主基板中継基板32を経由して、払出制御基板24に伝送される。制御コマンドCMD, CMD', CMD"は、何れも16ビット長であるが、主制御基板21や払出制御基板24が関係する制御コマンドは、8ビット長毎に2回に分けてパラレル送信されている。一方、演出制御基板22から画像制御基板23に伝送される制御コマンドCMD'は、16ビット長をまとめてパラレル伝送されている。そのため、可動予告演出を含む予告演出を、多様化して多数の制御コマンドを連続的に送受信するような場合でも、迅速にその処理を終えることができ、他の制御動作に支障を与えない。20

#### 【0030】

ところで、本実施例では、演出インタフェイス基板27と演出制御基板22とは、配線ケーブルを経由することなく、雄型コネクタと雌型コネクタとを直結されて二枚の回路基板が積層されている。同様に、画像インタフェイス基板28と画像制御基板23についても、配線ケーブルを経由することなく、雄型コネクタと雌型コネクタとを直結されて二枚の回路基板が積層されている。そのため、各電子回路の回路構成を複雑高度化しても基板全体の収納空間を最小化できると共に、接続ラインを最短化することで耐ノイズ性を高めることができる。30

#### 【0031】

これら主制御基板21、演出制御基板22、画像制御基板23、及び払出制御基板24には、ワンチップマイコン（MC）を備えるコンピュータ回路がそれぞれ搭載されている。そこで、これらの制御基板21～24とインタフェイス基板27～28に搭載された回路、及びその回路によって実現される動作を機能的に総称して、本明細書では、主制御部21、演出制御部22'、画像制御部23'、及び払出制御部24と言うことがある。すなわち、この実施例では、演出制御基板22と演出インタフェイス基板27とで演出制御部22'を構成し、画像制御基板23と画像インタフェイス基板28とで画像制御部23'を構成している。なお、演出制御部22'、画像制御部23'、及び払出制御部24の全部又は一部がサブ制御部である。40

#### 【0032】

また、このパチンコ機GMは、図3の破線で囲む枠側部材GM1と、遊技盤5の背面に固定された盤側部材GM2とに大別されている。枠側部材GM1には、ガラス扉6や前面板7が枢着された前枠3と、その外側の木製外枠1とが含まれており、機種の変更に拘わらず、長期間にわたって遊技ホールに固定的に設置される。一方、盤側部材GM2は、機種変更に対応して交換され、新たな盤側部材GM2が、元の盤側部材の代わりに枠側部材GM1を取り付けられる。なお、枠側部材1を除く全てが、盤側部材GM2である。50

## 【0033】

図3の破線枠に示す通り、枠側部材GM1には、電源基板20と、払出制御基板24と、発射制御基板25と、枠中継基板35とが含まれており、これらの回路基板が、前枠3の適所に各々固定されている。一方、遊技盤5の背面には、主制御基板21、演出制御基板22、画像制御基板23が、表示装置DSやその他の回路基板と共に固定されている。そして、枠側部材GM1と盤側部材GM2とは、一箇所に集中配置された接続コネクタC1～C4によって電気的に接続されている。

## 【0034】

電源基板20は、接続コネクタC2を通して、主基板中継基板32に接続され、接続コネクタC3を通して、電源中継基板33に接続されている。電源基板20には、交流電源の投入と遮断とを監視する電源監視部MNTが設けられている。電源監視部MNTは、交流電源が投入されたことを検知すると、所定時間だけシステムリセット信号SYSをLレベルに維持した後に、これをHレベルに遷移させる。10

## 【0035】

また、電源監視部MNTは、交流電源の遮断を検知すると、電源異常信号ABN1, ABN2を、直ちにLレベルに遷移させる。電源異常信号ABN1, ABN2は、電源投入後に速やかにHレベルとなる。

## 【0036】

ところで、本実施例のシステムリセット信号は、交流電源に基づく直流電源によって生成されている。そのため、交流電源の投入（通常は電源スイッチのON）を検知してHレベルに増加した後は、直流電源電圧が異常レベルまで低下しない限り、Hレベルを維持する。したがって、直流電源電圧が維持された状態で、交流電源が瞬停状態となっても、システムリセット信号SYSがCPUをリセットすることはない。なお、電源異常信号ABN1, ABN2は、交流電源の瞬停状態でも出力される。20

## 【0037】

主基板中継基板32は、電源基板20から出力される電源異常信号ABN1、バックアップ電源BAK、及びDC5V, DC12V, DC32Vを、そのまま主制御部21に出力している。一方、電源中継基板33は、電源基板20から受けたシステムリセット信号SYSや、交流及び直流の電源電圧を、そのまま演出インターフェイス基板27に出力している。演出インターフェイス基板27は、受けたシステムリセット信号SYSを、そのまま演出制御部22' と画像制御部23'に出力している。30

## 【0038】

一方、払出制御基板24は、中継基板を介することなく、電源基板20に直結されており、主制御部21が受けると同様の電源異常信号ABN2や、バックアップ電源BAKを、他の電源電圧と共に直接的に受けている。

## 【0039】

電源基板20が出力するシステムリセット信号SYSは、電源基板20に交流電源24Vが投入されたことを示す電源リセット信号であり、この電源リセット信号によって演出制御部22' と画像制御部23' のワンチップマイコンは、他のIC素子と共に電源リセットされるようになっている。40

## 【0040】

但し、このシステムリセット信号SYSは、主制御部21と払出制御部24には、供給されておらず、各々の回路基板21, 24のリセット回路\_RSTにおいて電源リセット信号(CPUリセット信号)が生成されている。そのため、例えば、接続コネクタC2がガタついたり、或いは、配線ケーブルにノイズが重畠しても、主制御部21や払出制御部24のCPUが異常リセットされるおそれはない。演出制御部22' と画像制御部23' は、主制御部21からの制御コマンドに基づいて、従属的に演出動作を実行することから、回路構成の複雑化を回避するために、電源基板20から出力されるシステムリセット信号SYSを利用している。

## 【0041】

ところで、主制御部21や払出制御部24に設けられたリセット回路RSTは、各々ウォッチドッグタイマを内蔵しており、各制御部21, 24のCPUから、定時的なクリアパルスを受けない限り、各CPUは強制的にリセットされる。

#### 【0042】

また、この実施例では、RAMクリア信号CLRは、主制御部21で生成されて主制御部21と払出制御部24のワンチップマイコンに伝送されている。ここで、RAMクリア信号CLRは、各制御部21, 24のワンチップマイコンの内蔵RAMの全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチSWのON/OFF状態に対応した値を有している。

#### 【0043】

10

主制御部21及び払出制御部24は、電源基板20から電源異常信号ABN1, ABN2を受けることによって、停電や営業終了に先立って、必要な終了処理を開始するようになっている。また、バックアップ電源BAKは、営業終了や停電により交流電源24Vが遮断された後も、主制御部21と払出制御部24のワンチップマイコンの内蔵RAMのデータを保持するDC5Vの直流電源である。したがって、主制御部21と払出制御部24は、電源遮断前の遊技動作を電源投入後に再開できることになる（電源バックアップ機能）。このパチンコ機では少なくとも数日は、各ワンチップマイコンのRAMの記憶内容が保持されるよう設計されている。

#### 【0044】

20

図3に示す通り、主制御部21は、主基板中継基板32を経由して、払出制御部24に制御コマンドCMD”を送信する一方、払出制御部24からは、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号CONや、動作開始信号BGNを受信している。ステータス信号CONには、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。動作開始信号BGNは、電源投入後、払出制御部24の初期動作が完了したことを主制御部21に通知する信号である。

#### 【0045】

30

また、主制御部21は、遊技盤中継基板31を経由して、遊技盤5の各遊技部品に接続されている。そして、遊技盤上の各入賞口16～18に内蔵された検出スイッチのスイッチ信号を受ける一方、電動式チューリップなどのソレノイド類を駆動している。ソレノイド類や検出スイッチは、主制御部21から配電された電源電圧VB(12V)で動作するよう構成されている。また、図柄始動口15への入賞状態などを示す各スイッチ信号は、電源電圧VB(12V)と電源電圧Vcc(5V)とで動作するインタフェイスICで、TTLレベル又はCMOSレベルのスイッチ信号に変換された上で、主制御部21に伝送される。

#### 【0046】

先に説明した通り、演出制御基板22と演出インターフェイス基板27とはコネクタ連結によって一体化されており、演出制御部22'は、電源中継基板33を経由して、電源基板20から各レベルの直流電圧(5V, 12V, 32V)と、システムリセット信号SYSを受けている（図3及び図4参照）。

#### 【0047】

40

また、演出制御部22'は、コマンド中継基板26を経由して、主制御部21から制御コマンドCMDとストローブ信号STBとを受けている（図3及び図4参照）。但し、製品の開発段階などで実行される動作試験においては、検査装置から演出制御部22'に対して各種のテスト用の制御コマンドがストローブ信号と共に供給される。

#### 【0048】

演出制御部22'は、ランプ駆動基板29にランプ駆動信号を出力することで多数のLEDランプや電飾ランプで構成されたランプ群を駆動している。また、モータ/ランプ駆動基板30に、ランプ駆動信号及びモータ駆動信号を出力することで、ランプ群を駆動すると共に、複数のステッピングモータで構成された演出モータ群M1～Mnを駆動している。なお、ランプ駆動信号とモータ駆動信号は、何れもシリアル信号であり、演出内容を

50

豊富化するべくランプ個数や演出モータ個数を如何に増やしても、配線ケーブルが増加することなく、機器構成が簡素化される。

#### 【0049】

ランプ群は、ほぼ定常にランプ演出を実現する一方、演出モータ群は、突然動作を開始して、可動演出体による可動予告演出を実現している。

#### 【0050】

また、演出制御部22'は、画像制御部23'に対して、制御コマンドCMD'及びストローブ信号STB'、電源基板20から受けたシステムリセット信号SYSと、2種類の直流電圧(12V, 5V)とを出力している(図3及び図4参照)。

#### 【0051】

そして、画像制御部23'では、制御コマンドCMD'に基づいて表示装置DSを駆動して各種の画像演出を実行している。図4に示す通り、表示装置DSは、LEDバックライトによって発光しており、画像インターフェイス基板28から5対のLVDS(低電圧差動伝送Low voltage differential signaling)信号と、バックライト電源電圧(12V)とを受けて駆動されている。表示装置DSのバックライト光は、PWM制御による輝度が制御可能に構成されている。

#### 【0052】

続いて、図4に基づいて、上記した演出制御部22'と画像制御部23'の構成を更に詳細に説明する。図4に示す通り、演出インターフェイス基板27は、電源中継基板33を経由して、電源基板20から3種類の直流電圧(5V, 12V, 32V)を受けている。ここで、直流電圧5Vは、デジタル論理回路の電源電圧として、演出インターフェイス基板27、ランプ駆動基板29、モータ/ランプ駆動基板30、画像インターフェイス基板28、及び画像制御基板23に配電されて各デジタル回路を動作させている。

#### 【0053】

但し、演出制御基板22には、直流電圧5Vが配電されておらず、12VからDC/DCコンバータで降圧された直流電圧3.3Vと、3.3VからDC/DCコンバータで更に降圧された直流電圧1.8Vだけが、演出インターフェイス基板27から演出制御基板22に配電されている。

#### 【0054】

このように、本実施例の演出制御基板22は、全ての回路が、電源電圧3.3V又はそれ以下の電源電圧で駆動されているので、電源電圧を5Vで動作する場合と比較して大幅に低電力化することができ、仮に、演出制御基板22の直上に演出インターフェイス基板27を配置しても積層しても放熱上の問題が生じない。

#### 【0055】

また、演出インターフェイス基板27が、電源基板20から受けた直流電圧12Vは、そのままデジタルアンプ46の電源電圧として使用されると共に、モータ/ランプ駆動基板30とランプ駆動基板29に配電されて各ランプ群の電源電圧となる。一方、電源基板20から受けた直流電圧32Vは、演出インターフェイス基板のDC/DCコンバータにおいて直流電圧13Vに降圧されて、モータ/ランプ駆動基板30に配電されている。

#### 【0056】

図4に示すように、演出制御部22'は、音声演出・ランプ演出・演出可動体による予告演出・データ転送などの処理を実行するワンチップマイコン40と、ワンチップマイコン40の制御プログラムPGMeや各種の演出データENを記憶するフラッシュメモリ(flash memory)41と、ワンチップマイコン40からの指示に基づいて音声信号を再生して出力する音声合成回路42と、再生される音声信号の元データである圧縮音声データを記憶する音声用メモリ43とを備えて構成されている。

#### 【0057】

なお、音声合成回路42と、音声用メモリ43とは、26ビット長の音声アドレスバスと、16ビット長の音声データバスで接続されている。そのため、音声用メモリ43には、1Gビットの圧縮音声データが記憶可能となる。そして、音声アドレスバス(26ビッ

10

20

30

40

50

ト)で指定される圧縮音声データ(16ビット)が、音声データバスに出力され、音声合成回路42において伸張されて音声データが再生される。

#### 【0058】

ところで、本実施例の場合、フラッシュメモリ41に記憶されている演出データENには、ランプ演出や音声演出の演出進行を管理するシナリオデータと、LEDの点滅様式を決定するランプ駆動データと、モータの回転様式を決定するモータ駆動データと、が含まれている。なお、ランプ駆動データやモータ駆動データは、1ビットずつ時間順次に出力されることで、ランプ駆動シリアル信号やモータ駆動シリアル信号となる。

#### 【0059】

図4や図8に示す通り、ワンチップマイコン40と、フラッシュメモリ41とは、23ビット長のCPUアドレスバスと、16ビット長のCPUデータバスとで接続されている。実施例のフラッシュメモリ41は、 $8M (=2^{23}) \times 16$ ビットのメモリ容量を有するが、フラッシュメモリ41に記憶されている制御プログラムには、演出データENを含んだ制御プログラムPGMeの全体について、チェックサム演算を実行するプログラムが内蔵されている。このチェックサム演算は、フラッシュメモリ41のデータを1バイト単位で加算し、その加算結果を2バイト長で保存する処理をしている。したがって、チェックサム値は、2バイト長となる。

#### 【0060】

ところで、ワンチップマイコン40、フラッシュメモリ41、及び音声用メモリ43は、電源電圧3.3Vで動作しており、また、音声合成回路42は、電源電圧3.3V及び電源電圧1.8Vで動作しており大幅な省電力化が実現されている。ここで、1.8Vは、音声合成回路のコンピュータ・コア部の電源電圧であり、3.3Vは、I/O部の電源電圧である。

#### 【0061】

ワンチップマイコン40には、複数のパラレル入出力ポートPIOが内蔵されている。そして、第1入力ポートPO1には、主制御部21からの制御コマンドCMD及びストローブ信号STBが入力され、第2入力ポートPO2からは、制御コマンドCMD'及びストローブ信号STB'が出力されるよう構成されている。

#### 【0062】

具体的には、第1入力ポートPO1には、主制御基板21から出力された制御コマンドCMDとストローブ信号(割込み信号)STBとが、演出インタフェイス基板27のバッファ44において、電源電圧3.3Vに対応する論理レベルに変換されて8ビット単位で二回に分けて供給される。そして、割込み信号STBは、ワンチップマイコンの割込み端子に供給され、受信割込み処理によって、演出制御部22'は、制御コマンドCMDを取得するよう構成されている。

#### 【0063】

演出制御部22'が取得する制御コマンドCMDには、(1)異常報知その他の報知用制御コマンドなどの他に、(2)図柄始動口への入賞に起因する各種演出動作の概要特定する制御コマンド(変動パターンコマンド)や、図柄種別を指定する制御コマンド(図柄指定コマンド)が含まれている。ここで、変動パターンコマンドで特定される演出動作の概要には、演出開始から演出終了までの演出総時間と、大当たり抽選における当否結果とが含まれている。

#### 【0064】

また、図柄指定コマンドには、大当たり抽選の結果に応じて、大当たりの場合には、大当たり種別に関する情報(15R確変、2R確変、15R通常、2R通常など)を特定する情報が含まれ、ハズレの場合には、ハズレを特定する情報が含まれている。変動パターンコマンドで特定される演出動作の概要には、演出開始から演出終了までの演出総時間と、大当たり抽選における当否結果とが含まれている。なお、これらに加えて、リーチ演出や予告演出の有無などを含めて変動パターンコマンドで特定しても良いが、この場合でも、演出内容の具体的な内容は特定されていない。

10

20

30

40

50

## 【0065】

そのため、演出制御部22'では、変動パターンコマンドを取得すると、これに続いて演出抽選を行い、取得した変動パターンコマンドで特定される演出概要を更に具体化している。例えば、リーチ演出や予告演出について、その具体的な内容が決定される。そして、決定された具体的な遊技内容にしたがい、LED群などの点滅によるランプ演出や、スピーカによる音声演出の準備動作を行うと共に、画像制御部23'に対して、ランプやスピーカによる演出動作に同期した画像演出に関する制御コマンドCMD'を出力する。

## 【0066】

このような演出動作に同期した画像演出を実現するため、演出制御部22'は、第2入力ポートPO2を通して、画像制御部23'に対するストローブ信号(割込み信号)STB'と共に、16ビット長の制御コマンドCMD'を演出インターフェイス基板27に向けて出力している。なお、演出制御部22'は、図柄指定コマンドや、表示装置DSに関連する報知用制御コマンドや、その他の制御コマンドを受信した場合は、その8ビット単位の制御コマンドを、16ビット長に纏めた状態で、割込み信号STB'と共に演出インターフェイス基板27に向けて出力している。

10

## 【0067】

上記した演出制御基板22の構成に対応して、演出インターフェイス基板27には出力バッファ45が設けられており、16ビット長の制御コマンドCMD'と1ビット長の割込み信号STB'を画像インターフェイス基板28に出力している。そして、これらのデータCMD'、STB'は、画像インターフェイス基板28を経由して、画像制御基板23に伝送される。

20

## 【0068】

また、演出インターフェイス基板27には、音声合成回路42から出力される音声信号を受けるデジタルアンプ46が配置されている。先に説明した通り、音声合成回路42は、3.3Vと1.8Vの電源電圧で動作しており、また、デジタルアンプ46は、電源電圧12VでD級増幅動作しており、消費電力を抑制しつつ大音量の音声演出を可能にしている。

## 【0069】

そして、デジタルアンプ46の出力によって、遊技機上部の左右スピーカと、遊技機下部のスピーカとを駆動している。そのため、音声合成回路42は、3チャネルの音声信号を生成する必要があり、これをパラレル伝送すると、音声合成回路42とデジタルアンプ46との配線が複雑化する。

30

## 【0070】

そこで、本実施例では、音質の劣化を防止すると共に、配線の複雑化を回避するため、音声合成回路42とデジタルアンプ46との間は、4本の信号線で接続されており、具体的には、転送クロック信号SCLKと、チャネル制御信号LRCLKと、2ビット長のシリアル信号SDATA1、SDATA2との合計4ビットの信号線に抑制されている。なお、何れの信号も、その振幅レベルは3.3Vである。

## 【0071】

ここで、SDATA1は、遊技機上部に配置された左右スピーカのステレオ信号R、Lを特定するPCMデータについてのシリアル信号であり、SDATA2は、遊技機下部に配置された重低音スピーカのモノラル信号を特定するPCMデータについてのシリアル信号である。そして、音声合成回路42は、チャネル制御信号LRCLKをLレベルに維持した状態で、左チャネルの音声信号Lを传送し、チャネル制御信号LRCLKをHレベルに維持した状態で、右チャネルの音声信号Rを传送する。重低音スピーカは、本実施例では1個であるので、モノラル音声信号が传送されているが、ステレオ音声信号として传送できるのは勿論である。

40

## 【0072】

何れにしても本実施例では、4種類の音声信号を4本のケーブルで传送可能であるので、最小のケーブル本数によってノイズによる音声劣化のない信号伝達が可能となる。すな

50

わち、シリアル伝送であるのでパラレル伝送より圧倒的にケーブル本数が少ない。アナログ伝送を探る場合には、ケーブル本数は同数であるが、3.3V振幅のアナログ信号に、少なからずノイズが重畠して、音質が大幅に劣化する。一方、振幅レベルを上げると、電源配線が複雑化する上に消費電力が増加する。

#### 【0073】

このようなシリアル信号SDATA1, SDATA2は、クロック信号SCLKの立上がりエッジに同期して、デジタルアンプ46に取得される。そして、デジタルアンプ46内部で、所定ビット長毎にパラレル変換され、DA変換後にD級増幅されて各スピーカに供給されている。

#### 【0074】

デジタルアンプ46の内部構成は適宜であるが、図5は、デジタルアンプとしてYDA171(YAMAHA)を使用した場合の内部構成図を示している。このような内部構成に限定されないが、何れにしても、本実施例では、音声合成回路42とデジタルアンプ46とをシリアル回線で接続するので、PCMデータ(音声データ)のビット長を如何に増やして高音質化を実現しても配線ケーブルその他を変更する必要がなく、回路構成の簡素化を維持することができる。

#### 【0075】

また、演出インターフェイス基板27には、ワンチップマイコン40から出力されるシリアルデータを出力するバッファ回路47, 48が設けられている。ここで、出力バッファ47は、ワンチップマイコン40から伝送されたランプ駆動信号(シリアル信号)を、ランプ駆動基板29に配置されたシフトレジスタ回路に転送している。そして、ランプ駆動基板29のシフトレジスタ回路(不図示)では、ランプ駆動信号をパラレル信号に変換してLEDランプ群を駆動している。

#### 【0076】

もう一方のバッファ回路48は、入出力バッファとして機能しており、ワンチップマイコン40から伝送されたシリアル信号をモータ/ランプ駆動基板30に、そのまま転送する一方、一群の演出モータM1~Mnの原点位置を示す原点センサ信号(シリアル信号)をワンチップマイコン40に転送している。

#### 【0077】

本実施例の場合、ワンチップマイコン40からバッファ回路48に伝送されたシリアル信号は、ランプ群を点灯させるためのランプ駆動信号(シリアル信号)と、演出モータを回転させるためのモータ駆動信号(シリアル信号)とが連続するよう構成されている。そして、モータ/ランプ駆動基板30では、これら一連のシリアル信号を16ビット長毎に分断すると共に、各16ビット長をパラレル信号に変換して、ランプ演出と可動予告演出を実行している。具体的には、制御コマンドCMDに対応して抽選決定された演出動作として、一連のランプ演出を実行すると共に、モータ駆動信号を受信した場合には、演出モータM1~Mnを回転させて適宜な可動予告演出を実行している。

#### 【0078】

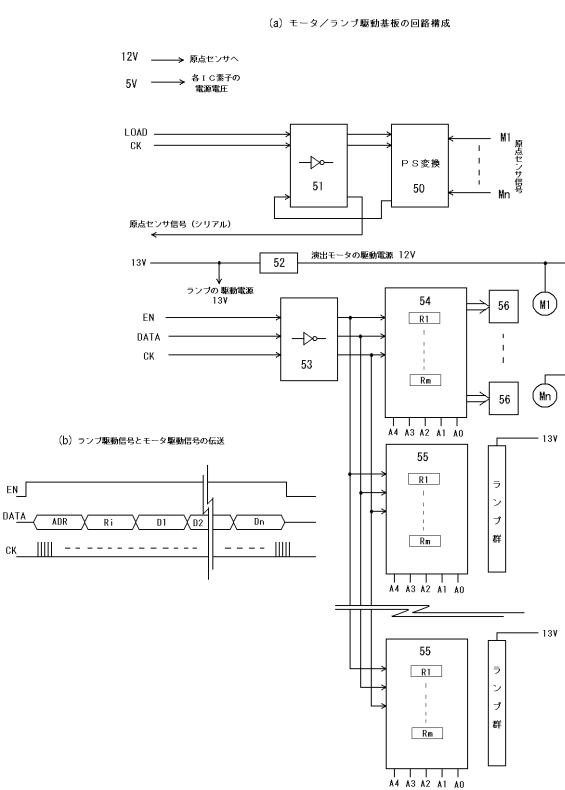

図6(a)は、モータ/ランプ駆動基板30の回路構成を、具体的に示すブロック図である。図示の通り、モータ/ランプ駆動基板30は、演出モータM1~Mnの原点センサ信号をシリアル変換するPS変換部50と、PS変換部50への制御信号をワンチップマイコン40から受ける入力バッファ51と、直流電圧13Vを12Vに降圧する降圧部52と、ランプ駆動信号やモータ駆動信号をワンチップマイコン40から受ける入力バッファ53と、ランプ群や演出モータ群を駆動制御する駆動制御部54, 55と、各演出モータの駆動電流を受けるシンクドライバ56とを有して構成されている。PS変換部50、入力バッファ51, 53、駆動制御部54、及び、シンクドライバ56は、直流電圧5Vを電源電圧として動作している。

#### 【0079】

原点センサ信号は、演出モータM1~Mnが原点に位置するか否かを検出する原点センサの出力であり、各原点センサは、直流電圧12V又は5Vを電源電圧としている。これ

10

20

30

40

50

ら各 1 ビットで全 n ビットの原点センサ信号は、ワンチップマイコン 40 が出力する保持信号 L O A D に同期して、P S 変換部 51 に取得され、P S 変換部 51 は、ワンチップマイコン 40 から受ける転送クロック C K に同期して、原点センサ信号をシリアル信号に変換してワンチップマイコン 40 に伝送している。

#### 【 0 0 8 0 】

このように、本実施例では、各演出モータ M1 ~ Mn が原点に位置しているか否かを、ワンチップマイコン 40 が適宜に把握できるよう構成されている。なお、各原点センサの電源電圧として、電磁ノイズが重畳する可能性のある電源ライン (13V) とは別系統の直流電圧 (12V, 5V) を使用することで誤判定の可能性を大幅に低減させている。

#### 【 0 0 8 1 】

次に、降圧部 52 は、その入力側 13V が各ランプの駆動電源として使用され、出力側 12V が演出モータ M1 ~ Mn の駆動電源として使用され、電源ラインが互いに分離されている。また、先に説明した通り、入力バッファ 53 や、駆動制御部 54, 55 は、直流電圧 13V とは全く別系統に生成された直流電圧 5V を電源電圧としている。

#### 【 0 0 8 2 】

そのため、大型の演出モータ群 M1 ~ Mn が突発的に動作を開始しても、各ランプのランプ駆動信号に電源ノイズなどの影響が及ぶ可能性が極めて低い。同様に、各ランプを高輝度で激しく点滅させても、各演出モータ M1 ~ Mn のモータ駆動信号に電源ノイズなどの影響が及ぶ可能性の極めて低い。

#### 【 0 0 8 3 】

ところで、演出モータ用の駆動制御部 54 と、ランプ用の駆動制御部 55 は、何れも同一構成であり、ワンチップマイコン 40 から、動作制御信号 E N と、シリアル信号 D A T A と、転送クロック信号 C K とを共通に受けて動作している。なお、シリアル信号 D A T A には、ランプ駆動信号とモータ駆動信号とが含まれている。

#### 【 0 0 8 4 】

この駆動制御部 54, 55 は、例えば、5 ビット長のアドレス端子 (A0 - A4) を有して、適宜にアドレスが付番可能に構成されている。この実施例では、5 ビット長のアドレス端子 (A0 - A4) は、ハードウェア構成として、予め H レベル又は L レベルに固定的に付番されている。

#### 【 0 0 8 5 】

また駆動制御部 54, 55 は、内部の多数の制御レジスタ R1 ~ Rm を有して構成され、各制御レジスタ R1 ~ Rm に制御データ D<sub>i</sub> (8 ビット長) を設定する (書込む) ことで、16 ビット長の出力端子の各出力が適宜に制御されるようになっている。

#### 【 0 0 8 6 】

制御レジスタ R1 ~ Rm のレジスタ番号は 8 ビット長である。また、5 ビット長のアドレス端子 (A0 - A4) は、この実施例では、予め、H / L レベルに設定されており、各素子 54, 55 のアドレス ADR<sub>i</sub> は固定値となる。

#### 【 0 0 8 7 】

各制御レジスタ R1 ~ Rm に制御データ D<sub>i</sub> を設定することで実現される動作内容としては、各出力端子の ON / OFF 状態だけでなく、ON / OFF 状態に至るまでのフェード動作 (fade in/out) の有無、ON 状態の出力端子の PWM 制御における duty 比 (0 ~ 99.6 %) などが可能である。そのため、輝度制御時や fade in/out 演出時に、ワンチップマイコン 40 は、ランプ駆動信号 (シリアルデータ) を、わざわざ PWM 制御用に変更する必要がなく、単に、該当レジスタ R<sub>i</sub> の制御データを設定変更するだけでよいので、制御負担が大幅に軽減される。

#### 【 0 0 8 8 】

もっとも、ランプ駆動信号を PWM 制御することで、固定的なフェード動作とは異なる fade in/out 演出時を実施できるのは勿論であり、要するに、本実施例によれば、多様なランプ演出が可能となる。このような多様なランプ演出を実行すると、駆動制御部 55 の出力信号に、かなりの高周波ノイズが重畳することが懸念されるが、その影響が演出モ-

10

20

30

40

50

タM<sub>1</sub>～M<sub>n</sub>に及びにくいことは前記した通りである。

#### 【0089】

ところで、図6(b)は、ワンチップマイコン40と、複数の駆動制御部54, 55・・・55との間の通信プロトコルを示すタイムチャートである。図示の通り、ワンチップマイコン40は、先ず、動作制御信号ENをON状態(Hレベル)に設定した状態で、(1)制御データDiを書込むべき駆動制御部54～55のアドレス番号ADRi(8ビット長)、(2)その駆動制御部における制御データDiを書込むべき制御レジスタR1～Rmの番号(8ビット長)、(3)その制御レジスタRiに書込むべき制御データDi(8ビット長の設定値)を、転送クロック信号CKに同期させてシリアル信号として出力する。

10

#### 【0090】

なお、一連の制御レジスタR1～Rmについて、その先頭レジスタ番号Riを指定すれば、その後に連続する制御データ(設定値)D1, D2, R3・・・は、Ri, Ri+1, Ri+2・・・の制御データであると駆動制御部54, 55に認識されて自動的に取得される。したがって、必ずしも、全ての制御レジスタRiに設定値を設定する必要は無く、例えば、一連M個の制御レジスタRi～Ri+M-1への書き込み処理であれば、制御データM個と、アドレスデータ2個とで、合計8×(M+2)ビット長の出力処理で足りる。

#### 【0091】

そして、全てのデータの出力を終えると、ワンチップマイコン40は、動作制御信号ENをON状態からOFF状態に戻せばよく、この動作に対応して、アドレス番号ADRiで特定された駆動制御部では、一連の制御レジスタRi・・・Ri+M-1に取得した制御データD1・・・に対応する動作を開始する。

20

#### 【0092】

演出モータM<sub>1</sub>～M<sub>n</sub>は、可動予告演出を実行するので、通常は隠蔽状態で原点位置に待機している。したがって、駆動制御部54は、OFF状態の制御データを保持したままであり、通常は、ワンチップマイコン40から、制御データの転送を受ける必要がない。しかし、この本実施例の制御駆動部は、アドレス番号ADRiを特定して制御データDiを受けるので、繰り返しシリアル信号が転送されても、アドレス番号で指定されない駆動制御部54には何の影響も与えない。

30

#### 【0093】

したがって、本発明の構成によれば、動的なランプ演出を継続的に繰り返すランプ制御用の駆動制御部55・・55と、稀にしか予告動作を開始しない可動予告演出用の駆動制御部54とを同一構成とすることができます。しかも、ワンチップマイコン40は、モータ駆動信号をランプ駆動信号に付加するか否かを判定する以外は、モータ駆動信号とランプ駆動信号とを同列に扱うことができるので、ワンチップマイコン40の制御負担を軽減することができる。

#### 【0094】

また、ランプ制御用の駆動制御部55・・55の全部又は一部を、同一アドレス値に設定することで、多数のランプに関する点灯データ(制御データ)の転送処理を纏めることができ、演出制御部22の制御負担が軽減される。例えば、遊技機の右側と左側のランプ群を、常に、同一態様で発光させる場合には、右側のランプ群を駆動する駆動制御部55Rと、左側のランプ群を駆動する駆動制御部55Lとを、同一アドレス値に設定するだけで、点灯データの転送処理を一回で終えることができる。

40

#### 【0095】

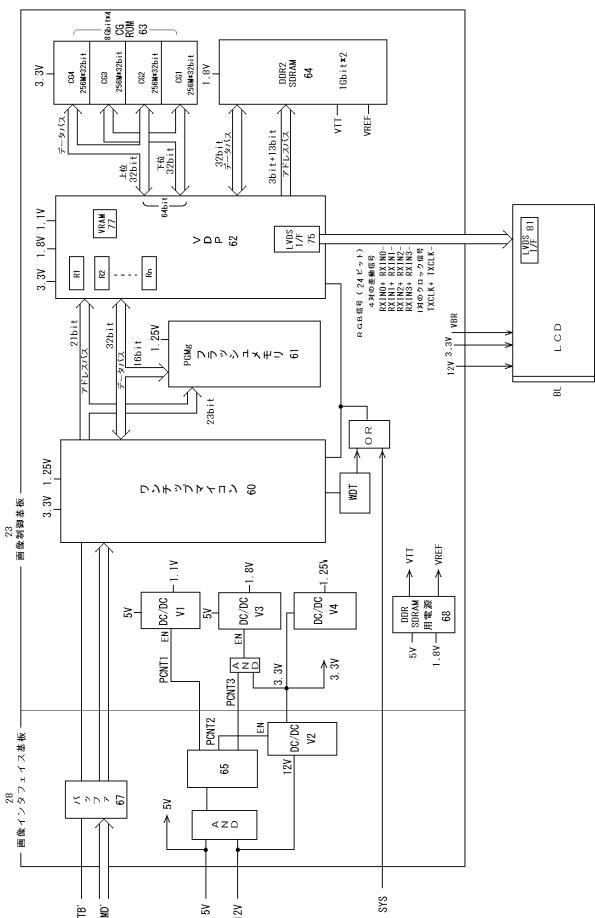

図7は、画像制御部23'(画像インタフェイス基板28と画像制御基板23)について、その周りの基板も含めて詳細に図示した回路ブロック図である。また、図8は、演出制御基板22と画像制御基板23について、特に、メモリ(ROM/RAM)と、マイクロプロセッサ(ワンチップマイコン)との接続関係を図示したブロック図である。先に説明した通り、画像制御部23'は、演出制御部22'から制御コマンドCMD'をストロ

50

ープ信号 S T B ' とシステムリセット信号 S Y S を受けて動作している。また、演出制御部を経由して 2 種類の直流電圧 5 V , 12 V を受けている。

#### 【 0 0 9 6 】

図 7 に示す通り、画像制御部 23' は、演出インターフェイス基板 27 を経由して制御コマンドを受信して画像制御動作を実行するワンチップマイコン 60 と、ワンチップマイコン 60 の制御プログラムなどを記憶するフラッシュメモリ 61 と、ワンチップマイコン 60 の指示に基づき表示装置 DS を駆動する VDP (Video Display Processor) 62 と、画像演出用の画像圧縮データを記憶するグラフィック ROM (CGROM) 63 と、VDP 62 の作業領域 (Video RAM) として機能する SDRAM (Synchronous Dynamic Random Access Memory) 64 と、ワンチップマイコン 60 を強制リセットさせるウォッチドッグタイマ WDT などを有して構成されている。なお、VDP 62 には、作業領域として活用される VRAM 77 も内蔵されている。

10

#### 【 0 0 9 7 】

CGROM 63 の画像圧縮データは、詳細には、動画圧縮データと静止画圧縮データに区分される。ここで、静止画とは、いわゆるスプライト画像であって、背景画や特別図柄やキャラクタなどを実現する単一の画像である。そして、表示装置 DS の所定位置に、所定の姿勢で 1 フレーム毎に描画される。一方、動画とは、連続的に変化する複数枚 (複数フレーム分) の静止画の集合を意味し、表示装置 DS に、複数枚の静止画が連続して描画されることで、円滑な移動動作が再現される。

#### 【 0 0 9 8 】

これらの圧縮データは、VDP 62 の内部回路でデコードされ、デコード後の画像データは、適宜な変換処理を経た上で、SDRAM 64 または内蔵 VRAM 77 に確保されたフレームバッファに格納され、これが表示装置 DS に出力されるようになっている。なお、これらの描画動作については図 12 に基づいて更に後述する。

20

#### 【 0 0 9 9 】

VDP 62 には、SDRAM 用のインターフェイス回路 (SDRAM\_I/F) と、CGROM 用のインターフェイス回路 (ROM\_I/F) と、ワンチップマイコン用のインターフェイス回路 (CPU\_I/F) とが内蔵されている (図 12 参照)。そして、VDP 62 と SDRAM 64 とは、SDRAM 用のインターフェイス回路 (SDRAM\_I/F) を経由して、3ビット + 13ビット長の SDRAM 用第一アドレスバスと、32ビット長の SDRAM 用第一データバスと、3ビット + 13ビット長の SDRAM 用第二アドレスバスと、32ビット長の SDRAM 用第二データバスと、で接続されている。

30

#### 【 0 1 0 0 】

ここで、第一と第二の各 16 ビット長のアドレス情報のうち、その 3 ビットは、バンク切替信号であり、残り 13 ビットは、時間分割されて認識される ROW データ (13 ビット) と COLUMN データ (10 ビット) である。このことに対応して、各メモリ (SDRAM) は、8 個のバンクに区分されているが、VDP 62 から SDRAM 64 に供給される 3 ビットが、バンク切替信号として機能する。

#### 【 0 1 0 1 】

また、ROW データ (13 ビット) と COLUMN データ (10 ビット) とを組み合わせることで、選択アドレスが  $8192 \times 1024 = 8M$  となり、これが 8 バンク存在するので、メモリ 1 個で合計  $64M \times 16\text{ビット} = 1G\text{ビット}$  長となる。

40

#### 【 0 1 0 2 】

本実施例の場合、SDRAM 64 は、動画圧縮データなどを伸張する作業領域として機能するが、メモリ容量 1 G ビットの DDR2 (double data rate 2) タイプの SDRAM を、合計 4 個使用することで、合計 4 G ビットである十分量のメモリ容量としている。

#### 【 0 1 0 3 】

各メモリのデータ入出力端子は、16 ビット長であるが、一対の SDRAM 64 について、一方のメモリのデータ入出力端子を、SDRAM 用データバスの上位 16 ビットに接続し、他方のメモリのデータ入出力端子を、SDRAM 用データバスの下位 16 ビットに

50

接続することで、32ビット単位での高速のデータアクセスを可能にしている。なお、このことは、第一データバス及び第二データバスに関して成立するので、第一と第二のデータバスを総合すると64ビット単位のデータアクセスが可能となる。また、本実施例では、特に、DDR2タイプのSDRAMを使用するので、高画質の動画データであっても支障なく円滑に再生することができ、高度な画像演出が可能となる。

#### 【0104】

続いて、CGRAM63について説明する。CGRAM63は、高画質の静止画や、高速で変化する演出動画などを生成するための画像データを、必要に応じて、圧縮状態で記憶するメモリである。そのため、SDRAM64のように任意のアドレスが、ランダムにアクセラルされる可能性が少なく、連続アドレスを順番にアクセスするシーケンシャルアクセスが多いと考えられる。10

#### 【0105】

そこで、本実施例では、この動作内容に着目して、CGRAM用のインターフェイス回路(ROM\_I/F)に用意されているROM用アドレスバスを使用することなく、全て、ROM用データバスによってデータリード動作を実現する構成を探っている。本実施例の構成によれば、基板上の配線を抑制して部品スペースを確保できるだけでなく、製造コストを抑制することができる。

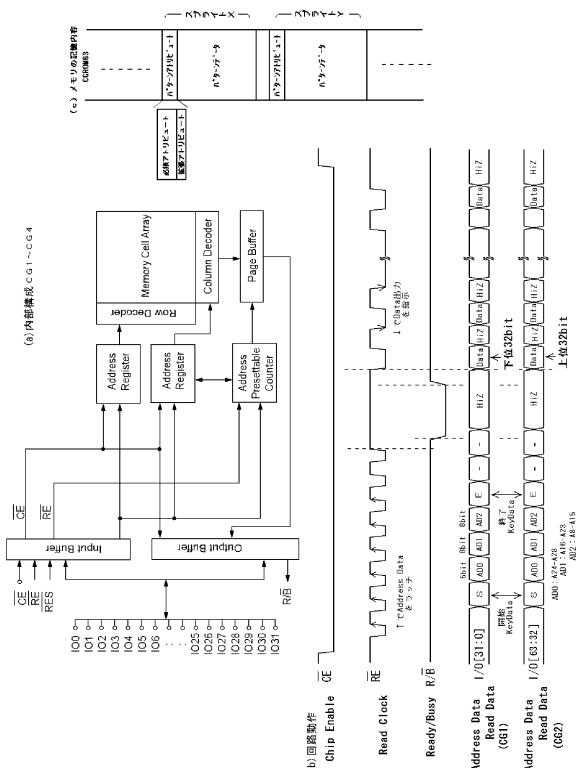

#### 【0106】

図9(a)は、本実施例の構成に好適なメモリ(8GビットROM)の内部構成を図示したものである。図示の通り、このメモリは、32ビット長のデータ入出力端子IO0～IO31と、チップイネーブル(Chip Enable)端子CEと、リードクロック(Read Clock)端子REと、動作状態出力端子R/Bと、リセット端子RESと、を有して構成されている。なお、素子一個の記憶容量は、 $256M \times 32\text{ビット} = 8\text{Gビット}$ 長である。20

#### 【0107】

図7～図8に示す通り、本実施例のCGRAM63は、上記した8Gビット長のメモリ(CG1～CG4)を4個配置して構成され、VDP62とCGRAM63とは、CGRAM用のインターフェイス回路(ROM\_I/F)を経由して、64ビット長のROM用データバスで接続されている。先に説明した通り、この実施例では、ROM用アドレスバスは使用しない。

#### 【0108】

4個のCGRAMのうち、メモリCG1とメモリCG3には、64ビットのROM用データバスの下位32ビットが接続され、メモリCG2とメモリCG4には、64ビットのROM用データバスの上位32ビットが接続されている。そして、メモリCG1とメモリCG2には、共通するチップイネーブル信号CE0とリードクロック信号RE0が供給されている(図8参照)。30

#### 【0109】

そのため、メモリCG1とメモリCG2は、同一タイミングでメモリリード(Memory Read)動作が実行されることになり、各メモリCG1, CG2から出力される各32ビットのデータが、ROM用データバスで連結されることで、64ビット単位のメモリリード動作が実現される。同様に、メモリCG3とメモリCG4にも、共通するチップイネーブル信号CE1と、リードクロック信号RE1が供給されることで、64ビット単位のメモリリード動作が実現される。40

#### 【0110】

図10(a)は、メモリCG1とメモリCG2の内部構成を図示したものであり、便宜上、0X0000\_0000番地以降の状態を示している。なお、0Xは、16進数表記を意味しており、例えば、本メモリの使用可能な最終アドレス0X0FAF\_FFFFは、10進数の263, 192, 575に該当する。

#### 【0111】

本実施例のVDP62は、CGRAM63のデータを1バイト単位で管理しており、1バイト単位でアドレスが付番されている。また、メモリCG1とメモリCG2には、同一50

のチップイネーブル信号 C E 0 とリードクロック信号 R E 0 が、共通して供給されると共に、メモリ C G 1 とメモリ C G 2 には、常に、同一のアドレス情報が供給されるよう構成されている。

#### 【 0 1 1 2 】

そのため、メモリ C G 1 の 3 2 ビットと、メモリ C G 2 の 3 2 ビットとを連続させてアドレス付番することができ、図 10 ( a ) に示す 0 、 1 、 2 、 3 、 4 、 5 、 6 、 7 … 4 0 9 5 は、各々、 1 バイト単位で付番される 0 番地、 1 番地、 2 番地、 … 4 0 9 5 番地を意味している。

#### 【 0 1 1 3 】

図 9 ( b ) は、各メモリ ( C G 1 , C G 2 ) の動作内容を示すタイムチャートであり、 V D P 6 2 が、メモリ C G 1 及びメモリ C G 2 から画像データを 6 4 ビット単位で読み出すメモリリード ( Memory Read ) 動作を図示している。 10

#### 【 0 1 1 4 】

V D P 6 2 は、先ず、チップイネーブル信号 C E 0 を L レベルにアサート ( assert ) した後、リードクロック信号 R E 0 を出力すると共に、 R O M 用データバスの下位 3 2 ビットと上位 3 2 ビットに、各々、適宜な同一のアドレス情報 A D 0 ~ A D 2 を出力する。ここで、アドレス情報 A D 0 ~ A D 2 は、一連のシーケンシャルアクセスの基点アドレス ( 開始アドレス ) を特定する 2 1 ビットデータである。このメモリ C G 1 ~ C G 4 では、基点アドレスの下位 9 ビット ( b i t 8 ~ b i t 0 ) が全て 0 である必要があるので、基点アドレスは、 0 X 2 0 0 飛びの値となる ( 図 10 ( a ) 参照 ) 。 20

#### 【 0 1 1 5 】

図 9 ( b ) に示す通り、アドレス情報 A D 0 ~ A D 2 は、開始用 K E Y データ S ( = 0 X B F B F \_ B F B F ) に続いて、三回に分けて、 A D 0 A D 1 A D 2 の順番に出力される。出力された各アドレス情報 A D 0 ~ A D 2 は、リードクロック信号 R E 0 の立上がりエッジに同期してメモリ C G 1 , C G 2 に取得される。

#### 【 0 1 1 6 】

この実施例では、 R O M 用データバスの上位 3 2 ビットがメモリ C G 2 に接続され、 R O M 用データバスの下位 3 2 ビットがメモリ C G 1 に接続されているが ( 図 7 参照 ) 、以下の説明において、同一のアドレス情報 A D 0 ~ A D 2 が、 R O M 用データバスの上位 3 2 ビットと下位 3 2 ビットに重複して出力される。したがって、例えば、基点アドレス 0 X 0 0 0 0 \_ 0 0 0 0 がアクセスされた場合には、図 10 ( a ) に示すメモリ C G 1 の 0 ~ 3 番地と、メモリ C G 2 の 4 ~ 7 番地がまとめてアクセスされることになる。 30

#### 【 0 1 1 7 】

何れにしても、アドレス情報 A D 0 は、 3 2 ビット長のアドレスのうち、 B i t 2 4 ~ B i t 2 8 の 5 ビットであり、同じ 5 ビットデータが、 B i t 8 ~ B i t 1 2 と、 B i t 1 6 ~ B i t 2 0 にも重複して出力される。そのため、データ伝送時に、例え、ビット化けが生じても、メモリ内部では、多数決論理などによって正しいビットデータを取得することができる。

#### 【 0 1 1 8 】

一方、アドレス情報 A D 1 は、 3 2 ビット長のアドレスのうち、 B i t 1 6 ~ B i t 2 3 の 8 ビットであり、同じ 8 ビットデータが、 B i t 8 ~ B i t 1 5 と、 B i t 2 4 ~ B i t 3 1 にも重複して出力される。また、アドレス情報 A D 2 は、 3 2 ビット長のアドレスのうち、 B i t 8 ~ B i t 1 5 の 8 ビットであり、同じ 5 ビットデータが、 B i t 1 6 ~ B i t 2 3 と、 B i t 2 4 ~ B i t 3 1 にも重複して出力される。 40

#### 【 0 1 1 9 】

このようにして、三回に分けてアドレス情報 A D 0 ~ A D 2 を出力した後、 V D P 6 2 が、終了用 K E Y データ E ( = 0 X 0 0 0 0 \_ 0 0 0 0 ) を出力することで、アドレス情報 A D 0 ~ A D 2 の送信が完了する。その後、同一のアドレス情報を受けたメモリ C G 1 , C G 2 においてデコード動作が完了すると、メモリ C G 1 , C G 2 の動作状態出力端子 R / B が L レベルのアサートされた後、メモリ C G 1 , C G 2 のデータが、各々、 3 2 ビ 50

ット単位で、ROM用データバスに出力される。なお、図9(b)において、HiZは、3状態出力におけるハイ・インピーダンス状態を意味し、-は、そのタイミングにおけるデータバスの値が、VDP62やメモリCG1, CG2に何の影響も与えないことを意味している。

#### 【0120】

VDP62が出力するリードクロックRE0の立下りエッジは、各メモリCG1, CG2に対するデータ出力指示となるので、VDP62は、リードクロックRE0の立下りエッジから所定タイミング経過後のROM用データバスのデータを取得することで、メモリリード動作を実行する。このようなメモリリード動作は、リードクロックRE0が継続される限り、連続して実行可能であり、本実施例の構成によれば、連続アドレスをアドレス順にアクセスするシーケンシャルアクセスを迅速に実行することができる。10

#### 【0121】

そして、必要なシーケンシャルアクセスが終われば、VDP62は、チップイネーブル信号CE0をHレベルに戻せば良く、その後ROMデータバスは、HiZ状態となる。

#### 【0122】

なお、開始用KEYデータS(=0XBFBF\_BFBF)に続けて、新規のアドレス情報(AD0~AD2)を出力すれば、別のアドレスのメモリリードを開始できるが、その基点アドレスは、0X0000\_0000に対して、0X200の整数倍の飛び飛びの値となる。図10(a)に示す通り、基点アドレスと次の基点アドレスとの間隔は、0X200=512であるので、512個のリードクロック(read clock)RE0が出力されることに対応して512\*64ビットのデータが取得される。20

#### 【0123】

このように、本実施例の構成によれば、開始用KEYデータS アドレス情報AD0 アドレス情報AD1 アドレス情報AD2 開始用KEYデータEのデータ伝送によって、メモリCG1とメモリCG2に、新規の同一の基点アドレスを指定した後は、リードクロック一個で、64ビット(CG1の32ビット+CG2の32ビット)のデータ(8番地分のデータ)をまとめて読み出すことができ、その後もリードクロックが出力される毎に、64ビットのデータが取得できるので、迅速なメモリリード動作が実現される。なお、この関係は、メモリCG3とメモリCG4についても同様である。30

#### 【0124】

ところで、このように構成されるCGROMには、図9(c)に示すデータ構造で、静止画や動画に関する多種類のスプライトを実現するCGデータが記憶されている。スプライトとは、例えば、キャラクタ図柄や背景画像など、一まとまりの画像を意味するが、このようなスプライトを実現するCGデータは、パターンアトリビュートとパターンデータとに区分されている。

#### 【0125】

ここで、パターンデータとは、スプライトの絵柄を決定するビットマップであり、例えば、画素数N×Mのスプライトについて、各画素を、例えば、24ビット階調のRGB三原色(RGB色空間)で表現する場合には、N×M×3×24ビット長となる。40

#### 【0126】

一方、パターンアトリビュートとは、パターンデータ固有の属性値を示す可変長データであり、4バイト長の必須アトリビュート領域と、可変長の拡張アトリビュート領域とで構成されている(図9(c)参照)。そして、必須アトリビュート領域には、スプライトの垂直方向及び水平方向のサイズを特定する3バイトデータの他に、パターンデータの情報(一画素のビット数や、色空間の種別など)や、アルファデータの格納フォーマットを指定する数ビットや、拡張アトリビュート領域にチェックサム値を記憶しているか否か、或いは、パターンデータ領域にアルファテーブルやパレットテーブルが存在するか否か、などを特定する数ビットが含まれている。

#### 【0127】

10

20

30

40

50

本実施例では、必須アトリビュート領域に所定ビットデータを記憶することで、拡張アトリビュート領域に、チェックサム値を記憶する構成を採っており、これに対応して、拡張アトリビュート領域の1バイト領域には、当該スプライトデータの8ビット総和値に加算すると、加算結果がゼロになるチェックサム値が記憶されている。

#### 【0128】

そして、スプライトデータ(CGデータ)を読み込む際には、VDP62は、付随してチェックサム演算を実行しており、全データ読み込み時の総和値に、チェックサム値を加算した加算結果がゼロにならない場合には、ROMエラー割り込みを発生させている。そして、このROMエラー割り込みに対応してワンチップマイコン60では、所定のエラー処理を実行するが、この点については後述する。

10

#### 【0129】

図7に戻って説明を続けると、画像制御部23'のワンチップマイコン60とVDP62は、21ビット長のCPUアドレスバスと、32ビット長のCPUデータバスとで接続されている。ワンチップマイコン60から評価すると、VDP62は、ワンチップマイコン60から任意にアクセス可能なI/Oデバイスに他ならず、VDP62に内蔵された多数のレジスタR<sub>1</sub>～R<sub>n</sub>がREAD/WRITEの対象となる。すなわち、CPUアドレスバスのアドレス情報で特定される所定のレジスタR<sub>i</sub>に、CPUデータバスに出力した情報を書き込むことで、VDP62に所定の動作の実行を指示することができ、また、所定のレジスタR<sub>j</sub>の情報を読み取ることで、VDP62の動作状態や動作結果を把握可能となっている。

20

#### 【0130】

VDPに内蔵されたレジスタR<sub>i</sub>には、例えば、チェックサム演算を実行する場合における(1)演算開始アドレスを規定するレジスタR<sub>x</sub>、(2)演算終了アドレスを規定するレジスタR<sub>y</sub>、(3)演算内容を規定するレジスタR<sub>z</sub>、及び、(4)2つの結果保存レジスタR<sub>sL</sub>、R<sub>sH</sub>が含まれている。そこで、本実施例では、これらのレジスタR<sub>x</sub>、R<sub>y</sub>、R<sub>z</sub>、R<sub>sL</sub>、R<sub>sH</sub>を活用することで、VDP62に、CGROM63の任意領域のチェックサム演算を実行させ、その演算結果をワンチップマイコン60がレジスタR<sub>sL</sub>、R<sub>sH</sub>から取得するようにしている。

#### 【0131】

このチェックサム演算は、ワンチップマイコン60が、上流側のワンチップマイコン40から検査用の制御コマンドを受けると開始され、レジスタR<sub>x</sub>に規定する演算開始アドレスから、レジスタR<sub>y</sub>に規定する演算終了アドレスまでのデータについてレジスタR<sub>z</sub>で規定された加算演算を実行する。

30

#### 【0132】

具体的には、CGROM63の1バイト単位の番地データについて、4バイト毎、つまりメモリ素子毎に、8ビット単位の加算演算を実行して、その演算結果を2つのレジスタR<sub>sL</sub>、R<sub>sH</sub>に、各々、16ビット長で保存している。図10(b)や図10(c)の矢印は、このチェックサム演算の手順を示すものであって、所定のメモリ素子CG<sub>i</sub>について、その実行開始アドレスから1バイト毎に、4バイト分の8ビット加算演算が完了すると、同じメモリ素子CG<sub>i</sub>の連続アドレスについて、8ビット加算演算が継続され、演算終了アドレスまでの加算演算が終わると、16ビット長の演算結果が、レジスタR<sub>sL</sub>とレジスタR<sub>sH</sub>に保存される。

40

#### 【0133】

なお、図示例では、メモリCG1及びCG2について、まとめてチェックサム演算を実行し、レジスタR<sub>sL</sub>にメモリCG1の加算結果を保存し、レジスタR<sub>sH</sub>にメモリCG2の加算結果を保存している。この点は、メモリCG3及びCG4についても同様であり、メモリCG3及びCG4について、まとめてチェックサム演算を実行して、レジスタR<sub>sL</sub>にメモリCG3の加算結果を保存し、レジスタR<sub>sH</sub>にメモリCG4の加算結果を保存している。

#### 【0134】

50

本実施例では、C G R O M 6 3に対する一回のアクセスで、64ビット長のデータが取得できるにも拘らず、あえて、4バイト毎に、8ビット長の加算演算を実行し、その結果を2バイト長で保存するので、ビット化けしたデータをメモリ素子C G i毎に検出することができる。すなわち、本実施例と相違して、64ビット長のデータを連續して加算したのでは、ビット化けを検出できても、ビット化けの生じているメモリ素子を特定することができない。

#### 【0135】

以上、S D R A M 6 4やC G R O M 6 3について説明したので、次に、画像制御部23'のフラッシュメモリ61について説明する。ワンチップマイコン60とフラッシュメモリ61は、23ビット長のC P Uアドレスバスと、16ビット長のC P Uデータバスとで接続されている。フラッシュメモリ61は、 $8M (=2^{23}) \times 16$ ビットのメモリ容量を有するが、制御プログラムには、定数データを含んだ制御プログラムの全体について、V D P 6 2が実行すると同じチェックサム演算を実行するプログラムが内蔵されている。すなわち、フラッシュメモリ61全体についても、1バイト単位の加算演算を実行して、その演算結果を16ビット長で保存している。

#### 【0136】

ところで、図7に示すウォッチドッグタイマW D Tの出力は、システムリセット信号S Y Sと共にO R回路に供給されており、O R回路への入力信号の何れかがアクティブルレベルになると、ワンチップマイコン60とV D P 6 2とが同期してリセットされるようになっている。したがって、ワンチップマイコン60のプログラム暴走などに起因して制御動作が初期化されると、これに対応して、V D P 6 2の動作を初期化されることになり、矛盾した不自然な画像演出が実行されることがない。

#### 【0137】

また、本実施例では、消費電力を可能な限り抑制するべく、各素子の電源電圧を最小化しており、各素子の電源電圧は、(1)ワンチップマイコン60が3.3Vと1.25V、(2)フラッシュメモリ61が1.25V、(3)V D P 6 2が3.3Vと1.8Vと1.1V、(4)C G R O M 6 3が3.3V、(5)S D R A M 6 4が1.8Vとなっている。

#### 【0138】

このように本実施例では、省電力化のために多数の直流電圧が必要となり、しかも、複数の電源電圧を有する回路素子については、その供給タイミングを最適化する必要がある。一方、演出制御部22' と画像制御部23'との間の配線ケーブル数を抑制する趣旨から2種類の直流電圧しか配電されていない。

#### 【0139】

そこで、制御端子を有する複数のD C / D Cコンバータを配置すると共に、電源シーケンサ65を設けることで、多数の直流電圧を最適なタイミングで各素子に供給している。図11は、電源シーケンサ65の一例としてL M 3 8 8 1(national semiconductor)の内部構成(a)と、電源シーケンサ65を使用した場合にも実行される動作タイムチャート(b)を図示したものである。

#### 【0140】

図11(a)の電源シーケンサ65の場合には、I N V端子がLレベルであると、Hレベルの動作開始指令E Nを受けて動作を開始し、T A D J端子に接続されるキャパシタンスで規定されるクロック信号C l o c kの9周期後に第一制御信号P C N T 1が立上り、クロック信号の8周期後に第二制御信号P C N T 2が立上り、クロック信号の更に8周期後に第三制御信号P C N T 3が立上がる。

#### 【0141】

一方、動作開始指令E NがLレベルに遷移すると、クロック信号の9周期後に第三制御信号P C N T 3が立下り、クロック信号の8周期後に第二制御信号P C N T 2が立下り、クロック信号の更に8周期後に第三制御信号P C N T 3が立上がる。

#### 【0142】

10

20

30

40

50

本実施例では、図7に示す通り、動作開始指令E Nは、演出制御部22'（演出インターフェイス基板27）から供給される2種類の直流電圧のAND論理出力となっている。そして、第一制御信号P C N T 1は、1.1V生成用のDC/DCコンバータV1の動作イネーブル端子E Nに供給され、第二制御信号P C N T 2は、3.3V生成用のDC/DCコンバータV2の動作イネーブル端子E Nに供給されている。

#### 【0143】

また、第三制御信号P C N T 3は、3.3VとのAND論理出力に変換されて、1.8V生成用のDC/DCコンバータV3の動作イネーブル端子E Nに供給されている。上記した各DC/DCコンバータは、動作イネーブル端子E NがHレベルとなることを条件に電圧変換動作を開始する。

10

#### 【0144】

そのため、図11(b)に示す通り、演出制御部22'から配電される5Vに基づいてDC/DCコンバータV1が最初に機能して、直流電圧1.1Vが生成される。この直流電圧1.1Vは、V D P 6 2に内蔵されたデジタル回路及び内蔵VRAM用の電源電圧であり、他の内蔵回路より先に動作を開始することで、電源投入後のV D P 6 2の正常な動作開始シーケンスが担保される。

#### 【0145】

上記の動作の後に、第二制御信号P C N T 2がHレベルになるので、演出制御部22'から配電される12Vを受けるDC/DCコンバータV2が機能して直流電圧3.3Vが生成される。直流電圧3.3Vは、1.25V用のDC/DCコンバータV4に供給されているが、このコンバータV4には、動作イネーブル端子が存在しないので、直ちに、動作を開始して、直流電圧1.25Vが生成される。

20

#### 【0146】

これら第二制御信号P C N T 2に制御されて生成される2種類の直流電圧3.3V、1.25Vは、ワンチップマイコン60、フラッシュメモリ61、及びC G R O M 6 3に、ほぼ同タイミングで供給されるので、前記の各回路素子は、電源投入後に遅滞なく動作開始の準備が完了することになる。なお、このタイミングでは、システムリセット信号S Y SがLレベルであり、このレベルがしばらく維持された後に、Hレベルに変化するよう電源基板の電源回路が動作しているので、ワンチップマイコン60は、正しく電源リセットされることになる。

30

#### 【0147】

最後に第三制御信号P C N T 3がHレベルに変化すると、第三制御信号P C N T 3と3.3VのAND論理出力が、DC/DCコンバータV3に供給されて直流電圧1.8Vが生成される。この直流電圧1.8Vは、V D P 6 2と、S D R A M 6 4と、SDRAM用の電源回路68とに、ほぼ同タイミングで供給されるので、S D R A M 6 4と、V D P 6 2内部のSDRAMインターフェイス回路が同期して動作可能状態となる。したがって、システムリセット信号S Y SがHレベルに変化すると、V D P 6 2は、円滑に初期設定動作を開始することができる。

#### 【0148】

図12(a)は、V D P 6 2の内部構成を示すブロック図であり、V D P 6 2と、C G R O M 6 3、D D R 2タイプのS D R A M 6 4、及びワンチップマイコン60(以下、ホストC P U 6 0と言う)との接続関係も含めて図示している。また、図12(b)は、V D P 6 2の動作を示す機能ブロック図であり、図12(c)は、V D P 6 2の動作手順を示す図面である。

40

#### 【0149】

図12(b)に示す通り、V D P 6 2からホストC P U 6 0に、V B l a n k割込み信号が伝送されており、通常1/60秒毎に生じるV B l a n k割込み信号に基づいて、ホストC P U 6 0は、表示装置DSの1フレーム分の表示動作が終わったことが把握できるよう構成されている。

#### 【0150】

50

図12(a)や図12(b)に示す通り、VDP62は、ホストCPU60によってコマンドリストが書込まれるコマンドメモリ70と、ホストCPU60からアクセスされるシステム制御レジスタ71と、コマンドリストを解析するコマンドパーサ(構文解析器)72と、静止画圧縮データをデコードする静止画デコーダ73と、動画圧縮データをデコードする動画デコーダ74と、デコーダでデコード(伸張)された画像について、拡大・縮小・回転・移動などのアフィン変換や投影変換などを実行するジオメトリエンジン80と、表示装置DSに出力可能な画像データを生成するレンダリングエンジン81と、LCD(Liquid Crystal Display)の各種の信号を生成するディスプレイコントローラ82、83と、信号出力部(LVDS送信部75及びRGB送信部76)と、を有して構成されている。

10

#### 【0151】

システム制御レジスタ71は、VDP62に対する指示データなどをホストCPU60が書込む入力レジスタ群と、VDP62の動作状態などを示す情報をホストCPU60が読み出す出力レジスタ群と、に大別される。そして、ホストCPU60は、適宜な入力レジスタに、必要な設定値を書き込むことで、VDP62を適宜に動作させ、必要な出力レジスタの値を参照することで、VDP62の動作状態を把握している。

#### 【0152】

VDP62の描画動作は、ホストCPU60がコマンドメモリ70に書き込んだコマンドリストを、コマンドパーサ72が解析することで毎フレーム実行される。この描画動作のため、本実施例では、静止画圧縮データをデコードして一時保存するスライトバッファS PBが、内蔵RAM77に確保され、動画圧縮データをデコード(伸張)して一次保存するムービーバッファM VBが、SDRAM64に確保されている。すなわち、静止画デコーダ73は、コマンドパーサ72によるコマンドリストの解析結果に基づいて、所定の静止画圧縮データをデコードして、デコード結果をスライトバッファS PB(内蔵RAM77)に格納する。また、動画デコーダ74は、コマンドパーサ72によるコマンドリストの解析結果に基づいて、所定の動画圧縮データをデコードして、デコード結果をムービーバッファM VB(SDRAM64)に格納する。

20

#### 【0153】

このようにして伸張された静止画や、動画一フレーム分の静止画は、スライトバッファS PBやムービーバッファM VBにおいて、コマンドリストで指示された内容に基づき、ジオメトリエンジン80が、拡大・縮小・回転・移動などのアフィン変換や、投影変換などの処理を施す。そして、その後、レンダリングエンジン81が機能して、スライトバッファS PBやムービーバッファM VBのデータが、SDRAM64か又は内蔵RAM77に確保されたフレームバッファFLBに纏められる。

30

#### 【0154】

本実施例ではフレームバッファFLBを内蔵RAM77に確保するが、DDR2タイプのSDRAM64を使用しているので、フレームバッファFLBをSDRAM64に確保しても処理速度上の問題が生じない。

#### 【0155】

何れのメモリ64,77に確保された場合でも、フレームバッファFLBは、ダブルバッファ構造を有しており、一方が表示用バンクとして機能し、他方が描画用バンクとして機能し、その機能を毎フレーム毎に切り替えて動作している。なお、表示用バンクの画像データが表示装置DSに出力され、描画用バンクには、レンダリングエンジン81によって画像データが書き込まれる。

40

#### 【0156】

次に、以上の説明を、図12(b)～図12(c)に基づいて整理しておく。ホストCPU60は、例えば、VB1ank割込み(t1)に起因して、コマンドメモリ70にコマンドリストを書き込む(t2)。次に、ホストCPU60は、コマンドリストの開始アドレスやその他の制御情報をシステム制御レジスタ71に設定することでVDP62の描画動作を開始させる(t3)。

50

**【0157】**

すると、この描画開始の指示に対応して静止画デコーダ73や動画デコーダ74が動作し、コマンドメモリ70のコマンドリストに基づいて、CGRAM63の圧縮データが読み出され、デコード結果が、スプライトバッファSPBや、ムービーバッファMVBに展開される(t4, t4')。

**【0158】**

次に、コマンドリストに基づいて、スプライトバッファSPBやムービーバッファMVBのデータに対して、ジオメトリエンジン80が座標演算を実行し、その演算結果に基づいて、レンダリングエンジン81が描画動作を実行する。そして、描画結果は、フレームバッファFLBの描画バンクに書き込まれる(t5)。

10

**【0159】**

次に、フレームバッファFLBの描画バンクと表示バンクを切り換えると(t6)、その後、ディスプレイコントローラ82が機能して、フレームバッファFLB(表示バンク)の画像データに基づいて、出力信号が生成され表示装置DSに出力される(t7)。なお、本実施例では、LVDSS\_I/F部75を経由してLCDたる表示装置DSが駆動されている。

**【0160】**

以上、VDPの動作手順を説明したので、続いて、図13に基づいてコマンドリストについて説明する。コマンドリストは、VDP62(コマンドパーサ72)に対する指令を列記したコマンド列であるが、その記載内容や記載順序が、静止画の描画を指示する場合と、動画の描画を指示する動作とでやや相違する。

20

**【0161】**

静止画の描画をVDPに指示するコマンドリストの場合には、図13(a)に示す通り、先ず、フレームバッファFLBやスプライトバッファSPBのメモリ領域を具体的に設定する(S1)。なお、先に説明した通り、この実施例では、スプライトバッファSPBと、フレームバッファFLBが内蔵VRAM77に設定され、バッファサイズは、スクリーンサイズ(例えば、640×320)に対応して設定される。

**【0162】**

次に、静止画のデコードを指示する(S2)。デコード指示は、具体的には、どの静止画圧縮データをデコードするかの指示であり、対象スプライトを記憶するCGRAM63の先頭アドレスやデータサイズなどを指示して実行される。なお、本実施例では、スプライトバッファSPBのメモリ領域を適宜に設定できるので、例えば、高頻度で使用する静止画を、予め、特別なスプライトバッファ領域にデコードしておくこともできる。

30

**【0163】**

このようにして、所定の静止画(スプライト)についてのデコード指示がされた後、デコードされた伸張データを、表示装置DSのどの座標位置に、どのような態様(回転角度や縮小拡大など)で描画するかを描画指示する(S3)。そして、バンクフリップなどの終了処理用コマンドを記入すれば(S4)、特定のスプライトについてのコマンドリストが完了する。なお、バンクフリップとは、描画バンクと表示バンクを切り替えることを意味する(図12(c)t6参照)。

40

**【0164】**

ところで、描画すべきスプライトが複数個存在する場合には、複数個のスプライトについて、デコード指示(S2)と描画指示(S3)とが繰り返し実行される。なお、このような場合、描画位置が重複する場合があるが、最初に描画された画像の優先度が最低となり、最後に描画された画像が最高優先度となる。また、先に説明した通り、上書きされない特別なスプライトバッファ領域にデコードされた伸張データは、デコード済み静止画の描画指示に基づいて、繰り返し使用することもできる。

**【0165】**

動画の描画をVDPに指示するコマンドリストの場合には、図13(b)の初期コマンドリストと、図13(c)の定常コマンドリストの構成となる。

50

**【 0 1 6 6 】**

図13(b)に示す通り、動画の場合も、最初に、フレームバッファFLBやムービーバッファMVBのメモリ領域を具体的に設定する(S11)。先に説明した通り、この実施例では、ムービーバッファMVBがSDRAM74に設定され、フレームバッファFLBは、内蔵VRAM77に設定される。なお、フレームバッファFLBのバッファサイズは、スクリーンサイズ(例えば、640×320)に対応して静止画の場合と同一に設定される。

**【 0 1 6 7 】**

次に、動画のデコードを指示する(S12)。デコード指示は、具体的には、どの動画圧縮データをデコードするかの指示であり、該当する動画を記憶するCGROM63の先頭アドレスを、その動画を特定するムービーIDや、その動画の総フレーム数などと共に指示する。そして、終了処理用コマンドを記入して初期コマンドリストを終える(S13)。

10

**【 0 1 6 8 】**

この初期コマンドリストが実行されると、一連の静止画の構成された動画圧縮データがデコードされて、伸張データがムービーバッファMVBに展開される。そこで、描画すべきフレーム番号についてのデコードが完了した後、ホストCPU60は、図13(c)の定常コマンドリストを、コマンドメモリ70に発行する。

**【 0 1 6 9 】**

定常コマンドリスト(図13(c))は、動画を構成する一連の静止画についての描画指示で構成されており、具体的には、ムービーIDで特定される動画について、どのフレーム番号の伸張データを、表示装置DSのどの座標位置に描画するかを描画指示する(S14)。そして、終了処理用コマンドを記入すれば(S14)、特定の動画についての定常コマンドリストが完了する。

20

**【 0 1 7 0 】**

その後、ホストCPU60は、同一のムービーIDについて、フレーム番号を更新した定常コマンドリストを繰り返しコマンドメモリ70に発行すればよく、動画の再生は、初回分のコマンドリスト(初期コマンドリスト)と、その後、フレーム数分の複数回のコマンドリスト(定常コマンドリスト)とで実現される。

**【 0 1 7 1 】**

30

図14は、上記した動作をして画像データを生成するVDP62と、表示装置DSとの接続関係について、LVDS送信部75をより詳細に図示したものである。図示の通り、本実施例の表示装置DSは、VDP62のLVDS送信部(LVDS\_I/F)75に対応するLVDS受信部(LVDS\_I/F)81を内蔵して構成されている。

**【 0 1 7 2 】**

図14(a)に示す通り、LVDS\_I/F部(LVDS送信部)75は、RGBデータ24ビットを含んだパラレルデータを、LVDS(low voltage differential signaling)信号に変換する部分である。LVDSとは、RGBデータなどを低ノイズ、低電力で高速伝送するための低電圧差動伝送方式を意味し、本実施例では、一対の信号伝送ライン(1本のツイストペア線)に数mAの程度の低レベルの信号電流を送信側から供給する一方、この信号電流を受信側に設けた100程度の終端抵抗で受ける構成を探っている。したがって、電圧振幅は、数100mV程度の低レベルであるが、論理レベル(H/L)に対応して電流方向を代えることで確実な信号伝送を実現している。

40

**【 0 1 7 3 】**

そして、この実施例では、図14(a)に示す通り、全24ビット長のRGB信号(各8ビット長)と、水平/垂直同期信号とを含んだ合計28ビット長のパラレルデータ(TA0~TA6, TB0~TB6, TC0~TC6, TD0~TD6)を、LVDS送信部75において、4対の差動信号に変換している。そして、これに、一対の転送クロックの差動信号を加えて、5本のツイストペア線で表示装置DSに伝送している。

**【 0 1 7 4 】**

50

なお、図7や図14(a)では、これら4対の差動信号を、表示装置DSの立場から評価して、(RXIN0+, RXIN0-), (RXIN1+, RXIN1-), (RXIN2+, RXIN2-), (RXIN3+, RXIN3-)、(RXCLK+, RXCLK-)と記載している。

#### 【0175】

図14(b)に示すように、転送クロックRXCLKの一周期の間に、ツイストペア線(RXIN0+, RXIN0-)では、G0 R5 R4 R3 R2 R1 R0をシリアル転送し、ツイストペア線(RXIN1+, RXIN1-)では、B1 B0 G5 G4 G3 G2 G1をシリアル転送し、ツイストペア線(RXIN2+, RXIN2-)では、DE (VS) (HS) B5 B4 B3 B2をシリアル転送し、ツイストペア線(RXIN3+, RXIN3-)では、NA B7 B6 G7 G6 R7 R6をシリアル転送している。

10

#### 【0176】

ここで、R0～R7は、赤色画素の輝度を示す8ビット長データ、G0～G7は、緑色画素の輝度を示す8ビット長データ、B0～B7は、青色画素の輝度を示す8ビット長データである。また、(VS)や(HS)は、垂直同期タイミング、水平同期タイミングであることを示し、DEは、DATA ENABLEを意味している。なお、NAは未使用である。

#### 【0177】

上記した4対の差動信号を受ける表示装置DSには、VDP62のLVDS送信部75に対応するLVDS受信部81が設けられている。そして、一連のシリアルデータがパラレル変換されて、4組のパラレルデータRA0～RA6, RB0～RB6, RC0～RC6, RD0～RD6となる。図14(b)に示すシリアルデータ列から明らか通り、パラレルデータRA0～RA6は、具体的には、R0～R5と、G0の7ビットであり、他のパラレルデータも、図14(b)に示すシリアルデータに対応したものである。

20

#### 【0178】

そして、表示装置DSは、これらから抽出されるRGB階調データに基づいて画面表示を実現する。このように本実施例では、画素データが、RGB各8ビット(256階調)であってフルカラーの画像演出を実現することができる。

#### 【0179】

しかも、VDP62と表示装置DSとの信号伝送にLVDS信号を使用するので、電圧振幅が低レベルで足り(数100mV)、その分だけデジタル信号の立上り時間や立下り時間が短いので、高速通信を実現することができ、高速度に推移する画像演出を滑らかに実現することができる。しかも、コモンモードノイズの影響を受けないので、不自然な画素が生じることもない。

30

#### 【0180】

また、ケーブル本数が少ないので、省スペース化や低コスト化が実現され、低レベルの電圧によって信号伝送ができるので省電力化を図ることができる。そのため、これらの利点を活用して、より多くの可動演出体を配置して遊技演出を豊富化することができる。

#### 【0181】

なお、ツイストペア線(RXIN3+, RXIN3-)では、NA B7 B6 G7 G6 R7 R6をシリアル転送する構成を探っているので、ツイストペア線(RXIN3+, RXIN3-)を使用しないか、或いは、ツイストペア線(RXIN3+, RXIN3-)でNULLデータをシリアル転送することで、RGB各々6ビットの64階調に抑制することも容易である。

40

#### 【0182】

ところで、図7に示す通り、表示装置DSには、上記したLVDS信号とは別に、画像インターフェイス基板28から、2種類の直流電圧(12V, 3.3V)とPWM制御信号VBRとが伝送されている。

#### 【0183】

ここで、直流電圧3.3Vは、LVDS受信部81を含む表示装置DSの電子回路の電

50

源電圧であり、低い電源電圧によって低電力化を図っている。一方、直流電圧 12V は、LED ランプで構成された液晶バックライト部 BL の電源電圧である。本実施例では、複数個が直列接続された LED ランプによってバックライト部 BL を構成し、冷陰極管を使用しないので、回路構成の簡素化と低電力化と高性能化を実現することができる。

#### 【 0184 】

逆に、冷陰極管を使用するには、直流 32V 程度の高電圧を、周波数 30kHz ~ 45kHz 程度で 1000V 程度の交流電圧に変換するインバータ回路が必要であり、設置スペースが大きく、消費電力が高い上に（数W程度）、ノイズ源となっていたが、本実施例では、これらの問題が全て解消される。

#### 【 0185 】

すなわち、本実施例のバックライト部 BL は、12V の直流駆動であるのでノイズ源とならず、また、インバータ回路も不要であり、消費電力も半分以下に低減される。

#### 【 0186 】

また、本実施例の表示装置 DS には、12V の直流電圧を受けて複数の LED ランプに 40 ~ 65mA 程度の駆動電流を供給する駆動回路が内蔵されている。この駆動回路は、 PWM 制御信号 VBR によって、 LED ランプの調光を制御可能に構成されており、例えば、遊技客が着席していない遊技機については、バックライトを消灯させることもでき、この意味でも省電力化が実現される。

#### 【 0187 】

なお、実施例の PWM 制御信号 VBR は、3.3V レベルの電圧振幅を有し、デューティ比を 0 ~ 100% の範囲で任意に設定できるよう構成されている。そして、通電状態の LED に、規定電流（40 ~ 65mA）を流した状態で、デューティ比を適宜に変化させることで、バックライトの輝度を所望レベルに変更することができる。

#### 【 0188 】

以上、画像制御部 23' のハードウェア構成を中心に説明したので、続いて、画像制御部 23' で実行される画像制御動作について具体的に説明する。

#### 【 0189 】

実施例の遊技機では、演出コマンド CMD ”を受信した画像制御部 23' によって実行される一連の画像演出は、画像演出用の演出コマンド CMD1 ” ~ CMDn ” に対応して設けられた演出進行テーブル Pr\_TBL1 ~ Pr\_TBLn によって管理されている。

#### 【 0190 】

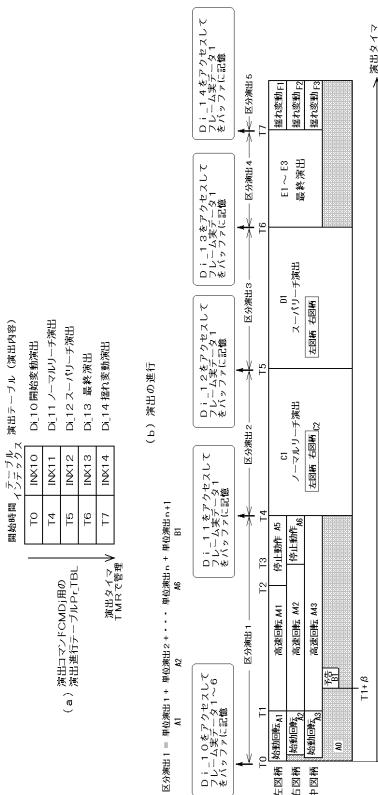

ここで、演出進行テーブル Pr\_TBL は、一連の画像演出を、時間軸上で適宜に区分した区分演出 ENi (EN1 ~ ENn) について、各々の開始時間 Ti を規定している。演出進行テーブル Pr\_TBL は、例えば、図 15 (a) に示す通りであり、各区分演出 ENi について、一連の演出動作の開始時からの開始タイミング Ti と、具体的な演出内容を規定する演出テーブル Di\_xy を特定するインデックス情報 INXxy と、を記憶して構成されている。なお、一連の演出動作の開始時からの経過時間は、演出タイム TM R で計測される。

#### 【 0191 】

図 15 (b) 及び図 15 (c) は、特定の演出コマンド CMD ”を受信すると実行される画像演出を例示したものであり、図 15 (a) に示す演出進行テーブル Pr\_TBL に基づいて実現される。

#### 【 0192 】

図 15 (b) に示す一連の画像演出は、3つの図柄の変動開始から、左右の図柄がリーチ状態で停止するまでの区分演出 EN1 (T0 ~ T4 の開始変動演出) と、これに続く区分演出 EN2 (T4 ~ T5 のノーマルリーチ演出) と、昇格状態で継続される区分演出 EN3 (T5 ~ T6 のスーパーリーチ演出) と、当選状態を示す区分演出 EN4 (T6 ~ T7 の最終演出) と、3つの図柄が浮遊する区分演出 EN5 (T7 以降の揺れ変動演出) と、に区分されている。なお、実施例では、区分演出 1 ~ 5 の演出時間が、互いに重複しないよう構成されているが、特に、限定されるものではない。

10

20

30

40

50

**【0193】**

図15(c)に示す通り、所定の演出コマンドCMD”を受けた画像制御部23では、タイミングT0から、例えば、左図柄「7」 中図柄「8」 右図柄「4」の順番で、各図柄の回転を開始させ、その後、タイミングT1から3つの図柄を高速回転させた後、タイミングT1+で予告演出を実行する。そして、タイミングT2で左図柄「2」で停止させ、その後、タイミングT3で右図柄「2」を停止させている。

**【0194】**

その後、一連の画像演出として、タイミングT4からノーマルリーチ演出を開始し、タイミングT5から、期待感の高まるスーパーリーチ演出に昇格させている。そして、タイミングT6から当選状態を示す最終演出を開始し、その後、タイミングT7から当選状態の停止図柄「3」「3」「3」で流れ変動演出を実行している。なお、流れ変動演出は、停止コマンドCMD”を受けることで終了する。10

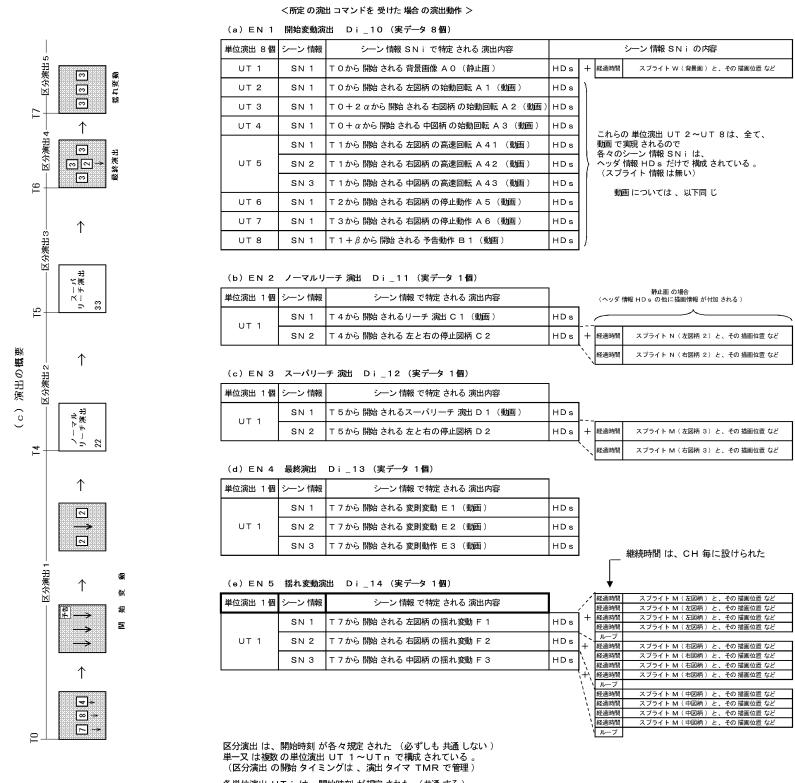

**【0195】**

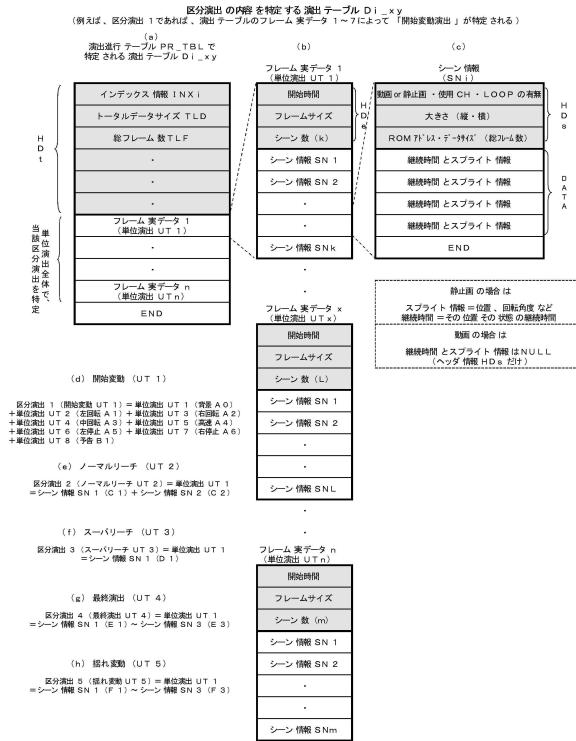

図16(a)は、上記した区分演出ENiを実現するための演出テーブルDi\_x\_yのデータ構造を例示したものである。図示の通り、演出テーブルDi\_x\_yは、自らが規定する区分演出ENiを総合的に特定するテーブルヘッダ情報HDtと、区分演出ENiを実現する単数又は複数の単位演出(UT1~UTn)について、個々の単位演出UTi毎に、その演出内容を特定するフレーム実データ1~nとで構成されている。すなわち、この実施例では、区分演出ENiを特定する演出テーブルDi\_x\_yは、Di\_x\_y = HDt + n個のフレーム実データの関係となっている。20

**【0196】**

図16(a)に示す通り、テーブルヘッダ情報HDtには、その演出テーブルDi\_TBLのインデックス情報INXiの他に、その区分演出ENiを実現する総フレーム数TLFや、トータルデータサイズTLDなどが含まれている。ここで、フレーム数TLFとは、表示装置に時間順次に描画される表示画面の個数であり、1/60秒毎に画像を表示する本実施例では、例えば、5分間の区分演出ENを実現する総フレーム数は、 $5 \times 60 \times 60$ 個となる。したがって、総フレーム数TLFは、当該区分演出ENの演出継続時間を意味することになる。

**【0197】**

フレーム実データ1~nは、当該区分演出ENxを実現する単位演出UTi毎に、その演出内容を特定するデータであり、図16(b)に示す通り、演出ヘッダ情報HDeと、任意個数のシーン情報SNkとで構成されている。すなわち、この実施例では、単位演出UTiを特定するフレーム実データは、HDe + SN1 + SN2 + ... + SNkの関係となっている。30

**【0198】**

ここで、演出ヘッダ情報HDeには、その単位演出UTiの開始時間と、単位演出UTiのために使用されるフレームサイズと、単位演出UTiを実現するシーン数(k, l, m)とが含まれており、シーン情報の個数(k, l, m)は、演出ヘッダ情報HDeで特定される(図16(b)参照)。

**【0199】**

図16(c)に示す通り、各シーン情報SN1~SNkは、各々、シーンヘッダ情報HDsと、継続時間及びスライド情報の組合せで構成されるシーンデータDATAと、で構成されている。なお、シーンデータDATAは、可変長データであり、ENDデータによってデータ範囲が特定される。

**【0200】**

そして、シーンヘッダ情報HDsには、(1)シーン情報SNkを構成する画像の統括情報と、(2)画像の縦横サイズを示すサイズ情報と、(3)画像のCROM63の記憶位置を示すメモリ位置情報やデータサイズなどが含まれている(図16(c)参照)。

**【0201】**

そして、画像の統括情報には、当該シーン情報SNkを構成する画像が、一纏まりの動40

50

画か、単数又は複数の静止画（スライド）かの情報や、描画する描画チャンネルC H iや、当該シーン情報を実行した後、演出動作を終えるか、最初から再実行するかのL O O P情報などを特定している。

#### 【0202】

単位演出U T iが動画で実現される場合、シーンヘッダ情報H D sのデータサイズには、その動画を実現するフレーム数が含まれている。すなわち、動画は、一連複数枚の静止画が連続することで実現されるところ、動画に関するシーンヘッダ情報H D sには、当該動画を実現する静止画の連続枚数（フレーム数）が含まれている。

#### 【0203】

描画チャンネルC H iは、重複して描画された複数の画像の優先順位を規定するものである。この実施例では、最小チャンネル番号C H 0の画像に関するコマンドリストを最初に書き、これに続いて、次チャンネルC H 1の画像に関するコマンドリストを書き、その後も同様に、最大チャンネル番号C H mに向けてコマンドリストを書くよう構成されている。そして、V D Pは、コマンドリストの順番に、フレームバッファF L Bに画像データを重複して記載するので、重ね書きされた画像において、最後に書かれた最大チャンネルC H mの画像が最優先されることになる。10

#### 【0204】

図16(d)と図17(a)には、区分演出E N 1(T 0～T 4の開始変動演出)の構成を整理して図示している。図17(a)に示す通り、区分演出E N 1は、8個の単位演出U T 1～U T 8で構成されており、具体的には、区分演出E N 1 = 単位演出U T 1(フレーム実データ1) + 単位演出U T 2(フレーム実データ2) + … + 単位演出U T 8(フレーム実データ8)の関係が成立している。20

#### 【0205】

ここで、単位演出U T 1～U T 4、及び、単位演出U T 6～8は、各々、单一のシーン情報S N 1～S N 1で構成されており、単位演出U T 1のシーン情報S N 1は、背景画像を意味している。一方、他の6個のシーン情報S N 1～S N 1は、全て動画による演出動作を特定して、各々、始動回転A 1、始動回転A 2、始動回転A 3、停止動作A 5、停止動作A 6、予告演出B 1を特定している。

#### 【0206】

これに対して、単位演出U T 5は、3つのシーン情報S N 1～S N 3で構成されており、各シーン情報S N 1～S N 3は、動画による演出動作を特定して、各々、左図柄と中図柄と右図柄の高速回転(A 4 1, A 4 2, A 4 3)を特定している。30

#### 【0207】

区分演出E N 2～区分演出E N 5についても同様であり、各々、図16(e)～図16(h)及び、図17(b)～図17(e)に示す通りである。

#### 【0208】

例えば、区分演出E N 2(ノーマルリーチ演出)や、区分演出E N 3(スーパーリーチ演出)は、各々、1個の単位演出(U T 1)で構成されている。そして、区分演出E N 2(ノーマルリーチ演出) = 単位演出U T 1であって、リーチ演出C 1を特定するシーン情報S N 1と、リーチ図柄(図柄2)を特定するシーン情報S N 2とで構成されている(U T 1 = S N 1 + S N 2)。同様に、区分演出E N 3(スーパーリーチ演出) = 単位演出U T 1であって、スーパーリーチ演出D 1を特定するシーン情報S N 1と、昇格したリーチ図柄(図柄3)を特定するシーン情報S N 2とで構成されている(U T 1 = S N 1 + S N 2)。40

#### 【0209】

区分演出E N 5(最終演出)や、区分演出E N 6(揺れ変動演出)も、各々、1個の単位演出U T 1で構成されるものの、区分演出E N 5(最終演出)の単位演出U T 1は、3つのシーン情報S N 1～S N 3で構成されている、そして、シーン情報S N 1～S N 3は、各々、動画による変則変動演出(E 1～E 3)を特定している。

#### 【0210】

一方、区分演出E N 5(最終演出)のシーン情報S N 1～S N 3は、各々、静止画によ50

るゆれ変動( F 1 ~ F 3 )を特定している。

#### 【 0 2 1 1 】

以上の構成から明らかなように、本実施例では、各区分演出 E N i は、開始時刻が各々規定された(つまり、必ずしも共通しない)、単一又は複数の単位演出 U T 1 ~ U T n で構成されている。そして、区分演出の開始タイミングは、演出タイマ T M R で管理される。

#### 【 0 2 1 2 】

一方、各単位演出 U T i は、開始時刻が規定された(つまり、開始時刻が共通する)、单一又は複数のシーン情報 S N 1 ~ S N k で構成されている。そして、シーン情報の開始タイミングも、演出タイマ T M R で管理されている。なお、シーン情報を構成する個々のスプライトの表示継続時間は、描画チャンネル C H 0 ~ C H m 毎に設けられた、継続タイム T M 0 ~ T M m で管理される。

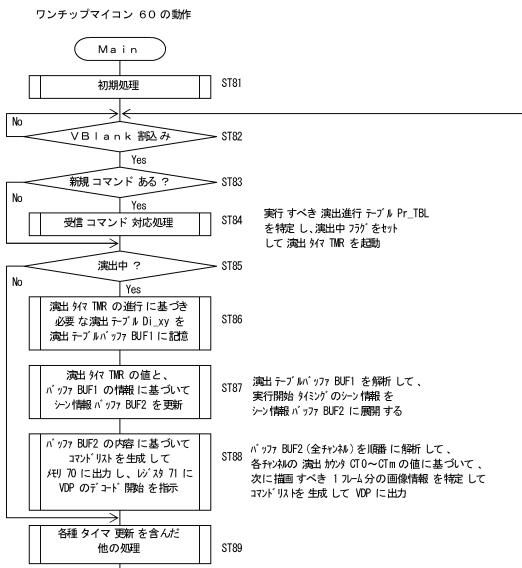

#### 【 0 2 1 3 】

図 18 は、画像制御部 23 のワンチップマイコン(ホスト C P U ) 60 のメイン処理の動作内容を示すフローチャートである。ホスト C P U 60 がリセットされると、ワンチップマイコンの各部や、V D P の各種レジスタ 71 を含んで、適宜な初期設定処理( S T 8 1 )が実行された後、一連のメイン処理( S T 8 2 ~ 8 9 )が無限ループ状に繰り返される。

#### 【 0 2 1 4 】

メイン処理では、先ず、V D P から V B 1 a n k 割込みが生じるのを待つ( S T 8 2 )。ここで、V b 1 a n k 割込みは、V D P 62 が表示装置 D S に 1 フレーム分の描画を終えたタイミングで発生し、例えば、1 / 60 秒毎に発生する。

#### 【 0 2 1 5 】

先に説明した通り、実施例の V D P 62 は、ダブルバッファ方式を探っており、表示バンクと描画バンクに、各々、表示装置 D S の 1 フレーム分の画像データを記憶するよう構成されている。そして、2つのフレームバッファ F L B の機能を交互に切り替えており、表示バンクの画像データを表示装置 D S に出力する一方、描画バンクに次回の画像データを描画している。

#### 【 0 2 1 6 】

そこで、V b 1 a n k 割込みがあれば( S T 8 2 )、新規の受信コマンドがあるか否かを判定し( S T 8 3 )、新規に制御コマンドを受信している場合には、これに対応する処理を実行する( S T 8 4 )。例えば、演出コマンド C M D ”を受けている場合には、その演出コマンドに対応する演出進行テーブル P r \_ T B L を特定する。

#### 【 0 2 1 7 】

また、ステップ S T 8 4 の処理では、画像演出動作を開始するべく、演出中フラグ F L G をセットし、画像演出の進行を管理する演出タイマ T M R を起動させる。なお、演出タイマ T M R は、ステップ S T 8 9 の処理でインクリメントされて、計時動作を実行する。

#### 【 0 2 1 8 】

なお、図 15 ( a )に関して説明した通り、演出進行テーブル P r \_ T B L には、一連の画像演出動作を実現する単数又は複数の演出テーブル D i \_ x y と、各演出テーブル D i \_ x y で規定される画像演出の演出開始タイミングとが、特定されるよう構成されており、演出テーブル D i \_ x y は、テーブルインデックスデータ I N X i で示される。

#### 【 0 2 1 9 】

次に、演出中フラグ F L G の値を判定し( S T 8 5 )、これがセット状態であれば、演出タイマ T M R の値と、演出進行テーブル P r \_ T B L に規定されている演出開始タイミングとを対比し、演出開始タイミングに達している場合には、テーブルインデックス I N X i で特定される演出テーブル D i \_ x y を、演出テーブルバッファ B U F 1 に格納する( S T 8 6 )。

#### 【 0 2 2 0 】

なお、この実施例では、演出テーブルバッファ B U F 1 に、新規の演出テーブル D i \_

10

20

30

40

50

$x\ y$  が格納されたことで、それまで格納されていた古い演出テーブル  $D_i\_x\ y$ ’は事実上消滅する。すなわち、新規の演出テーブル  $D_i\_x\ y$  の最終位置には、ENDデータが存在するので、それ以降のデータは消滅したのと同じである。但し、必ずしも、このような構成に限定されるものではなく、演出テーブルバッファ  $BUF_1$  の先頭アドレスから格納すべき演出テーブルと、演出テーブルバッファ  $BUF_1$  の空き領域に、追加して格納すべき演出テーブルと、を区別するよう構成すれば、例えば、予告動作 (B1) 用の単位演出  $UT_8$  を、開始変動演出用の演出テーブル  $D_i\_10$  から分離することができる。

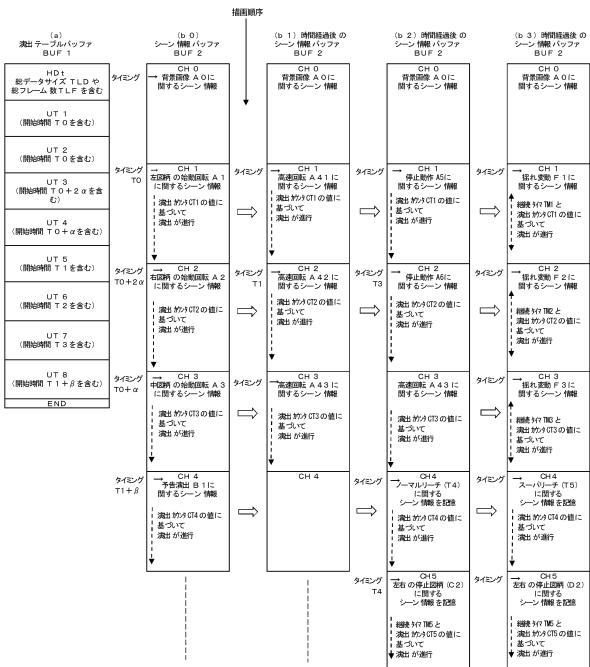

#### 【0221】

以上の点はさておき、図19(a)は、この実施例について、演出タイム  $TMR = T_0$  のタイミングで取得される演出テーブル  $D_i\_10$  を示している。先に説明した通り、演出テーブル  $D_i\_10$  は、区分演出  $EN_1$  である開始変動動作を特定しており、開始変動動作  $EN_1$  は、8個の単位演出  $UT_1 \sim UT_8$  によって構成されている(図16(a)参照)。そのため、演出テーブルバッファ  $BUF_1$  には、演出テーブル  $D_i\_10$  の記憶内容(図16(a)参照)に基づき、各単位演出  $UT_1 \sim UT_8$  の演出開始タイミングを含んだ情報が、各々、格納されることになる(図17(a)参照)。

#### 【0222】

以上のようなステップ  $ST_86$  の処理が終われば、次に、演出テーブルバッファ  $BUF_1$  のデータを参照し、演出タイム  $TMR$  の値に基づいて、演出開始タイミングに達している単位演出  $UT_x$  の有無を判定し、該当する単位演出  $UT_x$  が存在する場合には、その実フレームデータを、シーン情報バッファ  $BUF_2$  に展開する(ST87)。

#### 【0223】

シーン情報バッファ  $BUF_2$  は、 $VDP62$  に出力すべきコマンドリストを生成するために参照される記憶領域であり、最小チャンネル  $CH_0$  から最大チャンネル  $CH_m$  まで、描画チャンネル毎に区分されている(図19(b))。

#### 【0224】

先に説明した通り、本実施例では、演出ヘッダ情報  $HDe$  として、当該単位演出  $UT_x$  の開始タイミングが規定され、シーンヘッダ情報  $HDs$  として、当該単位演出を実現する動画や静止画の描画チャンネル  $CH$  が特定されている。したがって、ステップ  $ST_87$  の処理では、開始タイミングに達している単位演出  $UT_x$  について、その単位演出  $UT_x$  を実現する単数又は複数のシーン情報  $SN_1 \sim SN_i$  を、各々に規定されている描画チャンネル  $CH$  に対応するシーン情報バッファ  $BUF_2$  に格納することになる。

#### 【0225】

図19(b)に示す通り、タイミング  $T_0$  では、描画チャンネル  $CH_0$  に「背景画像  $A_0$  に関するシーン情報」が格納され、描画チャンネル  $CH_1$  に「左図柄の始動回転  $A_1$  に関するシーン情報」が格納される。その後、タイミング  $T_0 + \Delta$  で、描画チャンネル  $CH_3$  に「中図柄の始動回転  $A_3$  に関するシーン情報」が格納され、タイミング  $T_0 + 2\Delta$  で、描画チャンネル  $CH_2$  に「右図柄の始動回転  $A_3$  に関するシーン情報」が格納される。

#### 【0226】

なお、このときの左図柄、中図柄、右図柄は、前回の変動動作の終了時の停止図柄であり、ホスト  $CPU60$  は、各図柄を記憶しているので、停止図柄を特定した始動回転についての動画を特定することができる。そして、その後、タイミング  $T_1 + \Delta$  では、描画チャンネル  $CH_4$  に「予告演出  $B_1$  に関するシーン情報」が格納される。

#### 【0227】

本実施例では、描画チャンネル  $CH_0 \sim CH_m$  は、コマンドリストを生成する順番を示しており、 $VDP62$  は、コマンドリストの順番に描画動作を実行するので、実施例の開始変動では、背景画像 左図柄 右図柄 中図柄 予告画像の順番で優先度が上がることになる。

#### 【0228】

その後の動作も同じであり、タイミング  $T_1$  で、描画チャンネル  $CH_1 \sim CH_3$  に「高速回転  $A_4 \sim A_4$  に関するシーン情報」が格納され、タイミング  $T_2$  とタイミング  $T$

10

20

30

40

50

3で、描画チャンネルCH1とCH3に「停止動作A5と停止動作A6に関するシーン情報」が格納される。以下同様に、描画チャンネルCH1～CH4の内容が更新されるが、最後に、タイミングT7で、描画チャンネルCH1～CH3に「揺れ変動F1～F3に関するシーン情報」が格納される。

#### 【0229】

なお、この実施例では、多くの演出が動画で実現されているが、一つの動画を構成する複数フレームの静止画について、どの静止画を描画するかは、演出カウンタCTで管理され、このような演出カウンタCTiが描画チャンネルCHi毎に設けられている。

#### 【0230】

一方、描画チャンネルCH5の「停止図柄C2～D2の描画」や、描画チャンネルCH1～CH3の「揺れ変動F1～F3の演出」は、静止画で実現されているが、静止画（スプライト）による演出動作は、描画チャンネルCH0～CHm毎に設けられた継続タイムTM0～TMmと、演出カウンタCT0～CTmとによって管理されている。すなわち、図17に示す通り、シーンデータDATAは、継続時間とスプライト情報とで構成されており、継続タイムTMiで計測された所定のスプライト情報についての継続時間が終わると、演出カウンタCTiを更新して、次のスプライト情報による演出に移動し、その後、最後のスプライト情報の継続時間が終われば、演出を終えるか、最初の演出動作に戻る（LOOP）。

#### 【0231】

なお、演出を終えたシーン情報SNiは、継続タイムTMjや演出カウンタCTjの値に基づいて削除されるが、必ずしも必須ではなく、シーン情報バッファBUF2に新たなシーン情報SNjが格納されれば、古いシーン情報SNiは自動的に消去されることになる。

#### 【0232】

以上のような内容のステップST87の処理が終われば、次に、そのときのシーン情報バッファBUF2の内容に基づいて、コマンドリストが生成される（ST88）。

#### 【0233】

図13に関して説明したとおり、コマンドリストは、静止画について、どのスプライトの圧縮データをデコードして（S2）、その伸張データをどの座標位置に描画するか（S2）、或いは、どの動画の、どのフレーム番号の伸張データを、どの座標位置に描画するか（S14）の指示である。

#### 【0234】

そして、シーン情報バッファBUF2には、コマンドリストを生成するための情報が全て格納されているので、ホストCPU60は、シーン情報バッファBUF2を、最低位の描画チャンネルCH0から最高位の描画チャンネルCHmに向けて参照し、静止画の場合には、そのときの演出カウンタCTiと継続タイムTMiの値に基づいて、必要なコマンドリストを生成する。一方、動画の場合には、そのときの演出カウンタCTiの値が、動画のフレーム番号を意味するので、そのときの演出カウンタCTiの値に基づいて、必要なコマンドリストを生成する。

#### 【0235】

このようにして生成されたコマンドリストは、VDP62のコマンドメモリ70に書き込まれる。前記の通り、コマンドメモリ70の先頭には、描画チャンネルCH0のコマンドリストが登録され、以下、描画チャンネルCH1　描画チャンネルCH2　…の順番で、各々のコマンドリストが登録されるので、描画チャンネルCH0のコマンドリストの優先後が最低レベルとなる。

#### 【0236】

その後、ホストCPU60は、コマンドリストの開始アドレスやその他の制御情報をシステム制御レジスタ71に設定することでVDP62の描画動作を開始させる（ST88）。

#### 【0237】

10

20

30

40

50

以上の処理によって VDP62 は、デコード処理を開始するので、ホストCPU60 としては、演出タイマ TMR や継続タイマ TMなどを更新し、その他の必要な処理を実行した上で、VBlank 割込みを待つことになる (ST89)。

### 【0238】

以上の通り、本実施例では、ホストCPU60 と VDP62 とが協働して画像演出動作を実現しているので、複雑高度な画像演出を円滑に実行することができる。また、特殊なメモリ構成を有するので、高画質の画像を円滑に変化させることができ、万一、メモリに不備が生じても、そのメモリを特定することができ、メモリ素子単位で交換することも可能となる。

### 【符号の説明】

10

### 【0239】

- G M 遊技機

- 2 3' 画像制御部

- D S 表示装置

- 6 3 不揮発性メモリ

- M B V ムービーバッファ

- F L B フレームバッファ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 9 】

【図8】

【 図 1 0 】

(a) メモリ構成

(b) チェックサム演算

【 図 1 1 】

【図12】

【 四 1 3 】

【図14】

(b) RGB信号のLVDS(低電圧差動信号)伝送

【図15】

【図17】

【図18】

【図19】

## 【図16】

---

フロントページの続き

(56)参考文献 特開2012-040056(JP,A)

特開2012-147372(JP,A)

特開2011-104185(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 6 3 F        5 / 0 4 , 7 / 0 2