(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-124968

(P2018-124968A)

(43) 公開日 平成30年8月9日(2018.8.9)

(51) Int.Cl.

G06T 5/00 (2006.01)

H04N 5/232 (2006.01)

F 1

G06T 5/00

H04N 5/232

725

テーマコード(参考)

5B057

5C122

審査請求 未請求 請求項の数 11 O L (全 17 頁)

(21) 出願番号 特願2017-167619 (P2017-167619)

(22) 出願日 平成29年8月31日 (2017.8.31)

(31) 優先権主張番号 特願2017-12870 (P2017-12870)

(32) 優先日 平成29年1月27日 (2017.1.27)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71) 出願人 317011920

東芝デバイス&ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74) 代理人 100076233

弁理士 伊藤 進

(74) 代理人 100101661

弁理士 長谷川 靖

(74) 代理人 100135932

弁理士 篠浦 治

(72) 発明者 羽田 隆二

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】画像処理装置、及び、画像処理方法

## (57) 【要約】

【課題】ラインバッファの搭載量を低減することができる、画像処理装置、及び画像処理方法を提供する。

【解決手段】入力画像を構成する複数の入力画素がラスタスキャン順に入力される画像処理装置であって、入力画素の位置を出力画像における第1の画素位置に変換する、書き込み画素位置計算部12と、出力画像における第1の画素位置の近傍の出力画素の位置を、入力画像における第2の画素位置に変換する、読み出し画素位置計算部13と、第2の画素位置の画素値を、入力画像における周囲の画素からの補間により算出する画素補間部16とを備えている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

入力画像を構成する複数の入力画素がラスタスキヤン順に入力される画像処理装置であって、

前記入力画像における前記入力画素の位置を、第1の画素位置計算により、出力画像における第1の画素位置に変換する、第1の計算部と、

前記出力画像における第1の画素位置の近傍の出力画素の位置を、第2の画素位置計算により、前記入力画像における第2の画素位置に変換する、第2の計算部と、

前記第2の画素位置の画素値を、前記入力画像における周囲の画素からの補間により算出する画素補間部と、

を備える画像処理装置。

10

**【請求項 2】**

前記入力画素を格納するラインバッファを更に備えることを特徴とする、請求項1に記載の画像処理装置。

**【請求項 3】**

前記第1の画素位置計算は、多項式を用いた関数、または、グリッドテーブル変換、または、前記多項式を用いた関数と前記グリッドテーブル変換の組み合わせであること、

前記第2の画素位置計算は、前記第1の画素位置計算の逆関数を用いて行うこと、を特徴とする、請求項1又は請求項2に記載の画像処理装置。

20

**【請求項 4】**

前記入力画素は、複数の色画素を有し、

ひとつの前記色画素を用いて算出された、前記第1の画素位置、または、前記第2の画素位置を、他の前記色画素の前記第2の画素位置に変換する、第3の計算部を更に備えることを特徴とする、請求項1乃至請求項3のいずれか一項に記載の画像処理装置。

**【請求項 5】**

入力画像を構成する入力画素をラスタスキヤン順に入力し、

前記入力画素の位置を、画素位置計算により出力画像における第1の画素位置に変換し、

前記出力画像における前記第1の画素位置近傍の出力画素の位置を、前記画素位置計算の逆関数を用いて、前記第2の画素位置に変換し、

30

前記第2の画素位置の画素値を、前記入力画像における周囲の画素からの補間により算出し、

前記補間により画素値を算出した順に、前記第2の画素位置の画素値を出力することを特徴とする、画像処理方法。

**【請求項 6】**

前記入力画像は、複数の色画素から構成されており、ひとつの前記色画素を用いて算出した、前記第1の画素位置、または、前記第2の画素位置を、他の前記色画素の前記第2の画素位置に変換することを特徴とする、請求項5に記載の画像処理方法。

**【請求項 7】**

前記出力画像における第1の画素位置を、所定のスケール値を用いて前記出力画像のピラミッド画像における第3の画素位置に変換する、第4の計算部と、

前記ピラミッド画像における第3の画素位置の近傍の出力画素の位置を、前記所定のスケール値と前記第2の画素位置計算により、前記入力画像における第4の画素位置に変換する、第5の計算部と、を更に備え、

前記画素補間部は、前記第2の画素位置の画素値と、前記第4の画素位置の画素値とを、前記入力画像における周囲の画素からの補間により算出することを特徴とする、請求項1乃至請求項3のいずれか一項に記載の画像処理装置。

40

**【請求項 8】**

前記第4の計算部は、複数の異なる前記スケール値に対応した前記第3の画素位置を算出し、前記第5の計算部は、複数の異なる前記スケール値に対応した前記第4の画素位置

50

を算出することを特徴とする、請求項 7 に記載の画像処理装置。

【請求項 9】

前記入力画素は、複数の色画素を有し、

ひとつの前記色画素を用いて算出された、前記第 1 の画素位置、または、前記第 2 の画素位置を、他の前記色画素の前記第 2 の画素位置に変換し、ひとつの前記色画素を用いて算出された、前記第 3 の画素位置、または、前記第 4 の画素位置を、他の前記色画素の前記第 4 の画素位置に変換する、第 6 の計算部を更に備えることを特徴とする、請求項 7 又は請求項 8 に記載の画像処理装置。

【請求項 10】

前記入力画素の位置を、画素位置計算により出力画像における第 1 の画素位置に変換した後に、前記第 1 の画素位置を、所定のスケール値を用いて前記出力画像のピラミッド画像における第 3 の画素位置に変換し、

前記ピラミッド画像における前記第 3 の画素位置近傍の出力画素の位置を、前記所定のスケール値と前記画素位置計算の逆関数を用いて、前記第 4 の画素位置に変換し、

前記第 4 の画素位置の画素値を、前記入力画像における周囲の画素からの補間により算出し、

前記補間ににより画素値を算出した順に、前記第 4 の画素位置の画素値を出力することを特徴とする、請求項 5 に記載の画像処理方法。

【請求項 11】

前記入力画像は、複数の色画素から構成されており、ひとつの前記色画素を用いて算出した、前記第 1 の画素位置、または、前記第 2 の画素位置を、他の前記色画素の前記第 2 の画素位置に変換し、ひとつの前記色画素を用いて算出した、前記第 3 の画素位置、または、前記第 4 の画素位置を、他の前記色画素の前記第 4 の画素位置に変換することを特徴とする、請求項 10 に記載の画像処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

本実施形態は、画像処理装置、及び、画像処理方法に関する。

【背景技術】

【0002】

一般的に、デジタルカメラ等の撮像装置で被写体を撮像して得られた画像は、撮像レンズ等の光学系が有する歪曲収差や倍率色収差の影響を受ける。歪曲収差を抑制するためには、レンズの材質を工夫したり、非球面レンズを用いたりするが、設計や製造のコストが増大するという問題がある。また、倍率色収差を抑制するためには、屈折率の異なる素材のレンズの組を多数使用するためにレンズ数が多くなり、装置の大型化や製造コストが増大してしまうという問題がある。

【0003】

そこで、近年では、これらの問題を解決するものとして、歪曲収差や倍率色収差によって画像に歪みなどが生じる場合、画像に対して電気的に、光学系で生じる歪みを補正する画像処理装置が用いられている。

【0004】

従来の画像処理装置における電気的補正方法では、補正後の出力画素をラスタスキャン順に出力するため、出力画素位置から補正に必要な入力画素位置を計算していた。ところが、画像の歪みが大きい場合、出力画素位置と入力画素位置に大きなずれが生じる。従って、多数のラインバッファを用意して入力画素を保持しておく必要があるため、装置が大型化してしまう。また、一般的に、ラインバッファは S R A M で構成されるが、S R A M は高価であるため、製造コストが高くなってしまうという問題がある。

【先行技術文献】

【特許文献】

【0005】

10

20

30

40

50

【特許文献 1】特開 2005 - 229200 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本実施形態は、ラインバッファの搭載量を低減することができる、画像処理装置、及び画像処理方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本実施形態の画像処理装置は、入力画像を構成する複数の入力画素がラスタスキャン順に入力される画像処理装置であって、前記入力画像における前記入力画素の位置を、第1の画素位置計算により、出力画像における第1の画素位置に変換する、第1の計算部と、前記出力画像における第1の画素位置の近傍の出力画素の位置を、第2の画素位置計算により、前記入力画像における第2の画素位置に変換する、第2の計算部を備える。また、前記第2の画素位置の画素値を、前記入力画像における周囲の画素からの補間により算出する画素補間部も備える。

【図面の簡単な説明】

【0008】

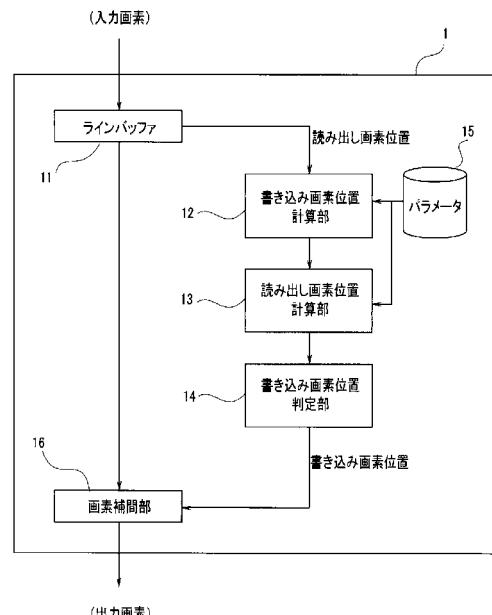

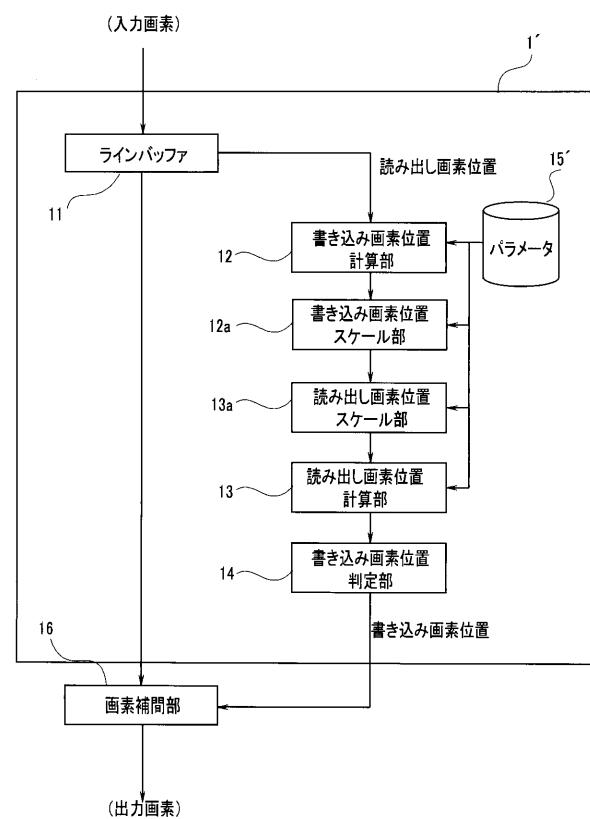

【図1】本発明の第1の実施形態に係わる画像処理装置の構成を説明する概略ブロック図。

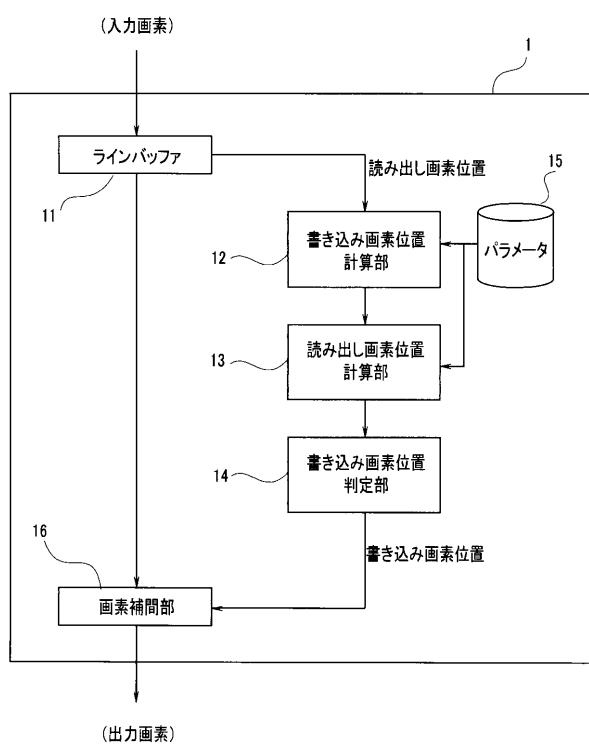

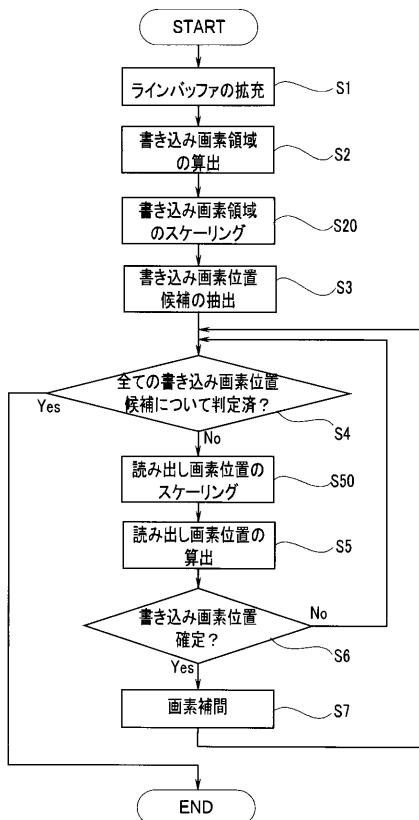

【図2】第1の実施形態における画像補正処理を説明するフローチャート。

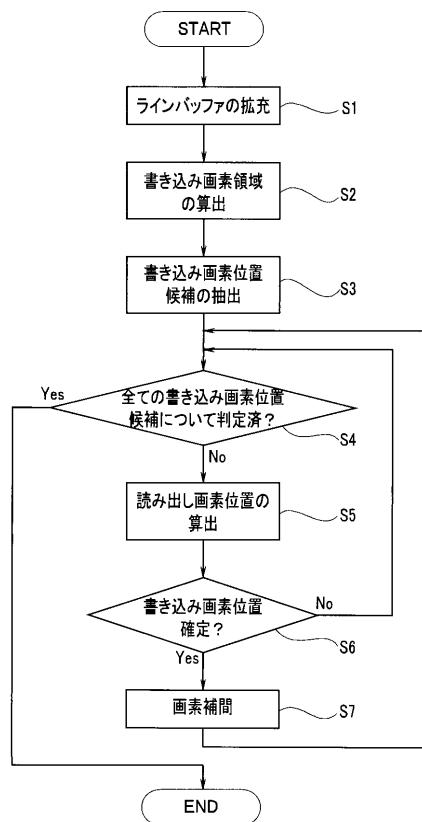

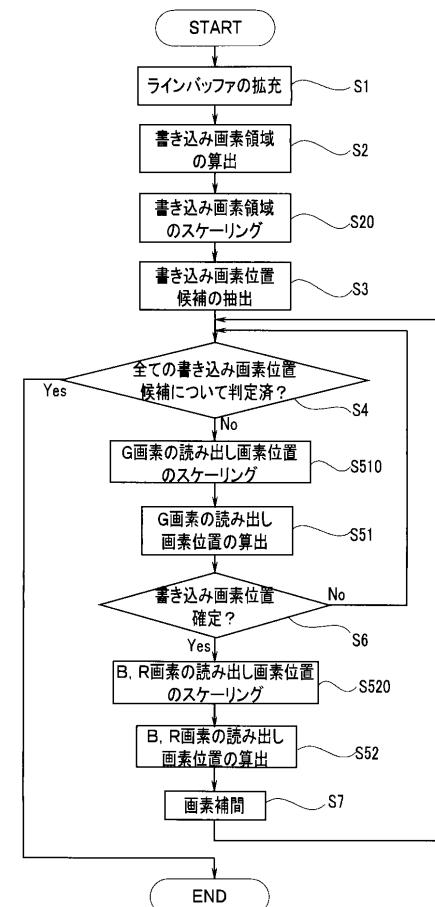

【図3】第2の実施形態における画像補正処理を説明するフローチャート。

【図4】第3の実施形態に係わる画像処理装置の構成を説明する概略ブロック図。

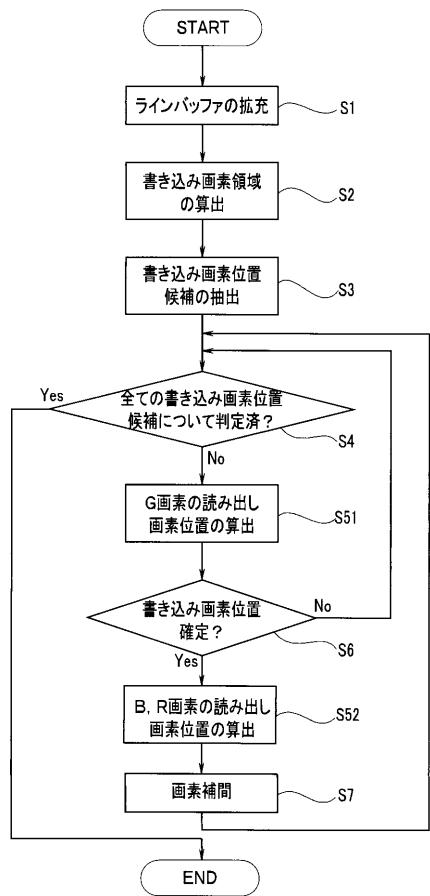

【図5】第3の実施形態における画像補正処理を説明するフローチャート。

【図6】第4の実施形態における画像補正処理を説明するフローチャート。

【発明を実施するための形態】

【0009】

以下、図面を参照して実施形態を説明する。

(第1の実施形態)

図1は、本発明の第1の実施形態に係わる画像処理装置の概略ブロック図である。画像処理装置は、カメラなどの撮像装置(図示せず)で撮像された被写体の画像(以下、入力画像と示す)に対し、電気的な処理を施して、レンズの歪曲収差など光学系で生じる歪みを補正する。

【0010】

画像処理装置1は、ラインバッファ11と、書き込み画素位置計算部12と、読み出し画素位置計算部13と、書き込み画素位置判定部14と、パラメータ格納部15と、画素補間部16とから主に構成されている。

【0011】

ラインバッファ11は、撮像装置からラスタスキャン順に読み込まれる入力画像の画素(入力画素)を、補正処理に必要なライン数だけ保持する。例えば、バイリニア補間を用いて歪曲収差の補正を行う場合、1~2ライン分の画素を保持する。

【0012】

第1の計算部としての書き込み画素位置計算部12は、補正対象である読み出し画素Piを用いて補間した画素が含まれると推定される、書き込み画素領域を算出する。具体的には、読み出し画素Piの位置(vo, ho)(以下、画素Pi(vo, ho)と示す)を含む、周辺4点の画素{Pi0(vo, ho)、Pi1(vo, ho-1)、Pi2(vo-1, ho-1)、Pi3(vo-1, ho)}からなる読み出し画素位置集合を定義する。なお、本説明において、画素位置座標(v, h)は、画像左上を原点(0, 0)として、vを垂直画素位置、hを水平画素位置としている。

【0013】

読み出し画素Pi0、Pi1、Pi2、Pi3のそれぞれについて、画素位置計算の関数を用い、対応する書き込み画素Po0、Po1、Po2、Po3の位置(vo', ho')、(vo', ho-1')、(vo'

10

20

30

40

50

$-1'$ ,  $ho-1'$ )、( $vo-1'$ ,  $ho'$ )を算出する。4点の画素 $Po0$ ( $vo'$ ,  $ho'$ )、 $Po1$ ( $vo'$ ,  $ho-1'$ )、 $Po2$ ( $vo-1'$ ,  $ho-1'$ )、 $Po3$ ( $vo-1'$ ,  $ho'$ )を頂点とする矩形領域が、書き込み画素領域となる。

#### 【0014】

画素位置計算には、例えば、多項式で表現される関数や、グリッドテーブル変換など、一般的な画素位置計算用の関数を用いることができる。ただし、画素位置計算関数は、逆関数が存在するものを用いる。

#### 【0015】

第2の計算部としての読み出し画素位置計算部13は、書き込み画素領域内において、垂直位置、水平位置ともに整数となる画素の位置(書き込み画素候補 $Poc(v', h')$ )を抽出する。そして、書き込み画素候補 $Poc(v', h')$ に対応する読み出し画素 $Pi(v'', h'')$ を、画素位置計算を行って算出する。なお、画素位置計算は、書き込み画素位置計算部12で行った画素位置計算の逆関数を用いて行う。候補が複数ある場合は、全ての候補 $Poc(v', h')$ に対して読み出し画素 $Pi(v'', h'')$ を算出する。10

#### 【0016】

書き込み画素位置判定部14は、読み出し画素 $Pi(v'', h'')$ が集合に含まれている場合、当該画素 $Pi(v'', h'')$ に対する書き込み画素候補 $Poc(v', h')$ を、書き込み画素 $Po(v', h')$ として確定する。

#### 【0017】

パラメータ格納部15は、書き込み画素位置計算部12および読み出し画素位置計算部13における画素位置計算関数に用いるパラメータが格納されている。20

#### 【0018】

画素補間部16は、確定した書き込み画素 $Po(v', h')$ に対応する読み出し画素 $Pi(v'', h'')$ の画素値を算出する。通常、読み出し画素 $Pi(v'', h'')$ の座標は非整数であるので、例えば周辺の4画素を用いたバイリニア補間など、既存の補間手法を用いて画素値を算出する。書き込み画素 $Po(v', h')$ の画素値として、算出した画素値を出力する。出力された画素値は、DRAMなどのメモリ(図示せず)に格納される。なお、出力画素は補正を行った順に出力するため、出力画素の位置はランダムとなる。

#### 【0019】

次に、画像処理装置1における画像補正処理の手順を説明する。図2は、第1の実施形態における画像補正処理を説明するフローチャートである。30

#### 【0020】

まず、ラスタスキャン順に画像処理装置1に入力された画素を、ラインバッファ11に拡充する(S1)。ラインバッファ11には、画素補間部16での処理に必要なライン数分、入力画素を格納する。例えば、バイリニア補間を用いる場合、補間対象画素の周辺 $2 \times 2$ 画素(4画素)の画素値が必要となるため、少なくとも1ライン+1画素分の画素値を格納する。

#### 【0021】

次に、補正対象画素である読み出し画素 $Pi(vo, ho)$ を特定し、読み出し画素 $Pi$ を用いて補間した画素が含まれると推定される、書き込み画素領域を算出する(S2)。具体的には、まず、読み出し画素 $Pi(vo, ho)$ を含む周囲4点の画素 $\{Pi0(vo, ho), Pi1(vo, ho-1), Pi2(vo-1, ho-1), Pi3(vo-1, ho)\}$ からなる集合を定義する。すなわち、 $Pi1(vo, ho-1)$ は、 $Pi(vo, ho)$ の左隣の画素、 $Pi2(vo-1, ho-1)$ は $Pi(vo, ho)$ の左上の画素、 $Pi3(vo-1, ho)$ は $Pi(vo, ho)$ の上の画素である。次に、画素 $Pi0, Pi1, Pi2, Pi3$ のそれについて、画素位置計算を行い、対応する書き込み画素 $Po0(vo', ho')$ 、 $Po1(vo', ho-1')$ 、 $Po2(vo-1', ho-1')$ 、 $Po3(vo-1', ho')$ を算出する。40

#### 【0022】

画素位置計算は、例えば、多項式で表現される関数を用いる場合、次の手順で行う。

#### 【0023】

(a) 像高の算出：入力画素の位置を、左上を原点とする( $v, h$ )の座標系から、光学

中心を原点とする( $x, y$ )の座標系に変換する。なお、両座標系とも、水平方向は右側を正とし、垂直方向は下側を正とする。また、光学中心から入力画素までの距離(像高) $r$ を算出する。以下に示す(1)~(3)式を用いて行う。

$$y = v_{in} + [\text{SENSOR\_CROP\_OFS\_V}] \quad \dots (1) \text{ 式}$$

$$x = h_{in} + [\text{SENSOR\_CROP\_OFS\_H}] \quad \dots (2) \text{ 式}$$

$$r = \sqrt{x^2 + y^2 * [\text{NORM\_SCALE}]} \quad \dots (3) \text{ 式}$$

#### 【0 0 2 4】

(1)式において、 $v_{in}$ は、垂直方向の入力画素位置(非負数)、 $[\text{SENSOR\_CROP\_OFS\_V}]$ は、光学中心からの垂直画素位置オフセット(光学中心と、 $(v, h)$ 座標系の原点との間の、垂直方向のオフセット)とする。また、(2)式において、 $h_{in}$ は、水平方向の入力画素位置(非負数)、 $[\text{SENSOR\_CROP\_OFS\_H}]$ は、光学中心からの水平画素位置オフセット(光学中心と、 $(v, h)$ 座標系の原点との間の、水平方向のオフセット)とする。また、(3)式において、 $[\text{NORM\_SCALE}]$ は正規化係数(非負数)とする。

#### 【0 0 2 5】

なお、画像中心と光学中心とが一致する場合、 $[\text{SENSOR\_CROP\_OFS\_V}]$ 、 $[\text{SENSOR\_CROP\_OFS\_H}]$ は、以下の(4)(5)式となる。

#### 【0 0 2 6】

$$[\text{SENSOR\_CROP\_OFS\_V}] = -(\text{入力画像垂直サイズ}/2 - 0.5) \quad \dots (4) \text{ 式}$$

$$[\text{SENSOR\_CROP\_OFS\_H}] = -(\text{入力画像水平サイズ}/2 - 0.5) \quad \dots (5) \text{ 式}$$

(b)画素位置計算の像高スケールの算出：光学中心から距離 $r$ にある点が、画素位置変換によって光学中心方向に移動する距離 $r_{scale}$ を算出する。以下に示す(6)式を用いて行う。

#### 【0 0 2 7】

$$\begin{aligned} r_{scale} = & P0 + P1 * r + P2 * r^2 + P3 * r^3 + P4 * r^4 + P5 * r^5 + P6 * r^6 + P7 * r^7 + P8 * r^8 \\ & + P9 * r^9 + P10 * r^{10} \end{aligned} \quad \dots (6) \text{ 式}$$

(6)式において、 $Px$ ( $x = 0 \sim 10$ )は、それぞれの次数に応じた多項式係数とする。

#### 【0 0 2 8】

(c)出力画素位置の算出：像高スケールを用いて入力画素位置を出力画素位置に変換し、 $(v, h)$ の座標系に戻す。以下に示す(7)(8)式を用いて行う。

#### 【0 0 2 9】

$$v_{out} = r_{scale} * y - [\text{SENSOR\_CROP\_OFS\_V}] \quad \dots (7) \text{ 式}$$

$$h_{out} = r_{scale} * x - [\text{SENSOR\_CROP\_OFS\_H}] \quad \dots (8) \text{ 式}$$

(7)式において、 $v_{out}$ は垂直方向の出力画素位置(非負数)、(8)式において、 $h_{out}$ は水平方向の出力画素位置(非負数)とする。

#### 【0 0 3 0】

すなわち、(a)から(c)の一連の手順により、読み出し画素 $Pi(v_o, h_o)$ 、 $Pi1(v_o, h_o-1)$ 、 $Pi2(v_o-1, h_o-1)$ 、 $Pi3(v_o-1, h_o)$ が、それぞれ、書き込み画素 $Po0(v_o', h_o')$ 、 $Po1(v_o', h_o-1')$ 、 $Po2(v_o-1', h_o-1')$ 、 $Po3(v_o-1', h_o')$ に変換される。

#### 【0 0 3 1】

なお、画素位置計算として、上述のような多項式で表現される関数を用いる場合、 $[\text{SENSOR\_CROP\_OFS\_V}]$ 、 $[\text{SENSOR\_CROP\_OFS\_H}]$ 、 $[\text{NORM\_SCALE}]$ 、 $Px$ ( $x = 0 \sim 10$ )の各パラメータは予め設定されており、パラメータ格納部15に格納されているものとする。

#### 【0 0 3 2】

画素位置計算は、グリッドテーブル変換を用いて行うこともできる。グリッドテーブルとは、画素位置( $v, h$ )をグリッドノードとした2次元のアドレステーブルである。各グリッドノードには、変換先の画素位置が格納されている。グリッドノードの間に位置する任意の画素位置に対応するアドレスは、近傍グリッドノードから補間することで算出する

10

20

30

40

50

。画素位置計算としてグリッドテーブル変換を用いる場合、次の手順で行う。

#### 【0 0 3 3】

(d) 参照グリッドノードの算出：参照グリッドノードとして、入力画素の左上に位置するグリッドノードを決定する。以下に示す(9)(10)式を用いて行う。

#### 【0 0 3 4】

$$\text{ref\_v} = v_{in} * \text{GRID_PATCH_VSIZE_INV} \quad \dots (9) \text{ 式}$$

$$\text{ref\_h} = h_{in} * \text{GRID_PATCH_HSIZE_INV} \quad \dots (10) \text{ 式}$$

(9)式において、 $v_{in}$ は、垂直方向の入力画素位置（非負数）、 $\text{GRID_PATCH_VSIZE_INV}$ は、垂直グリッドノード間距離の逆数とする。 $\text{GRID_PATCH_VSIZE_INV}$ は、以下の(11)式を用いて算出する。

10

$$\text{GRID_PATCH_VSIZE_INV} = \frac{1}{([\text{SENSOR_CROP_VSIZE}] - 1)/([\text{GRID_NODE_NUM_V}] - 1)} \quad \dots (11) \text{ 式}$$

#### 【0 0 3 5】

(11)式において、 $[\text{SENSOR_CROP_VSIZE}]$ は、入力画像垂直サイズ、 $[\text{GRID_NODE_NUM_V}]$ は、垂直グリッドノード数とする。

#### 【0 0 3 6】

また、(10)式において、 $h_{in}$ は、水平方向の入力画素位置（非負数）、 $\text{GRID_PATCH_HSIZE_INV}$ は、水平グリッドノード間距離の逆数とする。 $\text{GRID_PATCH_HSIZE_INV}$ は、以下の(12)式を用いて算出する。

20

$$\text{GRID_PATCH_HSIZE_INV} = \frac{1}{([\text{SENSOR_CROP_HSIZE}] - 1)/([\text{GRID_NODE_NUM_H}] - 1)} \quad \dots (12) \text{ 式}$$

#### 【0 0 3 7】

(12)式において、 $[\text{SENSOR_CROP_HSIZE}]$ は、入力画像水平サイズ、 $[\text{GRID_NODE_NUM_H}]$ は、水平グリッドノード数とする。

#### 【0 0 3 8】

(e) 重みの算出：入力画素位置から参照グリッドノードを含む周囲4点のグリッドノードに対する、垂直方向及び水平方向の距離の比に基づく重みを算出する。以下に示す(13)(14)式を用いて算出する。

30

#### 【0 0 3 9】

$$\text{weight\_v} = \text{ref\_v} - [\text{ref\_v}] \quad \dots (13) \text{ 式}$$

$$\text{weight\_h} = \text{ref\_h} - [\text{ref\_h}] \quad \dots (14) \text{ 式}$$

(13)(14)式において、[]はガウス記号を表す。参照グリッドノードに関する垂直方向の重みは $1 - \text{weight\_v}$ となる。また、参照グリッドノードに関する水平方向の重みは、 $1 - \text{weight\_h}$ となる。

#### 【0 0 4 0】

(f) 出力画素位置の算出：参照グリッドノードを含む周囲4点のグリッドノードのテーブルと、入力画素位置に対する各グリッドノードの重みを用い、バイリニア補間によって、出力画素位置を算出する。

40

#### 【0 0 4 1】

(f-1) 垂直方向の出力画素位置の算出

以下に示す(15)～(17)式を用いて算出する。

#### 【0 0 4 2】

$$v0_{out} = \text{table\_v}(\text{ref\_v}, \text{ref\_h}) * (1 - \text{weight\_h}) + \text{table\_v}(\text{ref\_v}, \text{ref\_h}+1) * \text{weight\_h} \quad \dots (15) \text{ 式}$$

$$v1_{out} = \text{table\_v}(\text{ref\_v}+1, \text{ref\_h}) * (1 - \text{weight\_h}) + \text{table\_v}(\text{ref\_v}+1, \text{ref\_h}+1) * \text{weight\_h} \quad \dots (16) \text{ 式}$$

50

$$v_{out} = v0_{out} * (1 - weight_v) + v1_{out} * weight_v \quad \dots (17) \text{式}$$

(15) (16)式において、table\_v(v, h)は、垂直画素位置グリッドテーブルとする。また、(17)式において、 $v_{out}$ は、は垂直方向の出力画素位置（非負数）である。

#### 【0043】

(f-2) 水平方向の出力画素位置の算出

以下に示す(18)～(20)式を用いて算出する。

#### 【0044】

$$h0_{out} = table_h(ref_v, ref_h) * (1 - weight_h) + table_h(ref_v, ref_h+1) * weight_h \quad \dots (18) \text{式}$$

$$h1_{out} = table_h(ref_v+1, ref_h) * (1 - weight_h)$$

$$+ table_h(ref_v+1, ref_h+1) * weight_h \quad \dots (19) \text{式}$$

$$h_{out} = h0_{out} * (1 - weight_h) + h1_{out} * weight_v \quad \dots (20) \text{式}$$

(18) (19)式において、table\_h(v, h)は、水平画素位置グリッドテーブルとする。また、(20)式において、 $h_{out}$ は、は水平方向の出力画素位置（非負数）である。

#### 【0045】

すなわち、(d)から(f)の一連の手順により、読み出し画素Pi(vo, ho)、Pi1(vo, ho-1)、Pi2(vo-1, ho-1)、Pi3(vo-1, ho)が、それぞれ、書き込み画素Po0(vo', ho')、Po1(vo', ho-1')、Po2(vo-1', ho-1')、Po3(vo-1', ho')に変換される。

#### 【0046】

なお、画素位置計算として、上述のようなグリッドテーブル変換を用いる場合、[SENSO\_R\_CROP\_VSIZE]、[GRID\_NODE\_NUM\_V]、[SENSOR\_CROP\_HSIZE]、[GRID\_NODE\_NUM\_H]、table\_v(v, h)、table\_h(v, h)の各パラメータは予め設定されており、パラメータ格納部15に格納されているものとする。

#### 【0047】

画素位置計算により算出された、4点の画素Po0(vo', ho')、Po1(vo', ho-1')、Po2(vo-1', ho-1')、Po3(vo-1', ho')を頂点とする矩形領域が、書き込み画素領域として特定される。

#### 【0048】

次に、上記特定された矩形領域内において、垂直座標、及び、水平座標が共に整数となる画素位置（書き込み画素候補Poc(v', h')）を抽出する。例えば、画素Po0(vo', ho')、Po1(vo', ho-1')、Po2(vo-1', ho-1')、Po3(vo-1', ho')の各座標を、繰り上げ・繰り下げにより調整・整数化し、得られた画素位置に外接する矩形領域内のすべての画素位置を、書き込み画素候補Poc(v', h')とする(S3)。繰り上げ・繰り下げによる調整・整数化は、以下に示す(21)(22)式を用いて行う。なお、4点のうち、左側または上側に位置する画素については、(21)式を行い、右側または下側に位置する画素については、(22)式を用いる。

#### 【0049】

$$\text{調整後画素位置} = [\text{書き込み画素位置} - \text{WRITE\_AREA\_DELTA}] \quad \dots (21) \text{式}$$

$$\text{調整後画素位置} = [\text{書き込み画素位置} + \text{WRITE\_AREA\_DELTA}] \quad \dots (22) \text{式}$$

(21)(22)式において、WRITE\_AREA\_DELTAは整数化調整値であり、予め設定された値である。また、[]はガウス記号を表す。

#### 【0050】

続いて、S3で求めたすべての書き込み画素候補Poc(v', h')に対し、書き込み画素Po(v', h')であるか否かの判定を行う。判定をまだ行っていない書き込み画素候補Poc(v', h')がある場合(S4、No)、画素位置計算により、対応する読み出し画素Pi(v", h")を算出する(S5)。画素位置計算は、S2で用いた画素位置計算の逆関数を用いて行う。このとき、Pi(v", h")の垂直座標、水平座標は、非整数となる。

#### 【0051】

10

20

30

40

50

次に、 $P_i(v'', h'')$  の画素値を補間にによって算出するために必要な画素を特定する。例えば、バイリニア補間にによって画素値を算出する場合、 $P_i(v'', h'')$  の周囲 4 点の画素が補間に必要な画素となる。補間に必要なすべての画素が、集合に含まれている場合、当該読み出し画素 $P_i(v'', h'')$  に対応する書き込み画素候補 $Poc(v', h')$  を、書き込み画素 $P_o(v', h')$  と確定する (S 6、Yes)。

#### 【0052】

この場合、確定した書き込み画素 $P_o(v', h')$  の画素値を、対応する読み出し画素 $P_i(v'', h'')$  の画素値を画素補間にによって算出して出力する (S 7)。なお、出力画素 $P_o(v', h')$  は、ラスタスキャン順でなくランダムとなる。続いて S 4 に戻り、未判定の書き込み画素候補 $Poc(v', h')$  の有無を調べる。10

#### 【0053】

一方、補間に必要な画素のうち、集合に含まれていない画素が存在する場合、当該読み出し画素 $P_i(v'', h'')$  に対応する書き込み画素候補 $Poc(v', h')$  は、書き込み画素 $P_o(v', h')$  でないと確定する (S 6、No)。この場合、画素補間は行わずに、S 4 に戻って、未判定の書き込み画素候補 $Poc(v', h')$  の有無を調べる。

#### 【0054】

S 4 において、S 3 で求めたすべての書き込み画素候補 $Poc(v', h')$  について、判定が行われている場合、画像補正処理の一連の手順を終了する。

#### 【0055】

このように、本実施形態によれば、撮像装置からラスタスキャン順に読み込まれる入力画素を、この順に補正処理を行う。従って、補正に必要な入力画素の範囲を 1 乃至数ライン程度で抑えることができるため、入力画素を格納するラインバッファ 11 の搭載量を低減することができ、製造コストを抑制することができる。20

#### 【0056】

なお、ラインバッファ 11 の搭載量は、画素補間の手法に応じて設定される。例えば、バイリニア法を用いる場合、2 ライン程度搭載すればよいが、バイキューピック法を用いる場合、4 ライン程度搭載する必要がある。

#### 【0057】

また、読み出し画素から書き込み画素を算出する画素位置計算の方法は、上述の方法に限定されない。すなわち、逆関数が存在する方法であれば、任意の方法を用いることができる。また、複数の画素位置計算方法を組み合わせて用いてもよい。30

#### (第 2 の実施形態)

第 1 の実施形態の画像処理装置では、レンズの歪曲収差の補正や単色の入力画像の補正を行っていた。これに対し、第 2 の実施形態においては、R、B、G の 3 チャネルの色画像について、倍率色収差補正を行う点が異なっている。第 2 の実施形態の画像処理装置は、第 1 の実施形態と同様の構成である。以下、画像補正処理方法について説明する。なお、同じ構成要素や同じ処理については、同じ符号を付して説明を省略する。

#### 【0058】

図 3 は、第 2 の実施形態における画像補正処理を説明するフローチャートである。G、B、R のそれぞれの色画素について、入力画素をラインバッファ 11 に拡充する (S 1)。まず、G 画素の補正対象入力画素 $Pi_g(v_o_g, h_o_g)$  に関する読み出し画素位置集合を算出する。この集合について、周知の画素位置計算方法を適用することにより、書き込み画素領域を特定し (S 2)、書き込み画素候補 $Poc(v', h')$  を抽出する (S 3)。そして、S 2 で用いた画素位置計算の逆関数を用いて、G 画素の読み出し画素 $Pi_g(v_g, h_g)$  を算出する (S 51)。40

#### 【0059】

読み出し画素 $Pi_g(v_g, h_g)$  の画素値を補間ににより算出するために必要なすべての画素が、集合に含まれている場合、当該読み出し画素 $Pi_g(v_g, h_g)$  に対応する書き込み画素候補 $Poc(v', h')$  を、書き込み画素 $P_o(v', h')$  と確定する (S 6、Yes)。50

## 【0060】

続いて、周知の画素位置計算方法を適用することにより、G画素の読み出し画素Pi\_g( $vg", hg"$ )からB、R画素の読み出し画素Pi\_b( $vb", hb"$ )、Pi\_r( $vr", hr"$ )をそれぞれ特定する(S52)。なお、画素位置計算に用いるパラメータは、G画素からB画素を算出する際に用いるものと、G画素からR画素を算出する際に用いるものが、それぞれ予め設定されている。

## 【0061】

最後に、Pi\_g( $vg", hg"$ )、Pi\_b( $vb", hb"$ )、Pi\_r( $vr", hr"$ )のそれぞれについて、画素補間を行って画素値を算出し、書き込み画素Po( $v', h'$ )における画素値として出力する(S7)。すべての書き込み画素候補Poc( $v', h'$ )について、確定判定と画素補間による画素値算出が終了したら、一連の画素補正処理を終了する。10

## 【0062】

このように、本実施形態によれば、R、B、Gの3チャネルの色画像について、倍率色収差補正を行う際にも、撮像装置からラスタスキャン順に読み込まれる入力画素を、この順に補正処理を行う。従って、補正に必要な入力画素の範囲を数ライン程度で抑えることができるため、入力画素を格納するラインバッファ11の搭載量を低減することができ、製造コストを抑制することができる。

## 【0063】

なお、上述では、B、R画素の読み出し画素Pi\_b( $vb", hb"$ )、Pi\_r( $vr", hr"$ )は、G画素の読み出し画素Pi\_g( $vg", hg"$ )から画素位置計算を用いて算出しているが、書き込み画素Po( $v', h'$ )から画素位置計算を用いて算出してもよい。20

## 【0064】

また、画素位置計算の方法は、逆関数が存在する方法であれば、任意の方法を用いることができる。更に、複数の画素位置計算方法を組み合わせて用いてもよい。例えば、多項式を用いた関数でレンズの歪曲収差の補正を行った後、グリッドテーブル変換を用いて色倍率収差の補正を行うなど、複数の補正を行うことが可能になる。

## (第3の実施形態)

第1の実施形態の画像処理装置では、入力画像に対してレンズの歪曲収差の補正を行い、歪みを補正した画像を出力していた。これに対し、第3の実施形態においては、歪み補正処理時にピラミッド処理も行い、ピラミッド画像(解像度の異なる同一画像の集合)も生成する点が異なっている。30

## 【0065】

図4は、第3の実施形態に係わる画像処理装置の概略ブロック図である。なお、第1の実施形態の画像処理装置と同じ構成要素については、同じ符号を付して説明を省略する。

## 【0066】

書き込み画素位置スケール部12aは、補正対象である読み出し画素Piを用いて補間した画素に、所定のスケールを乗じてピラミッド処理を施した画素が含まれると推定される、書き込み画素領域を算出する。具体的には、書き込み画素位置計算部12において算出された、書き込み画素領域の頂点の画素Po0( $vo', ho'$ )、Po1( $vo', ho-1'$ )、Po2( $vo-1', ho-1'$ )、Po3( $vo-1', ho'$ )のそれぞれについて、所定のピラミッド画像を生成するためのスケールを乗ずる。これにより、ピラミッド画像における書き込み画素領域の頂点の画素Po0( $vo_s', ho_s'$ )、Po1( $vo_s', ho-1_s'$ )、Po2( $vo-1_s', ho-1_s'$ )、Po3( $vo-1_s', ho_s'$ )を算出する。40

## 【0067】

読み出し画素位置スケール部13aは、書き込み画素位置スケール部12aで算出した、ピラミッド画像の書き込み画素領域内において、垂直位置、水平位置ともに整数となる画素の位置(書き込み画素候補Poc( $v_s', h_s'$ ))を抽出する。そして、所定のスケールの逆数を乗じ、等倍の出力画像における書き込み画素位置に変換する。書き込み画素候補Poc( $v_s', h_s'$ )に対応する読み出し画素Pi( $v_s", h_s"$ )を、画素位置計算を行って算出する。なお、画素位置計算は、書き込み画素位置計算部12で行った画素位50

置計算の逆関数を用いて行う。候補が複数ある場合は、全ての候補 $P_{oc}(v_s', h_s')$ に対して読み出し画素 $P_i(v_s'', h_s'')$ を算出する。

#### 【0068】

パラメータ格納部15'は、書き込み画素位置計算部12および読み出し画素位置計算部13における画素位置計算関数に用いるパラメータ加え、生成するピラミッド画像のスケールが格納されている。なお、複数のスケールのピラミッド画像を生成する場合、それぞれの画像に対応する複数のスケールが格納されている。

#### 【0069】

次に、本実施形態における画像処理方法について説明する。図5は、第3の実施形態における画像補正処理を説明するフローチャートである。なお、第1の実施形態の画像処理方法と同じ処理については、同じ符号を付して説明を省略する。

10

#### 【0070】

まず、ラスタスキヤン順に画像処理装置1'に入力された画素を、ラインバッファ11に拡充する(S1)。次に、補正対象画素である読み出し画素 $P_i(v_o, h_o)$ を特定し、読み出し画素 $P_i$ を用いて補間した画素が含まれると推定される、書き込み画素領域を算出する(S2)。画素位置計算は、多項式で表現される関数を用いてもよいし、グリッドテーブル変換を用いてもよい。また、多項式で表現される関数を用いて計算した結果に対してグリッドテーブル変換を更に用いてもよいし、グリッドテーブル変換により計算した結果に対して多項式で表現される関数を更に用いてもよい。

20

#### 【0071】

次に、所定のスケールのピラミッド画像に対応する書き込み画素領域を算出する(S20)。画素位置計算に多項式で表現される関数を用いる場合、S2において算出された画素位置計算の像高スケール( $r\_scale$ )を用い、ピラミッド画像のスケールに応じて当該像高スケールを再スケールする。具体的には、以下に示す(23)式を用いて行う。

20

#### 【0072】

$$r\_scale\_scaled = r\_scale * scale \quad \dots (23) \text{ 式}$$

(23)式において、 $scale$ は、通常の歪み補正のみを行う出力画像に対するピラミッド画像のスケール値である。また、 $scale$ の値は予め設定されており、パラメータ格納部15'に格納されているものとする。通常、 $scale$ の値は、0.5~2程度の値が設定されている。

30

#### 【0073】

続いて、ピラミッド画像用にスケールされた像高スケールを、(7)(8)式を用いて $(v, h)$ の座標系に戻す。ただし、(7)(8)式において、 $r\_scale$ には $r\_scale\_scaled$ を代入する。このようにして、読み出し画素 $P_i(v_o, h_o)$ 、 $P_{i1}(v_o, h_o-1)$ 、 $P_{i2}(v_o-1, h_o-1)$ 、 $P_{i3}(v_o-1, h_o)$ が、それぞれ、書き込み画素 $P_{o0}(v_{o\_s'}, h_{o\_s'})$ 、 $P_{o1}(v_{o\_s'}, h_{o\_s'-1})$ 、 $P_{o2}(v_{o\_s'}, h_{o\_s'-1})$ 、 $P_{o3}(v_{o\_s'}, h_{o\_s'})$ に変換される。

#### 【0074】

グリッドテーブル変換を用いて画素位置計算を行う場合、S2において算出された、書き込み画素 $P_{o0}(v_o', h_o')$ 、 $P_{o1}(v_o', h_o-1')$ 、 $P_{o2}(v_o-1', h_o-1')$ 、 $P_{o3}(v_o-1', h_o')$ について、水平方向の座標位置、及び、垂直方向の座標位置にピラミッド画像のスケールを乗ずる。具体的には、まず、(24)(25)式を用い、書き込み画素の位置を、左上を原点とする $(v, h)$ の座標系から、光学中心を原点とする $(x, y)$ の座標系に変換する。

40

#### 【0075】

$$x = h_{out} + [SENSOR_CROP_OFS_H] \quad \dots (24) \text{ 式}$$

$$y = v_{out} + [SENSOR_CROP_OFS_V] \quad \dots (25) \text{ 式}$$

変換後の座標位置に対し、ピラミッド画像のスケールを用いて再スケールする。具体的には、以下の(26)(27)式を用いて行う。

#### 【0076】

50

```

x_scaled = x * scale ... ( 2 6 ) 式

y_scaled = y * scale ... ( 2 7 ) 式

```

最後に、ピラミッド画像用にスケールされた座標位置を、左上を原点とする( $v$ ,  $h$ )の座標系に戻す。このようにして、読み出し画素 $P_i(v_o, h_o)$ 、 $P_{i1}(v_o, h_{o-1})$ 、 $P_{i2}(v_{o-1}, h_{o-1})$ 、 $P_{i3}(v_{o-1}, h_o)$ が、それぞれ、書き込み画素 $P_{o0}(v_{o\_s'}, h_{o\_s'})$ 、 $P_{o1}(v_{o\_s'}, h_{o-1\_s'})$ 、 $P_{o2}(v_{o-1\_s'}, h_{o-1\_s'})$ 、 $P_{o3}(v_{o-1\_s'}, h_{o\_s'})$ に変換される。

#### 【 0 0 7 7 】

すなわち、画素位置計算として、多項式で表現される関数を用いる場合にも、グリッドテーブル変換を用いる場合にも、S 2 の計算結果や途中経過を用い、4 点の画素 $P_{o0}(v_{o\_s'}, h_{o\_s'})$ 、 $P_{o1}(v_{o\_s'}, h_{o-1\_s'})$ 、 $P_{o2}(v_{o-1\_s'}, h_{o-1\_s'})$ 、 $P_{o3}(v_{o-1\_s'}, h_{o\_s'})$ を頂点とする矩形領域が、ピラミッド画像の書き込み画素領域を特定することができる。

10

#### 【 0 0 7 8 】

なお、複数のスケールのピラミッド画像を生成する場合、S 2 0 を繰り返し実行し、それぞれのスケールに対応する書き込み画素領域を特定する。

#### 【 0 0 7 9 】

次に、S 2、及び S 2 0 を実行することによって特定された各矩形領域(書き込み画素領域)内において、垂直座標、及び、水平座標が共に整数となる画素位置(書き込み画素候補 $P_{oc}(v', h')$ )を抽出する(S 3)。続いて、S 3 で求めたすべての書き込み画素候補 $P_{oc}(v', h')$ に対し、書き込み画素 $P_o(v', h')$ であるか否かの判定を行う。判定をまだ行っていない書き込み画素候補 $P_{oc}(v', h')$ がある場合(S 4、No)、画素位置計算により、対応する読み出し画素 $P_i(v'', h'')$ を算出する(S 5)。なお、S 5 では、S 2 において特定された書き込み画素領域に対応する書き込み画素候補について、対応する読み出し画素を算出する。

20

#### 【 0 0 8 0 】

なお、S 2 0 において特定された、ピラミッド画像用にスケールされた書き込み画素領域に対応する書き込み画素候補 $P_{oc}(v', h')$ については、S 5 において画素位置計算を行う前に、書き込み画素候補に対して S 2 0 において用いたスケールの逆数を乗じ、等倍の出力画像における書き込み画素位置に変換する(S 5 0)。次に、変換した画素位置に対し、S 2 0 で用いた画素位置計算の逆関数を用いて読み出し画素の画素位置計算を行う(S 5)。なお、S 5 において算出した、 $P_i(v'', h'')$ の垂直座標、水平座標は、非整数となる。

30

#### 【 0 0 8 1 】

次に、 $P_i(v'', h'')$ の画素値を補間にによって算出するためには必要な画素を特定する。例えば、バイリニア補間にによって画素値を算出する場合、 $P_i(v'', h'')$ の周囲 4 点の画素が補間に必要な画素となる。補間に必要なすべての画素が、集合に含まれている場合、当該読み出し画素 $P_i(v'', h'')$ に対応する書き込み画素候補 $P_{oc}(v', h')$ を、書き込み画素 $P_o(v', h')$ と確定する(S 6、Yes)。

#### 【 0 0 8 2 】

この場合、確定した書き込み画素 $P_o(v', h')$ の画素値を、対応する読み出し画素 $P_i(v'', h'')$ の画素値を画素補間にによって算出して出力する(S 7)。なお、出力画素 $P_o(v', h')$ は、ラスタスキャン順でなくランダムとなる。続いて S 4 に戻り、未判定の書き込み画素候補 $P_{oc}(v', h')$ の有無を調べる。

40

#### 【 0 0 8 3 】

一方、補間に必要な画素のうち、集合に含まれていない画素が存在する場合、当該読み出し画素 $P_i(v'', h'')$ に対応する書き込み画素候補 $P_{oc}(v', h')$ は、書き込み画素 $P_o(v', h')$ でないと確定する(S 6、No)。この場合、画素補間は行わずに、S 4 に戻って、未判定の書き込み画素候補 $P_{oc}(v', h')$ の有無を調べる。

#### 【 0 0 8 4 】

10

20

30

40

50

S 4において、S 3で求めたすべての書き込み画素候補Poc(v', h')について、判定が行われている場合、画像補正処理の一連の手順を終了する。

#### 【0085】

なお、S 2において、歪み補正処理を施した等倍の出力画像における書き込み画素領域を算出後、ピラミッド画像の各スケールの手順は依存関係がないため、算出順序の並び替えや、並列実行が可能である。例えば、複数のスケールのピラミッド画像を生成する場合、S 20とS 50については、どちらのスケールを先に実施してもよい。また、等倍の出力画像を生成した後、S 2の算出結果を用いてスケール画像を生成してもよい。

#### 【0086】

このように、本実施形態によれば、撮像装置からラスタスキヤン順に読み込まれる入力画素を、この順に補正処理を行う。従って、補正に必要な入力画素の範囲を1乃至数ライン程度で抑えることができるため、入力画素を格納するラインバッファ11の搭載量を低減することができ、製造コストを抑制することができる。

10

#### 【0087】

また、本実施形態によれば、歪み補正処理における画素位置計算時に、ピラミッド画像生成のための画素位置計算も含んで行う。従って、歪み補正処理後の画像に対してスケール処理を施してピラミッド画像を生成する場合に比べ、サンプリング補間処理回数が低減されるため、ピラミッド画像の画質劣化を抑制することができる。また、メモリに書き込まれた歪み補正処理後の画像を、ピラミッド画像生成用に読み出す必要がなくなるため、メモリへのアクセス時間を削減することができ、処理時間を低減することができる。

20

#### 【0088】

なお、読み出し画素から書き込み画素を算出する画素位置計算の方法は、上述の方法に限定されない。すなわち、逆関数が存在する方法であれば、任意の方法を用いることができる。また、複数の画素位置計算方法を組み合わせて用いてもよい。

#### (第4の実施形態)

第3の実施形態の画像処理装置では、レンズの歪曲収差の補正や単色の入力画像の補正を処理時にピラミッド画像を生成していた。これに対し、第4の実施形態においては、R、B、Gの3チャネルの色画像について、倍率色収差補正処理時にピラミッド画像を生成する点が異なっている。第4の実施形態の画像処理装置は、第3の実施形態と同様の構成である。以下、画像補正処理方法について説明する。なお、同じ構成要素や同じ処理については、同じ符号を付して説明を省略する。

30

#### 【0089】

図6は、第4の実施形態における画像補正処理を説明するフローチャートである。G、B、Rのそれぞれの色画素について、入力画素をラインバッファ11に拡充する(S1)。まず、G画素の補正対象入力画素Pi\_g(vo\_g, ho\_g)に関する読み出し画素位置集合を算出する。この集合について、周知の画素位置計算方法を適用することにより、書き込み画素領域を特定する(S2)。次に、所定のスケールのピラミッド画像に対応する書き込み画素領域を特定し(S20)、S2及びS20で特定した書き込み画素領域から書き込み画素候補Poc(v', h')を抽出する(S3)。

40

#### 【0090】

続いて、S3で求めたすべての書き込み画素候補Poc(v', h')に対し、書き込み画素Po(v', h')であるか否かの判定を行う。判定をまだ行っていない書き込み画素候補Poc(v', h')がある場合(S4、No)、画素位置計算により、S2で用いた画素位置計算の逆関数を用いて、G画素の読み出し画素Pi\_g(vg", hg")を算出する(S51)。なお、S5では、S2において特定された書き込み画素領域に対応する書き込み画素候補について、対応する読み出し画素を算出する。

#### 【0091】

なお、S20において特定された、ピラミッド画像用にスケールされた書き込み画素領域に対応する書き込み画素候補Poc(v', h')については、S5において画素位置計算を行う前に、書き込み画素候補に対してS20において用いたスケールの逆数を乗じ、等

50

倍の出力画像における書き込み画素位置に変換する（S510）。次に、対応するG画素の読み出し画素Pi\_g(vg", hg")を算出する（S51）。

#### 【0092】

読み出し画素Pi\_g(vg", hg")の画素値を補間により算出するために必要なすべての画素が、集合に含まれている場合、当該読み出し画素Pi\_g(vg", hg")に対応する書き込み画素候補Poc(v', h')を、書き込み画素Po(v', h')と確定する（S6、Yes）。

#### 【0093】

続いて、周知の画素位置計算方法を適用することにより、S51において算出されたG画素の読み出し画素Pi\_g(vg", hg")から、B、R画素の読み出し画素Pi\_b(vb", hb")、Pi\_r(vr", hr")をそれぞれ特定する（S52）。このとき、画素位置計算に用いるパラメータは、G画素からB画素を算出する際に用いるものと、G画素からR画素を算出する際に用いるものが、それぞれ予め設定されている。

10

#### 【0094】

なお、ピラミッド画像におけるG画素の読み出し画素Pi\_g(vg", hg")については、S20で用いた所定のスケールを用いてスケーリングを施した後（S520）、B、R画素の読み出し画素Pi\_b(vb", hb")、Pi\_r(vr", hr")をそれぞれ特定する（S52）。

20

#### 【0095】

最後に、Pi\_g(vg", hg")、Pi\_b(vb", hb")、Pi\_r(vr", hr")のそれについて、画素補間を行って画素値を算出し、書き込み画素Po(v', h')における画素値として出力する（S7）。すべての書き込み画素候補Poc(v', h')について、確定判定と画素補間による画素値算出が終了したら、一連の画素補正処理を終了する。

20

#### 【0096】

なお、S2において、等倍の出力画像における書き込み画素領域を算出後、ピラミッド画像の各スケールの手順は依存関係がないため、算出順序の並び替えや、並列実行が可能である。例えば、複数のスケールのピラミッド画像を生成する場合、S20とS510、S520については、どちらのスケールを先に実施してもよい。また、等倍の出力画像を生成した後、S2の算出結果を用いてスケール画像を生成してもよい。

30

#### 【0097】

このように、本実施形態によれば、R、B、Gの3チャネルの色画像について、倍率色収差補正を行う際にも、撮像装置からラスタスキャン順に読み込まれる入力画素を、この順に補正処理を行う。従って、補正に必要な入力画素の範囲を数ライン程度で抑えることができるため、入力画素を格納するラインバッファ11の搭載量を低減することができ、製造コストを抑制することができる。

30

#### 【0098】

また、本実施形態によれば、倍率色収差補正における画素位置計算時に、ピラミッド画像生成のための画素位置計算も含んで行う。従って、補正処理後の画像に対してスケール処理を施してピラミッド画像を生成する場合に比べ、サンプリング補間処理回数が低減されるため、ピラミッド画像の画質劣化を抑制することができる。また、メモリに書き込まれた歪み補正処理後の画像を、ピラミッド画像生成用に読み出す必要がなくなるため、メモリへのアクセス時間を削減することができ、処理時間を低減することができる。

40

#### 【0099】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、一例として示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0100】

50

1 ... 画像処理装置、11 ... ラインバッファ、12 ... 書き込み画素位置計算部、13 ... 読み出し画素位置計算部、14 ... 書き込み画素位置判定部、15 ... パラメータ格納部、16 ... 画素補間部、Pi... 入力画素、Po... 出力画素、Poc... 出力画素候補

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 増田 篤司

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターク(参考) 5B057 BA02 CA01 CA08 CA12 CA16 CB01 CB08 CB12 CB16 CD12

CH11

5C122 EA55 GA24 HA42 HA71 HA88