(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7572012号**

**(P7572012)**

(45)発行日 令和6年10月23日(2024.10.23)

(24)登録日 令和6年10月15日(2024.10.15)

(51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A |

| H 01 L | 31/10 (2006.01)  | H 01 L | 31/10  | A |

| H 04 N | 25/63 (2023.01)  | H 04 N | 25/63  |   |

| H 04 N | 25/76 (2023.01)  | H 04 N | 25/76  |   |

F I

請求項の数 7 (全25頁)

(21)出願番号 特願2022-135450(P2022-135450)

(22)出願日 令和4年8月27日(2022.8.27)

(65)公開番号 特開2024-32005(P2024-32005A)

(43)公開日 令和6年3月8日(2024.3.8)

審査請求日 令和6年8月19日(2024.8.19)

早期審査対象出願

(73)特許権者 000003193

T O P P A N ホールディングス株式会社

東京都台東区台東1丁目5番1号

(73)特許権者 505374783

国立研究開発法人日本原子力研究開発機構

茨城県那珂郡東海村大字舟石川765番地1

(73)特許権者 000209751

池上通信機株式会社

東京都大田区池上5丁目6番16号

(74)代理人 100218280

弁理士 安保 亜衣子

(74)代理人 100108914

弁理士 鈴木 壮兵衛

最終頁に続く

(54)【発明の名称】 光検出素子及び固体撮像装置

**(57)【特許請求の範囲】****【請求項1】**

第1導電型の基体領域と、

該基体領域の上部の一部に埋め込まれ、前記基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、

該電荷生成埋込層の上面に接し、前記基体領域の上部の他の一部に埋め込まれた前記基体領域よりも高不純物密度で第1導電型のシールド層と、

前記基体領域の上部の更に他の一部に前記電荷生成埋込層に接して埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、

前記シールド層の上面に接したフォトゲート絶縁膜と、

前記シールド層の一部の上方となる、前記フォトゲート絶縁膜の前記電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、

該緩和領域部に連続し、前記シールド層の他の一部の上方に位置する前記フォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層と、

を備え、前記主透明電極層の電位が、前記緩和領域部の電位よりも強く前記シールド層の半導体界面に第1導電型の電荷をピンニングすることを特徴とする光検出素子。

**【請求項2】**

第1導電型の基体領域と、

該基体領域の上部の一部に埋め込まれ、前記基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、

10

20

該電荷生成埋込層の上面に接し、前記基体領域の上部の他の一部に埋め込まれた前記基体領域よりも高不純物密度で第1導電型のシールド層と、

前記基体領域の上部の更に他の一部に前記電荷生成埋込層に接して埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、

前記シールド層の上面に接したフォトゲート絶縁膜と、

前記シールド層の一部の上方となる、前記フォトゲート絶縁膜の前記電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、

該緩和領域部に連続し、前記シールド層の他の一部の上方に位置する前記フォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層と、

前記緩和領域部とは反対側で前記主透明電極層に連続し、前記シールド層の更に他の一部の上方となる前記フォトゲート絶縁膜の上に設けられた透明電極である第2導電型の抵抗増大部と、

を備え、前記主透明電極層の電位が、前記緩和領域部及び前記抵抗増大部の電位よりも強く前記シールド層の半導体界面に第1導電型の電荷をピンニングすることを特徴とする光検出素子。

#### 【請求項3】

一部が前記電荷読出領域の一部の領域と重畠し、前記基体領域の上部の更に他の一部に埋め込まれた、前記基体領域よりも高不純物密度の第1導電型のウェル領域と、

前記電荷読出領域から離間して前記ウェル領域の上部の一部に埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型のリセットドレイン領域と、

前記電荷読出領域と前記リセットドレイン領域との間の前記ウェル領域の上面に接したリセットゲート絶縁膜と、

該リセットゲート絶縁膜上に設けられたリセットゲート電極と、

を更に備えることを特徴とする請求項1又は2に記載の光検出素子。

#### 【請求項4】

前記電荷読出領域に光電変換により発生した電荷を蓄積し、前記リセットゲート電極に印加する電圧により、前記蓄積された電荷を前記リセットドレイン領域へ排出することを特徴とする請求項3に記載の光検出素子。

#### 【請求項5】

第1導電型の基体領域と、

該基体領域の上部の一部に埋め込まれ、前記基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、

該電荷生成埋込層の上面に接し、前記基体領域の上部の他の一部に埋め込まれた前記基体領域よりも高不純物密度で第1導電型のシールド層と、

前記基体領域の上部の更に他の一部に前記電荷生成埋込層に接して埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、

前記シールド層の上面に接したフォトゲート絶縁膜と、

前記シールド層の一部の上方となる、前記フォトゲート絶縁膜の前記電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、

該緩和領域部に連続し、前記シールド層の他の一部の上方に位置する前記フォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層と、

を備える画素の複数を配列し、前記画素のそれぞれの内部において、前記主透明電極層の電位が、前記緩和領域部の電位よりも強く前記シールド層の半導体界面に第1導電型の電荷をピンニングすることを特徴とする固体撮像装置。

#### 【請求項6】

第1導電型の基体領域と、

該基体領域の上部の一部に埋め込まれ、前記基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、

該電荷生成埋込層の上面に接し、前記基体領域の上部の他の一部に埋め込まれた前記基体領域よりも高不純物密度で第1導電型のシールド層と、

10

20

30

40

50

前記基体領域の上部の更に他的一部に前記電荷生成埋込層に接して埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、

前記シールド層の上面に接したフォトゲート絶縁膜と、

前記シールド層の一部の上方となる、前記フォトゲート絶縁膜の前記電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、

該緩和領域部に連続し、前記シールド層の他の一部の上方に位置する前記フォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層と、

前記緩和領域部とは反対側で前記主透明電極層に連続し、前記シールド層の更に他的一部の上方となる前記フォトゲート絶縁膜の上に設けられた透明電極である第2導電型の抵抗増大部と、

を備える画素の複数を配列し、前記画素のそれぞれの内部において、前記主透明電極層の電位が、前記緩和領域部及び前記抵抗増大部の電位よりも強く前記シールド層の半導体界面に第1導電型の電荷をピンニングすることを特徴とする固体撮像装置。

#### 【請求項7】

前記画素のそれぞれが、

一部が前記電荷読出領域の一部の領域と重畠し、前記基体領域の上部の更に他的一部に埋め込まれた、前記基体領域よりも高不純物密度の第1導電型のウェル領域と、

前記電荷読出領域から離間して前記ウェル領域の上部の一部に埋め込まれ、前記電荷生成埋込層よりも高不純物密度で第2導電型のリセットドレイン領域と、

前記電荷読出領域と前記リセットドレイン領域との間の前記ウェル領域の上面に接したリセットゲート絶縁膜と、

該リセットゲート絶縁膜上に設けられたリセットゲート電極と、

を更に備えることを特徴とする請求項5又は6に記載の固体撮像装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、フォトゲート型の光検出素子及びこの光検出素子を画素として、半導体チップ上に多数の画素を配列したフォトゲート型の固体撮像装置に関する。

##### 【背景技術】

##### 【0002】

放射線耐性を目的として、MOS型ゲート電極を透明電極にした光電変換部（以下において、「フォトゲート型光電変換部」と称する。）を有する画素が知られている（特許文献1参照。）。フォトゲート型光電変換部は、p型の基体領域の上部に設けられたn型の電荷生成埋込層及びその上面に設けられた基体領域より高不純物密度のp型のシールド層を備える。透明電極は、電荷生成埋込層及びシールド層の上に絶縁膜を介したMOS構造のゲート電極として設けられる。透明電極は、一般にn型の不純物を添加した多結晶シリコン（ドープド・ポリシリコン：DOPoS）膜が用いられる。そして、透明電極の下に配置された電荷生成埋込層にチャネル部が形成される。

##### 【0003】

特許文献1に記載されたフォトゲート型光電変換部を有する固体撮像装置（以下において「フォトゲート型固体撮像装置」という。）の場合、フォトゲート型光電変換部の光電変換によって発生した電荷は、電荷生成埋込層及び電荷生成埋込層に隣接して設けられるn型の電荷読出領域（電荷蓄積部）に蓄積され、電荷読出領域での電位変化が信号として読み出される。ここで信号電荷が電子である場合、フォトゲート型光電変換部での暗電流の発生を抑えるために、半導体表面に形成されたシールド層に存在する正孔で埋めて不活性化させる「ピンニング動作」を実行する。特許文献1に記載された発明においては、このピンニング動作のために、フォトゲート型光電変換部の透明電極に常時、一定のゼロないし若干の正電圧を印加させる操作が必要である。

#### 【先行技術文献】

#### 【特許文献】

10

20

30

40

50

**【0004】**

【文献】特開2018-182044号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献1に記載された発明では、p型の透明電極による効果とn型の透明電極による効果の相違点は考慮されていなかった。本発明の発明者らは、電荷生成埋込層及び電荷読出領域がn型であり、シールド層がp型の構造に対し、先ず、透明電極がn型である場合を検討した。透明電極がn型である場合の課題は、透明電極に常時、一定のゼロないし若干の正電圧を印加した状態でフォトゲート型固体撮像装置を駆動すると、シールド層の半導体界面が僅かに空乏化し、暗電流抑圧が完全ではなくなるという問題である。一方、透明電極をp型にした場合には、半導体界面の空乏化が十分に抑制され暗電流抑圧には効果があるが、透明電極と電荷読出領域の間の電界集中が大きくなり、読み出し動作に悪影響を与えるという二律背反の問題が発生するという課題を、新たな知見として得た。

10

**【0006】**

上記問題に鑑み、本発明は、透明電極と電荷読出領域の間の電界集中を抑えると同時にシールド層の半導体界面の空乏化を抑制し、暗電流抑圧を完全なものとし、放射線環境下でも高感度かつ広ダイナミックレンジな光検出素子、及びこの光検出素子を画素とする固体撮像装置を提供することを目的とする。

20

**【課題を解決するための手段】****【0007】**

上記目的を達成するために、本発明の第1の態様は、(a)第1導電型の基体領域と、(b)基体領域の上部の一部に埋め込まれ、基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、(c)電荷生成埋込層の上面に接し、基体領域の上部の他の一部に埋め込まれた基体領域よりも高不純物密度で第1導電型のシールド層と、(d)基体領域の上部の更に他の一部に電荷生成埋込層に接して埋め込まれ、電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、(e)シールド層の上面に接したフォトゲート絶縁膜と、(f)シールド層の一部の上方となる、フォトゲート絶縁膜の電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、(g)この緩和領域部に連続し、シールド層の他の一部の上方に位置するフォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層を備える光検出素子であることを要旨とする。本発明の第1の態様に係る光検出素子においては、主透明電極層の電位が、緩和領域部の電位よりも強くシールド層の半導体界面に第1導電型の電荷をピンニングする。

30

**【0008】**

本発明の第2の態様は、(a)第1導電型の基体領域と、(b)基体領域の上部の一部に埋め込まれ、基体領域とのp-n接合で信号電荷を生成する第2導電型の電荷生成埋込層と、(c)電荷生成埋込層の上面に接し、基体領域の上部の他の一部に埋め込まれた基体領域よりも高不純物密度で第1導電型のシールド層と、(d)基体領域の上部の更に他の一部に電荷生成埋込層に接して埋め込まれ、電荷生成埋込層よりも高不純物密度で第2導電型の電荷読出領域と、(e)シールド層の上面に接したフォトゲート絶縁膜と、(f)シールド層の一部の上方となる、フォトゲート絶縁膜の電荷読出領域側の端部の上に設けられた透明電極である第2導電型の緩和領域部と、(g)この緩和領域部に連続し、シールド層の他の一部の上方に位置するフォトゲート絶縁膜の上に設けられた透明電極である第1導電型の主透明電極層と、(h)緩和領域部とは反対側で主透明電極層に連続し、シールド層の更に他の一部の上方となるフォトゲート絶縁膜の上に設けられた透明電極である第2導電型の抵抗増大部を備える、光検出素子であることを要旨とする。本発明の第2の態様に係る光検出素子においては、主透明電極層の電位が、緩和領域部及び抵抗増大部の電位よりも強くシールド層の半導体界面に第1導電型の電荷をピンニングする。

40

**【0009】**

本発明の第3の態様は、(a)第1導電型の基体領域と、(b)基体領域の上部の一部に埋め

50

込まれ、基体領域との p - n 接合で信号電荷を生成する第 2 導電型の電荷生成埋込層と、(c)電荷生成埋込層の上面に接し、基体領域の上部の他の一部に埋め込まれた基体領域よりも高不純物密度で第 1 導電型のシールド層と、(d)基体領域の上部の更に他の一部に電荷生成埋込層に接して埋め込まれ、電荷生成埋込層よりも高不純物密度で第 2 導電型の電荷読出領域と、(e)シールド層の上面に接したフォトゲート絶縁膜と、(f)シールド層の一部の上方となる、フォトゲート絶縁膜の電荷読出領域側の端部の上に設けられた透明電極である第 2 導電型の緩和領域部と、(g)この緩和領域部に連続し、シールド層の他の一部の上方に位置するフォトゲート絶縁膜の上に設けられた透明電極である第 1 導電型の主透明電極層を備える画素の複数を、配列した固体撮像装置であることを要旨とする。本発明の第 3 の態様に係る固体撮像装置を構成する画素のそれぞれの内部において、主透明電極層の電位が、緩和領域部の電位よりも強くシールド層の半導体界面に第 1 導電型の電荷をピンニングする。

#### 【 0 0 1 0 】

本発明の第 4 の態様は、(a)第 1 導電型の基体領域と、(b)基体領域の上部の一部に埋め込まれ、基体領域との p - n 接合で信号電荷を生成する第 2 導電型の電荷生成埋込層と、(c)電荷生成埋込層の上面に接し、基体領域の上部の他の一部に埋め込まれた基体領域よりも高不純物密度で第 1 導電型のシールド層と、(d)基体領域の上部の更に他の一部に電荷生成埋込層に接して埋め込まれ、電荷生成埋込層よりも高不純物密度で第 2 導電型の電荷読出領域と、(e)シールド層の上面に接したフォトゲート絶縁膜と、(f)シールド層の一部の上方となる、フォトゲート絶縁膜の電荷読出領域側の端部の上に設けられた透明電極である第 2 導電型の緩和領域部と、(g)この緩和領域部に連続し、シールド層の他の一部の上方に位置するフォトゲート絶縁膜の上に設けられた透明電極である第 1 導電型の主透明電極層と、(h)緩和領域部とは反対側で主透明電極層に連続し、シールド層の更に他の一部の上方となるフォトゲート絶縁膜の上に設けられた透明電極である第 2 導電型の抵抗増大部を備える画素の複数を、配列した固体撮像装置であることを要旨とする。本発明の第 4 の態様に係る固体撮像装置を構成する画素のそれぞれの内部において、主透明電極層の電位が、緩和領域部及び抵抗増大部の電位よりも強くシールド層の半導体界面に第 1 導電型の電荷をピンニングする。

#### 【 発明の効果 】

#### 【 0 0 1 1 】

本発明によれば、透明電極と電荷読出領域の間の電界集中を抑えると同時にシールド層の半導体界面の空乏化を抑制し、暗電流抑圧を完全なものとし、放射線環境下でも高感度かつ広ダイナミックレンジな光検出素子、及びこの光検出素子を画素とする固体撮像装置を提供することができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 2 】

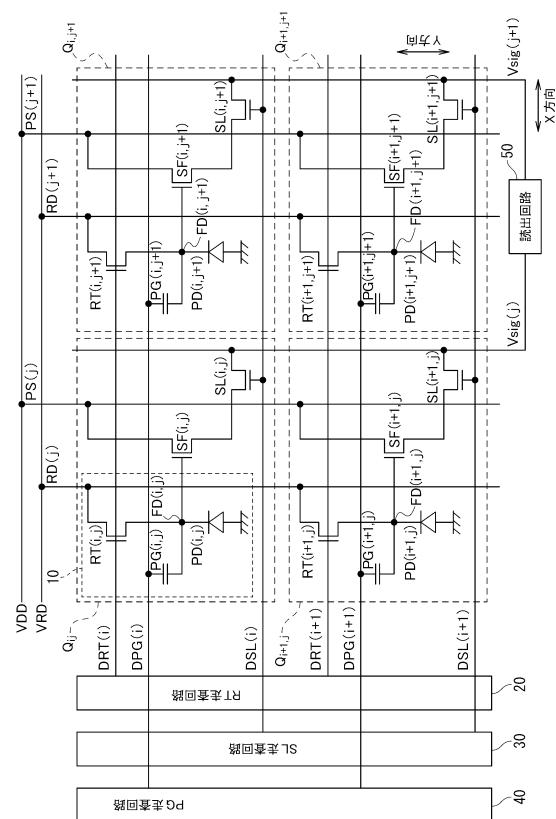

【図 1】本発明の第 1 実施形態に係る固体撮像装置の全体構成の概略を模式的に説明する回路図である。

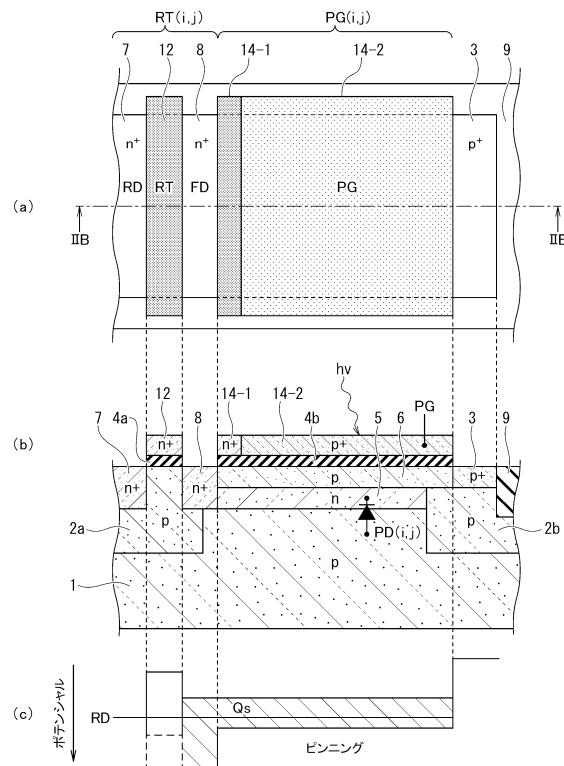

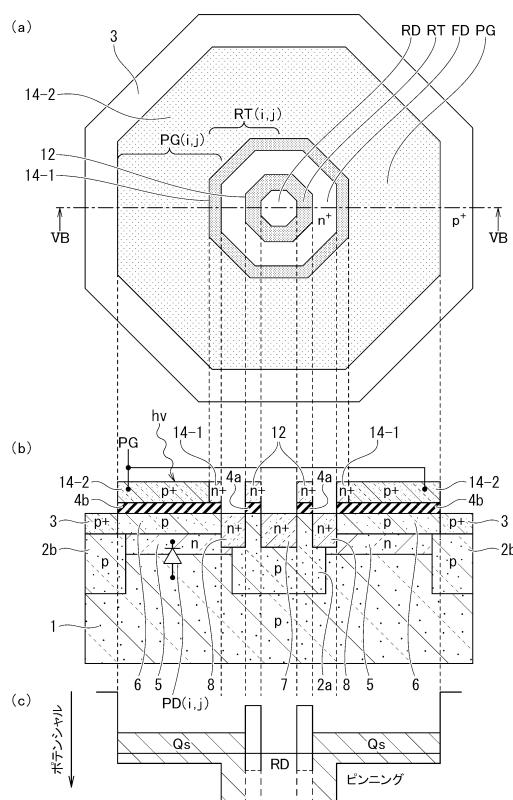

【図 2】図 2 ( a )は第 1 実施形態に係る光検出素子の概略を模式的に説明する平面図であり、図 2 ( b )は図 2 ( a )中の IIB - IIB 方向から見た断面図であり、図 2 ( c )は図 2 ( b )方向に沿ったポテンシャル分布である。

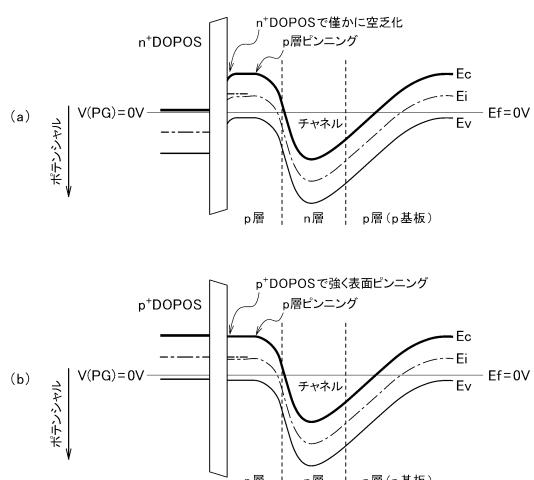

【図 3】図 3 ( a )は一様な n 層を透明電極に用いた場合のフォトゲート光電変換部における深さ方向のポテンシャル分布を示す図で、図 3 ( b )は、一様な p 層を透明電極に用いた場合のフォトゲート光電変換部における深さ方向のポテンシャル分布を示す図である。

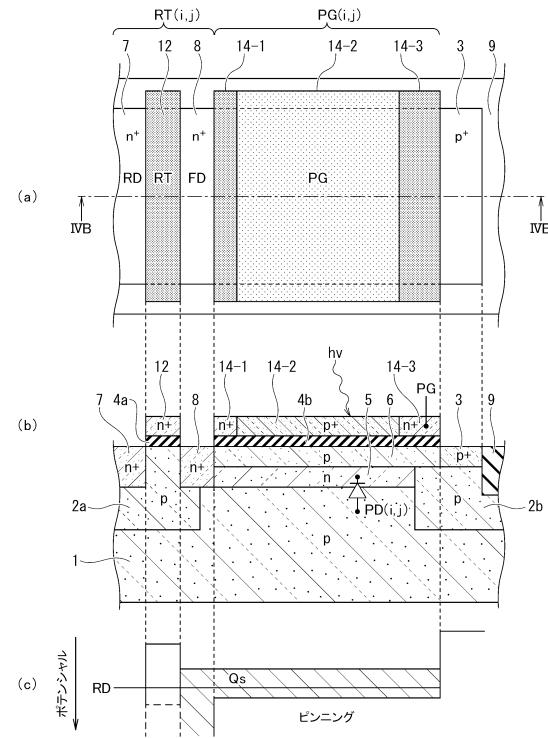

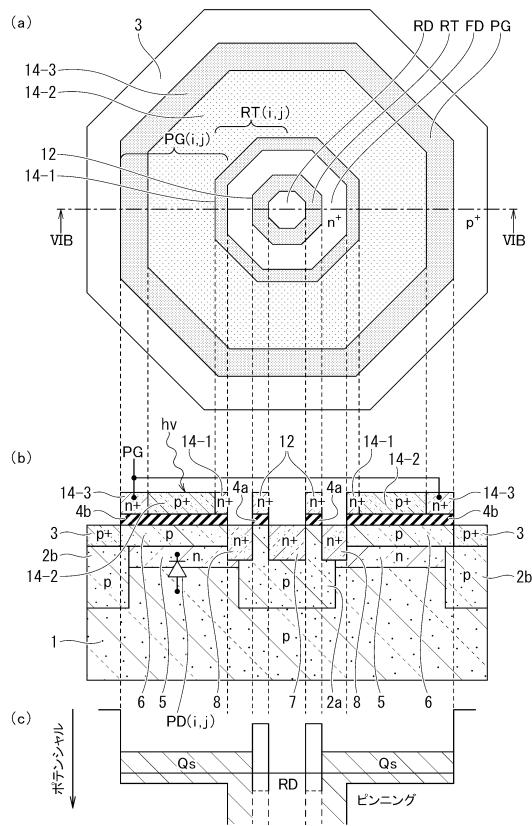

【図 4】図 4 ( a )は第 2 実施形態に係る光検出素子の概略を模式的に説明する平面図であり、図 4 ( b )は図 4 ( a )の IVB - IVB 方向から見た断面図であり、図 4 ( c )は図 4 ( b )方向に沿ったポテンシャル分布である。

【図 5】図 5 ( a )は第 3 実施形態に係る光検出素子の概略を模式的に説明する平面図であり、図 5 ( b )は図 5 ( a )の VB - VB 方向から見た断面図であり、図 5 ( c )は図 5 ( b )方向に沿ったポテンシャル分布である。

10

20

30

40

50

【図6】図6(a)は第4実施形態に係る光検出素子の概略を模式的に説明する平面図であり、図6(b)は図6(a)のV1B-V1B方向から見た断面図であり、図6(c)は図6(b)方向に沿ったポテンシャル分布である。

#### 【発明を実施するための形態】

##### 【0013】

次に、図面を参照して、本発明の第1～第4実施形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参照して判断すべきものである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることは勿論である。

10

##### 【0014】

また、以下に示す第1～第4実施形態は、本発明の技術的思想を具体化するための装置や方法を例示するものであって、本発明の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものではない。例えば、第1～第4実施形態の説明では、フォトゲートがDOPOSから構成される場合を説明するが例示に過ぎない。フォトゲートに用いられる電極材料は、信号電荷生成に用いられる光の波長に対して透明な導電体であり、且つ直下のシールド層に対して仕事関数が規定できる導電体であれば、シリコンを基礎とするDOPOSに限定されるものではない。更に、以下の説明における「左右」や「上下」の方向は、単に説明の便宜上の定義であって、本発明の技術的思想を限定するものではない。よって、例えば、紙面を90度回転すれば「左右」と「上下」とは交換して読みられ、紙面を180度回転すれば「左」が「右」に、「右」が「左」になることは勿論である。単なる便宜上の定義であるので、紙面を180度回転しないで、「左」を「右」に、「右」を「左」に読み替える選択でもよいことも勿論である。

20

##### 【0015】

以下の第1～第4実施形態の説明で、「第1導電型の」及び「第2導電型の」の修飾語の付された部材は、p型若しくはn型の伝導を示す半導体材料からなる部材を意味する。そして、第1～第4実施形態の説明では、第1導電型がp型、第2導電型がn型の場合について例示的に説明するが、単なる導電型の選択に過ぎない。よって、第1導電型をn型、第2導電型をp型と選択しても、ポテンシャルの方向を逆向きにする等の極性に留意すれば、同様な技術的思想が成立しうることは勿論である。また、図面において、n又はpを冠した領域や層が半導体領域や半導体層等の半導体を材料とする部材や構成要素を意味することは、当業者には自明な事項である。また、図面中でnやpに付した+の上付き文字は、+が付記されていない半導体領域に比して、相対的に不純物密度が高い半導体領域であることを意味する。

30

##### 【0016】

###### (第1実施形態)

本発明の第1実施形態に係る固体撮像装置は、図1に示すように、複数のフォトゲート型の画素(ピクセル) $Q_{ij}$ ,  $Q_{(i+1),j}$ ,  $Q_{i,(j+1)}$ ,  $Q_{(i+1),(j+1)}$ が二次元マトリクス状に配列された画素領域と、画素領域の周辺に各種回路を配置した周辺回路領域を備えたフォトゲート型の固体撮像装置である。なお、図1には、二次元マトリクスのレイアウトの一部を代表して $2 \times 2$ 行× $2$ 列のマトリクスを、便宜上抽出して示している。例えば、図1に抽出して例示した $2 \times 2$ マトリクス部分の左上に破線の矩形で示したi行、j列の画素 $Q_{ij}$ は、フォトゲート $P G(i,j)$ と、フォトゲート $P G(i,j)$ に隣接して設けられたフォトダイオード部 $P D(i,j)$ と、フォトダイオード部 $P D(i,j)$ に接続された電荷読出領域 $F D(i,j)$ と、電荷読出領域 $F D(i,j)$ の電位をリセットするリセットトランジスタ $R T(i,j)$ と、電荷読出領域 $F D(i,j)$ の電位変化を增幅する増幅トランジスタ $S F(i,j)$ と、増幅トランジスタ $S F(i,j)$ の出力を選択する選択トランジスタ $S L(i,j)$ を備える。フォトゲート $P G(i,j)$ とフォトダイオード部 $P D(i,j)$ で、画素 $Q_{ij}$ のフォトゲート光電変換部を構成している。図1の等価回路でコンデンサのシンボルマークで示されているように、フォトゲート $P G(i,j)$ は、画素

40

50

$Q_{ij}$  のフォトゲート光電変換部の透明な MOS キャパシタ部分を意味する。

#### 【 0 0 1 7 】

又、図 1 の左下に破線の矩形で示した ( $i + 1$ ) 行、 $j$  列の画素  $Q_{(i+1)j}$  は、フォトゲート  $P G((i+1), j)$  と、フォトゲート  $P G((i+1), j)$  に隣接して設けられたフォトダイオード部  $P D((i+1), j)$  と、フォトダイオード部  $P D((i+1), j)$  に接続された電荷読出領域  $F D((i+1), j)$  と、電荷読出領域  $F D((i+1), j)$  の電位をリセットするリセットトランジスタ  $R T((i+1), j)$  と、電荷読出領域  $F D((i+1), j)$  の電位変化を増幅する増幅トランジスタ  $S F((i+1), j)$  と、増幅トランジスタ  $S F((i+1), j)$  の出力を選択する選択トランジスタ  $S L((i+1), j)$  を備える。フォトゲート  $P G((i+1), j)$  とフォトダイオード部  $P D((i+1), j)$  で、画素  $Q_{(i+1)j}$  のフォトゲート光電変換部を構成している。図 1 の等価回路表示から分かるように、フォトゲート  $P G((i+1), j)$  は、画素  $Q_{(i+1)j}$  のフォトゲート光電変換部の透明な MOS キャパシタ部分に対応する。同様に、図 1 の右上に破線の矩形で示した  $i$  行、( $j + 1$ ) 列の画素  $Q_{i(j+1)}$  は、フォトゲート  $P G(i, (j+1))$  と、フォトゲート  $P G(i, (j+1))$  に隣接して設けられたフォトダイオード部  $P D(i, (j+1))$  と、フォトダイオード部  $P D(i, (j+1))$  に接続された電荷読出領域  $F D(i, (j+1))$  と、電荷読出領域  $F D(i, (j+1))$  の電位をリセットするリセットトランジスタ  $R T(i, (j+1))$  と、電荷読出領域  $F D(i, (j+1))$  の電位変化を増幅する増幅トランジスタ  $S F(i, (j+1))$  と、増幅トランジスタ  $S F(i, (j+1))$  の出力を選択する選択トランジスタ  $S L(i, (j+1))$  を備える。フォトゲート  $P G(i, (j+1))$  とフォトダイオード部  $P D(i, (j+1))$  で、画素  $Q_{i(j+1)}$  のフォトゲート光電変換部を構成している。等価回路表示が示すとおり、フォトゲート  $P G(i, (j+1))$  は、画素  $Q_{i(j+1)}$  のフォトゲート光電変換部の透明な MOS キャパシタ部分に対応する。

10

20

#### 【 0 0 1 8 】

更に、図 1 で便宜上抽出した  $2 \times 2$  マトリクス部分の右下に破線の矩形で示した ( $i + 1$ ) 行、( $j + 1$ ) 列の画素  $Q_{(i+1)(j+1)}$  は、フォトゲート  $P G((i+1), (j+1))$  と、フォトゲート  $P G((i+1), (j+1))$  に隣接して設けられたフォトダイオード部  $P D((i+1), (j+1))$  と、フォトダイオード部  $P D((i+1), (j+1))$  に接続された電荷読出領域  $F D((i+1), (j+1))$  と、電荷読出領域  $F D((i+1), (j+1))$  の電位をリセットするリセットトランジスタ  $R T((i+1), (j+1))$  と、電荷読出領域  $F D((i+1), (j+1))$  の電位変化を増幅する増幅トランジスタ  $S F((i+1), (j+1))$  と、増幅トランジスタ  $S F((i+1), (j+1))$  の出力を選択する選択トランジスタ  $S L((i+1), (j+1))$  を備える。フォトゲート  $P G((i+1), (j+1))$  とフォトダイオード部  $P D((i+1), (j+1))$  で、画素  $Q_{(i+1)(j+1)}$  のフォトゲート光電変換部を構成している。即ち、フォトゲート  $P G((i+1), (j+1))$  は、画素  $Q_{(i+1)(j+1)}$  のフォトゲート光電変換部の透明な MOS キャパシタ部分に対応する。但し、画素領域のマトリクスが  $m$  行  $\times$   $n$  列からなる場合、 $i$  は、 $1 \sim m$  ( $m$  は 2 以上の正の整数) のうちの 1 つであり、 $j$  は、 $1 \sim n$  ( $n$  は 2 以上の正の整数) のうちの 1 つである。例えば、 $m$  として、 $300 \sim 10000$  の範囲内の値、 $n$  として、 $200 \sim 8000$  の範囲内の値が設計仕様に応じて適宜選択される。

30

#### 【 0 0 1 9 】

図 1 で抽出された  $2 \times 2$  マトリクス部分の周辺に着目すると、周辺回路領域は、リセットトランジスタ  $R T(i, j)$ 、 $R T((i+1), j)$ 、 $R T(i, (j+1))$ 、 $R T((i+1), (j+1))$  を駆動するためのリセットトランジスタ走査駆動回路（以下、「 $R T$  走査回路」と称する。）

20 と、選択トランジスタ  $S L(i, j)$ 、 $S L((i+1), j)$ 、 $S L(i, (j+1))$ 、 $S L((i+1), (j+1))$  を駆動するための選択トランジスタ走査駆動回路（以下、「 $S L$  走査回路」と称する。）

30 と、フォトゲート  $P G(i, j)$ 、 $P G((i+1), j)$ 、 $P G(i, (j+1))$ 、 $P G((i+1), (j+1))$  を駆動するためのフォトゲート走査駆動回路（以下、「 $P G$  走査回路」と称する。）

40 を含んでいる。

#### 【 0 0 2 0 】

$m$  行  $\times$   $n$  列からなるマトリクス上においては、マトリクスの  $m$  行に対応して  $m$  本のリセット駆動線  $D R T(i)$  が X 方向に延びてあり、その一端が  $R T$  走査回路 20 に接続されている。リセット駆動線  $D R T(i)$  は、 $m \times n$  マトリクスの  $i$  行に属する  $n$  個の画素  $Q_{i1} \sim Q_{in}$  のリセットトランジスタ  $R T(i, 1) \sim T(i, n)$  のゲートに共通に接続されている。 $R T$  走査回路 20 は、リセット駆動線  $D R T(i)$  を介して、行単位で、即ち、 $i$  行に属する  $n$  個の画素

50

$Q_{i1} \sim Q_{in}$ に対して、リセットトランジスタ  $R T(i,1) \sim R T(i,n)$  のゲートに印加する電圧を制御する。リセットトランジスタ  $R T(i,1) \sim R T(i,n)$  のゲートに印加する電圧としては、高位側電圧  $V(H)$  として、電源電圧  $VDD$  を採用することができ、低位側電圧  $V(L)$  として、接地電圧  $VSS$  を採用することができる。

#### 【0021】

また、 $m \times n$  マトリクス上においては、マトリクスの  $m$  行に対応して  $m$  本の選択駆動線  $D S L(i)$  が  $X$  方向に延びてあり、その一端が  $S L$  走査回路 30 に接続されている。選択駆動線  $D S L(i)$  は、 $m \times n$  マトリクスの  $i$  行に属する  $n$  個の画素  $Q_{i1} \sim Q_{in}$  の選択トランジスタ  $S L(i,1) \sim S L(i,n)$  のゲートに共通に接続されている。 $S L$  走査回路 30 は、選択駆動線  $D S L(i)$  を介して、行単位で、即ち、 $i$  行に属する  $n$  個の画素  $Q_{i1} \sim Q_{in}$  に対して、選択トランジスタ  $S L(i,1) \sim S L(i,n)$  のゲートに印加する電圧を制御する。選択トランジスタ  $S L(i,1) \sim S L(i,n)$  についても、そのゲートに印加する電圧としては、高位側電圧  $V(H)$  として、電源電圧  $VDD$  を採用することができ、低位側電圧  $V(L)$  として、接地電圧  $VSS$  を採用することができる。

#### 【0022】

更に、 $m \times n$  マトリクス上においては、マトリクスの  $m$  行に対応して  $m$  本のフォトゲート駆動線  $D PG(i)$  が  $X$  方向に延びてあり、その一端が  $PG$  走査回路 40 に接続されている。フォトゲート駆動線  $D PG(i)$  は、 $m \times n$  マトリクスの  $i$  行に属する  $n$  個の画素  $Q_{i1} \sim Q_{in}$  のフォトゲート  $PG(i,1) \sim PG(i,n)$  に共通に接続されている。 $PG$  走査回路 40 は、フォトゲート駆動線  $D PG(i)$  を介して、行単位で、即ち、 $i$  行に属する  $n$  個の画素  $Q_{i1} \sim Q_{in}$  に対して、フォトゲート  $PG(i,1) \sim PG(i,n)$  の透明電極に印加する電圧を制御する。フォトゲート  $PG(i,1) \sim PG(i,n)$  についても、その透明電極に印加する電圧としては、高位側電圧  $V(H)$  として、電源電圧  $VDD$  を採用することができ、低位側電圧  $V(L)$  として、接地電圧  $VSS$  を採用することができる。なお、各画素のフォトゲート  $PG(i,j)$  に印加する電圧を  $0V$  ないし正電圧の共通の直流 ( $DC$ ) 電位とすることも可能であり、その場合には  $PG$  走査回路 40 は全行同一の  $DC$  電圧を与える。

#### 【0023】

以下の説明では、図 1 で抽出された  $2 \times 2$  マトリクス部分の左上の  $i$  行、 $j$  列の画素  $Q_{ij}$  に着目して説明する。但し、便宜上、画素  $Q_{ij}$  に関して説明するが、 $2 \times 2$  マトリクスを構成する他の画素  $Q_{(i+1),j}$ ,  $Q_{i,(j+1)}$ ,  $Q_{(i+1),(j+1)}$  や、更には  $m \times n$  マトリクスを構成する他の画素についても、基本的に同一構造であること勿論である。画素  $Q_{ij}$  は、光検出素子 10 と、光検出素子 10 の出力ノードとなる電荷読出領域  $FD(i,j)$  に接続された増幅トランジスタ  $S F(i,j)$  と、増幅トランジスタ  $S F(i,j)$  のソース側にドレイン側が接続された選択トランジスタ  $S L(i,j)$  を含む。選択トランジスタ  $S L(i,j)$  のソース側には  $Y$  方向に延びる出力信号線  $V_{sig(j)}$  が接続されている。フォトダイオード部  $PD(i,j)$  で生成された信号は、電荷読出領域  $FD(i,j)$  を介して増幅トランジスタ  $S F(i,j)$  のゲート信号となる。増幅トランジスタ  $S F(i,j)$  で増幅された信号は選択トランジスタ  $S L(i,j)$  を介して、出力信号線  $V_{sig(j)}$  に導かれ、更に、読出回路 50 に伝達される。読出回路 50 では、フォトダイオード部  $PD(i,j)$  で生成された信号に対して所定の処理が実行され、最終的に半導体チップの外部へ出力される。

#### 【0024】

図 1 の破線の矩形で示した  $i$  行、 $j$  列の画素  $Q_{ij}$  の内部に、別の破線の矩形で示した光検出素子 10 は、電荷生成部として機能するフォトダイオード部  $PD(i,j)$  と、フォトゲート  $PG(i,j)$  と、リセットトランジスタ  $RT(i,j)$  を備える。リセットトランジスタ  $RT(i,j)$  のドレイン側には  $Y$  方向に延びるリセット線  $RD(j)$  が接続され、リセット線  $RD(j)$  には、 $DC$  電圧であるリセットドレイン電圧  $RD$  が印加されている。増幅トランジスタ  $S F(i,j)$  のドレイン側には  $Y$  方向に延びる電源電圧線  $PS(j)$  が接続され、電源電圧線  $PS(j)$  には、 $DC$  電圧である電源電圧 (増幅ドレイン電圧)  $VDD$  が印加されている。図 1 に示すように、フォトゲート  $PG(i,j)$  の下部電極側、リセットトランジスタ  $RT(i,j)$  のソース側、及び増幅トランジスタ  $S F(i,j)$  のゲート側の共通接続点には、フォトダイオード部  $PD(i,j)$

10

20

30

40

50

のカソード側が接続されている。共通接続点は電荷読出領域  $F D(i,j)$  として機能している。

#### 【 0 0 2 5 】

図 1 に示すように、フォトダイオード部  $P D(i,j)$  のアノード側は、例えば、接地 (  $G N D$  ) 点に接続されている。フォトゲート  $P G(i,j)$  は、入射光  $h$  に対して透明な M O S キヤパシタ構造を有する。また、光検出素子 10 の平面レイアウトは、図 2 ( a ) に示すように、フォトゲート  $P G(i,j)$  とリセットトランジスタ  $R T(i,j)$  とが横並びに配置されたものとなる。リセットトランジスタ  $R T(i,j)$  のリセットゲート  $R T$  の一方側 ( 右側 ) 、即ち、透明電極であるフォトゲート  $P G(i,j)$  が配置されている側には、図 2 ( a ) の平面図に「  $F D$  」と表示した電荷読出領域 ( 電荷検出部 ) 8 が配置されている。図 2 ( a ) において、リセットゲート  $R T$  の他方側 ( 左側 ) には、 $R D$  で示したリセットドレイン領域 7 が配置されている。10

#### 【 0 0 2 6 】

図 2 ( a ) 及び ( b ) に示すように、第 1 導電型 (  $p$  型 ) の基体領域 1 と、基体領域 1 の上部に埋め込まれた第 2 導電型 (  $n$  型 ) の電荷生成埋込層 5 は、 $p - n$  接合によりフォトダイオード部  $P D(i,j)$  を構成する。フォトゲート  $P G(i,j)$  の透明電極を透過してフォトダイオード部  $P D(i,j)$  に光  $h$  が入射することにより、フォトダイオード部  $P D(i,j)$  は信号電荷を生成する。また、電荷生成埋込層 5 の上面には、基体領域 1 よりも高不純物密度の  $p$  型のシールド層 6 が設けられている。シールド層 6 は、フォトゲート型の構造以外の光検出素子では「仮想電極」と呼ばれることがある。更に、シールド層 6 の上面には、フォトゲート絶縁膜 ( 第 1 ゲート絶縁膜 ) 4 b と共に M O S キヤパシタを構成する透明電極であるフォトゲート  $P G(i,j)$  が設けられている。図 2 ( b ) に示すように、リセットドレイン領域 7 、電荷読出領域 8 、電荷生成埋込層 5 、シールド層 6 及び接続領域 3 は、素子分離絶縁膜 9 によって額縁状に囲まれた活性領域の内部に収納されている。20

#### 【 0 0 2 7 】

素子分離絶縁膜 9 は、例えば浅溝分離 ( S T I ) 構造によって、例えばシリコン酸化膜等で構成することが可能である。更に、図 2 ( b ) において、基体領域 1 よりも高不純物密度で第 1 導電型のウェル領域 2 a 及び素子分離埋込領域 2 b が、基体領域 1 の上部の両側にそれぞれ埋め込まれている。製造工程を鑑みると、ウェル領域 2 a と同一の深さ、同一不純物密度で素子分離埋込領域 2 b が設けるのが好ましい。素子分離絶縁膜 9 と素子分離絶縁膜 9 の下を埋め込む素子分離埋込領域 2 b によって素子分離領域 ( 画素分離領域 ) が構成されている。素子分離絶縁膜 9 によって囲まれた活性領域の内部において、リセットトランジスタ  $R T(i,j)$  が、左側のウェル領域 2 a を用いて構成されている ( 図 2 ( a ) の表面図の表現ではリセットトランジスタ  $R T(i,j)$  のゲート部分を「  $R T$  」と表示している。 )。30

#### 【 0 0 2 8 】

活性領域の範囲を規定する素子分離絶縁膜 9 は、基体領域 1 の右側に配置された素子分離埋込領域 2 b の上部の一部に埋め込まれている。また、素子分離埋込領域 2 b よりも高不純物密度の  $p^+$  型の接続領域 3 が、素子分離埋込領域 2 b の上部の他の一部に素子分離絶縁膜 9 に接して設けられている。シールド層 6 は、右側の端部を素子分離埋込領域 2 b の上部で接続領域 3 に接され、左側の端部が電荷読出領域 8 に接続されるように、素子分離絶縁膜 9 で周辺を定義された活性領域の内部に配置されている。シールド層 6 の右側の端部は接続領域 3 を介して素子分離埋込領域 2 b に電気的に接続される。この結果、シールド層 6 の端部は接続領域 3 を介して基体領域 1 に電気的に短絡されて接地電位となる。40

#### 【 0 0 2 9 】

リセットトランジスタ  $R T(i,j)$  は、図 2 ( a ) 及び ( b ) に示すように、電荷生成埋込層 5 よりも高不純物密度で  $n^+$  型の電荷読出領域 ( リセットソース領域 ) 8 と、電荷生成埋込層 5 よりも高不純物密度で  $n^+$  型のリセットドレイン領域 7 を備えている。更にリセットトランジスタ  $R T(i,j)$  は、電荷読出領域 8 とリセットドレイン領域 7 の間のチャネル領域として機能するウェル領域 2 a の上面にリセットゲート絶縁膜 ( 第 2 ゲート絶縁膜 ) 4 a を接し、絶縁膜・半導体界面を構成している。そして、リセットトランジスタ  $R T(i,j)$ 50

)は、リセットゲート絶縁膜 4 a の上に、第 2 導電型 ( $n^+$  型) の D O P O S からなるリセットゲート電極 1 2 を備えている。図 2 ( b ) の例示的表現では、電荷読出領域 8 は、電荷生成埋込層 5 の端部の左側端部及びシールド層 6 の左側端部に接するように、活性領域の内部のウェル領域 2 a の上部及び基体領域 1 の上部に埋め込まれている。フォトゲート PG(i,j) は、リセットトランジスタ R T(i,j) の電荷読出領域 8 側の端部に割り当てられた緩和領域部 1 4 - 1 と、電荷読出領域 8 側の反対側の接続領域 3 側に設けられた主透明電極層 1 4 - 2 の 2 つの領域に分割されている。連続した 2 つの領域に透明電極が分割されることにより、半導体界面の方向に沿って非一様に分布する静電ポテンシャルを生成する効果を奏している。緩和領域部 1 4 - 1 及び主透明電極層 1 4 - 2 のいずれも、入射光 h に対して透明な半導体電極であり、シールド層 6 に対して互いに異なる仕事関数の差を有している。

### 【 0 0 3 0 】

第 1 実施形態に係る固体撮像装置では、半導体透明電極である緩和領域部 1 4 - 1 は、リセットトランジスタ R T(i,j) のリセットゲート電極 1 2 と同じ第 2 導電型 ( $n^+$  型) の不純物元素を含む。一方、半導体透明電極である主透明電極層 1 4 - 2 は、リセットトランジスタ R T(i,j) のリセットゲート電極 1 2 と逆の第 1 導電型 ( $p^+$  型) の不純物元素が添加されている。主透明電極層 1 4 - 2 は、透明電極であるフォトゲート PG(i,j) の主要部分を占め、その平面パターンで定義される面積 ( サイズ ) は、図 2 ( a ) の平面パターンから分かるように緩和領域部 1 4 - 1 の面積よりも大きい。

### 【 0 0 3 1 】

第 1 実施形態に係る光検出素子において、主透明電極層 1 4 - 2 の平面パターンの面積を、緩和領域部 1 4 - 1 の面積よりも大きく設定する理由を、フォトゲート PG(i,j) の透明電極が一様な  $n^+$  D O P O S から構成される場合と一様な  $p^+$  D O P O S から構成される場合に分けて説明する。但し、フォトゲート PG(i,j) の電位 V ( PG ) は、基体領域 1 の電位 ( 基板電位 ) と同じ 0 V とする。図 3 ( a ) は、フォトゲート PG(i,j) の透明電極が一様な透明な n 型半導体層である場合のフォトゲート光電変換部の伝導帯のバンド端 E<sub>c</sub> 及び価電子帯のバンド端 E<sub>v</sub> の深さ方向のプロファイルを示す。一方、図 3 ( b ) は、フォトゲート PG(i,j) の透明電極が一様な透明な p 型半導体層である場合のフォトゲート光電変換部の伝導帯のバンド端 E<sub>c</sub> 及び価電子帯のバンド端 E<sub>v</sub> の深さ方向のプロファイルを示す。図 3 ( a ) 及び ( b ) において、バンド中央の一点鎖線で示した曲線は、バンド中間点に位置する真性フェルミ準位 E<sub>f</sub> の深さ方向のプロファイルを示す。この時、図 3 ( a ) 及び ( b ) に示すように、いずれの場合も、伝導帯のバンド端 E<sub>c</sub> 、価電子帯のバンド端 E<sub>v</sub> 及び真性フェルミ準位 E<sub>f</sub> を示す曲線が、電荷生成埋込層 5 を意味する n 層のところで下に凸となる p - n - p フック構造をなしている。

### 【 0 0 3 2 】

図 3 ( a ) 及び ( b ) において、下に凸となる曲線でプロファイルを示した中央の n 層の右側に示した p 層 ( p 基板 ) は基体領域 1 を意味し、n 层の左側に示した p 層は、シールド層 6 を意味している。シールド層 6 の更に左の平行四辺形はフォトゲート絶縁膜 4 b のバンド構造を示し、フォトゲート絶縁膜 4 b の更に左には、フォトゲート PG(i,j) の伝導帯のバンド端 E<sub>c</sub> 及び価電子帯のバンド端 E<sub>v</sub> を示している。図 3 ( a ) 及び ( b ) のいずれの場合も、n 层 ( 電荷生成埋込層 ) の伝導帯のバンド端 E<sub>c</sub> を示す曲線が、フェルミレベル E<sub>f</sub> = 0 V よりも下に位置して空乏化していることを示している。又、図 3 ( a ) 及び ( b ) のいずれの場合も、p 層 ( シールド層 ) の価電子帯のバンド端 E<sub>v</sub> を示す曲線がフェルミレベル E<sub>f</sub> = 0 V に近い位置に存在して中性化、即ち 0 V にピンニングしている。

### 【 0 0 3 3 】

しかし、図 3 ( a ) に示すように、フォトゲート PG(i,j) の透明電極が一様な  $n^+$  D O P O S で構成される場合には、シールド層 6 の伝導帯のバンド端 E<sub>c</sub> 及び価電子帯のバンド端 E<sub>v</sub> が、平行四辺形で示したフォトゲート絶縁膜 4 b との半導体界面において、下向きに曲がっている。即ち、フォトゲート PG(i,j) の透明電極が n 型の場合は、シールド層 6 のフォトゲート PG(i,j) 側の半導体界面が僅かに空乏化する。図 3 ( a ) において、フォトゲート PG(i,j) の透明電極が一様な  $p^+$  D O P O S で構成される場合には、シールド層 6 の伝導帯のバンド端 E<sub>c</sub> 及び価電子帯のバンド端 E<sub>v</sub> が、平行四辺形で示したフォトゲート絶縁膜 4 b との半導体界面において、下向きに曲がっていない。

トゲート絶縁膜 4 b のバンド構造の左側には  $n^+ DOPOS$  の伝導帯のバンド端  $E_c$  が  $V(PG) = 0V$  に近づくことが示されている。 $n^+ DOPOS$  でフォトゲート  $PG(i,j)$  が構成される場合には、フォトゲート  $PG(i,j)$  側の真性フェルミ準位  $E_i$  とシールド層 6 の真性フェルミ準位  $E_i$  に差が生じて、フォトゲート  $PG(i,j)$  の仕事関数とシールド層 6 の仕事関数の間に差があるからである。

#### 【 0 0 3 4 】

他方、フォトゲート  $PG(i,j)$  の透明電極が一様な  $p^+ DOPOS$  から構成される場合には、図 3 ( b ) に示すように、シールド層 6 の伝導帯のバンド端  $E_c$  及び価電子帯のバンド端  $E_v$  が、平行四辺形で示したフォトゲート絶縁膜 4 b に向かって平坦なフラットバンドのプロファイルを維持している。図 3 ( b ) において、フォトゲート絶縁膜 4 b のバンド構造の左側には  $p^+ DOPOS$  の価電子帯のバンド端  $E_v$  が  $V(PG) = 0V$  に近づくことが示されている。 $p^+ DOPOS$  でフォトゲート  $PG(i,j)$  が構成される場合には、フォトゲート  $PG(i,j)$  側の真性フェルミ準位  $E_i$  とシールド層 6 の真性フェルミ準位  $E_i$  は、ほぼ同じレベルに出来るので、フォトゲート  $PG(i,j)$  の仕事関数とシールド層 6 の仕事関数の間の差は殆どない。更に  $p^+ DOPOS$  の不純物密度がシールド  $p$  層 6 の不純物密度より高密度であれば、シールド層 6 の真性フェルミ準位  $E_i$  の界面がやや上向きに引っ張られ、より一層ピンニング効果が高まる。

10

#### 【 0 0 3 5 】

即ち、大きな仕事関数の差を伴うことなく、シールド層 6 の伝導帯のバンド端  $E_c$  及び価電子帯のバンド端  $E_v$  が、深さ方向のフラットバンドのプロファイルを維持したまま、 $p-n-p$  フック構造の負方向に引っ張られるので、半導体界面には空乏化が生じない。図 3 ( b ) に示すような深さ方向の伝導帯のバンド端  $E_c$  及び価電子帯のバンド端  $E_v$  が平坦なポテンシャル分布の形状では、シールド層 6 の半導体界面がシールド層 6 の多数キャリアである正孔 ( $p$  型電荷) で埋められて強くピンニングしている。ピンニングされる正孔は、信号電荷である電子 ( $n$  型電荷) とは逆極性の電荷である。

20

#### 【 0 0 3 6 】

したがって、シールド層 6 のフォトゲート  $PG(i,j)$  側の半導体界面における暗電流の発生については、半導体界面が多量の正孔で埋められるため不活性化されることを考慮すれば、フォトゲート  $PG(i,j)$  の透明電極が一様な  $p^+ DOPOS$  から構成される場合のほうが、フォトゲート  $PG(i,j)$  の透明電極が一様な  $n^+ DOPOS$  から構成される場合よりも抑えられることが分かる。半導体界面がシールド層 6 の多数キャリアである正孔 ( $p$  型電荷) でピンニングされることは、放射線耐性に関しても、フォトゲート  $PG(i,j)$  の透明電極が一様な  $p^+ DOPOS$  から構成される場合のほうが、フォトゲート  $PG(i,j)$  の透明電極が一様な  $n^+ DOPOS$  から構成される場合よりも有利に働くことを意味する。なお、 $n$  層である電荷生成埋込層 5 に形成されるチャネル電位については、フォトゲート  $PG(i,j)$  の透明電極が一様な  $p^+ DOPOS$  から構成される場合、及び一様な  $n^+ DOPOS$  から構成される場合のいずれであっても、 $p$  層であるシールド層 6 が  $0V$  にピンニングした状態を保持しているので、変わらない。

30

#### 【 0 0 3 7 】

以上の結果を考慮すると、図 2 ( a ) 及び ( b ) に示すように、入射光  $h$  に対して透明な半導体電極であるフォトゲート  $PG(i,j)$  の主透明電極層 14 - 2 を  $p$  型とし、リセットトランジスタ  $RT(i,j)$  の電荷読出領域 8 側の緩和領域部 14 - 1 を  $n$  型とする構造は、面積を大きく設定した主透明電極層 14 - 2 における暗電流の発生を抑制するという効果の面で非常に優れたものとなる。また、暗電流抑制効果のみを考えると、透明電極であるフォトゲート  $PG(i,j)$  のすべてを一様な  $p$  型にすればよいとも考えられるが、透明電極のすべてを一様な  $p$  型として場合、図 3 ( b ) から明らかなように、フォトゲート  $PG(i,j)$  の電荷読出領域 8 側の端部において、シールド層 6 のフォトゲート  $PG(i,j)$  側の界面電位が強くピンニングする結果、一様なフォトゲート  $PG(i,j)$  と電荷読出領域 8 の間の電界集中を招き望ましくない。したがって、フォトゲート  $PG(i,j)$  を分割し、面積を大きく設定した主透明電極層 14 - 2 を  $p$  型とし、リセットトランジスタ  $RT(i,j)$  の電荷読出領域 8

40

50

側の緩和領域部 14 - 1 を n 型とする非一様な構造が最も理想的なものとなる。フォトゲート PG(i,j) の領域を複数の領域に分割してシールド層 6 に対して互いに異なる仕事関数の差をそれぞれ発生させ、半導体界面の方向に沿って非一様に分布する静電ポテンシャルを生成する効果を奏するという技術的特徴は、以下に述べる第 2 ~ 第 4 実施形態に係る光検出器においても同様である。

#### 【 0 0 3 8 】

図 2 ( b ) に示した断面の方向に沿ったポテンシャル分布を、図 2 ( c ) に示す。図 2 ( c ) に示すように、リセットドレイン領域 7 の電位であるリセットドレイン電圧 RD を、電荷生成埋込層 5 の空乏化電位より低い値に設定することにより、光電変換により発生した電荷を、電荷生成埋込層 5 及び電荷読出領域 8 に蓄積することができる。リセットドレイン電圧 RD を空乏化電位より低くすることにより、信号電荷蓄積領域としての電荷生成埋込層 5 及び電荷読出領域 8 の電荷蓄積面積が電荷量 Qs によらず一定に保たれ、電荷電圧変換ゲインを一定にすることができるという効果が得られる。なお、上述したように、電荷生成埋込層 5 に形成されるチャネル電位については、フォトゲート PG(i,j) の透明電極が p 型であっても、n 型であっても、シールド層 6 が 0 V にピンニングした状態を保持しているので、変わることはなく等電位に保たれる。

10

#### 【 0 0 3 9 】

第 1 実施形態に係るフォトゲート型の光検出素子において、フォトゲート PG(i,j) は、フォトゲート PG(i,j) に入射する光  $h\nu$  の波長に対して透明な材料から選択することができる。例えば、フォトゲート PG(i,j) を燐 (P)、砒素 (As) 等の n 型の不純物元素がドープされた DOPOS から構成した場合、フォトゲート PG(i,j) と電荷読出領域 8 の位置合わせを自己整合的に行うことができるので、製造プロセス上便利となる。フォトゲート PG(i,j) は、DOPOS 等の入射光  $h\nu$  の波長に対して透明な半導体の多結晶膜以外にも、酸化錫 ( $SnO_2$ ) でもよい。但し、錫 (Sn) 等を添加した酸化インジウム (ITO) は、Sn がドナーとして働くので n 型になる。酸化錫は化学量論的組成に依存し、 $SnO_2$  は n 型、 $SnO$  は p 型である。アルミニウム (Al) を添加した酸化亜鉛 (AZO)、ガリウム (Ga) を添加した酸化亜鉛 (GZO)、インジウム (In) を添加した酸化亜鉛 (IZO) 等の酸化物薄膜 (透明導電性酸化物) 等も化学量論的組成に依存するが、一般に n 型半導体透明導電体である。

20

#### 【 0 0 4 0 】

p 型の透明導電体材料としては、ボロン (B) 等の p 型の不純物元素がドープされた DOPOS から構成するのが一般的であるが、シリコン以外に、酸化ニッケル (NiO)、酸化イリジウム (IrO) 等が例示できる。更に、銅酸化アルミニウム (CuAlO<sub>2</sub>)、銅酸化ガリウム (CuGaO<sub>2</sub>)、銅酸化インジウム (CuInO<sub>2</sub>) 等の CuMeO<sub>2</sub> デラフオサイト (Delafoseite) 構造を持つデラフオサイト型酸化物でもよい。CuFeO<sub>2</sub> : デラフオサイトは、Cu<sup>+</sup> と FeO<sub>2</sub><sup>-</sup> が c 軸に垂直な 2 次元平面を構成し、これらが交互に積層した構造となっている。又、酸化銅ストロンチウム (SrCu<sub>2</sub>O<sub>2</sub>)、硫酸化銅ランタン (LaCuO<sub>3</sub>) 等でもよい。「層状オキシカルコゲナイト : LnCuO<sub>n</sub>」は、Ln = ランタニド、Ch = カルコゲナイト、Ln 層と CuCh 層が c 軸に交互に積層されたものである。

30

#### 【 0 0 4 1 】

リセットゲート電極 12 についても、n<sup>+</sup> DOPOS から構成することにより、リセットゲート電極 12 と電荷読出領域 8 の位置合わせ、及びリセットゲート電極 12 とリセットドレイン領域 7 の位置合わせを自己整合的に行うことができるので、製造プロセス上便利となる。但し、フォトゲート PG(i,j) と同様に、リセットゲート電極 12 についても、i) 酸化錫 ( $SnO_2$ )、錫 (Sn) 等を添加した酸化インジウム (ITO)、ii) アルミニウム (Al) を添加した酸化亜鉛 (AZO)、iii) ガリウム (Ga) を添加した酸化亜鉛 (GZO)、iv) インジウム (In) を添加した酸化亜鉛 (IZO) 等の酸化物薄膜 (透明導電性酸化物) から構成してもよい。

40

#### 【 0 0 4 2 】

50

フォトゲート絶縁膜4b及びリセットゲート絶縁膜4aとしては、単なるMOSトランジスタの場合のように、シリコン酸化膜に限定されるものではない。即ち、フォトゲート絶縁膜4b及びリセットゲート絶縁膜4aとしては、シリコン酸化膜の他、ストロンチウム酸化物(SrO)膜、シリコン窒化物(Si<sub>3</sub>N<sub>4</sub>)膜、アルミニウム酸化物(Al<sub>2</sub>O<sub>3</sub>)膜、マグネシウム酸化物(MgO)膜、イットリウム酸化物(Y<sub>2</sub>O<sub>3</sub>)膜、ハフニウム酸化物(HfO<sub>2</sub>)膜、ジルコニア酸化物(ZrO<sub>2</sub>)膜、タンタル酸化物(Ta<sub>2</sub>O<sub>5</sub>)膜、ビスマス酸化物(Bi<sub>2</sub>O<sub>3</sub>)膜のいずれか1つの単層膜、或いはこれらの複数を積層した複合膜等を使用して、MISトランジスタを構成してもよい。但し、これらフォトゲート絶縁膜4b及びリセットゲート絶縁膜4aの材料としては、放射線に対して耐性があることが前提となる。

10

#### 【0043】

図3(a)及び(b)では、基体領域1として、p型の半導体基板(Si基板)を用いる場合を例示しているが、半導体基板の代わりに、i) p型の半導体基板上に、半導体基板よりも低不純物密度のp型のエピタキシャル成長層を形成して、エピタキシャル成長層を基体領域1として採用してもよく、ii) n型の半導体基板上に、n型のエピタキシャル成長層を形成して、エピタキシャル成長層を基体領域1として採用してもよく、iii) SOI構造のp型の半導体層(SOI層)を基体領域1として採用してもよい。

#### 【0044】

第1実施形態に係るフォトゲート型固体撮像装置の各画素Q<sub>ij</sub>においては、電荷蓄積期間にフォトゲート光電変換部の光電変換により発生した信号電荷が、出力信号線V<sub>sig(j)</sub>を介して読出回路50に読み出される。出力信号線V<sub>sig(j)</sub>を介して読み出す時、透明電極であるフォトゲートPG(i,j)に0V近傍の一定値(DC値)であるフォトゲート電圧V<sub>PG</sub>を印加することにより、フォトゲートPG(i,j)のフォトゲート絶縁膜4bの直下のシールド層6の多数キャリアである正孔(ホール)でシールド層6の表面電位をピンニングすることができる。なお、緩和領域部14-1の直下のシールド層6の半導体界面部分と、主透明電極層14-2の直下のシールド層6の半導体界面部分でピンニングの状態が界面方向に沿って非一様に変化していることは、既に、図3(a)及び(b)で説明した通りである。

20

#### 【0045】

第1実施形態に係る光検出素子によれば、X線やガンマ線等のイオン化放射線が照射されても、電荷生成埋込層5上のフォトゲート絶縁膜4bは4nm~10nm程度と薄いため、フォトゲート絶縁膜4b中に発生する電子正孔対は僅かである。従って、シールド層6の表面電位をピンニングすることによる暗電流の抑制効果と合わせて、耐放射線性能を向上させることができる。しかも、第1実施形態に係る光検出素子は、フォトゲートPG(i,j)の透明電極の主要部分をp型の主透明電極層14-2とし、リセットトランジスタRT(i,j)の電荷読出領域8側の端部をn型の緩和領域部14-1としている。よって、第1実施形態に係る光検出素子によれば、フォトゲートPG(i,j)と電荷読出領域8の間の電界集中を緩和しつつ、面積を大きく設定した主透明電極層14-2の直下のシールド層6の半導体界面の空乏化を抑え、暗電流抑圧を完全なものできる。したがって、第1実施形態に係る光検出素子を画素とした第1実施形態に係る固体撮像装置によれば、放射線環境下でも高感度かつ広ダイナミックレンジな撮像が可能になる。

30

#### 【0046】

##### (第2実施形態)

本発明の第2実施形態に係る固体撮像装置についても、回路構成としては第1実施形態と基本的に同じである。即ち、第2実施形態に係る固体撮像装置は、図1に例示した構成と同様に、複数のフォトゲート型の画素Q<sub>ij</sub>が二次元マトリクス状に配列された画素領域と、画素領域の周辺に配置され、RT走査回路20、SL走査回路30、及びPG走査回路40を含む周辺回路を備えている。第2実施形態に係る固体撮像装置の画素領域の内部の回路構成については、第1実施形態と同じであるので、重複する説明を省略し、二次元マトリクスを構成する画素である光検出素子の構造に注目して説明する。

40

50

### 【 0 0 4 7 】

第2実施形態に係る光検出素子が、第1実施形態で説明した光検出素子10と異なる点は、光検出素子内の入射光 $h$ に対して透明な半導体電極であるフォトゲート $P G(i,j)$ の構造にある。光検出素子は、図4(a)及び(b)に示すように、電荷生成部として機能するフォトダイオード部 $P D(i,j)$ と、フォトゲート $P G(i,j)$ と、リセットトランジスタ $R T(i,j)$ を備える。図4(a)に示す平面パターンにおいて、フォトゲート $P G(i,j)$ とリセットトランジスタ $R T(i,j)$ は横並びに配置されている。リセットトランジスタ $R T(i,j)$ のリセットゲート $R T$ を示す帯状のパターンの一方側(右側)、即ち、透明電極であるフォトゲート $P G(i,j)$ 側には、FDで示した電荷読出領域(電荷検出部)8が配置され、リセットゲート $R T$ の他方側(左側)にはRDで示したリセットドレイン領域7が配置されている。

10

### 【 0 0 4 8 】

図4(b)に示すように、第1導電型(p型)の基体領域1と基体領域1の上部に埋め込まれた第2導電型(n型)の電荷生成埋込層5は、p-n接合によりフォトダイオード部 $P D(i,j)$ を構成する。フォトゲート $P G(i,j)$ の透明電極を透過してフォトダイオード部 $P D(i,j)$ に光 $h$ が入射することにより、フォトダイオード部 $P D(i,j)$ は信号電荷を生成する。図4(a)に示した電荷読出領域FDは、基体領域1の内部においてフォトダイオード部 $P D(i,j)$ を構成する第2導電型(n型)の電荷生成埋込層5に接続されている。また、電荷生成埋込層5の上面には、基体領域1よりも高不純物密度のp型のシールド層6が設けられている。

20

### 【 0 0 4 9 】

そして、シールド層6の上面にフォトゲート絶縁膜(第1ゲート絶縁膜)4bが接して設けられることにより、シールド層6と絶縁膜・半導体界面が構成されている。そして、フォトゲート絶縁膜4bの上には入射光 $h$ に対して透明な半導体電極であるフォトゲート $P G(i,j)$ が設けられている。図4(a)に示すように、リセットドレイン領域7、電荷読出領域8、電荷生成埋込層5及び接続領域3は、素子分離絶縁膜9によって額縁状に囲まれた活性領域の敷地内に配置されている。図4(b)を見れば、シールド層6及び電荷生成埋込層5も、素子分離絶縁膜9によって周辺が定義された活性領域内に配置されていることが分かる。素子分離絶縁膜9は、例えばSTI構造によって、シリコン酸化膜等で構成することが可能である。

30

### 【 0 0 5 0 】

更に、図4(b)において、基体領域1よりも高不純物密度で第1導電型のウェル領域2a及び素子分離埋込領域2bが、基体領域1の上部の両側の位置にそれぞれ埋め込まれている。製造工程を鑑みると、ウェル領域2aと同一の深さ、同一不純物密度で素子分離埋込領域2bを設けて構わない。素子分離絶縁膜9と素子分離絶縁膜9の下を埋め込む素子分離埋込領域2bによって素子分離領域(画素分離領域)が構成される。

### 【 0 0 5 1 】

リセットトランジスタ $R T(i,j)$ は、左側のウェル領域2a内に設けられている。活性領域の範囲を規定する素子分離絶縁膜9は、基体領域1の右側に配置された素子分離埋込領域2bの上部の一部に埋め込まれている。また、素子分離埋込領域2bよりも高不純物密度のp<sup>+</sup>型の接続領域3が、素子分離埋込領域2bの上部の他の一部に素子分離絶縁膜9に接して設けられている。よって、接続領域3も活性領域の内部に位置する。シールド層6も、活性領域の内部に位置するように、素子分離埋込領域2bの上部において接続領域3に接して設けられている。シールド層6の右側の端部が接続領域3を介して素子分離埋込領域2bに電気的に接続されるので、シールド層6は接続領域3を介して基体領域1に電気的に短絡されて接地電位となる。

40

### 【 0 0 5 2 】

リセットトランジスタ $R T(i,j)$ は、電荷生成埋込層5よりも高不純物密度のn<sup>+</sup>型の電荷読出領域8をリセットソース領域として備え、更に電荷生成埋込層5よりも高不純物密度のn<sup>+</sup>型のリセットドレイン領域7を備えている。更にリセットトランジスタ $R T(i,j)$

50

は、電荷読出領域 8 とリセットドレイン領域 7 の間のチャネル領域として機能するウェル領域 2 a の上面にリセットゲート絶縁膜（第 2 ゲート絶縁膜）4 a を接し、絶縁膜・半導体界面を構成している。そして、リセットゲート絶縁膜 4 a の上には第 2 導電型（n<sup>+</sup>型）の D O P O S からなるリセットゲート電極 1 2 を備えている。電荷読出領域 8 は、電荷生成埋込層 5 の端部及びシールド層 6 の端部に接するように、ウェル領域 2 a の上部の一部と基体領域 1 の上部の一部に埋め込まれている。

#### 【 0 0 5 3 】

10 フォトゲート P G(i,j) の透明電極は、リセットトランジスタ R T(i,j) の電荷読出領域 8 側となる左側端部に割り当てられた緩和領域部 1 4 - 1 と、接続領域 3 側となる右側端部に割り当てられた抵抗増大部 1 4 - 3 と、緩和領域部 1 4 - 1 と抵抗増大部 1 4 - 3 間に設けられた主透明電極層 1 4 - 2 の 3 つの領域に分割されている。連続した 3 つの領域に透明電極が分割されることにより、半導体界面の方向に沿って非一様に分布する静電ポテンシャルを生成する効果を奏している。図 4 ( a ) に示す平面パターンにおいては、左側の緩和領域部 1 4 - 1 と右側の抵抗増大部 1 4 - 3 は、互いに平行に対向する帯状のパターンとなっている。

#### 【 0 0 5 4 】

20 第 2 実施形態に係る光検出器では、半導体透明電極である緩和領域部 1 4 - 1 及び抵抗増大部 1 4 - 3 は、リセットトランジスタ R T(i,j) のリセットゲート電極 1 2 と同じ第 2 導電型（n<sup>+</sup>型）の不純物元素が添加された D O P O S である。一方、半導体透明電極である主透明電極層 1 4 - 2 は、リセットゲート電極 1 2 と逆の第 1 導電型（p<sup>+</sup>型）の不純物元素が添加された D O P O S である。このため、抵抗増大部 1 4 - 3 と主透明電極層 1 4 - 2 の間、及び主透明電極層 1 4 - 2 と緩和領域部 1 4 - 1 の間にそれぞれ p-n 接合が構成される。また、主透明電極層 1 4 - 2 は、透明電極であるフォトゲート P G(i,j) の主要部分を占め、その平面パターンで定義される面積（サイズ）は、緩和領域部 1 4 - 1 の面積及び抵抗増大部 1 4 - 3 の面積よりも大きい。また、透明電極であるフォトゲート P G(i,j) に印加する電圧は、抵抗増大部 1 4 - 3 を入力端とし、抵抗増大部 1 4 - 3 から主透明電極層 1 4 - 2 を経由して緩和領域部 1 4 - 1 に供給される。

#### 【 0 0 5 5 】

30 主透明電極層 1 4 - 2 を第 1 導電型（p<sup>+</sup>型）としているので、シールド層 6 の半導体表面（半導体界面）との間の仕事関数差により、シールド層 6 の半導体表面がより強く、シールド層 6 の多数キャリアである正孔でピニングされることは第 1 実施形態に係る光検出器と同様である。ピンニングされる正孔（p 型電荷）は、信号電荷である電子（n 型電荷）とは逆極性の電荷である。半導体表面（半導体界面）の正孔が強くピンニングされるので、第 2 実施形態に係る光検出器を画素として固体撮像装置を構成すれば、半導体界面を多量の正孔で埋めて不活性化して暗電流の抑圧を完全化でき、放射線環境下でも高感度かつ広ダイナミックレンジな撮像が可能となる。また、緩和領域部 1 4 - 1 を第 2 導電型（n<sup>+</sup>型）とすることにより、フォトゲート P G(i,j) と電荷読出領域 8 の間の電界集中を緩和することが可能となる。更に、第 2 導電型（n<sup>+</sup>型）の抵抗増大部 1 4 - 3 を、フォトゲート P G(i,j) に印加する電圧を与える入力端とすることで、抵抗増大部 1 4 - 3 から緩和領域部 1 4 - 1 までには 2 つの p-n 接合が存在し、抵抗増大部 1 4 - 3 から緩和領域部 1 4 - 1 までの電気経路の抵抗が大きくなる。抵抗増大部 1 4 - 3 から主透明電極層 1 4 - 2 を経て緩和領域部 1 4 - 1 までの電気経路の抵抗が増大することにより、フォトゲート P G(i,j) と電荷読出領域 8 の間の電界集中を更に緩和することができる。

#### 【 0 0 5 6 】

40 図 4 ( b ) に示した断面の方向に沿ったポテンシャル分布を、図 4 ( c ) に示す。第 2 実施形態に係る光検出器では、リセットドレイン領域 7 の電位であるリセットドレイン電圧 R D を電荷生成埋込層 5 の空乏化電位より低い値に設定し、光電変換により発生した電荷を電荷生成埋込層 5 及び電荷読出領域 8 に蓄積する。リセットドレイン電圧 R D を電荷生成埋込層 5 の空乏化電位より低い値に設定することにより、信号電荷蓄積領域としての電荷生成埋込層 5 及び電荷読出領域 8 の電荷蓄積面積が電荷量 Q s によらず一定に保たれ、

電荷電圧変換ゲインを一定にすることができるという効果が得られる。なお、電荷生成埋込層5に形成されるチャネル電位については、フォトゲートPG(i,j)の透明電極がp型であっても、n型であっても、シールド層6が0Vにピンニングした状態を保持しているので、変わることはなく等電位に保たれる。

#### 【0057】

第2実施形態に係る光検出器においても、X線やガンマ線等のイオン化放射線が照射されても、電荷生成埋込層5上のフォトゲート絶縁膜4bは4nm~10nm程度と薄いため、フォトゲート絶縁膜4b中に発生する電子正孔対は僅かである。従って、シールド層6の表面電位をピンニングすることによる暗電流の抑制効果と合わせて、耐放射線性能を向上させることができる。しかも、フォトゲートPG(i,j)の透明電極の主要部分をp型の主透明電極層14-2とし、リセットトランジスタRT(i,j)の電荷読出領域8側の端部をn型の緩和領域部14-1とし、更に接続領域3側の端部をn型の抵抗増大部14-3としている。図3(a)及び(b)で説明した通り、緩和領域部14-1及び抵抗増大部14-3の直下のシールド層6の半導体界面部分と、主透明電極層14-2の直下のシールド層6の半導体界面部分では、ピンニングの状態が界面方向に沿って非一様に変化している。このため、第2実施形態に係る光検出器によれば、フォトゲートPG(i,j)と電荷読出領域8の間の電界集中を緩和しつつ、面積を大きく設定した主透明電極層14-2の直下のシールド層6の半導体界面の空乏化を抑えることができ、暗電流抑圧を完全なものにできる。したがって、3つの領域に透明電極を分割した第2実施形態に係る光検出器を画素として、第2実施形態に係る固体撮像装置を構成すれば、暗電流が抑圧され、放射線環境下でも高感度かつ広ダイナミックレンジな撮像が可能になる。

10

20

#### 【0058】

##### (第3実施形態)

本発明の第3実施形態に係る固体撮像装置は、第1実施形態に係る固体撮像装置の応用例に対応する。第3実施形態に係る固体撮像装置を構成する画素として機能する光検出素子は、第1実施形態に係る光検出素子の平面レイアウトに対し工夫を加えている。即ち、第3実施形態に係る光検出素子は、ガンマ線照射により劣化し易い、シリコン酸化膜等の素子分離絶縁膜を、電荷生成埋込層5から遠ざけることで、放射線耐性をより一層高める。このため、第3実施形態に係る光検出器では、フォトゲートPG(i,j)及び電荷読出領域FDの平面レイアウトがいずれも同心環状であり、平面レイアウトの中央部に環状のリセットゲート電極12を有するリセットトランジスタRT(i,j)を配置している。図5(a)及び(b)に例示する第3実施形態に係る光検出器では、フォトゲートPG(i,j)及び電荷読出領域FDの平面レイアウトをいずれも八角形リング状とし、フォトゲートPG(i,j)の中央部に八角形リング状のリセットゲート電極12を有するリセットトランジスタRT(i,j)を配置している。

30

#### 【0059】

図1の光検出素子に相当する部分は、図5(a)及び(b)に示すように、電荷生成部であるフォトダイオード部PD(i,j)と、フォトゲートPG(i,j)と、リセットトランジスタRT(i,j)を備える。フォトゲートPG(i,j)は、リセットトランジスタRT(i,j)を環状に取り囲むレイアウトを有している。リセットトランジスタRT(i,j)のリセットゲートRTの外周側、即ち、透明電極であるフォトゲートPG(i,j)側には、FDで示した電荷読出領域(電荷検出部)8が配置され、内周側には、RDで示したリセットドレイン領域7が配置されている。図5(a)及び(b)に示すように、第3実施形態に係る光検出器は、RDで示したリセットドレイン領域7を中心として、これを八角形リング状のリセットゲート電極12が取り囲み、更に、リセットゲート電極12を電荷読出領域FD及びフォトゲートPG(i,j)が取り囲むレイアウトを有している。

40

#### 【0060】

図5(b)から分かるように、第1導電型(p型)の基体領域1と、基体領域1の上部の一部に埋め込まれた第2導電型(n型)の電荷生成埋込層5は、p-n接合によりフォトダイオード部PD(i,j)を構成する。フォトゲートPG(i,j)の透明電極を透過してフォトダ

50

イオード部 P D(i,j)に光  $h_i$  が入射することにより、フォトダイオード部 P D(i,j)は信号電荷を生成する。図 5 ( a )に示した電荷読出領域 F Dは、基体領域 1 の内部において電荷生成埋込層 5 に接続されている。また、基体領域 1 の上部の他の一部となる電荷生成埋込層 5 の上面には、基体領域 1 よりも高不純物密度の p 型のシールド層 6 が設けられている。電荷生成埋込層 5 及びシールド層 6 は、例えば、八角形リング状等の環状を有している。シールド層 6 の上面にはフォトゲート絶縁膜（第 1 ゲート絶縁膜）4 b が接して設けられ、絶縁膜・半導体界面が構成されている。

#### 【 0 0 6 1 】

そして、シールド層 6 の上方となるフォトゲート絶縁膜 4 b の上には入射光  $h_i$  に対して透明な半導体電極であるフォトゲート P G(i,j)が設けられている。また、基体領域 1 の上部となる中央部には、基体領域 1 よりも高不純物密度で第 1 導電型のウェル領域 2 a が埋め込まれている。更に、基体領域 1 の上部となる周辺部には、基体領域 1 よりも高不純物密度で第 1 導電型の素子分離埋込領域 2 b が埋め込まれている。製造工程を鑑みると、ウェル領域 2 a と同一の深さ、同一不純物密度で素子分離埋込領域 2 b を埋め込んでも構わない。リセットトランジスタ R T(i,j)は、中央部のウェル領域 2 a の上部の一部に設けられている。更に、素子分離埋込領域 2 b よりも高不純物密度の p<sup>+</sup> 型の接続領域 3 が外周側に設けられた素子分離埋込領域 2 b の上部の一部に設けられている。シールド層 6 は、素子分離埋込領域 2 b 内の接続領域 3 に接して、基体領域 1 の上部の一部に設けられている。シールド層 6 の外周側の端部が接続領域 3 を介して素子分離埋込領域 2 b に電気的に接続されるので、シールド層 6 は接続領域 3 を介して基体領域 1 に電気的に短絡されて接地電位となる。

#### 【 0 0 6 2 】

図 5 ( a )及び( b )では図示を省略しているが、正八角形の接続領域 3 を囲むように、更に外側となる基体領域 1 の上部には素子分離絶縁膜が配置されている。素子分離絶縁膜（図示省略）と素子分離絶縁膜の下を埋め込む素子分離埋込領域 2 b によって素子分離領域（画素分離領域）が構成される。第 1 及び第 2 実施形態に係る固体撮像装置と同様に、素子分離絶縁膜は、例えば S T I 構造によって基体領域 1 の上部に埋め込むことが可能である。第 3 実施形態に係る光検出器では、素子分離絶縁膜（図示省略）が、光検出素子の最も外周側に位置する第 1 導電型の素子分離埋込領域 2 b 又は接続領域 3 の、更に外側に存在するレイアウトを採用しているので、フォトゲート型固体撮像装置の各画素のそれぞれの放射線耐性を高めることができる。

#### 【 0 0 6 3 】

第 3 実施形態に係る光検出器のリセットトランジスタ R T(i,j)は、電荷生成埋込層 5 よりも高不純物密度の n<sup>+</sup> 型のリセットドレイン領域 7 を、中央部のウェル領域 2 a の上部の中心に配置している。更に、図 5 ( b )に示すように、電荷生成埋込層 5 よりも高不純物密度の n<sup>+</sup> 型の電荷読出領域 8 をリセットドレイン領域 7 から離間して配置している。電荷読出領域 8 は、ウェル領域 2 a の上部の周辺部と、基体領域 1 の上部の一部に、ウェル領域 2 a の上部の周辺部から張り出すように埋め込んでいる。そして、リセットトランジスタ R T(i,j)は、電荷読出領域 8 とリセットドレイン領域 7 の間に形成されるチャネル領域となるウェル領域 2 a の上部の一部が露出した箇所の上にリセットゲート絶縁膜（第 2 ゲート絶縁膜）4 a を接し、絶縁膜・半導体界面を構成している。更に、図 5 ( b )に示すように、リセットゲート絶縁膜 4 a の上に第 2 導電型（n<sup>+</sup> 型）の D O P O S からなるリセットゲート電極 1 2 を配置している。

#### 【 0 0 6 4 】

図 5 ( a )に示すように、電荷読出領域 8 は、リセットドレイン領域 7 を中心とする、例えば八角形リング状等の環状を有している。そして図 5 ( b )に示すように、電荷生成埋込層 5 の内径側端部及びシールド層 6 の内径側端部に接して電荷読出領域 8 が埋め込まれている。電荷読出領域 8 が八角形リング状であれば、入射光  $h_i$  に対して透明な半導体電極であるフォトゲート P G(i,j)も八角形リング状等の環状を有することが好ましい。フォトゲート P G(i,j)の透明電極は、図 5 ( a )に示すようにリセットトランジスタ R T(i,j)

10

20

30

40

50

)の電荷読出領域 8 側の端部に割り当てられた内周側の緩和領域部 14 - 1 と、緩和領域部 14 - 1 を囲んで主要部分として設けられた主透明電極層 14 - 2 の 2 つの領域に分割されている。連続した 2 つの領域に透明電極が分割されることにより、半導体界面の方向に沿って非一様に分布する静電ポテンシャルを生成する効果を奏している。

#### 【 0 0 6 5 】

第 3 実施形態に係る光検出器では、第 1 実施形態と同様に、半導体透明電極である内周側の緩和領域部 14 - 1 は、リセットトランジスタ R T(i,j) のリセットゲート電極 12 と同じ第 2 導電型 (n<sup>+</sup> 型) の不純物元素が添加された D O P O S である。一方、半導体透明電極である主透明電極層 14 - 2 は、リセットトランジスタ R T(i,j) のリセットゲート電極 12 と逆の第 1 導電型 (p<sup>+</sup> 型) の不純物元素が添加された D O P O S である。また、主透明電極層 14 - 2 は、透明電極であるフォトゲート P G(i,j) の主要部分としての機能をなすものであるので、その平面パターンで定義される面積 (サイズ) は、緩和領域部 14 - 1 の面積よりも大きい。既に、図 3 (a) 及び (b) で説明した通り、緩和領域部 14 - 1 の直下のシールド層 6 の半導体界面部分と、主透明電極層 14 - 2 の直下のシールド層 6 の半導体界面部分では、ピンニングの状態が界面方向に沿って非一様に変化している。

#### 【 0 0 6 6 】

主透明電極層 14 - 2 を第 1 導電型 (p<sup>+</sup> 型) としているので、シールド層 6 の半導体表面 (半導体界面) との間の仕事関数差により、シールド層 6 の半導体表面がより強く、シールド層 6 の多数キャリアである正孔でピニングされる現象は、第 1 実施形態に係る光検出素子と同様である。ピニングされる正孔 (p 型電荷) は、信号電荷である電子 (n 型電荷) とは逆極性の電荷である。正孔のピニングにより半導体界面を多量の正孔で埋めることにより暗電流を不活性化できるので、この光検出素子を各画素として配列した固体撮像装置は、放射線環境下でも高感度かつ広ダイナミックレンジな撮像が可能となる。また、緩和領域部 14 - 1 を第 2 導電型 (n<sup>+</sup> 型) とすることにより、フォトゲート P G(i,j) と電荷読出領域 8 の間の電界集中を緩和することが可能となる。更に、リセットドレイン領域 7 を中心にして、リセットゲート電極 12、フォトゲート P G(i,j)、及び電荷読出領域 F D がそれぞれ同心環状となるような平面レイアウトを有している。したがって、第 3 実施形態に係る固体撮像装置は、各画素の内部において、ガンマ線照射により劣化しやすい素子分離絶縁膜が電荷生成埋込層 5 から遠い構造が容易に実現され、放射線耐性をより一層高めることができる。

#### 【 0 0 6 7 】

図 5 (b) に示した断面の方向に沿ったポテンシャル分布を、図 5 (c) に示す。図 5 (c) において、リセットドレイン領域 7 の電位であるリセットドレイン電圧 R D を電荷生成埋込層 5 の空乏化電位より低い値に設定することにより、光電変換により発生した電荷を電荷生成埋込層 5 及び電荷読出領域 8 に蓄積することができる。リセットドレイン電圧 R D を空乏化電位より低い値に設定することにより、信号電荷蓄積領域としての電荷生成埋込層 5 及び電荷読出領域 8 の電荷蓄積面積が電荷量 Q<sub>s</sub> によらず一定に保たれ、電荷電圧変換ゲインを一定にすることができるという効果が得られる。なお、電荷生成埋込層 5 に形成されるチャネル電位については、フォトゲート P G(i,j) の透明電極が p 型であっても、n 型であっても、シールド層 6 が 0 V にピニングした状態を保持しているので、変わることはなく等電位に保たれる。

#### 【 0 0 6 8 】

第 3 実施形態に係る光検出器においては、第 1 実施形態に係る光検出器と同様の効果、即ち、フォトゲート P G(i,j) と電荷読出領域 8 の間の電界集中を緩和しつつ、面積を大きく設定した主透明電極層 14 - 2 の直下のシールド層 6 の半導体界面の空乏化を抑え、暗電流抑圧を完全なものとすることができます。したがって第 3 実施形態に係る固体撮像装置によれば、放射線環境下でも高感度かつ広ダイナミックレンジな撮像を可能にする有利な効果を奏することができる。しかも、リセットドレイン領域 7 を中心にして、リセットゲート電極 12、フォトゲート P G(i,j)、及び電荷読出領域 F D が、それぞれ同心環状に囲

10

20

30

40

50

む平面レイアウトの画素構造であるので、各画素の内部において、ガンマ線照射により劣化し易い素子分離絶縁膜を電荷生成埋込層5から遠ざけ、放射線耐性をより一層高めることができる。

#### 【0069】

##### (第4実施形態)

本発明の第4実施形態に係る固体撮像装置は、第2実施形態に係る固体撮像装置の応用例に対応する。即ち、第2実施形態に係る固体撮像装置の各画素としてそれぞれ機能する光検出素子の平面レイアウトに対し工夫を加えている。第4実施形態に係る光検出素子は、ガンマ線照射により劣化し易い、シリコン酸化膜等の素子分離絶縁膜を電荷生成埋込層5から遠ざけることで、放射線耐性をより一層高め得る構造を提供する。即ち、第4実施形態に係る光検出器では、フォトゲートPG(i,j)及び電荷読出領域FDの平面レイアウトがいずれも同心環状であり、その中央部に環状のリセットゲート電極12を有するリセットトランジスタRT(i,j)を配置している。図6(a)及び(b)に示すように、フォトゲートPG(i,j)及び電荷読出領域FDの平面レイアウトが八角形リング状の場合は、その中央部に八角形リング状のリセットゲート電極12を有するリセットトランジスタRT(i,j)を配置するのが好ましい。

#### 【0070】

図6(a)及び(b)に示すように、第4実施形態に係る光検出器は、電荷生成部であるフォトダイオード部PD(i,j)と、フォトゲートPG(i,j)と、リセットトランジスタRT(i,j)を備える点では図1に示した第1実施形態に係る光検出器と同様である。しかし、第1実施形態に係る光検出器とは異なり、フォトゲートPG(i,j)は、中心に位置するリセットトランジスタRT(i,j)を環状に取り囲むレイアウトを有している。リセットトランジスタRT(i,j)のリセットゲートRTの外周側、即ち、透明電極であるフォトゲートPG(i,j)側には、図6(a)にFDで示した電荷読出領域(電荷検出部)8が配置され、内周側には、RDで示したリセットドレイン領域7が配置されている。

#### 【0071】

図6(b)に示すように、第1導電型(p型)の基体領域1と、基体領域1の上部の一部に埋め込まれた第2導電型(n型)の電荷生成埋込層5は、p-n接合によりフォトダイオード部PD(i,j)を構成する。フォトゲートPG(i,j)の透明電極を透過してフォトダイオード部PD(i,j)に光h<sub>入射</sub>が入射することにより、フォトダイオード部PD(i,j)は信号電荷を生成する。電荷読出領域FDは、基体領域1の内部において電荷生成埋込層5に接続されている。また、電荷生成埋込層5の上面となる基体領域1には、基体領域1よりも高不純物密度のp型のシールド層6が埋め込まれている。電荷生成埋込層5及びシールド層6は、例えば、八角形リング状等の環状を有している。シールド層6の上面にはフォトゲート絶縁膜(第1ゲート絶縁膜)4bが接して設けられ、シールド層6と絶縁膜・半導体界面が構成されている。そして、シールド層6の上方の位置において、フォトゲート絶縁膜4bの上には入射光h<sub>入射</sub>に対して透明な半導体電極であるフォトゲートPG(i,j)が設けられている。

#### 【0072】

また、基体領域1の上部となる中央部には、基体領域1よりも高不純物密度で第1導電型のウェル領域2aが埋め込まれ、基体領域1の上部となる周辺部には、基体領域1よりも高不純物密度で第1導電型の素子分離埋込領域2bが埋め込まれている。リセットトランジスタRT(i,j)は、ウェル領域2aの上部の一部に設けられている。更に、素子分離埋込領域2bよりも高不純物密度のp<sup>+</sup>型の接続領域3が素子分離埋込領域2bの上部に埋め込まれている。素子分離埋込領域2bは、ウェル領域2aと同一の深さ、同一不純物密度で構わない。シールド層6は、素子分離埋込領域2b内の接続領域3に接し、素子分離埋込領域2b内から内側の基体領域1の上部に張り出すように環状に設けられている。シールド層6の外周側の端部が接続領域3を介して素子分離埋込領域2bに電気的に接続されるので、シールド層6は接続領域3を介して基体領域1に電気的に短絡されて接地電位となる。

### 【 0 0 7 3 】

図 6 ( a ) 及び ( b ) では図示を省略しているが、正八角形の接続領域 3 を囲むように、更に外側となる基体領域 1 の上部には素子分離絶縁膜が配置されている。素子分離絶縁膜（図示省略）と素子分離絶縁膜の下を埋め込む素子分離埋込領域 2 b によって素子分離領域（画素分離領域）が構成される。第 1 ~ 第 3 実施形態に係る光検出器と同様に、素子分離絶縁膜は、例えば S T I 構造によって基体領域 1 の上部に埋め込むことが可能である。図 6 ( a ) 及び ( b ) に示すように、第 4 実施形態に係る光検出器を構成する画素となる光検出素子は、R D で示したリセットドレイン領域 7 を中心として、これを八角形リング状のリセットゲート電極 1 2 が取り囲み、更に、リセットゲート電極 1 2 を、電荷読出領域 F D 及びフォトゲート P G(i,j) が取り囲むレイアウトを有している。第 4 実施形態に係る光検出器では、素子分離絶縁膜（図示せず）は、最も外周の素子分離埋込領域 2 b 又は接続領域 3 の外側に存在する構造を採用しているので、フォトゲート型固体撮像装置を構成する各画素のそれぞれの放射線耐性を高めることができる。

### 【 0 0 7 4 】

第 4 実施形態に係る光検出器のリセットトランジスタ R T(i,j) は、電荷生成埋込層 5 よりも高不純物密度の  $n^+$  型のリセットドレイン領域 7 を、中央部のウェル領域 2 a の上部の中心に配置している。更に、リセットトランジスタ R T(i,j) は、電荷生成埋込層 5 よりも高不純物密度の  $n^+$  型の電荷読出領域 8 をリセットソース領域として、リセットドレイン領域 7 から離間して配置している。電荷読出領域 8 は、ウェル領域 2 a の上部の周辺部と、基体領域 1 の上部の一部に、ウェル領域 2 a の上部の周辺部から外周側に張り出すように埋め込んでいる。そして、リセットトランジスタ R T(i,j) は、電荷読出領域 8 とリセットドレイン領域 7 の間に形成されるチャネル領域となるウェル領域 2 a の上部の一部が露出した箇所の上にリセットゲート絶縁膜（第 2 ゲート絶縁膜）4 a を接し、絶縁膜・半導体界面を構成している。更に、リセットトランジスタ R T(i,j) は、リセットゲート絶縁膜 4 a の上に第 2 導電型（ $n^+$  型）の D O P O S からなるリセットゲート電極 1 2 を配置している。

### 【 0 0 7 5 】

図 6 ( a ) に例示したように、電荷読出領域 8 は、八角形リング状等の環状の形状で、リセットドレイン領域 7 を囲んでいる。図 6 ( b ) に示すように、電荷読出領域 8 は、基体領域 1 の内部において、電荷生成埋込層 5 の内径側端部及びシールド層 6 の内径側端部に接し、ウェル領域 2 a の上部から周辺の基体領域 1 の上部に渡る領域の一部に環状に埋め込まれている。フォトゲート P G(i,j) は、例えば、八角形リング状等の環状を有し、リセットトランジスタ R T(i,j) の電荷読出領域 8 側の端部に割り当てられた内周側の緩和領域部 1 4 - 1 と、接続領域 3 側の端部に割り当てられた抵抗増大部 1 4 - 3 と、これら緩和領域部 1 4 - 1 及び抵抗増大部 1 4 - 3 間に設けられた主透明電極層 1 4 - 2 の 3 つの領域に分割されている。連続した 3 つの領域に透明電極が分割されることにより、半導体界面の方向に沿って非一様に分布する静電ポテンシャルを生成する効果を奏している。図 3 ( a ) 及び ( b ) の説明から分かるように、緩和領域部 1 4 - 1 及び抵抗増大部 1 4 - 3 のそれぞれの直下のシールド層 6 の半導体界面部分と、主透明電極層 1 4 - 2 の直下のシールド層 6 の半導体界面部分でピンニングの状態が異なる。

### 【 0 0 7 6 】

本発明の第 4 実施形態に係る光検出器では、第 2 実施形態に係る光検出器と同様に、緩和領域部 1 4 - 1 及び抵抗増大部 1 4 - 3 は、リセットトランジスタ R T(i,j) のリセットゲート電極 1 2 と同じ第 2 導電型（ $n^+$  型）の不純物元素が添加された D O P O S である。一方、主透明電極層 1 4 - 2 は、リセットトランジスタ R T(i,j) のリセットゲート電極 1 2 と逆の第 1 導電型（ $p^+$  型）の不純物元素が添加された D O P O S である。このため、緩和領域部 1 4 - 1 と主透明電極層 1 4 - 2 の間、及び主透明電極層 1 4 - 2 と抵抗増大部 1 4 - 3との間にはそれぞれ p-n 接合が構成される。また、主透明電極層 1 4 - 2 は、透明電極であるフォトゲート P G(i,j) の主要部分としての機能をなすものであるので、図 6 ( a ) に示すように、主透明電極層 1 4 - 2 の同心環の半径方向の長さは、緩和領域

10

20

30

40

50

部 14 - 1 又は抵抗増大部 14 - 3 の半径方向の長さよりも長く設定している。この結果、主透明電極層 14 - 2 の平面パターンで定義される面積（サイズ）は、緩和領域部 14 - 1 又は抵抗増大部 14 - 3 の面積よりも大きい。

#### 【 0 0 7 7 】

主透明電極層 14 - 2 が第 1 導電型（ $p^+$  型）であるため、シールド層 6 の半導体表面（半導体界面）との間の仕事関数差により、シールド層 6 の半導体表面がより強く、シールド層 6 の多数キャリアである正孔でピニングされる現象は第 2 実施形態に係る光検出素子と同様である。ピニングされる正孔（ $p$  型電荷）は、信号電荷である電子（ $n$  型電荷）とは逆極性の電荷である。正孔のピニングにより暗電流抑圧が完全化されるので、第 4 実施形態に係る光検出素子を各画素として配列した個体撮像装置は、暗電流抑圧を完全にして、放射線環境下でも高感度かつ広ダイナミックレンジな撮像が可能となる。また、緩和領域部 14 - 1 を第 2 導電型（ $n^+$  型）とすることにより、フォトゲート PG(i,j) と電荷読出領域 8 の間の電界集中を緩和できる。特に、第 2 導電型（ $n^+$  型）の抵抗増大部 14 - 3 を入力端としてフォトゲート PG(i,j) に印加する電圧を与えるバイアス条件を採用することにより、主透明電極層 14 - 2 を経て緩和領域部 14 - 1 に至る 2 つの p-n 接合を経由する電気的な電気経路の抵抗が大きくなる。10

#### 【 0 0 7 8 】

抵抗増大部 14 - 3 から主透明電極層 14 - 2 を経て緩和領域部 14 - 1 に至る電気経路の抵抗を増大させることにより、フォトゲート PG(i,j) と電荷読出領域 8 の間の電界集中を更に緩和することができる。更に、第 4 実施形態に係る光検出素子は、リセットドレイン領域 7 を中心にして、リセットゲート電極 12、電荷読出領域 FD 及びフォトゲート PG(i,j) がそれぞれ同心環状となるような平面レイアウトを有している。環状レイアウトの光検出素子を個体撮像装置の各画素として同一半導体チップ上に配列することにより、各画素の内部において、ガンマ線照射により劣化し易い素子分離絶縁膜が電荷生成埋込層 5 から遠い構造が容易に実現され、放射線耐性をより一層高めることができる。20

#### 【 0 0 7 9 】

図 6 (b) に示した断面の方向に沿ったポテンシャル分布を、図 6 (c) に示す。図 6 (c) において、リセットドレイン領域 7 の電位であるリセットドレイン電圧 RD を電荷生成埋込層 5 の空乏化電位より低い値に設定することにより、光電変換により発生した電荷を電荷生成埋込層 5 及び電荷読出領域 8 に蓄積することができる。リセットドレイン電圧 RD を空乏化電位より低い値に設定することにより、信号電荷蓄積領域としての電荷生成埋込層 5 及び電荷読出領域 8 の電荷蓄積面積が電荷量 Qs によらず一定に保たれ、電荷電圧変換ゲインを一定にすることができるという効果が得られる。なお、電荷生成埋込層 5 に形成されるチャネル電位については、フォトゲート PG(i,j) の透明電極が  $p$  型であっても、 $n$  型であっても、シールド層 6 が 0 V にピニングした状態を保持しているので、変わることはなく等電位に保たれる。30

#### 【 0 0 8 0 】

第 4 実施形態に係る光検出器においては、第 2 実施形態に係る光検出器と同様の効果、即ち、フォトゲート PG(i,j) と電荷読出領域 8 の間の電界集中を緩和しつつ、面積を大きく設定した主透明電極層 14 - 2 の直下のシールド層 6 の半導体界面の空乏化を抑え、暗電流抑圧を完全なものにできる。したがって、第 4 実施形態に係る光検出器を画素として配列した、第 4 実施形態に係る固体撮像装置によれば、放射線環境下でも高感度かつ広ダイナミックレンジな撮像を可能にする有利な効果を奏することができる。しかも、リセットドレイン領域 7 を中心にして、リセットゲート電極 12、電荷読出領域 FD 及びフォトゲート PG(i,j) が、それぞれ同心環状に囲む平面レイアウトの画素構造であるので、各画素の内部において、ガンマ線照射により劣化し易い素子分離絶縁膜を電荷生成埋込層 5 から遠ざけ、放射線耐性をより一層高めることができる。40

#### 【 0 0 8 1 】

（その他の実施形態）

本発明は、上記した第 1 ~ 第 4 実施形態によって説明したが、この開示の一部をなす論

述及び図面は本発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施形態、実施例、及び運用技術が明らかとなろう。

#### 【0082】

例えば、第3又は第4実施形態に係る画素（図1の光検出素子に相当する部分）について、リセットゲート電極12、フォトゲートPG(i,j)、及び電荷読出領域FDの平面レイアウトは、図面上、八角形リング状の場合を例示しているが、これに限られることはなく、四角形リング状、六角形リング状、又は十角以上の多角形リング状、円形リング状、橢円形リング状等であってもよい。また、リセットゲート電極12、フォトゲートPG(i,j)、及び電荷読出領域FDの平面レイアウトは、図面上、同心環状となっているが、これらのリングは、同心になつていなくてもよい。

10

#### 【0083】

また、第1～第4実施形態の説明で第1導電型をp型、第2導電型をn型として説明したが、第1導電型をn型、第2導電型をp型としても構わない。例えば、第1～第4実施形態においては、信号電荷が電子（第1導電型電荷）で、ピンニングされる電荷が正孔（第2導電型電荷）で、画素内のトランジスタ、例えば、リセットトランジスタRT(i,j)がnMOSトランジスタである場合を例示した。しかし、信号電荷を正孔とし、画素内のトランジスタ、例えば、リセットトランジスタRT(i,j)をpMOSトランジスタとしても構わない。例えば、一例として、第1～第4実施形態における固体撮像装置の各要素の極性をすべて逆にするといった対応も可能である。また、画素内のトランジスタの種類についても、MOSFET等のMOSトランジスタに限られず、MISトランジスタ等を採用できる。

20

#### 【0084】

更に、第1～第4実施形態においては、2次元フォトゲート型固体撮像装置（エリアセンサ）を例示的に説明したが、本発明は2次元フォトゲート型固体撮像装置に限定して解説するべきではない。例えば、図1にその一部を例示的に示した二次元マトリクスの配列において、 $i = 1$ 又は $j = 1$ と固定し、画素 $Q_{ij}$ を一次元に配列した一次元フォトゲート型固体撮像装置（ラインセンサ）を構成してもよいことは、第1～第4実施形態で開示した技術的思想の内容から容易に理解できるはずである。

#### 【0085】

以上のとおり、本発明は上記において記載していない様々な実施形態等を含むとともに、本発明の技術的範囲は、上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

30

#### 【符号の説明】

#### 【0086】

1…基体領域、2a…ウェル領域、2b…素子分離埋込領域、3…接続領域、4a…リセットゲート絶縁膜（第2ゲート絶縁膜）、4b…フォトゲート絶縁膜（第1ゲート絶縁膜）、5…電荷生成埋込層、6…シールド層、7…リセットドレイン領域、8…電荷読出領域（リセットソース領域）、9…素子分離絶縁膜、10…光検出素子、12…リセットゲート電極、14-1…緩和領域部、14-2…主透明電極層、14-3…抵抗増大部、20…リセットトランジスタ走査駆動回路（RT走査回路）、30…選択トランジスタ走査駆動回路（SL走査回路）、40…フォトゲート走査駆動回路（PG走査回路）

40

50

【 図面 】

【 図 1 】

【 図 2 】

【図3】

【図4】

【図 5】

【図 6】

10

20

30

40

50

---

フロントページの続き

(74)代理人 100173864

弁理士 齊藤 健治

(72)発明者 渡辺 恭志

静岡県浜松市中区大工町125 株式会社ブルックマンテクノロジ内

(72)発明者 武内 伴照

茨城県東茨城郡大洗町成田町4002 日本原子力研究開発機構 大洗研究開発センター内

(72)発明者 駒野目 裕久

東京都大田区池上5丁目6番16号 池上通信機株式会社内

審査官 柴山 将隆

(56)参考文献 特開2018-182044 (JP, A)

米国特許出願公開第2011/0102620 (US, A1)

米国特許出願公開第2006/0001059 (US, A1)

特表2015-512562 (JP, A)

特開2013-239866 (JP, A)

特開2008-166607 (JP, A)

韓国公開特許第10-2013-0007121 (KR, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H01L 31/10

H04N 25/63

H04N 25/76