(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 22 456 T2 2004.12.23

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 976 226 B1

(51) Int Cl.<sup>7</sup>: H04L 12/44

(21) Deutsches Aktenzeichen: 698 22 456.6

(86) PCT-Aktenzeichen: PCT/US98/01760

(96) Europäisches Aktenzeichen: 98 903 831.0

(87) PCT-Veröffentlichungs-Nr.: WO 98/36535

(86) PCT-Anmeldetag: 29.01.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 20.08.1998

(97) Erstveröffentlichung durch das EPA: 02.02.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.03.2004

(47) Veröffentlichungstag im Patentblatt: 23.12.2004

(30) Unionspriorität:

38025 P 14.02.1997 US

992921 18.12.1997 US

(84) Benannte Vertragsstaaten:

DE, GB

(73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif.,

US

(72) Erfinder:

RUNALDUE, Jefferson, Thomas, San Jose, US;

CHOW, Ka-Fai, Peter, San Jose, US; VISWANATH,

Somnath, Sunnyvale, US

(74) Vertreter:

Patentanwälte von Kreisler, Selting, Werner et col.,

50667 Köln

(54) Bezeichnung: INTEGRIERTE MULTIPOINT-VERMITTLUNG MIT GETEILTER MEDIUMZUGRIFFSSTEUERUNGSSCHALTUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****TECHNISCHES GEBIET**

**[0001]** Die vorliegende Erfindung betrifft Netzumschaltungen und insbesondere eine gemeinsam genutzte Multiport-Medienzugriffssteuerung auf einem Datennetz-Schalter-Logik-Chip.

**HINTERGRUND DER ERFINDUNG**

**[0002]** Ein Datennetz-Schalter ermöglicht eine Datenübertragung zwischen mehreren Medienstationen in einem Lokalnetz. Datenblöcke oder -pakete werden unter Verwendung einer Datennetz-Schalter-Medienzugriffssteuerung (MAC), die Netz-Interface-Karten oder Schaltungsanordnungen an jedem Schalterport aktiviert, zwischen Stationen übermittelt. Die MAC überwacht das Senden von Daten von dem Port zu dem Netz, den Empfang von von dem Netz kommenden Daten am Port und vermittelt die Daten am Port, um Kollisionen zu vermeiden. Der Netzschatler leitet Datenblöcke von einer Sendestation zu einer Zielstation anhand der Kopfinformationen in dem empfangenen Datenblock. Sende- und Empfangspuffer an jedem Port sind mit der MAC gekoppelt. Je nach Betriebsmodus wird ein ankommendes Paket temporär in einem Empfangspuffer eines Ports gehalten, kann zwecks späteren Sendens zu einem außerhalb des Schalters befindlichen Speicher transportiert werden oder zwecks unverzüglichen Sendens aus dem Netz heraus in den Sendepuffer des entsprechenden Ports platziert werden.

**[0003]** Paketübertragungsereignisse werden typischerweise verfolgt, um eine Basis für die statistische Analyse einer Netzoperation in Bezug auf jeden Datennetz-Schalterport zu erzeugen. Beispielsweise kann die Anzahl von gesendeten Paketen, empfangenen Paketen, Sendekollisionen u. dgl. periodisch gezählt und abgefragt werden. Durch die Verwendung von Statistikzählern kann eine inkorrekte Operation einer Vorrichtung, wie beispielsweise der Verlust von Paketen, festgestellt werden. Typischerweise kann jede MAC-Einheit eine Empfangs-Zustandsmaschine und eine Sende-Zustandsmaschine mit internen Zählern mit begrenzter Kapazität zum Zählen einer kleinen Anzahl von Sendeereignisparametern für jeden Block aufweisen, der den jeweiligen Schalterport durchläuft. Flip-Flops, die für die speziellen Parameter zweckbestimmt sind, werden jeweils jedes Mal dann inkrementiert, wenn ein Element in diesem Block identifiziert wird. Bei jedem ankommenden Block, der temporär in einem Empfangs-FIFO-Puffer gespeichert werden kann, werden die jeweiligen Flip-Flops in der Empfangs-Zustandsmaschine gelesen und die daraus resultierenden Daten dem Block angehängt. Bei ausgehenden Blöcken erfolgt eine im wesentlichen gleiche Verarbeitung. Somit enthält der ausgehende Block, der vorüberge-

hend in einem Sende-FIFO-Puffer gespeichert wird, angehängte Daten bezüglich der Empfangsoperation und der Sendeoperation. Die Sendeoperationsdaten werden hinzugefügt, wenn der Block aus dem Sende-FIFO-Puffer heraus gesendet wird.

**[0004]** Da Datennetze robuster werden und der Datenverkehr größer wird, sind zusätzliche Operationsparameter von Bedeutung. Das Verfolgen einer größeren Anzahl von Parametern macht eine größere Komplexität der MAC erforderlich, was beispielsweise das Vorsehen von mehr Registern und das Unterstützen von Logikelementen sowie größere Pufferkapazitäten beinhaltet. Die Integration dieser zusätzlichen Elemente für jede MAC auf dem Schalter-Logik-Chip belastet die Chip-Architektur. Da die Entwicklung der Schalter größere Kapazitäten hinsichtlich des Datenverkehrsumfangs zur Folge hat und die Anzahl von Schalterports steigt, wird die effiziente Nutzung der Chip-Architektur noch kritischer.

**[0005]** In EP-A-0 603 443 ist eine Brücke zum Verbinden von Token-Ring-Lokalnetzen beschrieben. Das Patent beschreibt das Konzept einer "gemeinsam genutzten MAC", wobei die MAC-pro-Port durch eine zentralisierte Funktion innerhalb eines zentralisierten Prozessors ersetzt wird.

**[0006]** EP-A-0 603 444 enthält eine im wesentlichen gleiche Beschreibung wie EP-A-0 603 443 und betrifft einen Schalter mit N Ports, wobei jeder Port mit einem reellen Segment des Token-Rings verbunden ist.

**OFFENBARUNG DER ERFINDUNG**

**[0007]** Die vorliegende Erfindung stellt einen integrierten Multiport-Netzschatler gemäß Anspruch 1 bereit. Ferner stellt die vorliegende Erfindung ein Verfahren zum Steuern eines Medienzugriffs an mehreren Ports eines integrierten Multiport-Netzschatlers mit den Schritten gemäß Anspruch 9 bereit.

**[0008]** Die vorliegende Erfindung behandelt die oben beschriebenen Erfordernisse und Nachteile teilweise aufgrund der Erkenntnis, dass bestimmte MAC-Funktionen für jeden Port mittels einer Schaltungsanordnung ausführbar sind, die nicht, wie beim Stand der Technik, an jedem einzelnen Port vorgesehen zu sein braucht. Ein Vorteil der Erfindung liegt darin, dass eine Schaltlogik- und Registeranordnung zum Ausführen von im wesentlichen gleichen Funktionen für mehrere Schalterports vorgesehen ist. Dieser Vorteil basiert teilweise auf der Erkenntnis, dass, wenn die Funktionalität einer gemeinsamen Schaltungsanordnung zu einem beliebigen Zeitpunkt akkurat dem jeweiligen Port zugeordnet werden kann, ein diskretes Vorsehen einer im wesentlichen gleichen Schaltungsanordnung an jedem Port redundant und unnötig wird.

**[0009]** Ein weiterer Vorteil der vorliegenden Erfindung liegt darin, dass der aktuelle Zugriffszustand an jedem der mehreren Schalterports an einer einzelnen Zustandsspeicherstelle aufrechterhalten wird, wodurch der Zugriff auf einen gespeicherten Port-MAC-Zustand und Aktualisierung dieses Zustands vereinfacht werden. Ein weiterer Vorteil der vorliegenden Erfindung liegt darin, dass es der Zugriff auf den Zustandsspeicher in Koordination mit der einzelnen gemeinsamen Schaltlogik- und Registeranordnung ermöglicht, dass MAC-Funktionen für jeden der mehreren Ports auf einer Zeitteilbasis ausgeführt werden. Die Erfindung sorgt somit für eine effizientere Ausnutzung von Chip-Resourcen und Architekturraum als es bei dem Stand der Technik entsprechenden Vorrichtungen der Fall ist.

**[0010]** Weitere Vorteile der vorliegenden Erfindung werden für Fachleute auf dem Sachgebiet anhand der folgenden detaillierten Beschreibung ersichtlich, in der nur die bevorzugte Ausführungsform der Erfindung zur Erläuterung der besten Art zur Durchführung der Erfindung dargestellt und beschrieben ist. Es wird festgestellt werden, dass die Erfindung andere und unterschiedliche Ausführungsformen bieten kann und die unterschiedlichen Details in unterschiedlicher offensichtlicher Hinsicht modifizierbar sind, ohne dass dadurch vom Umfang der Erfindung, wie er in den beiliegenden Patentansprüchen definiert ist, abgewichen wird. Entsprechend dürfen die Zeichnungen und die Beschreibung nur als Erläuterung und nicht als Einschränkung angesehen werden.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0011]** Es wird auf die beiliegenden Zeichnungen Bezug genommen, in denen Elemente mit den gleichen Bezugszeichen gleiche Elemente bezeichnen. Es zeigen:

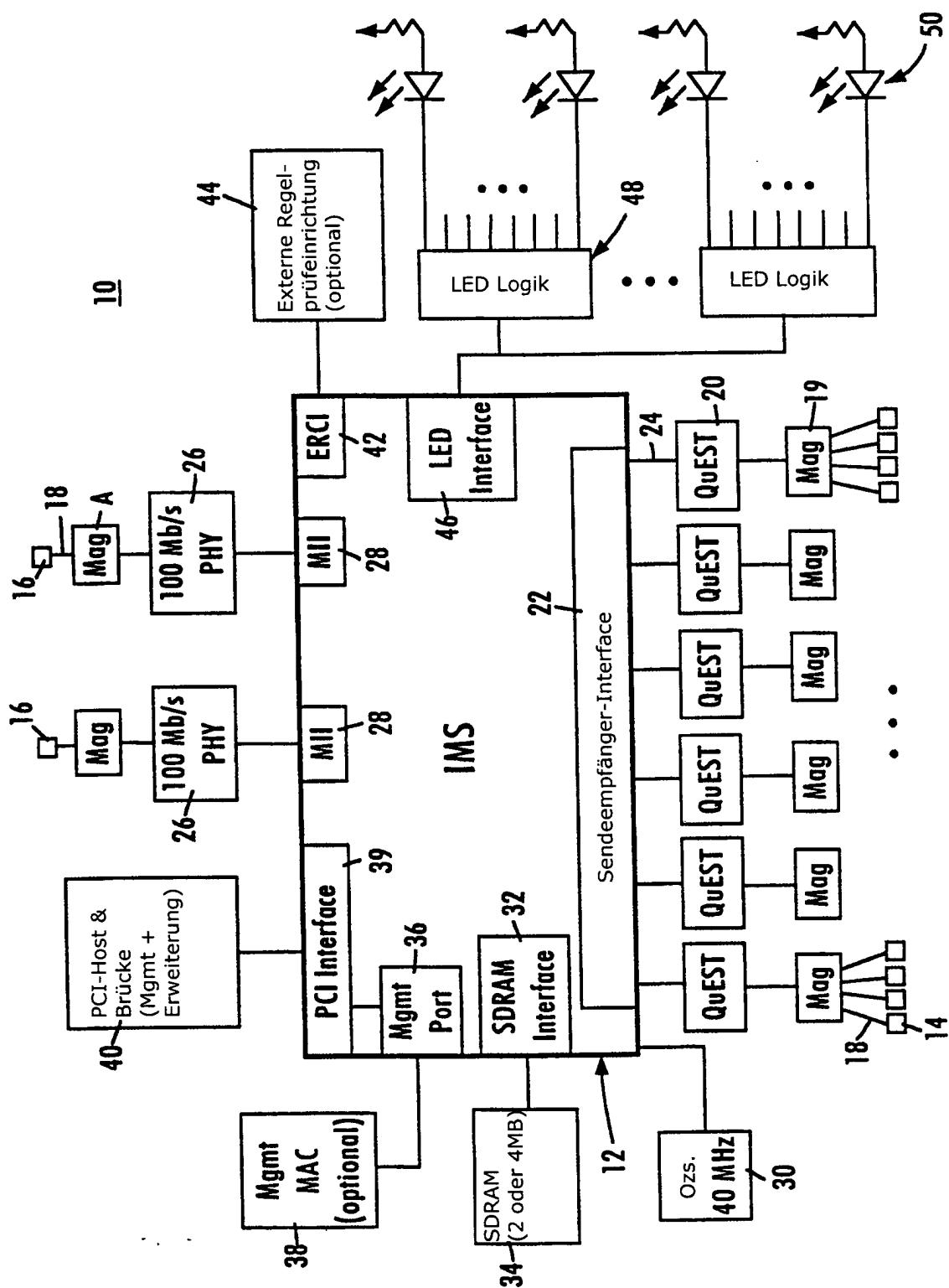

**[0012]** **Fig. 1** ein Blockschaltbild einer Umgebung eines paketgeschalteten Systems gemäß der vorliegenden Erfindung;

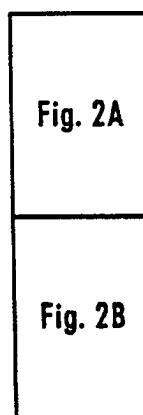

**[0013]** **Fig. 2** ein Blockschaltbild eines erfindungsgemäßen Multiport-Schalters, der in dem in **Fig. 1** gezeigten paketgeschalteten System verwendbar ist;

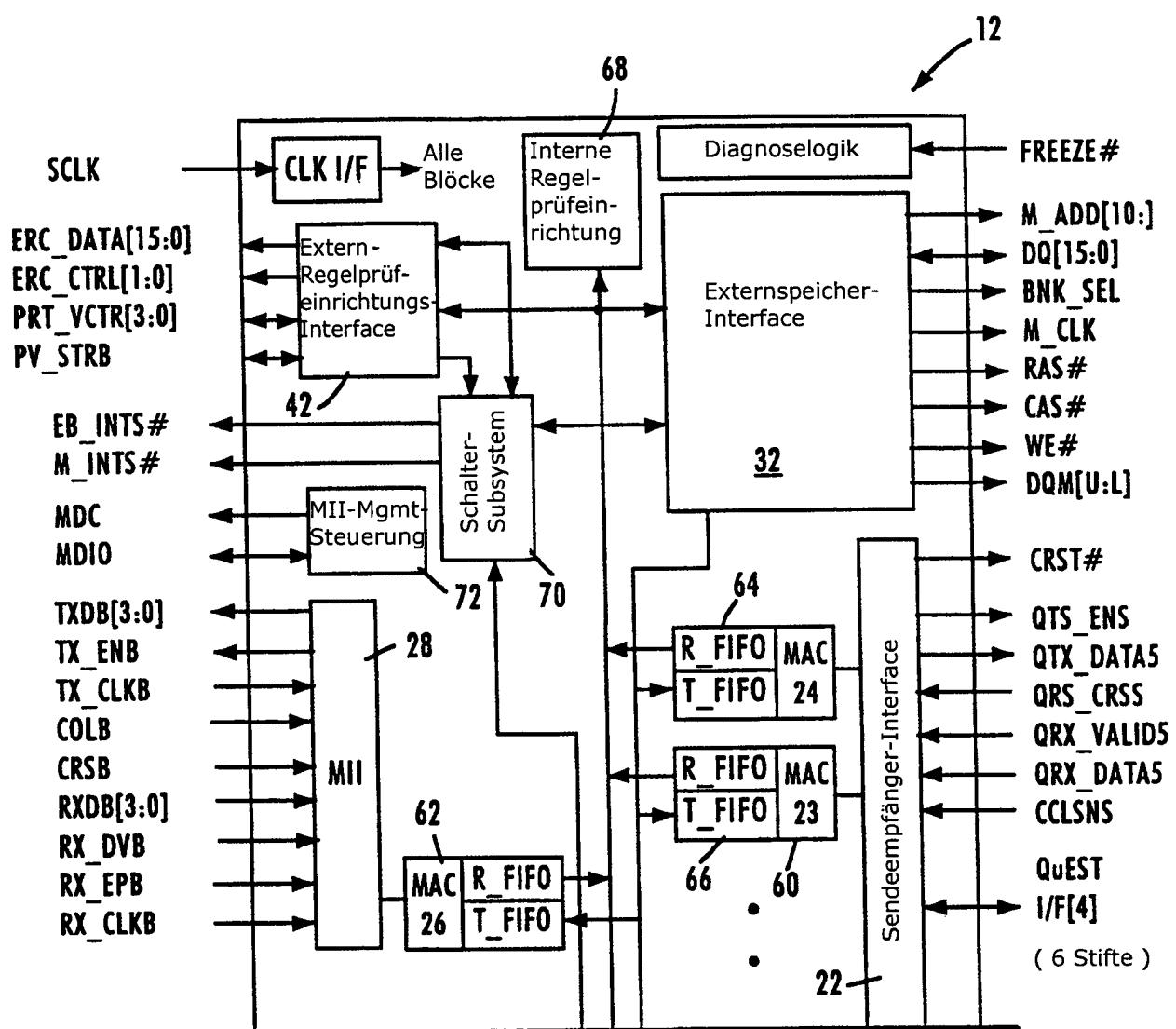

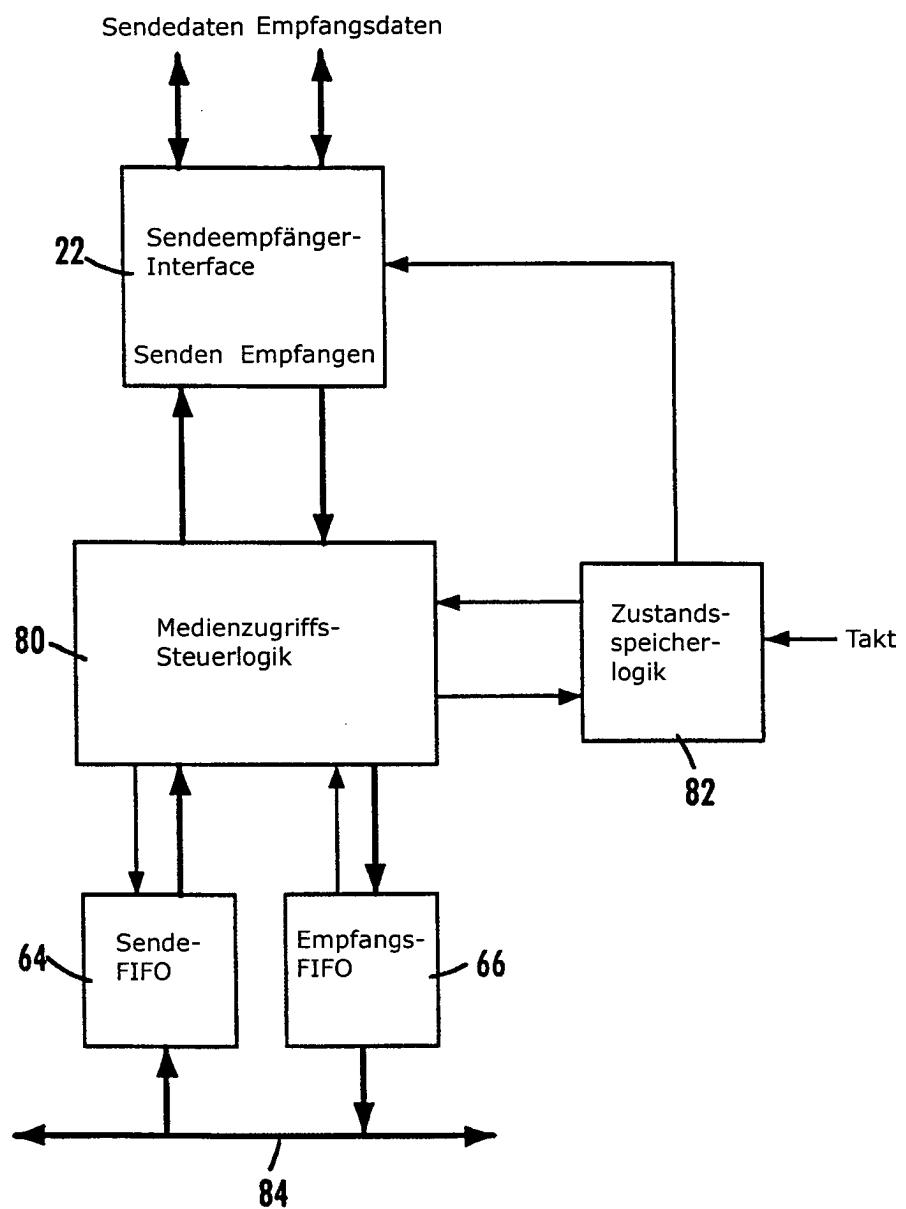

**[0014]** **Fig. 3** ein Blockschaltbild mit Darstellung der erfindungsgemäßen Medienzugriffssteuerung;

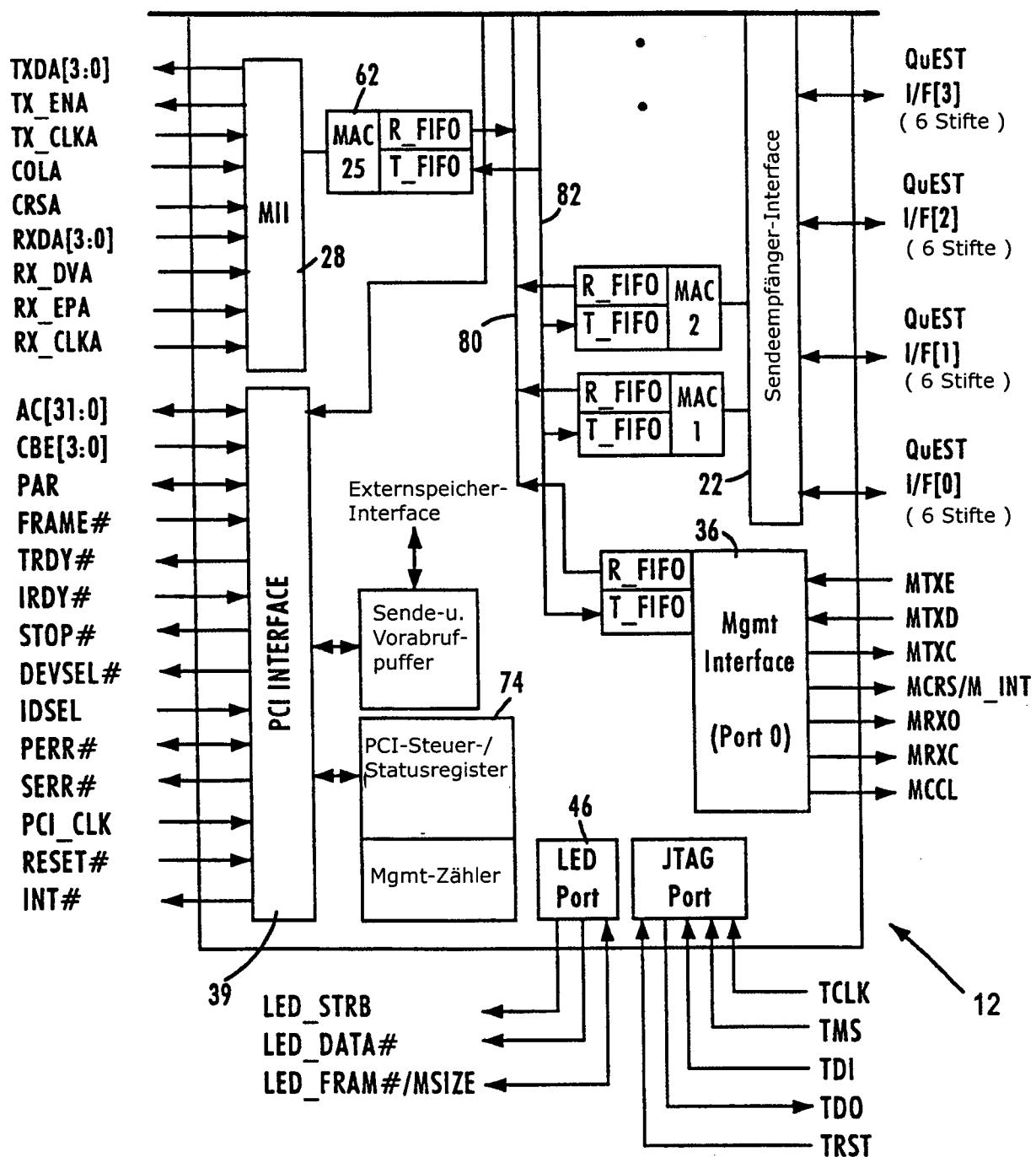

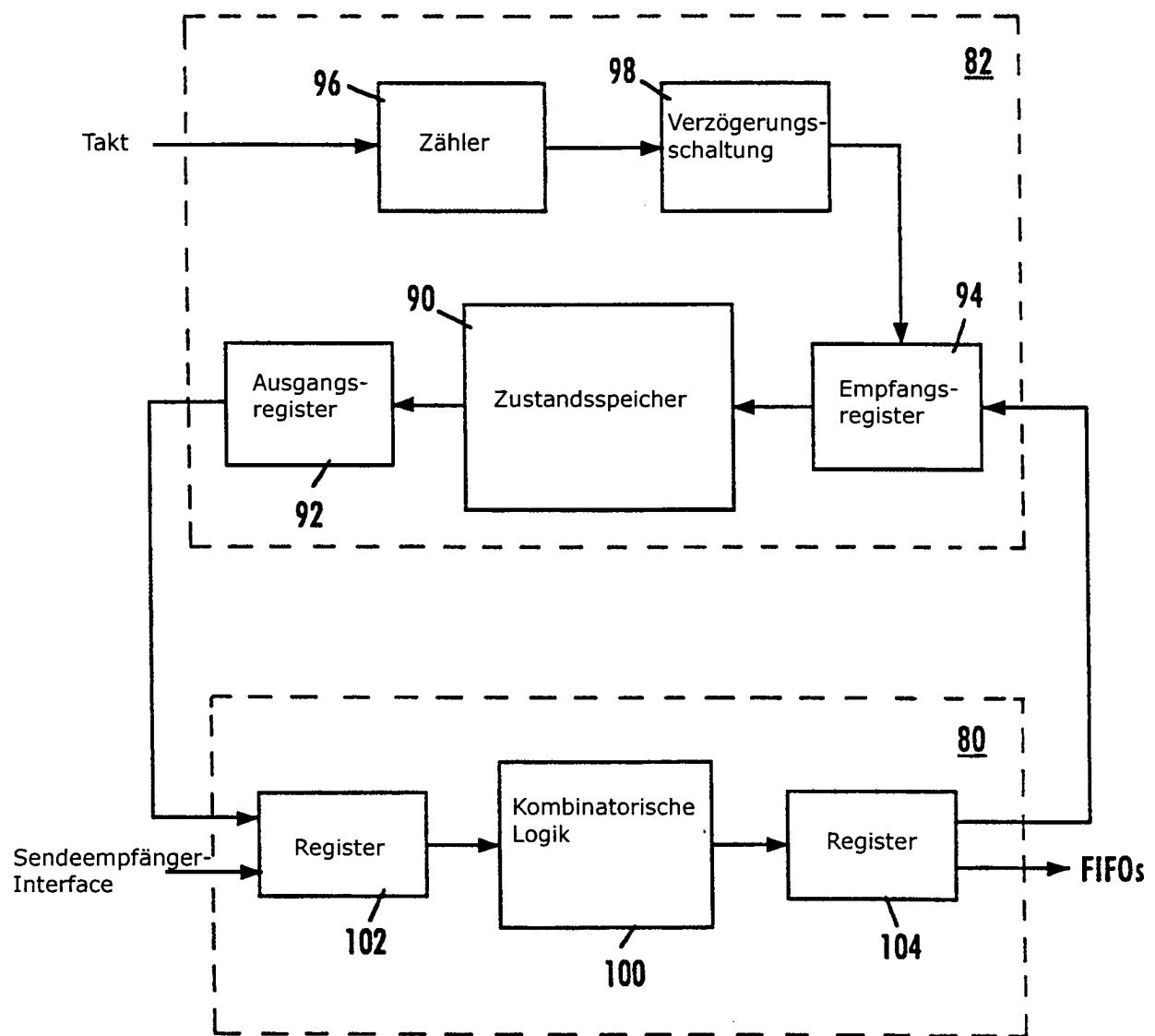

**[0015]** **Fig. 4** ein detaillierteres Blockschaltbild einer bevorzugten Konfiguration der Medienzugriffs-Steuerlogikeinheit **80** und der Zustandsspeicher-Steuer-einheit **82** gemäß der vorliegenden Erfindung;

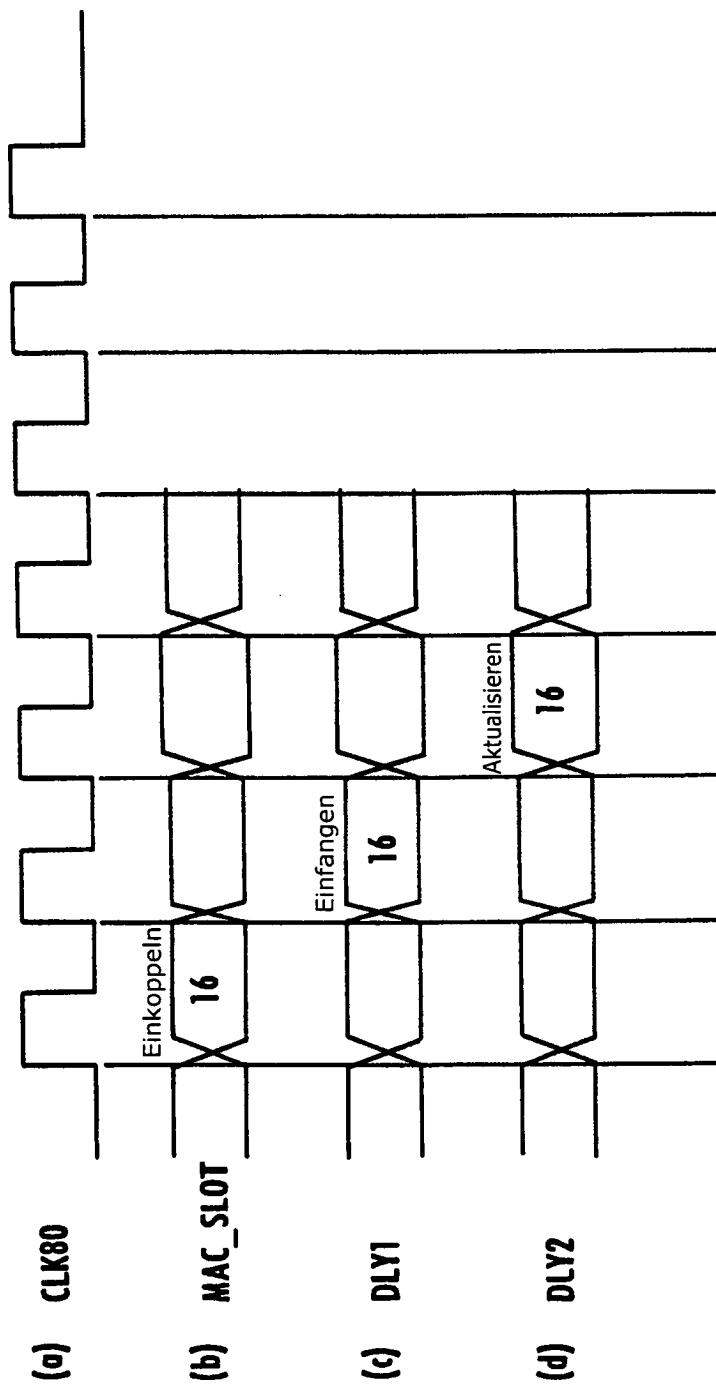

**[0016]** **Fig. 5** ein Wellenformdiagramm mit Darstellung der gestuften Pipeline-Operation gemäß der vorliegenden Erfindung.

#### BESTE ART ZUR DURCHFÜHRUNG DER ERFINDUNG

**[0017]** Die vorliegende Erfindung ist hier beispielhaft in einer Umgebung eines paketgeschalteten Netzes, wie z. B. eines Ethernet (IEEE 802.3) dargestellt. Aus der folgenden detaillierten Beschreibung geht hervor, dass die vorliegende Erfindung auch auf andere paketgeschaltete Systeme anwendbar ist. **Fig. 1** zeigt ein Blockschaltbild für ein paketgeschaltetes System **10**, das die Umgebung der vorliegenden Erfindung bildet. Das paketgeschaltete Netz weist einen integrierten Multiport-Schalter (IMS) **12** auf, der eine Datenpaketübertragung zwischen Netzstationen ermöglicht. Die Netzstationen können unterschiedlich konfiguriert sein. Bei dem aktuellen Beispiel senden und empfangen vierundzwanzig (24) 10 Megabyte-pro-Sekunde- (Mb/s-) Netzstationen **14** Daten mit einer Netz-Datenrate von 10 Mb/s und senden und empfangen zwei 100 Mb/s-Netzstationen **16** Datenpakete mit einer Netzgeschwindigkeit von 100 Mb/s. Der Multiport-Schalter **12** leitet anhand des Ethernet-Protokolls von der Netzstation **14** oder **16** kommende Datenpakete selektiv zu der entsprechenden Zielstation.

**[0018]** Die 10 Mb/s-Netzstationen **14** senden und empfangen Datenpakete über ein Medium **18** entsprechend dem Halbduplex-Ethernet-Protokoll zu und von dem Multiport-Schalter **12**. Das Ethernet-Protokoll ISO/IEC 8802-3 (ANSI/IEEE Std. 802.3, 1993 Ed.) bildet einen Halbduplex-Medienzugriffsmechanismus, der es sämtlichen Stationen **14** ermöglicht, gleichberechtigt auf das Netz zuzugreifen. Der Datenverkehr in einer Halbduplex-Umgebung wird nicht gegenüber dem Medium **18** abgegrenzt oder priorisiert. Vielmehr weist jede Station **14** eine Ethernet-Interface-Karte auf, die einen Vielfachzugriff mit Leitungsabfrage mit Kollisionsdetektierung (CS-MA/CD) zum Beobachten des Datenverkehrs auf dem Medium anwendet. Das Nichtvorhanden sein von Netzverkehr wird durch Abfragen einer Deaktivierung eines Empfangs-Trägers auf dem Medium detektiert. Eine beliebige Station **14**, von der aus Daten gesendet werden sollen, versucht einen Zugriff auf den Kanal, indem sie eine vorbestimmte Zeit im Anschluss an die Deaktivierung eines Empfangs-Trägers auf dem Medium, die als Interpaket-Lücken-Intervall (IPG) bekannt ist, abwartet. Wenn mehrere Stationen **14** Daten im Netz versenden müssen, unternimmt jede Station einen Sendevorschuss in Reaktion auf die detektierte Deaktivierung des Empfangsträgers auf dem Medium nach dem IPG-Intervall, was zu einer Kollision führt. Aus diesem Grund überwacht die Sendestation das Medium um festzustellen, ob eine Kollision aufgrund von gleichzeitig von einer anderen Station aus gesendeten Daten aufgetreten ist. Wenn eine Kollision detektiert wird, brechen beide Stationen den Sendevorgang ab, warten einen willkürlich festgelegten Zeitraum und versuchen erneut,

eine Übertragung durchzuführen.

**[0019]** Die mit 100 Mb/s arbeitenden Netzstationen **16** werden vorzugsweise im Vollduplex-Modus nach dem vorgeschlagenen Ethernet-Standard IEEE 802.3x Full-Duplex with Flow Control – Working Draft (0.3) betrieben. Der Vollduplex-Betrieb bildet ein Zwei-Wege-Punkt-zu-Punkt-Datenübertragungslink zwischen jeder mit 100 Mb/s arbeitenden Netzstation **16** und dem Multiport-Schalter **12**, so dass der IMS und die betreffenden Stationen **16** Datenpakete ohne Kollision simultan senden und empfangen können. Die mit 100 Mb/s arbeitenden Netzstationen **16** sind jeweils über ebenfalls mit 100 Mb/s arbeitende reelle (PHY-) Vorrichtungen **26** vom Typ **100** Base-TX, **100** Base-T4 oder **100** Base-FX mit dem Netzmedium **18** gekoppelt. Der Multiport-Schalter **12** verfügt über ein medienunabhängiges Interface (MII) (**24**), das eine Verbindung zu den reellen Vorrichtungen **26** bildet. Die mit 100 Mb/s arbeitenden Netzstationen **16** können entweder als Server oder Router für die Verbindung mit anderen Netzen eingesetzt werden. Die mit 100 Mb/s arbeitenden Netzstationen **16** können auch im Halbduplex-Modus arbeiten, wenn dies gewünscht ist. Ähnlich können die mit 10 Mb/s arbeitenden Netzstationen **14** derart modifiziert werden, dass sie entsprechend dem Vollduplex-Protokoll mit Flusssteuerung arbeiten.

**[0020]** Wie in **Fig. 1** dargestellt, weist das paketgeschaltete Netz **10** diverse Schalt-Sendeempfänger **20** auf, die als QuEST bezeichnet sind, die das Zeitmultiplexing und das Zeitdemultiplexing für die zwischen dem Multiport-Schalter **12** und den mit 10 Mb/s arbeitenden Stationen **14** gesendeten Datenpakete durchführen. Ein magnetisches Transformatormodul **19** sorgt dafür, dass die Wellenform der Signale auf dem Medium **18** erhalten bleiben. Der Multiport-Schalter **12** weist ein Sendeempfänger-Interface **22** auf, über das das Senden und Empfangen der Datenpakete an jeden und von jedem Schalter-Sendeempfänger **20** unter Verwendung eines Zeitmultiplex-Protokolls über eine einzelne serielle Ohne-Rückkehr-zu-Null- (NRZ-) Interface-Leitung **24** erfolgt. Der Schalter-Sendeempfänger **20** empfängt Pakete von der Seriell-NRZ-Interface-Leitung **24**, demultiplext die empfangenen Pakete und gibt die Pakete über das Netzmedium **18** an die betreffende Endstation **14** aus. Bei dem offenbarten Ausführungsbeispiel weist jeder Schalter-Sendeempfänger **20** vier unabhängige, mit 10 Mb/s arbeitende Twisted-Pair-Ports auf und wendet ein 4 : 1-Multiplexing über das serielle NRZ-Interface zum Ermöglichen einer Verringerung der Anzahl von von dem Multiport-Schalter **12** benötigten PINs um das Vierfache an.

**[0021]** Der Multiport-Schalter **12** weist eine Entscheidungsfindungsmaschine, eine Umschaltmaschine, ein Pufferspeicher-Interface, Konfigurations-/Steuer-/Statusregister, Verwaltungszähler so-

wie ein MAC- (Medienzugriffssteuerungs-) Protokoll-Interface zur Unterstützung des Routing der Datenpakete zwischen den die Netzstationen **14** und **16** bedienenden Ethernet-Ports auf. Der Multiport-Schalter **12** weist ferner eine erweiterte Funktionalität zum Treffen intelligenter Umschalt-Entscheidungen und zum Liefern statischer Netzinformationen in Form von Managementinformationsbasis-(MIB-) Objekten an eine weiter unten beschriebene externe Managementeinheit auf. Es sind weitere Interfaces für das externe Speichern von Paketdaten sowie der Umschaltlogik zum Minimieren der Chipgröße des Multiport-Schalters **12** vorgesehen. So weist der Multiport-Schalter **12** beispielsweise ein SDRAM-Interface **32** auf, über das der Zugriff auf einen externen Speicher **34**, auf dem die empfangenen Datenblockdaten, Speicherstrukturen und MIB-Zählerdaten gespeichert sind, erfolgt. Als Speicher **34** kann ein 80-, 100- oder 120-MHz-SDRAM mit einer Speichergröße von 2 oder 4 Mb verwendet werden.

**[0022]** Ein Managementport **36** ermöglicht es einer externen Managementeinheit, den gesamten Betrieb des Multiport-Schalters **12** über ein Management-MAC-Interface **38** zu steuern. Ein PCI-Interface **39** ermöglicht einen Zugriff durch die Managementeinheit über einen PCI-Host und eine Brücke **40**. Alternativ können der PCI-Host und die Brücke **40** auch als Erweiterungsbus für mehrere IMS-Vorrichtungen verwendet werden.

**[0023]** Eine interne Entscheidungsfindungsmaschine im Schalter **12** überträgt selektiv die von einer Quelle empfangenen Datenpakete an mindestens eine Zielstation. Es besteht die Möglichkeit, diese interne Entscheidungsfindungsmaschine durch eine externe Regelprüfseinrichtung zu ersetzen. Ein External-Regelprüfseinrichtungs-Interface (ERCI) **42** ermöglicht es, anstelle der internen Entscheidungsfindungsmaschine eine externe Regelprüfereinrichtung **44** zur Entscheidungsfindung hinsichtlich der Weiterleitung von Datenblöcken zu verwenden. Somit können Entscheidungen zur Weiterleitung der Datenblöcke entweder von der internen Umschaltmaschine oder von der externen Regelprüfseinrichtung **44** getroffen werden.

**[0024]** Ein LED-Interface **46** taktet den Bedingungsstatus pro Port aus und treibt die LED-externe Logik **48**. Die LED-externe Logik **48** treibt ihrerseits für den Menschen lesbare LED-Anzeigeelemente **50**. Ein Oszillator **30** liefert ein 40 MHz-Takteingabesignal für die Systemfunktionen des Multiport-Schalters **12**.

**[0025]** **Fig. 2** zeigt ein detaillierteres Blockschaltbild eines erfindungsgemäßen Multiport-Schalters, der in dem in **Fig. 1** gezeigten paketgeschalteten System verwendet werden kann. Der Multiport-Schalter **12** enthält vierundzwanzig (24) mit 10 Mb/s arbeitende Medienzugangssteuer- (MAC-) Ports **60** für das Sen-

den und Empfangen von Datenpaketen im Halbduplex-Modus zwischen den betreffenden mit 10 Mb/s arbeitenden Netzstationen **14** (Ports 1–24) sowie zwei mit 100 Mb/s arbeitende MAC-Ports **62** für das Senden und Empfangen von Datenpaketen im Voll-duplex-Modus zwischen den betreffenden mit 100 Mb/s arbeitenden Netzstationen **16** (Ports 25, 26). Wie oben beschrieben, arbeitet das Management-Interface **36** auch gemäß dem MAC-Layer-Protokoll (Port 0).

**[0026]** Jeder der MAC-Ports **60**, **62** und **36** weist eine herkömmliche Logik- und Registerzugriffssteuer-Schaltungsanordnung auf, die eine Steuerung der Datenübertragung, des Datenempfangs und der Vermittlung bei Kollisionen an dem Port ermöglicht. Ein Empfangs-FIFO-Puffer **64** und ein Sende-FIFO-Puffer **66** sind ebenfalls an jedem Port vorgesehen. Ein Externspeicher-Interface **32** ist über einen gemeinsamen Bus mit jedem der MAC-Empfangs-FIFO-Puffer und über einen weiteren gemeinsamen Bus mit jedem der MAC-Sende-FIFO-Puffer verbunden.

**[0027]** Datenpakete von einer Netzstation werden vom betreffenden MAC-Port empfangen und in dem entsprechenden Empfangs-FIFO-Puffer **64** gespeichert. Das empfangene Datenpaket wird von dem betreffenden Empfangs-FIFO-Puffer **64** an das Externspeicher-Interface **32** zur Speicherung im Externspeicher **34** ausgegeben.

**[0028]** Die Kopfdaten des empfangenen Pakets werden ebenfalls an eine Entscheidungsfindungsma schine mit einer internen Regelprüfseinrichtung **68** und einem Extern-Regelprüfseinrichtungs-Interface **42** weitergeleitet, um zu ermitteln, an welchen MAC-Ports die Ausgabe des Datenpaket erfolgt. Ob die Paketkopfdaten an die interne Regelprüfseinrichtung **68** oder an das Extern-Regelprüfseinrichtungs-Interface **42** weitergeleitet werden, ist von der Operationskonfiguration des Multiport-Schalters **12** abhängig. Die Verwendung der externen Regelprüfseinrichtung **44** bietet Vorteile, wie z. B. eine höhere Kapazität, eine willkürliche Einreihung in der Entscheidungsfindungs-Warteschlange, wodurch es möglich ist, dass Datenblock-Weiterleitungs-Entscheidungen getroffen werden, bevor der Datenblock vollständig in dem Externspeicher gepuffert ist, und es möglich ist, dass Entscheidungen in einer von der Reihenfolge, in der die Datenblöcke von dem Multiport-Schalter **12** empfangen werden, unabhängigen Reihenfolge getroffen werden.

**[0029]** Die interne Regelprüfseinrichtung **68** und die externe Regelprüfseinrichtung **44** bilden die Entscheidungsfindungs-Logik zum Bestimmen des Ziel-MAC-Ports für ein bestimmtes Datenpaket. Die Entscheidungsfindungsma schine kann die Ausgabe eines Datenpaket entweder an einen einzelnen Port, an mehrere Ports oder an sämtliche Ports (bei-

spielsweise Rundsenden) anzeigen. Jedes Datenpaket enthält einen Kopf, in welchem die Ausgangs- und die Zieladresse angegeben sind, gemäß der die Entscheidungsfindungsma schine den (die) entsprechenden Ausgangs-MAC-Ports identifizieren kann. Die Zieladresse kann einer virtuellen Adresse entsprechen, und in diesem Fall identifiziert die Entscheidungsfindungsma schine die Ausgangs-Ports für mehrere Netzstationen. Alternativ kann das empfangene Datenpaket auch einen als VLAN (virtuelles LAN) gekennzeichneten Datenabschnitt nach dem IEEE 802.1d-Protokoll enthalten, in dem ein anderes Netz (über mit 100 Mb/s arbeitende Stationen **16**) oder eine vorgeschriebene Gruppe von Stationen angegeben ist. In diesem Fall muss entweder die interne Regelprüfseinrichtung **68** oder die externe Regelprüfseinrichtung **44** über das Interface **42** entscheiden, ob ein temporär im Pufferspeicher **34** gespeicherter Datenblock an einen einzelnen MAC-Port oder an mehrere MAC-Ports ausgegeben werden soll.

**[0030]** Die Entscheidungsfindungsma schine gibt eine Weiterleitungsentscheidung an ein Schaltersubsystem **70** in Form eines Portvektors aus, welcher jeden MAC-Ports identifiziert, an dem das Datenpaket empfangen werden soll. Der Portvektor von der entsprechenden Regelprüfseinrichtung enthält die Speicheradresse für das Datenpaket im externen Speicher **34** und die Identifizierung der MAC-Ports, an denen das Datenpaket zu Sendeziwecken empfangen werden soll (z. B. MAC-Ports 0–26). Das Schaltersubsystem **70** holt das im Portvektor angegebene Datenpaket über das Externspeicher-Interface **32** aus dem Externspeicher **34** und liefert das wiedergewonnenen Datenpaket zu dem entsprechenden FIFO **66** der identifizierten Ports.

**[0031]** Weitere Interfaces liefern Management- und Steuerinformationen, wie anhand der folgenden Elemente beispielhaft erläutert. So bietet beispielsweise ein Managementdaten-Interface **72** dem Multiport-Schalter **12** die Möglichkeit, Steuer- und Statusinformationen gemäß der MIL-Management-Spezifikation (IEEE 802.3u) mit den Schalter-Sendeempfängern **20** und den mit 100 Mb/s arbeitenden reellen Vorrichtungen **26** auszutauschen. Das Managementdaten-Interface **72** gibt ferner einen Managementdatentakt (MDC) aus, welcher einen Zeitbezug auf dem bidirektionalen Managementdaten-IO- (MDIO-) Signalpfad herstellt. Das PCI-Interface **39** ist ein 32-Bit-Slave-Interface nach PCI-Revision 2.1 für den Zugriff des PCI-Host-Prozessors **40** auf die internen IMS-Status- und Konfigurationsregister **74** sowie für den Zugriff auf den Externspeicher SDRAM **34**. Das PCI-Interface **39** kann darüber hinaus auch als Erweiterungsbus für mehrere IMS-Vorrichtungen dienen. Der Managementport **36** stellt über ein standardmäßiges siebenadriges invertiertes serielles GPSI-Interface eine Verbindung zu einer externen

MAC-Maschine her und ermöglicht so einen Zugriff des Host-Controllers auf den Multiport-Schalter **12** unter Verwendung eines Standard-MAC-Layer-Protokolls.

**[0032]** Fig. 3 ist ein Blockschaltbild mit Darstellung der Medienzugriffssteuerung für das in Fig. 1 gezeigte System gemäß der vorliegenden Erfindung. Im Gegensatz zu der in Fig. 2 gezeigten Anordnung ist eine einzelne Medienzugriffs-Steuerlogikeinheit **80** zur gemeinsamen Verwendung durch die vierundzwanzig (24) mit 10 Mb/s arbeitenden Schaltparts **60** und den MII-Management-Steuerport vorgesehen. Die Einheit **80** ist über eine Sendeverbindung und eine Empfangsverbindung mit dem Sendeempfänger-Interface **22** verbunden. Die Einheit **80** ist ferner mit dem Sende-FIFO **66** und dem Empfangs-FIFO **64** an jedem Port **60** verbunden. Es sei darauf hingewiesen, dass zur einfacheren Darstellung zwar nur ein einzelner Port-FIFO-Paar gezeigt ist, jedoch die entsprechenden FIFOs sämtlicher Ports **60** repräsentiert sind. FIFO **64** und FIFO **66** sind mit einem Bus **84** verbunden. Obwohl als einzelne Leitung gezeigt, repräsentiert der Bus **84** eine gemeinsame Empfangsbusverbindung für sämtliche Port-**60**-Empfangs-FIFOs und das Externspeicher-Interface **32** sowie eine gemeinsame Sendebusverbindung für sämtliche Port-**60**-Sende-FIFOs und das Externspeicher-Interface **32**.

**[0033]** Eine Zustandsspeicher-Steuereinheit **82** speichert den Medienzugriffszustand jedes Ports **60**. Die Einheit **82** ist zur Übermittlung von Zustandsdaten mit der Medienzugriffs-Steuerlogikeinheit **80** verbunden. Es besteht ferner eine Datenübertragung zwischen der Zustandsspeicher-Steuereinheit **82** und dem Sendeempfänger-Interface **22**. Die Zustandsspeicher-Steuereinheit **82** weist einen Takteingang zum Empfangen eines 80 MHz-Signals auf. Wie nachstehend genauer beschrieben, bewirkt dieses Taktignal eine Synchronisier-Zeitgebung für eine Zeitteil-Medienzugriffssteuer-Funktionalität, die von der Logikeinheit **80** für jeden der vierundzwanzig Schaltparts **60** durchgeführt wird.

**[0034]** Fig. 4 zeigt ein detaillierteres Blockschaltbild einer bevorzugten Konfiguration der Medienzugriffs-Steuerlogikeinheit **80** und der Zustandsspeicher-Steuereinheit **82** aus Fig. 3. Die Zustandsspeicher-Steuereinheit **82** weist einen Zustandsspeicher **90**, ein Ausgangsregister **92**, ein Eingangsregister **94**, einen Zähler **96** und eine Verzögerungsschaltung **98** auf. Der Zustandsspeicher **90**, in dem die Zugriffszustände an jedem Port **60** gespeichert sind, kann beispielsweise als Direktzugriffsspeicher (RAM) oder als ein oder mehrere für jeden Port **60** zweckbestimmte Register ausgebildet sein. Das Ausgangsregister **92** und das Eingangsregister **94** sind mit dem Zustandsspeicher **90** verbunden, um Daten von dem Zustandsspeicher zu empfangen bzw. Daten in den

Zustandsspeicher einzugeben. Der Zähler **96**, der einen Eingang von der 80-MHz-Taktquelle aufweist, gibt ein Datensignal mit einer ausreichenden Anzahl von Bits aus, um jeden Port **60** eindeutig zu identifizieren. Bei der in Fig. 1 gezeigten Ausführungsform mit vierundzwanzig Ports hat das Zähler-Ausgangssignal vorzugsweise eine Länge von fünf Bits. Dieses Signal wird bei jedem empfangenen Taktimpuls inkrementiert.

**[0035]** Das Zähler-Ausgangssignal wird an das Ausgangsregister **92** angelegt, wodurch der Port identifiziert wird, für den von dem Zustandsspeicher **90** aus auf die Daten des Zustandsspeichers zugegriffen wird. Das Zähler-Ausgangssignal wird ferner an die Verzögerungsschaltung **98** angelegt, die das Signal über mehrere Taktstufen hält und verzögert. Das Ausgangssignal der Verzögerungsschaltung **98** wird an das Eingangsregister **94** angelegt, wodurch derjenige Port identifiziert wird, für den Daten in dem Zustandsspeicher **90** gespeichert werden. Somit ist der Zeitraum zwischen dem Wiedergewinnen gespeicherter Daten für einen bestimmten Port und dem Schreiben neuer Daten für diesen Port von der Anzahl von von der Verzögerungsschaltung **98** verzögerten Taktstufen abhängig. Das Bestimmen dieser Anzahl wird mit der Anzahl von der Medienzugriffs-Steuerlogikeinheit **80** benötigten Takt-Pipeline-Stufen koordiniert. Die Register sowie die Zähler- und Verzögerungsschaltungen sind jeweils herkömmliche bekannte Elemente.

**[0036]** Das Verarbeiten der Medienzugriffs-Steuerfunktionen und der Zugriffszustandsanzeige erfolgt in der kombinatorischen Logikeinheit **100**, die mehrere Logikgatter aufweist. Register **102** sind mit Eingangsdaten für die Logikeinheit verbunden, die von dem Zustandsausgangsregister **92** und dem Sendeempfänger-Interface **22** kommen. Nach dem Verarbeiten der von den Registern **102** kommenden Daten gibt die Logikeinheit die verarbeiteten Daten an Register **104** aus. Diese verarbeiteten Daten enthalten zu den FIFOs an den diesen zugeordneten Ports zu sendende Befehle, zu übermittelnde Kommunikationsdaten und die Veränderungen, falls solche vorhanden sind, des Port-Zugriffszustands, wobei letztere an das Zustandseingangsregister **94** gesendet werden. Der Dateneingang in die Register **102**, die Übermittlung von Daten von den Registern **102** an die Logikeinheit **100** zu Verarbeitungszwecken, die Übermittlung von verarbeiteten Daten von den Registern **104** zu dem Zustandseingangsregister **94** und das Aktualisieren des Zustandsspeichers **90** erfolgt in sequentiellen getakteten Pipeline-Stufen.

**[0037]** Fig. 5 zeigt ein Wellenformdiagramm mit Darstellung der gestuften Pipeline-Operation. Bei der bevorzugten Ausführungsform weist die Verzögerungsschaltung **98** zwei Verzögerungsstufen auf. Wellenform (a) repräsentiert das 80 MHz-Taktsignal.

Wellenform (b) repräsentiert das Ausgangssignal des Zählers **96** bei jedem Zyklus des Taktsignals mit der Wellenform (a). Dieses Signal identifiziert einen MAC-Port und wird mit jedem Taktsignal inkrementiert, wodurch eine sequentielle Operation auf Zeitteilbasis erzeugt wird. Jeder Taktzyklus definiert somit einen "MAC-Schlitz" entsprechend einem von einem Zähler identifizierten Port. Zu Erläuterungszwecken handelt es sich bei dem während des ersten Taktzyklus von dem Zählerausgang identifizierten MAC-Schlitz um Schlitz **16**. Wellenformen (c) und (d) repräsentieren eine MAC-Schlitz-Identifizierung für zwei Verzögerungsstufen während jedes Taktsignalzyklus. Somit wird der MAC-Schlitz **16** während des zweiten Taktzyklus von der Wellenform (c) und während des dritten Taktzyklus von der Wellenform (d) angezeigt.

**[0038]** Jede Wellenform (b) bis (c) ist einer von drei Stufen einer Medienzugriffs-Steueraktivität (in der Figur durch die Bezeichnungen "Einkoppeln", "Einfangen" und "Aktualisieren" angezeigt) zugeordnet und identifiziert somit den MAC-Port, auf den sich diese Aktivität bezieht. Die drei Aktivitäten laufen während jedes Taktzyklus für unterschiedliche MAC-Ports jeweils gleichzeitig ab. Die Figur zeigt die drei Stufen der Operation für den MAC-Port **16**. Die Einkoppel-Stufe für diesen Port erfolgt bei dem ersten dargestellten Taktzyklus. Während dieses Zyklus identifiziert der Zähler den Port **16**, für den von dem Zustandsspeicher **90** aus auf Daten zugegriffen wird, die in dem Register **92** gehalten werden. Während des nächsten Taktzyklus läuft die Einfang-Stufe für den MAC-Port **16** ab. Daten aus dem Register **92** und von dem Sendeempfänger-Interface werden dann in die Register **80** eingegeben und von der kombinatorischen Logikeinheit **100** verarbeitet, und die daraus resultierenden Daten werden in den Registern **104** gehalten. Während dieses Zyklus hat ferner der Zähler den nächsten MAC-Port für eine Einkoppel-Stufen-Operation identifiziert. Während des nächsten Taktzyklus läuft die Aktualisierungs-Stufe für den MAC-Port **16** ab. Zustandsaktualisierungsdaten aus den Registern **104** werden an das Eingangsregister **94** übermittelt und in dem Zustandsspeicher **90** gespeichert. Operationsdaten werden an den entsprechenden FIFO übermittelt. Die Medienzugriffssteuerung geht für jeden MAC-Port sequentiell auf diese Weise weiter.

**[0039]** Die vorliegende Erfindung bietet somit auf vorteilhafte Weise eine Medienzugriffssteuerung bei Beibehaltung der Chip-Architektur. Nur die bevorzugte Ausführungform der Erfindung und nur einige wenige Beispiele ihrer vielseitigen Anwendbarkeit sind in der vorliegenden Offenbarung dargestellt und beschrieben. Es sei darauf hingewiesen, dass die Erfindung in verschiedenen anderen Kombinationen und Umgebungen verwendet werden kann und innerhalb des Umfangs des erfindungsgemäßen Konzepts, wie

es hier dargestellt ist, verändert oder modifiziert werden kann.

## Patentansprüche

1. Integrierter Multiport-Netzschatzer (**12**) zum Anschließen an ein Datennetz zwecks Ermöglichung einer Datenübertragung zwischen mehreren mit dem Datennetz gekoppelten Fernstationen, wobei der Schalter einen Logik-Chip aufweist, der folgendes umfasst:

mehrere Ports (**60, 62**) zum Übermitteln von Datenblöcken zu und Empfangen von Datenblöcken von dem Datennetz; und

eine zentral auf dem Chip angeordnete Medienzugriffssteuer- (MAC-) Schaltungsanordnung (**80**) zum Steuern des Datenblockflusses an jedem Port, wobei die MAC-Schaltungsanordnung auf Zeitteilbasis jeweils mit jedem Port gekoppelt ist;

**dadurch gekennzeichnet**, dass

die MAC-Schaltungsanordnung (**80**) eine Logik-Schaltungseinrichtung (**100, 102, 104**) zum Durchführen von Medienzugriffs-Steuerfunktionen und eine Zustandsspeichereinrichtung (**82**) zum Speichern von Medienzugriffszuständen der mehreren Ports (**60**) aufweist.

2. Integrierter Multiport-Netzschatzer nach Anspruch 1, bei dem die Medienzugriffs-Steuerfunktionen Datenübermittlung, Datenempfang und Vermittlung bei Datenkollisionen umfassen.

3. Integrierter Multiport-Netzschatzer nach Anspruch 1 oder 2, ferner mit mindestens einem Eingangsempfangs-FIFO-Puffer (**64**) an jedem Port zum temporären Halten von aus dem Netz empfangenen Datenblöcken an dem jeweiligen Port und mindestens einem Sende-FIFO-Puffer (**66**) an jedem Port zum temporären Halten von an das Netz zu übermittelnden Datenblöcken an dem jeweiligen Port, wobei der FIFO-Puffer (**64, 66**) mit der Logik-Schaltungseinrichtung (**100, 102, 104**) gekoppelt ist.

4. Integrierter Multiport-Netzschatzer nach Anspruch 3, bei dem der Schalter (**12**) mehrere jeweiligen Netz-Fernstationen (**14**) zugeordnete Schalter-Sendeempfänger (**20**) aufweist und der Chip ferner umfasst:

ein zwischen der Logik-Schaltungseinrichtung (**100, 102, 104**) und den mehreren Schalter-Sendeempfängern (**20**) gekoppeltes Zeitmultiplex/-demultiplex-Sendeempfänger-Interface (**22**).

5. Integrierter Multiport-Netzschatzer nach Anspruch 4, bei dem mindestens einer der Schalter-Sendeempfänger (**20**) eine Multiplex-/Demultiplexeinrichtung für die Zeitteilung von Datenübertragungen für mehrere Fernstationen (**14**) aufweist.

6. Integrierter Multiport-Netzschatzer nach An-

spruch 5, bei dem die Zustandsspeichereinrichtung (82) aufweist:

einen Datenspeicher (90) mit Teilbereichen, die jeweils Daten zugewiesen sind, die den aktuellen Zustand jedes Ports repräsentieren;

ein mit dem Datenspeicher (90) gekoppeltes Ausgangsregister (92) zum Empfangen gespeicherter Daten aus dem Datenspeicher, die den Zustand eines ersten bestimmten der Ports (60) repräsentieren, wobei das Ausgangsregister (92) zum Ausgeben von Daten an die Logik-Schaltungseinrichtung (100, 102, 104) mit dieser gekoppelt ist;

ein mit der Logik-Schaltungseinrichtung (100, 102, 104) gekoppeltes Eingangsregister (94) zum Empfangen von Daten von der Logik-Schaltungseinrichtung, die den Zustand eines zweiten bestimmten der Ports (60) repräsentieren, wobei das Eingangsregister zum Eingeben von Daten in den Datenspeicher (90) mit diesem gekoppelt ist; und

eine Zugriffseinrichtung (96, 98) zum Zugreifen auf die Datenspeicher-Teilbereiche in sequentiellen getakteten Stufen.

7. Integrierter Multiport-Netzschalter nach Anspruch 6, bei dem die Datenspeicher-Teilbereiche durch Schalterportadressen identifiziert werden und die Zugriffseinrichtung aufweist:

einen Zähler (96), der auf ein Taktsignal anspricht und zum sequentiellen Zuführen einer Portadresse, für die Daten aus dem entsprechenden Datenspeicher-Teilbereich zurückgewonnen werden, zu dem Ausgangsregister (92) mit diesem gekoppelt ist; und eine zwischen dem Zähler (96) und dem Eingangsregister (94) geschaltete Verzögerungseinrichtung (98) zum Verzögern des Anlegens der von dem Zähler (96) gelieferten Portadresse an das Eingangsregister um mindestens eine Taktstufe;

wobei aktualisierte Medienzugriffs-Zustandsdaten für die von dem Zähler gelieferte Portadresse von der Logik-Schaltungseinrichtung (100, 102, 104) empfangen und an den entsprechenden Datenspeicher-Teilbereich angelegt werden.

8. Integrierter Multiport-Netzschalter nach Anspruch 7, bei dem die Logik-Schaltungseinrichtung (100, 102, 104) Register (102) mit einem ersten Eingang zum Empfangen von Daten aus dem Ausgangsregister (92) und einem zweiten Eingang zum Empfangen von Daten von dem Sendeempfänger-Interface aufweist.

9. Verfahren zum Steuern eines Medienzugriffs an mehreren Ports eines integrierten Multiport-Netzschalters (12) mit einem Logik-Chip, der mit einem Datennetz gekoppelt ist, um eine Datenübertragung zwischen mehreren mit dem Datennetz verbundenen Fernstationen (14) zu ermöglichen,

gekennzeichnet durch folgende Schritte:

sequentielles Auslesen des Zugriffszustands jedes der mehreren Ports (60, 62) aus einer Zustandsspei-

chereinrichtung (82), die zentral auf dem Logik-Chip angeordnet ist und gemeinsam für sämtliche Ports vorgesehen ist;

im Anschluss an jeden sequentiellen Ausleseschritt, Ausführen einer Datenübertragungs-Zugriffsfunktion an dem entsprechenden Port in Reaktion auf von einem mit dem Port gekoppelten Sendeempfänger-Interface (22) empfangene Daten; und

im Anschluss an jeden Ausführschritt, Aktualisieren der gemeinsamen Zustandsspeichereinrichtung (82); wobei der Ausführschritt umfasst:

Verarbeiten von in dem Ausleseschritt ausgelesenen Daten und von dem Interface (22) empfangenen Daten in einer Logik-Schaltungseinrichtung (100, 102, 104), die zentral auf dem Logik-Chip angeordnet ist und gemeinsam für sämtliche Ports vorgesehen ist; und

Erzeugen neuer Zustandsdaten für den Port in der gemeinsamen Logik-Schaltungseinrichtung (100, 102, 104).

10. Verfahren nach Anspruch 9, bei dem der Schritt des sequentiellen Auslesens das Adressieren der Zustandsspeichereinrichtung (82) in Reaktion auf das Ausgangssignal eines getakteten Zählers umfasst und der Aktualisierungsschritt umfasst:

Verzögern des Ausgangssignals des getakteten Zählers;

Adressieren der Zustandsspeichereinrichtung (82) in Reaktion auf das verzögerte Ausgangssignal des getakteten Zählers; und

Schreiben neuer Zustandsdaten in die Zustandsspeichereinrichtung (82) an der in dem Adressierschritt verwendeten Adresse.

11. Verfahren nach Anspruch 9 oder 10, bei dem der Ausführschritt das Senden von in einem Sende puffer (66) gespeicherten Daten an dem Port zu dem Datennetz umfasst.

12. Verfahren nach Anspruch 9, 10 oder 11, bei dem der Ausführschritt das Empfangen von Daten aus dem Netz an einem Empfangspuffer (64) an dem Port umfasst.

13. Verfahren nach Anspruch 9, 10, 11 oder 12, bei dem der Ausführschritt das Vermitteln bei einer Datenkollision an dem Port umfasst.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen

Fig. 1

Fig. 2

Fig. 2A

Fig. 2B

Fig. 3

Fig. 4

Fig. 5