(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0130205

(43) 공개일자 2010년12월10일

(51) Int. Cl.

H03M 1/50 (2006.01)

(21) 출원번호 10-2010-7021650

(22) 출원일자(국제출원일자) 2009년03월03일

심사청구일자 2010년09월28일

(85) 번역문제출일자 2010년09월28일

(86) 국제출원번호 PCT/US2009/035908

(87) 국제공개번호 WO 2009/111491

국제공개일자 2009년09월11일

(30) 우선권주장

12/041,403 2008년03월03일 미국(US)

(71) 출원인

웰컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 별명자

선보

미국 92121 캘리포니아주 샌디에고 모어하우스 드라이브 5775

양 쪽상

미국 92121 캘리포니아주 샌디에고 모어하우스 드라이브 5775

(74) 대리인

특허법인코리아나

전체 청구항 수 : 총 28 항

(54) 고속 시간-디지털 변환기

### (57) 요 약

시간-디지털 변환기 (TDC) 가 서보-인버터 지연 리졸루션으로 샘플링 할 수 있게 하기 위한 기술들이 개시된다. 일 실시형태에서, TDC 내의 차동 D-Q 플립-플롭에 대한 입력들은 싱글-엔디드 신호에 커플링되며, 그 신호의 지연된 및 인버팅된 버전은 그 신호의 시간 보간을 허용한다. 제 1 지연 라인의 부하들과 TDC 내의 상보적인 지연 라인의 부하들을 벨런싱하기 위한 기술들이 추가적으로 개시된다.

### 대 표 도

FIG. 3

## 특허청구의 범위

### 청구항 1

시간-디지털 변환기 (TDC)로서,

신호 A의 적어도 하나의 지연된 버전  $A(m)$  을 생성하기 위한 지연 라인으로서, 상기  $A(m)$  은  $m$  지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 지연 라인; 및

일 시간 인스턴트에서 상기  $A(m)$  과 신호  $B[A(m)]$  사이의 차이를 샘플링하기 위한 샘플링 메커니즘으로서, 상기 신호  $B[A(m)]$  은 적어도 하나의 지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 샘플링 메커니즘을 포함하는, 시간-디지털 변환기.

### 청구항 2

제 1 항에 있어서,

상기 신호  $B[A(m)]$  은 신호  $A(m+1)$  이며,

상기 신호  $A(m+1)$  은  $m+1$  지연 유닛만큼 상기 신호 A에 대해 지연되는, 시간-디지털 변환기.

### 청구항 3

제 2 항에 있어서,

각각의 지연 유닛은 유닛 버퍼의 지연에 대응하는, 시간-디지털 변환기.

### 청구항 4

제 3 항에 있어서,

상기 유닛 버퍼는 단일 인버터인, 시간-디지털 변환기.

### 청구항 5

제 1 항에 있어서,

상기 샘플링 메커니즘은 차동 D-Q 플립-플롭이며,

상기 차동 D-Q 플립-플롭의 입력 D에 신호  $A(n)$  가 커플링되고, D-Q 플립-플롭의 입력 D'에 상기 신호 B가 커플링되는, 시간-디지털 변환기.

### 청구항 6

제 5 항에 있어서,

상기 차동 D-Q 플립-플롭은 차동 입력  $D/D'$  의 전압 극성을 샘플링하는, 시간-디지털 변환기.

### 청구항 7

제 5 항에 있어서,

상기 지연 라인은, 또한, 상기 신호 A의 복수의 지연된 버전들  $A(n)$  을 생성하고,

상기 샘플링 메커니즘은, 또한, 상기 신호들  $A(n)$  의 각각 및 대응하는 신호  $B[A(n)]$  사이의 차이를 샘플링하며,

각각의  $B[A(n)]$  은 대응하는  $A(n)$  에 대해 상기 적어도 하나의 지연 유닛만큼 지연되는, 시간-디지털 변환기.

### 청구항 8

제 7 항에 있어서,

상기 신호 A에 상보적인 신호  $A'$  의 복수의 지연된 버전들  $A'(n)$  을 생성하기 위한 상보적인 지연 라인을 더 포

함하며,

상기 시간-디지털 변환기는, 각각의 신호  $A(n)$  와 대응하는 신호  $A'(n)$  사이의 차이를 샘플링하기 위한 복수의 차동 D-Q 플립-플롭들을 더 포함하는, 시간-디지털 변환기.

### 청구항 9

제 8 항에 있어서,

상기 상보적인 지연 라인은, 상기 상보적인 지연 라인의 부하와 상기 지연 라인의 부하를 별련성하기 위해 적어도 하나의 부하에 커플링되는, 시간-디지털 변환기.

### 청구항 10

시간 간격을 디지털 표현으로 변환하기 위한 방법으로서,

신호 A의 적어도 하나의 지연된 버전  $A(m)$  을 생성하는 단계로서, 상기  $A(m)$  은  $m$  지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 생성하는 단계; 및

일 시간 인스턴트에서 상기  $A(m)$  과 신호  $B[A(m)]$  사이의 차이를 샘플링하는 단계로서, 상기 신호  $B[A(m)]$  은 적어도 하나의 지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 샘플링하는 단계를 포함하는, 변환 방법.

### 청구항 11

제 10 항에 있어서,

상기 신호  $B[A(m)]$  은 신호  $A(m+1)$  이며,

상기 신호  $A(m+1)$  은  $m+1$  지연 유닛만큼 상기 신호 A에 대해 지연되는, 변환 방법.

### 청구항 12

제 11 항에 있어서,

각각의 지연 유닛은 유닛 버퍼의 지연에 대응하는, 변환 방법.

### 청구항 13

제 12 항에 있어서,

상기 유닛 버퍼는 단일 인버터인, 변환 방법.

### 청구항 14

제 10 항에 있어서,

상기 샘플링하는 단계는 차동 D-Q 플립-플롭에 의해 수행되며,

상기 차동 D-Q 플립-플롭의 입력 D에 신호  $A(n)$  가 커플링되고, 상기 차동 D-Q 플립-플롭의 입력  $D'$ 에 상기 신호 B가 커플링되는, 변환 방법.

### 청구항 15

제 14 항에 있어서,

상기 차동 D-Q 플립-플롭은 차동 입력  $D/D'$ 의 전압 극성을 샘플링하는, 변환 방법.

### 청구항 16

제 14 항에 있어서,

상기 신호 A의 복수의 지연된 버전들  $A(n)$  을 생성하는 단계를 더 포함하며,

상기 샘플링 메커니즘은, 상기 신호들  $A(n)$  의 각각과 대응하는 신호  $B[A(n)]$  사이의 차이를 샘플링하는 단계를 더 포함하고,

각각의 신호  $B[A(n)]$  은 대응하는  $A(n)$  에 대해 상기 적어도 하나의 지연 유닛만큼 지연되는, 변환 방법.

### 청구항 17

제 16 항에 있어서,

상기 신호  $A$ 에 상보적인 신호  $A'$  의 복수의 지연된 버전들  $A'(n)$  을 생성하는 단계를 더 포함하며,

상기 변환 방법은, 각각의 신호  $A(n)$  와 대응하는 신호  $A'(n)$  사이의 차이를 샘플링하는 단계를 더 포함하는, 변환 방법.

### 청구항 18

제 17 항에 있어서,

적어도 하나의 부하를 상기 신호들  $A'(n)$  을 생성하기 위한 지연 라인에 커플링하여, 상기 지연 라인을 상기 신호들  $A(n)$  을 생성하기 위한 지연 라인과 별련성하는 단계를 더 포함하는, 변환 방법.

### 청구항 19

시간-디지털 변환기 (TDC) 로서,

신호  $A$ 의 적어도 하나의 지연된 버전  $A(m)$  을 생성하는 수단으로서, 상기  $A(m)$  은  $m$  지연 유닛만큼 상기 신호  $A$ 에 대해 지연되는, 상기 생성하는 수단; 및

일 시간 인스턴트에서 상기  $A(m)$  과 신호  $B[A(m)]$  사이의 차이를 샘플링하는 수단으로서, 상기 신호  $B[A(m)]$  은 적어도 하나의 지연 유닛만큼 상기 신호  $A$ 에 대해 지연되는, 상기 샘플링하는 수단을 포함하는, 시간-디지털 변환기.

### 청구항 20

제 19 항에 있어서,

상기 신호  $B[A(m)]$  은 신호  $A(m+1)$  이며,

상기 신호  $A(m+1)$  은  $m+1$  지연 유닛만큼 상기 신호  $A$ 에 대해 지연되는, 시간-디지털 변환기.

### 청구항 21

제 20 항에 있어서,

각각의 지연 유닛은 유닛 버퍼의 지연에 대응하는, 시간-디지털 변환기.

### 청구항 22

제 21 항에 있어서,

상기 유닛 버퍼는 단일 인버터인, 시간-디지털 변환기.

### 청구항 23

제 19 항에 있어서,

상기 차이를 샘플링하는 수단은 D-Q 플립-플롭을 포함하며,

상기 D-Q 플립-플롭의 입력  $D$ 에 신호  $A(n)$  가 커플링되고, 상기 D-Q 플립-플롭의 입력  $D'$  에 신호  $B$ 가 커플링되는, 시간-디지털 변환기.

### 청구항 24

시간 간격을 디지털 표현으로 변환하기 위한, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품으로서,

상기 컴퓨터-판독가능 매체는,

컴퓨터로 하여금, 신호  $A$ 의 적어도 하나의 지연된 버전  $A(m)$  을 생성하게 하기 위한 코드로서, 상기  $A(m)$  은  $m$

지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 생성하게 하기 위한 코드; 및

컴퓨터로 하여금, 일 시간 인스턴트에서 상기 A(m) 과 신호 B[A(m)] 사이의 차이를 샘플링하게 하기 위한 코드로서, 상기 신호 B[A(m)] 은 적어도 하나의 지연 유닛만큼 상기 신호 A에 대해 지연되는, 상기 샘플링하게 하기 위한 코드를 포함하는, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품.

### 청구항 25

제 24 항에 있어서,

상기 신호 B[A(m)] 은 신호 A(m+1) 이며,

상기 컴퓨터-판독가능 매체는, 상기 신호 A(m+1) 로 하여금 m+1 지연 유닛만큼 상기 신호 A에 대해 지연되게 하기 위한 코드를 더 포함하는, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품.

### 청구항 26

제 25 항에 있어서,

각각의 지연 유닛은 유닛 베퍼의 지연에 대응하는, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품.

### 청구항 27

제 24 항에 있어서,

상기 컴퓨터로 하여금 차이를 샘플링하게 하기 위한 코드는,

상기 샘플링이 차동 D-Q 플립-플롭에 의해 수행되게 하기 위한 코드;

상기 차동 D-Q 플립-플롭의 입력 D에 신호 A(n) 를 커플링하게 하기 위한 코드; 및

상기 차동 D-Q 플립-플롭의 입력 D' 에 상기 신호 B를 커플링하게 하기 위한 코드를 포함하는, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품.

### 청구항 28

제 27 항에 있어서,

상기 컴퓨터-판독가능 매체는,

컴퓨터로 하여금, 상기 신호 A의 복수의 지연된 버전들 A(n) 을 생성하게 하기 위한 코드를 더 포함하며,

각각의 B[A(n)] 은 대응하는 A(n) 에 대해 상기 적어도 하나의 지연 유닛만큼 지연되는, 컴퓨터-판독가능 매체를 포함하는 컴퓨터 프로그램 제품.

## 명세서

### 기술 분야

[0001]

본 발명은 시간-디지털 변환기 (TDC) 의 설계에 관한 것으로, 더 상세하게는, 서브-유닛 지연 리졸루션 (resolution) 을 갖는 TDC의 설계에 관한 것이다.

### 배경 기술

[0002]

시간-디지털 변환기들은, 2개의 이벤트들 사이에서 경과하는 시간 간격의 디지털 표현을 생성하도록 설계된다.

아날로그-디지털 변환기 (ADC) 들이 아날로그 신호 진폭을 이산화 (discretize) 시킴에 따라, TDC들은 시간 간격을 이산화시킨다. 실제 시간 간격과 그 시간 간격의 이산화된 버전 사이의 차이는 양자화 에러로 공지되어 있으며, TDC 리졸루션에 의해 결정된다.

[0003]

통상적으로, TDC 리졸루션은 TDC의 지연 라인에서의 유닛 셀의 지연에 의해 제한된다. 예를 들어, 그 지연은, 인버터의 게이트 지연일 수도 있으며, 이용되는 특정한 반도체 프로세싱 기술의 특징이다. 특정한 고속 TDC 애플리케이션에 대해, 유닛 셀의 지연을 넘어서 TDC 리졸루션을 개선시키기 위한 설계 기술들을 갖는 것이 바람직할 것이다.

## 발명의 내용

### 과제의 해결 수단

[0004] 본 발명의 일 양태는, 신호 A의 지연된 버전 A(m) 을 생성하기 위한 지연 라인으로서, A(m) 은 m 지연 유닛만큼 A에 대해 지연되는, 그 지연 라인; 및 시간 인스턴트에서 A(m) 과 신호 B[A(m)] 사이의 차이를 샘플링하기 위한 샘플링 메커니즘으로서, B[A(m)] 은 적어도 하나의 지연 유닛만큼 A에 대해 지연되는, 그 샘플링 메커니즘을 포함하는 시간-디지털 변환기를 제공한다.

[0005] 본 발명의 또 다른 양태는 시간 간격을 디지털 표현으로 변환하기 위한 방법을 제공하며, 그 방법은, 신호 A의 적어도 하나의 지연된 버전 A(m) 을 생성하는 단계로서, A(m) 은 m 지연 유닛만큼 A에 대해 지연되는, 그 생성하는 단계; 및 시간 인스턴트에서 A(m) 과 신호 B[A(m)] 사이의 차이를 샘플링하는 단계로서, B[A(m)] 은 적어도 하나의 지연 유닛만큼 A에 대해 지연되는, 그 샘플링하는 단계를 포함한다.

[0006] 본 발명의 또 다른 양태는, 신호 A의 적어도 하나의 지연된 버전 A(m) 을 생성하는 수단으로서, A(m) 은 m 지연 유닛만큼 A에 대해 지연되는, 그 생성하는 수단; 및 시간 인스턴트에서 A(m) 과 신호 B[A(m)] 사이의 차이를 샘플링하는 수단으로서, B[A(m)] 은 적어도 하나의 지연 유닛만큼 A에 대해 지연되는, 그 샘플링하는 수단을 포함하는 시간-디지털 변환기 (TDC) 를 제공한다.

[0007] 본 발명의 또 다른 양태는, 시간 간격을 디지털 표현으로 변환하기 위한 컴퓨터 프로그램 제품을 제공하며, 그 제품은, 컴퓨터로 하여금 신호 A의 적어도 하나의 지연된 버전 A(m) 을 생성하게 하는 코드로서, A(m) 은 m 지연 유닛만큼 A에 대해 지연되는, 그 생성하게 하는 코드; 및 컴퓨터로 하여금 시간 인스턴트에서 A(m) 과 신호 B[A(m)] 사이의 차이를 샘플링하게 하는 코드로서, B[A(m)] 은 적어도 하나의 지연 유닛만큼 A에 대해 지연되는, 그 샘플링하게 하는 코드를 포함하는 컴퓨터-관독가능 매체를 포함한다.

### 도면의 간단한 설명

[0008] 도 1은 종래 기술의 TDC의 일부의 일 구현을 도시한다.

도 2는 도 1에 도시된 신호들의 타이밍의 일 예를 도시한다.

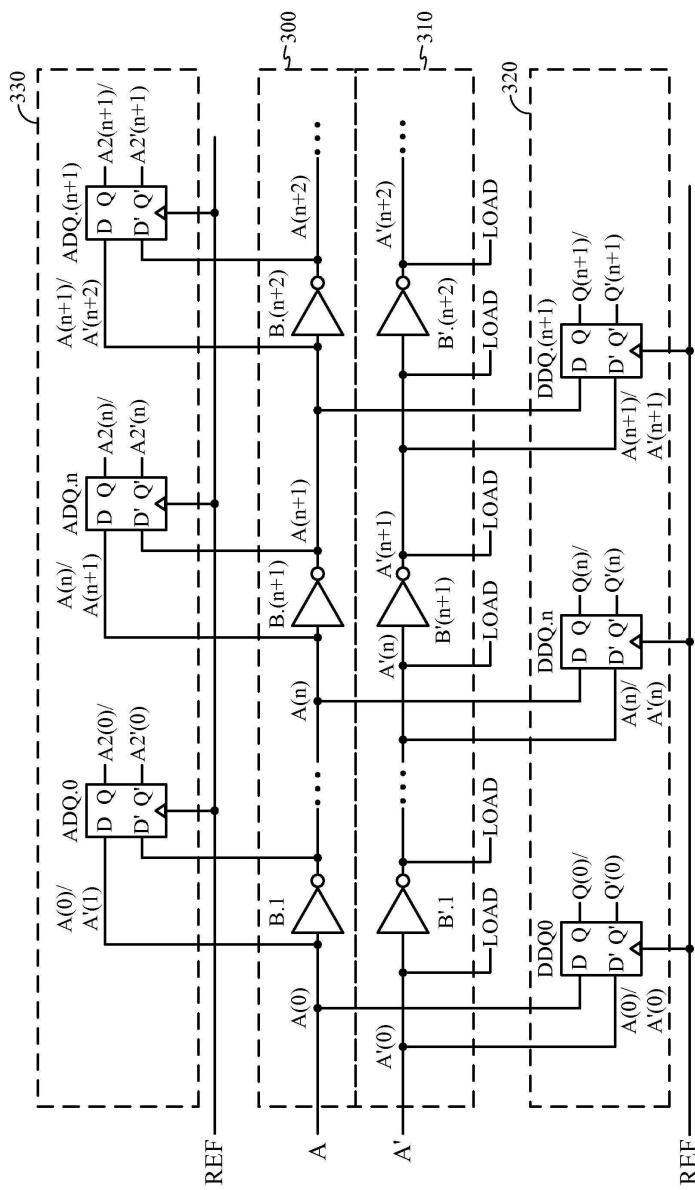

도 3은, 서브-인버터 지연 리졸루션을 달성하기 위한 본 발명에 따른 일 실시형태를 도시한다.

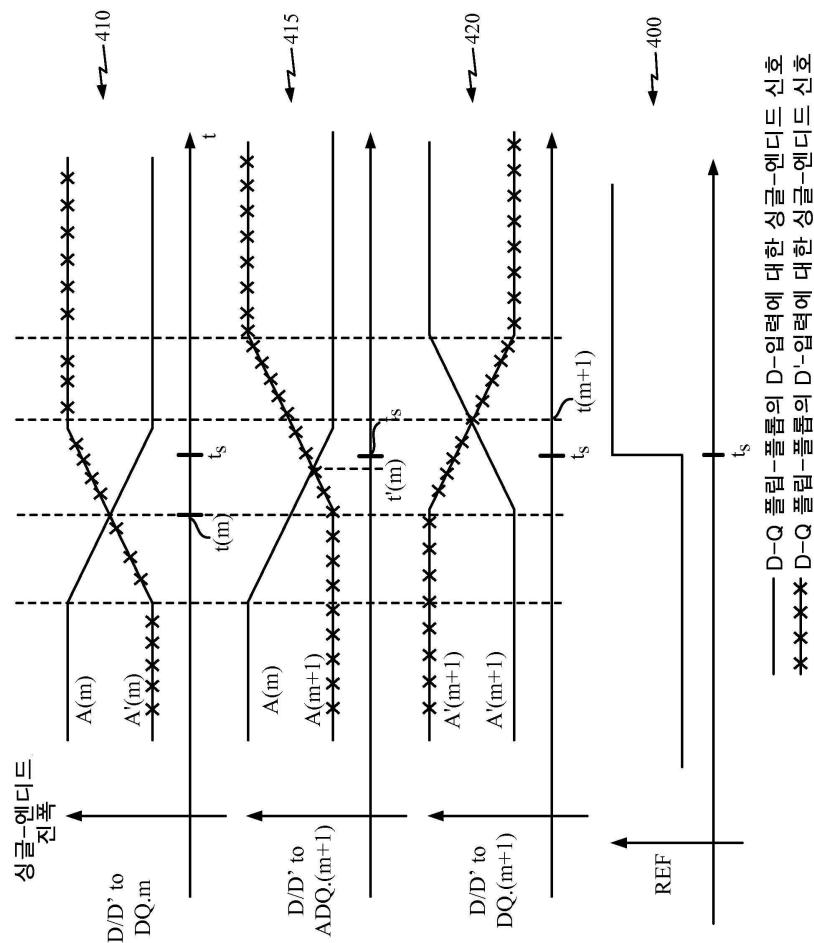

도 4는, 플립-플롭들 DQ.m 및 DQ.(m+1) 에 커플링된 차동 입력 신호들의 타이밍과 비교하여, 보간 플립-플롭 ADQ.m 에 커플링된 차동 입력 신호의 타이밍의 일 예를 도시한다.

도 5는 본 발명의 방법에 따른 단계들을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

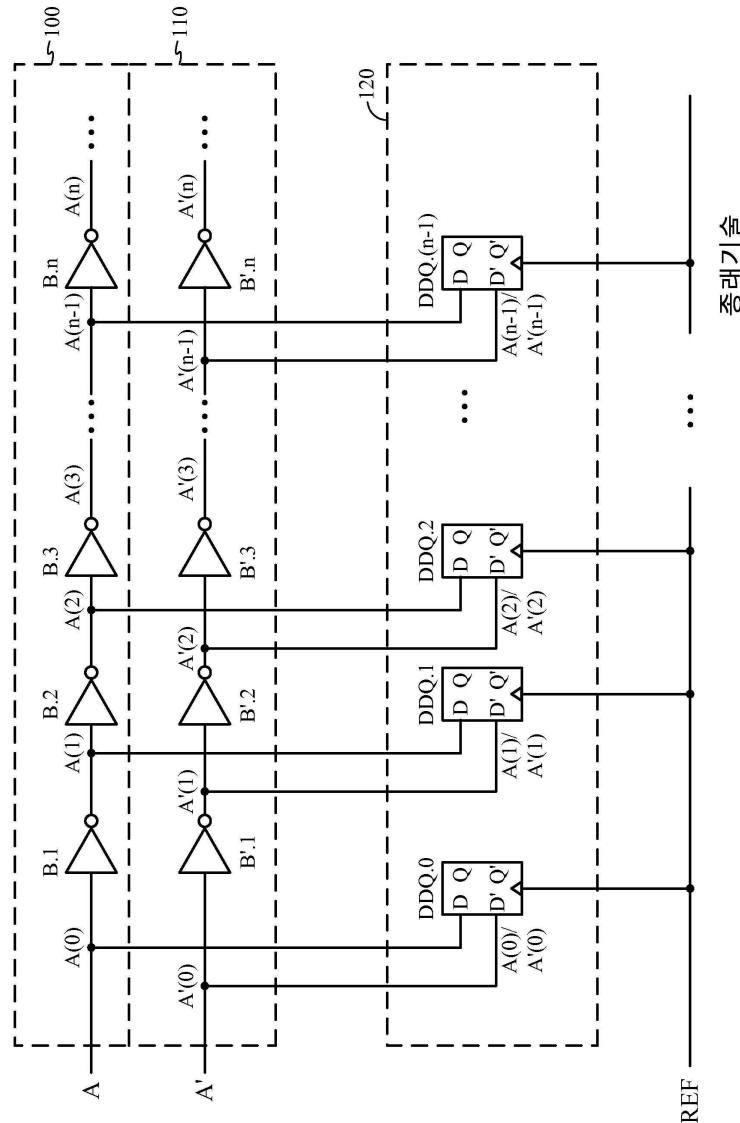

[0009] 도 1은 종래 기술의 TDC의 일부의 일 구현을 도시한다.      도 1에서, 지연  $T_D$  를 각각 갖는 인버팅 버퍼들 B.n 은 지연 라인 (100) 을 형성한다.      지연 라인 (100) 은, 본래의 싱글-엔디드 신호 A의 점차로 지연된 버전들 A(n) 을 생성하며, 여기서, n은 제로로부터 (지연없음) 지연 라인 (100) 의 최대 지연까지의 범위인 인덱스이다.

[0010] 또한, 도 1에 도시된 것은 A에 상보적인 신호 A' 이다.      신호 A 및 A' 는 서로의 논리 반전이며, TDC 데이터 경로에서의 차동 신호 프로세싱을 허용한다.      싱글-엔디드 프로세싱에 대한 차동 프로세싱의 이점들은 당업계에 주지되어 있으며, 예를 들어, 플립-플롭의 입력 및 출력에서의 공통-모드 잡음의 더 양호한 거부를 포함한다.      A' 는, 인버팅 버퍼들 B'.n 을 사용하여 A' 의 점차로 지연된 버전들 A'(n) 을 생성하는 그 자신의 지연 라인 (110) 을 제공받는다.

[0011] 또한, 도 1은 복수의 차동 D-Q 플립-플롭들 (120) 을 도시한다.      각각의 D-Q 플립-플롭은, 신호 REF의 상승 예지 상에서, 그의 차동 입력 D/D' 에서 전압 (또는 전류) 차이를 샘플링하도록 설계된다.      본 명세서 및 본 청구항에서, 용어 X/Y는 싱글-엔디드 신호 X 및 Y 로 구성된 차동 신호를 나타낸다.      각각의 플립-플롭은 그의 차동 입력에서의 샘플링된 전압 차이의 논리값을 후속 시간에서의 차동 플립-플롭 출력 Q/Q' 에 제공한다.      예를 들어, 일 실시형태에서, 싱글-엔디드 입력 D가 싱글-엔디드 입력 D'의 전압 레벨보다 더 높은 전압 레벨을 가지면, 차동 출력 Q/Q' 은 후속 시간에서 HIGH 레벨을 생성할 수도 있으며, 그 역도 행해질 수도 있다.      본 명세서에서, HIGH 의 논리 레벨은, 설명의 용이함을 위해 양의 차동 입력 신호 D/D' 와 관련될 것이다.

당업자는, 이러한 설명이 반대의 관례에도 적용된다는 것을 인식할 것이다.

[0012] 또한, 당업자는, 대안적인 TDC 구현들이 D-Q 플립-플롭들 이외에 차동 샘플링 메커니즘들을 이용할 수도 있음을 이해할 것이다. 본 발명의 기술들은, 그러한 구현들에 용이하게 적용될 수도 있다.

[0013] 도 1에서, 각각의 플립-플롭 DQ.n에 대한 입력 D/D'는, 지연 라인들 (100 및 110)로부터 텝핑된 대응하는 차동 입력 A(n)/A'(n)에 커플링된다. 집합적으로, 플립-플롭들 DQ.n이 REF의 상승 에지 상에서 차동 신호 A/A'의 점차로 지연된 버전들 A(n)/A'(n)을 동시에 샘플링한다는 것이 관측된다. 복수의 플립-플롭 출력들 Q/Q'을 디코더 (미도시)에 커플링함으로써, REF의 상승 에지와 신호 A/A'에서의 논리 천이들 사이의 상대적인 타이밍이 결정될 수도 있다. TDC는, 이에 따라 측정된 상대적인 타이밍의 이산화된 표현 (미도시)을 출력할 수도 있다.

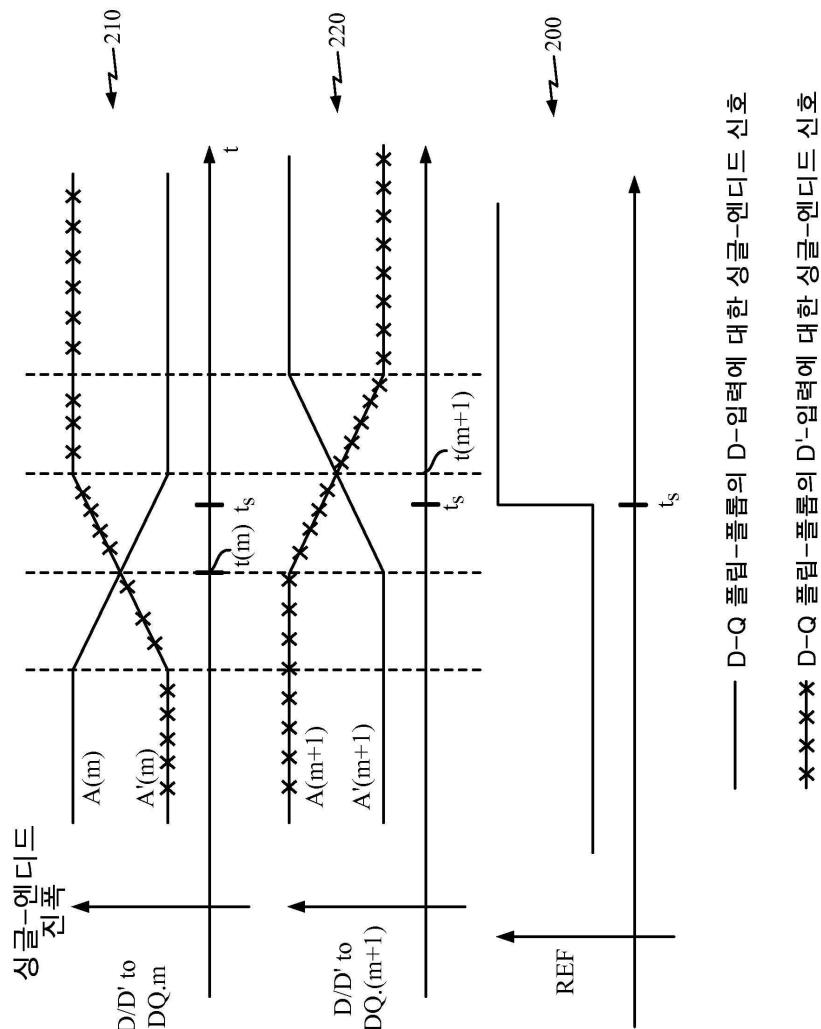

[0014] 도 2는, 도 1에 도시된 신호들의 타이밍의 일 예를 도시한다. 도 2에서, 플롯 (200)은 시간  $t_s$ 에서의 신호 REF의 상승 에지를 도시한다. 플롯 (210)은, 플립-플롭 DQ.m의 입력 D/D'에 커플링된 차동 신호 A(m)/A'(m)를 도시하며, 여기서, m은 도시된 신호들의 특정 인스턴스에 대한 인덱스이다. 플롯 (220)은, 플립-플롭 DQ.(m+1)의 입력 D/D'에 커플링된 차동 신호 A(m+1)/A'(m+1)를 도시한다. DQ.(m+1)은, 도 1의 플립-플롭들 (120)에서 플립-플롭 DQ.m에 바로 후속하는 플립-플롭이다. 버퍼들 B.m 및 B'(m)에 의해 도입된 반전으로 인해, A(m)/A'(m)과 A(m+1)/A'(m+1) 사이의 비교는 그 2개의 차동 신호들 사이의 극성에서의 차이를 고려해야 한다. 대안적인 실시형태들에서, 예를 들어, 지연 라인들 (100 및 110)로부터의 신호들 A(n)/A'(n)이 도 1의 연속하는 플립-플롭들에 대한 입력들 D/D' 사이에서 교번하면, 그러한 신호 반전은 존재하지 않을 수도 있다. 그러한 실시형태들은, 본 발명의 범위내에 있는 것으로 고려된다.

[0015] 도 2에서, 플립-플롭 DQ.m이 시간  $t_s$ 에서, REF의 상승 에지 상에서 논리 LOW를 샘플링하는 동안, 플립-플롭 DQ.(m+1) 또한  $t_s$ 에서 논리 LOW를 샘플링한다. 상술된 신호 반전으로 인해, 플립-플롭들 DQ.m 및 DQ.(m+1)에 의해 샘플링된 2개의 연속하는 LOW들은, REF의 상승 에지 이전에 m  $T_D$ 로부터 (m+1)  $T_D$ 까지의 시간 간격 동안 신호 A에서 논리 천이가 발생한다는 것을 나타낸다. 도 1의 종래 기술의 TDC의 리졸루션이 단일 인버터 지연  $T_D$ 에 제한되기 때문에, TDC는,  $\pm T_D/2$ 보다 양호한 정확도로 논리 천이의 타이밍을 결정할 수 없다.

[0016] 대안적으로, 도 1의 TDC의 리졸루션은, 본래의 신호 A/A'의 연속적으로 지연된 버전들의 제로-크로싱 (zero-crossing) 시간들 사이의 차이를 참조하여 이해될 수도 있다. 제로-크로싱 시간은, 차동 신호가 논리 HIGH로부터 논리 LOW로 천이하는 시간, 또는 그 역의 시간을 나타낸다. 도 2에서, 시간 인스턴트들 t(m) 및 t(m+1)은, 각각, 차동 신호들 A(m)/A'(m) 및 A(m+1)/A'(m+1)에 대한 제로-크로싱 시간들을 반영한다. TDC의 타이밍 리졸루션은, 단일 지연 버퍼의 지연  $T_D$ 에 대응하는 t(m+1)-t(m)으로서 계산될 수도 있다. TDC의 리졸루션을 개선시키기 위해, TDC에서 이용가능한 연속하는 제로-크로싱 시간들 사이의 차이를 감소시키는 것이 바람직할 것이다.

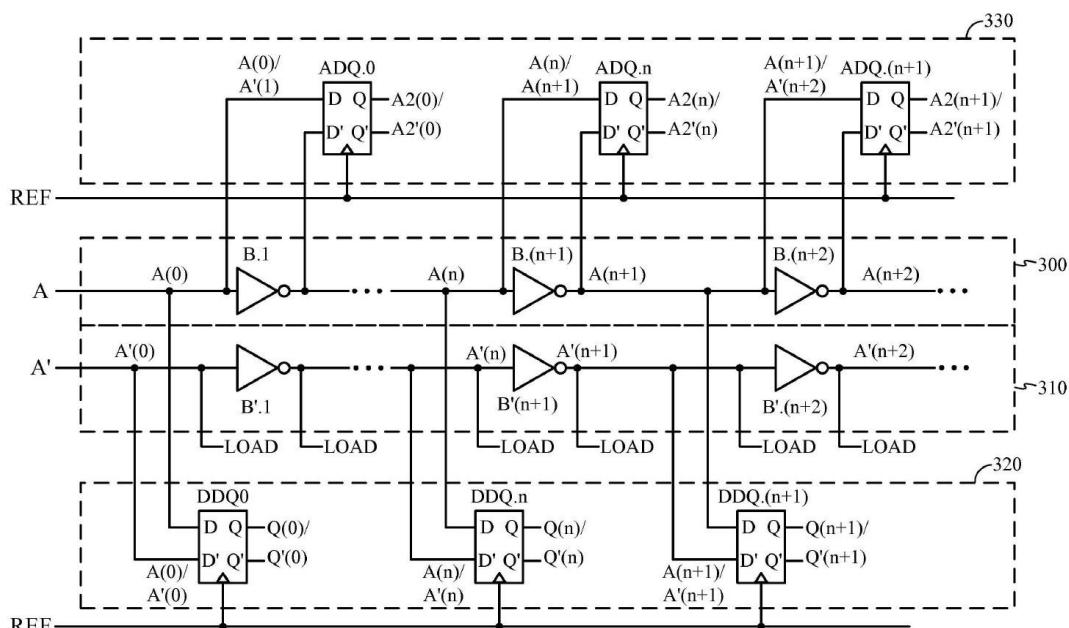

[0017] 본 발명에 따르면, 서브-인버터 지연 리졸루션은, 도 3에 도시된 바와 같은 대안적인 TDC 아키텍처를 이용함으로써 달성될 수도 있다.

[0018] 도 3에서, D-Q 플립-플롭들 DQ.n의 세트 (320) 이외에 "보간" 플립-플롭들 ADQ.n의 세트 (330)가 제공된다. 각각의 보간 플립-플롭 ADQ.n은 차동 출력 Q/Q'를 생성하기 위해 차동 입력 D/D'를 샘플링한다. 각각의 ADQ.n에 대한 입력 D는 지연 라인 (300)에 의해 생성된 신호 A(n)에 커플링되지만, 입력 D'는 지연 라인 (300)에 의해 생성된 신호 A(n+1)에 커플링된다. ADQ.n에 대한 입력들 D 및 D'은 하나의 유닛 지연, 예를 들어, 하나의 인버터 지연만큼 이격되는 서로에 대한 반전된 버전들로 관측된다. 도 3에 도시된 실시형태에서, 더미 부하 "LOAD"의 인스턴스들은, 지연 라인 (310) 상의 부하들을 지연 라인 (300) 상의 부하와 밸런싱하기 위해 지연 라인 (310)에 제공된다.

[0019] 도 4는, DQ.m 및 DQ.(m+1)에 커플링된 차동 입력 신호들의 타이밍과 비교하여 단일 플립-플롭 ADQ.m에 커플링된 차동 입력 신호의 타이밍의 일 예를 도시한다. 도 4에서, 플롯 (400)은 도 2에 도시된 것과 동일한 레퍼런스 신호 REF를 도시한다. 플롯들 (410 및 420)은, 각각, DQ.m 및 DQ.(m+1)의 입력들에 커플링된 차동 신호들 A(m)/A'(m) 및 A(m+1)/A'(m+1)을 도시한다. 플롯 (415)은, ADQ.m의 입력들에 커플링된 차동 입력 신호 A(m)/A(m+1)를 도시한다.

[0020] 플롯들 (410 및 420)에서, 제로-크로싱 시간들은, 각각, 도 2의 플롯들 (210 및 220)과 유사한  $t(m)$  및

$t(m+1)$  인 것으로 도시되어 있다. 그러나, 플롯 (415) 에서,  $A(m)/A(m+1)$  에 대한 제로-크로싱 시간은,  $t(m)$  과  $t(m+1)$  사이에 놓여있는  $t'(m)$  인 것으로 도시되어 있다. 도시된 방식은,  $m T_D$  보다 크지만  $(m+1) T_D$  보다는 작은 지연을 갖는 신호  $A/A'$  의 "보간된" 버전을  $ADQ.m$  에 효율적으로 제공한다. 모든 신호들에 대해 동일한 상승 및 하강 시간들을 가정하면, 그러한 지연은  $m T_D$  와  $(m+1) T_D$  사이의 대략적인 중간일 것이다.

도 3에 도시된 바와 같이 복수의 플립-플롭들  $ADQ.n$  (300) 을 제공함으로써, 신호  $A$ 는 유닛 지연, 예를 들어, 단일 인버터의 지연  $T_D$  보다 작은 타이밍 리졸루션으로 그에 따라 샘플링될 수도 있다.

[0021] 실시형태에 의존하여, 본래의 신호에 대한 보간된 신호의 실제 지연이  $m T_D$  와  $(m+1) T_D$  사이의 중간보다 크거나 작을 수도 있음을 유의한다. 당업자는, 보간된 신호의 실제 지연에 영향을 주는 팩터들이, 예를 들어, 디바이스 미스매치 및/또는 프로세스 변형들로 인한 버퍼들의 상승 및 하강 시간들에서의 불균형을 포함할 수도 있음을 인식할 것이다. 일 실시형태에서, 상승 및 하강 시간들에서의 불균형으로 인한 TDC 샘플링의 레벨에서의 변형들은, 예를 들어, 상승 및 하강 시간들을 모니터링하고 최종 측정치로부터 기대된 부정확도를 소거시킴으로써 TDC 측정치로 팩터화될 수도 있다.

[0022] 당업자는, 다양한 변형들이 도 3에 도시된 실시형태들에 행해질 수도 있지만, 본 발명의 기술들을 여전히 이용한다는 것을 인식할 것이다. 일 실시형태에서, 버퍼들  $B.n$  의 인버팅 특징을 보상하기 위해, 플립-플롭들  $DQ.n$ 에 대한 차동 입력들이 구성에서 연속적으로 펼쳐질 수도 있다.

[0023] 또한, 당업자는, 대안적인 실시형태들에서, 비-인버팅 버퍼들이 도 1 및 도 3에 도시된 인버팅 버퍼들  $B.n$  대신에 이용될 수도 있음을 인식할 것이다. 이러한 경우, 보간 D-Q 플립-플롭  $ADQ.n$ 에 대한 입력  $D/D'$  가 신호들  $A(n)/A'(n+1)$ 에 커플링될 수도 있으며, 여기서,  $A(n)$ 은 본래의 신호  $A$ 에 대응하는 제 1 지연 라인으로부터 탭핑되고,  $A'(n+1)$ 은 상보적인 신호  $A'$ 에 대응하는 제 2 지연 라인으로부터 탭핑된다. 이를 및 다른 실시형태들은, 본 발명의 범위내에 있는 것으로 고려된다.

[0024] 설명된 제로-크로싱 시간들이 TDC 양자화 경계 근방의 샘플링 메커니즘의 작동을 예시하기 위해서만 선택됨을 유의한다. 당업자는, 제로-크로싱 시간들이 단지 예시의 목적을 위해 언급되며, 임의의 시간 주기에 걸쳐 또 다른 레벨로 천이하지 않으면서 통상적인 차동 입력 신호  $A$ 가 일반적으로 일정하게 유지될 수도 있음을 인식할 것이다.

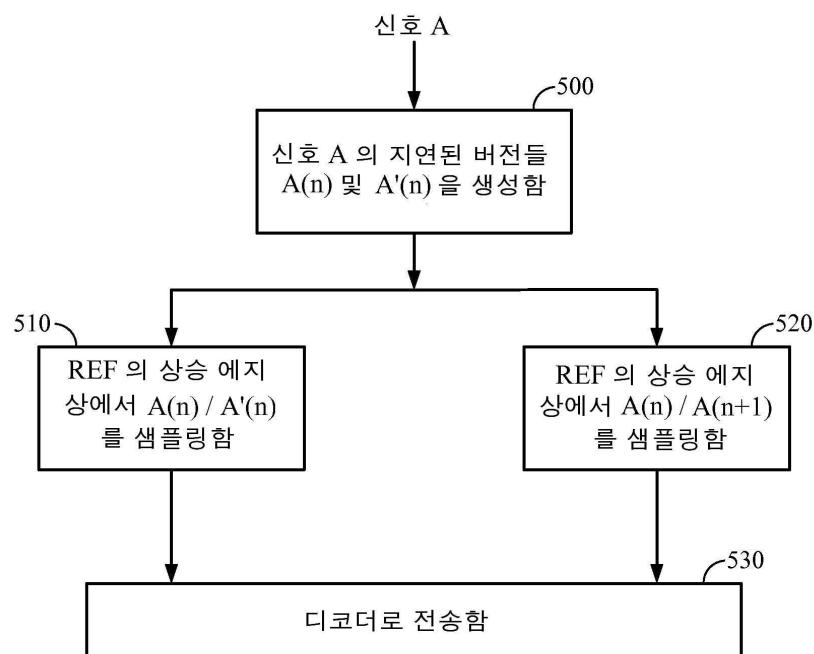

[0025] 도 5는, 본 발명의 방법에 따른 단계들을 도시한다. 도 5에서, 신호  $A$ 의 지연된 버전들  $A(n)$  및  $A'(n)$ 이 단계 (500)에서 생성된다. 단계 (510)에서,  $A(n)/A'(n)$ 가 REF의 상승 에지 상에서 샘플링된다. 단계 (520)에서,  $A(n)/A'(n+1)$ 이 또한 REF의 상승 에지 상에서 샘플링된다. 단계 (530)에서, 그 샘플들은 추가적인 프로세싱을 위해 디코더에 제공된다. 당업자는, 도 5에 도시된 단계들이 단지 예시의 목적을 위한 것이며, 도시된 임의의 특정한 단계들로 본 발명의 범위를 제한하려는 것이 아님을 인식할 것이다.

[0026] 하나 이상의 예시적인 실시형태들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합으로 구현될 수도 있다. 소프트웨어로 구현되면, 그 기능들은 컴퓨터-판독가능 매체 상의 하나 이상의 명령들 또는 코드로서 저장되거나 송신될 수도 있다. 컴퓨터-판독가능 매체는, 일 장소로부터 또 다른 장소로의 컴퓨터 프로그램의 전달을 용이하게 하는 임의의 매체를 포함하는 컴퓨터 저장 매체 및 통신 매체 양자를 포함한다. 저장 매체는, 컴퓨터에 의해 액세스될 수 있는 임의의 이용가능한 매체일 수도 있다. 제한이 아닌 예로서, 그러한 컴퓨터-판독가능 매체는, RAM, ROM, EEPROM, CD-ROM 또는 다른 공학 디스크 저장부, 자성 디스크 저장부 또는 다른 자성 저장 디바이스, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드를 운반 또는 저장하는데 사용될 수 있고 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다.

또한, 임의의 접속은 컴퓨터-판독가능 매체를 적절히 지칭한다. 예를 들어, 소프트웨어가 동축 케이블, 광섬유 케이블, 꼬인 쌍, 디지털가입자 라인 (DSL), 또는 적외선, 무선, 및 마이크로파와 같은 무선 기술들을 사용하여 웹사이트, 서버, 또는 다른 원격 소스로부터 송신되면, 동축 케이블, 광섬유 케이블, 꼬인 쌍, DSL, 또는 적외선, 무선, 및 마이크로파와 같은 무선 기술들은 매체의 정의 내에 포함된다. 여기에서 사용된 바와 같이, 디스크 및 disc는, 컴팩 disc (CD), 레이저 disc, 광 disc, DVD (digital versatile disc), 플로피 디스크 및 블루-레이 disc를 포함하며, 여기서, 디스크들은 일반적으로 데이터를 자성적으로 재생하지만, disc는 레이저를 이용하여 광학적으로 데이터를 재생한다. 또한, 상기의 조합들은 컴퓨터-판독가능 매체의 범위 내에 포함되어야 한다.

[0027] 컴퓨터 프로그램 제품의 컴퓨터-판독가능 매체와 관련된 명령들 또는 코드는 컴퓨터, 예를 들어, 하나 이상의 디지털 신호 프로세서 (DSP), 범용 마이크로프로세서, ASIC, FPGA, 또는 다른 동등한 집적 또는 이산 논리 회로

와 같은 하나 이상의 프로세서들에 의해 실행될 수도 있다.

[0028]

본 명세서 및 청구항에서, 엘리먼트가 또 다른 엘리먼트에 "접속된" 또는 "커플링된"다는 것으로 지칭될 경우, 그것은 다른 엘리먼트에 직접 접속되거나 커플링될 수 있거나, 개개 엘리먼트가 존재할 수도 있다는 것임을 이해할 것이다. 이와 대조적으로, 엘리먼트가 또 다른 엘리먼트에 "직접적으로 접속된" 또는 "직접적으로 커플링된"다는 것으로 지칭될 경우, 개개 엘리먼트들은 존재하지 않는다.

[0029]

다수의 양태들 및 예들이 설명되었다. 그러나, 이들 예들에 대한 다양한 변형들이 가능하며, 여기에서 제공된 원리들이 다른 양태들에 또한 적용될 수도 있다. 이들 및 다른 양태들은 다음의 청구항의 범위내에 존재한다.

## 도면

### 도면1

## 도면2

### 도면3

FIG. 3

## 도면4

— D-Q 플립-플롭의 D-입력에 대한 싱글-엔디드 신호

\*— D-Q 플립-플롭의 D-입력에 대한 싱글-엔디드 신호

## 도면5