(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

10 October 2002 (10.10.2002)

PCT

(10) International Publication Number

WO 02/080271 A2

(51) International Patent Classification<sup>7</sup>: H01L 23/485, 21/60, 21/603

(21) International Application Number: PCT/US02/05087

(22) International Filing Date: 21 February 2002 (21.02.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 09/821,331 28 March 2001 (28.03.2001) US

(71) Applicant: INTEL CORPORATION [US/US]; (a Delaware Corporation), 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

(72) Inventors: KUBOTA, Jiro; 2-25-4, Umezono Puti- Highland Heights 202, Tsukuba, Ibaraki 305-0045 (JP). TAKA-HASHI, Kenji; 4848 Pine Hill Court, San Jose, CA 95129 (US).

(74) Agents: MALLIE, Michael, J. et al.; Blakely, Sokoloff, Taylor & Zafman, 12400 Wilshire Boulevard, 7th Floor, Los Angeles, CA 90025 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

WO 02/080271 A2

(54) Title: FLUXLESS FLIP CHIP INTERCONNECTION

(57) Abstract: A flip chip method of joining a chip and a substrate is described. A thermocompression bonder is utilized to align the chip and substrate and apply a contact force to hold solder bumps on the substrate against metal bumps on the chip. The chip is rapidly heated from its non-native side by a pulse heater in the head of the bonder until the re-flow temperature of the solder bumps is reached. Proximate with reaching the re-flow temperature at the solder bumps, the contact force is released. The solder is held above its re-flow temperature for several seconds to facilitate wetting of the substrate's metal protrusions and joining. Metal caps comprised of a noble metal such as palladium is applied to the surface of the metal bumps to prevent the metal bumps (which generally comprise a highly-conductive and highly-reactive metal such as copper) from oxidizing in the elevated temperatures just prior to and during the re-flow operation.

**FLUXLESS FLIP CHIP INTERCONNECTION****COPYRIGHT NOTICE**

[0001] Contained herein is material that is subject to copyright protection. The 5 copyright owner has no objection to the facsimile reproduction of the patent disclosure by any person as it appears in the Patent and Trademark Office patent files or records, but otherwise reserves all rights to the copyright whatsoever.

**BACKGROUND OF THE INVENTION**10 Field of the Invention

[0002] The invention relates generally to the field of semi-conductor chip packaging. More particularly, the invention relates to the joining of the semi-conductor chip and a substrate using a flip chip process.

15 Description of the Related Art

[0003] Traditionally, semi-conductor chips have been electrically coupled to electrical traces on a substrate via wire interconnects that are soldered on one end to the top area of a chip and soldered to trace pads on the substrate that surround the chip on the other end. These types of interconnects are not particularly space-efficient, requiring area 20 for both the footprint of the chip and a trace pad perimeter. To more efficiently utilize the substrate surface and facilitate smaller chip packages, the flip chip interconnection process was developed. Essentially, the active surface of the semi-conductor chip is flipped over to face the substrate and the chip is soldered directly to trace pads located adjacent to the active surface. The result is a more compact and space-efficient package.

**[0004]** One of the most successful and effective methods of electrically connecting a flipped chip to a substrate utilizes controlled-collapse chip connection technology (C4).

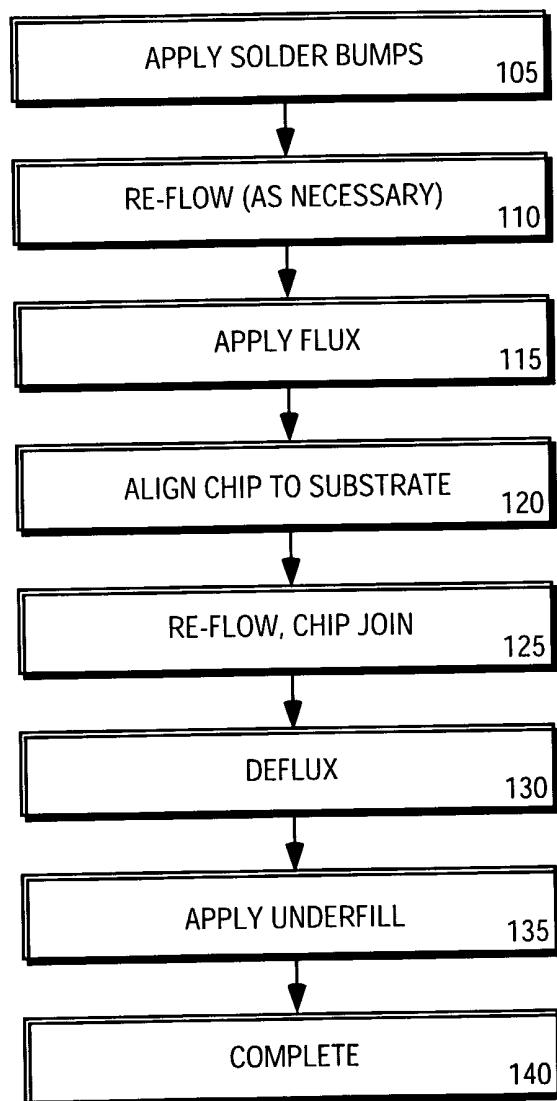

Figure 1 illustrates the C4 process. First, as shown in box 105, solder bumps are typically applied to pads on the substrate using any number of suitable processes including plating and vapor deposition. Generally, lead-tin solders having melting points below 200 degrees Celsius are used. Next, in box 110, the solder bumps are re-flowed by heating the solder bumps to a temperature above the solder's melting point, to fully wet the solder bumps to their respective pads. Typically, metal bumps or protrusions having a high lead content are deposited on the corresponding chip pads.

10 **[0005]** In box 115, a flux is applied to at least one of the surfaces to be joined. Typically, the flux comprises a vehicle and an activator. The flux vehicle acts to isolate the surface of the solder from the atmosphere during a second re-flow, minimizing the risks of oxidation while the solder is hot and/or molten. The flux vehicle is generally tacky and provides an adhesive force to hold the chip and substrate together prior to the 15 second re-flow. The activator is typically an organic or inorganic acid that removes any oxides or surface films present on the solder facilitating solder wetting of the metallic surfaces to be joined. In box 120, the flux bearing surfaces of the chip and substrate are placed in contact with each other in general alignment.

**[0006]** Next, as illustrated in box 125, the second re-flow is performed by heating 20 the chip and substrate package to a temperature above the solder's melting point. The molten solder bumps wet the corresponding metal bumps and the surface tension of the molten solder causes the metal bumps to self-align with each of the corresponding substrate pads. The newly formed interconnects are then cooled to solidify the solder.

**[0007]** Any flux or flux residue is removed from the chip and substrate package in 25 a defluxing operation as indicated in box 130. This operation will typically include

solvent washing the package to remove flux residue. A post-interconnection bake cycle may also be specified to volatilize any remaining solvent or low boiling point flux constituents.

[0008] An epoxy under-fill is applied between the active surface of the chip and 5 the top surface of the substrate to surround and support the solder interconnects. Under-filling significantly increases the reliability and fatigue resistance of the package's interconnections. The under-fill helps to more evenly distribute stress caused by thermally induced strains due to the differences in coefficients of thermal expansion (CTE) between the chip and substrate across the entire surface of the chip and substrate. If the gap 10 between the interconnected chip and substrate were not under-filled, the stress would be carried by the relatively thin solder interconnects, often resulting in premature package failure. However, in order for the under-fill to perform properly, it must be well-adhered to the chip and substrate surfaces. Even a thin film of flux residue can cause premature delamination of a bonded surface, eventually resulting in failure in one or more of the 15 interconnects. Accordingly, one of the great challenges using C4 technology has been to completely remove all flux residues from the package. This has become especially troublesome as the thickness of the gap between the chip and the substrate has decreased.

[0009] The total throughput time (TPT), or the time it takes to create a soldered chip, is affected significantly by the time required to remove residues from the protective 20 flux, which can be particularly time-consuming. For instance, chemical defluxing may take minutes while a post-bake to remove any remaining flux or solvent residue may take several hours. Fluxes have been developed that completely volatilize at elevated temperature. However, because the flux is required in the C4 process to hold the chip and substrate together before re-flow, only those fluxes that have volatilization temperature at 25 or above the solder melting point are suitable for use with the C4 process. The small

thickness of the gap distance between the chip and the substrate coupled with the flux's high volatilization temperatures, however, make it difficult, if not impossible, to boil off all of the flux residues during the re-flow process or in a subsequent post-bake operation at a temperature slightly below solder melting temperature. The long post-bake times and 5 defluxing operations required to volatize the flux eliminate any opportunity for significant TPT reductions.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0010] The present invention is illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings and in which like reference numerals refer to similar elements and in which:

[0011] **Figure 1** is a prior art block diagram illustrating the operations typically required to create a flip chip bond using a C4 joining process.

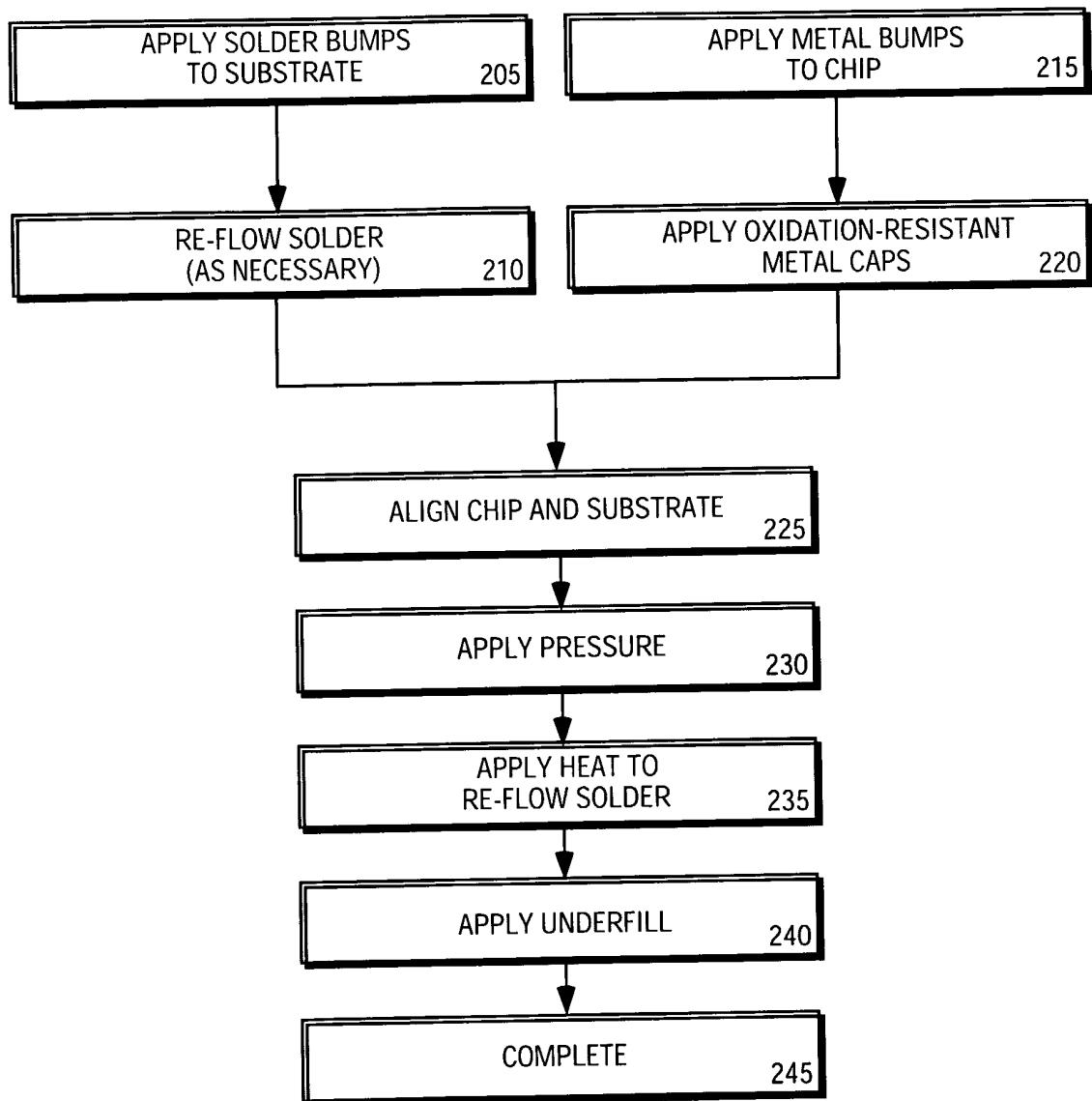

[0012] **Figure 2** is a block diagram illustrating the joining process utilized 15 according to one embodiment of the present invention.

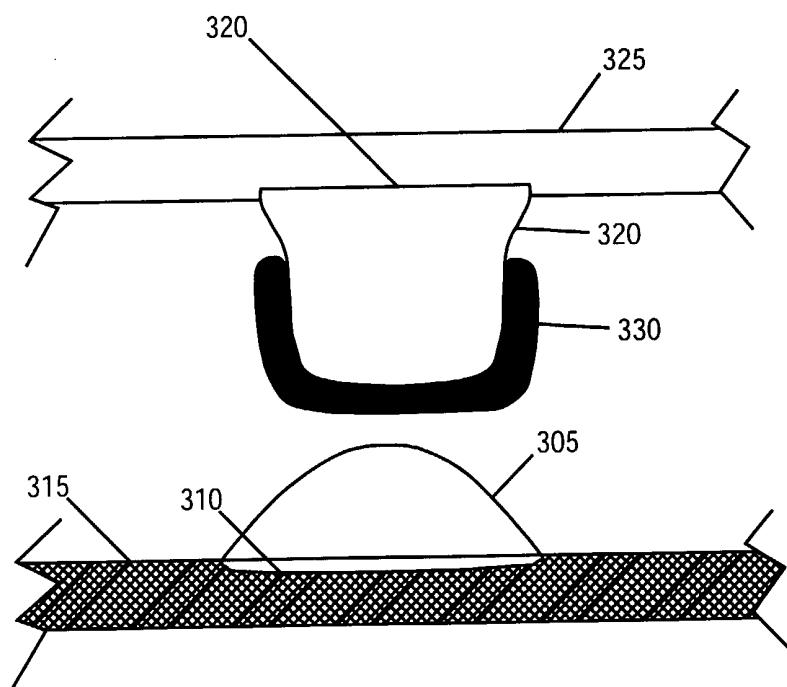

[0013] **Figure 3** illustrates a solder bump that has been applied to a bonding pad on a substrate and re-flowed, as well as a copper base metal bump coated with a noble metal cap that has been applied to a bonding pad on the top surface of a chip.

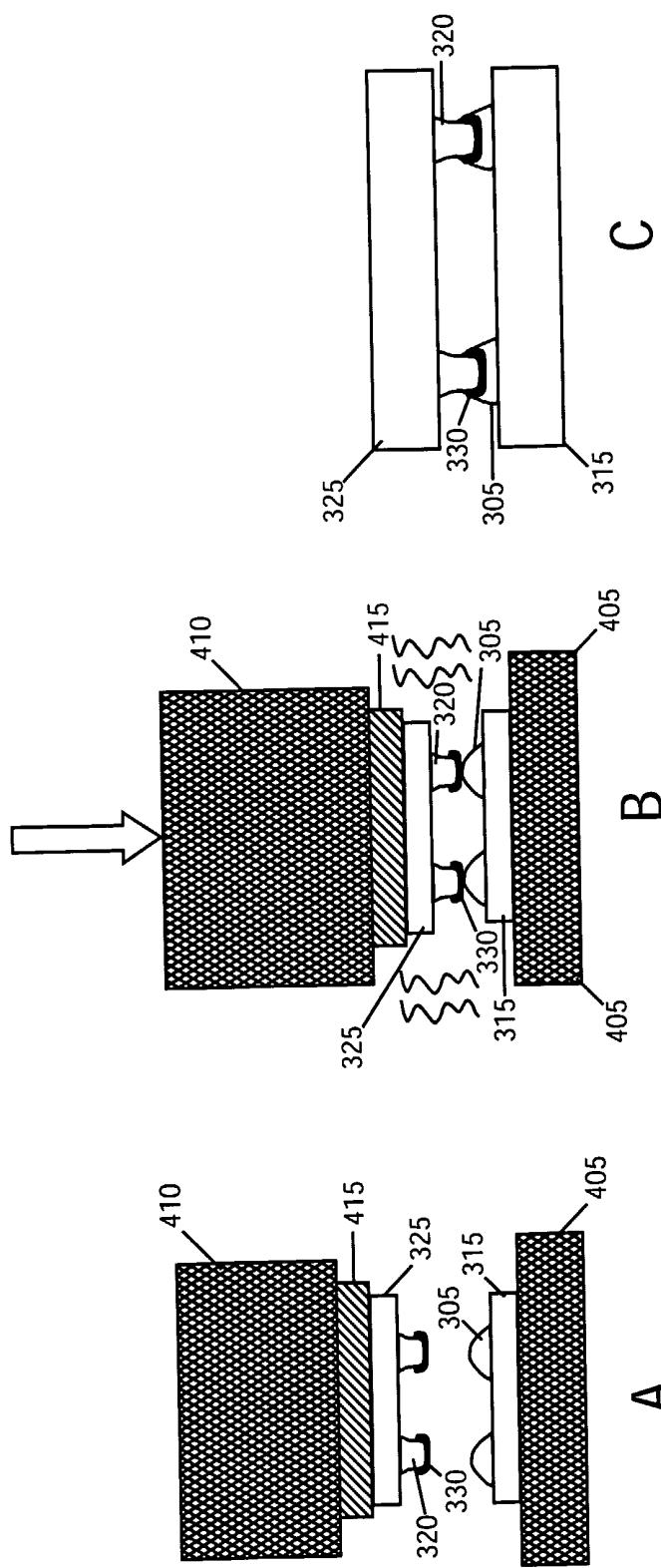

[0014] **Figure 4a-c** illustrates a chip and substrate during various operations 20 during the interconnection process.

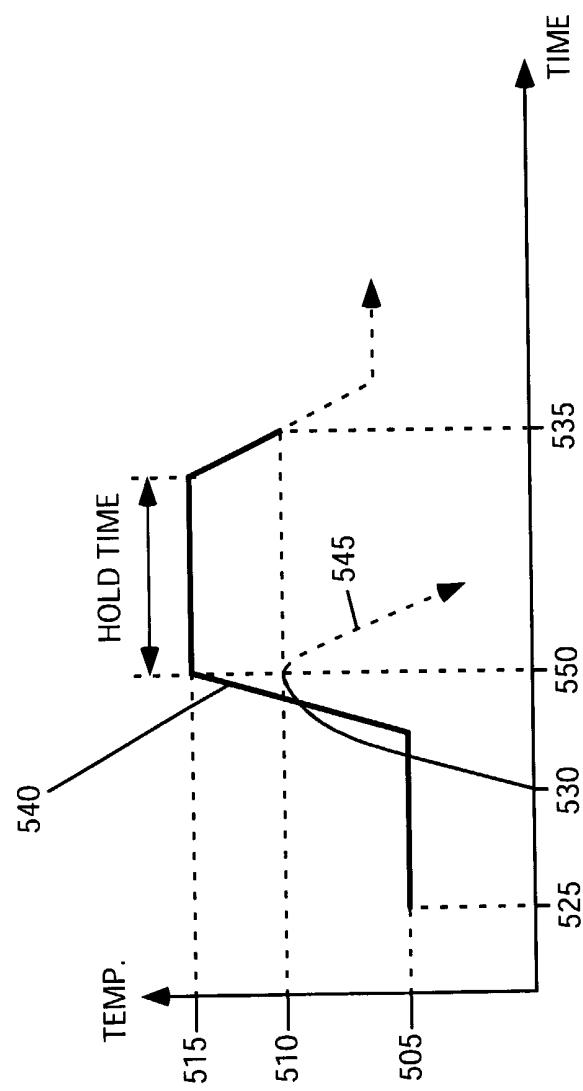

[0015] **Figure 5** provides a diagram of a joining cycle that may be utilized in embodiments of the present invention.

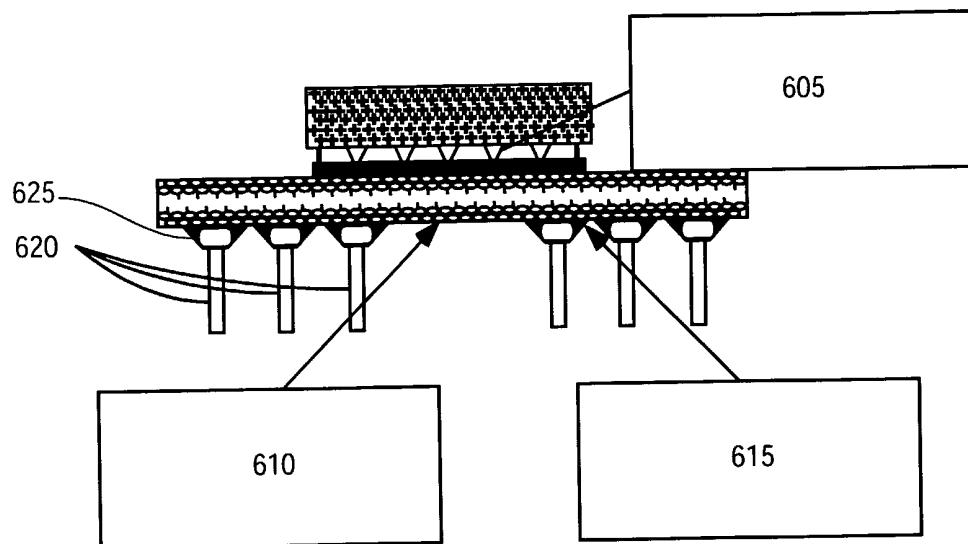

[0016] **Figure 6A** is an illustration of a chip/substrate package wherein the substrate comprises a pin grid array.

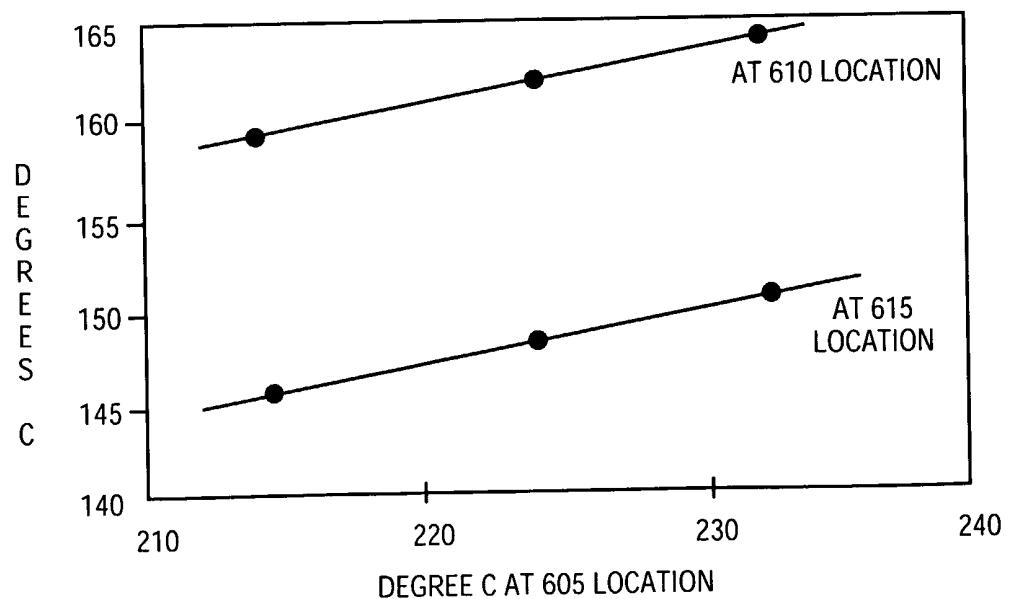

[0017] **Figure 6B** is a chart derived from experimentation indicating the temperatures observed at several locations on the chip and substrate during a chip interconnection process performed according to an embodiment of the present invention.

5

## DETAILED DESCRIPTION OF THE INVENTION

[0018] A flip chip method for interconnecting a chip to a substrate without using flux is described. Through the use of a thermo-compression bonder (or a similarly equipped apparatus) that uses contact pressure to hold the chip and the associated substrate 10 in general alignment prior to re-flow of the solder bumps, the need to use a flux that can adhesively hold the chip and substrate together until solder bump re-flow is eliminated. Accordingly, through the use of a metal cap of an oxidation-resistant noble metal to 15 protect the metal bump (or protrusion) during the elevated temperature joining process, the use of a flux can be eliminated entirely. Advantageously, by eliminating the time-consuming deflux and bake cycles, the TPT is significantly reduced. The use of a thermo-compression bonder to perform the joining operation further deceases the TPT as opposed to prior art C4 joins that used an oven to provide the necessary heat for solder re-flow. Additionally, the integrity of the under-fill bonds with the surfaces of the chip and 20 substrate is potentially increased, resulting in chip packages with higher fatigue resistance and longer expected life-spans.

[0019] Figure 2 is a block diagram illustrating the joining process utilized according to one embodiment of the present invention. First, as indicated in block 205, a solder is typically applied to bond pads on the top surface of the substrate, although in alternative embodiments the solder may be applied to bond pads on the chip (die) instead. 25 The solder may be applied to the bond pads using any number of suitable techniques

known to those skilled in the art, including, but not limited to, vapor deposition and electroplating. After the solder is applied, the substrate is heated to beyond the solder's melting point to re-flow the solder as indicated in block 210 to facilitate complete wetting of the bond pads. In the preferred embodiment, a 96.5% tin/ 3.5% silver eutectic solder 5 with a melting point of around 221 degrees Celsius is specified, although any number of suitable solder compounds may be utilized. Ideally, lead-free solders are specified, eliminating the potential environmental problems caused by lead.

[0020] Typically, as indicated in block 215, metal bumps are applied to the bond pads on the chip, although in alternative embodiments the metal bumps may be applied to 10 the substrate instead. The metal bumps may be applied to the bonding pad by any number of methods as would be known to one skilled in the art including, but not limited to, vapor deposition, plating, and wire bumping. Ideally, a bump metal is chosen that has good electrical properties. Traditionally, an oxidation-resistant, lead-based bump metal such as a 97%Pb3%Sn alloy has been utilized in conventional C4 flip chip joining processes.

15 Lead-based bump metals, and solders for that matter, provide necessary oxidation resistance, especially when a flux is used, during the furnace temperature ramp up and hold times utilized in a conventional C4 process. The lead-based bump metals, however, have relatively poor electrical properties, providing significant room for improvement. In 20 embodiments of the present invention, the ramp up and hold times are relatively short (100 degrees @ second ramp and 1-5 second hold); thereby, the potential for significant oxidation is minimized and a more reactive base metal with superior electrical properties may be utilized in the metal bumps. In the preferred embodiment, copper base metal bumps are specified.

[0021] To help ensure the surface of the metal bumps remain oxidation free prior 25 to solder re-flow and joining, the joining surfaces of the metal bumps are fitted with a

metal cap as indicated in block 220. The metal cap is typically comprised of a metal or metal alloy having good oxidation resistance at elevated temperatures of 100 to 300 degrees Celsius. Suitable metals include the noble metals, such as platinum, iridium, gold and palladium. Preferably, a metal is specified that has reasonable electrical properties as well. The metal caps may be applied to the metal bumps using a number of methods that would be known to one of skill in the art, including plating and vapor deposition. Figure 3 illustrates a solder bump 305 that has been applied to a bonding pad 310 on a substrate 315 and has been re-flowed. A copper base metal bump 320 that has been applied to a bonding pad 335 on the top surface of a chip 325 is also illustrated. The metal bump 320 has a portion of its surface covered with a palladium metal cap 330 to prevent oxidation of the copper during the chip interconnection process.

[0022] Referring to block 225 of Figure 2, the chip 320 is picked up by the head of the thermo-compression bonder and aligned with the substrate 315. A solder bumped substrate 315 aligned with a metal bumped chip is illustrated in Figure 4A. A thermo-compression bonder is an apparatus often used in chip packaging operations that has the capability to provide heat and pressure through a platen 405 and a moving head 410. Since pressure applied by the thermo-compression bonder is used to hold the chip and substrate together prior to re-flow in the preferred embodiments of the invention, no flux is necessary to hold the chip and substrate together prior to re-flow in contrast to the prior art C4 process. In the preferred embodiment, the lower platen 405 of the thermo-compression bonder is outfitted with a platen heater, so that the platen 405 may be maintained at an intermediate temperature between room temperature and the melting temperature of the solder bumps. In the preferred embodiment, the lower platen 405 is maintained at a temperature of about 135 degrees Celsius. Likewise, the head 410 may be maintained at a temperature, typically between 30 to 100 degrees Celsius. The head 410

may comprise an internal heating element or as shown in Figure 4A, a pulse heat tool 415 capable of very rapid heating (e.g., greater than 25 degrees Celsius @ second) may be utilized.

[0023] Next, in block 230, the interconnection cycle is commenced. First, as shown in Figure 4B, the cap metal covered base metal bumps 320 of the chip 325 are brought into contact with corresponding solder bumps 305 on the substrate 315, and pressure is applied. In block 235, the pulse heat tool 415 is rapidly heated to a temperature well in excess of the melting point of the solder bumps 305. Figure 5 illustrates a joining cycle that may be utilized in a preferred embodiment of the present invention. Line 540 represents the temperature of the pulse heat tool 340 at a given time during the cycle. Line 545 is a pressure curve indicating the amount of force applied to the interface between the metal bumps 325 and the solder bumps 305 at a given time. Initially, as discussed *supra*, the pulse heat tool is maintained at an intermediate temperature such as 30 degrees Celsius. The chip is picked up by the thermo-compression bonder head at time 525. The chip and substrate are aligned and the chip is brought into contact with the substrate and pressure is applied at around time 530. Typically, a force of 2 to 5 kilograms is applied depending on the dimensions of the chip and the number of flip chip connections to be made. Shortly thereafter, the pulse heat tool is energized and rapidly heated to its hold temperature. In the preferred embodiment, heat-up rates on the order of 100 degrees Celsius are specified. The peak hold temperature 515 is typically on the order of 250 to 400 degrees Celsius depending on several factors, including the thickness of the chip, the thermal conductivity of the chip, and the melting point and desired re-flow temperature of the solder bumps 305. Typically, a temperature gradient will be established through the chip such that the temperature at the interface with the solder bumps 305 will be less than the temperature at the interface with the pulse heat tool 415. Accordingly, the hold

temperature 515 of the pulse heat tool 415 will typically be greater than the re-flow temperature of the solder bumps 305. At or about time 550, the melting temperature of the solder is reached at the interface between the chip and the substrate and pressure is no longer required to hold the chip and substrate together as the solder bumps begin to melt 5 and wet the metal bumps. Accordingly, the force applied to the chip is released causing the applied pressure to be reduced to zero as indicated by pressure curve 545. While the pulse heat tool is held at temperature 515, the solder bumps become completely molten and re-flow. The wetting of the metal bumps on the chip along with the surface tension of the molten solder tends to promote self-alignment of the chip and substrate, wherein the 10 chip moves laterally small amounts as necessary to minimize the average effective surface tension of all of the interconnects. The pulse heat tool is maintained at temperature 515 for a short period of time, typically 1 to 5 seconds, after which the pulse heat tool 340 is de-energized and the solder bumps re-solidify shortly thereafter. Once the pulse heat tool has reached a temperature 510, about 200 degrees Celsius in the preferred embodiment, 15 the bonded chip and substrate are removed from the thermo-compression bonder, freeing the bonder to perform another chip join. Figure 4C illustrates a interconnected chip and substrate, wherein the solder bumps have deformed and wetted the capped surface of the metal bumps.

[0024] Unlike the C4 wherein the re-flow is performed in an oven, the total period 20 of time that the metal bumps and the solder are exposed to elevated temperatures is very short. Accordingly, there is little time for a significant amount of oxidation to occur to the preferred tin and silver solder bumps. Additionally, the oxides that could inhibit wetting of the bump metal by the solder do not form on the oxidation resistant metal cap at the elevated interconnect temperatures.

[0025] In the preferred embodiment, as mentioned *supra*, a 96.5% Sn 3.5% Ag solder is utilized to form the solder bumps. This solder has a melting point of approximately 221 degrees Celsius and requires a re-flow temperature at least a few degrees greater than the melting point. As discussed *supra*, prior art methods such as C4 typically utilized lead based solders (such as 37% lead 63% tin) that have melting points of less than 190 degrees Celsius. The lower melting point solders are especially necessary when joining a chip to a pinned substrate using a C4 process, since temperatures in excess of 210 degrees Celsius can cause softening of the pinning solder (typically, 95% tin 5% antimony which begins melting around 232 degrees Celsius), resulting in movement of the pins. In preferred embodiments of the present invention using a 96.5% Sn 3.5% Ag solder, the temperature of the pinning solder does not exceed 200 degrees Celsius. The temperature gradient between the chip-to-pulse heat tool interface at the high end and the platen-to-substrate interface at the low end never has the opportunity to equalize in the short time the pulse heat tool is energized. Figure 6A is an illustration of a chip/substrate package wherein the substrate comprises a pin grid array (PGA). The pins 620 of the PGA are held in place by pinning solder 620. Figure 6B is a chart derived from experimentation indicating the temperatures observed at several locations on the chip and substrate during a chip join performed according to an embodiment of the present invention. The temperatures listed along the horizontal axis indicate the temperature at the center of the chip join region 605. It is noted that the melt and re-flow of the preferred solder typically occurs at temperatures between 220 and 235 degrees Celsius. The top line indicates the corresponding temperature at the center of the pin grid array side of the substrate. The bottom line indicates the corresponding temperature at the edge of the pin grid array side of the substrate. As is indicated by Figure 6B, the temperature on the pin grid array side

of the substrate never exceeds 165 degrees Celsius, while the melt temperature of the solder bumps are reached and exceeded to facilitate re-flow and joining.

[0026] Referring back to Figure 2, the gap between the chip and the substrate is typically under-filled with an epoxy resin to substantially increase the longevity, 5 environmental resistance, and fatigue strength of the interconnects as indicated by block 240. Using the prior art C4 process, any flux residues present between the chip and substrate surfaces need to be removed in a de-fluxing operation that typically involves a solvent wash. Furthermore, a bake cycle may be performed to “burn-off” any remaining residue. As can be appreciated, these operations consume significant amounts of time and 10 significantly increase the TPT of chip/substrate interconnection. Using a preferred embodiment of the present invention without flux, the de-flux and bake operations can be eliminated, permitting significant reductions in TPT.

#### Alternative Embodiments

[0027] In the foregoing description, for the purposes of explanation, numerous 15 specific details have been set forth in order to provide a thorough understanding of the present invention. The detailed description and embodiments discussed herein are not intended to limit the scope of the invention as claimed. To the contrary, embodiments of the claims have been contemplated that encompass the full breadth of the claim language. 20 Accordingly, the present invention may be practiced without some of the specific detail provided herein.

[0028] For instance, the embodiments of the invention have been described above 25 primarily in terms of a flip chip joining process using a thermo-compression bonder. It is conceivable that other apparatus may be used to accomplish the limitations of the claims as would be obvious to one of ordinary skill in the art. Likewise, although the process has

been described in terms of an exemplary embodiment wherein a 96.5% tin 3.5% silver solder is used, other suitable solders are contemplated. In the preferred embodiment, the pressure applied to the chip against the substrate is removed once the solder bumps have begun to melt, however alternative embodiments are contemplated wherein at least some 5 pressure is maintained against the chip throughout the interconnection process. Furthermore, in other alternative embodiments it is contemplated that a thin coating of no-clean flux having a volatilization temperature below the melting temperature of the solder may be applied to the solder bumps to remove any oxides from the solder bumps during heat up. The no-clean flux would completely boil off prior to completion of the chip join, 10 eliminating the need for any subsequent de-fluxing or bake operations. In the embodiments described heretofore, the metal bumps have been applied to the chip surface and the solder bumps have been applied to the substrate, however it is contemplated the placement of the metal and solder bumps may be reversed.

## CLAIMS

What is claimed is:

- 1 1. A method comprising:

- 2 aligning a substrate with a corresponding chip,

- 3 the substrate having opposing a first and second substrate surfaces, the

- 4 first substrate surface having a plurality of solder bumps attached

- 5 thereto,

- 6 the solder bumps having a melting temperature,

- 7 the chip having opposing first and second chip surfaces, the first chip

- 8 surface having metal protrusions attached thereto,

- 9 the metal protrusions at least partially covered with a metal cap, the metal

- 10 protrusions primarily comprising a first metal and the metal cap

- 11 primarily comprising a second metal;

- 12 bringing the plurality of solder bumps and the plurality of bump metal

- 13 protrusions in contact with each other; and

- 14 heating the plurality of solder bumps to a first temperature greater than the

- 15 melting temperature to melt the plurality of solder bumps.

- 1 2. The method of claim 1, wherein said the bringing the plurality of solder bumps

- 2 and the plurality of bump metal protrusions in contact with each other, further

- 3 comprises applying a contact force.

- 1 3. The method of claim 2, wherein the contact force is released once the plurality of

- 2 solder bumps have begun to melt during said heating the plurality of solder bumps

- 3 to a first temperature.

1 4. The method of claim 1, wherein said heating the plurality of solder bumps to a

2 first temperature comprises creating a temperature gradient through the chip by

3 rapidly heating the second chip surface fixture to a second temperature, the

4 second temperature being much greater than the first temperature.

1 5. The method of claim 4, wherein heat to accomplish said rapidly heating the

2 second chip surface is provided by a heater in contact with the second chip

3 surface.

1 6. The method of claim 4, wherein a third temperature at the second substrate

2 surface is significantly below the first temperature, when the plurality of solder

3 bumps are at the first temperature.

1 7. The method of claim 1, further comprising maintaining the plurality of solder

2 bumps at a temperature at or above the first temperature for a period of time.

1 8. The method of claim 1, wherein the second metal is a metal or metal alloy that is

2 oxidation resistant at elevated temperatures.

1 9. The method of claim 1, wherein the plurality of solder bumps are comprised of a

2 lead-free solder.

1 10. The method of claim 4, wherein said rapidly heating the second chip surface to a

2 second temperature is accomplished using a heat up rate in excess of 50 degrees

3 Celsius a second.

1 11. A method comprising:

2 placing either a substrate or a chip in a first fixture,

3 the substrate or chip having deposited thereon a plurality of solder bumps,

4 the solder bumps having a melting point at a first temperature,

5 the first fixture being maintained at a second temperature below the first

6 temperature;

7 placing the other of the chip or the substrate in a second fixture,

8 the other of the chip or substrate have affixed thereto a plurality of metal

9 protrusions primarily comprised of a first metal, the plurality of

10 metal protrusions each being at least partially coated a metal cap,

11 the metal cap primarily comprising a second metal;

12 bringing the plurality of solder bumps into contact with the plurality of metal

13 protrusions by moving the one or both of the first and second fixtures

14 towards each other;

15 rapidly heating a heater coupled with the first or second fixtures from a third

16 temperature to a fourth temperature,

17 the third temperature being lower than the first temperature, and

18 the fourth temperature being higher than the first temperature;

19 holding the heater approximately at or above the fourth temperature until the

20 plurality of solder bumps have melted and have wetted at least a portion of

21 the metal cap of each metal protrusion.

1 12. The method of claim 11, wherein the heater, and the first and second fixtures

2 comprise a thermo-compression bonder.

1 13. The method of claim 11, wherein the substrate has deposited thereon the plurality

2 of solder bumps, and the chip has affixed thereto a plurality of metal protrusions.

1 14. The method of claim 11, wherein the pulse heat tool is held at the fourth

2 temperature for a period of time approximately between 1 and 5 seconds.

1 15. The method of claim 11, wherein said bringing the plurality of solder bumps into

2 contact with the plurality of metal protrusions further comprises applying a

3 contact force to hold the plurality of solder bumps and metal protrusions in

4 contact with each other.

1 16. A flip chip method of joining a chip and substrate comprising:

2 applying metal protrusions to electrical interconnect pads on an active surface of a

3 chip, the chip also having second surface opposite the active surface, the

4 metal protrusions comprising a first metal and having a surface, wherein a

5 metal cap comprising an oxidation resistant metal or metal alloy is cover

6 at least a portion of the surface;

7 applying lead-free solder bumps to electrical interconnect pads on a top surface of

8 a substrate, the substrate also having a bottom surface opposite the top

9 surface, the solder bumps having a melting temperature, the melting

10 temperature being within the range of 200-240 degrees Celsius;

11 placing the bottom surface of the substrate on a platen of a thermo-compression

12 bonder, the platen being maintained at a first temperature that is less than

13 the melting temperature, the first temperature being within the range of

14 70-190 degrees Celsius;

15 affixing the second surface of the chip to a head of the thermo-compression

16 bonder, the head including a heater, the head being maintained at a second

17 temperature, the second temperature being less than 120 degrees Celsius;

18 generally aligning the solder bumps with corresponding metal protrusions;

19 lowering the head or raising the platen to bring the solder bumps into contact with

20 the metal protrusions;

21 applying a contact force to hold the solder bumps and corresponding metal

22 protrusions together;

23 rapidly increasing the temperature of the heater to a third temperature until the top

24 surface of the substrate reaches a fourth temperature, the third temperature

25 being within the range of 250-400 degrees Celsius, the fourth temperature

26 being greater than the melting temperature; and

27 holding the top surface at the fourth temperature for a period of time.

1 17. The method of claim 16, further comprising releasing the contact force after the

2 solder bumps have begun to melt, but before the period of time has expired.

1 18. The method of claim 16, further comprising:

2 removing an interconnected chip and substrate package from the thermo-

3 compression bonder after the period of time has expired and the solder

4 bumps have solidified.

1 19. The method of claim 16, wherein the solder bumps are comprised of a tin based

2 solder.

1 20. A method comprising:

2 applying a plurality of metal protrusions to a chip surface of a chip, the plurality

3 of metal protrusions primarily comprising a first metal; and

4 coating the plurality of metal protrusions, at least partially, with metal caps, the

5 metal caps primarily comprising a second metal.

1 21. The method of claim 20, wherein the metal protrusions are applied to electrical

2 bonding pads located on the chip surface.

1 22. The method of claim 20, wherein the second metal is resistant to oxidation at

2 elevated temperatures between 175 and 250 degrees Celsius.

1 23. The method of claim 20, wherein the first metal is copper.

1

1/6

100

FIG. 1 (PRIOR ART)

2/6

FIG. 2

3/6

FIG. 3

4/6

FIG. 4

5/6

FIG. 5

6/6

FIG. 6A

FIG. 6B