(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-530352

(P2004-530352A)

(43) 公表日 平成16年9月30日(2004.9.30)

(51) Int.CI.<sup>7</sup>

**H03K 5/13**

**H03F 3/45**

**H03K 19/017**

F 1

**H03K 5/13**

**H03F 3/45**

**H03K 19/017**

テーマコード (参考)

**5 J 001**

**5 J 056**

**5 J 500**

審査請求 未請求 予備審査請求 有 (全 32 頁)

(21) 出願番号 特願2002-580489 (P2002-580489)

(86) (22) 出願日 平成14年4月8日 (2002.4.8)

(85) 翻訳文提出日 平成15年10月6日 (2003.10.6)

(86) 國際出願番号 PCT/US2002/010889

(87) 國際公開番号 WO2002/082649

(87) 國際公開日 平成14年10月17日 (2002.10.17)

(31) 優先権主張番号 09/828,398

(32) 優先日 平成13年4月6日 (2001.4.6)

(33) 優先権主張国 米国(US)

(71) 出願人 503367147

エランテック セミコンダクター インコ

ーポレーテッド

アメリカ合衆国 カルフォルニア州 95

035、ミルピタス、トレードゾーン ブ

ールバード 675

(74) 代理人 100071526

弁理士 平田 忠雄

(72) 発明者 リン、シージャン

アメリカ合衆国 カルフォルニア州 94

539、フレモント、ヴァレロ ドライブ

40951

最終頁に続く

(54) 【発明の名称】電圧制御発振器用一定の出力揺れ及び可変時間遅延を有するCMOS回路

## (57) 【要約】

## 【発明の要旨】

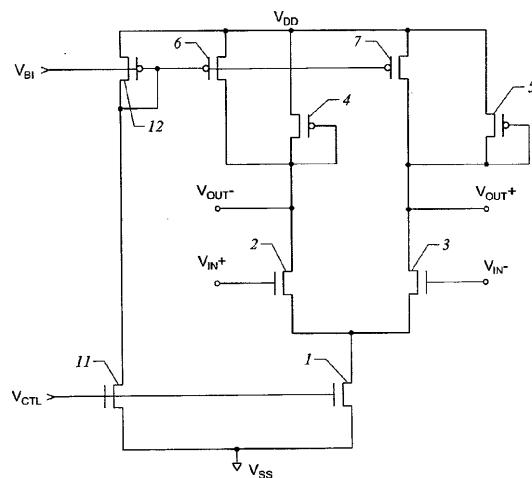

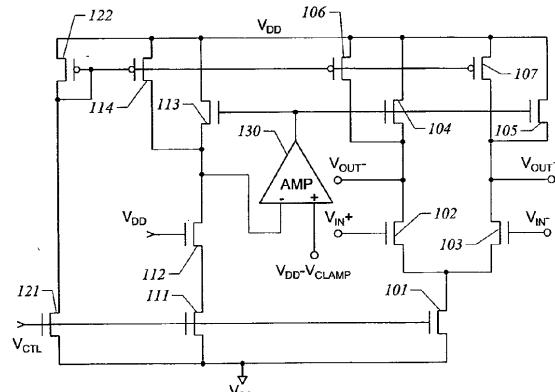

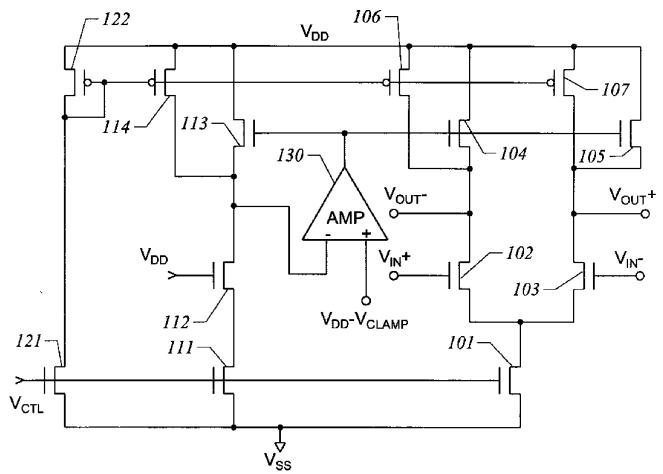

位相ロックループのリング発振器に使用される遅延回路を提供する。この遅延回路は、差動対に末尾電流を提供するN MOSトランジスタ101を有するN MOSトランジスタ102と103の差動対を含む。相補型N MOSとPMOS負荷トランジスタ104、106と105、107は、差動トランジスタ102と103に負荷を提供する。トランジスタ111～114及び121～122は、増幅器130と一緒に遅延デバイスにバイアスを提供する。増幅器130は $V_{DD} - V_{CLAMP}$ に設定した非反転入力を有する。設定に基づいて、 $V_{DD}$ から $V_{DD} - V_{CLAMP}$ までの一定の出力電圧揺れは、末尾電流を設定するのに使用する制御電圧 $V_{CTL}$ と独立して、遅延デバイスの出力 $V_{OUT+}$ と $V_{OUT-}$ で提供される。図1中のPMOSトランジスタ4とは反対に、N MOS負荷トランジスタ104はゲート寄生容量に寄与せず、少ない供給電流消費で高い動作速度を実現できる。リング発振器の動作周波数はトランジスタ101を通る末尾電流に正比例するため、図2の遅延回路を使用するリング発振器の

**【特許請求の範囲】****【請求項 1】**

遅延回路に対して相補型入力を形成する差動対の第1及び第2のトランジスタのゲートと、遅延回路の相補型出力を形成する前記差動対の前記第1及び第2のトランジスタのドレインが共通のソース構成において接続されたトランジスタ(102、103)の差動対、第1の電源( $V_{DD}$ )を前記差動対の前記第1のトランジスタ(102)のドレインに結合する分路に接続されたソースドレイン路を有する第3及び第4のトランジスタ(104、106)からなる第1の負荷、

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のトランジスタ(103)のドレインに結合する分路に接続されたソースドレイン路を有する第5及び第6のトランジスタ(105、107)からなる第2の負荷、及び

基準電圧に接続された第1の入力と、第2の入力と、出力を有する増幅器(130)と、第1の電源( $V_{DD}$ )と増幅器(130)の第2の入力間に結合したソースドレイン路を有する第7及び8のトランジスタ(113、114)からなる第3の負荷を含むバイアス回路を含み、前記第3、5及び7のトランジスタのゲートは増幅器(130)の出力に結合することを特徴とする発振器用遅延回路。

**【請求項 2】**

第1の電源( $V_{DD}$ )に結合したソースと、前記第4、6及び8のトランジスタのゲートと一緒に結合したドレインとゲートを有する第9のPMOSトランジスタ(122)を更に含むことを特徴とする請求項1に記載の遅延回路。

**【請求項 3】**

差動対の第1及び第2のトランジスタ(102、103)の共通のソースに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )に結合したゲートを有する第9のトランジスタ(101)、及び

第9のトランジスタ(122)のドレインに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )と第9のトランジスタ(101)のゲートに結合したゲートを有する第10のトランジスタ(121)を更に含むことを特徴とする請求項1に記載の遅延回路。

**【請求項 4】**

増幅器(130)の第2の入力に結合したドレインと、第1の電源( $V_{DD}$ )に結合したゲートと、ソースを有する第11のトランジスタ(112)、及び

第11のトランジスタ(112)のソースに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )と第9及び10のトランジスタ(101、122)のゲートに結合したゲートを有する第12のトランジスタ(111)を更に含むことを特徴とする請求項3に記載の遅延回路。

**【請求項 5】**

遅延回路に対して非反転入力( $V_{IN+}$ )を形成するゲートと、遅延回路の反転出力( $V_{OUT-}$ )を形成するドレインと、ソースを有する第1のNMOStранзистор(102)、及び、遅延回路の反転入力( $V_{IN-}$ )を形成するゲートと、遅延回路の非反転出力( $V_{OUT+}$ )を形成するドレインと、差動対の第1のNMOStранзисторのソースに結合したソースを有する第2のNMOStранзистор(103)からなるトランジスタの差動対、第1の電源( $V_{DD}$ )に結合したドレインと、非反転出力( $V_{OUT+}$ )に結合したソースと、ゲートを有する第3のNMOStранзистор(105)、及び、第1の電源( $V_{DD}$ )に結合したソースと、非反転出力( $V_{OUT+}$ )に結合したドレインと、ゲートを有する第1のPMOSトранзистор(107)からなる第1の負荷、

第1の電源( $V_{DD}$ )に結合したドレインと、反転出力( $V_{OUT-}$ )に結合したソースと、第3のNMOStранзистор(105)のゲートに結合したゲートを有する第4のNMOStранзистор(104)、及び、第1の電源( $V_{DD}$ )に結合したソースと、反転出力( $V_{OUT-}$ )に結合したドレインと、第1のPMOSトранзистор(107)のゲートに結合したゲートを有する第2のPMOSトранзистор(106)からなる第2の負荷、

10

20

30

40

50

第1のN MOSトランジスタ(102)と第2のN MOSトランジスタ(103)のソースに結合したドレインと、第2の電源( $V_{SS}$ )に接続されたソースと、ゲートを有する第5のN MOSトランジスタ(101)、及び

基準電圧に接続された非反転入力と、反転入力と、出力を有する増幅器(130)、

第1の電源( $V_{DD}$ )に結合したドレインと、増幅器(130)の反転入力に結合したソースと、第3のN MOSトランジスタ(105)のゲートに結合したゲートを有する第6のN MOSトランジスタ(113)、及び、第1の電源( $V_{DD}$ )に結合したソースと、増幅器(130)の反転入力に結合したドレインと、第1のPMOSトランジスタ(107)のゲートに結合したゲートを有する第3のPMOSトランジスタ(114)からなる第3の負荷、

10

増幅器(130)の反転入力に結合したドレインと、第1の電源( $V_{DD}$ )に結合したゲートと、ソースを有する第7のN MOSトランジスタ(112)、

第7のN MOSトランジスタ(112)のソースに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、第5のN MOSトランジスタ(101)のゲートに結合したゲートを有する第8のN MOSトランジスタ(111)、

第2の電源( $V_{SS}$ )に結合したソースと、第5のN MOSトランジスタ(112)のゲートと遅延回路の遅延制御電圧入力( $V_{CTL}$ )とに結合したゲートと、ドレインを有する第9のN MOSトランジスタ(121)、及び

第1の電源( $V_{DD}$ )に結合したソースと、第9のN MOSトランジスタ(121)のドレインと第1のPMOSトランジスタ(107)のゲートとに一緒に結合したドレインとゲートを有する第4のPMOSトランジスタ(122)を含むバイアス回路を含むことを特徴とする発振器用遅延回路。

20

#### 【請求項6】

第1、2、3及び4のPMOSトランジスタ(107、106、114122)の各々のW/L(幅対長さ)比を等しくし、第3、4及び6のN MOSトランジスタ(105、104、113)の各々のW/L(幅対長さ)比を等しくし、第1、2及び7のN MOSトランジスタ(102、103、112)の各々のW/L(幅対長さ)比を等しくし、第5のN MOSトランジスタ(101)のW/L(幅対長さ)比を第8及び9のトランジスタ(111、121)の各々のW/L(幅対長さ)比の2倍にし、第3及び4のN MOSトランジスタ(104、105)のW/L(幅対長さ)比を第1及び2のPMOSトランジスタ(107、106)の各々のW/L(幅対長さ)比の1/3にすることを特徴とする請求項5に記載の遅延回路。

30

#### 【請求項7】

遅延回路に対して相補型入力を形成する差動対の第1及び第2のN MOSトランジスタのゲートと、遅延回路の相補型出力を形成する前記差動対の前記第1及び第2のN MOSトランジスタのドレインが共通のソース構成において接続されたN MOSトランジスタ(102、103)の差動対、

第1の電源( $V_{DD}$ )を前記差動対の前記第1のN MOSトランジスタ(102)のドレインに結合する分路に接続されたソースドレイン路を有する第1のPMOSトランジスタ(106)と第3のN MOSトランジスタ(104)からなる第1の負荷、

40

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のN MOSトランジスタ(103)のドレインに結合する分路に接続されたソースドレイン路を有する第2のPMOSトランジスタ(107)と第4のN MOSトランジスタ(105)からなる第2の負荷、及び前記第1の負荷の前記第1のPMOSトランジスタ(106)と前記第3のN MOSトランジスタ(104)のゲートと、前記第2の負荷の前記第2のPMOSトランジスタ(107)と前記第4のN MOSトランジスタ(105)とにバイアス電圧を提供する電圧バイアス回路を含むことを特徴とする発振器用遅延回路。

#### 【請求項8】

遅延回路に対して相補型入力を形成する差動対の第1及び第2のトランジスタのゲートと、遅延回路からの相補型出力を形成する前記差動対の前記第1及び第2のトランジスタの

50

ドレインが共通のソース構成において接続されたトランジスタ(102、103)の差動対、

第1の電源( $V_{DD}$ )を前記差動対の前記第1のトランジスタ(102)のドレインに結合する分路に接続されたソースドレイン路を有する第3及び第4のトランジスタ(104、106)からなる第1の負荷、

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のトランジスタ(103)のドレインに結合する分路に接続されたソースドレイン路を有する第5及び第6のトランジスタ(105、107)からなる第2の負荷、及び

高低電圧入力が遅延回路の入力に印加される時、遅延回路の出力間電圧揺れが一定のままであるように、前記第1の負荷と前記第2の負荷のトランジスタのゲートにバイアス電圧を提供する電圧バイアス回路を含むことを特徴とする発振器用遅延回路。

10

#### 【請求項9】

遅延回路に対して相補型入力を形成する差動対の第1及び第2のトランジスタのゲートと、遅延回路からの相補型出力を形成する前記差動対の前記第1及び第2のトランジスタのドレインが共通のソース構成において接続されたトランジスタ(102、103)の差動対、

第1の電源( $V_{DD}$ )を前記差動対の前記第1のトランジスタ(102)のドレインに結合する分路に接続されたソースドレイン路を有する第3及び第4のトランジスタ(104、106)からなる第1の負荷、

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のトランジスタ(103)のドレインに結合する分路に接続されたソースドレイン路を有する第5及び第6のトランジスタ(105、107)からなる第2の負荷、

20

差動トランジスタ対のソースを第2の電源( $V_{SS}$ )に結合するソースドレイン路を有し、遅延回路により提供される時間遅延を制御するように制御電圧を印加するゲートを有する末尾電流制御トランジスタ(101)、及び

前記時間遅延が前記末尾電流制御トランジスタ(101)のソースからドレインへ提供される末尾電流に線形比例するように、前記第1の負荷と前記第2の負荷のトランジスタのゲートにバイアス電圧を提供する電圧バイアス回路を含むことを特徴とする発振器用遅延回路。

#### 【発明の詳細な説明】

30

#### 【技術分野】

#### 【0001】

本発明は、位相ロックループのリング発振器において使用される遅延回路に関するものである。

#### 【背景技術】

#### 【0002】

位相ロックループは、通信、デジタル回路及び大量記憶電子装置を含む多くの用途に使用される。多くの位相ロックループ設計が当業者に周知である。従来の位相ロックループ設計は、位相ロックループの性能を決定する重要な部分である電圧または電流制御発振器を備える。位相ロックループ用電圧または電流制御発振器の重要なパラメータは、(1)出力振幅の最小変動と低ジッターを有する電圧制御発振器周波数の同調範囲、または最小値と最大値間範囲、(2)電源と基板の雑音除去、及び(3)電力消費を含む。

40

#### 【0003】

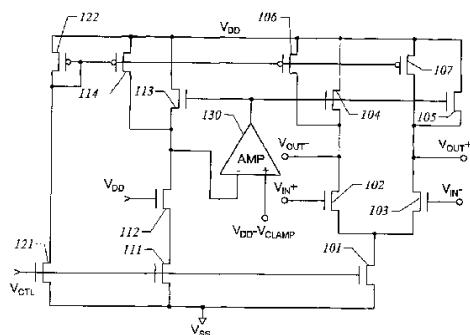

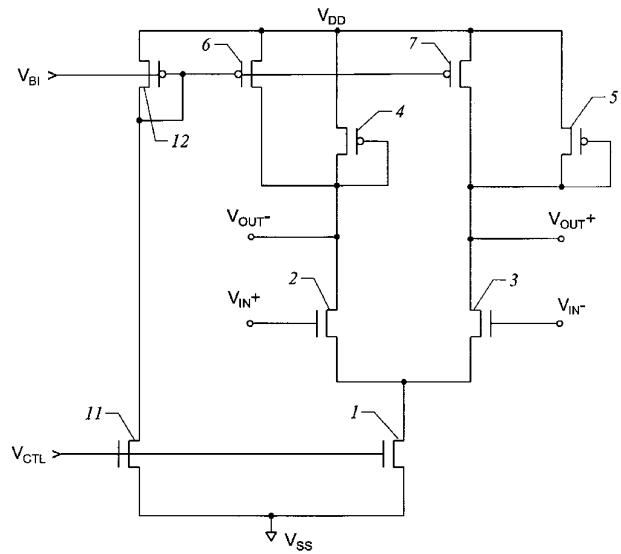

図1は、位相ロックループの電圧または電流制御発振器のリング発振器において使用される従来の遅延回路を示す。図1の遅延回路は、IEEE JSSC、Vol. 31、No. 11、1996年11月号の第1723～1732頁に開示されている。トランジスタ1～7は遅延段を形成し、トランジスタ11と12は遅延回路にバイアスを提供する。

#### 【0004】

遅延段は、抵抗負荷4～7を有するトランジスタ2と3とのソース結合対を含む。抵抗負荷はそれぞれ、等しい大きさにされバイアスされたPMOSデバイス6又は7との分路に

50

おいてダイオードが接続されたPMOSデバイス4又は5を含む。トランジスタ4～7はそれらのゲート上に与えた円で図示されるPMOSデバイスであり、かかるゲートの円なしトランジスタ例えは2と3はNMOSデバイスである。ゲートの円は、図1とそれ以降の図において、どのトランジスタがPMOSとNMOSデバイスであるかを示すのに使用する。

#### 【0005】

適正なバイアスに対して、トランジスタ11、12、6及び7の大きさは、例えばトランジスタ2がオンであるとき、トランジスタ6がトランジスタ1の電流の1/2を引き出すように選ぶ。同様に、トランジスタ3がオンであるとき、トランジスタ7がトランジスタ1の電流の1/2を引き出す。

10

#### 【0006】

図1の遅延回路は、 $V_{DD}$ から $V_{DD} - V_{GS}$ までの出力電圧の揺れを有する。ここで、 $V_{GS}$ は、 $V_T + 2 * I_D / k$ に等しいゲートとソース間電圧である（kは導通している負荷トランジスタ4又は5の一方のデバイスの相互コンダクタンスであり、 $I_D$ はトランジスタ4又は5の一方のドレイン電流であり、通常、時間遅延制御電圧 $V_{CTL}$ によって制御されるトランジスタ1を通る末尾電流の半分である）。

#### 【0007】

図1の遅延回路の遅延時間は、 $T_D = R_{EFF} * C_{EFF} = (1 / 2 * k * I_D) * C_{EFF}$ として近似される。 $R_{EFF}$ は、電圧の揺れの範囲の端での小信号抵抗であり、導通している負荷トランジスタ4又は5の一方の相互コンダクタンスの逆数である。 $C_{EFF}$ は、合計有効容量であり、トランジスタ2と6とのドレイン容量、トランジスタ4のゲートとドレインの容量、及びリング発振器の次の後続の遅延段の入力トランジスタのゲート容量を含む。有効容量 $C_{EFF}$ を制限することで、電力消費を減少し、更に動作速度を増加できる。

20

#### 【0008】

図1に示す回路のN段を有するリング発振器に対して、リング発振器の動作周波数 $f_1$ は

$$f_1 = 1 / (2 * N * T_D) = 2 * k * I_D / (2 * N * C_{EFF})$$

従って、図1に示す回路を使用するリング発振器は、( $I_D$ と( $I_D$ に比例する動作周波数 $f_1$ とともに変化する出力電圧の揺れを有する。出力電圧の揺れが( $I_D$ とともに変動するのは、動作周波数の全範囲で電源と基板の雑音除去を減少させるため、望ましくない。なお、動作周波数 $f_1$ の同調範囲は、平方根関数に従う末尾電流 $I_D$ の制限によって制御される。

30

#### 【0009】

本発明の目的は、図1の遅延回路に比べて、一定の出力揺れ、広い同調範囲、高い動作速度及び低い電力消費を有する電圧または電流制御発振器用遅延回路を提供することにある。

#### 【0010】

本発明の目的は、電圧または電流制御発振器のリング発振器において使用される遅延回路を提供することにある。この遅延回路は、差動対に末尾電流を提供するNMOSトランジスタ101を有するNMOSトランジスタ102と103の差動対を含む。相補型NMO SとPMOS負荷トランジスタ104、106と105、107は、差動トランジスタ102と103に負荷を提供する。トランジスタ111～114及び121～122は、増幅器130と一緒に、遅延調節回路にバイアスを提供する。

40

#### 【0011】

増幅器130は、 $V_{DD} - V_{CLAMP}$ に設定した非反転入力(+)を有し、遅延回路のトランジスタのW/L(幅対長さ)比は、トランジスタ101、102、104及び106、又は101、103、105及び107のいずれかがバイアストランジスタ111、112、113及び114をそれぞれ複製するように設定する。設定に基づいて、 $V_{DD}$ から $V_{DD} - V_{CLAMP}$ までの一定の出力電圧揺れが遅延デバイスの出力 $V_{OUT+}$ と $V_{OUT-}$ で提供される。 $V_{CLAMP}$ はトランジスタ101からのバイアス末尾電流を制御する制御電圧 $V_{CTL}$ と独

50

立であるので、時間遅延回路の出力電圧の揺れは、制御電圧  $V_{CTL}$  によって制御される異なる末尾電流に対して一定になる。一定の出力電圧の揺れのため、遅延回路は動作電流の変動範囲で、図 1 の遅延回路に比べてより良い雑音除去を提供できる。

#### 【0012】

図 1 (従来) の PMOS ドランジスタ 4 又は 5 はリング発振器の動作周波数に影響する有効容量  $C_{EFF}$  に寄与するが、図 2 (本発明) の遅延回路では、リング発振器の動作周波数に影響する有効容量  $C_{EFF}$  への NMOS 負荷ドランジスタ 104 又は 105 の寄与は少ないので、図 2 の遅延回路はより少ない供給電流消費でより高い動作速度を得ることができる。加えて、図 1 のデバイス動作周波数は末尾電流の平方根に比例するのに対し、図 2 の遅延回路を使用するリング発振器の動作周波数は末尾電流に比例するため、図 2 の遅延回路を使用するリング発振器の周波数の同調範囲は、図 1 の回路の同調範囲より広くすることができる。

10

#### 【0013】

#### 【0014】

図 2 は、本発明による電圧または電流制御発振器のリング発振器において使用される遅延回路を示す。この遅延回路は、NMOS ドランジスタ 102 と 103 の差動対に末尾電流を提供する NMOS ドランジスタ 101 を含む。NMOS ドランジスタ 104 と PMOS ドランジスタ 106 は、差動対のドランジスタ 102 に対する相補負荷を形成する。同様に、NMOS ドランジスタ 105 と PMOS ドランジスタ 107 は、差動対のドランジスタ 103 に対する相補負荷を形成する。ドランジスタ 111 ~ 114 及び 121 ~ 122 20 は、増幅器 130 と一緒に、遅延デバイスに適正なバイアスを提供する。

#### 【0015】

ドランジスタ 106 と 107 のゲートバイアスは、図 1 のドランジスタ 6 と 7 のバイアスと同様である。バイアスの 1 例では、ドランジスタ 106、107、114 及び 122 の W / L (幅対長さ) 比を等しくする。更に、ドランジスタ 104、105 及び 113 の W / L (幅対長さ) 比を等しくし、ドランジスタ 102、103 及び 112 の W / L (幅対長さ) 比を等しくする。更に、ドランジスタ 101 の W / L (幅対長さ) 比は、ドランジスタ 111 と 121 の W / L (幅対長さ) 比の 2 倍にする。最後に、ドランジスタ 104 と 105 の W / L (幅対長さ) 比は、ドランジスタ 106 と 107 の W / L (幅対長さ) 比の 1 / 3 にする。

30

#### 【0016】

図 2 の遅延回路は、後述するように、電圧または電流制御発振器において使用する場合に図 1 の遅延回路より幾つかの利点を提供する。

#### 【0017】

図 2 の遅延回路の第 1 の利点は、 $V_{DD}$  から  $V_{DD} - V_{CLAMP}$  までの一定の出力電圧揺れを有することである。例えば  $V_{IN+}$  が高く  $V_{IN-}$  が低い場合、ドランジスタ 101、102、104 及び 106 がそれぞれドランジスタ 111、112、113 及び 114 のバイアスを複製するため、 $V_{OUT-}$  は  $V_{DD} - V_{CLAMP}$  になるようにクランプされる。同時に、ドランジスタ 107 がカットオフになるまでドランジスタ 107 は出力ノードをチャージするため、 $V_{OUT+}$  は  $V_{DD}$  になる。同じ理由で、 $V_{IN+}$  が低く  $V_{IN-}$  が高い場合、 $V_{OUT-}$  は  $V_{DD}$  になり、 $V_{OUT+}$  は  $V_{DD} - V_{CLAMP}$  になる。 $V_{CLAMP}$  はドランジスタ 101 からのバイアス末尾電流を制御する制御電圧  $V_{CTL}$  と独立であるので、図 2 の時間遅延回路の出力電圧の揺れは、制御電圧  $V_{CTL}$  によって制御される異なる末尾電流に対して一定になる。図 1 の遅延回路に比べて、一定の出力電圧の揺れを有する図 2 の遅延回路によって、差動 単終端 (differential to single ended) 変換器をより容易に設計でき、完全な同調範囲に亘ってより良い電源と基板の雑音除去を有する発振器を作ることに使用できる。

40

#### 【0018】

図 2 の遅延回路の第 2 の利点は、遅延時間が、 $T_D = R_{EFF} * C_{EFF} = C_{EFF} * V / I$  として近似されることである (ここで、I は制御電圧  $V_{CTL}$  によって制御されるドランジスタ 1

50

0 1 の末尾電流の半分であり、V はクランプ電圧  $V_{CLAMP}$  と同じである）。 $C_{EFF}$  は、トランジスタ 103 と 107 のドレイン容量、トランジスタ 105 のソース容量、及び次の遅延段の入力トランジスタのゲート容量の合計寄生容量である。図 2 の回路の N 段を有する発振器に対して、回路の動作周波数  $f_2$  は、

$$f_2 = 1 / (2 * N * T_D) = I / (2 * N * C_{EFF} * V)$$

図 2 中の NMOS トランジスタ 104 の大きさは、図 1 中の PMOS トランジスタ 4 の大きさの  $1/3$  であり、NMOS トランジスタ 104 はゲート～基板容量  $C_{GB} \sim C_{EFF}$  に寄与しないが、図 1 の PMOS トランジスタ 4 は寄与する。図 2 の遅延回路の  $C_{EFF}$  は図 1 の遅延回路の  $C_{EFF}$  より著しく少ない。それ故、図 2 の遅延回路はより少ない供給電流消費でより高い動作速度を得ることができる。加えて、図 1 の遅延回路を使用するリング発振器の動作周波数は末尾電流  $I_D$  の平方根に比例するのに対して、図 2 の遅延回路を使用するリング発振器の動作周波数は末尾電流  $I_D$  に比例するため、図 2 の遅延回路の周波数の同調範囲は、図 1 の回路の周波数の同調範囲より広くすることができる。

### 【0019】

本発明を特定の構成について上述したが、これは本発明の製造及び使用方法を単に例示するためのものであり、多くの他の修正は発明の請求の範囲内であり得るであろう。

### 【図面の簡単な説明】

### 【0020】

【図 1】従来のリング発振器用遅延回路である。

【図 2】本発明によるリング発振器用遅延回路である。

10

20

【図 1】

図 1

【図 2】

図2

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

17 October 2002 (17.10.2002)

PCT

(10) International Publication Number

WO 02/082649 A1

(51) International Patent Classification': H03K 5/08

(21) International Application Number: PCT/US02/10889

(22) International Filing Date: 8 April 2002 (08.04.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/828,398 6 April 2001 (06.04.2001) US(71) Applicant: ELANTEC SEMICONDUCTOR, INC.

[US/US]; 675 Tradezone Boulevard, Milpitas, CA 95035

(US).(72) Inventors: LIN, Xijian; 40951 Valero Drive, Fremont, CA

94539 (US). HARVEY, Barry; 1701 Holt Avenue, Los

Altos, CA 94025 (US). FAIRGRIVE, Alexander; 2139

Gordon Avenue, Menlo Park, CA 94025 (US).(74) Agents: FLIESLER, Martin, C. et al.; Fliesler Dubb

Meyer and Lovejoy LLP, Four Embarcadero Center, Suite

400, San Francisco, CA 94111-4156 (US).(81) Designated States (national): AL, AG, AL, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU,

CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GR, GU,

GM, IIR, IHU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG,

SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN,

YU, ZA, ZM, ZW.(84) Designated States (regional): ARIPO patent (GH, GM,

KE, LS, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW),

Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR,

GB, GR, IE, IL, LU, MC, NL, PL, SE, TR), OAPI patent

(BJ, BJ, CH, CG, CI, CM, GA, GN, GQ, GW, ML, MR,

NE, SN, TD, TG).Published:

with international search report

before the expiration of the time limit for amending the

claims and to be republished in the event of receipt of

amendments

[Continued on next page]

(54) Title: A CMOS CIRCUIT WITH CONSTANT OUTPUT SWING AND VARIABLE TIME DELAY FOR A VOLTAGE CONTROLLED OSCILLATOR

A1

WO 02/082649

**(57) Abstract:** A delay circuit is provided for use in a ring oscillator of a phase locked loop (PLL). The delay circuit includes a differential pair of NMOS transistors 102 and 103 with an NMOS transistor 101 providing the tail current for the differential pair. Complementary NMOS and PMOS load transistors 104, 106 and 105, 107 provide loads for the differential transistor 102 and 103. Transistors 111-114 and 121-123 together with an amplifier 130 provide biasing for the delay device. The amplifier 130 has a non-inverting input set to  $V_{DD}-V_{CLAMP}$ . As configured, a constant output voltage swing from  $V_{DD}$  to  $V_{DD}-V_{CLAMP}$  is provided at the outputs  $V_{OUT+}$  and  $V_{OUT-}$  of the delay device, independent of a control voltage  $V_{CTRL}$  used to set the tail current. The NMOS load transistor 104, as opposed to the PMOS transistor 4 in fig. 1, does not contribute to the gate parasitic capacitance enabling a high operation speed without consumption of more supply current. A wide frequency tuning range of a ring oscillator using the delay circuit of fig. 2 is provided because the operating frequency for a ring oscillator will be directly proportional to the tail current through transistor 101.

---

**WO 02/082649 A1**

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 02/082649

PCT/US02/10889

A CMOS Circuit with Constant Output Swing and Variable Time Delay for a Voltage Controlled Oscillator

5

**BACKGROUND OF THE INVENTION**

1. Field of the Invention

The present invention relates to delay circuits for use in a ring oscillator of a phase locked loop.

10

2. Background

Phase-Locked loops (PLL) are used in a number of applications, including communications, digital circuits and mass storage electronics. A number of designs for PLLs are known to a person of ordinary skill in the art. The conventional PLL designs include a voltage or current controlled oscillator (VCO or ICO), a critical part in determining the performance of the PLL. Important parameters of a VCO or ICO for a PLL include: (1) Tuning range, or the range between the minimum and maximum values of the VCO frequency with minimal variation of the output amplitude and low jitter; (2) Supply and substrate noise rejection; and (3) Power consumption.

25 Fig. 1 shows a conventional delay circuit which can be used in a ring oscillator of a VCO or ICO of a PLL. The delay circuit of Fig. 1 is disclosed in IEEE JSSC, Vol. 31, No. 11, November 1996, pp. 1723-1732. Transistors 1-7 form a delay stage and transistors 11

30 and 12 provide the biasing for the delay circuit.

The delay stage contains a source-coupled pair of transistors 2 and 3 with resistive loads 4-7. The loads each include a diode-connected PMOS device 4 or

WO 02/082649

PCT/US02/10889

- 2 -

5 in shunt with an equally sized biased PMOS device 6 or 7. Transistors 4-7 are PMOS devices as illustrated by the circle provided on their gate, while transistors such as 2 and 3 without such a gate circle are NMOS 5 devices. The gate circles are used to show which transistors are PMOS and NMOS devices in Fig. 1, as well as in subsequent figures.

For proper bias, the sizes of transistors 11, 12, 6 and 7 are chosen so that when, for example transistor 10 2 is fully on, transistor 6 draws  $\frac{1}{2}$  the current of transistor 1. Likewise, if transistor 3 is fully on, then transistor 7 draws  $\frac{1}{2}$  the current of transistor 1.

The delay circuit of Fig. 1 has an output voltage swing from  $V_{DD}$  to  $V_{DD}-V_{GS}$ . Here,  $V_{GS}$  is a gate-source 15 voltage equal to  $V_t + \sqrt{2}I_D/k$ , where  $k$  is the device transconductance of one of conducting load transistors 4 or 5.  $I_D$  is the drain current of one of transistors 15 4 or 5, which is typically half of the tail current through transistor 1, as controlled by the time delay 20 control voltage  $V_{CTL}$ .

The delay time of the delay circuit of Fig. 1 can be approximated as  $T_d = R_{EFF} * C_{EFF} = (1/\sqrt{2}k * I_D) * C_{EFF}$ .  $R_{EFF}$  is the small signal resistance at the ends of the voltage swing ranges that is the inverse of the 25 transconductance for one of the two conducting load transistors 4 or 5.  $C_{EFF}$  is the total effective capacitance and includes the drain capacitance of transistors 2 and 6, the gate and drain capacitance of transistor 4, and the gate capacitance of the input 30 transistor of a next subsequent delay stage of the ring

WO 02/082649

PCT/US02/10889

- 3 -

oscillator. Limiting the effective capacitance,  $C_{eff}$ , reduces power consumption and further can enable increased operation speed.

For a ring oscillator with N stages of the circuit shown in Fig. 1, the operating frequency  $f_1$  of the ring oscillator will be:

$$f_1 = 1 / (2 * N * T_0) = \sqrt{2 * k * I_b} / (2 * N * C_{eff})$$

Accordingly, the ring oscillator using the circuit shown in Fig. 1 has the output voltage swing changing with  $\sqrt{I_b}$  and an operating frequency  $f_1$  proportional to  $\sqrt{I_b}$ . Variations of the output voltage swing with  $\sqrt{I_b}$  is an undesirable feature because such variation decreases power supply and substrate noise rejection over the whole operating frequency range. Further, the tuning range of the operating frequency  $f_1$  is controlled by limitations on the tail current  $I_b$  according to the square root function.

20

#### SUMMARY OF THE INVENTION

In accordance with the present invention, an improved delay circuit for a VCO or ICO with a constant output swing, a wide tuning range, a high operation speed and low power consumption relative to the circuit of Fig. 1 is provided.

In accordance with the present invention, referring to Fig. 2, a delay circuit is provided which may be used in a ring oscillator of a VCO or ICO. The delay circuit includes a differential pair of NMOS

- 4 -

transistors 102 and 103 with an NMOS transistor 101 providing the tail current for the differential pair. Complementary NMOS and PMOS load transistors 104, 106 and 105, 107 provide loads for the differential 5 transistors 102 and 103. Transistors 111-114 and 121-122 together with an amplifier 130 provide biasing for the delay adjustment circuitry.

The amplifier 130 has a non-inverting (+) input set to  $V_{DD}-V_{CLAMP}$ , and W/L ratios of the transistors of the 10 delay circuit are set so that either transistors 101, 102, 104 and 106, or 101, 103, 105 and 107 replicate the biasing transistors 111, 112, 113 and 114 respectively. As configured, a constant output voltage 15 swing from  $V_{DD}$  to  $V_{DD}-V_{CLAMP}$  is provided at the outputs  $V_{out+}$  and  $V_{out-}$  of the delay device. Since  $V_{CLAMP}$  is independent of the control voltage  $V_{CTL}$  which controls the bias tail current from transistor 101, the output voltage swing of the time delay circuit will be constant for different tail currents as controlled by 20  $V_{CTL}$ . The constant output voltage swing enables the delay circuit to provide better noise rejection relative to the circuit of Fig. 1 over variations of operating current.

For the circuit of Fig. 2, the NMOS load transistors 25 104 or 105 contribute less to the effective capacitance  $C_{eff}$  which affects the operating frequency of a ring oscillator, whereas the PMOS transistors 4 or 5 of Fig. 1 do, so the circuit of Fig. 2 can obtain a higher operation speed without consuming more supply current.

30 In addition, the frequency tuning range of a ring

WO 02/082649

PCT/US02/10889

- 5 -

oscillator using the circuit of Fig. 2 can be made wider than that of the circuit of Fig. 1 because the operating frequency for a ring oscillator using the circuit of Fig. 2 is proportional to the tail current whereas the operating frequency using the device of Fig. 1 is proportional to the square root of the tail current.

**BRIEF DESCRIPTION OF THE DRAWINGS**

- 10 The present invention will be described with respect to particular embodiments thereof, and references will be made to the drawings in which:

Fig. 1 shows a conventional delay circuit for a ring oscillator; and

15 Fig. 2 shows a delay circuit for a ring oscillator in accordance with the present invention.

**DETAILED DESCRIPTION**

Fig. 2 shows an improved delay circuit for use in a ring oscillator of a VCO or an ICO in accordance with the present invention. The circuit includes an NMOS transistor 101 providing the tail current for the differential pair of NMOS transistors 102 and 103. An NMOS transistor 104 and a PMOS transistor 106 form a complementary load for transistor 102 of the differential pair. Similarly, an NMOS transistor 105 and a PMOS transistor 106 form a complementary load for the transistor 103 of the differential pair. Transistors 111-114 and 121-122 together with the

WO 02/082649

PCT/US02/10889

- 6 -

amplifier 130 shown in Fig. 2 provide proper biasing for the delay device.

The gate bias of transistors 106 and 107 follows the same considerations as the bias of transistors 6 and 7 of Fig. 1. In one example for biasing, the W/L ratio of transistors 106, 107, 114 and 122 are set equal. Further, the W/L ratio of transistors 104, 105 and 113 are set equal, and the W/L ratio of transistors 102, 103 and 112 are set equal. Further, the W/L ratios of transistor 101 is set to two times the W/L ratio of transistors 111 and 121. Finally, the W/L ratios of transistors 104 and 105 are set at 1/3 of the W/L ratio of transistors 106 and 107.

The circuit of Fig. 2 provides several advantages when used in a VCO or ICO over the circuit of Fig. 1. The advantages are described in subsequent paragraphs.

First, the delay circuit of Fig. 2 has a constant output voltage swing from  $V_{DD}$  to  $V_{DD}-V_{CLAMP}$ . When  $V_{IN+}$  is high and  $V_{IN-}$  is low, for example,  $V_{OUT-}$  will be clamped to be  $V_{DD}-V_{CLAMP}$  because transistors 101, 102, 104 and 106 replicate the biasing of transistors 111, 112, 113 and 114, respectively. At the same time,  $V_{OUT+}$  will be  $V_{DD}$  because transistor 107 will charge the output node until transistor 107 becomes cutoff. For the same reason, if  $V_{IN+}$  is low and  $V_{IN-}$  is high,  $V_{OUT-}$  will be at  $V_{DD}$  and  $V_{OUT+}$  will be at  $V_{DD}-V_{CLAMP}$ . Since  $V_{CLAMP}$  is independent of the control voltage  $V_{ctrl}$  which controls the bias tail current from transistor 101, the output voltage swing of the time delay circuit of Fig. 2 is constant for the different tail currents as controlled

WO 02/082649

PCT/US02/10889

- 7 -

by  $V_{CTRL}$ . Compared with the circuit in Fig. 1, the circuit having the constant output voltage swing in Fig. 2 enables a differential-to-single-ended converter to be designed more easily and can be used to make an 5 oscillator with a better power supply and substrate noise rejection over a complete tuning range.

Further, the time delay of the circuit of Fig. 2 is approximately,  $T_D = R_{EFF} \cdot C_{EFF} = C_{EFF} \cdot V / I$ , where  $I$  is a half of the tail current of transistor 101 as controlled by 10 control voltage  $V_{CTRL}$  and  $V$  is the same as the clamping voltage  $V_{CLAMP}$ .  $C_{EFF}$  is the total parasitic capacitance at the drains of transistors 103 and 107, the source capacitance of transistor 105, and the gate capacitance of an input transistor of the next stage. For an 15 oscillator with  $N$  stages of the circuit of Fig. 2, the circuit will have an operating frequency  $f_2$  expressed as follows:

$$f_2 = 1 / (2 * N * T_D) = I / (2 * N * C_{EFF} * V)$$

20

Since the size of NMOS transistor 104 in Fig. 2 is one third of that of PMOS transistor 4 in Fig. 1, and NMOS transistor 104 does not contribute to the gate to 25 substrate capacitance  $C_{GS}$  to  $C_{EFF}$  whereas PMOS transistor 4 does,  $C_{EFF}$  for the circuit of Fig. 2 is significantly less than  $C_{EFF}$  for the circuit shown in Fig. 1. Therefore, the circuit of Fig. 2 can obtain a higher operation speed without consuming more supply current. In addition, the frequency tuning range of the circuit 30 of Fig. 2 should be wider than that of the previous

WO 02/082649

PCT/US02/10889

- 8 -

circuit because the operating frequency of a ring oscillator using the circuit of Fig. 2 is proportional to the tail current  $I_D$ , whereas the operating frequency of a ring oscillator using the circuit of Fig. 1 will 5 be proportional to the square root of the tail current  $I_D$ .

Although the present invention has been described above with particularity, this was merely to teach one of ordinary skill in the art how to make and use the 10 invention. Many other modifications will fall within the scope of the invention, as that scope is defined by the claims provided below.

- 9 -

**CLAIMS**

What is claimed is:

1. A delay circuit for an oscillator comprising:

- 5 a differential pair of transistors (102,103) connected in a common source configuration with gates of first and second transistors of the differential pair forming complementary inputs to the delay circuit, and drains of the first and second transistors of the differential pair forming complementary outputs of the delay circuit;

- 10 a first load comprising third and fourth transistors (104,106) having source-drain paths connected in shunt to couple a first voltage supply ( $V_{DD}$ ) to the drain of the first transistor (102) of the differential pair;

- 15 a second load comprising fifth and sixth transistors (105,107) having source-drain paths connected in shunt to couple the first voltage supply ( $V_{DD}$ ) to the drain of the second transistor (103) of the differential pair;

- 20 and

- a bias circuit comprising:

- an amplifier (130) having a first input connected to a voltage reference, a second input and an output;

- 25 a third load comprising seventh and eighth transistors (113,114) having source-drain paths coupled between the first voltage supply ( $V_{DD}$ ) and the second input of the amplifier, wherein gates of the third, fifth and seventh transistors are coupled to the output

- 30 of the amplifier.

WO 02/082649

PCT/US02/10889

- 10 -

2. The delay circuit of claim 1 further comprising:

a ninth transistor (122) having a source coupled to

the first voltage supply ( $V_{DD}$ ) and a drain and gate

coupled together and to the gates of the fourth, sixth

5 and eight transistors.

3. The delay circuit of claim 1 further comprising:

an ninth transistor (101) having a drain coupled to

the common sources of the first and second transistors

10 (102,103) of the differential pair and a source coupled

to a second voltage supply ( $V_{SS}$ ), and having a gate

coupled to a delay control voltage input ( $V_{ctrl}$ ); and

a tenth transistor (121) having a drain coupled to

the drain of the ninth transistor (122), a source

15 coupled to the second voltage supply ( $V_{SS}$ ) and a gate

coupled to the delay control voltage input ( $V_{ctrl}$ ) and

the gate of the ninth transistor.

4. The delay control transistor of claim 3 further

20 comprising:

an eleventh transistor (112) having a drain coupled

to the second input of the amplifier, a gate coupled to

the first voltage supply ( $V_{DD}$ ), and having a source; and

a twelfth transistor (111) having a drain coupled to

25 the source of the eleventh transistor (112) a source

coupled to the second voltage supply ( $V_{SS}$ ), and a gate

coupled to the delay control voltage and the gates of

the ninth and tenth transistors (101,122).

30 5. A delay circuit for an oscillator comprising:

- 11 -

a differential pair of transistors comprising:

a first NMOS transistor (102) having a gate forming a noninverting input ( $V_{IN^+}$ ) to the delay circuit, a drain forming an inverting output ( $V_{OUT^-}$ ) of

5 the delay circuit, and having a source; and

a second NMOS transistor (103) having a gate forming an inverting input ( $V_{IN^-}$ ) of the delay circuit, a drain forming a noninverting output ( $V_{OUT^+}$ ) of the delay circuit, and having a source coupled to the

10 source of the first transistor of the differential pair;

a first load comprising:

a third NMOS transistor (105) having a drain coupled to a first voltage supply ( $V_{DD}$ ), a source coupled to the noninverting output ( $V_{OUT^+}$ ), and having

15 a gate; and

a first PMOS transistor (107) having a source coupled to the first voltage supply ( $V_{DD}$ ), a drain coupled to the noninverting output ( $V_{OUT^+}$ ), and having

20 a gate;

a second load comprising:

a fourth NMOS transistor (104) having a drain coupled to the first voltage supply ( $V_{DD}$ ), a source coupled to the inverting output ( $V_{OUT^-}$ ), and having a

25 gate coupled to the gate of the third NMOS transistor (105); and

a second PMOS transistor (106) having a source coupled to the first voltage supply ( $V_{DD}$ ), a drain coupled to the inverting output ( $V_{OUT^-}$ ), and having a

WO 02/082649

PCT/US02/10889

- 12 -

gate coupled to the gate of the first PMOS transistor (107);

a fifth NMOS transistor (101) having a drain coupled to the sources of the first and second transistors, a

5 source connected to a second voltage supply ( $V_{ss}$ ), and

having a gate; and

a bias circuit comprising:

an amplifier (130) having a noninverting input

connected to a voltage reference, an inverting input

10 and an output;

a third load comprising:

an sixth NMOS transistor (113) having a drain coupled to the first voltage supply ( $V_{dd}$ ), a source coupled to the inverting input of the amplifier

15 (130), and having a gate coupled to the gate of the third NMOS transistor (105); and

a third PMOS transistor (114) having a source coupled to the first voltage supply ( $V_{dd}$ ), a drain coupled to the inverting input of the amplifier

20 (130), and having a gate coupled to the gate of the first PMOS transistor (107);

a seventh NMOS transistor (112) having a drain coupled to the inverting input of the amplifier (130), a gate coupled to the first voltage supply ( $V_{dd}$ ), and

25 having a source;

a eighth NMOS transistor (111) having a drain coupled to the source of the seventh NMOS transistor (112), a source coupled to the second voltage supply ( $V_{ss}$ ), a gate coupled to the gate of the fifth NMOS

30 transistor (101);

WO 02/082649

PCT/US02/10889

- 13 -

a ninth NMOS transistor (121) having a source coupled to the second voltage supply ( $V_{SS}$ ), a gate coupled to the gate of the fifth NMOS transistor (112) and to a delay control voltage input ( $V_{CN}$ ) of the delay circuit, and having a drain; and

5 a fourth PMOS transistor (122) having a source coupled to the first voltage supply ( $V_{DD}$ ), and a drain and gate coupled together to the drain of the ninth NMOS transistor (121) and to the gate of the first PMOS transistor (107).

10

6. The delay circuit of claim 5,

wherein a width-to-length (W/L) ratio of each of the first, second, third, and fourth PMOS transistors (107, 106, 114, 122) are equal,

15 wherein a W/L ratio of each of the third, fourth, and sixth NMOS transistors (105, 104, 113) are equal,

wherein a W/L ratio of each of the first, second, and seventh NMOS transistors (102, 103, 112) are equal,

20 wherein a W/L ratio of the fifth NMOS transistor (101) is equal to two times the W/L ratio of each of the eighth and ninth NMOS transistors (111, 121), and

wherein the W/L ratio of each of the third and fourth NMOS transistors (104, 105) is equal to one third

25 of the W/L of each of the first and second PMOS transistors (107, 106).

26

7. A delay circuit for an oscillator comprising:

a differential pair of NMOS transistors (102, 103)

30 connected in a common source configuration with gates

WO 02/082649

PCT/US02/10889

- 14 -

of first and second NMOS transistors of the differential pair forming complementary inputs to the delay circuit, and drains of the first and second NMOS transistors of the differential pair forming complementary outputs of the delay circuit;

a first load comprising a first PMOS transistor (106) and a third NMOS transistor (104) having source-drain paths connected in shunt to couple a first voltage supply ( $V_{DD}$ ) to the drain of the first NMOS transistor (102) of the differential pair;

a second load comprising a second PMOS transistor (107) and a fourth NMOS transistor (105) having source-drain paths connected in shunt to couple the first voltage supply ( $V_{DD}$ ) to the drain of the second transistor of the differential pair; and

a voltage bias circuit providing bias voltages to the gates of the first PMOS transistor (106) and the third NMOS transistor (104) of the first load, and to the second PMOS transistor (107) and fourth NMOS transistor (105) of the second load.

8. A delay circuit for an oscillator comprising:

a differential pair of transistors (102,103) connected in a common source configuration with gates of first and second transistors of the differential pair forming complementary inputs to the delay circuit, and drains of the first and second transistors of the differential pair forming complementary outputs from the delay circuit;

- 15 -

- a first load comprising third and fourth transistors (104,106) having source-drain paths connected in shunt to couple a first voltage supply ( $V_{DD}$ ) to the drain of the first transistor (102) of the differential pair;

- 5 a second load comprising fifth and sixth transistors (105,107) having source-drain paths connected in shunt to couple the first voltage supply ( $V_{DD}$ ) to the drain of the second transistor (103) of the differential pair; and

- 10 a voltage bias circuit providing bias voltages to the gates of the transistors of the first load and the second load so a voltage swing between the outputs of the delay circuit remain constant when high and low voltage inputs are applied to the inputs of the delay circuit.

- 15

9. A delay circuit for an oscillator comprising:

a differential pair of transistors (102,103)

connected in a common source configuration with gates

20 of first and second transistors of the differential pair forming complementary inputs to the delay circuit,

and drains of the first and second transistors of the differential pair forming complementary outputs from the delay circuit;

- 25 a first load comprising third and fourth transistors (104,106) having source-drain paths connected in shunt to couple a first voltage supply ( $V_{DD}$ ) to the drain of the first transistor (102) of the differential pair;

- 30 a second load comprising fifth and sixth transistors (105,107) having source-drain paths connected in shunt

WO 02/082649

PCT/US02/10889

- 16 -

to couple the first voltage supply ( $V_{DD}$ ) to the drain of the second transistor of the differential pair;

a tail current control transistor (101) having a source-drain path coupling the sources of the pair of

5 differential transistors to a second voltage supply ( $V_{SS}$ ), and having a gate for applying a control voltage

to control a time delay provided by the delay circuit;

and

a voltage bias circuit providing bias voltages to

10 the gates of the transistors of the first load and the second load so the time delay is linearly proportional

to tail current provided from the source to drain of the tail current control transistor.

WO 02/082649

PCT/US02/10889

1/2

FIG. 1

SUBSTITUTE SHEET (RULE 26)

FIG. 2

SUBSTITUTE SHEET (RULE 26)

**【手続補正書】**

【提出日】平成15年5月2日(2003.5.2)

**【手続補正1】**

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

遅延回路に対して相補型入力を形成する差動対の第1及び第2のトランジスタのゲートと、遅延回路の相補型出力を形成する前記差動対の前記第1及び第2のトランジスタのドレインが共通のソース構成において接続されたトランジスタ(102、103)の差動対、第1の電源( $V_{DD}$ )を前記差動対の前記第1のトランジスタ(102)のドレインに結合する並列に接続されたソースドレン路を有する第3及び第4のトランジスタ(104、106)からなる第1の負荷、

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のトランジスタ(103)のドレインに結合する並列に接続されたソースドレン路を有する第5及び第6のトランジスタ(105、107)からなる第2の負荷、及び

基準電圧に接続された第1の入力と、第2の入力と、出力を有する増幅器(130)と、第1の電源( $V_{DD}$ )と増幅器(130)の第2の入力間に結合したソースドレン路を有する第7及び8のトランジスタ(113、114)からなる第3の負荷を含むバイアス回路を含み、前記第3、5及び7のトランジスタのゲートは増幅器(130)の出力に結合することを特徴とする発振器用遅延回路。

**【請求項2】**

第1の電源( $V_{DD}$ )に結合したソースと、前記第4、6及び8のトランジスタのゲートと一緒に結合したドレインとゲートを有する第9のPMOSトランジスタ(122)を更に含むことを特徴とする請求項1に記載の遅延回路。

**【請求項3】**

差動対の第1及び第2のトランジスタ(102、103)の共通のソースに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )に結合したゲートを有する第10のトランジスタ(101)、及び

第9のトランジスタ(122)のドレインに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )と第10のトランジスタ(101)のゲートに結合したゲートを有する第11のトランジスタ(121)を更に含むことを特徴とする請求項2に記載の遅延回路。

**【請求項4】**

増幅器(130)の第2の入力に結合したドレインと、第1の電源( $V_{DD}$ )に結合したゲートと、ソースを有する第12のトランジスタ(112)、及び

第12のトランジスタ(112)のソースに結合したドレインと、第2の電源( $V_{SS}$ )に結合したソースと、遅延制御電圧入力( $V_{CTL}$ )と第10及び11のトランジスタ(101、121)のゲートに結合したゲートを有する第13のトランジスタ(111)を更に含むことを特徴とする請求項3に記載の遅延回路。

**【請求項5】**

遅延回路に対して非反転入力( $V_{IN+}$ )を形成するゲートと、遅延回路の反転出力( $V_{OUT-}$ )を形成するドレインと、ソースを有する第1のNMOStранзистор(102)、及び、遅延回路の反転入力( $V_{IN-}$ )を形成するゲートと、遅延回路の非反転出力( $V_{OUT+}$ )を形成するドレインと、差動対の第1のNMOStранзисторのソースに結合したソースを有する第2のNMOStранзистор(103)からなるトранзисторの差動対、第1の電源( $V_{DD}$ )に結合したドレインと、非反転出力( $V_{OUT+}$ )に結合したソースと、ゲートを有する第3のNMOStранзистор(105)、及び、第1の電源( $V_{DD}$ )に

結合したソースと、非反転出力 ( $V_{OUT+}$ ) に結合したドレインと、ゲートを有する第 1 の PMOS ランジスタ (107) からなる第 1 の負荷、

第 1 の電源 ( $V_{DD}$ ) に結合したドレインと、反転出力 ( $V_{OUT-}$ ) に結合したソースと、第 3 の NMOS ランジスタ (105) のゲートに結合したゲートを有する第 4 の NMOS ランジスタ (104)、及び、第 1 の電源 ( $V_{DD}$ ) に結合したソースと、反転出力 ( $V_{OUT-}$ ) に結合したドレインと、第 1 の PMOS ランジスタ (107) のゲートに結合したゲートを有する第 2 の PMOS ランジスタ (106) からなる第 2 の負荷、

第 1 の NMOS ランジスタ (102) と第 2 の NMOS ランジスタ (103) のソースに結合したドレインと、第 2 の電源 ( $V_{SS}$ ) に接続されたソースと、ゲートを有する第 5 の NMOS ランジスタ (101)、及び

基準電圧に接続された非反転入力と、反転入力と、出力を有する増幅器 (130)、

第 1 の電源 ( $V_{DD}$ ) に結合したドレインと、増幅器 (130) の反転入力に結合したソースと、第 3 の NMOS ランジスタ (105) のゲートに結合したゲートを有する第 6 の NMOS ランジスタ (113)、及び、第 1 の電源 ( $V_{DD}$ ) に結合したソースと、増幅器 (130) の反転入力に結合したドレインと、第 1 の PMOS ランジスタ (107) のゲートに結合したゲートを有する第 3 の PMOS ランジスタ (114) からなる第 3 の負荷、

増幅器 (130) の反転入力に結合したドレインと、第 1 の電源 ( $V_{DD}$ ) に結合したゲートと、ソースを有する第 7 の NMOS ランジスタ (112)、

第 7 の NMOS ランジスタ (112) のソースに結合したドレインと、第 2 の電源 ( $V_{SS}$ ) に結合したソースと、第 5 の NMOS ランジスタ (101) のゲートに結合したゲートを有する第 8 の NMOS ランジスタ (111)、

第 2 の電源 ( $V_{SS}$ ) に結合したソースと、第 5 の NMOS ランジスタ (101) のゲートと遅延回路の遅延制御電圧入力 ( $V_{CTL}$ ) とに結合したゲートと、ドレインを有する第 9 の NMOS ランジスタ (121)、及び

第 1 の電源 ( $V_{DD}$ ) に結合したソースと、第 9 の NMOS ランジスタ (121) のドレインと第 1 の PMOS ランジスタ (107) のゲートとに一緒に結合したドレインとゲートを有する第 4 の PMOS ランジスタ (122) を含むバイアス回路を含むことを特徴とする発振器用遅延回路。

#### 【請求項 6】

第 1、2、3 及び 4 の PMOS ランジスタ (107、106、114、122) の各々の  $W/L$  (幅対長さ) 比を等しくし、第 3、4 及び 6 の NMOS ランジスタ (105、104、113) の各々の  $W/L$  (幅対長さ) 比を等しくし、第 1、2 及び 7 の NMOS ランジスタ (102、103、112) の各々の  $W/L$  (幅対長さ) 比を等しくし、第 5 の NMOS ランジスタ (101) の  $W/L$  (幅対長さ) 比を第 8 及び 9 のランジスタ (111、121) の各々の  $W/L$  (幅対長さ) 比の 2 倍にし、第 3 及び 4 の NMOS ランジスタ (104、105) の  $W/L$  (幅対長さ) 比を第 1 及び 2 の PMOS ランジスタ (107、106) の各々の  $W/L$  (幅対長さ) 比の 1/3 にすることを特徴とする請求項 5 に記載の遅延回路。

#### 【請求項 7】

遅延回路に対して相補型入力を形成する差動対の第 1 及び第 2 の NMOS ランジスタのゲートと、遅延回路の相補型出力を形成する前記差動対の前記第 1 及び第 2 の NMOS ランジスタのドレインが共通のソース構成において接続された NMOS ランジスタ (102、103) の差動対、

第 1 の電源 ( $V_{DD}$ ) を前記差動対の前記第 1 の NMOS ランジスタ (102) のドレインに結合する並列に接続されたソース ドレイン路を有する第 1 の PMOS ランジスタ (106) と第 3 の NMOS ランジスタ (104) からなる第 1 の負荷、

前記第 1 の電源 ( $V_{DD}$ ) を前記差動対の前記第 2 の NMOS ランジスタ (103) のドレインに結合する並列に接続されたソース ドレイン路を有する第 2 の PMOS ランジスタ (107) と第 4 の NMOS ランジスタ (105) からなる第 2 の負荷、及び

前記第1の負荷の前記第1のPMOSトランジスタ(106)と前記第3のNMOSトランジスタ(104)のゲートと、前記第2の負荷の前記第2のPMOSトランジスタ(107)と前記第4のNMOSトランジスタ(105)とにバイアス電圧を提供する電圧バイアス回路を含むことを特徴とする発振器用遅延回路。

【請求項8】

遅延回路に対して相補型入力を形成する差動対の第1及び第2のトランジスタのゲートと、遅延回路からの相補型出力を形成する前記差動対の前記第1及び第2のトランジスタのドレインが共通のソース構成において接続されたトランジスタ(102、103)の差動対、

第1の電源( $V_{DD}$ )を前記差動対の前記第1のトランジスタ(102)のドレインに結合する並列に接続されたソースドレイン路を有する第3及び第4のトランジスタ(104、106)からなる第1の負荷、ここで前記第3のトランジスタ(104)はNMOSデバイスからなり、前記第4のトランジスタ(106)はPMOSデバイスからなる、

前記第1の電源( $V_{DD}$ )を前記差動対の前記第2のトランジスタ(103)のドレインに結合する並列に接続されたソースドレイン路を有する第5及び第6のトランジスタ(105、107)からなる第2の負荷、ここで前記第5のトランジスタ(105)はNMO Sデバイスからなり、前記第6のトランジスタ(107)はPMOSデバイスからなる、差動トランジスタ対のソースを第2の電源( $V_{SS}$ )に結合するソースドレイン路を有し、遅延回路により提供される時間遅延を制御するように制御電圧を印加するゲートを有する末尾電流制御トランジスタ(101)、及び

前記時間遅延が前記末尾電流制御トランジスタ(101)のソースからドレインへ提供される末尾電流に線形比例するように、前記第1の負荷と前記第2の負荷のトランジスタのゲートにバイアス電圧を提供する電圧バイアス回路を含むことを特徴とする発振器用遅延回路。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          | International application No.<br>PCT/US02/10899 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                                 |

| IPC(7): H05K 5/08<br>US CL.: 327/280, 287, 266, 274, 309, 318, 327, 65, 331/57, 108R<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                                 |

| <b>B. FIELDS SEARCHED</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |                                                 |

| Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 327/280, 287, 266, 274, 309, 318, 327, 65, 331/57, 108R                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |                                                 |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |                                                 |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |                                                 |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |                                                 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Citation of document, with indication, where appropriate, of the relevant passages                       | Relevant to claim No.                           |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | US 5,994,939 A (JOHNSON et al.) 30 November 1999 (30.11.1999), Figure 2.                                 | 8, 9                                            |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |                                                 |

| * Special categories of cited documents<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"B" earlier document published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reasons (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                          |                                                 |

| Date of the actual completion of the international search<br>06 JUNE 2002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date of mailing of the international search report<br><b>21 AUG 2002</b>                                 |                                                 |

| Name and mailing address of the ISA/US<br>Commissioner of Patents and Trademarks<br>100 PCT<br>Washington, D.C. 20231<br>Facsimile No. (703) 305-3250                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer <i>Margaret Rose Wambach</i><br>MARGARET ROSE WAMBACH<br>Telephone No. (703) 308 4875 |                                                 |

Form PCT/ISA/210 (second sheet) (July 1998)\*

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN, TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE, GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,P L,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(72)発明者 ハービー、バリー

アメリカ合衆国 カルifornニア州 94025、ロス アルトス、ホルト アベニュー 170

1

(72)発明者 フェアグリープ、アレキサンダー

アメリカ合衆国 カルifornニア州 94025、メンロ パーク、ゴードン アベニュー 21

39

F ターム(参考) 5J001 AA04 BB14 BB25 DD09

5J056 AA00 BB07 BB17 CC02 CC05 CC09 DD13 DD28 DD43 FF07

FF09 HH01 HH02

5J500 AA01 AA12 AC18 AC62 AF10 AH17 AK02 AK09 AK15 AK32

DN22

【要約の続き】

周波数の同調範囲が広くなる。