(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4360736号

(P4360736)

(45) 発行日 平成21年11月11日(2009.11.11)

(24) 登録日 平成21年8月21日(2009.8.21)

(51) Int.CI.

G 11 C 16/02 (2006.01)

F 1

G 11 C 17/00 612 D

G 11 C 17/00 612 E

請求項の数 11 (全 44 頁)

(21) 出願番号 特願2000-97705 (P2000-97705)

(22) 出願日 平成12年3月31日 (2000.3.31)

(65) 公開番号 特開2001-283595 (P2001-283595A)

(43) 公開日 平成13年10月12日 (2001.10.12)

審査請求日 平成18年8月9日 (2006.8.9)

(31) 優先権主張番号 特願2000-18508 (P2000-18508)

(32) 優先日 平成12年1月27日 (2000.1.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 將行

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置および不揮発性半導体記憶装置のデータ消去方法

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配置される不揮発性の複数のメモリトランジスタを含むメモリブロックと、前記メモリトランジスタの行を選択する複数のワード線と、前記メモリトランジスタの列に対応して設けられる複数のビット線と、前記複数のワード線、前記複数のビット線、前記複数のメモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、前記電位発生部の発生する電位を制御し前記メモリブロックのデータ消去を行なう書き消去制御部とを備え、

前記書き消去制御部は、前記メモリブロックが保持する情報を消去する際に、イレース状態のメモリトランジスタとプログラム状態のメモリトランジスタとを両方含み得る状態の前記複数のメモリトランジスタに一括して第1の消去パルスを与えた後に前記複数のメモリトランジスタに一括して書き消去を行ない、さらに前記複数のメモリトランジスタが消去状態になるまで第2の消去パルスを前記複数のメモリトランジスタに一括して繰り返し与え、前記消去状態が確認されると、過消去状態になった前記メモリトランジスタに対して、選択的に書き戻し動作を行なう、不揮発性半導体記憶装置。

10

## 【請求項 2】

前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、前記第1の消去パルスの印加による前記メモリトランジスタのしきい値電圧のシフト量

20

は、前記第2の消去パルスを一括して繰り返し与えることによる前記メモリトランジスタのしきい値電圧のシフト量よりも少ない、請求項1に記載の不揮発性半導体記憶装置。

【請求項3】

前記第1の消去パルスは、前記メモリブロックが保持する情報を一回消去する際に一回与えられる、請求項2に記載の不揮発性半導体記憶装置。

【請求項4】

前記メモリトランジスタはN型であり、

前記書き消去制御部は、前記メモリトランジスタのドレイン・ソース間に電位差を与えて流れる電流を検出することによって前記消去状態を確認する際に、前記メモリトランジスタのサブスレッシュルド電流を小さくする負電位を前記基板部に与える、請求項1に記載の不揮発性半導体記憶装置。

10

【請求項5】

行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、前記メモリトランジスタの行を選択する複数のワード線と、前記メモリトランジスタの列に対応して設けられる複数のビット線と、前記複数のワード線、前記複数のビット線、前記メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、前記電位発生部を制御して前記メモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、

イレース状態のメモリトランジスタとプログラム状態のメモリトランジスタとを両方含み得る状態の前記複数のメモリトランジスタに一括して第1の消去パルスを与えた後に前記複数のメモリトランジスタに一括して書きを行なうステップと、

20

前記複数のメモリトランジスタが消去状態になるまで第2の消去パルスを前記複数のメモリトランジスタに一括して繰り返し与えるステップと、

前記消去状態が確認されると、過消去状態になった前記メモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備える、不揮発性半導体記憶装置のデータ消去方法。

【請求項6】

前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、

前記第1の消去パルスの印加による前記メモリトランジスタのしきい値電圧のシフト量は、前記第2の消去パルスを一括して繰り返し与えることによる前記メモリトランジスタのしきい値電圧のシフト量よりも少ない、請求項5に記載の不揮発性半導体記憶装置のデータ消去方法。

30

【請求項7】

行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、前記メモリトランジスタの行を選択する複数のワード線と、前記メモリトランジスタの列に対応して設けられる複数のビット線と、前記複数のワード線、前記複数のビット線、前記メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、前記電位発生部を制御して前記メモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、

40

前記複数のメモリトランジスタに対して一括して第1の消去パルスを与える動作を前記複数のメモリトランジスタが消去状態になるまで繰り返すステップと、

前記複数のメモリトランジスタに対して、一括して第1の書きパルスを与えた後に一括して第2の消去パルスを与えるステップと、

過消去状態になった前記メモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備え、

前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、

前記第2の消去パルスの印加による前記メモリトランジスタのしきい値電圧のシフト量は、最後に与えられた前記第1の消去パルスの印加による前記メモリトランジスタのしき

50

い値電圧のシフト量以下である、不揮発性半導体記憶装置のデータ消去方法。

**【請求項 8】**

行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、前記メモリトランジスタの行を選択する複数のワード線と、前記メモリトランジスタの列に対応して設けられる複数のビット線と、前記複数のワード線、前記複数のビット線、前記メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、前記電位発生部を制御して前記メモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、

一括して前記複数のメモリトランジスタに対して第1の消去パルスを与える動作を前記複数のメモリトランジスタが第1の消去状態になるまで繰り返すステップと、

前記第1の消去状態にある前記複数のメモリトランジスタに対して一括して書きパルスを与えるステップと、

前記書き込みパルスが印加された後に、一括して前記複数のメモリトランジスタに対して第2の消去パルスを与える動作を前記複数のメモリトランジスタが第2の消去状態になるまで繰り返すステップと、

前記第2の消去状態が確認されると、過消去状態になった前記メモリトランジスタに対して、選択的に書き戻し動作を行なうステップと、

第1の消去パルスを与える動作を繰り返すステップに先立って、前記複数のメモリトランジスタに対して一括して消去前の予備書き込みを行なう予備書き込みパルスを与えるステップとを備え、

前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、

前記書き込みパルスの印加による前記メモリトランジスタのしきい値電圧のシフト量は、前記予備書き込みパルスの印加による前記メモリトランジスタのしきい値電圧のシフト量よりも小さく、

前記第1の消去状態は、前記メモリトランジスタのしきい値電圧が第1の値以下となる状態であり、

前記第2の消去状態は、前記メモリトランジスタのしきい値電圧が前記第1の値より小さい第2の値以下となる状態であり、

最初に与えられた前記第2の消去パルスの印加による前記メモリトランジスタのしきい値電圧のシフト量は、最後に与えられた前記第1の消去パルスの印加による前記メモリトランジスタのしきい値電圧のシフト量以下である、不揮発性半導体記憶装置のデータ消去方法。

**【請求項 9】**

前記第1の消去パルスは、前記複数のメモリトランジスタが第1の消去状態になるまでに、段階的に強度が強められる、請求項8に記載の不揮発性半導体記憶装置のデータ消去方法。

**【請求項 10】**

前記第2の消去パルスは、前記複数のメモリトランジスタが第2の消去状態になるまでに、段階的に強度が強められる、請求項9に記載の不揮発性半導体記憶装置のデータ消去方法。

**【請求項 11】**

行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、前記メモリトランジスタの行を選択する複数のワード線と、前記メモリトランジスタの列に対応して設けられる複数のビット線と、前記複数のワード線、前記複数のビット線、前記メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、前記電位発生部を制御して前記メモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、

前記複数のメモリトランジスタに対して一括して第1の消去パルスを与える動作を前記複数のメモリトランジスタが第1の消去状態になるまで繰り返すステップと、

10

20

30

40

50

前記第1の消去状態にある前記複数のメモリトランジスタに対して、一括して書込パルスを与えた後に一括して第2の消去パルスを与える動作を第2の消去状態になるまで繰返すステップと、

前記第2の消去状態が確認されると、過消去状態になった前記メモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備え、

前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり

前記第1の消去状態は、前記メモリトランジスタのしきい値電圧が第1の値以下となる状態であり、

前記第2の消去状態は、前記メモリトランジスタのしきい値電圧が前記第1の値より小さい第2の値以下となる状態である、不揮発性半導体記憶装置のデータ消去方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、不揮発性半導体記憶装置に関し、より特定的には、フラッシュ型の不揮発性半導体記憶装置に関する。

【0002】

【従来の技術】

フラッシュ型の不揮発性半導体記憶装置すなわち、フラッシュメモリは、機能的には、一括消去型の電気的に書込消去が可能な不揮発性半導体記憶装置であるが、その低コスト性、電気的消去機能を有することから携帯機器等に大きな需要があり、近年最も盛んに研究開発が行なわれている不揮発性半導体記憶装置である。フラッシュメモリは、メモリセルとして、フローティングゲートを有し、しきい値電圧を変化させることができるトランジスタ（以下、メモリトランジスタと称する）を使用する。

【0003】

現在、フラッシュメモリの主流となっているのはNOR型のフラッシュメモリである。NOR型のフラッシュメモリは、たとえばDINOR型などと比べると、チャネルホットエレクトロンで書込を行なうため、書込速度が速いという利点がある。

【0004】

NOR型のフラッシュメモリは、消去時には、メモリトランジスタのしきい値電圧を高から低に変化させる。一方、DINOR型は、消去時にはメモリトランジスタのしきい値電圧を低から高へ変化させる。したがって、DINOR型のフラッシュメモリは、消去時にはメモリトランジスタがしきい値電圧が低くなり過ぎることによるデプレッション型トランジスタになることはなく、消去速度が速いという利点がある。

【0005】

NOR型のフラッシュメモリの中でも現在主流となっているのは、消去時にフローティングゲートの電子をソース領域に引き抜くエッジ引抜き型のフラッシュメモリであるが、本発明では例としてチャネル全面に電子を引抜いて消去を行なうNOR型のフラッシュメモリの場合の印加電圧を示している。かかるチャネル全面引抜き型消去のNOR型フラッシュメモリは、従来のエッジ引抜き型のフラッシュメモリに比べセルサイズをスケーリングできる、つまり比例縮小できるという利点がある。

【0006】

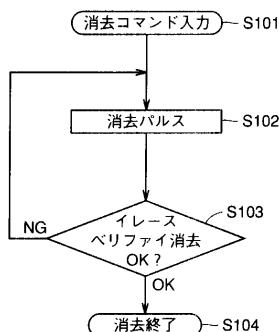

図47は、従来のフラッシュメモリの最もシンプルな消去シーケンスの例を示したフローチャートである。

【0007】

図47を参照して、ステップS101において消去コマンドが入力されると、続くステップS102において所定のパルス幅を有する消去パルスがメモリトランジスタに印加される。

【0008】

そして、その後ステップS103において消去されたかどうかを判定するイレースベリフ

10

20

30

40

50

アイ機能による判定が行なわれる。

【0009】

ステップS103においてメモリセルの保持情報が消去されていないと判断された場合には、ステップS102に戻り、メモリトランジスタのしきい値電圧が消去判定電圧以下となるまでステップS102、S103を繰返し通ることにより消去パルスの印加とイレースベリファイを繰返し行なう。

【0010】

ステップS103においてメモリトランジスタのしきい値電圧が消去判定電圧以下になつたときにはステップS104に進み消去動作が終了する。

【0011】

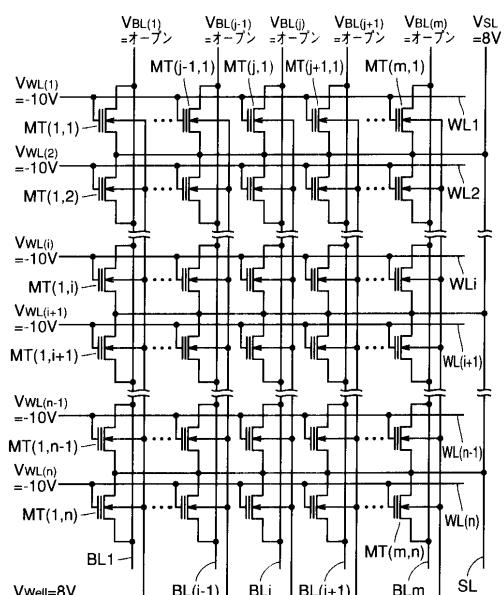

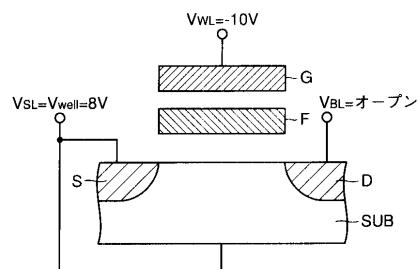

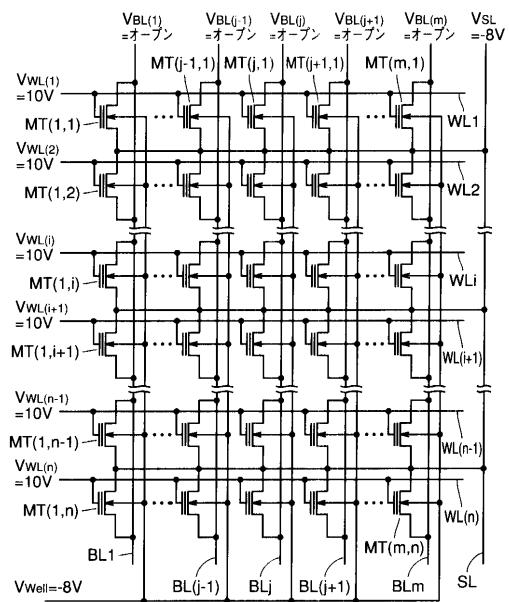

図48は、図47におけるステップS102で行なわれる消去パルスを与えていた時の印加電圧を説明するためのメモリブロックの回路図である。

【0012】

図48を参照して、このメモリブロックには、n行m列に配置された各々がフローティングゲートを有するメモリトランジスタが示されている。消去パルスを印加するときには、ソース線電位 $V_{SL}$ およびウェル電位 $V_{well}$ はともに8Vに設定される。そして、各行のメモリトランジスタを活性化するワード線はすべて-10Vに設定される。また、各列のメモリトランジスタからデータを読出すためのビット線 $BL_1 \sim BL_m$ はすべて開放状態に設定される。

【0013】

図49は、消去パルスが印加されている場合のメモリトランジスタに印加されている電圧を説明するための図である。

【0014】

図49を参照して、メモリトランジスタのソースに与えられるソース線電位 $V_{SL}$ およびメモリトランジスタの基板部に与えられるウェル電位 $V_{well}$ はともに8Vに設定される。メモリトランジスタを選択するためのワード線に印加されるワード線電位 $V_{WL}$ は-10Vに設定される。メモリトランジスタのドレインはこのときは開放状態にされている。ゲートとソース間だけでなく、ゲートと基板間にも高電界が印加されているので、メモリトランジスタのチャネル全面に電子が引抜かれ、消去が行なわれる。

【0015】

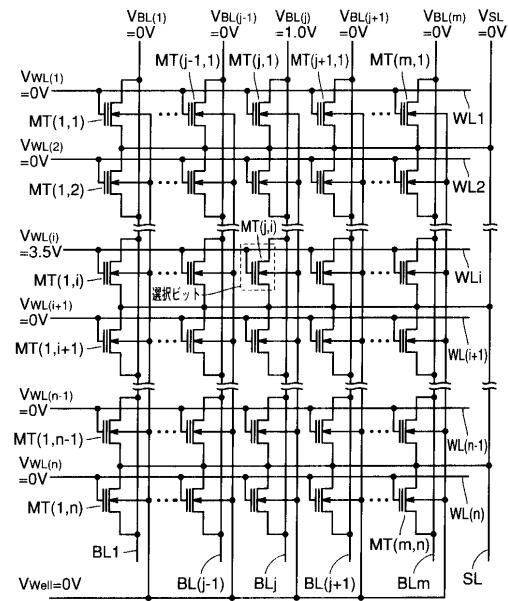

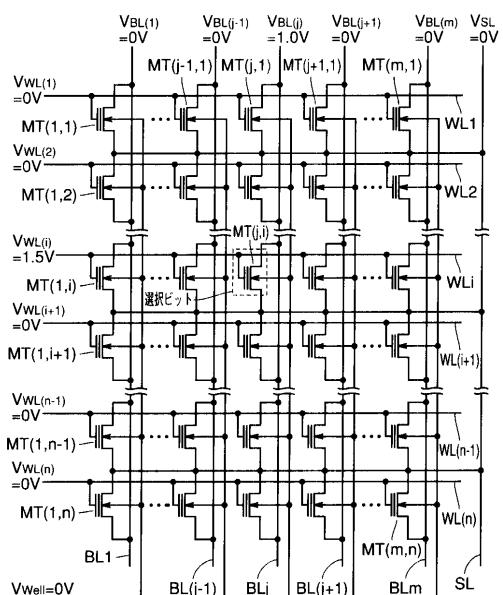

図50は、図47に示したシーケンスにおいてステップS103で行なわれるイレースベリファイの場合に印加される電圧を説明するための回路図である。

【0016】

図50を参照して、ウェル電位 $V_{well}$ およびソース線電位 $V_{SL}$ はともに0Vに設定される。選択ビットに対応するメモリトランジスタを選択するワード線 $WL_i$ は3.5Vに設定され、他のワード線はすべて0Vに設定される。選択ビットに対応するメモリトランジスタに接続されたビット線 $BL_j$ は1.0Vに設定され、他のビット線はすべて0Vに設定される。このような電位に設定し、メモリトランジスタに流れる電流を確認することにより、メモリトランジスタ $MT(i, j)$ の消去が行なわれたか否かが確認される。

【0017】

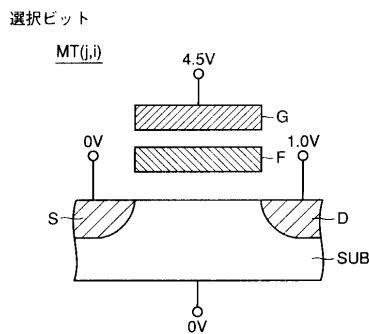

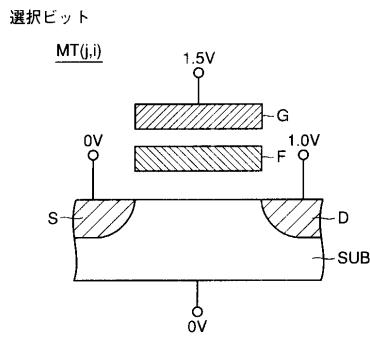

図51は、図50の選択ビットに対応したメモリトランジスタに印加される電圧を示した図である。

【0018】

図51を参照して、選択されたメモリトランジスタ $MT(j, i)$ のソースおよびウェルはともに0Vに設定される。メモリトランジスタのゲートには3.5Vが与えられドレインには1.0Vが与えられる。

【0019】

次に、従来のフラッシュメモリにおけるリード時の電圧設定を説明しておく。

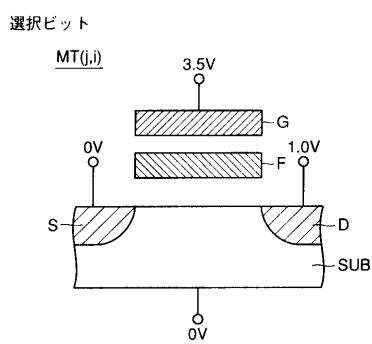

図52は、従来のフラッシュメモリのリード時の電圧設定を説明するための回路図である。

10

20

30

40

50

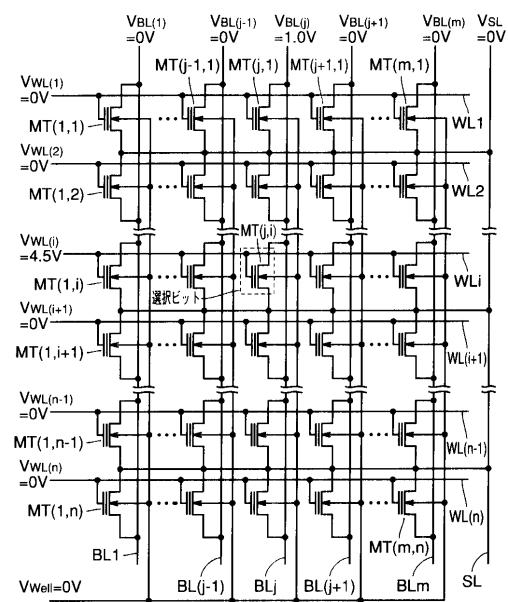

## 【0020】

図52を参照して、選択ビットに対応するメモリトランジスタのゲートに接続されるワード線 $WL_i$ は4.5Vに設定され、他にワード線はすべて0Vに設定される。このとき、ソース線電位 $V_{SL}$ およびウェル電位 $V_{well}$ はともに0Vに設定されている。

## 【0021】

図53は、図52に示したリード時の選択されたメモリトランジスタに与えられる電位を示した図である。

## 【0022】

図53を参照して、選択ビットに相当するメモリトランジスタのソースおよびウェルはともに0Vに設定されている。そしてドレインには1.0Vが与えられゲートには4.5Vが与えられる。このときに、メモリトランジスタのしきい値電圧が高いとドレインからソースへは電流が流れず、逆にメモリトランジスタのしきい値電圧が低い場合には、ドレインからソースに電流が流れる。この電流を検出することによりメモリトランジスタにデータが書かれているか否かが判別できる。

10

## 【0023】

## 【発明が解決しようとする課題】

図47に示した従来のフラッシュメモリの消去シーケンスを使用すると、メモリトランジスタの一部が過消去状態となってしまうという問題が生じる。以降この過消去状態について説明する。

## 【0024】

20

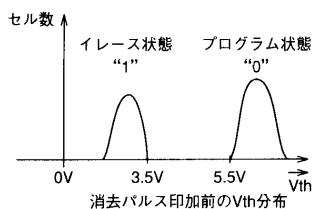

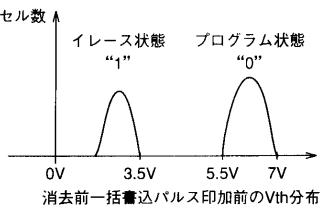

図54は、消去パルス印加前のしきい値電圧の分布を示す図である。

図54を参照して、図47のステップS101において消去コマンドが入力される直前の状態、つまり消去時における初期状態では、プログラム状態すなわちメモリトランジスタに“0”が記憶されている状態とイレース状態すなわちメモリトランジスタに“1”が記憶されている状態とが存在する。図の縦軸は、メモリブロックにおいて各しきい値電圧を保持しているメモリトランジスタの数を示している。

## 【0025】

なお、NOR型フラッシュメモリでは、しきい値電圧が高い状態にある場合がプログラム状態、すなわち、“0”を保持している状態に対応している。一方、しきい値電圧が低い状態がイレース状態、すなわち、“1”を保持している状態に対応している。

30

## 【0026】

図54で示した状態は、それまでのシーケンスによりメモリブロックにデータが記憶されている状態であり、その記憶状態に応じてプログラム状態、イレース状態のメモリトランジスタ数が定まっている。また、プログラム状態のメモリトランジスタは、しきい値電圧が5.5V以上に分布しており、イレース状態のメモリトランジスタはしきい値電圧が3.5V以下に分布している。

## 【0027】

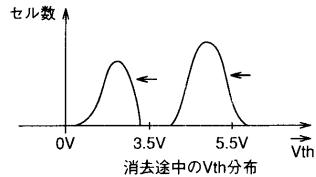

図55は、図47の消去シーケンスにおいて消去パルスが印加されても、完全に全ビットのデータが消去されていない不完全な消去状態を示した図である。

## 【0028】

40

図47、図55を参照して、ステップS102では、所定の幅の消去パルスをメモリブロック内のメモリトランジスタに一括して与えることにより、FN(ファウラーノルドハイム)トンネル電流を用いてメモリブロック単位で消去が行なわれる。したがって、図54で示したように1ブロックの中にイレース状態のメモリトランジスタとプログラム状態のメモリトランジスタがある場合に、ブロック単位で消去パルスが印加されると、イレース状態のメモリセルもプログラム状態のメモリセルとともに図54においてしきい値電圧が低くなる方にシフトしていく。

## 【0029】

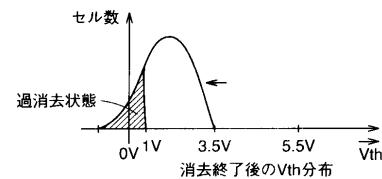

図56は、図47のステップS103においてイレースベリファイが完了した場合のしきい値電圧の分布を示した図である。

50

## 【0030】

図56を参照して、イレースペリファイが完了すると、メモリブロック中のメモリトランジスタのしきい値電圧は、すべて3.5V以下になっている。しかし、メモリブロックにおける各メモリトランジスタのしきい値電圧は、この場合にはかなりばらつきが生じていることがわかる。すなわち、図56において、しきい値電圧の分布幅が広くなってしまっている。

## 【0031】

その結果、しきい値電圧が1V以下であるメモリセル、つまり、過消去状態にあるメモリトランジスタが存在することが斜線部に示されている。過消去状態では、メモリトランジスタは、ゲート電圧が0Vであってもドレイン電流が流れるデプレッション型トランジスタとなってしまう場合がある。

10

## 【0032】

このばらつきは、図54においてイレース状態にあるメモリトランジスタのしきい値電圧のばらつきおよびプログラム状態にあるメモリトランジスタのしきい値電圧のばらつきにも起因するが、イレース状態にあるメモリトランジスタとプログラム状態にあるメモリトランジスタに同じ消去パルスを印加することによって、さらに、ばらつきが増大する。

## 【0033】

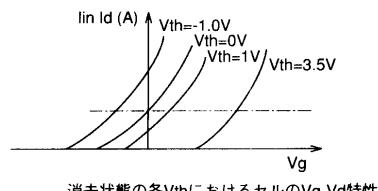

図57は、消去状態の各しきい値電圧を有するメモリトランジスタのゲート電圧とドレイン電流の特性を表わした図である。

20

## 【0034】

図57を参照して、しきい値電圧が1.5Vおよび3.5Vの場合、ゲート電圧 $V_g$ が0Vのときには、ドレイン電流は判定値よりも小さい。しかし、しきい値電圧が0Vの場合には、ゲート電圧 $V_g$ が0Vの場合にも、メモリトランジスタに所定の判定値に等しい電流が流れてしまう。さらに、しきい値電圧が-1.0Vのメモリトランジスタでは、ゲート電圧をかなり負電位に設定しないとドレイン電流が流れてしまう状態が起こっている。

## 【0035】

このような過消去のメモリトランジスタと正常な消去状態のメモリトランジスタを比較すると、過消去状態のメモリトランジスタがデプレッショントランジスタとなってゲート電圧が0Vの場合つまり、メモリトランジスタが非選択状態にある場合にもリーク電流が多く流れることがわかる。

30

## 【0036】

このような過消去状態のメモリトランジスタが存在すると、図51、図53で示した電圧でベリファイおよびリードを行なうときに同一ビット線上に非選択の過消去状態のメモリトランジスタによるリーク電流が多く流れてしまい、このリーク電流の総和で選択されたメモリトランジスタの電流値がわからなくなってしまう。つまり、読出不能になってしまふ。そのため、正確なベリファイおよびリードができなくなってしまうという問題点があった。

## 【0037】

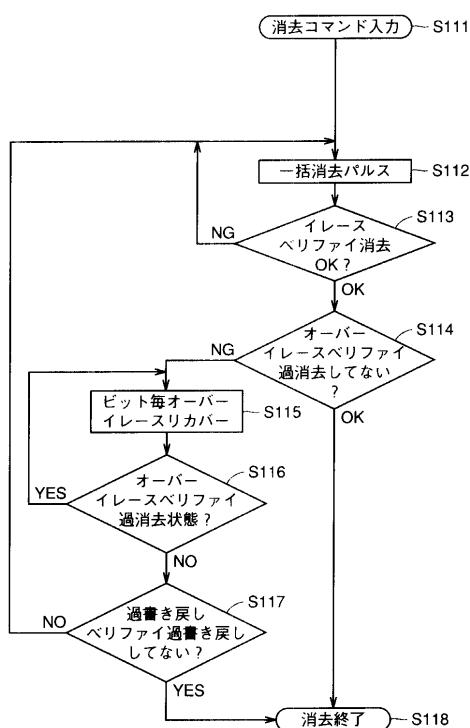

図58は、図47で示した消去シーケンスの過消去の問題に対する対策を施したフローを示したフローチャートである。

40

## 【0038】

図58を参照して、ステップS111で消去コマンドが入力されると、ステップS112でメモリブロックに一括して消去パルスが印加されFNトンネル電流によるしきい値電圧の変更が行なわれる。続いて、ステップS113でイレースペリファイが実行される。すべてのメモリセルのイレースが確認されるまでステップS113とS112とが繰返される。ステップS113ですべてのメモリセルのイレースが確認されるとステップS114に進む。

## 【0039】

ステップS114ではメモリトランジスタが過消去状態になっていないかを確認するオーバイレースペリファイが行なわれる。すなわち、消去ベリファイが完了した後に、しきい

50

値電圧がある値（たとえば1.5V）以下になっているメモリトランジスタを検出する。過消去状態にあるメモリトランジスタを検出するとステップS115に進み、ビットごとのオーバイレースリカバーが行なわれる。オーバイレースリカバーとは、ビットごとにチャネルホットエレクトロン（CHE）を用いてデータを書き戻す機能、つまり、メモリトランジスタ毎にしきい値電圧を正方向に大きくする機能である。そしてステップS116に進み、再び過消去状態にあるメモリトランジスタがあるかどうかが判定される。

【0040】

次に過消去状態のメモリトランジスタが存在しないことが確認されたらステップS117に進む。ステップS117では、ステップS115において行なわれたオーバイレースリカバー機能により過剰に書き戻された「過書き戻し」の可能性があるため再び過書き戻しペリファイが行なわれる。過書き戻しが検出されると、再びステップS112に進む。一方過書き戻しのメモリトランジスタが存在しない場合にはステップS118に進み消去が終了する。

10

【0041】

図59は、図58のステップS114において実行されたオーバイレースペリファイ時にメモリブロックに与えられる電圧を説明するための回路図である。

【0042】

図59を参照して、オーバイレースペリファイ時には、選択ビットに対応するメモリトランジスタを選択するためのワード線WL<sub>i</sub>には1.5Vが与えられ、他のワード線には0Vが与えられる。一方、選択ビットに対応するメモリトランジスタのドレインに接続されるビット線BL<sub>j</sub>には1.0Vが与えられ、他のビット線には0Vが与えられる。ソース線電位V<sub>SL</sub>およびウェル電位V<sub>well</sub>は0Vに設定されている。

20

【0043】

図60は、オーバイレースペリファイ時における選択ビットに対応するメモリトランジスタに与えられる電圧を示した図である。

【0044】

図60を参照して、選択ビットのメモリトランジスタは、そのソースおよび基板部には0Vが与えられる。そしてゲートには1.5Vが与えられ、ドレインには1.0Vが与えられる。

【0045】

30

このように、読み出時よりもやや低い電圧をゲートに与えてソースドレイン間に電流が流れるか否かを検出することにより過消去状態にあるメモリトランジスタを検出することができる。

【0046】

図61は、図58のステップS115に示したビット毎オーバイレースリカバー時におけるメモリブロックに与える電圧を示した回路図である。

【0047】

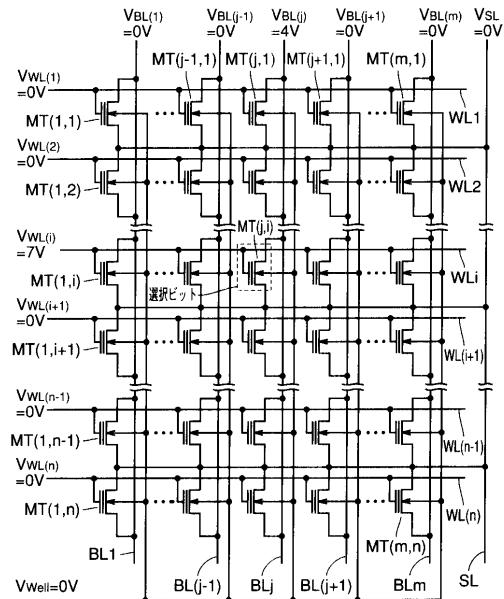

図61を参照して、ビット毎オーバイレースリカバー時には、選択ビットに対応するメモリトランジスタを選択するワード線WL<sub>i</sub>には7Vが与えられ、他のワード線には0Vが与えられる。一方、選択ビットに対応するメモリトランジスタのドレインに接続されるビット線BL<sub>j</sub>には4Vが与えられ、他のビット線は0Vに設定される。ソース線電位V<sub>SL</sub>およびウェル電位V<sub>well</sub>はともに0Vに設定される。

40

【0048】

ゲート電圧を通常読み出し時（たとえば4.5V）より高く設定すれば、しきい値電圧が通常の“0”状態にあるメモリトランジスタにもドレイン電流が流れる。このような電圧を選択ビットに対応するメモリトランジスタに与えた場合に電流が流れることを検出することで、過消去状態になったメモリトランジスタを検出することができる。

【0049】

以上、図58で示した消去シーケンスの場合には、過消去のメモリトランジスタに対しては書き戻しを行なうため、正確なペリファイおよびリードはできるが、その代わり、ビッ

50

トごとに行なうオーバイレースリカバー動作およびそのペリファイに時間を要するため、合計の消去時間が長くなってしまうという問題点があった。

【0050】

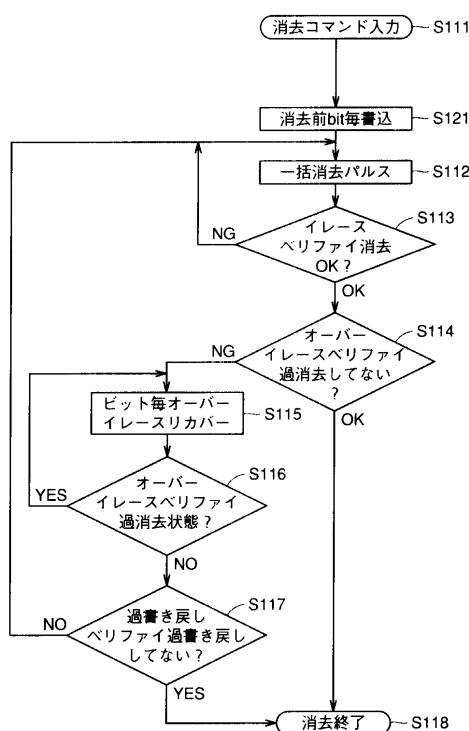

図62は、図58の消去シーケンスの消去時間をさらに短縮する消去シーケンスを説明するためのフローチャートである。

【0051】

図62を参照して、ステップS111において消去コマンドが入力されると、次にステップS121に進みチャネルホットエレクトロンを用いた消去前のビット毎書きを行なう。この消去前ビット毎書きは、図54で示したようなイレース状態にあるビットを最初に書き状態にして消去パルスが印加される前のしきい値電圧を揃えておくためのものであり、チャネルホットエレクトロンを用いてしきい値電圧の変更が行なわれる。これにより、消去ペリファイが完了した後にしきい値電圧の分布幅が狭くなり、オーバイレースリカバーの対象となるメモリトランジスタの数が少なくなる。したがって、合計の消去時間が短くなる。ステップS112～S118は、図58で示した場合と同様な動作であるので説明は繰返さない。

【0052】

しかしながら、図62で示した消去前ビット毎書きを行なう消去シーケンスの場合でも、消去前ビット毎書きにかかる時間が多く、それほどトータルの消去時間は短くならないという問題点があった。

【0053】

図63は、図62に示した消去シーケンスの消去時間のさらなる短縮を図ったフローチャートである。

【0054】

図63を参照して、この消去シーケンスには、図62に示したフローチャートのステップS121に代えてステップS131が設けられる。ステップS131では、消去パルスを与える前にメモリブロック単位で消去前の一括書きが実施される。

【0055】

このようにすれば、図62に示したようなビットごとの書きを行なわないため消去時間を短縮することができる。

【0056】

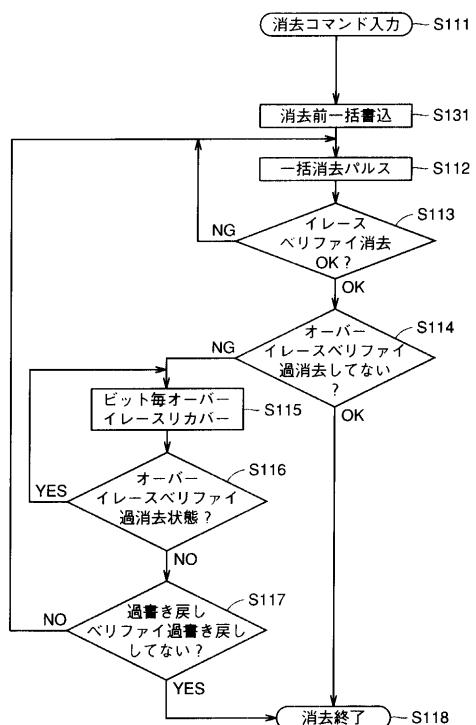

図64は、図63のステップS131における消去前一括書きを行なう場合のメモリブロックに与える電圧を説明するための回路図である。

【0057】

図64を参照して、ソース線電位V<sub>SL</sub>およびウェル電位V<sub>well</sub>はともに-8Vに設定される。ワード線W<sub>L</sub>1～W<sub>L</sub>nはすべて+10Vに設定される。またビット線B<sub>L</sub>1～B<sub>L</sub>mはすべて開放状態とされる。

【0058】

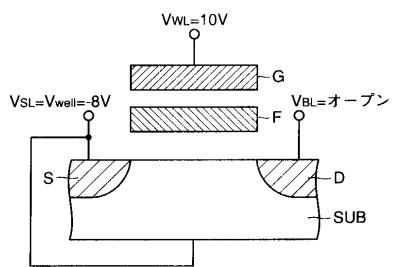

図65は、図64に示した消去前一括書き時にメモリトランジスタに印加される電圧を説明するための図である。

【0059】

図65を参照して、メモリトランジスタのソースおよびウェルには-8Vが与えられ、ゲートには+10Vが与えられる。またドレインは開放状態にされる。このように設定すれば、トランジスタのチャネル部とゲートとの間に高電界がかかるため、チャネル部からフローティングゲートに対して電子が注入され、しきい値電圧が大きくなり、メモリブロックのメモリトランジスタに一括して書きが行なわれることになる。

【0060】

図66は、図63の消去シーケンスにおいてステップS131の消去前一括書きを行なう前のしきい値電圧の分布を示した図である。

【0061】

図66を参照して、“1”を記憶しているメモリトランジスタはしきい値が3.5V以下

10

20

30

40

50

になっている。一方、“0”を記憶しているメモリトランジスタはしきい値電圧が5.5V～7Vの間に分布している。

【0062】

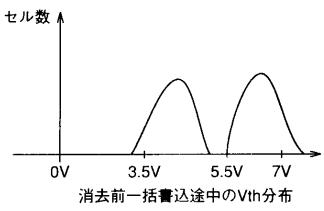

図67は、消去前一括書き込みをしている途中のメモリトランジスタのしきい値電圧の分布を示した図である。

【0063】

図67を参照して、消去前一括書き込みが実施されると、図66に示した“1”を保持しているメモリトランジスタのしきい値と“0”を保持しているメモリトランジスタのしきい値はともに大きくなる方向にシフトする。

【0064】

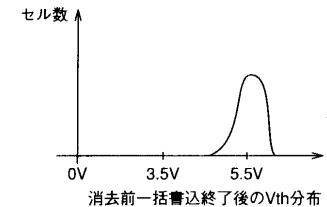

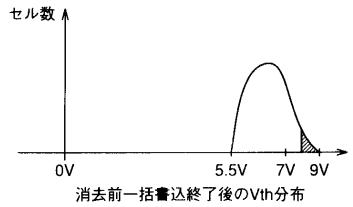

図68は、消去前一括書き込みが終了した後のしきい値電圧の分布を示した図である。

【0065】

すべてのメモリトランジスタのしきい値電圧が5.5V以上になったときには、しきい値電圧のばらつきにより、しきい値電圧が9V程度に高くなってしまっているメモリトランジスタも存在していることがわかる。このようなしきい値電圧が高くなってしまったメモリトランジスタは、メモリセルのトンネル酸化膜に非常に高電界がかかるため、信頼性を劣化させてしまうという問題点があった。

【0066】

本発明は、これらの従来のフラッシュメモリの消去シーケンスの問題点を解決するためになされた発明であって、トータルの消去時間の短縮および高信頼性の確保を実現することができる不揮発性半導体記憶装置を提供することを目的とする。

【0067】

【課題を解決するための手段】

この発明のある局面における不揮発性半導体記憶装置は、行列状に配置される不揮発性の複数のメモリトランジスタを含むメモリブロックと、メモリトランジスタの行を選択する複数のワード線と、メモリトランジスタの列に対応して設けられる複数のビット線と、複数のワード線、複数のビット線、複数のメモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、電位発生部の発生する電位を制御しメモリブロックのデータ消去を行なう書き込み消去制御部とを備え、書き込み消去制御部は、メモリブロックが保持する情報を消去する際に、イレース状態のメモリトランジスタとプログラム状態のメモリトランジスタとを両方含み得る状態の複数のメモリトランジスタに一括して第1の消去パルスを与えた後に複数のメモリトランジスタに一括して書き込みを行ない、さらに複数のメモリトランジスタが消去状態になるまで第2の消去パルスを複数のメモリトランジスタに一括して繰り返し与え、消去状態が確認されると、過消去状態になったメモリトランジスタに対して、選択的に書き戻し動作を行なう。

【0068】

好ましくは、メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、第1の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量は、第2の消去パルスを一括して繰り返し与えることによるメモリトランジスタのしきい値電圧のシフト量よりも少ない。

【0069】

より好ましくは、第1の消去パルスは、メモリブロックが保持する情報を一回消去する際に一回与えられる。

【0070】

好ましくは、メモリトランジスタはN型であり、書き込み消去制御部は、メモリトランジスタのドレイン-ソース間に電位差を与えて流れる電流を検出することによって消去状態を確認する際に、メモリトランジスタのサブスレッショルド電流を小さくする負電位を基板部に与える。

【0074】

この発明の他の局面における不揮発性半導体記憶装置のデータ消去方法は、行列状に配

10

20

30

40

50

置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、メモリトランジスタの行を選択する複数のワード線と、メモリトランジスタの列に対応して設けられる複数のビット線と、複数のワード線、複数のビット線、メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、電位発生部を制御してメモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、イレース状態のメモリトランジスタとプログラム状態のメモリトランジスタとを両方含み得る状態の複数のメモリトランジスタに一括して第1の消去パルスを与えた後に複数のメモリトランジスタに一括して書き消去制御部と、複数のメモリトランジスタが消去状態になるまで第2の消去パルスを複数のメモリトランジスタに一括して繰り返し与えるステップと、消去状態が確認されると、過消去状態になったメモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備える。

10

#### 【0075】

好ましくは、メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、第1の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量は、第2の消去パルスを一括して繰り返し与えることによるメモリトランジスタのしきい値電圧のシフト量よりも少ない。

#### 【0081】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、メモリトランジスタの行を選択する複数のワード線と、メモリトランジスタの列に対応して設けられる複数のビット線と、複数のワード線、複数のビット線、メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、電位発生部を制御してメモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、複数のメモリトランジスタに対して一括して第1の消去パルスを与える動作を複数のメモリトランジスタが消去状態になるまで繰り返すステップと、複数のメモリトランジスタに対して、一括して第1の書き消去パルスを与えた後に一括して第2の消去パルスを与えるステップと、過消去状態になったメモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備える。メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、第2の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量は、最後に与えられた第1の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量以下である。

20

#### 【0083】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、メモリトランジスタの行を選択する複数のワード線と、メモリトランジスタの列に対応して設けられる複数のビット線と、複数のワード線、複数のビット線、メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、電位発生部を制御してメモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、一括して複数のメモリトランジスタに対して第1の消去パルスを与える動作を複数のメモリトランジスタが第1の消去状態になるまで繰り返すステップと、第1の消去状態にある複数のメモリトランジスタに対して一括して書き消去パルスを与えるステップと、書き消去パルスが印加された後に、一括して複数のメモリトランジスタに対して第2の消去パルスを与える動作を複数のメモリトランジスタが第2の消去状態になるまで繰り返すステップと、第2の消去状態が確認されると、過消去状態になったメモリトランジスタに対して、選択的に書き戻し動作を行なうステップと、第1の消去パルスを与える動作を繰り返すステップに先立って、複数のメモリトランジスタに対して一括して消去前の予備書き込みを行なう予備書き込みパルスを与えるステップとを備え、前記メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、書き消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量は、予備書き込みパルスの印加によるメモリトランジスタのしきい値電圧のシフト量よりも小さく、第1の消去状態は、メモリトランジスタ

30

40

50

のしきい値電圧が第1の値以下となる状態であり、第2の消去状態は、メモリトランジスタのしきい値電圧が第1の値より小さい第2の値以下となる状態であり、最初に与えられた第2の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量は、最後に与えられた第1の消去パルスの印加によるメモリトランジスタのしきい値電圧のシフト量以下である。

【0087】

好ましくは、第1の消去パルスは、複数のメモリトランジスタが第1の消去状態になるまでに、段階的に強度が強められる。

【0088】

より好ましくは、第2の消去パルスは、複数のメモリトランジスタが第2の消去状態になるまでに、段階的に強度が強められる。

【0090】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、行列状に配置された不揮発性の複数のメモリトランジスタを含むメモリブロックと、メモリトランジスタの行を選択する複数のワード線と、メモリトランジスタの列に対応して設けられる複数のビット線と、複数のワード線、複数のビット線、メモリトランジスタの基板部およびソースに与える電位を発生する電位発生部と、電位発生部を制御してメモリブロックのデータ消去を行なう書き消去制御部とを備える不揮発性半導体記憶装置のデータ消去方法であって、複数のメモリトランジスタに対して一括して第1の消去パルスを与える動作を複数のメモリトランジスタが第1の消去状態になるまで繰り返すステップと、第1の消去状態にある複数のメモリトランジスタに対して、一括して書き消去パルスを与えた後に一括して第2の消去パルスを与える動作を第2の消去状態になるまで繰り返すステップと、第2の消去状態が確認されると、過消去状態になったメモリトランジスタに対して、選択的に書き戻し動作を行なうステップとを備え、メモリトランジスタは、フローティングゲートを有するMOSトランジスタであり、第1の消去状態は、メモリトランジスタのしきい値電圧が第1の値以下となる状態であり、第2の消去状態は、メモリトランジスタのしきい値電圧が第1の値より小さい第2の値以下となる状態である。

【0097】

【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳しく説明する。なお、図中同一符号は同一または相当部分を示す。

【0098】

[実施の形態1]

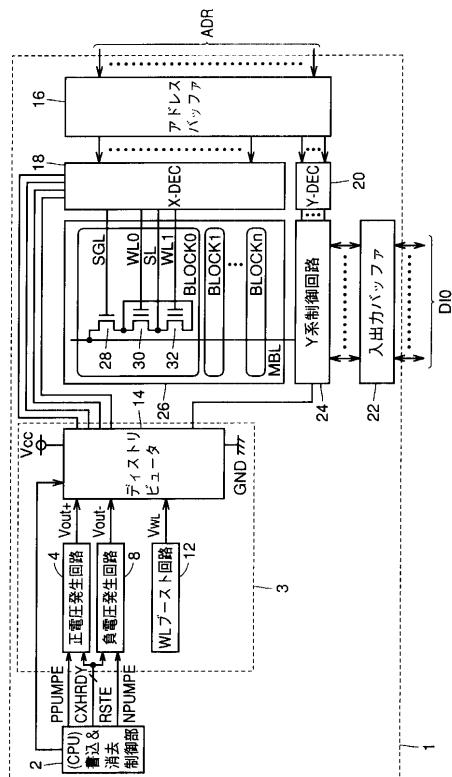

図1は、本発明の不揮発性半導体記憶装置1の概略構成を示すブロック図である。

【0099】

図1を参照して、不揮発性半導体記憶装置1は、内部にROMを用い、このROMに保持しているプログラムコードに基づき書き消去の制御を行なう書き&消去制御部2と、書き&消去制御部2からスタンバイ信号CXHRDYおよびチャージポンプ活性化信号PPUMPE、リセット信号RSTEを受けてこれらに応じて出力電位Vout+、Vout-、VWLを発生して出力する電圧発生部3と、外部からアドレス信号ADRを受けるアドレスバッファ16と、アドレスバッファ16から内部アドレス信号を受け電圧発生部3から電位の供給を受けセレクトゲート線SGL、ワード線WL0, WL1, ソース線SLおよびウェルの各電位を決定するXデコーダ18と、データ入出力信号DIOを授受するための入出力バッファ22と、アドレスバッファ16からアドレス信号を受けデコードするYデコーダ20と、Yデコーダ20の出力に応じてデータ入出力信号に対応しメインビット線MBLに高電圧を印加するY系制御回路24とを含む。

【0100】

電圧発生部3は、書き&消去制御部2からスタンバイ信号CXHRDYおよびチャージポンプ活性化信号PPUMPE、リセット信号RSTEを受けてこれらに応じて出力電位Vout+を発生させる正電圧発生回路4と、スタンバイ信号CXHRDY、リセット信号

10

20

30

40

50

R S T E およびチャージポンプ活性化信号N P U M P E を受けて出力電位V o u t - を発生させる電圧発生回路8と、ワード線電位V <sub>WL</sub> を発生させるW L ブースト回路12と、書き込み＆消去制御部2によって制御され出力電位V o u t +、V o u t - およびワード線電位V <sub>WL</sub> を受けて各内部回路に分配するディストリビュータ14とを含む。

【0101】

Xデコーダは、図示しないが、ワード線を選択するためのW L デコーダと、セレクトゲートを選択するためのS G デコーダと、選択されたメモリブロックに対応するウェル領域を選択するW E L L デコーダと、ソース線を選択するためのS L デコーダとを含む。

【0102】

Y系制御回路24は、読み出時にカラム選択を行ないセンスアンプで読み出作業を行なうY G & センスアンプとラッチ回路と、ラッチしているデータに基づき書き込み時のメインビット線M B L に高電位を印加するかどうかを決定するページバッファとを含む。

【0103】

W L ブースト回路12は、高速アクセスを実現するために読み出時に選択されたワード線W L および選択されたセレクトゲートS G に与える昇圧電位を発生する回路である。

【0104】

不揮発性半導体記憶装置1は、さらに、メモリアレイ26を含む。メモリアレイ26は、それぞれが分離されたウェルの内部に形成されるメモリブロックB L O C K 0 ~ B L O C K <sub>n</sub> を含む。

【0105】

メモリブロックB L O C K 0 は、メモリセル30, 32と、セレクトゲート28とを含む。メモリブロックB L O C K 0 では、Xデコーダ18によって選択されたセレクトゲート線S G L 、ワード線W L 0 , W L 1 およびソース線S L に対応するメモリセルが選択され、メインビット線M B L からデータに対応する信号を受けてデータ保持が行なわれる。図1では、選択されたセレクトゲート線S G L 、ワード線W L 0 , W L 1 およびソース線S L に対応するセレクトゲート28、メモリセル30, 32が代表的に図示されている。

【0106】

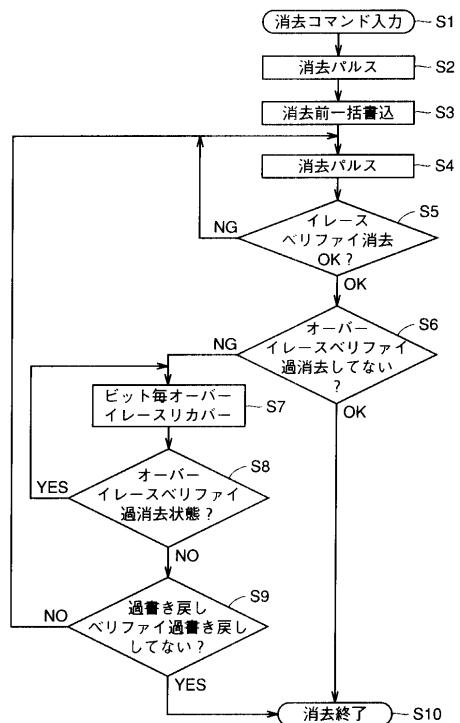

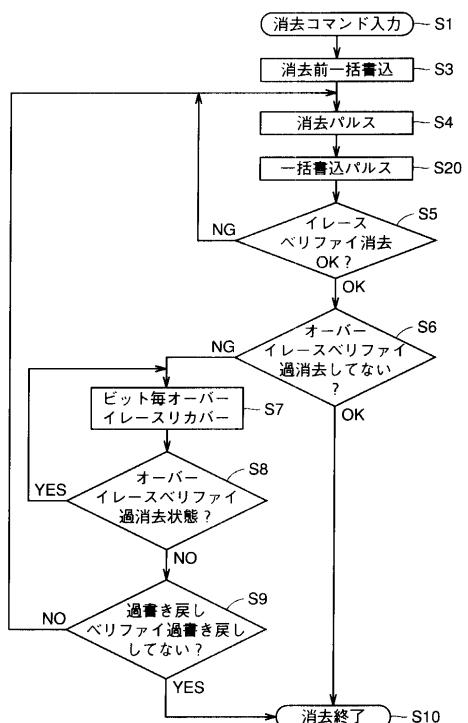

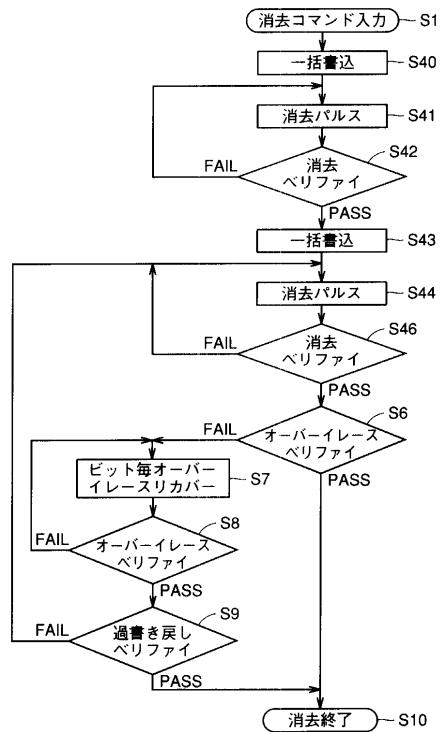

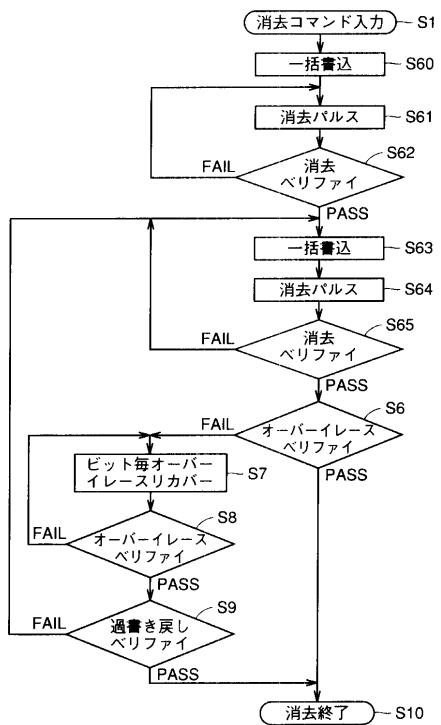

図2は、図1の書き込み＆消去制御部2が制御するフラッシュメモリの消去シーケンスを示したフローチャートである。

【0107】

図2を参照して、ステップS 1において消去コマンドが入力される。続くステップS 2においては、後に説明するブロック単位でF N トンネル電流を用いた消去パルスが印加される。その後、ステップS 3においてF N トンネル電流を用いてブロック単位で一括書き込み行なう消去前一括書き込みが実施される。この消去前一括書き込み時には、たとえば、図64で説明した電圧がメモリブロックに与えられる。

【0108】

続いて、ステップS 4においてF N トンネル電流を用いてブロック単位で消去を行なうために所定のパルス幅の消去パルスが印加される。この消去パルス印加時には、たとえば、図48で説明した電圧がメモリブロックに与えられる。

【0109】

そして、ステップS 5においてメモリブロックのすべてのメモリトランジスタのデータ消去が実施されたか否かを確認するためのイレースベリファイが行なわれる。このイレースベリファイ時には、たとえば、図50で説明した電圧がメモリブロックに与えられる。

【0110】

消去が完了していないときは、再びステップS 4に戻り消去パルスの印加が行なわれる。

【0111】

一方、メモリトランジスタのデータ消去が確認されると、ステップS 6に進みオーバイレースベリファイが実施される。オーバイレースベリファイではすべてのメモリセルが過消去状態になつてないかが確認される。このオーバイレースベリファイ時には、たとえば、図59で説明した電圧がメモリブロックに与えられる。

10

20

30

40

50

## 【0112】

過消去状態にあるメモリトランジスタが存在する場合には、ステップS7に進みビット毎オーバイレースリカバーが行なわれる。ビット毎オーバイレースリカバーでは、チャネルホットエレクトロンを用いてメモリトランジスタを選択的に書き戻す作業、すなわち、低くなりすぎたしきい値電圧を高くする作業が行なわれる。

## 【0113】

実際には、バイト単位(8bit)またはワード単位(16bit)でベリファイの読み出を行ない、過消去状態にあるか否かが判断される。過消去状態にあると判断されたビットについて書き戻し動作が行なわれる。書き戻し動作のばあいでもベリファイ時と同様にバイト単位またはワード単位で選択処理が行なわれ、そのうち書き戻し対象となったビットに書き戻しのための電圧が印加される。

10

## 【0114】

このビット毎オーバイレースリカバーを行なう時には、たとえば、図61で説明した電圧がメモリブロックに与えられる。

## 【0115】

そして、ステップS8に進みオーバイレースベリファイが行なわれる。オーバイレースベリファイではステップS6と同様にブロック内のすべてのメモリトランジスタが過消去状態になつてないかがチェックされる。過消去状態にあるメモリトランジスタが残っているときには、再びステップS7に戻る。

20

## 【0116】

一方、過消去状態のメモリトランジスタが存在していない場合には、ステップS9に進み過書き戻しベリファイが行なわれ、過書き戻しになっているメモリトランジスタがあるかどうかが確認される。過書き戻しのメモリトランジスタがあった場合には、再びステップS4に戻り消去パルスの印加が行なわれる。

## 【0117】

一方、過書き戻しのメモリトランジスタがなかった場合には、ステップS10に進み消去が終了する。

## 【0118】

実施の形態1のフローチャートの特徴は、図63で示した従来の消去シーケンスの場合に比べてステップS2において消去前一括書き込みの前にブロック単位でFNトンネル電流を用いた消去パルスを印加することである。

30

## 【0119】

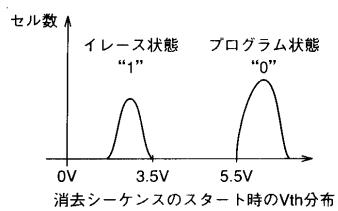

図3は、図2の消去シーケンスにおいてステップS1の消去コマンド入力前のしきい値電圧の分布を示した図である。

## 【0120】

本発明の不揮発性半導体記憶装置は、NOR型フラッシュメモリを例として示している。しきい値電圧が5.5V以上のメモリトランジスタは“0”を保持することに対応する。一方、しきい値電圧が3.5V以下のメモリトランジスタは“1”を保持していることに対応している。また、“1”的状態がイレース状態に対応し“0”的状態がプログラム状態に対応する。また“1”的状態から“0”的状態にすることを書き込みと呼ぶ。

40

## 【0121】

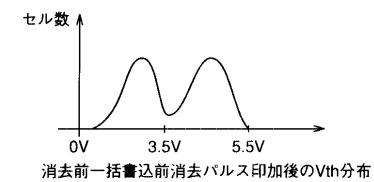

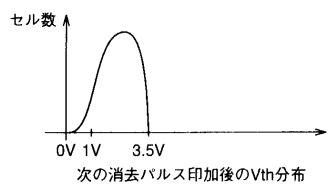

図4は、図2におけるステップS2が実施された後の消去パルス印加後のメモリブロック内のしきい値電圧の分布を示した図である。

## 【0122】

図4を参照して、消去パルスを印加すると、図3に示したプログラム状態にあったメモリトランジスタがイレース状態に近づく。また、イレース状態になったメモリトランジスタはしきい値電圧がより小さくなる方向にシフトする。

## 【0123】

しかしながら、ステップS2で与えられる消去パルスは、メモリトランジスタのしきい値のシフト量がステップS4、S5が完了した場合のシフト量に比べて少ない。つまり、メ

50

モリブロックの“0”の状態にあるメモリトランジスタ全体が完全に消去されるまでパルスが印加されるわけではないのでデプレッション状態にあるメモリトランジスタは存在していない。つまり、図2のステップS4で使用される消去パルスをたとえば一回のみ印加することで、このようなしきい値電圧の分布を実現することができる。さらに、消去パルス幅を小さくすることでしきい値電圧のシフト量を小さくしてもよい。

【0124】

図2に示したステップS2における消去パルスの印加の電圧は、図48に示した消去パルスの印加電圧と同じ電圧で実現することができるが、さらに、異なる電圧でも構わない。たとえば、フローティングゲートから電子の引き抜きが少しずつ行なわれるよう、ゲート電位を-10Vよりもソース電位に近づけても良い。

10

【0125】

図5は、図2のステップS3が終了し、消去前一括書き込みが終わった後のメモリトランジスタのしきい値分布を示した図である。

【0126】

図5を参照して、メモリトランジスタのしきい値電圧の分布は、図68に示した従来の消去シーケンスの一括書き込み終了後のしきい値電圧の分布と比べると、しきい値電圧が非常に高くなってしまったメモリトランジスタの存在がなくなり、メモリトランジスタのトンネル酸化膜にかかる電圧を低く抑えることができ信頼性が向上する。

【0127】

以上説明したように、消去前一括書き込みの前にブロック単位で消去パルスを印加することにより、消去パルス印加後のしきい値電圧の分布幅が狭くなるので、オーバイレースリカバーの処理がされる対象となるメモリトランジスタが少なくなり、合計の消去時間を短くすることができる。

20

【0128】

[実施の形態2]

図6は、実施の形態2の不揮発性半導体記憶装置において行なわれる消去シーケンスを示したフローチャートである。

【0129】

図6を参照して、この消去シーケンスのフローチャートは、図2で示した実施の形態1において用いられる消去シーケンスのフローチャートにおいてステップS2の消去パルス印加に代えてステップS4とステップS5の間に一括書き込みパルスを与えるステップS20を備える点が異なる。他の点は図2に示した消去シーケンスのフローチャートと同様な処理が行なわれる所以説明は繰返さない。

30

【0130】

ステップS20では、ステップS4の消去パルス印加後にブロック単位のFNトンネル電流を用いた一括書き込みパルスを印加することが行なわれる。

【0131】

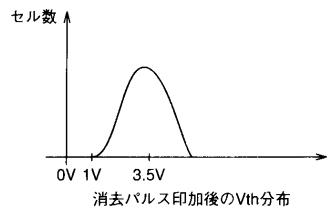

図7は、消去パルス印加後のしきい値電圧の分布を示した図である。

図7を参照して、消去パルス印加後では、しきい値電圧はかなりばらついており、グラフの形は裾野が広い山形になっている。

40

【0132】

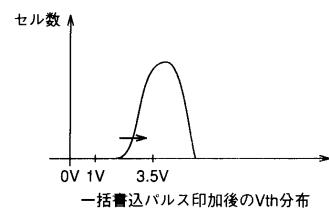

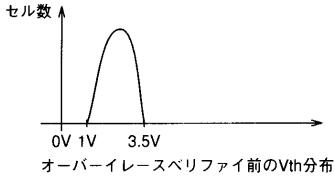

図8は、図6のステップS20の一括書き込みパルスを与えた後のしきい値電圧の分布を示した図である。

【0133】

図8を参照して、一括書き込みパルスを印加すると、図7に示されたしきい値電圧の分布のうちしきい値電圧が低い部分に分布していたメモリトランジスタのしきい値は、しきい値電圧が高くなるように書き戻しが行なわれることになる。したがって、しきい値電圧の分布幅は図7と比べると狭くなる。ただし、この状態では、図6のステップS5に進むと3.5Vよりしきい値電圧が大きいメモリトランジスタが多数存在し、イレースペリファイが完了しないため、再びステップS6に戻り消去パルスが印加されることになる。

50

## 【0134】

図9は、再びステップS4で消去パルスが印加された後のしきい値電圧分布を示した図である。

## 【0135】

図9を参照して、消去パルスが印加されたことにより、しきい値電圧が3.5Vより大きいメモリトランジスタは存在しなくなっている。

## 【0136】

図10は、図9に示したしきい値電圧の分布をとっていたメモリブロックにさらにステップS20の一括書き込みパルスを与え、ステップS5のイレースペリファイが完了した後のメモリトランジスタのしきい値電圧の分布を示した図である。

10

## 【0137】

図10を参照して、ステップS20の一括書き込みパルスを印加しているので、一括書き込みパルスを加えない場合に比べてしきい値電圧の分布幅が狭くなっていることがわかる。したがって、過消去になっているメモリトランジスタの数も少ないので、オーバイレースリカバーの処理の対象となるメモリトランジスタの数が少なくなり、合計の消去時間が短くなる。

## 【0138】

このときのステップS20の一括書き込みパルスの印加電圧は、通常のデータ書き込み時よりもしきい値電圧のシフト量が少なくなるように設定されている。通常は、ステップS4の消去パルス印加によるしきい値電圧のシフト量よりもシフト量は少ない。したがって、ステップS4の消去パルス印加後にステップS20において一括書き込みパルスを印加してもステップS4の消去パルス印加前よりしきい値電圧が大きくなってしまう可能性は少ない。

20

## 【0139】

このときの印加電圧は、ステップS3の消去前一括書き込み時の電圧と同じでもよいが、異なる電圧を印加しても実現は可能である。たとえば、しきい値電圧のシフト量を小さくするために、ワード線電位を10Vからソース電位にすこし近づけても良い。さらに、書き込みパルス幅を小さくすることでききい値電圧のシフト量を小さくしてもよい。

## 【0140】

以上説明したように、一回の消去パルスを印加するごとにFNトンネル電流を用いた一括書き込みパルスによる軽い書き込みを実施することにより、FNトンネル電流を用いた一括消去を実施して広くなつたしきい値電圧の分布幅を一回の消去パルスを印加するごとに狭くする。したがって、オーバイレースリカバーの処理の対象となるメモリトランジスタの数が少なくなるとともに、オーバイレースリカバーの対象となったメモリトランジスタに対しては、チャネルホットエレクトロンにより高速で書き戻すことができるので、合計の消去シーケンスの完了時間を短くすることが可能となる。

30

## 【0141】

## [実施の形態3]

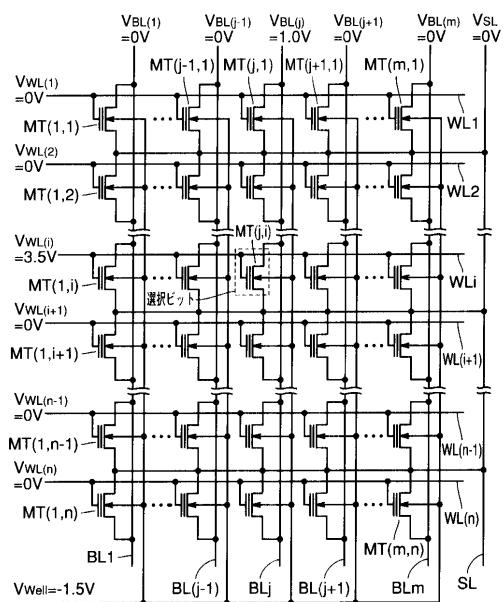

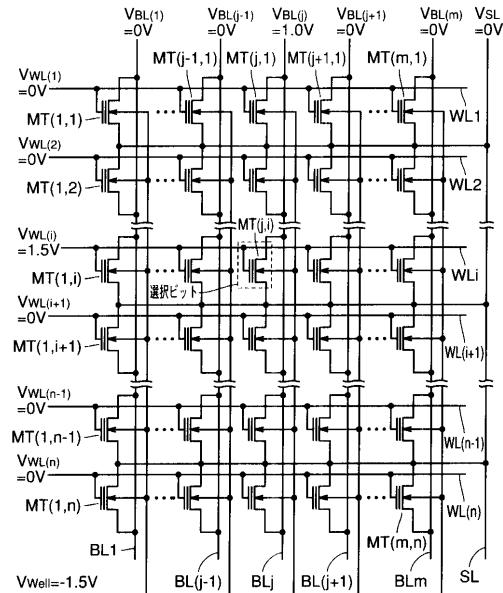

図11は、実施の形態3においてイレースペリファイ時にメモリブロックに印加される電圧の設定を説明するための回路図である。

## 【0142】

図11を参照して、このメモリブロックには、n行m列に配置された各々がフローティングゲートを有するメモリトランジスタが示されている。各行のメモリセルを選択するためにはワード線WL1～WLnが設けられている。各列のメモリトランジスタのドレインは列毎にそれぞれビット線BL1～BLmに接続されている。

40

## 【0143】

また、メモリブロックに含まれるメモリトランジスタのソースはすべてソース線SLに接続され、ソース線SLにはソース線電位V<sub>SL</sub>が与えられる。一つのメモリブロック内のメモリトランジスタは、共通したウエル内に形成されており、このウエルにはウェル電位V<sub>well</sub>が与えられる。

## 【0144】

50

選択ビットに対応するメモリトランジスタを選択するためのワード線  $W_{L_i}$  には  $3.5V$  が与えられる。その他のワード線には  $0V$  が与えられる。選択ビットに対応するメモリトランジスタのドレインに接続されるビット線  $B_{L_j}$  には  $1.0V$  が与えられ他のビット線には  $0V$  が与えられる。そして、ソース線電位  $V_{SL}$  は  $0V$  に設定され、ウェル電位  $V_{well}$  は  $-1.5V$  に設定される。

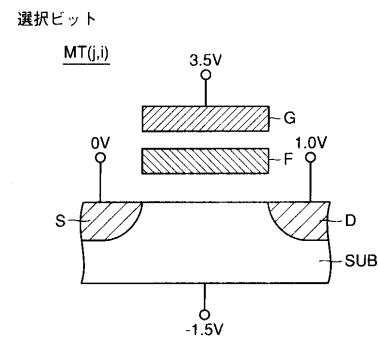

【0145】

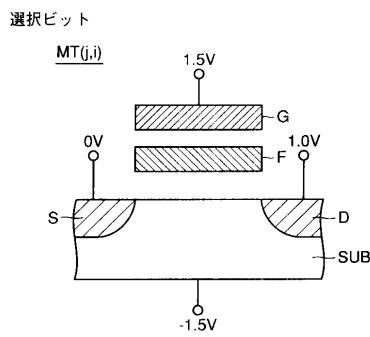

図12は、図11の回路図の選択されたメモリトランジスタに与えられる電位を説明するための図である。

【0146】

図12を参照して、選択されたメモリトランジスタのゲートには  $3.5V$  が与えられ、ソースには  $0V$  が与えられ、ドレインには  $1.0V$  が与えられる。そして、基板部には  $-1.5V$  が与えられる。 10

【0147】

すなわち、ペリファイリード時に基板部の電位、すなわち、ウェル電位  $V_{well}$  を  $0V$  よりも小さく設定することが特徴となっている。

【0148】

図13は、実施の形態3におけるオーバイレースペリファイ時のメモリブロックの電圧設定を説明するための回路図である。

【0149】

図13を参照して、選択ビットに対応するメモリトランジスタを選択するためのワード線  $W_{L_i}$  には  $1.5V$  が与えられ、他のワード線には  $0V$  が与えられる。一方、選択ビットに対応するメモリトランジスタのドレインに接続されているビット線  $B_{L_j}$  には  $1.0V$  が与えられ、他のビット線には  $0V$  が与えられている。またソース線電位  $V_{SL}$  として  $0V$  が与えられ、ウェル電位  $V_{well}$  は  $-1.5V$  に設定される。 20

【0150】

図14は、図13に示した選択ビットに対応するメモリトランジスタの設定電位を説明するための図である。

【0151】

図14を参照して、選択されたメモリトランジスタのゲートには  $1.5V$  が与えられ、ソースには  $0V$  が与えられ、ドレインには  $1.0V$  が与えられる。そして、ウェルには  $-1.5V$  が与えられている。 30

【0152】

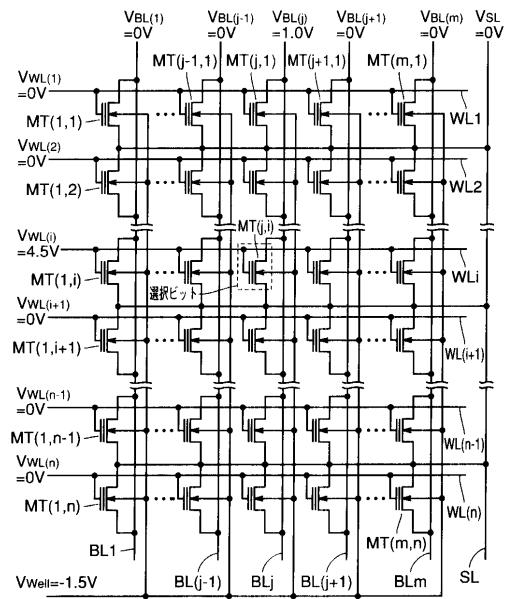

図15は、実施の形態3におけるリード時の電圧設定を説明するための回路図である。

【0153】

図15を参照して、選択ビットに対応するメモリトランジスタを選択するためのワード線  $W_{L_i}$  には  $4.5V$  が与えられ、他のワード線には  $0V$  が与えられている。また、選択ビットに対応するメモリトランジスタのドレインに接続されているビット線  $B_{L_j}$  には  $1.0V$  が与えられ、他のビット線には  $0V$  が与えられている。また、ソース線電位  $V_{SL}$  として  $0V$  が与えられ、ウェル電位  $V_{well}$  は  $-1.5V$  に設定される。 40

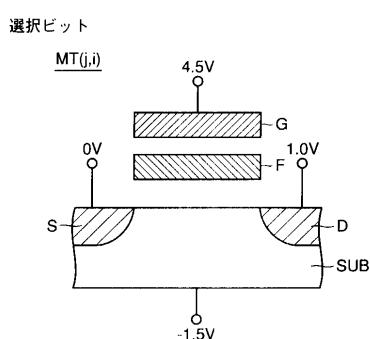

【0154】

図16は、リード時の選択ビットに対応するメモリトランジスタの設定電位を説明するための図である。

【0155】

図16を参照して、リード時には、選択されたメモリトランジスタのゲートには  $4.5V$  が与えられ、ソースには  $0V$  が与えられ、ドレインには  $1.0V$  が与えられる。そして、ウェルには  $-1.5V$  が与えられている。

【0156】

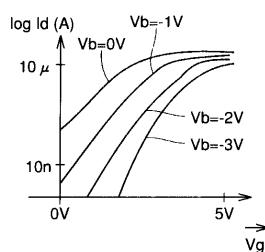

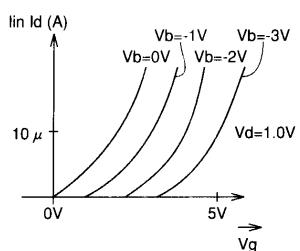

図17は、しきい値電圧  $V_{th}$  を  $2.0V$  に設定した場合のメモリトランジスタのゲート電位とドレイン電流の基板電位の依存性を示した図である。

【0157】

図18は、図17の縦軸を対数表示にした図である。

図17、図18を参照して、基板部分に負電位を与えることにより、サブスレッショルド係数(S. factor)が小さくなることが示される。

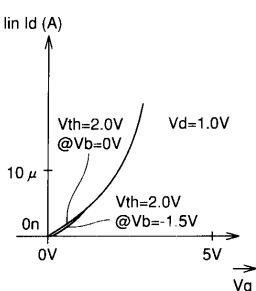

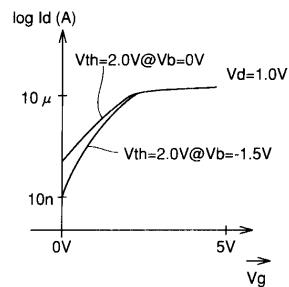

#### 【0158】

図19、図20は、基板電位V<sub>b</sub>が0Vの状態でしきい値電圧V<sub>th</sub>を2.0Vにした場合と、基板電位V<sub>b</sub>が-1.5Vの状態でしきい値電圧V<sub>th</sub>を2.0Vにした場合のゲート電位とドレイン電流の関係を示す図である。

#### 【0159】

図19、図20を参照すると、基板電位V<sub>b</sub>を負にした場合には、基板電位V<sub>b</sub>が0Vの場合よりもサブスレッショルド係数が小さいため、同じしきい値電圧でもオフリーク電流、すなわちゲート電位が0Vのときのドレイン電流I<sub>d</sub>は小さくなることがわかる。

10

#### 【0160】

これにより、従来例の課題であった同一ビット線上にある非選択セルのオフリーク電流の総和によるペリファイおよびリードの誤動作を回避することができる。

#### 【0161】

また、実施の形態1、2と併せて用いれば、イレースベリファイ時のしきい値電圧の分布幅も狭くなるので、オーバイレースリカバーおよびそのペリファイに要する時間を短縮することができ、トータルの消去完了時間を短くすることができる。

#### 【0162】

以上はN型フラッシュメモリの場合の例を示したが、P型フラッシュメモリにおいては、基板部分すなわちウェルには正の電位を印加することで同様な効果を得ることができる。

20

#### 【0163】

以上説明したように、基板部分に負電位を印加することで、メモリセルのゲート電位-ドレイン電流特性におけるサブスレッショルド係数が小さくなるので、同じしきい値電圧でもオフリークを抑制することができる。

#### 【0164】

これにより、しきい値電圧が低いメモリトランジスタをペリファイおよびリードする際に、同一ビット線上にある非選択メモリトランジスタのオフリークの総和によって生じるオーバイレースリカバーの誤動作を防ぐことができる。また、しきい値電圧の分布幅も狭くすることができるのでオーバイレースリカバーおよびそのペリファイに要する時間を短縮でき、トータルの消去完了時間を短くすることができる。

30

#### 【0165】

##### [実施の形態4]

実施の形態1～3では、動作の基本として、消去しようとするメモリセル領域(ブロック)に対して消去前書込と呼ばれる動作を行なうことを説明した。この動作は、消去をするために選択したブロックのメモリセルに対して、一括して書込時に与える電圧に相当する電圧を印加することで行なう。消去前書込の動作により、消去状態にあったメモリセルを消去パルスを印加する前に書込状態にすることで、消去パルスが印加されたときにしきい値電圧V<sub>th</sub>が下がりすぎ、過消去状態になりにくくすることができる。

#### 【0166】

40

さらに、実施の形態2においては、図6に示したように消去前一括書込よりは弱い強度の電圧パルスを消去パルスと組合せて与え、消去状態を確認しつつ与えるというステップを繰返している。

#### 【0167】

この消去パルスと一括書込パルスとを組合せて与える動作により、従来から行なわれている消去パルスのみを印加する場合と比べて、しきい値電圧が低くなりすぎた過消去状態のメモリセルの数を大きく減らすことができる。

#### 【0168】

しかし、過消去状態のメモリセル数を削減するために図6のステップS4, S20を繰返しても、メモリセル特性のばらつきによりすべてのメモリトランジスタのしきい値電圧を

50

設定した範囲内に入るのは困難な場合もあり得る。

【0169】

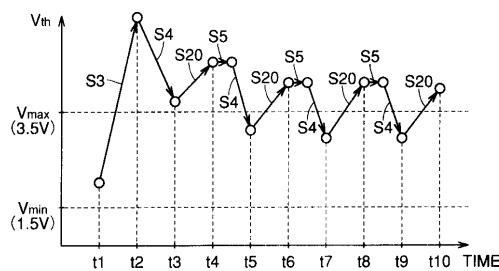

図21は、設定したしきい値電圧の範囲内に入れるのが困難なメモリトランジスタのしきい値電圧の変化を説明するための図である。

【0170】

図6、図21を参照して、時刻t1において、消去コマンドが入力される前には、メモリセルは消去状態、すなわちしきい値電圧が低い状態あった場合について説明する。

【0171】

ステップS3の消去前一括書き込みによって時刻t2においては、メモリトランジスタは、しきい値電圧が消去判定電圧の上限値である $V_{max}(3.5V)$ よりかなり高い状態になる。続いて、ステップS4において消去パルスがそのメモリトランジスタに印加されると、時刻t3において、しきい値電圧はやや低くなり消去判定電圧の上限値である $V_{max}(3.5V)$ に近づく。

10

【0172】

次に、ステップS20において一括書き込みパルスが印加されると、時刻t4においてしきい値電圧は再び大きくなり消去判定電圧 $V_{max}$ から遠ざかる。そしてステップS5においてイレースペリファイが行なわれるが、このメモリトランジスタの存在により、イレースペリファイの結果は未消去であるという判定となる。

【0173】

そして、再びステップS4の消去パルスが印加されると、しきい値電圧は小さくなり、一旦は判定電圧である $V_{max}$ よりも小さくなる。しかし、ステップS20において一括書き込みパルスが印加されるため、時刻t6において再びしきい値電圧は判定電圧である $V_{max}$ を超てしまう。そしてステップS5のイレースペリファイが実施され、消去が未完了であると判定される。

20

【0174】

メモリトランジスタは、製造ばらつきにより、トンネル効率やフローティングゲートに蓄積される電荷量がさまざまであるため、ステップS4の消去パルスの印加によるしきい値電圧の低下と、ステップS20の一括書き込みパルス印加によるしきい値電圧の上昇とが判定電位である $V_{max}$ 付近で均衡してしまうメモリトランジスタが存在する。このようなメモリトランジスタは、時刻t6で消去未完了と判定されると、ステップS4、ステップS20を経て再び時刻t8で消去未完了と判定され、最悪の場合には、ステップS4、S20、S5のループを何度も繰返す、いわゆる無限ループ状態に陥ってしまう。

30

【0175】

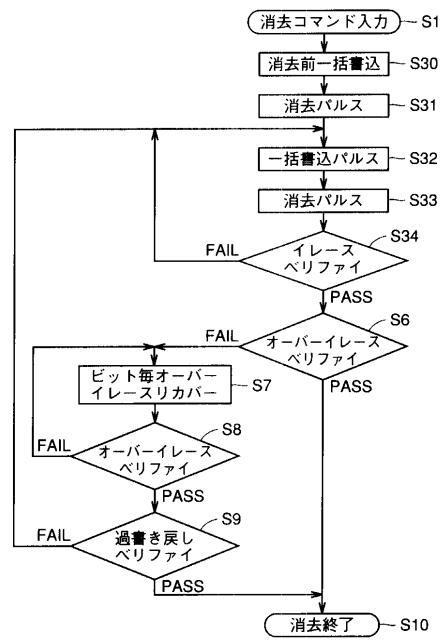

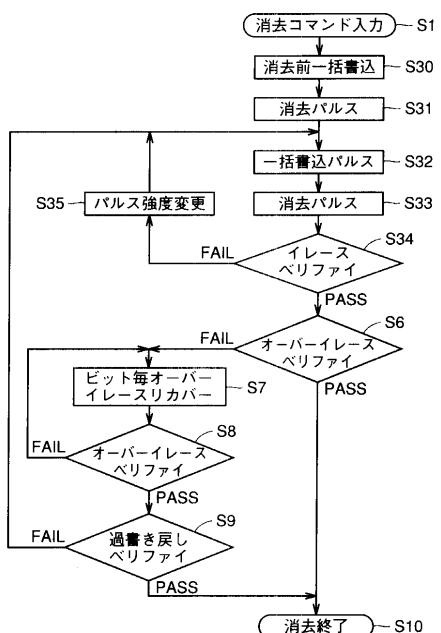

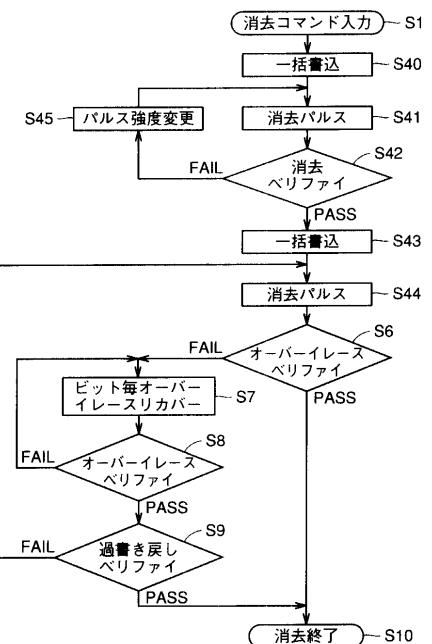

図22は、実施の形態4の不揮発性半導体記憶装置において行なわれる消去のシーケンスを示したフローチャートである。

【0176】

図22のフローチャートは、図6に示した実施の形態2の場合の消去シーケンスのフローチャートにおいて、ステップS3、S4、S20、S5に代えてステップS30～S34を備える。ステップS6～S10は、図6に示したフローチャートと同様であるため説明は繰返さない。

40

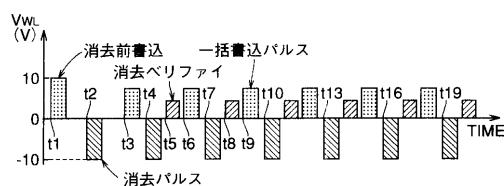

【0177】

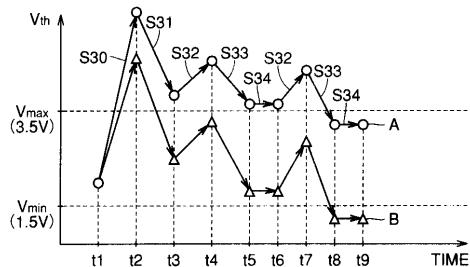

図23は、図22に示したフローチャートのシーケンスによって消去する場合に、メモリトランジスタのゲート電圧すなわちワード線電位 $V_{WL}$ の変化を示した波形図である。

【0178】

図24は、図22のフローチャートに従う消去シーケンスにおけるメモリトランジスタのしきい値電圧の変化を示した図である。

【0179】

図23、図24を参照して、時刻t1において、図22のステップS30の消去前一括書き込みによってメモリトランジスタのゲート電位は10Vに設定される。このとき、たとえば図65によって示したように、ソース電位およびウェル電位は-8Vに設定され、ビット

50

線はオープンに設定されている。この書込パルスの印加によって、図24の時刻 $t_1 \sim t_2$ に示されるように、しきい値電圧は、イレースベリファイの消去判定電圧である $V_{max}$ よりも大きくなる。ここで、図24において、Aで示したのは、消去されるメモリブロックにおいてしきい値電圧が変化しにくいメモリトランジスタのしきい値電圧の挙動であり、Bで示したのは、同じメモリブロック中のしきい値電圧が変化しやすいメモリトランジスタのしきい値電圧の挙動である。

【0180】

再び図23を参照して、時刻 $t_2$ において図22のステップS31に示される消去パルスの印加が開始される。このとき、たとえば図49によって示したように、ワード線電位は-10Vに設定され、ソース電位およびウェル電位は8Vに設定され、ビット線はオープンに設定される。

10

【0181】

消去パルスの印加に応じて、図24の時刻 $t_2 \sim t_3$ において、しきい値電圧は小さくなる。

【0182】

時刻 $t_3$ において、一括書込パルスがステップS32で印加される。この一括書込パルスは、ステップS3の消去前一括書込より強度が弱い。一括書込パルスの印加により、図24の時刻 $t_3 \sim t_4$ に示されるように、再びしきい値電圧は上昇する。

【0183】

時刻 $t_4$ では、ステップS33に示される消去パルスの印加がなされる。この消去パルスの印加により、図24の時刻 $t_4 \sim t_5$ に示すように、しきい値電圧は再び小さくなる。

20

【0184】

時刻 $t_5$ においては、ステップS34のイレースベリファイが実施される。イレースベリファイでは、たとえば、図51において説明したように、ワード線の電位は3.5Vに設定され、ソース電位およびウェル電位は0Vに設定され、ビット線の電位は1.0Vに設定されている。しかしながら、図24のAで示されるメモリトランジスタのしきい値電圧は、判定値である $V_{max}$ よりもまだ大きいため、図22のフローチャートに従い再びステップS32が実施される。

【0185】

時刻 $t_6$ においては、ステップS32の一括書込パルスの印加が開始される。図24の時刻 $t_6 \sim t_7$ に示されるように、一括書込パルスの印加によって、再びしきい値電圧は大きくなる。続いて時刻 $t_7$ において、ステップS33の消去パルスの印加がなされると、図24の時刻 $t_7 \sim t_8$ に示されるように、しきい値電圧は、再び小さくなり、Aで示されるメモリトランジスタもステップS34のイレースベリファイをパスすることになる。なおBで示されるメモリトランジスタは判定電圧 $V_{min}$ (1.5V)を下回っているため後に選択的にオーバーイレースリカバーが行なわれることになる。

30

【0186】

他にも、消去されにくいメモリトランジスタが存在し、ベリファイ時に判定電圧 $V_{max}$ よりもそのメモリトランジスタのしきい値電圧が大きい場合には、図23の時刻 $t_{10}$ 以降に示すように一括書込パルスと消去パルスおよびイレースベリファイのためのパルスの印加が繰返され、消去するメモリブロック内のメモリトランジスタの大部分のしきい値電圧が消去半定電位 $V_{max}$ 以下となるまでステップS32～S34の処理が続けられる。

40

【0187】

このように、一括書込パルスをステップS32で与えた後にステップS33で消去パルスを与え、そしてステップS34においてイレースベリファイを実施するようにすれば、図21に示したような判定値 $V_{max}$ 付近でしきい値電圧が上下を繰返してしまうようなメモリトランジスタの場合でも、ステップS34のイレースベリファイをパスすることになる。

【0188】

したがって、消去コマンドの入力がされてからイレースベリファイが完了するまでのパル

50

ス印加数を少なくすることができ、消去時間を短縮することができる。

【0189】

[実施の形態4の変形例]

図25は、実施の形態4の不揮発性半導体記憶装置の消去シーケンスの変形例を示すフローチャートである。

【0190】

図25に示したフローチャートは、図22に示した実施の形態4のフローチャートにおいて、ステップS34のイレースベリファイが消去未完了と判定された場合において、パルス強度変更を行なうステップS35をさらに有する。他の部分は、図22で示したフローチャートと同様であるため説明は繰返さない。

10

【0191】

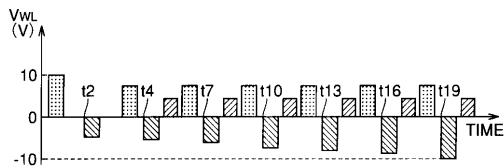

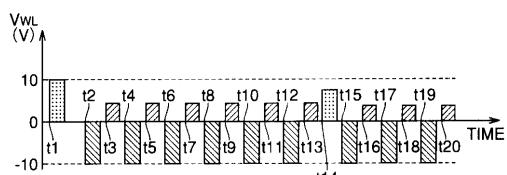

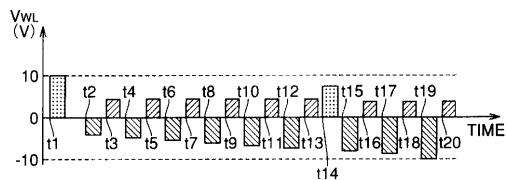

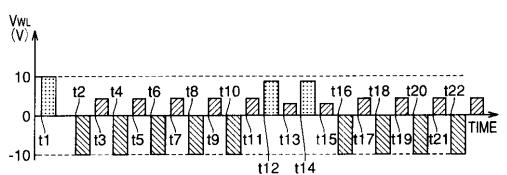

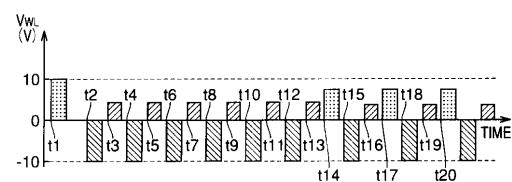

図26は、図25のフローチャートに従った消去動作を説明するためのワード線電位の変化を示した波形図である。

【0192】

図25、図26を参照して、時刻t2においてステップS31で印加される消去パルスは、たとえば、ワード線電位が-5V程度に設定される。そしてステップS32の一括書き込みパルス印加を経て、時刻t4においてステップS33の消去パルスが印加される場合には、この消去パルスはステップS31で印加されたパルスに比べて、たとえば0.5V程度絶対値が大きく設定される。ステップS34においてイレースベリファイが消去未完了と判定されると、ステップS35においてパルス強度がさらに0.5V程度絶対値が大きくなるように設定され、応じて次のステップS33における消去パルス印加時には、時刻t7に示されるようにさらに消去パルスの強度が強く設定される。このように、ステップS34のイレースベリファイにおいて消去未完了と判定されると、ステップS35において次に印加される消去パルスの強度がさらに強く設定され、時刻t10, t13, t16, t19に示されるように段階的に消去パルスの強度が大きくなる。このようにして、消去パルスを段階的に強くすることで、繰返し与えるパルスの合計回数を少なくすることができる。したがって、さらに不揮発性半導体記憶装置の消去時間の短縮をすることができる。

20

【0193】

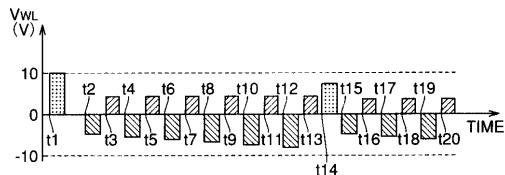

図27は、図26の波形においてさらに、一括書き込みパルスを段階的に強くした場合の波形を示す図である。

30

【0194】

図27には、時刻t3以降に繰返し印加されるステップS32の一括書き込みパルスを消去パルスの強度の変化に応じて段階的に強くすることが示されている。消去時間の短縮を図るとともに、一括書き込みパルスの強度を調節することでステップS34のイレースベリファイ完了後におけるメモリトランジスタのしきい値電圧の分布幅のより狭帯化をすることができる。

【0195】

このように、ステップS35において一括書き込みパルスの強度と消去パルスの強度とを同時に段階的に強度を強くすることによってしきい値電圧の分布が狭くなるため、ステップS6のオーバイレースベリファイにおいてビットごとオーバイレースリカバーに分岐するメモリセルの数が減り、合計の消去時間を短縮することができる。

40

【0196】

[実施の形態5]

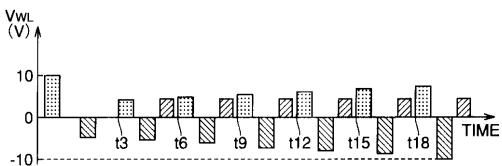

図28は、実施の形態5の不揮発性半導体記憶装置における消去シーケンスを説明するためのフローチャートである。

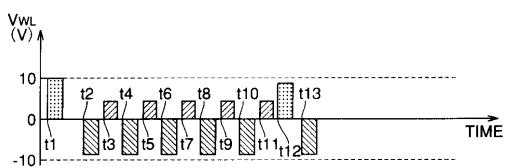

【0197】

図29は、図28のフローチャートに従い消去動作を行なった場合のワード線電位の変化を示した波形図である。

【0198】

50

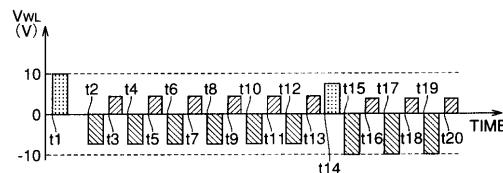

図28、図29を参照して、実施の形態5における消去フローは、図6に示した消去動作のフローチャートにおいてステップS3、S4、S20、S5に代えて、ステップS40～S44を備える点が異なる。ステップS6～S10は図6に示したフローチャートと同様であり説明は繰返さない。

【0199】

時刻t1において消去コマンドが入力されると、ステップS40の一括書き込みパルスが印加される。

【0200】

続いて時刻t2においてステップS41の消去パルスが印加される。続いて時刻t3においてステップS42の消去ベリファイが行なわれる。消去が指定されたブロックの消去が完了していないため、時刻t4～時刻t10では、ステップS41の消去パルスの印加とステップS42の消去ベリファイとが繰返し行なわれる。

10

【0201】

そして、時刻t11においてステップS42の消去ベリファイが行なわれ、消去が指定されたブロックの消去が完了したと判定されると、ステップS43に進み時刻t12において一括書き込みパルスが印加される。この一括書き込みパルスの印加により、ステップS41、S42の消去動作によって消去ベリファイ電圧以下において広く分布していたメモリブロック中のメモリトランジスタのしきい値電圧は、分布幅が狭くなる。

【0202】

時刻t13においてステップS44の消去パルスが印加されるが、この消去パルスの強度を適切な強度に設定しておけば、時刻t14においてステップS6のオーバイレースベリファイにおいて過消去と判定され、ステップS7以降のビットごとオーバイレースリカバーの処理がなされるメモリセルの数を少なくすることができる。

20

【0203】

以上説明したように、実施の形態5において示した消去動作のシーケンスは、ステップS40～S42において、まず消去動作を先に完了させておき、その後、ステップS43、ステップS44のパルス印加によって過消去状態にばらついたメモリセルの分布を狭める。このようにして、ビットごとのオーバイレースリカバーの処理をしなければならないメモリセルの数を減らすことにより、時間短縮を図るものである。ステップS41、S42の消去動作の中に一括書き込みパルスを印加するステップがないため、ステップS42の消去ベリファイが完了するまでの時間の短縮を図ることができる。

30

【0204】

[実施の形態5の変形例]

図30は、実施の形態5の変形例における消去動作を説明するためのフローチャートである。

【0205】

図31は、図30に示したフローチャートに従った消去動作を説明するためのワード線電位の変化を示す波形図である。

【0206】

図30に示したフローチャートは、図28に示したフローチャートにおいて、ステップS42の消去ベリファイにおいて消去が未完了であると判定された場合に、消去パルスの強度を変更するステップS45をさらに備える点が異なる。他の部分は図28に示したフローチャートと同様であり、説明は繰返さない。

40

【0207】

図30に示したフローチャートの消去シーケンスに従うと、図31の時刻t2において第1回目に与えられるステップS41の消去パルスの強度を小さく設定しておき、消去ベリファイがパスしない場合にステップS45においてパルス強度を変更し、時刻t4においてはさらに強い消去パルスを与えている。このように、消去ベリファイがパスしない場合にはさらに強い消去パルスを次に印加するため、ステップS42の消去ベリファイにおいてパスするまでに印加する消去パルスの数を少なくすることができ、時間短縮を図ること

50

ができる。

【0208】

図32は、図31に示した波形で表わされる消去シーケンスの変形例を示した波形図である。

【0209】

図31、図32を参照して、図31では、時刻t13において印加されるステップS44の消去パルスは、ステップS42の消去ベリファイがパスした場合におけるステップS41の消去パルスの強度と同じである。これに対して、図32の波形においては、時刻t13において印加されるステップS44の消去パルスの強度は、消去ベリファイが完了した場合における最後に与えられたステップS41の消去パルスの強度よりも弱く設定されている。

10

【0210】

これは、一旦消去が完了したメモリブロックに対してステップS43の一括書きが行なわれた際に、一括書きによりしきい値電圧が消去判定電圧を再び超してしまうメモリトランジスタは、フローティングゲートのカップリングが他のセルよりもよく、消去もされやすいので、時刻t10において印加されていた消去パルスの強度よりも時刻t3で印加する消去パルスの強度を弱くしても、しきい値電圧の分布の狭帯化に十分効果を発揮するためである。

【0211】

[実施の形態6]

20

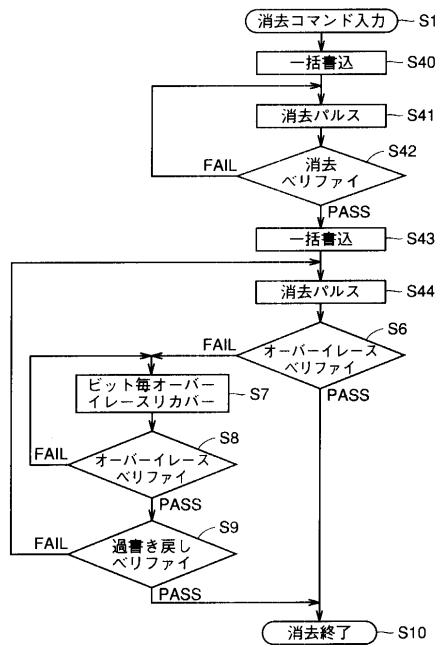

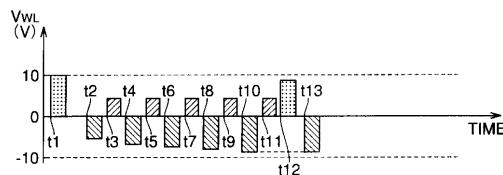

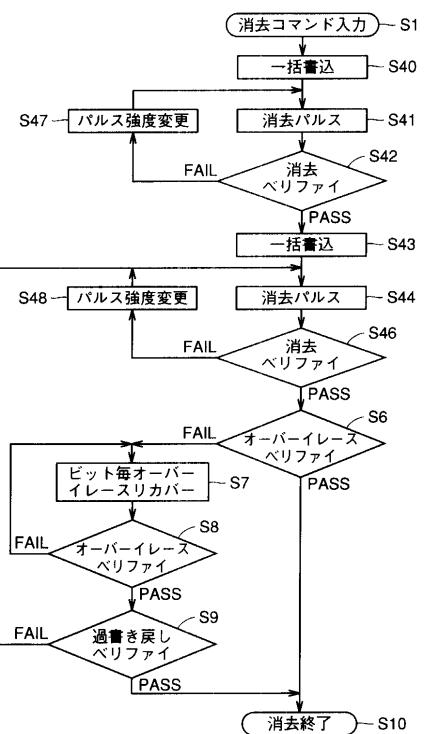

図33は、実施の形態6の不揮発性半導体記憶装置の消去シーケンスを示すフローチャートである。

【0212】

図33に示したフローチャートは、図6に示した実施の形態2の消去シーケンスを示すフローチャートにおいて、ステップS3, S4, S20, S5に代えて、ステップS40～S46を備える点が異なる。ステップS6～S10は図6に示したフローチャートと同様であるので説明は繰返さない。

【0213】

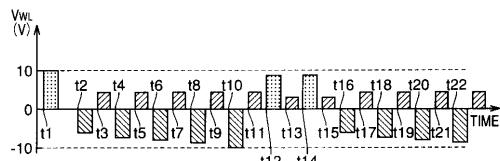

図34は、図33に示したフローチャートの動作を説明するためのワード線電位の変化を示した波形図である。

30

【0214】

図33、図34を参照して、時刻t1においてステップS40に示す消去コマンドが入力された後の一括書きパルスの印加が開始される。

【0215】

続いて時刻t2においてステップS41における消去パルスの印加が開始される。そして、時刻t3において消去ベリファイが行なわれ（ステップS42）、メモリブロックの消去が完了していないと判定され、再び時刻t4においてステップS41の消去パルスの印加がなされる。以降、時刻t5～t13までは消去ベリファイと消去パルス印加が繰返し実施される。

【0216】

40

そして、時刻t13の消去ベリファイ（ステップS42）においてメモリブロックの消去が完了したと判定されると、時刻t14においてステップS43の一括書きパルスが印加される。この書きパルスはステップS40において印加された書きパルスよりも強度が弱い。ステップS43の一括書きパルスの印加によってしきい値電圧の分布がかなり狭帯域化されることがわかっている。たとえば、しきい値電圧が1.5V以下のメモリトランジスタの数も従来と比べてかなり減っている。

【0217】

続いて時刻t15においてステップS44の消去パルスが印加され、時刻t16において消去ベリファイが行なわれる。そして、消去ベリファイがパスするまでステップS44とステップS46が繰返される（時刻t17～t20）。

50

## 【0218】

すなわち、実施の形態6の消去シーケンスにおいては、時間の短縮のため、一括書きパルスは消去ベリファイのループの中には入れず、ステップS43に示すようにステップS42の消去ベリファイの後に1回だけ実施する。その後の消去パルスの印加の効果をステップS46の消去ベリファイを実施することにより、確認する。したがって、実施の形態5に示した消去シーケンスよりもさらに高精度にしきい値電圧を制御することができる。

## 【0219】

また、図34では、時刻t3～t14の間に与えられるステップS42の消去ベリファイ時のワード線電位は4.0V程度に設定され、一方、時刻t16～t20において与えられるステップS46の消去ベリファイ時のワード線電位は3.5V程度に設定されている。

10

## 【0220】

これにより、時刻t14において印加開始されるステップS43の一括書きパルス印加前には、メモリブロックに含まれるメモリトランジスタのしきい値電圧が4.0V以下になる程度まで消去が行なわれる。その後、ステップS43の一括書きによりメモリブロック内のメモリトランジスタのしきい値電圧の分布を狭くする。その後、さらに、しきい値電圧が3.5V以下となるように消去パルスの印加(ステップS44)と消去ベリファイ(ステップS46)とが行なわれる。

## 【0221】

このように2段階に制御することにより、しきい値電圧の分布を狭めつつ、高精度にしきい値電圧の制御を行なうことができる。

20

## 【0222】

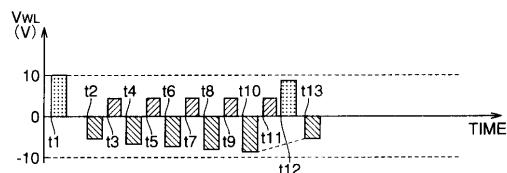

図35は、図34に示したワード線電位の変化を示す波形の変形例を示した図である。

## 【0223】

図35に示した波形は、時刻t2～t13の間に印加されるステップS41の消去パルスの強度がやや弱く設定され、時刻t15～t20で与えられるステップS44の消去パルスの強度の方が強く設定されている点が、消去パルスの強度に特に変化を付けられていない図34に示した波形と異なる。

## 【0224】

つまり、ベリファイを行なう判定電圧付近までしきい値電圧を変化させるために、ベリファイを行なう判定電圧に対応して最適と思われる強度に消去パルスの強度を変化させて与えてもいい。

30

## 【0225】

## [実施の形態6の変形例]

図36は、実施の形態6の変形例の消去シーケンスを示したフローチャートである。

## 【0226】

図36に示したフローチャートは、図33に示したフローチャートの構成において、ステップS42の消去ベリファイにおいて消去が未完了であると判定された場合にパルス強度を変更するステップS47と、ステップS46の消去ベリファイにおいて消去が未完了であると判定された場合に、パルス強度を変更するステップS48とをさらに備える点が異なる。他のステップは図33に示したフローチャートと同様であり、説明は繰返さない。

40

## 【0227】

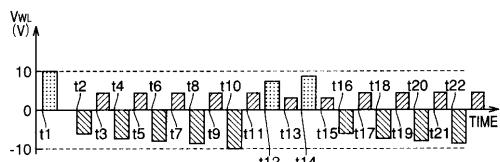

図37は、図36に示したフローチャートに従う消去シーケンスの動作を説明するためにワード線電位の変化を示した第1の波形図である。

## 【0228】

図37を参照して、ステップS41の消去パルスが第1回目に印加される時刻t2においては、消去パルスの強度は弱く設定され、時刻t2～t14においてステップS42の消去ベリファイで消去未完了と判定されるたびごとに、消去パルスの強度がステップS47において増加される。

## 【0229】

50

このようにすることにより、過消去になるメモリセルを最小限に抑えつつもステップ S 4 2 の消去ベリファイが完了するまでの時間を短縮することができる。そして、この波形例においては、時刻  $t_{15}$ において印加されるステップ S 4 4 の消去パルスは、時刻  $t_{12}$ において印加された消去パルスよりもやや強い強度に設定され、時刻  $t_{15} \sim t_{20}$  では、ステップ S 4 6 の消去ベリファイにおいて消去未完了と判定されるたびごとにステップ S 4 8 においてパルス強度が強くなるように変更されている。このようにすることにより、ステップ S 4 6 の消去ベリファイが完了する時間も短縮することができ、かつ、ステップ S 6 において過消去と判定されるメモリセルの数も減らすことができる。

【0230】

図38は、図36に示したフローチャートに従う消去シーケンスの第2の波形例を示した図である。 10

【0231】

図38に示した波形では、時刻  $t_5$  以降に印加されるステップ S 4 4 の消去パルスの初期値が、時刻  $t_2$  において第1回目に印加されるステップ S 4 1 の消去パルスの強度と同じ強度から再び印加開始される点が、消去パルスの強度が連続的に増加する図37に示した波形と異なる。このように変更することにより、図37に示した波形を印加する場合よりもステップ S 6 において過消去と判定されるメモリトランジスタの数を減らすことができる。

【0232】

図39は、図36のフローチャートに従う消去シーケンスの第3の波形例を示した図である。 20

【0233】

図39に示した波形では、時刻  $t_{15}$ において与えられるステップ S 4 4 の消去パルスの第1回目の強度は、ステップ S 4 1 において第1回目に与えられる消去パルスの強度よりもさらに小さく設定される点が図38の波形の場合と異なっている。このように設定することにより、ステップ S 4 1、S 4 2 においては大まかに速く消去を完了させ、ステップ S 4 4、S 4 6 では高精度にしきい値電圧を制御しつつ消去動作を完了させることができる。

【0234】

[実施の形態7]

30

図40は、実施の形態7の不揮発性半導体記憶装置の消去シーケンスのフローチャートである。

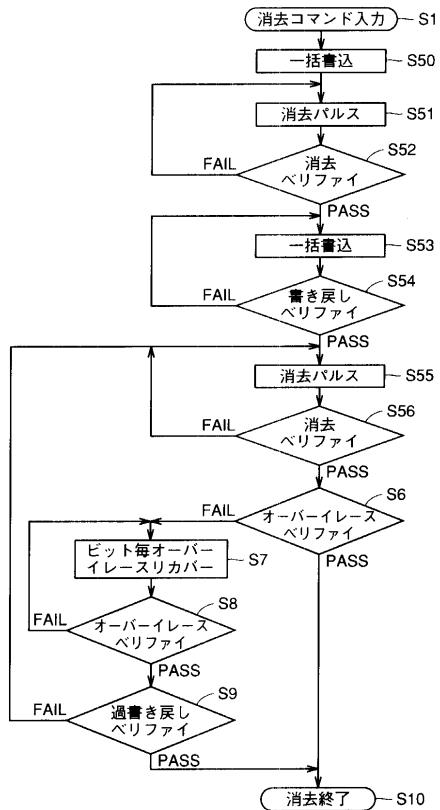

【0235】

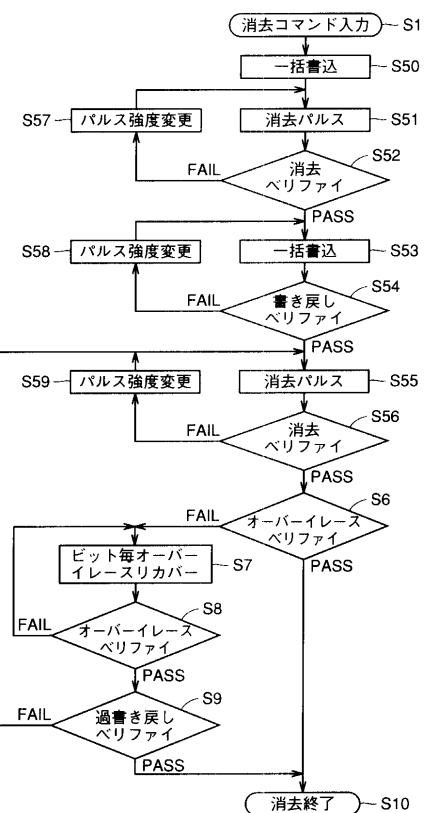

図40に示したフローチャートは、図6に示した実施の形態2の消去シーケンスのフローチャートにおいて、ステップ S 3, S 4, S 20, S 5 に代えてステップ S 50 ~ S 56 を備える点が図6に示したフローチャートと異なる。ステップ S 6 ~ S 10 については、図6に示したフローチャートと同様であるので説明は繰返さない。

【0236】

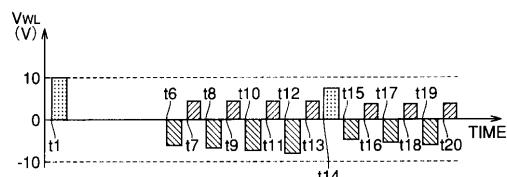

図41は、図40に示したフローチャートに従う消去シーケンスを説明するためのワード線電位の変化を示す波形図である。 40

【0237】

図40、図41を参照して、ステップ S 1 において消去コマンドが入力され、時刻  $t_1$  において一括書きパルスが与えられる（ステップ S 50）。

【0238】

続いて時刻  $t_2$  においてステップ S 51 の消去パルスの印加がされる。そして、ステップ S 52 の消去ベリファイのために時刻  $t_3$  において 3.5 V 程度の電位がワード線に印加される。以降、時刻  $t_4 \sim t_{12}$  まではステップ S 51、ステップ S 52 が繰返される。

【0239】

時刻  $t_{11}$  の消去ベリファイにおいてしきい値電圧が 3.5 V 以下になったことが確認されると、ステップ S 53 に進み時刻  $t_{12}$  において一括書きパルスが与えられる。そして 50

、時刻  $t_{13}$  においてステップ S 5 4 の書き戻しへリファイが実施される。このときには、ステップ S 5 2 の消去ベリファイの場合よりも低い 1.5 V 程度のゲート電位が与えられる。

#### 【 0 2 4 0 】

そして、時刻  $t_{15}$  において書き戻しへリファイが完了した場合には、時刻  $t_{16}$  においてステップ S 5 5 の消去パルスが印加される。そしてステップ S 5 6 の消去ベリファイが完了するまで繰返しステップ S 5 5 の消去パルスの印加がされる。

#### 【 0 2 4 1 】

以上説明したように、ステップ S 5 1、ステップ S 5 2 においてまず消去を完了する。そして、ステップ S 5 3、ステップ S 5 4 において過消去状態となったメモリトランジスタの書き戻しが実行されたことを確認する。そして、再びステップ S 5 5、ステップ S 5 6 においてメモリブロック内のメモリトランジスタの消去が完了したことを確認する。このようにすることにより、より確実にメモリブロック内のメモリトランジスタのしきい値電圧の分布幅を狭めることができ、ステップ S 6 においてビットごとオーバイレースリカバーの実行を行なわなければならないメモリトランジスタの数を減らすことができ、全体的には消去時間の短縮を行なうことができる。

10

#### 【 0 2 4 2 】

さらに、ステップ S 5 4 の書き戻しへリファイの判定条件をメモリトランジスタの数で規定することも可能である。

20

#### 【 0 2 4 3 】

すなわち、通常は、メモリブロックに書き込みパルスを印加し、しきい値電圧がたとえば 1.5 V より小さい過消去状態にあるメモリトランジスタがメモリブロック内になくなったときに、書き戻しへリファイが完了したと判定する。

#### 【 0 2 4 4 】

これに対して、過消去状態にあるメモリトランジスタの数を調べる。この過消去状態にあるメモリトランジスタの数が所定の数より少なければ書き戻しへリファイが完了したと判定することも可能である。

#### 【 0 2 4 5 】

たとえば、ステップ S 7 ~ S 9 のメモリセルのオーバイレースリカバーに 1 ビットあたり  $10 \mu s$  程度かかるとすると、通常の消去動作を行った後に 1 万ビットの過消去のメモリセルがあった場合には、 $100 ms$  の処理時間が必要となる。このときステップ S 5 4 の判定条件として、たとえば、所定の数として 100 ビットを設定したときには、100 ビットまでの過消去状態のメモリトランジスタが容認され、オーバイレースリカバーの処理時間は  $1 ms$  に減ることになる。

30

#### 【 0 2 4 6 】

つまり、ステップ S 5 4 の処理をある程度で切り上げたとしても合計の消去時間の短縮には十分効果がある。したがって、ステップ S 5 4 において、過消去のメモリセルをすべて書き戻すのに要する時間との兼ね合いによって、所定数の過消去状態のメモリトランジスタを容認するようにしても良い。

#### 【 0 2 4 7 】

40

図 4 2 は、実施の形態 7 の変形例のフローチャートである。

図 4 2 のフローチャートは、図 4 0 のフローチャートの構成に加えて、ステップ S 5 2 において消去未完了と判定された場合にパルス強度を変更するステップ S 5 7 と、ステップ S 5 4 において書き戻しが未完了と判定された場合にパルス強度を変更するステップ S 5 8 と、ステップ S 5 6 において消去が未完了と判定された場合にパルス強度を変更するステップ S 5 9 をさらに備える。他のステップは、図 4 0 に示したフローチャートと同様であるため説明は繰返さない。

#### 【 0 2 4 8 】

図 4 3、図 4 4 は、図 4 2 に示したフローチャートの動作を説明するために、ワード線電位の変化を示した第 1、第 2 の波形図である。

50

## 【0249】

図43を参照して、まずステップS57によって時刻t2～t11の間に印加される消去パルスは、ステップS52において消去ベリファイが未完了であると判定されるたびごとに強くなるように段階的に強度が変更される。このようにすることにより、過消去となるメモリトランジスタ数を抑制しつつ、消去時間の短縮を図ることができる。

## 【0250】

また、時刻t16～t22において印加される消去パルスは、ステップS56の消去ベリファイにおいて消去未完了と判定されるたびごとに、ステップS59においてパルス強度が段階的に強くされる。したがって、過消去となるメモリトランジスタ数を抑制しつつも、ステップS56の消去ベリファイが完了するまでの所要時間を短くすることができる。

10

## 【0251】

さらに、図44においては、時刻t12～t15において印加されるステップS53の一括書き込みパルスも、ステップS54の書き戻しへリファイにおいて書き戻しが未完了であると判定されるたびごとに、ステップS58においてパルス強度が強く段階的に設定されるため、過剰に書き戻されるメモリトランジスタの数を抑制しつつ、ステップS54の書き戻しへリファイが完了する時間を短くすることができる。

## 【0252】

## [実施の形態8]

図45は、実施の形態8の不揮発性半導体記憶装置の消去シーケンスを示したフローチャートである。

20

## 【0253】

図46は、図45のフローチャートの動作を説明するための、ワード線電位の変化を示した波形図である。

## 【0254】

図45に示したフローチャートは、図6に示したフローチャートの構成においてステップS3, S4, S20, S5に代えて、ステップS60～S65を備える点が図6に示したフローチャートと異なる。ステップS6～S10については図6に示したフローチャートと同様であり説明は繰返さない。

## 【0255】

図45、図46を参照して、消去コマンドがステップS1において入力されると、時刻t1において消去前の一括書き込みが実施される(ステップS60)。そして、時刻t2において消去パルスが印加される(ステップS61)。

30

## 【0256】

続いて、時刻t3においてステップS62の消去ベリファイのためにパルスが印加される。このパルスは4.0V程度の電位をワード線に与えるパルスである。そして、このベリファイが完了するまで繰返しステップS61の消去パルスが時刻t4～t12の間印加される。

## 【0257】

時刻t12においてステップS62の消去ベリファイにおいて消去が完了されたと判定されると、時刻t14においてステップS63の一括書き込みパルスが印加される。そして時刻t15においてステップS64の消去パルスが印加され、時刻t16においてステップS65の消去ベリファイが実施される。ステップS65の消去ベリファイにおいてはワード線の電位は3.5V程度に設定され、完全に消去されたか否かが判定される。そして時刻t17～時刻t20においてはステップS65の消去ベリファイが完了するまでステップS63、ステップS64の一括書き込みパルス、消去パルスの印加が繰返し実施されることになる。

40

## 【0258】

このような構成にすることにより、ステップS61、S62において第1回目の消去パルスによる消去を実施し、その後さらに高精度にしきい値電圧を小さくする消去動作をステップS63～S65で行なう。実施の形態8に示した消去シーケンスでも、実施の形態6

50

、7と同様に、従来に比べてしきい値電圧の分布幅を狭くしつつ消去時間を短縮することができる。

【0259】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内のすべての変更が含まれることが意図される。

【0260】

【発明の効果】

この発明のある局面における不揮発性半導体記憶装置は、消去前一括書き込みの前にブロック単位で消去パルスを印加することにより、消去パルス印加後のしきい値電圧の分布幅が狭くなるので、オーバイレースリカバーの処理がされる対象となるメモリトランジスタが少なくなり、合計の消去時間を短くすることができる。 10

【0261】

上記効果に加えて、しきい値電圧が低いメモリトランジスタをベリファイおよびリードする際に、同一ビット線上にある非選択メモリトランジスタのオフリードの総和によって生じるオーバイレースリカバーの誤動作を防ぐことができる。

【0264】

この発明の他の局面における不揮発性半導体記憶装置のデータ消去方法は、消去前一括書き込みの前にブロック単位で消去パルスを印加することにより、消去パルス印加後のしきい値電圧の分布幅が狭くなるので、オーバイレースリカバーの処理がされる対象となるメモリトランジスタが少なくなり、合計の消去時間を短くすることができる。 20

【0268】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、まず消去動作を先に完了させておき、パルス印加によって過消去状態にばらついたメモリセルの分布を狭めるので、ビットごとのオーバイレースリカバーの処理をしなければならないメモリセルの数を減らすことができ、時間短縮を図ることができる。

【0269】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、2段階にわたり消去ベリファイを行なうので、より高精度なしきい値電圧の制御が可能である。 30

【0270】

上記効果に加えて、消去パルスを最初に加える前に予備書き込みを行なうので、さらに消去時間の短縮を図ることができる。

【0271】

また、上記効果に加えて、予備書き込みパルスに対して消去パルスを与えた後に印加する書き込みパルスは、印加によって生ずるメモリトランジスタのしきい値電圧のシフト量が小さいので、より高精度なしきい値電圧の制御が可能である。

【0272】

また、上記効果に加えて、消去時に印加するパルス数を少なくできるので、さらに消去時間を短縮することができる。 40

【0273】

この発明のさらに他の局面における不揮発性半導体記憶装置のデータ消去方法は、2段階にわたり消去ベリファイを行ない、消去ベリファイ時に書き込みパルスと消去パルスを組合せて印加するので、より高精度なしきい値電圧の制御が可能である。

【図面の簡単な説明】

【図1】 本発明の不揮発性半導体記憶装置1の概略構成を示すブロック図である。

【図2】 図1の書き込み&消去制御部2が制御するフラッシュメモリの消去シーケンスを示したフローチャートである。

【図3】 図2の消去シーケンスにおいてステップS1の消去コマンド入力前のしきい値 50

電圧の分布を示した図である。

【図 4】 図 2 におけるステップ S 2 が実施された後の消去パルス印加後のメモリプロック内のしきい値電圧の分布を示した図である。

【図 5】 図 2 のステップ S 3 が終了し、消去前一括書き込みが終わった後のメモリトランジスタのしきい値分布を示した図である。

【図 6】 実施の形態 2 の不揮発性半導体記憶装置において行なわれる消去シーケンスを示したフローチャートである。

【図 7】 消去パルス印加後のしきい値電圧の分布を示した図である。

【図 8】 図 6 のステップ S 20 の一括書き込みパルスを与えた後のしきい値電圧の分布を示した図である。

【図 9】 再びステップ S 4 で消去パルスが印加された後のしきい値電圧分布を示した図である。

【図 10】 図 9 に示したしきい値電圧の分布をとっていたメモリプロックにさらにステップ S 20 の一括書き込みパルスを与え、ステップ S 5 のイレースペリファイが完了した後のメモリトランジスタのしきい値電圧の分布を示した図である。

【図 11】 実施の形態 3 においてイレースペリファイ時にメモリプロックに印加される電圧の設定を説明するための回路図である。

【図 12】 図 11 の回路図の選択されたメモリトランジスタに与えられる電位を説明するための図である。

【図 13】 実施の形態 3 におけるオーバイレースペリファイ時のメモリプロックの電圧設定を説明するための回路図である。

【図 14】 図 13 に示した選択ビットに対応するメモリトランジスタの設定電位を説明するための図である。

【図 15】 実施の形態 3 におけるリード時の電圧設定を説明するための回路図である。

【図 16】 リード時の選択ビットに対応するメモリトランジスタの設定電位を説明するための図である。

【図 17】 しきい値電圧  $V_{th}$  を 2.0 V に設定した場合のメモリトランジスタのゲート電位とドレイン電流の基板電位の依存性を示した図である。

【図 18】 図 17 の縦軸を対数表示にした図である。

【図 19】 基板電位  $V_b$  が 0 V の状態でしきい値電圧  $V_{th}$  を 2.0 V にした場合と、基板電位  $V_b$  が -1.5 V の状態でしきい値電圧  $V_{th}$  を 2.0 V にした場合のゲート電位とドレイン電流の関係を示す図である。

【図 20】 図 19 の縦軸を対数表示にした図である。

【図 21】 設定したしきい値電圧の範囲内に入れるのが困難なメモリトランジスタのしきい値電圧の変化を説明するための図である。

【図 22】 実施の形態 4 の不揮発性半導体記憶装置において行なわれる消去のシーケンスを示したフローチャートである。

【図 23】 図 22 に示したフローチャートのシーケンスによって消去する場合に、メモリトランジスタのゲート電圧すなわちワード線電位  $V_{WL}$  の変化を示した波形図である。

【図 24】 図 22 のフローチャートに従う消去シーケンスにおけるメモリトランジスタのしきい値電圧の変化を示した図である。

【図 25】 実施の形態 4 の不揮発性半導体記憶装置の消去シーケンスの変形例を示すフローチャートである。

【図 26】 図 25 のフローチャートに従った消去動作を説明するためのワード線電位の変化を示した波形図である。

【図 27】 図 26 の波形においてさらに、一括書き込みパルスを段階的に強くした場合の波形を示す図である。

【図 28】 実施の形態 5 の不揮発性半導体記憶装置における消去シーケンスを説明するためのフローチャートである。

【図 29】 図 28 のフローチャートに従い消去動作を行なった場合のワード線電位の変

10

20

30

40

50

化を示した波形図である。

【図30】 実施の形態5の変形例における消去動作を説明するためのフローチャートである。

【図31】 図30に示したフローチャートに従った消去動作を説明するためのワード線電位の変化を示す波形図である。

【図32】 図31に示した波形で表わされる消去シーケンスの変形例を示した波形図である。

【図33】 実施の形態6の不揮発性半導体記憶装置の消去シーケンスを示すフローチャートである。

【図34】 図33に示したフローチャートの動作を説明するためのワード線電位の変化を示した波形図である。 10

【図35】 図34に示したワード線電位の変化を示す波形の変形例を示した図である。

【図36】 実施の形態6の変形例の消去シーケンスを示したフローチャートである。

【図37】 図36に示したフローチャートに従う消去シーケンスの動作を説明するためにはワード線電位の変化を示した第1の波形図である。

【図38】 図36に示したフローチャートに従う消去シーケンスの第2の波形例を示した図である。

【図39】 図36のフローチャートに従う消去シーケンスの第3の波形例を示した図である。

【図40】 実施の形態7の不揮発性半導体記憶装置の消去シーケンスのフローチャートである。 20

【図41】 図40に示したフローチャートに従う消去シーケンスを説明するためのワード線電位の変化を示す波形図である。

【図42】 実施の形態7の変形例のフローチャートである。

【図43】 図42に示したフローチャートの動作を説明するために、ワード線電位の変化を示した第1の波形図である。

【図44】 図42に示したフローチャートの動作を説明するために、ワード線電位の変化を示した第2の波形図である。

【図45】 実施の形態8の不揮発性半導体記憶装置の消去シーケンスを示したフローチャートである。 30

【図46】 図45のフローチャートの動作を説明するため、ワード線電位の変化を示した波形図である。

【図47】 従来のフラッシュメモリの最もシンプルな消去シーケンスの例を示したフローチャートである。

【図48】 図47におけるステップS102で行なわれる消去パルスを与えていた時の印加電圧を説明するためのメモリブロックの回路図である。

【図49】 消去パルスが印加されている場合のメモリトランジスタに印加されている電圧を説明するための図である。

【図50】 図47に示したシーケンスにおいてステップS103で行なわれるイレースペリファイの場合に印加される電圧を説明するための回路図である。 40

【図51】 図50の選択ビットに対応したメモリトランジスタに印加される電圧を示した図である。

【図52】 従来のフラッシュメモリのリード時の電圧設定を説明するための回路図である。

【図53】 図52に示したリード時の選択されたメモリトランジスタに与えられる電位を示した図である。

【図54】 消去パルス印加前のしきい値電圧の分布を示す図である。

【図55】 図47の消去シーケンスにおいて消去パルスが印加されても、完全に全ビットのデータが消去されていない不完全な消去状態を示した図である。

【図56】 図47のステップS103においてイレースペリファイが完了した場合のし 50

きい値電圧の分布を示した図である。

【図57】 消去状態の各しきい値電圧を有するメモリトランジスタのゲート電圧とドレン電流の特性を表わした図である。

【図58】 図47で示した消去シーケンスの過消去の問題に対する対策を施したフローを示したフローチャートである。

【図59】 図58のステップS114において実行されたオーバイレースペリファイ時にメモリブロックに与えられる電圧を説明するための回路図である。

【図60】 オーバイレースペリファイ時における選択ビットに対応するメモリトランジスタに与えられる電圧を示した図である。

【図61】 図58のステップS115に示したビット毎オーバイレースリカバー時におけるメモリブロックに与える電圧を示した回路図である。 10

【図62】 図58の消去シーケンスの消去時間をさらに短縮する消去シーケンスを説明するためのフローチャートである。

【図63】 図62に示した消去シーケンスの消去時間のさらなる短縮を図ったフローチャートである。

【図64】 図63のステップS131における消去前一括書き込みを行なう場合のメモリブロックに与える電圧を説明するための回路図である。

【図65】 図64に示した消去前一括書き込み時においてメモリトランジスタに印加される電圧を説明するための図である。

【図66】 図63の消去シーケンスにおいてステップS131の消去前一括書き込みを行なう前のしきい値電圧の分布を示した図である。 20

【図67】 消去前一括書き込みをしている途中のメモリトランジスタのしきい値電圧の分布を示した図である。

【図68】 消去前一括書き込みが終了した後のしきい値電圧の分布を示した図である。

【符号の説明】

1 不揮発性半導体記憶装置、2 消去制御部、3 電圧発生部、4 正電圧発生回路、

8 電圧発生回路、12 WLブースト回路、14 ディストリビュータ、16 アドレスバッファ、18 Xデコーダ、20 Yデコーダ、22 入出力バッファ、24 Y系制御回路、26 メモリアレイ、28 セレクトゲート、BL1～BLm ビット線、BLLOCK0～BLLOCKn メモリブロック、MBL メインビット線、MT メモリトランジスタ、S1～S131 ステップ、SG セレクトゲート、SGL セレクトゲート線、SL ソース線、WL0～WLn ワード線。 30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図17】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図 5 3】

【図 5 4】

【図 5 5】

【図 5 6】

【図 5 7】

消去状態の各VthにおけるセルのVg-Vd特性

【図 5 8】

【図 5 9】

【図 6 0】

【図 6 1】

【図 6 2】

【図 6 3】

【図 6 4】

【図 6 5】

【図 6 6】

【図 6 7】

【図 6 8】

---

フロントページの続き

(72)発明者 大庭 敦

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 清水 悟

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 宮脇 好和

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 外山 賀

(56)参考文献 特開平07-122091(JP, A)

特開平11-144481(JP, A)

国際公開第98/018132(WO, A1)

特開平07-320488(JP, A)

特開2001-085546(JP, A)

特開平09-320287(JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/00-16/34