(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6514433号

(P6514433)

(45) 発行日 令和1年5月15日(2019.5.15)

(24) 登録日 平成31年4月19日(2019.4.19)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO3K 19/00   | (2006.01)  |

| HO3K 3/356   | (2006.01)  |

| GO1R 31/28   | (2006.01)  |

| HO1L 21/822  | (2006.01)  |

| HO1L 27/04   | (2006.01)  |

| HO3K 19/00   | HO3K 3/356 |

| GO1R 31/28   | GO1L 27/04 |

| HO1L 21/822  | Z E C B    |

| HO1L 27/04   | Z N M V    |

|              | T          |

請求項の数 3 (全 31 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2014-46014 (P2014-46014)    |

| (22) 出願日     | 平成26年3月10日 (2014.3.10)        |

| (65) 公開番号    | 特開2014-200081 (P2014-200081A) |

| (43) 公開日     | 平成26年10月23日 (2014.10.23)      |

| 審査請求日        | 平成29年3月3日 (2017.3.3)          |

| (31) 優先権主張番号 | 特願2013-51426 (P2013-51426)    |

| (32) 優先日     | 平成25年3月14日 (2013.3.14)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 上杉 航                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| 審査官       | 及川 尚人               |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第3の順序回路と、第1及び第2の組み合わせ回路と、第1乃至第5の記憶回路と、を有する半導体装置であって、

第1乃至第8の期間を有し、

前記第1の期間において、前記第1の記憶回路において保持されている第1のデータが前記第2の記憶回路に書き込まれ、

前記第2の期間において、前記第2の記憶回路において保持されている前記第1のデータが前記第3の記憶回路に書き込まれ、

前記第2の期間において、第2のデータが前記第1の記憶回路に書き込まれ、

前記第3の期間において、前記第3の記憶回路において保持されている前記第1のデータが前記第2の順序回路に書き込まれ、

前記第3の期間において、前記第1の記憶回路において保持されている前記第2のデータが前記第1の順序回路に書き込まれ、

前記第4の期間において、前記第2の順序回路において保持されている前記第1のデータが前記第2の組み合わせ回路に供給され、

前記第4の期間において、前記第1の順序回路において保持されている前記第2のデータが前記第1の組み合わせ回路に供給され、

前記第5の期間において、前記第2の組み合わせ回路は供給された前記第1のデータを用いて論理演算を行うことで第3のデータを出力し、前記第3のデータが前記第3の順序

10

20

回路に書き込まれ、

前記第5の期間において、前記第1の組み合わせ回路は供給された前記第2のデータを用いて論理演算を行うことで第4のデータを出力し、前記第4のデータが前記第2の順序回路に書き込まれ、

前記第6の期間において、前記第3の順序回路において保持されている前記第3のデータが前記第5の記憶回路に書き込まれ、

前記第6の期間において、前記第2の順序回路において保持されている前記第4のデータが前記第3の記憶回路に書き込まれ、

前記第7の期間において、前記第5の記憶回路において保持されている前記第3のデータが出力された後、前記第3の記憶回路において保持されている前記第4のデータが前記第4の記憶回路を介して前記第5の記憶回路に書き込まれ、 10

前記第8の期間において、前記第5の記憶回路において保持されている前記第4のデータが出力されることを特徴とする半導体装置。

**【請求項2】**

第1乃至第3の順序回路と、第1及び第2の組み合わせ回路と、第1乃至第5の記憶回路と、を有する半導体装置であって、

第1乃至第8の期間を有し、

前記第1の期間において、前記第1の記憶回路において保持されている第1のデータが前記第2の記憶回路に書き込まれ、

前記第2の期間において、前記第2の記憶回路において保持されている前記第1のデータが前記第3の記憶回路に書き込まれ、 20

前記第2の期間において、第2のデータが前記第1の記憶回路に書き込まれ、

前記第3の期間において、前記第3の記憶回路において保持されている前記第1のデータが前記第2の順序回路に書き込まれ、

前記第3の期間において、前記第1の記憶回路において保持されている前記第2のデータが前記第1の順序回路に書き込まれ、

前記第4の期間において、前記第2の順序回路において保持されている前記第1のデータが前記第2の組み合わせ回路に供給され、

前記第4の期間において、前記第1の順序回路において保持されている前記第2のデータが前記第1の組み合わせ回路に供給され、 30

前記第5の期間において、前記第2の組み合わせ回路は供給された前記第1のデータを用いて論理演算を行うことで第3のデータを出力し、前記第3のデータが前記第3の順序回路に書き込まれ、

前記第5の期間において、前記第1の組み合わせ回路は供給された前記第2のデータを用いて論理演算を行うことで第4のデータを出力し、前記第4のデータが前記第2の順序回路に書き込まれ、

前記第6の期間において、前記第3の順序回路において保持されている前記第3のデータが前記第5の記憶回路に書き込まれ、

前記第6の期間において、前記第2の順序回路において保持されている前記第4のデータが前記第3の記憶回路に書き込まれ、 40

前記第7の期間において、前記第5の記憶回路において保持されている前記第3のデータが出力された後、前記第3の記憶回路において保持されている前記第4のデータが前記第4の記憶回路を介して前記第5の記憶回路に書き込まれ、

前記第8の期間において、前記第5の記憶回路において保持されている前記第4のデータが出力され、

前記第4の記憶回路は、第1のスイッチと、第2のスイッチと、ノードと、前記ノードに電気的に接続された容量素子と、を有し、

前記第1のスイッチは、前記第3の記憶回路から出力される前記第4のデータの前記ノードへの書き込みを制御する機能を有し、

前記第2のスイッチは、前記ノードからの前記第4のデータの出力を制御する機能を有

することを特徴とする半導体装置。

【請求項 3】

請求項 2 において、

前記第 1 のスイッチ及び前記第 2 のスイッチは、トランジスタを有し、

前記トランジスタは、酸化物半導体膜を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は半導体装置に関する。例えば、本発明は、スキャンテストの実施が可能な論理回路を備えた半導体装置に関する。

10

【背景技術】

【0002】

製造された半導体装置が正常に動作するか否かを検証する手法の一つに、スキャンテストがある。スキャンテストでは、半導体装置が有する複数の順序回路を、動作の検証時において直列に接続することで、スキャンチェーンと呼ばれるシフトレジスタを形成し、当該スキャンチェーンに検証用のデータを外部入力端子から直接入力する。そして、入力されたデータに従って論理回路を動作させ、それにより論理回路から出力されたデータを、スキャンチェーンから外部出力端子を介して直接取り出すことで、論理回路の動作を検証することができる。

【0003】

20

スキャンテストを実施するためには、動作の検証時においてのみ複数の順序回路を直列に接続する必要があり、そのために、マルチプレクサが各順序回路の入力側に設けられている。マルチプレクサを設けることで、通常の動作時と、動作の検証時とで、複数の順序回路どうしの接続構造を変えることができる。下記の特許文献 1 には、マルチプレクサとスキャンフリップフロップとで構成された入力データレジスタを有する、メモリテスト回路装置について記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開平 6 - 295597 号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0005】

スキャンチェーンを構成することができる半導体装置では、その回路規模が大きくなり順序回路の数が増加すると、マルチプレクサの数も順序回路の数に付随して増加する。マルチプレクサは複数の論理ゲートで構成されているため、マルチプレクサの数が増加すると、信号が経由するゲート段数も増加する。よって、スキャンチェーンを構成することができる半導体装置では、回路規模が大きくなるほど、通常の動作時に半導体装置において生じる信号の伝搬遅延時間が長くなりやすい。

【0006】

40

上述したような技術的背景のもと、本発明の一態様は、スキャンテストの実施が可能な論理回路であって、なおかつ、信号の遅延を抑えることができる論理回路を備える半導体装置の提供を、課題の一つとする。

【課題を解決するための手段】

【0007】

本発明の一態様では、組み合わせ回路と、組み合わせ回路に供給される第 1 データ、または組み合わせ回路から出力される第 2 データを保持する複数の順序回路と、複数の順序回路のそれぞれにそれぞれが対応する複数の第 1 記憶回路とを備える。第 1 記憶回路は、対応する順序回路に供給される第 1 データを保持する機能を有する。また、第 1 記憶回路は、対応する順序回路から出力される第 2 データを、保持する機能を有する。

50

## 【0008】

さらに、本発明の一態様では、複数の第1記憶回路において、一の第1記憶回路から供給された第1データまたは第2データを、他の一の第1記憶回路に供給することで、複数の第1記憶回路を直列に電気的に接続する複数の第2記憶回路を有する。第2記憶回路は、ノードへの上記データの供給を制御する第1スイッチと、上記ノードに電気的に接続された容量素子と、上記ノードからの上記データの出力を制御する第2スイッチとを有する。

## 【0009】

本発明の一態様に係る半導体装置では、複数の第2記憶回路を介して直列に接続された複数の第1記憶回路を用いることで、動作の検証時において、複数の順序回路を直列に接続しなくとも、外部入出力端子から複数の第1記憶回路を介して、複数の順序回路に検証用の第1データを書き込むことができる。また、複数の順序回路を直列に接続しなくとも、外部入出力端子から複数の第1記憶回路を介して、複数の順序回路に保持されている検証用の第2データを読み出すことができる。よって、複数の順序回路を直列に接続するための、マルチプレクサ等の論理回路を複数の各順序回路の入力側に設けなくとも、組み合わせ回路の動作を検証することができる。そのため、通常の動作を行う場合、すなわち第1データが通常の動作に用いるデータである場合、第1データが組み合わせ回路に供給されることで、当該組み合わせ回路から出力される第2データを、マルチプレクサ等の論理回路を介さずに、順序回路に供給することができる。

## 【発明の効果】

## 【0010】

本発明の一態様により、スキャンテストの実施が可能な論理回路であって、なおかつ、信号の遅延を抑えることができる論理回路を備える半導体装置を、提供することができる。

## 【図面の簡単な説明】

## 【0011】

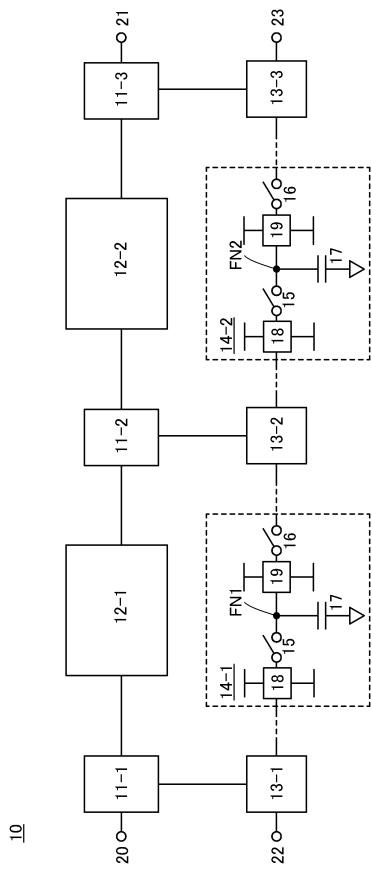

【図1】半導体装置の構成を示す図。

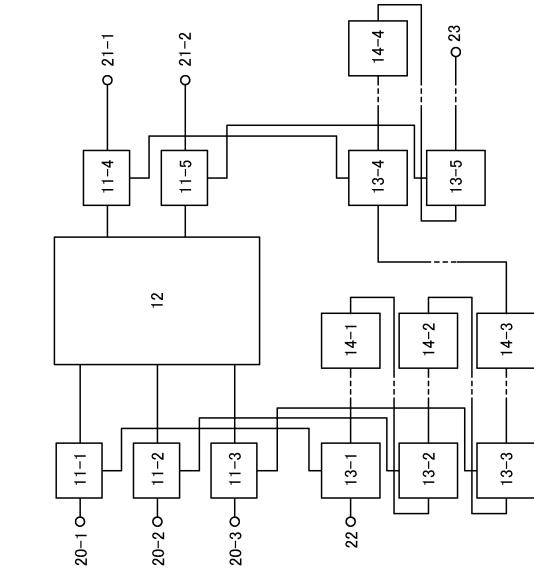

【図2】半導体装置の構成を示す図。

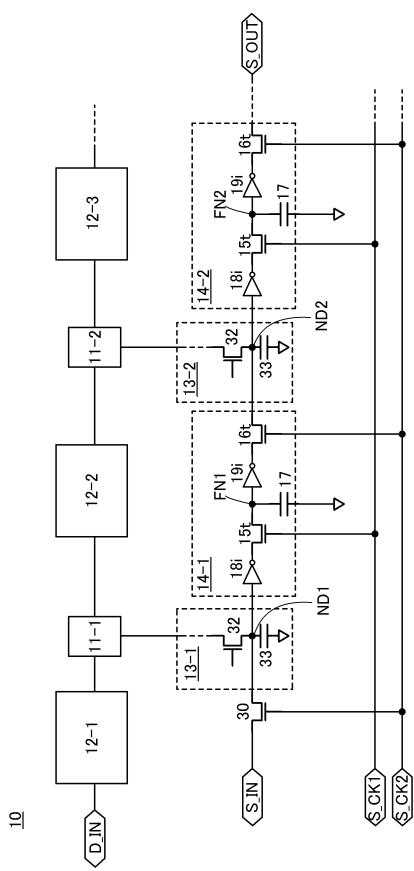

【図3】半導体装置の構成を示す図。

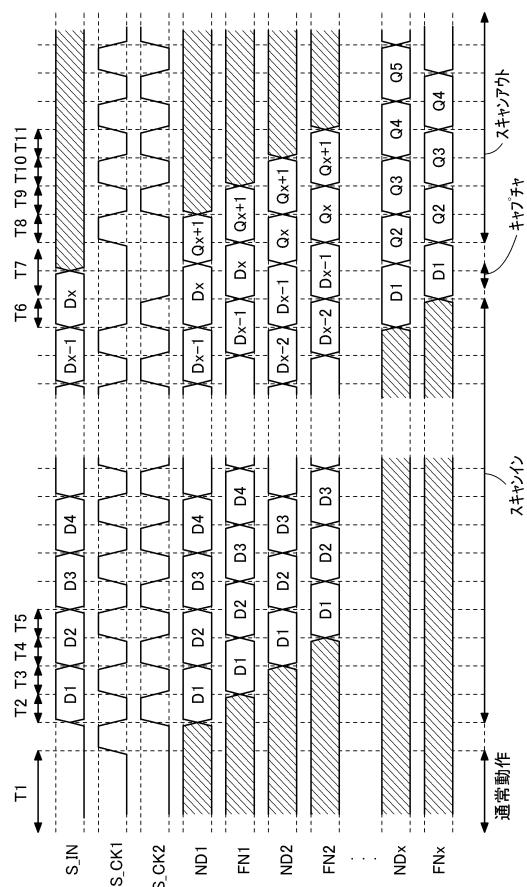

【図4】タイミングチャート。

【図5】第2記憶回路の構成を示す図。

【図6】第1記憶回路及び第2記憶回路の構成を示す図。

【図7】第2記憶回路の構成を示す図。

【図8】第1記憶回路及び第2記憶回路の構成を示す図。

【図9】半導体装置の断面図。

【図10】チップとモジュールの図。

【図11】電子機器の図。

## 【発明を実施するための形態】

## 【0012】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

## 【0013】

なお、本発明は、集積回路、RFタグ、半導体表示装置など、順序回路及び組み合わせ回路を用いたあらゆる半導体装置を、その範疇に含む。なお、集積回路には、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、マイクロコントローラを含むLSI(Large Scale Integrated Circuit)、FPGA(Field Programmable Gate Array)やCPLD(Complex PLD)などのプログラマブル論理回路(PLD:Programmable Logic Device)が、その範疇に含まれる。

10

20

30

40

50

また、半導体表示装置には、液晶表示装置、有機発光素子に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD (Digital Micromirror Device)、PDP (Plasma Display Panel)、FED (Field Emission Display) など、順序回路及び組み合わせ回路を駆動回路、コントローラなどに有する半導体表示装置が、その範疇に含まれる。

【0014】

半導体装置の構成例 1

図1に、本発明の一態様に係る半導体装置10の構成を、ブロック図で一例として示す。なお、本明細書に添付した図面では、構成要素を機能ごとに分類し、互いに独立したブロックとしてブロック図を示しているが、実際の構成要素は機能ごとに完全に切り分けることが難しく、一つの構成要素が複数の機能に係わることもあり得る。

10

【0015】

図1に示す半導体装置10は、順序回路11-1乃至順序回路11-3で例示される複数の順序回路11と、組み合わせ回路12-1及び組み合わせ回路12-2で例示される複数の組み合わせ回路12と、第1記憶回路13-1乃至第1記憶回路13-3で例示される複数の第1記憶回路13と、第2記憶回路14-1及び第2記憶回路14-2で例示される複数の第2記憶回路14（中継記憶回路ともいう）とを有する。

【0016】

順序回路11には、フリップフロップなどを用いることができる。順序回路11は、組み合わせ回路12に供給されるデータを保持する機能を有する。また、順序回路11は、組み合わせ回路12から出力されるデータを保持する機能を有する。

20

【0017】

具体的に、順序回路11-1は、組み合わせ回路12-1に供給されるデータを保持する機能を有する。順序回路11-2は、データが順序回路11-1から組み合わせ回路12-1に供給されることで、組み合わせ回路12-1から出力されるデータを、保持する機能を有する。また、順序回路11-2は、組み合わせ回路12-2に供給されるデータを保持する機能を有する。順序回路11-3は、データが順序回路11-2から組み合わせ回路12-2に供給されることで、組み合わせ回路12-2から出力されるデータを、保持する機能を有する。

【0018】

30

組み合わせ回路12は、論理ゲートを単数または複数有する論理回路であり、供給されるデータを用いて論理演算を行い、それによって得られるデータを出力する機能を有する。

【0019】

また、複数の第1記憶回路13は、複数の順序回路11にそれぞれ対応している。第1記憶回路13は、対応する順序回路11に供給されるデータを保持する機能を有する。また、第1記憶回路13は、対応する順序回路11から出力されるデータを、保持する機能を有する。

【0020】

具体的に、図1では、第1記憶回路13-1が順序回路11-1に対応しており、第1記憶回路13-2が順序回路11-2に対応しており、第1記憶回路13-3が順序回路11-3に対応している場合を例示している。そして、第1記憶回路13-1は、順序回路11-1に供給されるデータを保持する機能を有し、第1記憶回路13-2は、順序回路11-2に供給されるデータを保持する機能を有し、第1記憶回路13-3は、順序回路11-3に供給されるデータを保持する機能を有する。また、第1記憶回路13-1は、順序回路11-1から出力されるデータを保持する機能を有し、第1記憶回路13-2は、順序回路11-2から出力されるデータを保持する機能を有し、第1記憶回路13-3は、順序回路11-3から出力されるデータを保持する機能を有する。

40

【0021】

また、第2記憶回路14は、一の第1記憶回路13から供給されたデータを保持する機能と、保持したデータを、他の一の第1記憶回路13に供給する機能とを有する。半導体装

50

置 10 は、複数の第 1 記憶回路 13 間に位置する第 2 記憶回路 14 を有することで、一の第 1 記憶回路 13 に供給されるデータを、第 2 記憶回路 14 を介して、後段の第 1 記憶回路 13 に順次移すことができる。すなわち、第 2 記憶回路 14 を介して、複数の第 1 記憶回路 13 は直列に接続されることとなる。

【 0 0 2 2 】

具体的に、図 1 では、第 1 記憶回路 13 - 1 の出力側、及び第 1 記憶回路 13 - 2 の入力側に、第 2 記憶回路 14 - 1 が位置している。また、第 1 記憶回路 13 - 2 の出力側、及び第 1 記憶回路 13 - 3 の入力側に、第 2 記憶回路 14 - 2 が位置している。そして、図 1 では、第 2 記憶回路 14 - 1 は、第 1 記憶回路 13 - 1 から供給されたデータを保持する機能と、保持したデータを、第 1 記憶回路 13 - 2 に供給する機能とを有する。また、第 2 記憶回路 14 - 2 は、第 1 記憶回路 13 - 2 から供給されたデータを保持する機能と、保持したデータを、第 1 記憶回路 13 - 3 に供給する機能とを有する。よって、第 1 記憶回路 13 - 1 に供給されるデータは、第 2 記憶回路 14 - 1 または第 2 記憶回路 14 - 2 を介して、後段の第 1 記憶回路 13 - 2 または第 1 記憶回路 13 - 3 に、順次移すことができる。したがって、第 2 記憶回路 14 を介して、第 1 記憶回路 13 - 1 乃至第 1 記憶回路 13 - 3 が直列に接続されることとなる。

10

【 0 0 2 3 】

第 2 記憶回路 14 は、第 2 記憶回路 14 内のノード FN へのデータの供給を制御するスイッチ 15 と、ノード FN に電気的に接続された容量素子 17 と、ノード FN からのデータの出力を制御するスイッチ 16 と、論理ゲート 18 及び論理ゲート 19 とを有する。図 1 では、第 2 記憶回路 14 - 1 においてデータが供給されるノードを、ノード FN 1 とし、第 2 記憶回路 14 - 2 においてデータが供給されるノードを、ノード FN 2 として図示する。

20

【 0 0 2 4 】

論理ゲート 18 及び論理ゲート 19 には、ハイレベルの電位とローレベルの電位とが与えられている。そして、論理ゲート 18 及び論理ゲート 19 は、入力されたデータに従って、ハイレベルの電位またはローレベルの電位を出力することにより、入力されたデータを含む信号の電位の振幅が減衰するのを防ぐ機能を有する。例えば、論理ゲート 18 または論理ゲート 19 として、インバータ、バッファなどを用いることができる。

30

【 0 0 2 5 】

具体的に、図 1 では、スイッチ 15 が導通状態にあり、スイッチ 16 が非導通状態にあるとき、第 1 記憶回路 13 - 1 から供給されるデータは、論理ゲート 18 を通った後、スイッチ 15 を介してノード FN に供給される。次いで、スイッチ 15 が非導通状態にあり、スイッチ 16 が導通状態にあるとき、ノード FN に保持されているデータは、論理ゲート 19 を通った後、スイッチ 16 を介して後段の第 1 記憶回路 13 - 2 に供給される。

【 0 0 2 6 】

半導体装置の動作例

次いで、図 1 に示す半導体装置 10 を例に挙げて、本発明の一態様に係る半導体装置 10 の、通常の動作例と、検証の動作例とについて説明する。

40

【 0 0 2 7 】

まず、半導体装置 10 における通常の動作について説明する。通常の動作を行う場合、端子 20 から、通常の動作に用いるデータが、順序回路 11 - 1 に供給される。順序回路 11 - 1 は、供給されたデータを保持し、順序回路 11 - 1 の動作を制御するクロック信号などの信号に従って、当該データを組み合わせ回路 12 - 1 に供給する。組み合わせ回路 12 - 1 では、供給されたデータを用いて論理演算を行い、それによって得られるデータを出力する。順序回路 11 - 2 は、組み合わせ回路 12 - 1 から供給されるデータを保持し、順序回路 11 - 2 の動作を制御するクロック信号などの信号に従って、当該データを、組み合わせ回路 12 - 2 に供給する。組み合わせ回路 12 - 2 では、供給されたデータを用いて論理演算を行い、それによって得られるデータを出力する。順序回路 11 - 3 は、組み合わせ回路 12 - 2 から供給されるデータを保持し、順序回路 11 - 3 の動作を制

50

御するクロック信号などの信号に従って、当該データを端子 21 に供給する。

【0028】

次いで、半導体装置 10 における検証の動作について説明する。検証の動作を行う場合、まず、複数の第 1 記憶回路 13 への、検証用のデータの書き込み（スキャンイン）を行う。

【0029】

具体的には、端子 22 から、検証用のデータ D1 が第 1 記憶回路 13-1 に供給される。第 1 記憶回路 13-1 に供給された検証用のデータ D1 は、第 1 記憶回路 13-1 において保持される。そして、第 2 記憶回路 14-1 において、スイッチ 15 が導通状態となり、スイッチ 16 が非導通状態となり、第 1 記憶回路 13-1 から検証用のデータ D1 が、ノード FN1 に供給される。次いで、第 2 記憶回路 14-1 において、スイッチ 15 が非導通状態となり、スイッチ 16 が導通状態となり、ノード FN1 から第 1 記憶回路 13-2 に、検証用のデータ D1 が供給される。第 1 記憶回路 13-2 に供給された検証用のデータ D1 は、第 1 記憶回路 13-2 において保持される。また、第 1 記憶回路 13-2 に検証用のデータ D1 が供給されるのと並行して、端子 22 から、検証用のデータ D2 が第 1 記憶回路 13-1 に供給される。第 1 記憶回路 13-1 に供給された検証用のデータ D2 は、第 1 記憶回路 13-1 において保持される。

【0030】

次いで、複数の第 1 記憶回路 13 への検証用のデータの書き込み（スキャンイン）が終了したら、複数の第 1 記憶回路 13 に書き込まれた検証用のデータを、対応する複数の順序回路 11 にそれぞれ書き込む。

【0031】

具体的には、第 1 記憶回路 13-1 において保持されている検証用のデータ D2 が、第 1 記憶回路 13-1 に対応する順序回路 11-1 に供給される。順序回路 11-1 に供給された検証用のデータ D2 は、順序回路 11-1 において保持される。また、第 1 記憶回路 13-2 において保持されている検証用のデータ D1 が、第 1 記憶回路 13-2 に対応する順序回路 11-2 に供給される。順序回路 11-2 に供給された検証用のデータ D1 は、順序回路 11-2 において保持される。

【0032】

次いで、複数の順序回路 11 において保持されている検証用のデータが、複数の組み合わせ回路 12 にそれぞれ供給されることで、複数の組み合わせ回路 12 において検証用のデータを用いた論理演算が行われる。そして、上記論理演算によって得られた検証用のデータの、複数の順序回路 11 への書き込み（キャプチャ）が行われ、検証用のデータが複数の順序回路 11 に保持される。

【0033】

具体的には、順序回路 11-1 において保持されている検証用のデータ D2 が、組み合わせ回路 12-1 に供給され、組み合わせ回路 12-1 における論理演算によって得られた検証用のデータ Q2 が、組み合わせ回路 12-1 の後段に位置する順序回路 11-2 に書き込まれる。そして、当該データ Q2 は、順序回路 11-2 において保持される。また、上記動作と並行して、順序回路 11-2 において保持されている検証用のデータ D1 が、組み合わせ回路 12-2 に供給され、組み合わせ回路 12-2 における論理演算によって得られた検証用のデータ Q1 が、組み合わせ回路 12-2 の後段に位置する順序回路 11-3 に書き込まれる。そして、当該データ Q1 は、順序回路 11-3 において保持される。

【0034】

次いで、複数の順序回路 11 において保持されている検証用のデータが、対応する複数の第 1 記憶回路 13 にそれぞれ書き込まれる。

【0035】

具体的には、順序回路 11-2 において保持されている検証用のデータ Q2 は、第 1 記憶回路 13-2 に書き込まれ、保持される。また、順序回路 11-3 において保持されてい

10

20

30

40

50

る検証用のデータQ1は、第1記憶回路13-3に書き込まれ、保持される。

【0036】

次いで、検証用のデータの、複数の第1記憶回路13からの読み出し(スキャンアウト)を行う。

【0037】

具体的には、第1記憶回路13-3において保持されている検証用のデータQ1が、端子23に供給される。また、検証用のデータQ1が端子23に供給されるのと並行して、第2記憶回路14-2において、スイッチ15が導通状態となり、スイッチ16が非導通状態となり、第1記憶回路13-2から検証用のデータQ2が、ノードFN2に供給される。次いで、第2記憶回路14-2において、スイッチ15が非導通状態となり、スイッチ16が導通状態となり、ノードFN2から第1記憶回路13-3に、検証用のデータQ2が供給される。第1記憶回路13-3に供給された検証用のデータQ2は、第1記憶回路13-3において保持される。次いで、第1記憶回路13-3において保持されている検証用のデータQ2が、端子23に供給される。上記動作により、検証用のデータQ1及び検証用のデータQ2が、端子23から読み出される。

【0038】

本発明の一態様に係る半導体装置10では、上述したように、複数の第2記憶回路14を介して直列に接続された複数の第1記憶回路13を用いることで、複数の順序回路11を直列に接続しなくとも、複数の順序回路11に端子22を介して検証用のデータを書き込み、なおかつ、複数の順序回路11から端子23を介して検証用のデータを読み出すことができる。よって、複数の順序回路11を直列に接続するための、マルチプレクサ等の論理回路を複数の各順序回路11の入力側に設けなくとも、組み合わせ回路12の動作を検証することができる。そのため、通常の動作を行う場合、すなわちデータが通常の動作に用いるデータである場合、データが組み合わせ回路12に供給されることで、当該組み合わせ回路12から出力されるデータを、マルチプレクサ等の論理回路を介さずに、順序回路11に供給することができる。

【0039】

半導体装置の構成例2

なお、図1に示す半導体装置10では、一の組み合わせ回路12にデータを供給する順序回路と、一の組み合わせ回路12からデータが供給される順序回路とが、それぞれ一つずつである場合を例示している。しかし、本発明の一態様に係る半導体装置10では、一の組み合わせ回路12に対し、データを供給する順序回路、または一の組み合わせ回路12からデータが供給される順序回路を、複数有していても良い。

【0040】

図2に、一の組み合わせ回路12に対し、データを供給する順序回路11または一の組み合わせ回路12からデータが供給される順序回路11を複数有する、本発明の一態様に係る半導体装置10の構成を、ブロック図で一例として示す。

【0041】

図2に示す半導体装置10は、順序回路11-1乃至順序回路11-5で例示される複数の順序回路11と、組み合わせ回路12と、第1記憶回路13-1乃至第1記憶回路13-5で例示される複数の第1記憶回路13と、第2記憶回路14-1及び第2記憶回路14-4で例示される複数の第2記憶回路14とを有する。

【0042】

順序回路11-1乃至順序回路11-3は、組み合わせ回路12に供給されるデータを保持する機能を有する。順序回路11-4及び順序回路11-5は、データが順序回路11-1乃至順序回路11-3から組み合わせ回路12に供給されることで、組み合わせ回路12から出力されるデータを、保持する機能を有する。

【0043】

また、図2では、第1記憶回路13-1乃至第1記憶回路13-5が、順序回路11-1乃至順序回路11-5にそれぞれ対応している場合を例示している。そして、第1記憶回

路 13 - 1 乃至第 1 記憶回路 13 - 3 は、順序回路 11 - 1 乃至順序回路 11 - 3 に供給されるデータをそれぞれ保持する機能を有する。また、第 1 記憶回路 13 - 4 及び第 1 記憶回路 13 - 5 は、順序回路 11 - 4 及び順序回路 11 - 5 から出力されるデータをそれぞれ保持する機能を有する。

【 0 0 4 4 】

また、第 1 記憶回路 13 - 1 の出力側、及び第 1 記憶回路 13 - 2 の入力側に、第 2 記憶回路 14 - 1 が接続されている。第 1 記憶回路 13 - 2 の出力側、及び第 1 記憶回路 13 - 3 の入力側に、第 2 記憶回路 14 - 2 が接続されている。第 1 記憶回路 13 - 3 の出力側、及び第 1 記憶回路 13 - 4 の入力側に、第 2 記憶回路 14 - 3 が接続されている。第 1 記憶回路 13 - 4 の出力側、及び第 1 記憶回路 13 - 5 の入力側に、第 2 記憶回路 14 - 4 が接続されている。よって、第 2 記憶回路 14 - 1 乃至第 2 記憶回路 14 - 4 を介して、第 1 記憶回路 13 - 1 乃至第 1 記憶回路 13 - 5 が直列に接続されることとなる。 10

【 0 0 4 5 】

半導体装置の具体的な構成例

次いで、図 1 に示した半導体装置 10 のより具体的な構成を、図 3 に一例として示す。

【 0 0 4 6 】

図 3 に示す半導体装置 10 は、図 1 に示す半導体装置 10 と同様に、複数の順序回路 11 と、複数の組み合わせ回路 12 と、複数の第 1 記憶回路 13 と、複数の第 2 記憶回路 14 と、を有する。具体的に、図 3 に示す半導体装置 10 は、順序回路 11 - 1 乃至順序回路 11 - x ( x は 2 以上の自然数 ) で構成される、複数の順序回路 11 を有するものとする。また、図 3 に示す半導体装置 10 は、組み合わせ回路 12 - 1 乃至組み合わせ回路 12 - x で構成される、複数の組み合わせ回路 12 を有するものとする。また、図 3 に示す半導体装置 10 は、第 1 記憶回路 13 - 1 乃至第 1 記憶回路 13 - x で構成される、複数の第 1 記憶回路 13 を有するものとする。また、図 3 に示す半導体装置 10 は、第 2 記憶回路 14 - 1 乃至第 2 記憶回路 14 - x で構成される、複数の第 2 記憶回路 14 を有するものとする。 20

【 0 0 4 7 】

さらに、図 3 に示す半導体装置 10 は、第 1 記憶回路 13 - 1 の入力側にトランジスタ 30 を有する。トランジスタ 30 は、ゲートに入力される信号 S\_C K 2 に従って、検証用のデータを含む信号 S\_IN の、第 1 記憶回路 13 - 1 への供給を制御する機能を有する。 30

【 0 0 4 8 】

また、図 3 に示す半導体装置 10 では、通常の動作に用いるデータを含む信号 D\_IN が、組み合わせ回路 12 - 1 に供給される。

【 0 0 4 9 】

また、図 3 に示す半導体装置 10 では、第 1 記憶回路 13 がトランジスタ 32 と、容量素子 33 とを有する。トランジスタ 32 は、ノード N\_D に供給されるデータを保持する機能を有する。容量素子 33 は、ノード N\_D に供給されたデータを保持する機能を有する。

【 0 0 5 0 】

なお、図 3 では、第 1 記憶回路 13 - 1 乃至第 1 記憶回路 13 - x が、それぞれノード N\_D 1 乃至ノード N\_D x を有するものとする。 40

【 0 0 5 1 】

また、図 3 に示す半導体装置 10 では、スイッチ 15 として機能するトランジスタ 15\_t と、スイッチ 16 として機能するトランジスタ 16\_t と、容量素子 17 と、論理ゲート 18 として機能するインバータ 18\_i と、論理ゲート 19 として機能するインバータ 19\_i とを、第 2 記憶回路 14 に有する。トランジスタ 15\_t は、ゲートに入力される信号 S\_C K 1 に従って、導通状態または非導通状態が選択される。トランジスタ 16\_t は、ゲートに入力される信号 S\_C K 2 に従って、導通状態または非導通状態が選択される。そして、第 1 記憶回路 13 から供給されるデータは、インバータ 18\_i を通った後、トランジスタ 15\_t を介してノード F\_N に与えられる。また、ノード F\_N から、データが、インバ 50

ータ 19 i を通った後、トランジスタ 16 t を介して後段の第 1 記憶回路 13 に供給される。

【0052】

半導体装置 10 に用いられるトランジスタは、非晶質、微結晶、多結晶または单結晶である、シリコン又はゲルマニウムなどの半導体膜にチャネル形成領域を有することができる。或いは、半導体装置 10 に用いられるトランジスタは、酸化物半導体膜にチャネル形成領域を有していても良い。

【0053】

なお、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体膜に、チャネル形成領域が形成されるトランジスタは、オフ電流が著しく小さい。このような半導体としては、例えば、シリコンの 2 倍以上の大きなバンドギャップを有する、酸化物半導体、窒化ガリウムなどが挙げられる。上記半導体を有するトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流を極めて小さくすることができる。よって、上記構成を有するトランジスタ 15 t またはトランジスタ 16 t を第 2 記憶回路 14 に用いることで、第 2 記憶回路 14 において、ノード FN におけるデータの保持時間を、長く確保することができる。

【0054】

なお、特に断りがない限り、本明細書でオフ電流とは、遮断領域においてトランジスタのソースとドレイン間に流れる電流を意味する。

【0055】

半導体装置の具体的な動作例

次いで、図 3 に示す半導体装置 10 の動作例について、図 4 に示すタイミングチャートを用いて説明する。

【0056】

まず、半導体装置 10 では、期間 T1 において通常の動作が行われる。期間 T1 では、図 4 に示すように、信号 S\_IN、信号 S\_CK1、及び信号 S\_CK2 は、全てその電位がローレベルとなる。よって、トランジスタ 30、トランジスタ 15 t、及びトランジスタ 16 t は非導通状態である。

【0057】

なお、期間 T1 において、ノード ND1 乃至ノード NDx と、ノード FN1 乃至ノード FNx とでは、その電位のレベルが特に定まっていない。図 4 に示すタイミングチャートでは、電位が定まっていない期間を斜線で示す。

【0058】

次いで、半導体装置 10 ではスキャンインの動作が行われるものとする。スキャンインでは、まず、期間 T2 において、信号 S\_CK1 の電位がローレベル、信号 S\_CK2 の電位がハイレベルとなる。よって、トランジスタ 30、及びトランジスタ 16 t は導通状態となり、トランジスタ 15 t は非導通状態を維持する。そして、検証用のデータ D1 を含む信号 S\_IN が、トランジスタ 30 を介して、第 1 記憶回路 13-1 のノード ND1 に入力される。

【0059】

次いで、期間 T3 において、信号 S\_CK1 の電位がハイレベル、信号 S\_CK2 の電位がローレベルとなる。よって、トランジスタ 30、及びトランジスタ 16 t は非導通状態となり、トランジスタ 15 t は導通状態となる。そして、検証用のデータ D1 を含む信号 S\_IN は、ノード ND1 からインバータ 18 i 及びトランジスタ 15 t を介して、第 2 記憶回路 14-1 のノード FN1 に入力される。

【0060】

なお、信号 S\_IN の電位は、インバータ 18 i によりその極性が反転する。よって、実際には、ノード ND1 に供給される信号 S\_IN の電位と、ノード FN1 に供給される信号 S\_IN の電位とは、その極性が互いに反転している。

【0061】

10

20

30

40

50

次いで、期間T4において、信号S\_CK1の電位がローレベル、信号S\_CK2の電位がハイレベルとなる。よって、トランジスタ30、及びトランジスタ16tは導通状態となり、トランジスタ15tは非導通状態となる。そして、検証用のデータD2を含む信号S\_INが、トランジスタ30を介して、第1記憶回路13-1のノードND1に入力される。また、検証用のデータD1を含む信号S\_INは、ノードFN1からインバータ19i及びトランジスタ16tを介して、第1記憶回路13-1のノードND2に入力される。

#### 【0062】

次いで、期間T5において、信号S\_CK1の電位がハイレベル、信号S\_CK2の電位がローレベルとなる。よって、トランジスタ30、及びトランジスタ16tは非導通状態となり、トランジスタ15tは導通状態となる。そして、検証用のデータD2を含む信号S\_INは、ノードND1からインバータ18i及びトランジスタ15tを介して、第2記憶回路14-1のノードFN1に入力される。また、検証用のデータD1を含む信号S\_INは、ノードND2からインバータ18i及びトランジスタ15tを介して、第2記憶回路14-2のノードFN2に入力される。

10

#### 【0063】

上記期間T2乃至期間T5と同様の動作を繰り返すことで、最終的には期間T6に示すように、検証用のデータDx-1乃至データD1が、第1記憶回路13-1乃至第1記憶回路13-(x-1)が有するノードND1乃至ノードND(x-1)に、それぞれ供給される。すなわち、期間T2から始まったスキャンインの動作は、期間T6において完了することとなる。

20

#### 【0064】

次いで、期間T7において、キャプチャの動作を行う。具体的に、期間T7では、信号S\_CK1の電位がローレベル、信号S\_CK2の電位がローレベルとなる。よって、トランジスタ30、トランジスタ15t、及びトランジスタ16tは非導通状態となる。そして、第1記憶回路13から検証用のデータが順序回路11に書き込まれた後、組み合わせ回路12から出力される検証用のデータを、後段の順序回路11に書き込むことで、キャプチャの動作を行う。次いで、順序回路11から第1記憶回路13に、検証用のデータを書き込む。

#### 【0065】

30

なお、図4に示すタイミングチャートでは、検証用のデータDx乃至データD2が、組み合わせ回路12-2乃至組み合わせ回路12-xにそれぞれ供給されることで、検証用のデータQx乃至データQ2が、ノードND2乃至ノードNDxに、それぞれ供給される場合を例示している。

#### 【0066】

また、組み合わせ回路12-1には、信号D\_INが入力される端子から、別途、検証用のデータDx+1を含む信号S\_INを供給すれば良い。上記動作により、図4に示すように、ノードND1には検証用のデータQx+1が供給される。

#### 【0067】

40

なお、図4では、期間T7が、信号S\_CK1及び信号S\_CK2の1周期よりも短い場合を例示しているが、期間T7の長さは、信号S\_CK1及び信号S\_CK2をローレベルとする期間の長さを調整することで、適宜設定することができる。

#### 【0068】

次いで、半導体装置10ではスキャンアウトの動作が行われるものとする。スキャンアウトでは、まず、期間T8において、信号S\_CK1の電位がハイレベル、信号S\_CK2の電位がローレベルとなる。よって、トランジスタ30、及びトランジスタ16tは非導通状態となり、トランジスタ15tは導通状態となる。そして、検証用のデータQx+1乃至データQ2を含む信号S\_OUTは、ノードND1乃至ノードNDxからインバータ18i及びトランジスタ15tを介して、ノードFN1乃至ノードFNxにそれぞれ入力される。

50

## 【0069】

次いで、期間T9において、信号S\_CK1の電位がロー・レベル、信号S\_CK2の電位がハイ・レベルとなる。よって、トランジスタ30、及びトランジスタ16tは導通状態となり、トランジスタ15tは非導通状態となる。そして、検証用のデータQ<sub>x+1</sub>乃至データQ<sub>3</sub>を含む信号S\_OUTは、ノードFN1乃至ノードFN<sub>x-1</sub>から、インバータ19i及びトランジスタ16tを介して、ノードND2乃至ノードND<sub>x</sub>にそれぞれ入力される。また、検証用のデータQ<sub>2</sub>を含む信号S\_OUTは、インバータ19i及びトランジスタ16tを介して、半導体装置10から出力される。

## 【0070】

次いで、期間T10において、信号S\_CK1の電位がハイ・レベル、信号S\_CK2の電位がロー・レベルとなる。よって、トランジスタ30、及びトランジスタ16tは非導通状態となり、トランジスタ15tは導通状態となる。そして、検証用のデータQ<sub>x+1</sub>乃至データQ<sub>3</sub>を含む信号S\_OUTは、ノードND2乃至ノードND<sub>x</sub>からインバータ18i及びトランジスタ15tを介して、ノードFN2乃至ノードFN<sub>x</sub>にそれぞれ入力される。

10

## 【0071】

次いで、期間T11において、信号S\_CK1の電位がロー・レベル、信号S\_CK2の電位がハイ・レベルとなる。よって、トランジスタ30、及びトランジスタ16tは導通状態となり、トランジスタ15tは非導通状態となる。そして、検証用のデータQ<sub>x+1</sub>乃至データQ<sub>4</sub>を含む信号S\_OUTは、ノードFN2乃至ノードFN<sub>x-1</sub>から、インバータ19i及びトランジスタ16tを介して、ノードND3乃至ノードND<sub>x</sub>にそれぞれ入力される。また、検証用のデータQ<sub>3</sub>を含む信号S\_OUTは、インバータ19i及びトランジスタ16tを介して、半導体装置10から出力される。

20

## 【0072】

上記期間T8乃至期間T11と同様の動作を繰り返すことで、最終的には検証用のデータQ<sub>x+1</sub>乃至データQ<sub>2</sub>を、全て半導体装置10から出力し、スキャンアウトの動作を完了させることができる。

## 【0073】

## 第1記憶回路及び順序回路の構成例1

次いで、第1記憶回路13の具体的な構成例について説明する。

30

## 【0074】

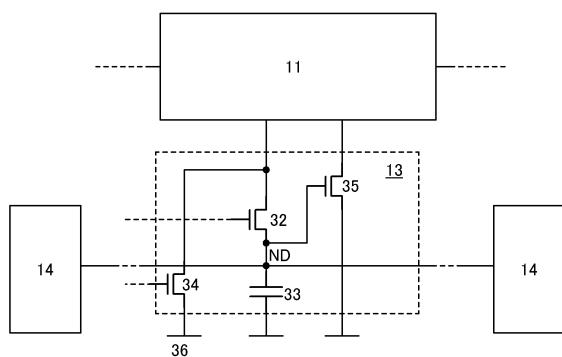

図5に、順序回路11、第1記憶回路13、及び第2記憶回路14の、接続構造を一例として示す。

## 【0075】

第1記憶回路13は、容量素子33及びトランジスタ32に加えて、トランジスタ34及びトランジスタ35を有する。トランジスタ32は、ノードNDに供給されるデータを保持する機能を有する。容量素子33は、ノードNDに供給されたデータを保持する機能を有する。トランジスタ35は、ノードNDに保持されているデータに従って、導通状態または非導通状態が選択される。トランジスタ34は、トランジスタ32が導通状態であるときに、配線36の電位をノードNDに供給する機能を有する。また、ノードNDは、第2記憶回路14に接続されている。

40

## 【0076】

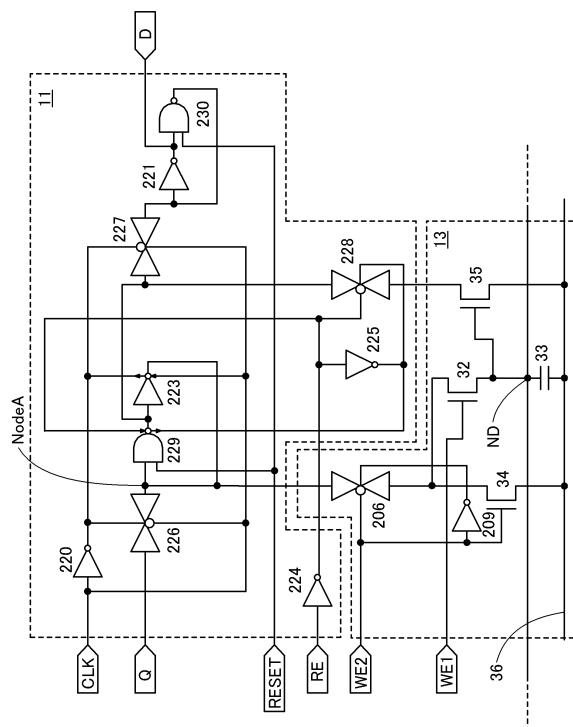

次いで、図6に、図5に示した順序回路11と、第1記憶回路13の、より具体的な構成例を示す。

## 【0077】

順序回路11は、インバータ220及びインバータ221と、インバータ223乃至インバータ225と、トランスマッシュゲート226乃至トランスマッシュゲート228と、NAND229及びNAND230を有する。また、第1記憶回路13は、トランジスタ32、トランジスタ35、容量素子33、トランスマッシュゲート206、トランジスタ34、及びインバータ209を有する。

50

## 【0078】

インバータ220は、クロック信号C L Kの電位の極性を反転させたクロック信号C L K bを、生成する機能を有する。そして、トランスマッショングート226、227は、クロック信号C L K及びクロック信号C L K bに従って、導通状態または非導通状態が選択され、インバータ223は、クロック信号C L K及びクロック信号C L K bに従って、信号の出力の有無が選択される。

## 【0079】

具体的に、トランスマッショングート226は、クロック信号C L Kの電位がL（ローレベル）、クロック信号C L K bの電位がH（ハイレベル）のとき、トランスマッショングート226の入力端子に供給された、通常の動作に用いるデータQまたは検証用のデータQを、NAND229の第1入力端子、及び、第1記憶回路13が有するトランスマッショングート206の入力端子に供給する機能を有する。また、トランスマッショングート226は、クロック信号C L Kの電位がH、クロック信号C L K bの電位がLのとき、ハイインピーダンスとなり、NAND229の第1入力端子、及び、第1記憶回路13が有するトランスマッショングート206の入力端子への、上記データQの供給を停止する機能を有する。

10

## 【0080】

また、具体的に、トランスマッショングート227は、クロック信号C L Kの電位がH、クロック信号C L K bの電位がLのとき、NAND229の出力端子から入力された信号及びトランスマッショングート228の出力端子から入力された検証用のデータDを、インバータ221の入力端子に供給する機能を有する。また、トランスマッショングート227は、クロック信号C L Kの電位がL、クロック信号C L K bの電位がHのとき、NAND229の出力端子から入力された信号またはトランスマッショングート228の出力端子から入力された検証用のデータDの、インバータ221の入力端子への供給を停止する機能を有する。

20

## 【0081】

また、インバータ224は、信号R Eの電位の極性を反転させた信号R E bを、生成する機能を有する。また、インバータ225は、信号R E bの電位の極性を反転させて、信号R Eを生成する機能を有する。そして、トランスマッショングート228、及びNAND229のそれぞれは、信号R E及び信号R E bに従って、信号の出力の有無が選択される。

30

## 【0082】

具体的に、トランスマッショングート228は、信号R Eの電位がH、信号R E bの電位がLのとき、第1記憶回路13から出力される検証用のデータDを、トランスマッショングート227の入力端子、及び、インバータ223の入力端子に供給する機能を有する。また、トランスマッショングート228は、信号R Eの電位がL、信号R E bの電位がHのとき、ハイインピーダンスとなり、第1記憶回路13から出力される検証用のデータDの、トランスマッショングート227の入力端子、及び、インバータ223の入力端子への供給を停止する機能を有する。

40

## 【0083】

NAND229は2入力のNANDであり、第1入力端子にトランスマッショングート226から出力されるデータQが供給され、第2入力端子に信号R E S E Tが供給される。そして、NAND229は、信号R Eの電位がL、信号R E bの電位がHのとき、第1入力端子及び第2入力端子に入力された信号に従って、信号を出力する機能を有する。また、NAND229は、信号R Eの電位がH、信号R E bの電位がLのとき、第1入力端子及び第2入力端子に入力される信号に関わらず、信号の出力を停止する機能を有する。

## 【0084】

インバータ223は、クロック信号C L Kの電位がH、クロック信号C L K bの電位がLのとき、入力端子に供給された信号が有する電位の極性を反転させて、出力する機能を有する。出力された信号は、NAND229の第1入力端子に供給される。

50

## 【0085】

インバータ221は、トランスマッシュゲート227の出力端子、及びNAND230の出力端子から供給される信号の電位を反転させ、通常の動作に用いるデータDまたは検証用のデータDとして出力する機能を有する。また、インバータ221から出力される上記データDは、NAND230の第1入力端子に供給される。

## 【0086】

NAND230は2入力のNANDであり、第1入力端子にインバータ221から出力されるデータDが供給され、第2入力端子に信号RESETが供給される。

## 【0087】

トランジスタ32は、信号WE1の電位に従って、導通状態または非導通状態が選択される。また、トランスマッシュゲート206は、信号WE2に従って、導通状態または非導通状態が選択される。具体的に、図6では、トランスマッシュゲート206は、信号WE2と、信号WE2の極性がインバータ209により反転させられることで得られる信号により、導通状態または非導通状態が選択される。トランジスタ34は、信号WE2により、導通状態または非導通状態が選択される。10

## 【0088】

トランスマッシュゲート206及びトランジスタ32が導通状態であるとき、順序回路11が有するノードAに保持されている検証用のデータQが、ノードNDに供給される。また、ノードNDには、動作の検証時において、第2記憶回路14から検証用のデータDが供給される。また、トランジスタ32及びトランジスタ34が導通状態であるとき、配線36の電位が、ノードNDに供給される。20

## 【0089】

トランジスタ35は、ノードNDの電位に従って、導通状態または非導通状態が制御される。トランジスタ35が導通状態のとき、配線36の電位がトランジスタ35を介して順序回路11に与えられる。容量素子33は、トランジスタ32が非導通状態にあるとき、ノードNDの電位を保持する機能を有する。

## 【0090】

順序回路11及び第1記憶回路13に用いられるトランジスタは、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜にチャネル形成領域を有することができる。或いは、順序回路11及び第1記憶回路13に用いられるトランジスタは、酸化物半導体膜にチャネル形成領域を有していても良い。30

## 【0091】

なお、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体膜に、チャネル形成領域が形成されるトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流を極めて小さくすることができる。このような半導体としては、例えば、シリコンの2倍以上の大きなバンドギャップを有する、酸化物半導体、窒化ガリウムなどが挙げられる。よって、上記構成を有するトランジスタ32を第1記憶回路13に用いることで、第1記憶回路13において、ノードNDにおけるデータの保持時間を、長く確保することができる。

## 【0092】

トランジスタ32に酸化物半導体膜を用い、トランジスタ32以外のトランジスタはシリコン膜を用い、トランジスタ32及び容量素子33は、シリコン膜を用いたトランジスタ上に積層することで、第1記憶回路13の面積を小さく抑えることができる。40

## 【0093】

## 第1記憶回路及び順序回路の構成例2

次いで、第1記憶回路13の、別の具体的な構成例について説明する。

## 【0094】

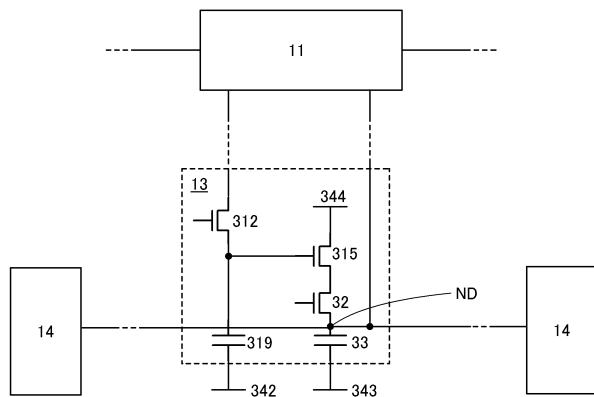

図7に、順序回路11、第1記憶回路13、及び第2記憶回路14の、接続構造を一例として示す。

## 【0095】

トランジスタ312は、順序回路11に保持されている、通常の動作に用いるデータQまたは検証用のデータQを、容量素子319に供給する機能を有する。また、トランジスタ315は、容量素子319に供給されたデータQに従って導通状態または非導通状態が選択される。トランジスタ32は、トランジスタ315が導通状態であるときに、配線344の電位を容量素子33に供給する機能を有する。なお、ノードNDには、容量素子319に対するデータQの供給に先立って、前段の第2記憶回路14から配線344の電位とは異なる電位が供給されている。例えば、配線344の電位がハイレベルの電位であれば、前段の第2記憶回路14からローレベルの電位を供給すればよい。この場合、データQに応じてノードNDの電位が選択される。すなわち、ノードNDには、データQが保持されることになる。

10

#### 【0096】

具体的に、トランジスタ312のソース及びドレインの一方は、順序回路11に接続されている。また、トランジスタ312のソース及びドレインの他方は、容量素子319の一方の電極、及びトランジスタ315のゲートに接続されている。容量素子319の他方の電極は、配線342に接続されている。トランジスタ315のソース及びドレインの一方は、配線344に接続されている。トランジスタ315のソース及びドレインの他方は、トランジスタ32のソース及びドレインの一方に接続されている。トランジスタ32のソース及びドレインの他方は、容量素子33の一方の電極、及び順序回路11に接続されている。容量素子33の他方の電極は、配線343に接続されている。

20

#### 【0097】

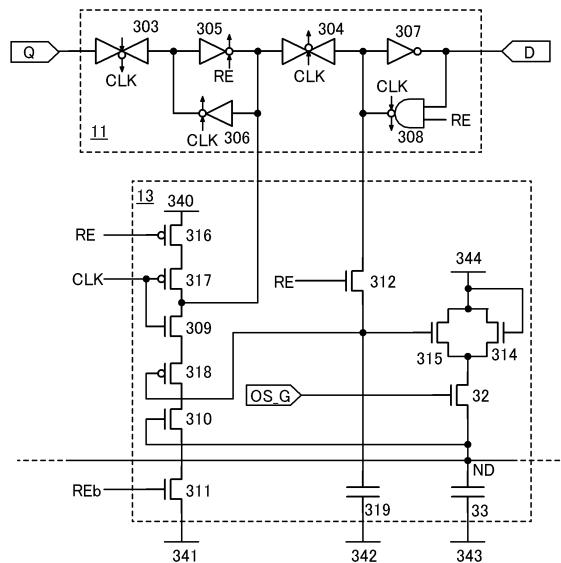

次いで、図8に、図7に示した順序回路11と、第1記憶回路13の、より具体的な構成例を示す。

#### 【0098】

順序回路11は、トランスマッシュョンゲート303、トランスマッシュョンゲート304、インバータ305乃至インバータ307、及びNAND308を有する。なお、順序回路11は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子をさらに有していても良い。

30

#### 【0099】

トランスマッシュョンゲート303は、クロック信号CLKに従って、信号の出力の有無が選択される。具体的に、トランスマッシュョンゲート303は、クロック信号CLKの電位がローレベルのときに、通常の動作に用いるデータQまたは検証用のデータQをインバータ305の入力端子に供給する機能を有する。また、トランスマッシュョンゲート303は、クロック信号CLKの電位がハイレベルのときにハイインピーダンスとなり、インバータ305の入力端子への、上記データQの供給を停止する機能を有する。

#### 【0100】

インバータ305は、信号REに従って信号の出力の有無が選択される。具体的に、インバータ305は、信号REの電位がハイレベルのときに、入力端子に供給された電位の極性を反転させた信号を、トランスマッシュョンゲート304の入力端子、及びインバータ306の入力端子に、供給する機能を有する。また、インバータ305は、信号REの電位がローレベルのときにトランスマッシュョンゲート304の入力端子、及びインバータ306の入力端子への、信号の供給を停止する機能を有する。

40

#### 【0101】

インバータ306は、クロック信号CLKに従って信号の出力の有無が選択される。具体的に、インバータ306は、クロック信号CLKの電位がハイレベルのときに、入力端子に供給された電位の極性を反転させた信号を、インバータ305の入力端子に供給する機能を有する。また、インバータ306は、クロック信号CLKの電位がローレベルのときにインバータ305の入力端子への、信号の供給を停止する機能を有する。

#### 【0102】

トランスマッシュョンゲート304は、クロック信号CLKに従って、信号の出力の有無が選択される。具体的に、トランスマッシュョンゲート304は、クロック信号CLKの電位

50

がハイレベルのときに、入力端子に供給された信号をインバータ307の入力端子に供給する機能を有する。また、トランスマッシュゲート304は、クロック信号CLKの電位がローレベルのときにハイインピーダンスとなり、インバータ307の入力端子への、信号の供給を停止する機能を有する。

【0103】

インバータ307は、入力端子に供給された電位の極性を反転させることで得られる、通常の動作に用いるデータDを、NAND308の第1入力端子に供給する機能を有する。

【0104】

NAND308は2入力のNANDであり、クロック信号CLKに従って信号の出力の有無が選択される。また、NAND308は、第2入力端子に信号REが供給される。具体的に、NAND308は、クロック信号CLKの電位がローレベルのとき、第1入力端子及び第2入力端子に入力された信号に従って、インバータ307の入力端子に信号を供給する機能を有する。また、NAND308は、クロック信号CLKの電位がハイレベルのとき、第1入力端子及び第2入力端子に入力される信号に関わらず、信号の出力を停止する機能を有する。

10

【0105】

また、第1記憶回路13は、nチャネル型のトランジスタ312及び容量素子319と、nチャネル型のトランジスタ32、トランジスタ314、及びトランジスタ315と、容量素子33とを有する。さらに、第1記憶回路13は、nチャネル型のトランジスタ309乃至トランジスタ311と、pチャネル型のトランジスタ316乃至トランジスタ318とを有する。なお、第1記憶回路13は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子をさらに有していても良い。

20

【0106】

トランジスタ316、トランジスタ317、トランジスタ309、トランジスタ318、トランジスタ310、及びトランジスタ311は、電位V2が与えられる配線340と、電位V1が与えられる配線341との間ににおいて、順に直列に接続されている。具体的に、トランジスタ316のソース及びドレインは、一方が配線340に、他方がトランジスタ317のソース及びドレインの一方に接続されている。トランジスタ317のソース及びドレインの他方は、トランジスタ309のソース及びドレインの一方に接続されている。トランジスタ309のソース及びドレインの他方は、トランジスタ318のソース及びドレインの一方に接続されている。トランジスタ318のソース及びドレインの他方は、トランジスタ310のソース及びドレインの一方に接続されている。トランジスタ310のソース及びドレインの他方は、トランジスタ311のソース及びドレインの一方に接続されている。トランジスタ311のソース及びドレインの他方は、配線341に接続されている。

30

【0107】

トランジスタ316のゲート及びトランジスタ312のゲートには信号REが供給され、トランジスタ311のゲートには信号REの電位の極性を反転させることで得られる信号REbが供給される。また、トランジスタ317のゲートと、トランジスタ309のゲートには、クロック信号CLKが供給される。トランジスタ32のゲートには、信号OS\_Gが供給される。

40

【0108】

また、トランジスタ318のゲートは、トランジスタ312のソース及びドレインの他方と、トランジスタ315のゲートと、容量素子319の一方の電極とに接続されている。容量素子319の他方の電極は、電位V1が与えられる配線342に接続されている。

【0109】

また、トランジスタ310のゲートは、トランジスタ32のソース及びドレインの他方と、容量素子33の一方の電極、すなわちノードNDに接続されている。容量素子33の他方の電極は、電位V1が与えられる配線343に接続されている。ノードNDには、動作の検証時において、第2記憶回路14から検証用のデータDが供給される。

50

## 【0110】

なお、配線340と、配線344とは、接続されても良い。また、配線341と、配線342と、配線343とは、接続されても良い。

## 【0111】

トランジスタ315のソース及びドレインの一方は、電位V2の与えられる配線344と、トランジスタ314のソース及びドレインの一方と、トランジスタ314のゲートとともに接続されている。トランジスタ315のソース及びドレインの他方は、トランジスタ32のソース及びドレインの一方と、トランジスタ314のソース及びドレインの他方とともに接続されている。

## 【0112】

10

そして、順序回路11が有する、インバータ305の出力端子、トランスマッシュゲート304の入力端子、及びインバータ306の入力端子は、トランジスタ317のソース及びドレインの他方と、トランジスタ309のソース及びドレインの一方とに接続されている。

## 【0113】

また、順序回路11が有する、トランスマッシュゲート304の出力端子、インバータ307の入力端子、及びNAND308の出力端子は、第1記憶回路13が有するトランジスタ312のソース及びドレインの一方に接続されている。

## 【0114】

20

順序回路11及び第1記憶回路13に用いられるトランジスタは、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜にチャネル形成領域を有することができる。或いは、順序回路11及び第1記憶回路13に用いられるトランジスタは、酸化物半導体膜にチャネル形成領域を有しても良い。

## 【0115】

30

なお、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体膜に、チャネル形成領域が形成されるトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流を極めて小さくすることができる。このような半導体としては、例えば、シリコンの2倍以上の大きなバンドギャップを有する、酸化物半導体、窒化ガリウムなどが挙げられる。よって、上記構成を有するトランジスタ32を第1記憶回路13に用いることで、第1記憶回路13において、ノードNDにおけるデータの保持時間を、長く確保することができる。

## 【0116】

トランジスタ32に酸化物半導体膜を用い、トランジスタ32以外のトランジスタはシリコン膜を用い、トランジスタ32及び容量素子33は、シリコン膜を用いたトランジスタ上に積層することで、第1記憶回路13の面積を小さく抑えることができる。

## 【0117】

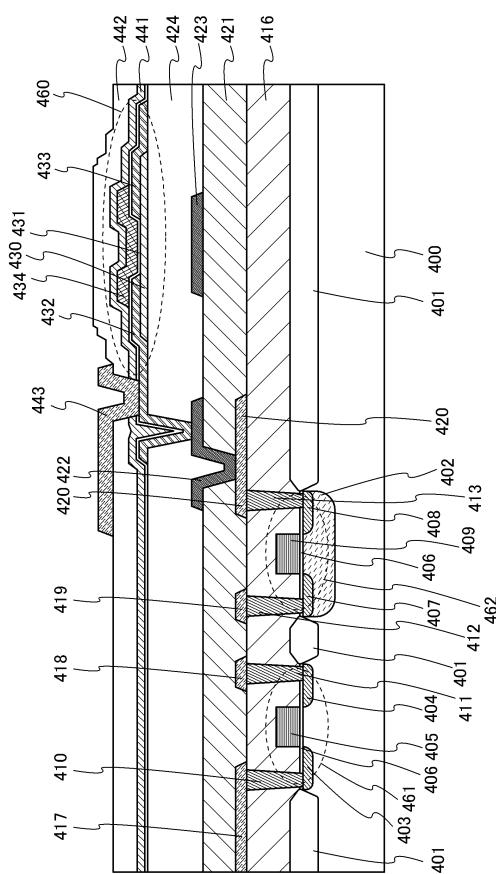

## 半導体装置の断面構造

次いで、本発明の一態様に係る半導体装置の、断面構造の一例について説明する。

## 【0118】

40

図9に、本発明の一態様に係る半導体装置の断面構造の一部を、一例として示す。なお、図9では、酸化物半導体膜にチャネル形成領域を有するトランジスタ460と、シリコン基板にチャネル形成領域を有するpチャネル型トランジスタ461及びnチャネル型トランジスタ462とを図示している。

## 【0119】

また、本実施の形態では、pチャネル型トランジスタ461及びnチャネル型トランジスタ462が、単結晶のシリコン基板に形成され、酸化物半導体膜を用いたトランジスタ460がpチャネル型トランジスタ461及びnチャネル型トランジスタ462上に形成されている場合を例示している。pチャネル型トランジスタ461及びnチャネル型トランジスタ462は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの薄膜の半導体膜を用いていても良い。或いは、pチャネル型トランジスタ461

50

及びnチャネル型トランジスタ462は、酸化物半導体膜を用いていても良い。全てのトランジスタが酸化物半導体膜を用いている場合、トランジスタ460はpチャネル型トランジスタ461及びnチャネル型トランジスタ462上に積層されていなくとも良く、同一の絶縁表面上に全てのトランジスタが形成されていても良い。

【0120】

なお、薄膜のシリコンを用いてpチャネル型トランジスタ461及びnチャネル型トランジスタ462を形成する場合、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

10

【0121】

図9では、半導体基板400にpチャネル型トランジスタ461及びnチャネル型トランジスタ462が形成されている。

【0122】

半導体基板400は、例えば、n型またはp型の導電型を有する単結晶シリコン基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、ZnSe基板等)等を用いることができる。図9では、n型の導電性を有する単結晶シリコン基板を用いた場合を例示している。

【0123】

また、pチャネル型トランジスタ461とnチャネル型トランジスタ462とは、素子分離用絶縁膜401により、電気的に分離されている。素子分離用絶縁膜401の形成には、選択酸化法(LOCOS(Local Oxidation of Silicon)法)またはトレンチ分離法等を用いることができる。

20

【0124】

nチャネル型トランジスタ462が形成される領域には、p型の導電性を付与する不純物元素を選択的に導入することにより、pウェル402を形成する。

【0125】

具体的に、pチャネル型トランジスタ461は、半導体基板400と、半導体基板400に形成されたソース領域またはドレイン領域として機能する不純物領域403及び不純物領域404と、ゲート電極405と、半導体基板400とゲート電極405の間に設けられたゲート絶縁膜406とを有する。ゲート電極405は、ゲート絶縁膜406を間に挟んで、不純物領域403と不純物領域404の間に形成されるチャネル形成領域と重なる。

30

【0126】

また、nチャネル型トランジスタ462は、半導体基板400と、半導体基板400に形成されたソース領域またはドレイン領域として機能する不純物領域407及び不純物領域408と、ゲート電極409と、半導体基板400とゲート電極409の間に設けられたゲート絶縁膜406とを有する。ゲート電極409は、ゲート絶縁膜406を間に挟んで、不純物領域407と不純物領域408の間に形成されるチャネル形成領域と重なる。

【0127】

pチャネル型トランジスタ461及びnチャネル型トランジスタ462上には、絶縁膜416が設けられている。絶縁膜416には開口部が形成されており、上記開口部に、不純物領域403、不純物領域404、不純物領域407、及び不純物領域408にそれぞれ接する配線410乃至配線413が形成されている。

40

【0128】

そして、配線410は、絶縁膜416上に形成された配線417に接続されており、配線411は、絶縁膜416上に形成された配線418に接続されており、配線412は、絶縁膜416上に形成された配線419に接続されており、配線413は、絶縁膜416上に形成された配線420に接続されている。

【0129】

50

配線 417 乃至配線 420 上には、絶縁膜 421 が形成されている。絶縁膜 421 には開口部が形成されており、絶縁膜 421 上には、上記開口部において配線 420 に接続された配線 422 と、配線 423 とが形成されている。また、配線 422 及び配線 423 上には、絶縁膜 424 が形成されている。

## 【0130】

そして、図 9 では、絶縁膜 424 上にトランジスタ 460 が形成されている。

## 【0131】

トランジスタ 460 は、絶縁膜 424 上に、酸化物半導体を含む半導体膜 430 と、半導体膜 430 上の、ソース電極またはドレイン電極として機能する導電膜 432 及び導電膜 433 と、半導体膜 430 、導電膜 432 及び導電膜 433 上のゲート絶縁膜 431 と、導電膜 432 と導電膜 433 の間ににおいて、ゲート絶縁膜 431 を間に挟んで半導体膜 430 と重なっているゲート電極 434 と、を有する。

10

## 【0132】

そして、導電膜 432 は、絶縁膜 424 に設けられた開口部において、配線 422 に接続されている。

## 【0133】

また、配線 423 は、絶縁膜 424 を間に挟んで半導体膜 430 と重なる位置に設けられている。配線 423 は、トランジスタ 460 のバックゲートとしての機能を有する。配線 423 は、必ずしも設ける必要はない。

20

## 【0134】

トランジスタ 460 上には、絶縁膜 441 及び絶縁膜 442 が、順に積層するように設けられている。絶縁膜 441 は、絶縁膜 442 から放出された水素が半導体膜 430 に侵入するのを防ぐ機能を有する、窒化珪素などを用いた絶縁膜であることが望ましい。

## 【0135】

絶縁膜 441 、絶縁膜 442 、及びゲート絶縁膜 431 には開口部が設けられており、上記開口部において導電膜 432 に接する導電膜 443 が、絶縁膜 441 上に設けられている。

## 【0136】

## 半導体膜について

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、i型（真性半導体）又はi型に限りなく近い。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。

30

## 【0137】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が  $1 \times 10^6 \mu\text{m}$  でチャネル長が  $10 \mu\text{m}$  の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が  $1\text{V}$  から  $10\text{V}$  の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13} \text{ A}$  以下という特性を得ることができる。この場合、トランジスタのチャネル幅で規格化したオフ電流は、 $100 \text{ zA} / \mu\text{m}$  以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が  $3\text{V}$  の場合に、数十  $\text{yA} / \mu\text{m}$  という、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。

40

## 【0138】

50

なお、半導体膜として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジウム (In) あるいは亜鉛 (Zn) を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム (Ga) を有することが好ましい。また、スタビライザーとしてスズ (Sn) を有することが好ましい。また、スタビライザーとしてハフニウム (Hf) を有することが好ましい。また、スタビライザーとしてアルミニウム (Al) を有することが好ましい。また、スタビライザーとしてジルコニウム (Zr) を含むことが好ましい。

#### 【0139】

酸化物半導体の中でも In - Ga - Zn 系酸化物、In - Sn - Zn 系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記 In - Ga - Zn 系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

10

#### 【0140】

また、他のスタビライザーとして、ランタノイドである、ランタン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) のいずれか一種または複数種を含んでいてもよい。

20

#### 【0141】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In - Zn 系酸化物、Sn - Zn 系酸化物、Al - Zn 系酸化物、Zn - Mg 系酸化物、Sn - Mg 系酸化物、In - Mg 系酸化物、In - Ga 系酸化物、In - Ga - Zn 系酸化物 (IGZOとも表記する)、In - Al - Zn 系酸化物、In - Sn - Zn 系酸化物、Sn - Ga - Zn 系酸化物、Al - Ga - Zn 系酸化物、Sn - Al - Zn 系酸化物、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物、In - Sn - Ga - Zn 系酸化物、In - Hf - Ga - Zn 系酸化物、In - Al - Ga - Zn 系酸化物、In - Sn - Al - Zn 系酸化物、In - Sn - Hf - Zn 系酸化物、In - Hf - Al - Zn 系酸化物を用いることができる。

30

#### 【0142】

なお、例えば、In - Ga - Zn 系酸化物とは、In と Ga と Zn を含む酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素を含んでいてもよい。In - Ga - Zn 系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

40

#### 【0143】

例えば、In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3) あるいは In : Ga : Zn = 2 : 2 : 1 (= 2 / 5 : 2 / 5 : 1 / 5) の原子比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In : Sn : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)、In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2) あるいは In : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8) の原子比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0144】

例えば、In - Sn - Zn 系酸化物では比較的容易に高い移動度が得られる。しかしながら、In - Ga - Zn 系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

50

## 【0145】

以下では、酸化物半導体膜の構造について説明する。

## 【0146】

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、C A A C - O S ( C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜などをいう。

## 【0147】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。 10

## 【0148】

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

## 【0149】

C A A C - O S 膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100 nm未満の立方体内に収まる大きさである。従って、C A A C - O S 膜に含まれる結晶部は、一辺が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。C A A C - O S 膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、C A A C - O S 膜について詳細な説明を行う。 20

## 【0150】

C A A C - O S 膜を透過型電子顕微鏡（T E M : T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ）によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、C A A C - O S 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0151】

C A A C - O S 膜を、試料面と概略平行な方向からT E Mによって観察（断面T E M観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C A A C - O S 膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、C A A C - O S 膜の被形成面または上面と平行に配列する。 30

## 【0152】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

## 【0153】

一方、C A A C - O S 膜を、試料面と概略垂直な方向からT E Mによって観察（平面T E M観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。 40

## 【0154】

断面T E M観察および平面T E M観察より、C A A C - O S 膜の結晶部は配向性を有していることがわかる。

## 【0155】

C A A C - O S 膜に対し、X線回折（X R D : X - R a y D i f f r a c t i o n ）装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するC A A C - O S 膜のout-of-plane法による解析では、回折角（2θ）が31°近傍にピークが 50

現れる場合がある。このピークは、 $InGaZnO_4$  の結晶の(009)面に帰属されることから、 $CAAC-OS$  膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【0156】

一方、 $CAAC-OS$  膜に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$  の結晶の(110)面に帰属される。 $InGaZnO_4$  の単結晶酸化物半導体膜であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、(110)面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、 $CAAC-OS$  膜の場合は、 $2\theta$  を  $56^\circ$  近傍に固定してスキャンした場合でも、明瞭なピークが現れない。10

【0157】

以上のことから、 $CAAC-OS$  膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

【0158】

なお、結晶部は、 $CAAC-OS$  膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、 $CAAC-OS$  膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、 $CAAC-OS$  膜の形状をエッティングなどによって変化させた場合、結晶の c 軸が  $CAAC-OS$  膜の被形成面または上面の法線ベクトルと平行にならないこともある。20

【0159】

また、 $CAAC-OS$  膜中の結晶化度が均一でなくてもよい。例えば、 $CAAC-OS$  膜の結晶部が、 $CAAC-OS$  膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、 $CAAC-OS$  膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

【0160】

なお、 $InGaZnO_4$  の結晶を有する $CAAC-OS$  膜の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、 $CAAC-OS$  膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。 $CAAC-OS$  膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。30

【0161】

$CAAC-OS$  膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【0162】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、 $CAAC-OS$  膜のうち、二種以上を有する積層膜であってもよい。40

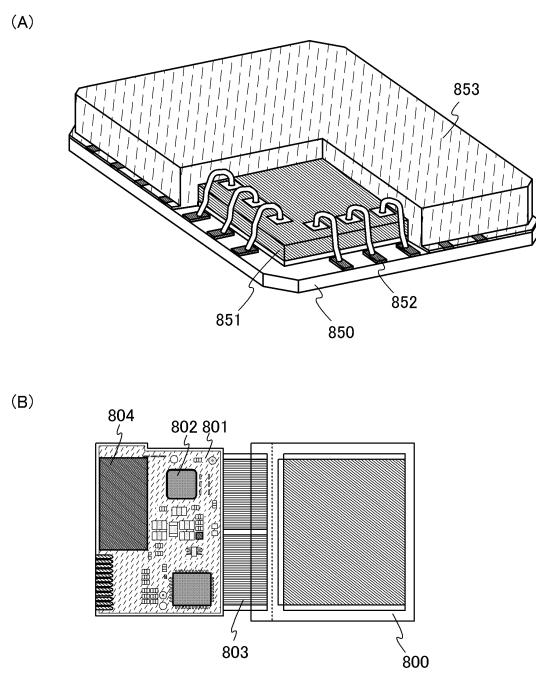

【0163】

チップの構成

図 10 (A) に、リードフレーム型のインターポーラを用いたパッケージの断面構造を表す斜視図を示す。

【0164】

図 10 (A) に示すパッケージは、本発明の一態様にかかる半導体装置に相当するチップ 851 が、ワイヤボンディング法により、インターポーラ 850 上の端子 852 と接続されている。端子 852 は、インターポーラ 850 のチップ 851 がマウントされている面上に配置されている。そしてチップ 851 はモールド樹脂 853 によって封止されている。そしてチップ 851 はモールド樹脂 853 によって封止されても良いが、各端子 852 の一部が露出した状態で封止されるようにする。50

## 【0165】

パッケージが回路基板に実装されている電子機器のモジュールの構成を、図10（B）に示す。

## 【0166】

図10（B）に示す携帯電話のモジュールは、プリント配線基板801に、パッケージ802と、バッテリー804とが実装されている。また、表示素子が設けられたパネル800に、プリント配線基板801がFPC803によって実装されている。

## 【0167】

## 電子機器の例

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図11に示す。

10

## 【0168】

図11（A）は携帯型ゲーム機であり、筐体5001、筐体5002、表示部5003、表示部5004、マイクロフォン5005、スピーカー5006、操作キー5007、スタイルス5008等を有する。なお、図11（A）に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

20

## 【0169】

図11（B）は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602との間の角度は、接続部5605により変更が可能である。第1表示部5603における映像を、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としても良い。また、第1表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

30

## 【0170】

図11（C）はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。

40

## 【0171】

図11（D）は電気冷凍冷蔵庫であり、筐体5301、冷蔵室用扉5302、冷凍室用扉5303等を有する。

## 【0172】

図11（E）はビデオカメラであり、第1筐体5801、第2筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。操作キー5804及びレンズ5805は第1筐体5801に設けられており、表示部5803は第2筐体5802に設けられている。そして、第1筐体5801と第2筐体5802とは、接続部5806により接続されており、第1筐体5801と第2筐体5802との間の角度は、接続部5806により変更が可能である。表示部5803における映像を、接続部5806

50

における第1筐体5801と第2筐体5802との間の角度に従って切り替える構成としても良い。

【0173】

図11(F)は普通自動車であり、車体5101、車輪5102、ダッシュボード5103、ライト5104等を有する。

【符号の説明】

【0174】

|        |         |    |

|--------|---------|----|

| 10     | 半導体装置   |    |

| 11     | 順序回路    |    |

| 11 - x | 順序回路    | 10 |

| 11 - 1 | 順序回路    |    |

| 11 - 2 | 順序回路    |    |

| 11 - 3 | 順序回路    |    |

| 11 - 4 | 順序回路    |    |

| 11 - 5 | 順序回路    |    |

| 12     | 組み合わせ回路 |    |

| 12 - 1 | 組み合わせ回路 |    |

| 12 - 2 | 組み合わせ回路 |    |

| 12 - x | 組み合わせ回路 |    |

| 13     | 第1記憶回路  | 20 |

| 13 - 1 | 第1記憶回路  |    |

| 13 - 2 | 第1記憶回路  |    |

| 13 - 3 | 第1記憶回路  |    |

| 13 - 4 | 第1記憶回路  |    |

| 13 - 5 | 第1記憶回路  |    |

| 13 - x | 第1記憶回路  |    |

| 14     | 第2記憶回路  |    |

| 14 - 1 | 第2記憶回路  |    |

| 14 - 2 | 第2記憶回路  |    |

| 14 - 3 | 第2記憶回路  | 30 |

| 14 - 4 | 第2記憶回路  |    |

| 14 - x | 第2記憶回路  |    |

| 15     | スイッチ    |    |

| 15 t   | トランジスタ  |    |

| 16     | スイッチ    |    |

| 16 t   | トランジスタ  |    |

| 17     | 容量素子    |    |

| 18     | 論理ゲート   |    |

| 18 i   | インバータ   |    |

| 19     | 論理ゲート   | 40 |

| 19 i   | インバータ   |    |

| 20     | 端子      |    |

| 21     | 端子      |    |

| 22     | 端子      |    |

| 23     | 端子      |    |

| 30     | トランジスタ  |    |

| 32     | トランジスタ  |    |

| 33     | 容量素子    |    |

| 34     | トランジスタ  |    |

| 35     | トランジスタ  | 50 |

|       |              |    |

|-------|--------------|----|

| 3 6   | 配線           |    |

| 2 0 6 | トランスマッショングート |    |

| 2 0 9 | インバータ        |    |

| 2 2 0 | インバータ        |    |

| 2 2 1 | インバータ        |    |

| 2 2 3 | インバータ        |    |

| 2 2 4 | インバータ        |    |

| 2 2 5 | インバータ        |    |

| 2 2 6 | トランスマッショングート | 10 |

| 2 2 7 | トランスマッショングート |    |

| 2 2 8 | トランスマッショングート |    |

| 2 2 9 | N A N D      |    |

| 2 3 0 | N A N D      |    |

| 3 0 3 | トランスマッショングート |    |

| 3 0 4 | トランスマッショングート |    |

| 3 0 5 | インバータ        |    |

| 3 0 6 | インバータ        |    |

| 3 0 7 | インバータ        |    |

| 3 0 8 | N A N D      |    |

| 3 0 9 | トランジスタ       | 20 |

| 3 1 0 | トランジスタ       |    |

| 3 1 1 | トランジスタ       |    |

| 3 1 2 | トランジスタ       |    |

| 3 1 4 | トランジスタ       |    |

| 3 1 5 | トランジスタ       |    |

| 3 1 6 | トランジスタ       |    |

| 3 1 7 | トランジスタ       |    |

| 3 1 8 | トランジスタ       |    |

| 3 1 9 | 容量素子         |    |

| 3 4 0 | 配線           | 30 |

| 3 4 1 | 配線           |    |

| 3 4 2 | 配線           |    |

| 3 4 3 | 配線           |    |

| 3 4 4 | 配線           |    |

| 4 0 0 | 半導体基板        |    |

| 4 0 1 | 素子分離用絶縁膜     |    |

| 4 0 2 | p ウェル        |    |

| 4 0 3 | 不純物領域        |    |

| 4 0 4 | 不純物領域        |    |

| 4 0 5 | ゲート電極        | 40 |

| 4 0 6 | ゲート絶縁膜       |    |

| 4 0 7 | 不純物領域        |    |

| 4 0 8 | 不純物領域        |    |

| 4 0 9 | ゲート電極        |    |

| 4 1 0 | 配線           |    |

| 4 1 1 | 配線           |    |

| 4 1 2 | 配線           |    |

| 4 1 3 | 配線           |    |

| 4 1 6 | 絶縁膜          |    |

| 4 1 7 | 配線           | 50 |

|         |               |    |

|---------|---------------|----|

| 4 1 8   | 配線            |    |

| 4 1 9   | 配線            |    |

| 4 2 0   | 配線            |    |

| 4 2 1   | 絶縁膜           |    |

| 4 2 2   | 配線            |    |

| 4 2 3   | 配線            |    |

| 4 2 4   | 絶縁膜           |    |

| 4 3 0   | 半導体膜          |    |

| 4 3 1   | ゲート絶縁膜        |    |

| 4 3 2   | 導電膜           | 10 |

| 4 3 3   | 導電膜           |    |

| 4 3 4   | ゲート電極         |    |

| 4 4 1   | 絶縁膜           |    |

| 4 4 2   | 絶縁膜           |    |

| 4 4 3   | 導電膜           |    |

| 4 6 0   | トランジスタ        |    |

| 4 6 1   | p チャネル型トランジスタ |    |

| 4 6 2   | n チャネル型トランジスタ |    |

| 8 0 0   | パネル           |    |

| 8 0 1   | プリント配線基板      | 20 |

| 8 0 2   | パッケージ         |    |

| 8 0 3   | F P C         |    |

| 8 0 4   | バッテリー         |    |

| 8 5 0   | インターポーラ       |    |

| 8 5 1   | チップ           |    |

| 8 5 2   | 端子            |    |

| 8 5 3   | モールド樹脂        |    |

| 5 0 0 1 | 筐体            |    |

| 5 0 0 2 | 筐体            |    |

| 5 0 0 3 | 表示部           | 30 |

| 5 0 0 4 | 表示部           |    |

| 5 0 0 5 | マイクロフォン       |    |

| 5 0 0 6 | スピーカー         |    |

| 5 0 0 7 | 操作キー          |    |

| 5 0 0 8 | スタイラス         |    |

| 5 1 0 1 | 車体            |    |

| 5 1 0 2 | 車輪            |    |

| 5 1 0 3 | ダッシュボード       |    |

| 5 1 0 4 | ライト           |    |

| 5 3 0 1 | 筐体            | 40 |

| 5 3 0 2 | 冷蔵室用扉         |    |

| 5 3 0 3 | 冷凍室用扉         |    |

| 5 4 0 1 | 筐体            |    |

| 5 4 0 2 | 表示部           |    |

| 5 4 0 3 | キー ボード        |    |

| 5 4 0 4 | ポインティングデバイス   |    |

| 5 6 0 1 | 筐体            |    |

| 5 6 0 2 | 筐体            |    |

| 5 6 0 3 | 表示部           |    |

| 5 6 0 4 | 表示部           | 50 |

|         |      |

|---------|------|

| 5 6 0 5 | 接続部  |

| 5 6 0 6 | 操作キー |

| 5 8 0 1 | 筐体   |

| 5 8 0 2 | 筐体   |

| 5 8 0 3 | 表示部  |

| 5 8 0 4 | 操作キー |

| 5 8 0 5 | レンズ  |

| 5 8 0 6 | 接続部  |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 义 7 】

【 図 8 】

【図9】

【図10】

## 【図 1 1】

---

フロントページの続き

(56)参考文献 特開2005-300308(JP,A)

特開2000-022503(JP,A)

特開2010-135762(JP,A)

特開2003-255025(JP,A)

特開平05-110392(JP,A)

特開2004-012374(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00-19/096

G01R 31/28

H01L 21/822

H01L 27/04

H03K 3/356