**(12) STANDARD PATENT**

**(19) AUSTRALIAN PATENT OFFICE**

**(11) Application No. AU 2012300694 C1**

(54) Title

**Photovoltaic device**

(51) International Patent Classification(s)

**H01L 31/0328** (2006.01)      **H01L 31/028** (2006.01)

**H01L 29/861** (2006.01)      **H01L 31/0725** (2012.01)

**H01L 29/88** (2006.01)

(21) Application No: **2012300694**      (22) Date of Filing: **2012.08.14**

(87) WIPO No: **WO13/030531**

(30) Priority Data

(31) Number      (32) Date      (33) Country

**61/528,650**      **2011.08.29**      **US**

(43) Publication Date: **2013.03.07**

(44) Accepted Journal Date: **2015.10.22**

(44) Amended Journal Date: **2016.04.21**

(71) Applicant(s)

**IQE Plc.**

(72) Inventor(s)

**Johnson, Andrew;Nelson, Andrew William;Harper, Robert Cameron**

(74) Agent / Attorney

**FB Rice, Level 23 44 Market Street, Sydney, NSW, 2000**

(56) Related Art

**US2008/0257405**

**WO2010/102345**

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

7 March 2013 (07.03.2013)

WIPO | PCT

(10) International Publication Number

WO 2013/030531 A1

(51) International Patent Classification:

*H01L 31/0328* (2006.01) *H01L 29/861* (2006.01)

*H01L 31/0725* (2012.01) *H01L 29/88* (2006.01)

*H01L 31/028* (2006.01)

(21) International Application Number:

PCT/GB2012/051982

(22) International Filing Date:

14 August 2012 (14.08.2012)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/528,650 29 August 2011 (29.08.2011) US

(71) Applicant (for all designated States except US): IQE PLC. [GB/GB]; Pascal Close, St Mellons, Cardiff, Wales CF3 0LW (GB).

(72) Inventors; and

(75) Inventors/Applicants (for US only): **JOHNSON, Andrew** [GB/GB]; 27 Priory Way, Langstone, Newport, Wales NP18 2JE (GB). **NELSON, Andrew William** [GB/GB]; Llansannor House, City, Cowbridge, Vale of Glamorgan, Wales CF71 7RW (GB). **HARPER, Robert Cameron** [GB/GB]; 6 Beacons Close, Manor Chase, Rogerstone, Newport, Wales NP10 9AX (GB).

(74) Agent: **LEGG, Cyrus James Grahame**; Abel & Imray, 20 Red Lion Street, London, Greater London WC1R 4PQ (GB).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: PHOTOVOLTAIC DEVICE

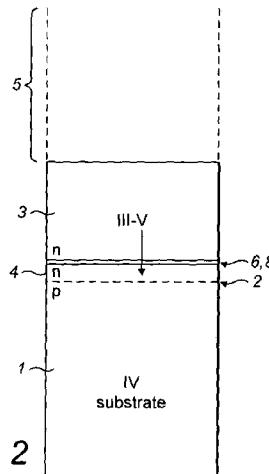

FIG. 2

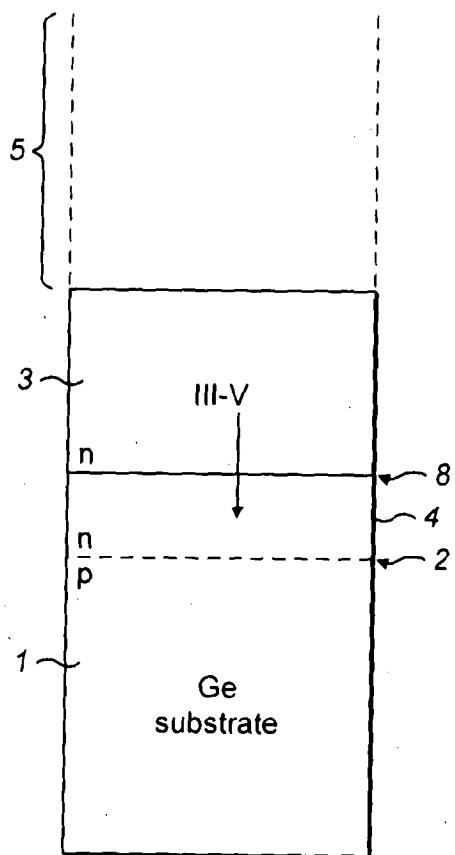

FIG. 11

(57) Abstract: A photovoltaic device comprises an interface (8) between a layer of Group III-V material (3) and a layer of Group IV material (1) with a thin silicon diffusion barrier (6) provided at or near the interface. The silicon barrier controls the diffusion of Group V atoms into the Group IV material, which is doped n-type thereby. The n-type doped region can provide the p-n junction of a solar cell in the Group IV material with superior solar cell properties. It can also provide a tunnel diode in contact with a p-type region of the III-V material, which tunnel diode is also useful in solar cells. In another aspect, a multijunction photovoltaic device is provided in which there are at least a first light-absorbing layer (111) of SiGe or SiGeSn and a second light-absorbing layer (112) of SiGeSn, both layers being lattice-matched to GaAs.

WO 2013/030531 A1

## PHOTOVOLTAIC DEVICE

The present disclosure relates to photovoltaic devices, including solar cells.

### BACKGROUND INFORMATION

One well-known kind of photovoltaic device has two or more cells connected in series formed from a vertical layer structure of semiconductor materials, each cell containing a p-n junction of a different bandgap, which junctions are used to absorb different parts of the spectrum of the light falling on the device (Tandem Cell). The majority of multi-junction photovoltaic devices that are currently in use are manufactured on a germanium substrate.

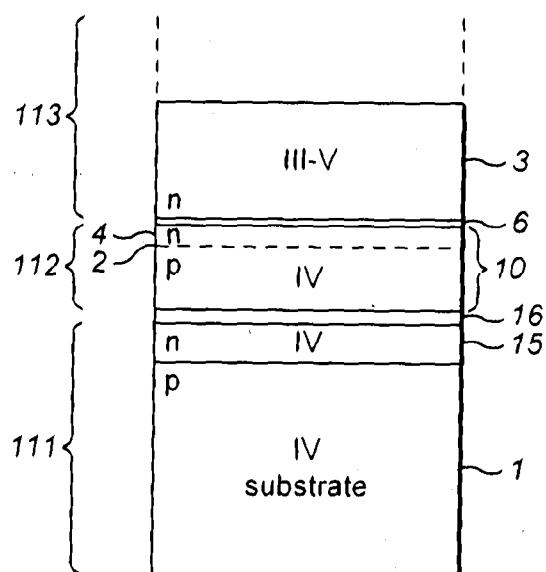

Figure 1 shows the typical structure of the lower cell in such a device. A p-type germanium (Ge) substrate 1 is provided and the first p-n junction 2 of the device is fabricated by growing a layer 3 of a III-V semiconductor material onto the germanium substrate, the two meeting at interface 8. This layer 3 is termed, in the art, a nucleation layer. At the elevated temperatures used during processing, Group V atoms from the nucleation layer 3 diffuse across the interface into the germanium substrate creating the p-n junction 2 at a point below the surface of the germanium. The junction forms because the Group V atoms act as an n-type dopant in the germanium and so when they have diffused in sufficient concentration an n-type region 4 is formed. (The other border of the n-type region 4 is of course the interface 8 between the III-V and the Group IV materials.) The Group III-V layer 3 is provided n-type so that there is low resistance contact between that and the Group IV n-type region 4. Control of the depth of the diffusion of the Group

V atoms is important in defining the quality of the p-n junction, with a shallower junction being preferable. Diffusion is controlled by the temperature and duration of the growth and annealing (and any other processing) of both the nucleation layer 3 of any further semiconductor layers 5. The further layers 5 of semiconductor are provided to form one or more further p-n junctions for absorbing different parts of the spectrum. Examples of multi-junction solar cells having a bottom cell similar to Figure 1 are given by US 6,380,601 and US 2002/0040727.

A paper *Si as a diffusion barrier in Ge/GaAs heterojunctions* by S. Strite, M.S. Ünlü, K. Adomi, and H. Morkoç (Appl. Phys Lett. 56(17)) was published in 1990. The authors of this paper were interested in phototransistors and hole based modulation doped structures, and the paper itself discussed their investigation of a diode formed of a gallium arsenide epitaxial layer overgrown with germanium. This basic diode was said to suffer from microplasma assisted breakdown caused by poor sample uniformity caused, they suggest, by vacancies in the GaAs (caused in turn by Ga and As outdiffusion into the Ge). An interlayer of pseudomorphic silicon of 10Å in thickness was provided to prevent this. (The germanium was p-type, being doped with Ga to a concentration of  $5 \times 10^{18} \text{ cm}^{-3}$ . The GaAs at the junction was more lightly doped, to a concentration of  $5 \times 10^{16} \text{ cm}^{-3}$ , with silicon.) In particular it may be controlled to a predetermined depth.

Solar cells are used to generate electrical power, preferably from sunlight. They may be used directly irradiated by the sun or with concentrators that gather sunlight onto the cell in a higher concentration, which improves their efficiency.

Any discussion of documents, acts, materials, devices, articles or the like which has been included in the present specification is not to be taken as an admission that any or all of these matters form part of the prior art base or were common general knowledge in the field relevant to the present disclosure as it existed before the priority date of each claim of this application.

#### **SUMMARY OF THE PRESENT DISCLOSURE**

Throughout this specification the word "comprise", or variations such as "comprises" or "comprising", will be understood to imply the inclusion of a stated element, integer or step, or group of elements, integers or steps, but not the exclusion of any other element, integer or step, or group of elements, integers or steps.

According to embodiments of the present disclosure, there is provided a semiconductor material comprising:

a Group IV semiconductor material layer, the material not being silicon,

a layer of Group III-V semiconductor material formed of at least one kind of Group III atoms and at least one kind of Group V atoms, and having an interface with the Group IV semiconductor layer,

a silicon layer either at the interface between III-V semiconductor layer and the Group IV semiconductor material layer, or in either the Group IV semiconductor material layer, or the III-V semiconductor layer, spaced from the interface to control the diffusion of the Group V atoms into the Group IV semiconductor material layer,

an n-type Group V doped region in the Group IV semiconductor layer that has a border with the interface and that is doped by Group V atoms of at least one of the kinds of those forming the Group III-V semiconductor layer.

As mentioned above, the silicon layer acts to control the diffusion of the Group V atoms into the Group IV layer (by reducing it), and hence controls the doping of the Group IV layer in terms of its depth and concentration. Further changing the thickness of the Si layer allows doping to be changed for different requirements. In this way the doping of the Group IV layer can be controlled as desired.

That part of the n-type Group V doped region in the Group IV semiconductor layer that is to a particular side of the silicon layer may be doped by Group V atoms of at least one of the kinds of those forming that part the Group III-V semiconductor that is on the opposite side of the silicon layer.

At least some of the Group V atoms doping that part of the Group IV semiconductor layer that is to a particular side of the silicon layer may be from that part of the Group III-V layer that is on the opposite side of the silicon layer.

The n-type Group V doped region in the Group IV semiconductor layer may be doped by Group V atoms of at least one of the kinds of those forming a region of the Group III-V semiconductor layer that borders the interface.

The Group V doped region in the semiconductor layer may provide a p-n junction with a p-type region in the Group IV layer.

The Group III-V material at the interface may be n-type.

The Group III-V material layer may be n-type.

Alternatively, the Group V doped region in the Group IV layer and the Group III-V layer may form a tunnel diode at the interface. The Group III-V material at the interface may be p-doped.

The Group IV semiconductor material layer may be germanium, or may be silicon-germanium, or may be silicon-germanium-tin.

The Group III-V material may comprise Group III atoms that are one or more of Al, Ga, In and may comprise Group V atoms that are one or more or P, As, Sb, Bi. The Group III-V material may comprise a material selected from the group consisting of InGaAsP, AlGaAs, AlGaAsP, GaAs, GaAsP, AlAs, InGaP, InGaAs, AlInGaAs, AlInGaP.

The Group IV layer may comprise an epitaxial Group IV semiconductor layer between the silicon layer and the III-V semiconductor layer.

The Group III-V semiconductor layer may comprise an epitaxial Group III-V semiconductor layer between the silicon layer and the Group IV semiconductor layer.

The Group IV semiconductor layer may comprise a substrate layer and an epitaxial layer grown on the substrate layer.

The silicon layer may have a thickness of less than or equal to 7.5 Å or may have less than or equal to 3 atomic layers. The silicon may have less than or equal to 1 atomic layer, or may have less than 1 atomic layer.

The concentration of the doping of the Group III-V semiconductor layer bordering the interface may be greater than  $1 \times 10^{17}$  atoms per  $\text{cm}^3$ , or may be greater than  $1 \times 10^{18}$  atoms per  $\text{cm}^3$ , or may be between than  $1 \times 10^{18}$  and  $5 \times 10^{18}$  atoms per  $\text{cm}^3$ .

The concentration of the Group V atoms of the doping of the n-type Group V doped region in the Group IV semiconductor layer may be greater than  $1 \times 10^{17}$  atoms per  $\text{cm}^3$ , or may be greater than  $1 \times 10^{18}$  atoms per  $\text{cm}^3$ , or may be greater than  $6 \times 10^{18}$  atoms per  $\text{cm}^3$ .

The doping concentration of the Group IV layer not doped by the Group V atoms may be less than  $4 \times 10^{18}$  atoms per  $\text{cm}^3$ , or may be between  $5 \times 10^{16}$  and  $2 \times 10^{18}$  atoms per  $\text{cm}^3$ , or may be between  $1 \times 10^{17}$  and  $1 \times 10^{18}$  atoms per  $\text{cm}^3$ .

The semiconductor material may comprise a second layer of Group III-V semiconductor material having an interface with the Group IV semiconductor layer at the opposite side of the Group IV layer to the interface with the first Group III-V layer and may comprise a second silicon layer at the interface between the second III-V semiconductor layer and the Group IV layer.

The present disclosure also provides a photovoltaic device comprising a light absorbing cell comprising the semiconductor material of embodiments of the present disclosure.

The photovoltaic device may comprise a plurality of light absorbing cells, one or more of which comprises a semiconductor material of the present disclosure. One of the plurality of cells may have a different bandgap from another

one of the cells of the plurality. The light absorbing cell(s) may be a light absorbing p-n diode. The photovoltaic device may be a solar cell.

The present disclosure further provides a method of making a semiconductor material comprising:

providing a Group IV semiconductor material layer, the material not being silicon,

providing a layer of Group III-V semiconductor material formed of at least one kind of Group III atoms and at least one kind of Group V atoms, and having an interface with the Group IV semiconductor layer,

providing a silicon layer either at the interface between III-V semiconductor layer, or in either the Group IV semiconductor layer or the III-V semiconductor layer, spaced from the interface,

diffusing Group V atoms from the Group III-V material layer through the silicon layer to dope the Group IV material to form an n-type Group V doped region in the Group IV semiconductor layer that has a border with the interface.

The diffusing of the Group V atoms may form a p-n junction in the Group IV layer.

The diffusing of the Group V atoms may be into a region of the Group IV layer that was already n-type to form a region of n-type doping having a higher concentration on n-type dopants.

The Group III-V layer may be grown directly on the Group IV layer or on the silicon layer.

Materials in accordance with embodiments of the present disclosure or made by the method of the present disclosure may be used to generate power from sunlight by:

providing a solar cell formed of those materials, and irradiating the solar cell with sunlight. That may comprise the step of concentrating the sunlight that irradiates the solar cell.

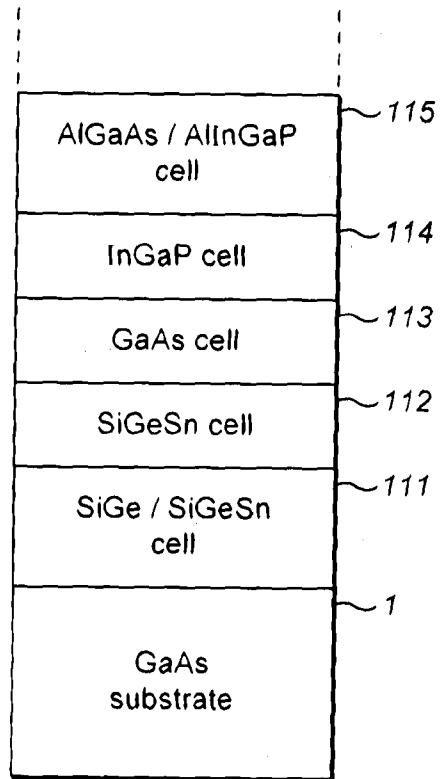

The present disclosure further describes a multijunction photovoltaic device having two or more light absorbing cells formed from semiconductor layers comprising:

a first cell of silicon germanium or silicon germanium tin material,

a second cell of silicon germanium tin material,

wherein the silicon germanium or silicon germanium tin of the first cell and the silicon germanium tin of the second cell are lattice matched to gallium arsenide.

The multijunction photovoltaic device may further comprise a cell of gallium arsenide material.

The multijunction photovoltaic device may further comprise a cell of indium gallium phosphide lattice matched to gallium arsenide.

The multijunction photovoltaic device may further comprise a cell of aluminium gallium arsenide lattice matched to gallium arsenide or a cell of aluminium indium gallium phosphide lattice matched to gallium arsenide.

The multijunction photovoltaic device may comprise a gallium arsenide substrate, the semiconductor layers of the cells being on and lattice matched to the substrate. Alternatively, the multijunction photovoltaic device may comprise a

substrate that is lattice matched to gallium arsenide, the semiconductor layers being on and lattice matched to the substrate.

The multijunction photovoltaic device may be a solar cell.

The first cell may be of silicon germanium material.

The present disclosure also describes a method of making a multijunction photovoltaic device comprising:

providing a substrate of gallium arsenide or another material that is lattice matched to gallium arsenide,

growing a first cell of silicon germanium or silicon germanium tin material lattice matched to the substrate,

growing a second cell of silicon germanium tin material lattice matched to the first light absorbing cell.

The method may comprise growing a cell of gallium arsenide material.

The method may comprise growing a cell of indium gallium phosphide material lattice matched to gallium arsenide.

The method may comprise growing a light absorbing layer of aluminium gallium arsenide material lattice matched to gallium arsenide.

The method may comprise growing a cell of aluminium indium gallium phosphide lattice matched to gallium arsenide.

The method may comprise providing at least one further layer between two neighbouring ones of the said cells, the at least one further layer being lattice matched to gallium arsenide.

The method may comprise removing the substrate.

#### BRIEF DESCRIPTION OF FIGURES

Examples of the present disclosure will now be described with reference to the accompanying drawings, of which:

Figure 1 is a cross-section of the semiconductor layers of the lower cell of a known multi-junction photovoltaic cell,

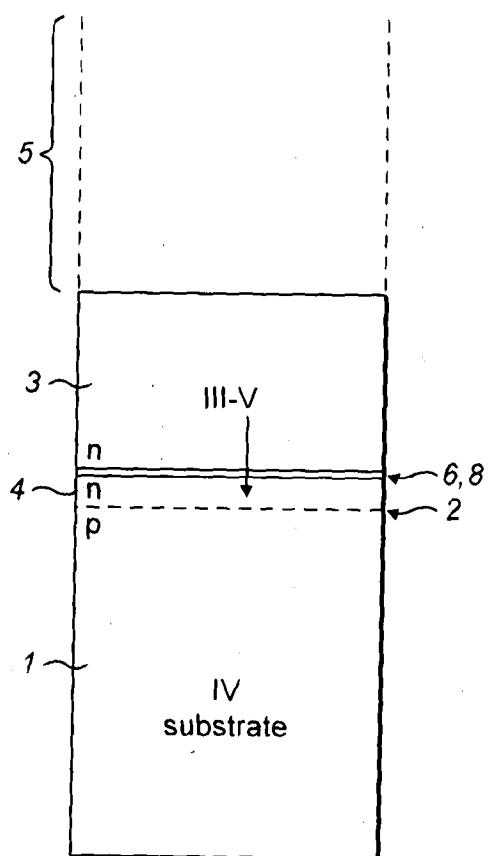

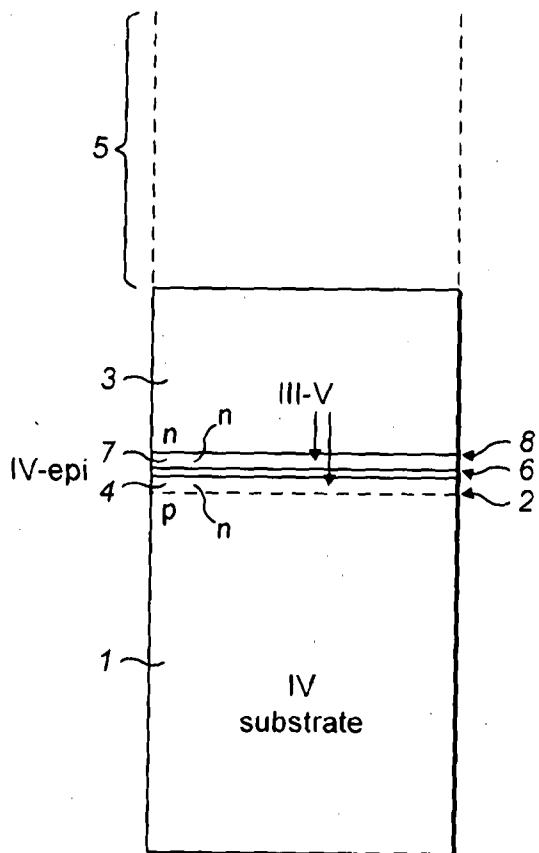

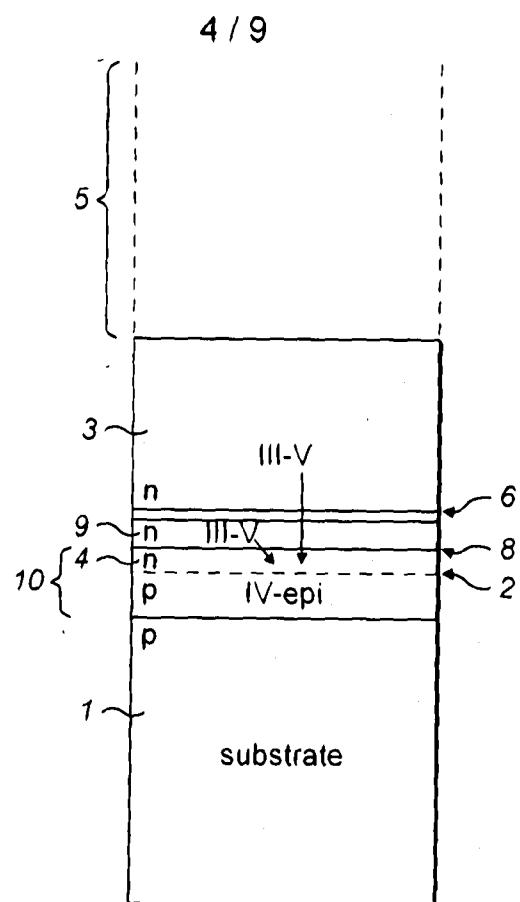

Figure 2 is a cross-section of the semiconductor layers of the lower cell of a first example of a multi-junction photovoltaic device in accordance with the present disclosure,

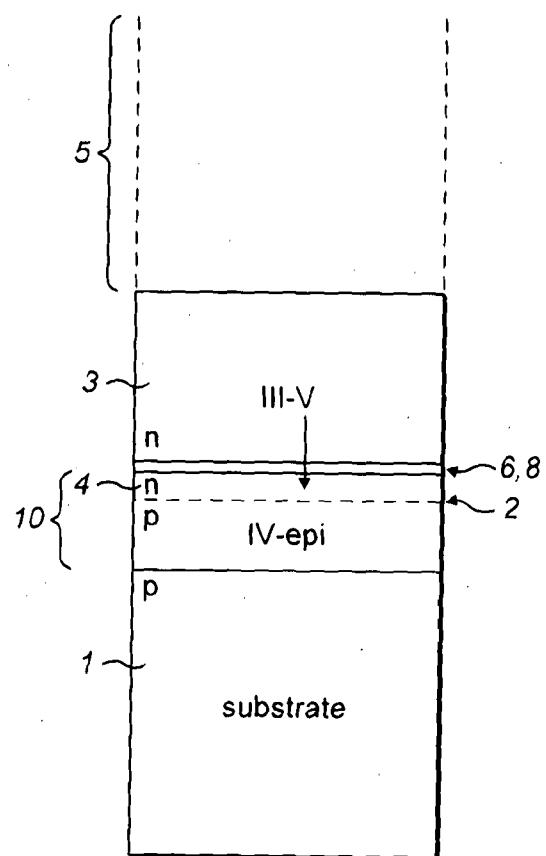

Figure 3 is a cross-section of the semiconductor layers of the lower cell of a second example of a multi-junction photovoltaic device in accordance with the present disclosure,

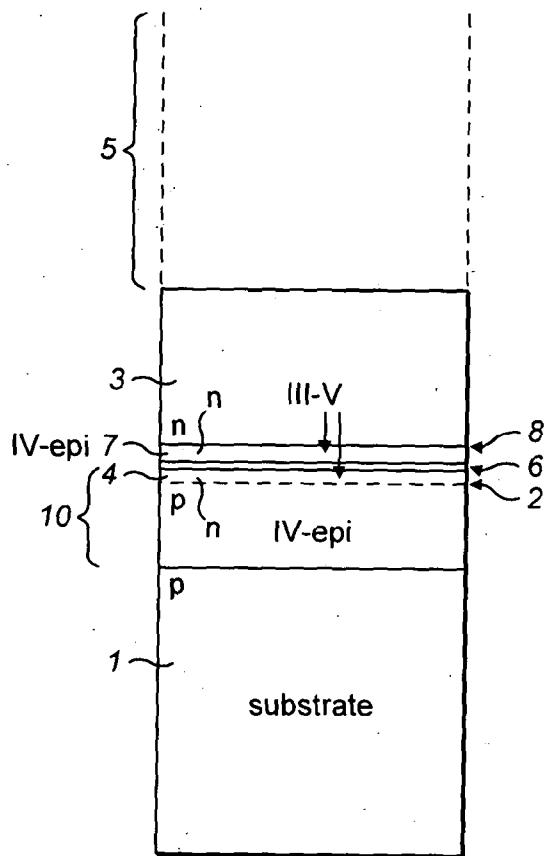

Figure 4 is a cross-section of the semiconductor layers of the lower cell of a third example of a multi-junction photovoltaic device in accordance with the present disclosure,

Figure 5 is a cross-section of the semiconductor layers of the lower cell of a fourth example of a multi-junction photovoltaic device in accordance with the present disclosure,

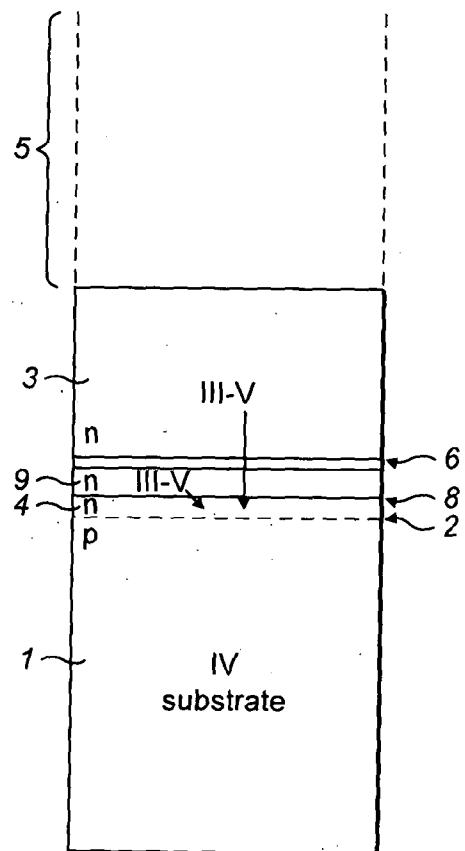

Figure 6 is a cross-section of the semiconductor layers of the lower cell of a fifth example of a multi-junction photovoltaic device in accordance with the present disclosure,

Figure 7 is a cross-section of the semiconductor layers of the lower cell of a sixth example of a multi-junction photovoltaic device in accordance with the present disclosure,

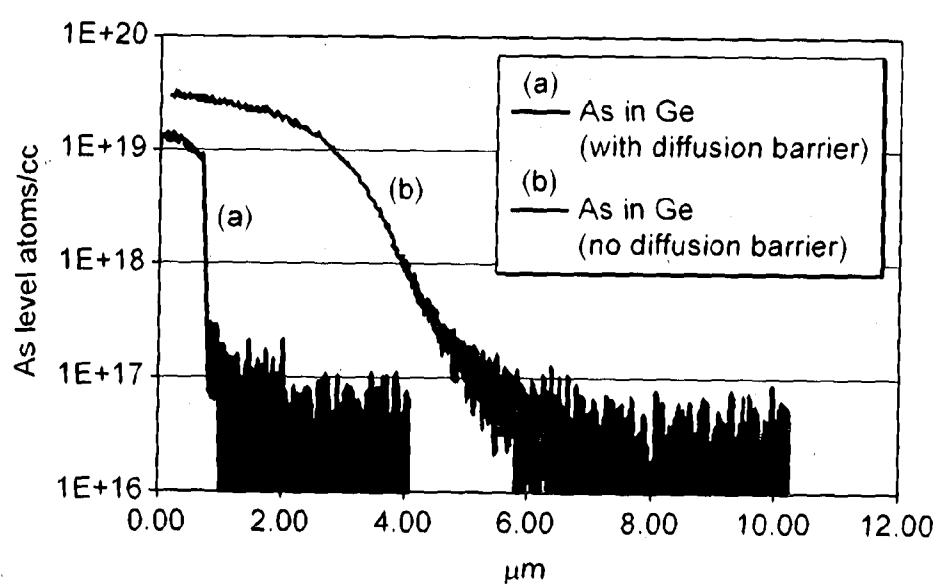

Figure 8 is a secondary ion mass spectrometer plot comparing semiconductor layer structures with and without the silicon layer of the present disclosure,

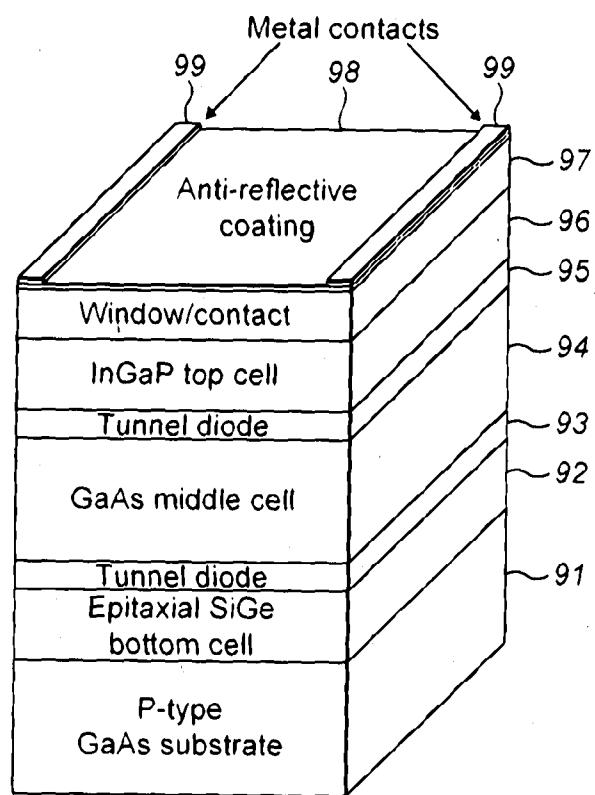

Figure 9 is another example of a device using the present disclosure,

Figures 9A and 9B show examples of the use of the present disclosure in a cell of the device of Figure 9,

Figures 10A to 10D illustrate a method of forming an example of the present disclosure involving the transfer of a SiGe layer between substrates,

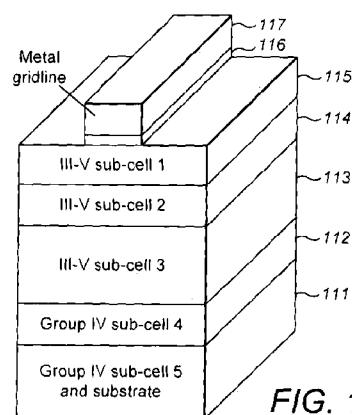

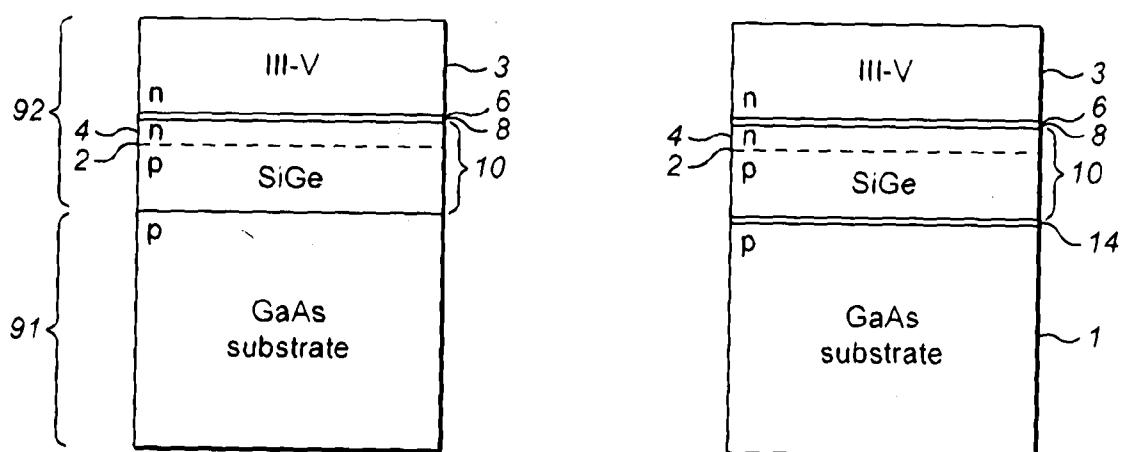

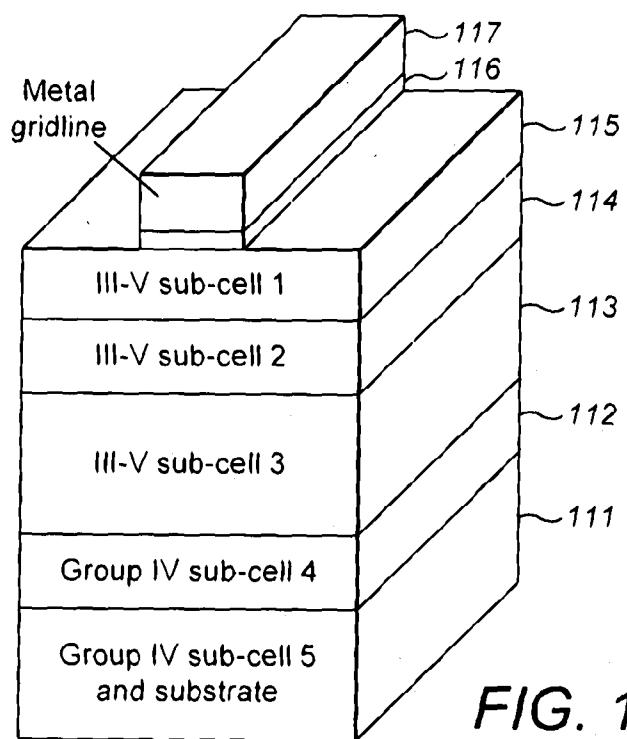

Figure 11 is a further example of a device using the present disclosure,

Figures 11A to 11D show examples of the use of the present disclosure, and

Figure 12 is an example of a tunnel diode using the present disclosure,

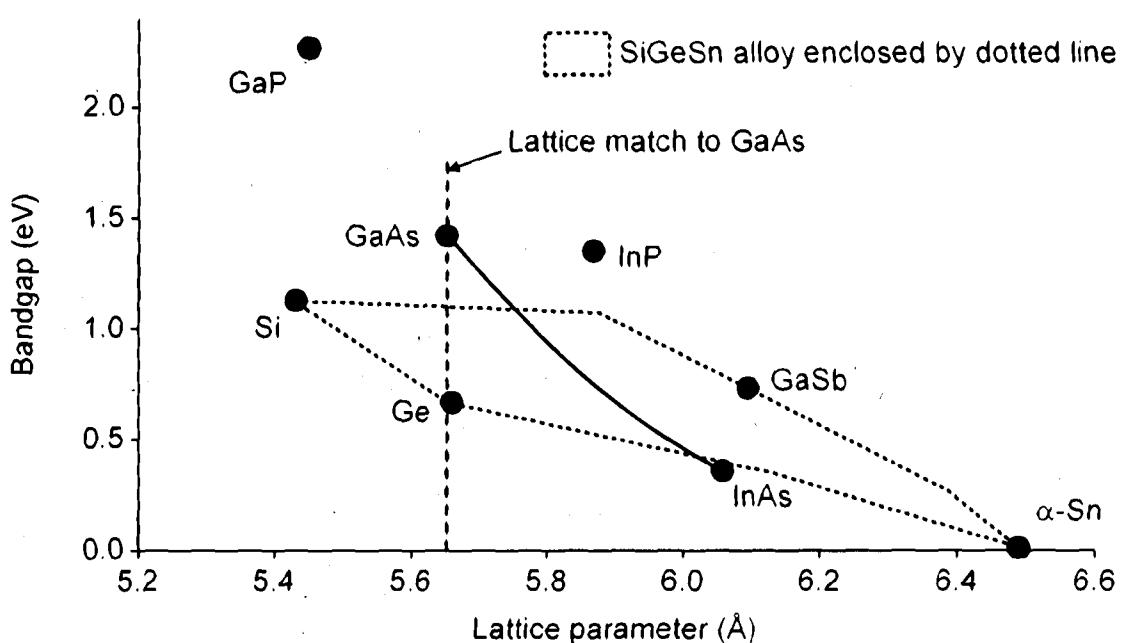

Figure 13 is a graph showing the bandgap and lattice parameter of the alloy SiGeSn, showing that it can be lattice matched to GaAs and Ge and the resultant bandgaps.

#### DETAILED DESCRIPTION

A first example of a photovoltaic device in accordance with the present disclosure is illustrated by Figure 2. This shows a cross-section of the layers of the lower cell with, if present, further semiconductor layers 5 forming one or more further p-n junctions being indicated by dashed lines. Generally, the structure is similar to that shown in Figure 1. A p-type Group IV semiconductor substrate 1, for example germanium, is provided, together with a layer 3 of n-type III-V semiconductor grown on it, the two again meeting at interface 8. Also again Group V atoms from the III-V layer 3 diffuse into the Group IV layer forming an n-type region 4

adjacent to the interface 8, which provides a p-n junction 2 where that region meets the remaining p-type part of the Group IV material. However, a thin layer of silicon 6 is first provided between the layer 3 and the Group IV substrate 1. (Possibilities for the particular Group IV semiconductor material are discussed later below, but the material is not silicon itself. Possibilities for the Group III-V material are also discussed later.)

Figure 3 shows a second example, which is similar to the first except a layer 7 of epitaxial Group IV semiconductor (other than silicon itself) is first grown on the Si layer 6 before the nucleation layer 3 of III-V material is grown on that. In general, this layer 7 could be doped initially, as it is grown, either p- or n-type.

In both these examples, the silicon layer 6 acts to control the diffusion of the Group V atoms from the layer 3 into the Group IV material. The silicon acts as a barrier to the Group V diffusion and so under the same set of processing conditions used to form the device the p-n junction 2 is shallower, i.e. the position of the p-n junction is closer to the interface 8 between the Group IV semiconductor and the nucleation layer. The barrier is not total; it reduces, rather than eliminates entirely, the Group V diffusion into the Group IV material that is on the opposite side of the Si barrier from the III-V material that is the source of the Group V atoms. Setting the barrier thickness can be used to control the depth of the p-n junction 2.

In both those examples, the preferred thickness of the barrier 6 is 3 mono layers (7.5 Å) of silicon or less. Indeed, it may be less than a single complete mono layer.

The 3 mono layers is the preferred maximum thickness for the silicon layer because the silicon layer is strained (because it is trying to match the lattice parameter of the Group IV semiconductor). Above that critical thickness, dislocations form in the silicon to relieve the strain, and those dislocations would be disadvantageous to device performance. The range up to 3 monolayers also produces the depths of junction preferred in photovoltaic devices.

In the second example (Figure 3) the thickness of the Group IV epilayer 7 should preferably not exceed the distance over which the Group V atoms diffuse through the material of that Group IV semiconductor material during the processing of the device, since beyond that distance the amount of Group V atoms traversing the Si barrier will be minimal. Typically, that distance is up to a 1 $\mu$ m, depending on the Group V species being used and the temperatures of the steps of the processing of the device.

(A point to note about the example of Figure 3 is while generally the p-n junction 2 is on the other side of silicon barrier 6 from the III-V layer, the present disclosure generally describes the case where the barrier 6 limits the diffusion of the Group V atoms but not enough pass through the barrier to convert the Group IV material to n-type, the p-n junction being at, or around\*, the barrier (\*a p-n junction of course having an extent larger than the few mono layers of the barrier).)

Figures 4 and 5 show third and fourth examples having the same layers respectively as the first and second examples (Figures 2 and 3), but an epitaxial layer 10 of p-type Group

IV semiconductor is first provided before the silicon layer 6 and the III-V layer 3 are grown. In this particular example the epi-layer 10 is grown on the substrate 1, but having intermediate layers is possible. Having the layer 10 as an epi-layer also helps to accurately control the thickness and doping profile of the junction in the Group IV semiconductor material. Preferably layer 10 is thick enough that the p-n junction 2 forms in this Group IV epilayer 10, as shown, rather than in the substrate 1 (or in an intermediate layer of Group IV material), but the latter are not excluded. Note also however that that substrate 1 need not be Group IV material since the Group IV epi-layer 10 can be grown on other materials.

Figures 6 and 7 show fifth and sixth examples having the same layers respectively as the first and third examples (Figures 2 and 4), but an epitaxial layer 9 of n-type III-V semiconductor material is first provided on the Group IV layer(s) before the silicon layer 6 and the main III-V layer 3 are grown. Again, the silicon layer acts as a barrier to control the diffusion of Group V atoms from the layer 3 into the Group IV material on the other side of the barrier 6. The Group IV material is also doped by Group V atoms diffusing from layer 9. For the presence of the Si barrier to make a significant difference to the level of doping in the Group IV layer from the group III-V layer on the other side of the barrier this III-V epilayer 9 should be thinner than the distance the Group V atoms from the layer 3 will diffuse through layer 9 under the processing conditions of the device.

An example of the Group IV semiconductor material used to be the material in which the p-n junction is formed is

germanium. Also germanium substrates are readily available. The preferred orientations for germanium as the substrate are slightly misaligned from (100) and (111). (Substrates misaligned from exact crystal planes are known generally in the art.)

Group IV semiconductors other than germanium can also be used, such as silicon-germanium and silicon-germanium-tin. SiGe, and SiGeSn, are not available as a basic substrate but can be grown lattice matched on GaAs. Such SiGe or SiGeSn can also be removed from its original GaAs substrate and attached to a cheaper substrate before use in the present disclosure. Examples of this process are described later below.  $Si_xGe_{1-x}$  with a composition with  $x$  of up to at least 0.04, and perhaps  $x = 0.06$  or more, may be used, but preferably  $x$  is in the range  $0.01 \leq x \leq 0.03$ . The corresponding lattice mismatch of the  $Si_xGe_{1-x}$  with GaAs will be about 0.04% for every change of 0.01 in  $x$  away from the lattice matched condition at about  $x = 0.018$ . Figure 13 is a graph showing the bandgap and lattice parameter of the alloy SiGeSn, showing that it can be lattice matched to GaAs with a bandgap range for the SiGeSn of 0.66-1.1eV. It also shows that SiGeSn can be lattice matched to Ge and since the lattice parameter of Ge is fairly close to that of GaAs the range of bandgaps over which SiGeSn can be lattice matched to Ge is similar to that given above for SiGeSn lattice matched to GaAs. SiGeSn is lattice matched to GaAs where the ratio of Si to Sn is approximately 4:1. Where for example the proportion of Si is 2% and that of Sn is 0.5% this provides a larger bandgap than SiGe lattice matched to GaAs, where the proportion of Si is 8% and that of Sn is 2% the bandgap is wider, and where the proportions are much larger the bandgap can extend further - for example at

the limit of 80% Si and 20% Sn the bandgap of that material is around 1.1eV.

As is known in the art, the nucleation layer 3 can be made from various III-V materials, such as InGaAs, InGaP. Other materials are InGaAsP, AlGaAs, AlGaAsP, GaAs, GaAsP, AlAs, InGaP, InGaAs, AlInGaAs, AlInGaP, etc.. They also include those including Sb (or possibly Bi) as the, or a one of, the Group V atom(s) of the material. As is known in the art most of these materials can be grown lattice matched, or nearly so, to at least one of germanium, silicon, or silicon-germanium, silicon-germanium-tin.

Many of these materials contain As and/or P for the Group V atoms. It is noted here that both As and P diffuse from the Group III-V material into the Group IV material, with, for Ge at least for the Group IV material, As diffusing further and faster than P.

Where there is more than one III-V epitaxial layer (e.g. the examples of Figures 6 and 7 have epitaxial layers 3 and 9) it is preferred that these layers have the same composition in terms both the Group III and V atoms making up the basic material but also in doping provided during deposition. However differences are possible and that may be useful to control the doping profile in the Group IV region. Indeed differences within a layer are also not excluded.

Similarly where there is more than one Group IV epitaxial layer (e.g. the example of 5) it is preferred that these layers have the same composition in terms of both the Group IV atoms making up the basic material but also in doping provided before the Group V diffusion discussed above, e.g.

during deposition of the Group IV material. However differences are possible. Indeed differences in composition and/or doping within a layer are also not excluded.

However, as is frequently done in the art for epitaxial layers, even when the epi-layer and the substrate are the same basic material, it is preferred for group IV epilayer and the substrate (Figures 4, 5 and 7) to have different doping.

As foreshadowed above with the examples of SiGe and SiGeSn grown on GaAs, materials for the Group IV layer 10 can be grown on substrates of non-Group IV materials.

Some doping concentrations that may be used, or are preferred, are as follows. For the III-V layer at the interface with the Group IV layer the doping concentration would normally be greater than  $1 \times 10^{17}$  atoms per  $\text{cm}^3$ ; more preferably it would be greater than  $1 \times 10^{18}$  atoms per  $\text{cm}^3$ , and still more preferably it would be between  $1 \times 10^{18}$  atoms per  $\text{cm}^3$  and  $5 \times 10^{18}$  atoms per  $\text{cm}^3$ . The number of diffused Group V atoms forming the doping in the Group IV material would normally be greater than  $1 \times 10^{17}$  atoms per  $\text{cm}^3$ ; it would preferably be greater than  $1 \times 10^{18}$  atoms per  $\text{cm}^3$  and may be greater than  $6 \times 10^{18}$  atoms per  $\text{cm}^3$ . For the remainder of the Group IV layer (not diffused significantly by the Group V atoms) the doping concentration would normally be less than  $4 \times 10^{18}$  atoms per  $\text{cm}^3$ ; preferably it would be between  $5 \times 10^{16}$  atoms per  $\text{cm}^3$  and  $2 \times 10^{18}$  atoms per  $\text{cm}^3$  and more preferably it would be between  $1 \times 10^{17}$  atoms per  $\text{cm}^3$  and  $1 \times 10^{18}$  atoms per  $\text{cm}^3$ .

The silicon layer 6 and other layers can be grown using conventional techniques. Some possible methods are as follows.

The silicon layer can, for example, be grown in a conventional MOCVD reactor that is also used to provide the epitaxy of the III-V layers (such a tool is conventionally used for III-V epitaxy of multi-junction photovoltaic devices). This is particularly suited to, but not limited to, the first example (Figure 2) since the germanium substrate (taking that as an example of the Group IV semiconductor material) can be placed straight in the MOCVD reactor, which is then used to grow both the silicon and III-V layers in turn. Silicon is used as a dopant source in such reactors and is therefore available to be used to deposit the silicon directly onto the germanium substrate prior to III-V nucleation layer.

The silicon layer 6 can also be grown epitaxially in a CVD deposition tool used for the growth of germanium, silicon and silicon-germanium or silicon-germanium-tin. This particularly suited to, but is not limited to, the second example (Figure 3) since the germanium etc. substrate can first be placed in the tool and then the silicon and Ge epitaxial layers 6 and 7 grown in turn. The work piece can then be transferred to a MOCVD reactor (preferably using a cluster tool arrangement so that germanium epitaxial layer 7 remains clean) for deposition of the III-V layer 3.

MBE may also be used for the deposition of III-V materials or of silicon.

Figure 8 is a plot from a secondary ion mass spectrometer comparing samples of multi-junction tandem cell device having a InGaAs/Ge junction for the bottom cell (a) with and (b) without the silicon layer of the present disclosure directly at the interface. The vertical axis is the concentration of As atoms in the Ge in atoms /  $\text{cm}^3$  and the horizontal axis is the depth into the Ge layer in microns. The graph clearly shows that with the silicon layer the As dopant diffused into the InGaAs layer is confined to a depth of 1  $\mu\text{m}$  into the Ge layer ((a)), while in the control without a Si layer, but otherwise with same process conditions, the As atoms have penetrated to about 4  $\mu\text{m}$ ((b)). Further the concentration of As atoms is lower in the sample with the Si layer. These observations demonstrate that the Si layer acts as a barrier to diffusion of the As. Similar results are obtained with III-V semiconductor materials having different Group V atoms.

Triple junction photovoltaic structure samples having a silicon layer in accordance with the present disclosure have also been measured to provide a useful increase in the maximum power output when irradiated by 1-sun compared to those without, and also in the open circuit voltage ( $V_{\text{oc}}$ ).

Figure 9 shows another example of a multi-junction solar cell, which makes use of the present disclosure, this time illustrating all the cells. The Figure shows the tandem arrangement of the cells of the device (each of which is made up of various semiconductor layers, but these are not shown in detail). This device starts with a GaAs substrate 91 on which is grown a SiGe cell 92 in accordance with the present disclosure (so comprising a SiGe layer having the p-n junction, a Si diffusion barrier layer and a III-V layer above (for example GaInP) that providing the doping, none of

which are shown in detail in the Figure within the cell 92). Above that are provided a GaAs cell 94 and a InGaP cell 96. Tunnel diodes 93 and 95 respectively between the SiGe and GaAs cells and between the GaAs and InGaP cells reduce the resistance between the cells. Finally a window layer 97 protects the device but allows the light in and metal contact lines 99 thereon collect the current produced by the device. Finally an anti-reflective coating 98 covers the window.

Figure 9A shows an example of the bottom cell 92 and substrate 91 of Figure 9 in more detail (although of course use of this example is not limited to the particular example of Figure 9). This has the structure of the example of Figure 4 with the substrate 1 being GaAs. On that is grown an epi-layer 10 of p-type SiGe largely (or exactly) lattice matched to the GaAs. On that is grown the Si diffusion 6 barrier and on that a III-V nucleation layer 3, again largely (or exactly) lattice matched to the SiGe. The Group V atoms diffuse from layer 3, under the conditions of the deposition of layer 3 and of subsequent processing steps, controlled by the barrier 6, into the SiGe, doping it to form n-type region 4 next to the interface 8 and hence the p-n junction 2 in the SiGe layer 10. In a similar example to this the SiGe layer 10 is made instead from SiGeSn.

In this device doping of the SiGe (or SiGeSn) with Group V atoms from the GaAs substrate 1 is a potential problem: overdoping of the SiGe from p-type to n-type by As atoms to form another p-n junction in the SiGe near the interface between the SiGe 10 and the substrate 1.

This can be addressed in two ways. First, another Si barrier 14 can be provided at that interface to reduce the diffusion

to a level where the SiGe remains p-type. (A thickness of 7.5Å, or 3 atomic layers, is for the Si barrier 6 and 14 is preferred. This limit is as the earlier examples above because the Si is being grown to the lattice parameter of the GaAs substrate which is very similar to that of Ge.)

Another way is to avoid the problem by transferring the SiGe onto a different substrate before subsequent processing steps are carried out. This transfer is described below and in our International patent application published as WO2010094919 published on 26 August 2010, which is incorporated herein by reference.

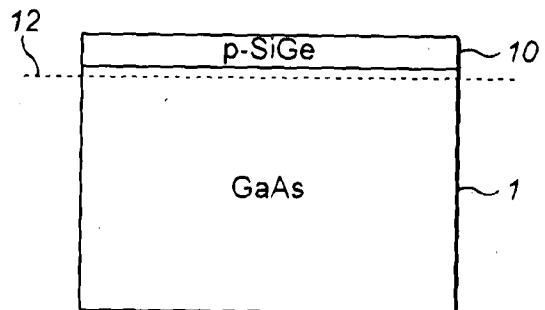

For this the SiGe layer 10 can be grown (Figure 10A) on the GaAs substrate 1 using an epitaxy process, lattice matched, using a gas mixture of a germanium containing precursor (e.g. GeH<sub>4</sub>, GeCl<sub>4</sub>, etc) and a silicon containing precursor (e.g. SiH<sub>4</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, disilane, etc) with a carrier gas (e.g. H<sub>2</sub>). The SiGe layers 10 can be in-situ doped with p-type dopants, using gaseous or solid doping sources including, but not limited to, diborane. The layer 10 can be grown, for example, at atmospheric pressure or reduced pressure in the range 1~1000 Torr, and temperature 350°C~800°C. A range of GaAs substrates may be used including p- type, n-type and semi-insulating, and the wafers may be cleaned ex-situ or in the process chamber prior to epitaxy. Crystallinity properties of the SiGe layer 10 may be measured using X-ray diffraction techniques, for example to check lattice matching, and the thicknesses of the layers may typically be monitored using variable angle spectroscopic ellipsometry, although other techniques are available.

In this process, the change of material composition between the GaAs substrate and the SiGe layer 10 provides a hetero-interface which acts as a good etch-stop, enabling the GaAs substrate to be removed conveniently and accurately to leave a smooth surface of the SiGe layer 10. Some of the GaAs substrate may be removed by mechanical means if this provides more rapid or otherwise convenient or cost-effective manufacture process. For example, if the GaAs substrate is 500  $\mu\text{m}$  thick, about 400  $\mu\text{m}$  may be removed by grinding from which the GaAs material can be more easily recovered and reused, and the final 100  $\mu\text{m}$  may be removed by selective wet etching.

The photovoltaic cell structure resulting from use of this method can be of lighter weight because the substrate thickness has been removed, which may be important particularly in space-based applications. An alternative base which has favourable flexibility, thermal behaviour, or other desirable mechanical or electrical properties may be advantageously provided. Replacement of the substrate with a heatsink can result in more efficient thermal conduction away from the device because the substrate no longer acts to reduce the flow of heat. The heatsink or another metallic base layer can act directly as a conductive electrode to the bottom of the device.

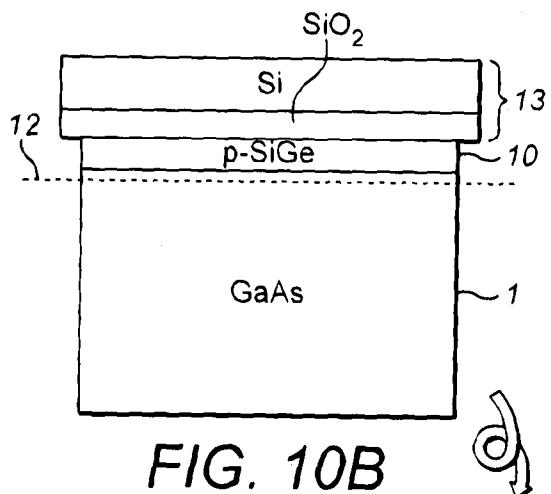

A particular technique is illustrated in Figures 10A - 10D. Starting with a GaAs substrate 1, a layer 10 of SiGe is grown epitaxially as previously described, and as shown in Figure 10A. A layer transfer technique is then used to remove all but a thin layer of the GaAs substrate. The layer transfer may be achieved using a proprietary exfoliation technique such as Smart Cut (RTM) or similar, in which a cleave plane

12 is formed in the GaAs substrate just beneath the layer 10 of SiGe. The cleave plane 12 may be formed using ion beam implant techniques to deposit hydrogen or helium atoms at a precise depth determined by the beam particle energy, for example at depths of up to about 1.5  $\mu\text{m}$ , making the technique practical in the present context if the thickness of the layer of SiGe is of approximately this thickness.

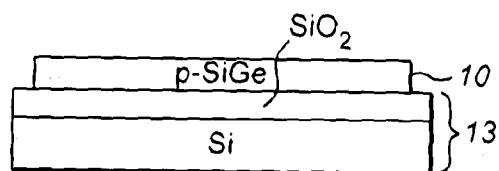

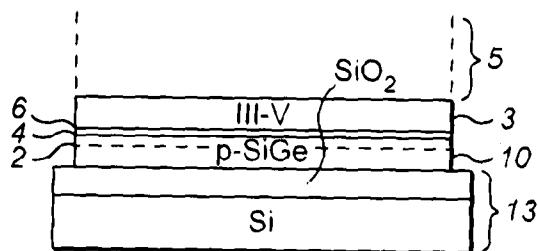

An alternative base 13 is then bonded to the SiGe layer 10. As shown in Figure 10B the alternative base may be an oxidised silicon wafer such that the SiGe layer is bonded to a layer of  $\text{SiO}_2$ , although other bases may be used such as the metallic heat sink layer discussed above. Some other bases which can be used are metallic, glass and semiconductor bases, which may themselves already comprise two or more layers selected from metal, semiconductor and insulator materials, and may include active elements such as one or more photovoltaic junctions. The bulk of the GaAs substrate is then separated from the structure, and the fine remaining layer of GaAs is removed, for example by selective wet etching, to leave the layer 10 of SiGe on an alternative base such as the oxidised silicon wafer discussed, and as shown in Figure 10C. Subsequent layers of the device are then formed as shown in Figure 10D, for example the Si barrier 6 and the III-V layer 3 and subsequent layers 5.

One variation of the described technique is to form the cleave plane just above the interface with the substrate, within the lower SiGe layer. Following layer transfer the transferred SiGe is already exposed for any necessary further preparation. The residual SiGe remaining on the GaAs substrate can be removed, at least partially using a wet etch

selective for SiGe and ineffective on GaAs, to leave a reusable GaAs substrate wafer.

A wide variety of different alternative bases may be contemplated for the structure of Figure 10D, including metallic, glass, and semiconductor bases, which may themselves already comprise two or more layers selected from metal, semiconductor, and insulator materials, and may include active elements such as one or more photovoltaic junctions. The initial formation of the SiGe layer on a GaAs substrate provides an ideal etchstop for accurate removal of the remaining GaAs following cleaving or exfoliation.

Figure 11 shows a further example of a multi-junction solar cell, which makes use of the present disclosure. This shows a five cell solar cell device, again with all the cells connected in tandem. These are, in order from the substrate, a Ge cell 111, another Ge cell 112, a GaInAs cell 113, an AlGaInAs cell 114 and a AlGaInP cell 115 (covered by a heavily n-type contact layer 116 and metal lines 117). In this device the present disclosure is used to form the Ge cell 112; this has an interface with the III-V material of the cell 113 above, which provides the Group V dopant so the Si diffusion barrier 6 is provided at the interface between cells 112 and 113.

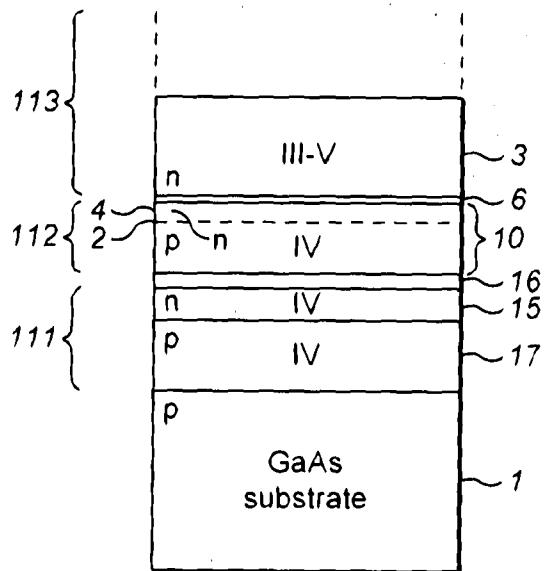

Figure 11A shows an example of the bottom cells 111, 112 of Figure 11 in more detail, although of course its use is not limited to the particular example of Figure 11.

The lowest cell 111 has a p-type Group IV substrate 1 (for example Ge) on which is grown n-type Group IV (for example Ge) epilayer to form the first p-n junction. In order to

provide a low resistance contact to the next cell 112 the layers 16 of a tunnel diode are deposited next. On top of that are formed epilayer 10 of p-type Group IV material (for example Ge) followed by a silicon diffusion barrier 6 and a Group III-V epilayer 3 to form in the manner of the examples above a p-n junction 2 between the n-type material 4 of the epilayer 10 doped by Group V atoms diffused through the barrier 6 from the epilayer 3 and the remainder of the Group IV layer 10, thereby forming cell 112.

Figure 11B shows another example that is similar to that of Figure 11A. However in this example first cell does not include the substrate but is made of an additional Group IV epi-layer 17 that is p-type grown on the substrate 1 (generally lattice matched to the substrate) with the n-type Group IV layer 15 grown on top of that to form the p-n junction of the first cell.

In a particular example of the example of Figure 11B the material of the substrate is GaAs (as marked in Figure 11B (and in Figure 11C)). The Group IV layers are then preferably ones that can be grown generally lattice matched to that, examples of which are SiGe and SiGeSn. SiGe provides a bandgap of 0.66eV when lattice matched to GaAs and SiGeSn provides a bandgap of greater than that, up to ~1.1eV. If two bandgaps of greater than 0.66eV are desired, while remaining lattice matched to GaAs, then the lowest cell 111 and the next cell 112 can both be made of SiGeSn but with different compositions to each other to provide the desired bandgaps.

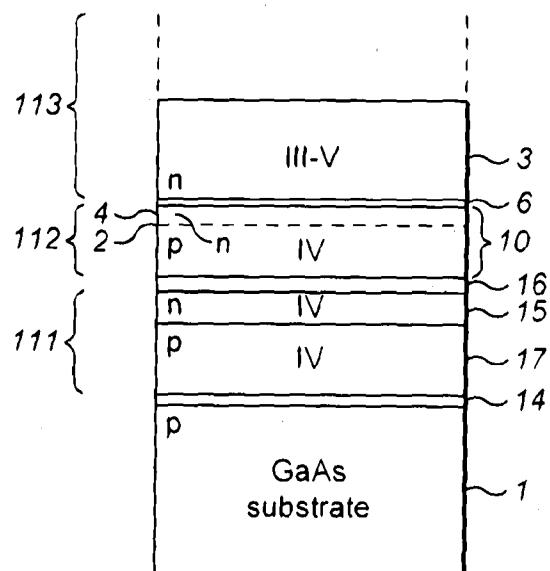

Figure 11C shows a further example that is similar to that of Figure 11B but in this example an additional Si diffusion barrier 14 is provided (like that of example of Figure 9B) to

prevent the formation of an unwanted p-n junction in the Group IV material layer 17 when the substrate is a III-V material (for example GaAs).

Figure 11D shows another example of a multi-junction solar cell. As with the examples of Figures 11B and IIC a first cell of SiGe or SiGeSn is provided on a GaAs substrate and above that is provided a second cell of SiGeSn. In this example a further three cells are provided, also in tandem: a third cell of GaAs above the second cell, a fourth cell of InGaP above the third cell and a fifth cell of AlGaAs or AlInGaP above the fourth cell. All the cells are all lattice matched to the GaAs substrate. (Although AlGaAs does not have exactly the same lattice parameter as GaAs, it is nearly equal enough so to still be lattice matched, only with a small strain where the AlGaAs layer is below the critical thickness where strain relieving dislocations would occur. This applies throughout its compositional range of the proportion of aluminium to gallium. In this example, the other materials have compositions that are exactly lattice matched to GaAs, which compositions are used for preference.) An example of the bandgaps of the cells are in order from the first cell to the last: 0.7eV, 1.0eV, 1.4eV, 1.8eV 2.0eV. Each cell therefore absorbs a different part of the spectrum of the light falling on the device. The device may be provided, if desired, with the Si barriers, tunnel diodes, window layers etc. mentioned in the other examples. Also the substrate may be removed as described with reference to Figure 10A to 10D. Further the materials of the cells may be grown not on GaAs itself but on another substrate that is lattice matched to GaAs. Other layers may be used between the light absorbing cells, for example, tunnel diodes, and these

are preferably lattice matched to the cells and also preferably to the substrate.

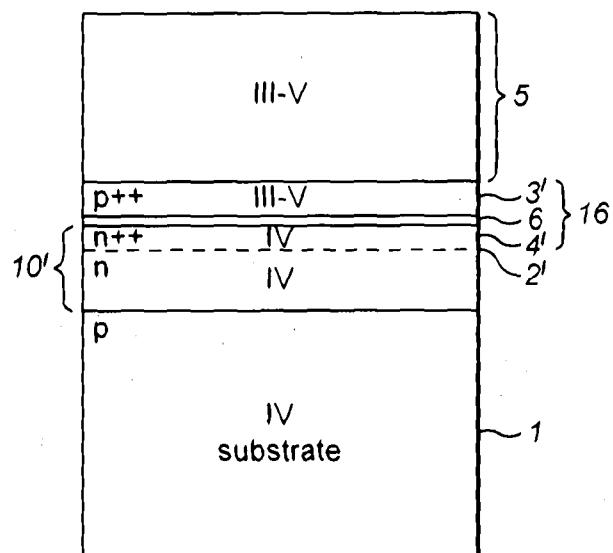

Figure 12 shows the layers of an example of another aspect of the present disclosure. Here the Si diffusion barrier 6 between Group IV 10' and Group III-V layers 3' controls the diffusion of Group V atoms through the barrier into Group IV material that is already n-type, the diffused region 4' produced therefore being highly n-doped. In this example, layers 3' and 4' form a tunnel diode 16.

The example shown in Figure 12 shows the tunnel diode in combination with a Group IV photocell (and so this example will be of use in tandem photovoltaic devices). A p-type Group IV substrate 1 is provided on which is grown an n-type Group IV epilayer 10', which junction provides the photovoltaic cell. Above that is provided a thin Si diffusion barrier 6 and on top of that a highly doped layer 3' of Group III-V material the Group V atoms of which diffuse through the barrier to form the highly doped n++ region 4'. Above that may be grown other layers 5 for example other photovoltaic cells, for example in III-V materials. The highly doped n++ Group IV region 4' and the highly doped p++ III-V layer 3' form a low resistance tunnel diode 16, which allows photo current produced by the p-n junction between layers 1 and 10' to be conducted to the layers above without excessive resistive loss.

As with the earlier examples above the silicon barrier need not be exactly at the interface between the Group IV and Group III-V materials but may be at a distance to one side where it can still influence the diffusion of the Group V atoms.

In the above examples, the subcells may alternatively be grown in reverse order on a GaAs substrate (or a substrate lattice matched to GaAs, or other substrate appropriate to the lattice parameter of the structure) starting with the wider bandgap cells and then followed by in order smaller bandgap cells ending for example with the SiGe / SiGeSn cell. A sacrificial layer is provided between the widest gap cell and the substrate allowing the cells to be removed and transferred to a suitable handle or heat sink, inverted so that the narrowest bandgap cell is next to the substrate and the widest bandgap cell receives the incident light first.

Devices using these materials, typically solar cells, are usually manufactured by first providing a semiconductor material having the necessary layers, or at least some of those. Usually the material is made uniformly over a whole semiconductor wafer. The material is then processed with lithographic techniques to form individual devices and connections. The manufacture of the material is often carried out by a different manufacturer from that performing the lithographic and packaging steps.

CLAIMS:

1. A semiconductor material comprising:

a Group IV semiconductor material layer, the material not being silicon,

a layer of Group III-V semiconductor material formed of at least one kind of Group III atoms and at least one kind of Group V atoms, and having an interface with the Group IV semiconductor material layer,

a silicon layer either at the interface between the III-V semiconductor layer and the Group IV semiconductor material layer, or in either the Group IV semiconductor material layer, or the III-V semiconductor layer, spaced from the interface to control diffusion of the Group V atoms into the Group IV semiconductor material layer, and

an n-type Group V doped region in the Group IV semiconductor material layer that has a border with the interface and that is doped by Group V atoms of at least one of the kinds of those forming the Group III-V semiconductor layer.

2. A semiconductor material as claimed in claim 1 wherein the Group V doped region in the Group IV semiconductor material layer provides a p-n junction with a p-type region in the Group IV semiconductor material layer.

3. A semiconductor material as claimed in claim 1, wherein the Group V doped region in the Group IV semiconductor material layer and the Group III-V layer form a tunnel diode at the interface.

4. A semiconductor material as claimed in any one of the preceding claims wherein the Group IV semiconductor material layer is germanium.

5. A semiconductor material as claimed in any one of claims 1 to 3 wherein the Group IV semiconductor material layer is silicon-germanium, or is silicon-germanium-tin.

6. A semiconductor material as claimed in any one of the preceding claims wherein the Group III-V material comprises Group III atoms that are one or more of Al, Ga, In and comprises Group V atoms that are one or more of P, As, Sb, Bi.

7. A semiconductor material as claimed in any one of the preceding claims wherein the Group IV semiconductor material layer comprises an epitaxial Group IV semiconductor layer between the silicon layer and the III-V semiconductor layer.

8. A semiconductor material as claimed in any one of the preceding claims wherein the Group IV semiconductor material layer comprises a substrate layer and an epitaxial layer grown on the substrate layer.

9. A semiconductor material as claimed in any one of the preceding claims wherein the silicon layer has a thickness of less than or equal to 7.5 Å.

10. A semiconductor material as claimed in any one of the preceding claims comprising a second layer of Group III-V semiconductor material having an interface with the Group IV semiconductor material layer at the opposite side of the Group IV semiconductor material layer to the interface with

the first Group III-V layer and comprising a second silicon layer at the interface between the second III-V semiconductor layer and the Group IV semiconductor material layer.

11. A solar cell comprising a photovoltaic device as claimed in any one of the preceding claims.

12. A method of making a semiconductor material comprising:

providing a Group IV semiconductor material layer, the material not being silicon,

providing a layer of Group III-V semiconductor material formed of at least one kind of Group III atoms and at least one kind of Group V atoms, and having an interface with the Group IV semiconductor material layer,

providing a silicon layer either at the interface between III-V semiconductor layer, or in either the Group IV semiconductor material layer or the III-V semiconductor layer, spaced from the interface,

diffusing Group V atoms from the Group III-V material layer through the silicon layer to dope the Group IV material to form an n-type Group V doped region in the Group IV semiconductor material layer that has a border with the interface.

13. A method as claimed in claim 12 wherein the diffusing of the Group V atoms forms a p-n junction in the Group IV semiconductor material layer.

14. A method as claimed in claim 12 wherein the diffusing of the Group V atoms is into a region of the Group IV semiconductor material layer that was already n-type to form a region of n-type doping having a higher concentration on n-type dopants.

15. A method of generating power from sunlight comprising:

providing a solar cell as claimed in claim 11 or

providing a solar cell from a material made by the method of

any one of claims 12 to 14, and

irradiating the solar cell with sunlight.

1 / 9

FIG. 1

FIG. 2

2 / 9

FIG. 3

FIG. 4

3 / 9

FIG. 5

FIG. 6

FIG. 7

FIG. 8

5 / 9

FIG. 9

FIG. 9A

FIG. 9B

6 / 9

FIG. 10A

FIG. 10B

FIG. 10C

FIG. 10D

7 / 9

FIG. 11A

8 / 9

FIG. 11B

FIG. 11C

FIG. 11D

9 / 9

FIG. 12

FIG. 13