(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5158764号

(P5158764)

(45) 発行日 平成25年3月6日(2013.3.6)

(24) 登録日 平成24年12月21日(2012.12.21)

(51) Int.Cl.

H03K 5/13 (2006.01)

H03K 5/1532 (2006.01)

F 1

H03K 5/13

H03K 5/00

E

請求項の数 8 (全 10 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2007-251589 (P2007-251589) |

| (22) 出願日  | 平成19年9月27日 (2007.9.27)       |

| (65) 公開番号 | 特開2009-88600 (P2009-88600A)  |

| (43) 公開日  | 平成21年4月23日 (2009.4.23)       |

| 審査請求日     | 平成22年8月20日 (2010.8.20)       |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 501285133<br>川崎マイクロエレクトロニクス株式会社<br>千葉県千葉市美浜区中瀬一丁目3番地 |

| (74) 代理人  | 100083194<br>弁理士 長尾 常明                               |

| (72) 発明者  | 吉田 慎也<br>千葉県千葉市美浜区中瀬一丁目3番地 川<br>崎マイクロエレクトロニクス株式会社内   |

審査官 石田 勝

最終頁に続く

(54) 【発明の名称】位相シフト方法および回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号の立上り又は立下りの一方向のエッジ信号を、第1の遅延セルを複数段直列接続した第1の遅延セル群の初段の前記第1の遅延セルに入力し、前記第1の遅延セル群の終段の前記第1の遅延セル以外の特定の段数目の前記第1の遅延セルが反応し、且つ前記終段の前記第1の遅延セルが反応する前に、前記終段の前記第1の遅延セルの出力側を前記初段の前記第1の遅延セルの入力側に接続することによりループ接続して、前記終段の前記第1の遅延セルから出力する前記立上がり又は立下がりの逆方向のエッジ信号を前記初段の前記第1の遅延素子に入力し、前記一方向および逆方向のエッジ信号を巡回させ、該巡回が所定回数に達した後に所望段数目の前記第1の遅延セルから出力信号を出力することを特徴とする位相シフト方法。

## 【請求項 2】

請求項1に記載の位相シフト方法において、

前記所望段目の前記第1の遅延セルから出力する前記出力信号を、第2の遅延セルを複数段直列接続した第2の遅延セル群の内の1つ以上の前記第2の遅延セルを経由させてから出力することを特徴とする位相シフト方法。

## 【請求項 3】

入力信号の立上りのエッジ信号を前記請求項1に記載の方法で第1のルートで遅延させ、前記入力信号の立下りのエッジ信号を前記請求項1に記載の方法で第2のルートで遅延させ、前記第1のルートで得られた出力信号と前記第2のルートで得られた出力信号から

、新たな出力信号を生成することを特徴とする位相シフト方法。

**【請求項 4】**

入力信号の立上りのエッジ信号を前記請求項 2 に記載の方法で第 1 のルートで遅延させ、前記入力信号の立下りのエッジ信号を前記請求項 2 に記載の方法で第 2 のルートで遅延させ、前記第 1 のルートで得られた出力信号と前記第 2 のルートで得られた出力信号から、新たな出力信号を生成することを特徴とする位相シフト方法。

**【請求項 5】**

入力信号の立上り又は立下りのエッジを検出する第 1 のエッジ検出回路と、該第 1 のエッジ検出回路の出力信号を遅延させる第 1 の遅延セルを複数段直列接続した第 1 の遅延セル群と、

10

該第 1 の遅延セル群の内の終段以外の特定の段数目の前記第 1 の遅延セルの出力信号が変化し、且つ前記終段の前記第 1 の遅延セルの出力信号が変化する前に、前記終段の前記第 1 の遅延セルの出力側を初段の前記第 1 の遅延セルの入力側に接続してループ接続するループ切替制御回路と、

前記第 1 の遅延セル群の内の所望段数目の前記第 1 の遅延セルの出力信号の同一方向の変化回数を予め設定した所定数だけカウントするとパルスを出力するカウンタとを備え、

前記カウンタから出力する前記パルスを出力信号としたことを特徴とする位相シフト回路。

**【請求項 6】**

請求項 5 に記載の位相シフト回路において、

第 2 の遅延セルを複数段直列接続した第 2 の遅延セル群と、

20

前記カウンタから出力する前記パルスを前記第 2 の遅延セル群の内の 1 つ以上の前記第 2 の遅延セルを経由させるセル段数設定回路とを備え、

前記第 2 の遅延セル群の内の 1 つ以上の前記第 2 の遅延セルを経由させた信号を出力信号とすることを特徴とする位相シフト回路。

**【請求項 7】**

第 2 のエッジ検出回路を備え、

入力信号の立上りのエッジ信号を入力する請求項 5 に記載の位相シフト回路を立上り側の位相シフト部とし、前記入力信号の立下りのエッジ信号を入力する請求項 5 に記載の位相シフト回路を立下り側の位相シフト部とし、

30

前記第 2 のエッジ検出回路は、前記立上り側の位相シフト部でシフトされた信号で出力信号を立ち上げ、前記立下り側の位相シフト部でシフトされた信号で前記出力信号を立ち下げる特徴とする位相シフト回路。

**【請求項 8】**

第 2 のエッジ検出回路を備え、

入力信号の立上りのエッジ信号を入力する請求項 6 に記載の位相シフト回路を立上り側の位相シフト部とし、前記入力信号の立下りのエッジ信号を入力する請求項 6 に記載の位相シフト回路を立下り側の位相シフト部とし、

前記第 2 のエッジ検出回路は、前記立上り側の位相シフト部でシフトされた信号で出力信号を立ち上げ、前記立下り側の位相シフト部でシフトされた信号で前記出力信号を立ち下げる特徴とする位相シフト回路。

40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、单一の遅延時間を有する複数の遅延セルを直列に接続し、その中の任意段数のみを有効にすることで所望の遅延時間を得る位相シフト方法および回路に係り、特に、必要となる遅延セルの全てを直列に接続するのではなく、少ない段数をループ状に接続して繰り返し使うことにより、遅延セル段数の大幅な削減を可能にした位相シフト方法および回路に関するものである。

**【背景技術】**

50

**【0002】**

DDR SDRAM (DDR : Double Data Rate) の普及に伴い、DLL (Delay Locked Loop) 回路が必要不可欠となっている。 DLL回路と呼ばれているが、実質的な目的は、基準クロックに対し 90 度や 270 度の位相シフトを行なうための絶対遅延を生成する回路である。

**【0003】**

位相シフト回路のひとつの構成方法として、単一の遅延時間を持つ複数の遅延セルを直列に接続し、その中の任意段数だけ有効にすることで、所望の遅延時間を得ることができる（例えば、特許文献 1 の図 9 参照）。遅延セルの構成は限定するものではないが、例えば CMOS ゲート回路でも良い。この位相シフト回路におけるシフト量（遅延時間）が基準クロックを基準とした（例えば）90 度の絶対遅延時間となるには、基準クロックの周期  $T_{ref}$  と遅延セル 1 段当たりの遅延時間  $T_{dl}$  の 2 つがわかれば、 $(T_{ref} / T_{dl}) \times (90 / 360)$  の段数分だけ遅延セルを有効にすれば良い。

10

**【0004】**

しかし、半導体集積回路の中でアナログ的な時間を測定するのは難しいため、位相シフト回路と同じ遅延セルを内部可変遅延として有する DLL 回路を基準クロック 1 周期でロックさせ、ロックした時に使用している遅延段数を「クロック 1 周期分の時間」として出力するマスター DLL 回路を用いてクロック周期を測定する。マスター DLL 回路が、例えば遅延セル 400 段を使ってロックすれば、それを 1/4 倍した 100 段の遅延セルを位相シフト回路で有効にすれば、基準クロックの 90 度分の絶対遅延が得られる。

20

**【0005】**

なお、マスター DLL 回路は、通常、一旦ロックした後も温度変動などによる遅延セルの遅延時間変動を常にトラッキングし、クロック 1 周期当たりの遅延段数を更新するため（例えば、温度が上がって遅延セルの遅延時間が大きくなると、400 段 399 段 398 段と更新していく）、位相シフト回路は「クロック 1 周期分の段数の 1/4 の段数を有効にする」という関係を維持していれば、常に 90 度分の絶対遅延を維持できる。

**【特許文献 1】特開平 11 - 298307 号公報**

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

30

この DLL 回路を利用した位相シフト回路の問題点のひとつとして、セル面積が挙げられる。 DDR SDRAM の規格は世代によって異なるが、800Mbps のデータレート（400MHz クロックの両エッジを使う）も視野に入っているため、遅延調整の分解能は数 10 ps が必要と言われている。つまり遅延セル 1 段当たりが数 10 ps ということである。一方、全てのアプリケーションでそのような高速データレートが必要なわけではなく、DDRSRAM の下限周波数の限界（第一世代では約 80MHz）で使われる場合もある。

**【0007】**

したがって、位相シフト回路に周波数的な汎用性を持たせようすると、遅延時間のはらつき（特に遅延時間が最も小さくなる条件）も考慮すれば 1000 段オーダーの多大な遅延セルを備えておく必要がある。前記した特許文献 1 では、その段落 0068 に必要な段数だけ直列に接続して構成することが述べられている。

40

**【0008】**

本発明の目的は、少ない数の遅延セルをループ状に接続し、同一の遅延セルを繰り返し使用することにより、遅延セルの段数を大幅に削減できるようにした位相シフト方法および回路を提供することである。

**【課題を解決するための手段】****【0009】**

上記目的を達成するために、請求項 1 にかかる発明の位相シフト方法は、入力信号の立ち上り又は立ち下りの 一方向 のエッジ信号を、第 1 の遅延セルを複数段直列接続した第 1 の遅

50

延セル群の初段の前記第1の遅延セルに入力し、前記第1の遅延セル群の終段の前記第1の遅延セル以外の特定の段数目の前記第1の遅延セルが反応し、且つ前記終段の前記第1の遅延セルが反応する前に、前記終段の前記第1の遅延セルの出力側を前記初段の前記第1の遅延セルの入力側に接続することによりループ接続して、前記終段の前記第1の遅延セルから出力する前記立上がり又は立下がりの逆方向のエッジ信号を前記初段の前記第1の遅延素子に入力し、前記一方向および逆方向のエッジ信号を巡回させ、該巡回が所定回数に達した後に所望段数目の前記第1の遅延セルから出力信号を出力することを特徴とする。

請求項2にかかる発明は、請求項1に記載の位相シフト方法において、前記所望段目の前記第1の遅延セルから出力する前記出力信号を、第2の遅延セルを複数段直列接続した第2の遅延セル群の内の1つ以上の前記第2の遅延セルを経由させてから出力することを特徴とする。10

請求項3にかかる発明は、入力信号の立上りのエッジ信号を前記請求項1に記載の方法で第1のルートで遅延させ、前記入力信号の立下りのエッジ信号を前記請求項1に記載の方法で第2のルートで遅延させ、前記第1のルートで得られた出力信号と前記第2のルートで得られた出力信号から、新たな出力信号を生成することを特徴とする。

請求項4にかかる発明の位相シフト方法は、入力信号の立上りのエッジ信号を前記請求項2に記載の方法で第1のルートで遅延させ、前記入力信号の立下りのエッジ信号を前記請求項2に記載の方法で第2のルートで遅延させ、前記第1のルートで得られた出力信号と前記第2のルートで得られた出力信号から、新たな出力信号を生成することを特徴とする。20

請求項5にかかる発明の位相シフト回路は、入力信号の立上り又は立下りのエッジを検出する第1のエッジ検出回路と、該第1のエッジ検出回路の出力信号を遅延させる第1の遅延セルを複数段直列接続した第1の遅延セル群と、該第1の遅延セル群の内の終段以外の特定の段数目の前記第1の遅延セルの出力信号が変化し、且つ前記終段の前記第1の遅延セルの出力信号が変化する前に、前記終段の前記第1の遅延セルの出力側を初段の前記第1の遅延セルの入力側に接続してループ接続するループ切替制御回路と、前記第1の遅延セル群の内の所望段数目の前記第1の遅延セルの出力信号の同一方向の変化回数を予め設定した所定数だけカウントするとパルスを出力するカウンタとを備え、前記カウンタから出力する前記パルスを出力信号としたことを特徴とする。30

請求項6にかかる発明は、請求項5に記載の位相シフト回路において、第2の遅延セルを複数段直列接続した第2の遅延セル群と、前記カウンタから出力する前記パルスを前記第2の遅延セル群の内の1つ以上の前記第2の遅延セルを経由させるセル段数設定回路とを備え、前記第2の遅延セル群の内の1つ以上の前記第2の遅延セルを経由させた信号を出力信号とすることを特徴とする。

請求項7にかかる発明の位相シフト回路は、第2のエッジ検出回路を備え、入力信号の立上りのエッジ信号を入力する請求項5に記載の位相シフト回路を立上り側の位相シフト部とし、前記入力信号の立下りのエッジ信号を入力する請求項5に記載の位相シフト回路を立下り側の位相シフト部とし、前記第2のエッジ検出回路は、前記立上り側の位相シフト部でシフトされた信号で出力信号を立ち上げ、前記立下り側の位相シフト部でシフトされた信号で前記出力信号を立ち下げる特徴とする。40

請求項8にかかる発明の位相シフト回路は、第2のエッジ検出回路を備え、入力信号の立上りのエッジ信号を入力する請求項6に記載の位相シフト回路を立上り側の位相シフト部とし、前記入力信号の立下りのエッジ信号を入力する請求項6に記載の位相シフト回路を立下り側の位相シフト部とし、前記第2のエッジ検出回路は、前記立上り側の位相シフト部でシフトされた信号で出力信号を立ち上げ、前記立下り側の位相シフト部でシフトされた信号で前記出力信号を立ち下げる特徴とする。

#### 【発明の効果】

#### 【0010】

本発明によれば、従来に比べて遅延セルの直列接続段数を大幅に少なくすることができます。50

、セル面積を大幅に縮小できることに加え、この構成により、最低動作周波数の規定は、遅延ループのデューティ維持特性と巡回回数計測の規模のみに依存することになり、対応周波数の下限を考慮した遅延セル面積の増大も抑制される。また、遅延処理は立上りエッジのみを利用して行うので、入力端子に入力されるパルスのデューティを維持して遅延処理し出力端子に出力させることが容易となる。

**【発明を実施するための最良の形態】**

**【0011】**

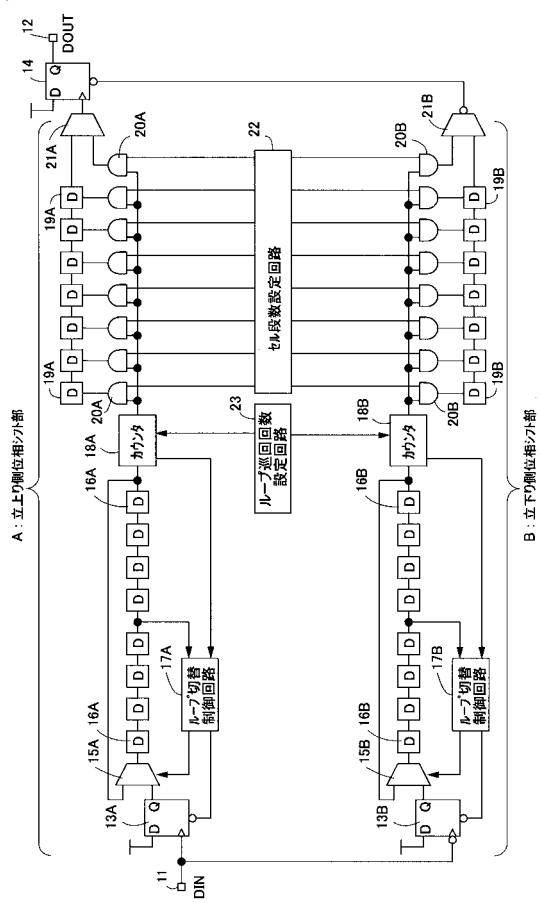

図1に本発明の実施例の位相シフト回路の構成を示す。Aは入力クロックの立上りエッジ側の位相シフト部、Bは同クロックの立下りエッジ側の位相シフト部を示す。11はクロックが入力する入力端子、12は遅延処理されたクロックの出力端子、13A, 13B, 14はD型のフリップフロップ、15A, 15Bは入力セレクタ、16A, 16Bは単一の遅延時間の遅延セル、17A, 17Bはループ切替制御回路、18A, 18Bはカウンタ、19A, 19Bは単一の遅延時間の遅延セル、20A, 20Bはアンドゲート、21A, 21Bは出力セレクタ、22はセル段数設定回路、23はループ巡回回数設定回路である。

10

**【0012】**

ループ切替制御回路17Aは、8段直列接続の遅延セル16Aの内の所定(図1では4段分)の遅延セルの出力に立上りエッジが現れると、それを検知して入力セレクタ15Aの入力側をループ側に切り替えるが、カウンタ18Aが設定した値をカウントした時は、入力セレクタ15Aをフリップフロップ13A側に切り替え、同時にフリップフロップ13Aをリセットする。ループ切替制御回路17Bも同様である。

20

**【0013】**

セル段数設定回路22は、立上りエッジ側の位相シフト部Aの8個のアンドゲート20Aおよび立下りエッジ側の位相シフト部Bの8個のアンドゲート20Bの内の同じ段数目の1つのアンドゲートにH信号を与え、これにより当該アンドゲートのみのゲートを開く。なお、アンドゲート20Aの内、初段から7段までのいずれかがゲートを開くときは出力セレクタ21Aは遅延セル19A側の入力側を選択し、終段のアンドゲート20Aのみがゲートを開くときは当該終段のアンドゲート20Aの側の入力側を選択する。出力セレクタ21Bも同様である。この結果、カウンタ18A, 18Bから出力されるパルスが、当該アンドゲート20A, 20Bと1段以上の遅延セル19A, 19Bまたは全く遅延セルを通過せず、フリップフロップ14のクロック端子、又はリセット端子に入力される。

30

**【0014】**

ループ巡回回数設定回路23は、カウンタ18A, 18Bに同じプリセット値を与える。このカウンタ18A, 18Bは当該プリセット値までカウントアップされると、前記したようにループ切替制御回路17A, 17Bに制御信号を与えると同時に、アンドゲート20A, 20Bにパルスを出力する。

**【0015】**

本実施例は、複数段直列接続の遅延セルをループ状に接続してそのループで信号を巡回させて遅延時間を生成する点に特徴をもち、図1では入力セレクタ15Aとカウンタ18Aの間および入力セレクタ15Bとカウンタ18Bの間で、各々8段の遅延セル16A, 16Bによりループが構成されるようにしている。また、カウンタ18Aと出力セレクタ21Aの間およびカウンタ18Bと出力セレクタ21Bの間で、前記ループ段数よりも1段少ない段数(図では7段)の遅延セル19A, 19Bがそれぞれ接続され、これらを合わせて位相シフト回路としての遅延時間を生成することになる。例えば100段分の遅延時間が必要な場合は、立上りエッジ側のシフト部Aでは、入力信号が前段で8段の遅延セル16Aのループを12周した後に、後段の余りの4段の遅延セル19Aを通って出力されれば、合計で100段になる。立下りエッジ側のシフト部Bでも同様である。同じ要領でどのような段数指定にも対応可能である。この段数指定は、ループ巡回回数設定回路23とセル段数設定回路22により行われる。

40

**【0016】**

50

さて、初期状態では、入力端子 11 からクロックを受けるフリップフロップ 13A は、一旦リセットされてクロックの立上りエッジを待っている状態 ( $Q = L$ ) である。その後段の入力セレクタ 15A はフリップフロップ 13A の出力  $Q$  を選択している状態である。遅延セル 16A は、正転型である（反転インバータではない）ので、ループを形成する全ての遅延セル 16A の出力が  $L$  になっている。

#### 【0017】

この状態で、入力端子 11 がクロックの立上りエッジを受けると、フリップフロップ 13A の出力  $Q$  が  $H$  に変わり、それがセレクタ 15A を通って遅延セル 16A に伝わり、遅延セル 16A の出力が順次  $H$  に変わっていく。ただし、このループは、電圧制御発振器のような自己発振機能を備えていないので、ループ接続されたとしても、このままでは  $L$  か  $H$  で全てのノードが固定されてしまい、後段のカウンタ 18A をカウントアップさせることができなくなる。10

#### 【0018】

そこで、立上りエッジと同様に立下りエッジも意図的に入れてやる必要がある。入力端子 11 の立上りエッジを受けた  $H$  の信号が遅延セル 16A を伝わっていくが、半分の 4 段目まできたところで、ループ切替制御回路 17A がそれを検知して、入力セレクタ 15A の入力側をフリップフロップ 13A の側からループ側に切り替え、このとき同時にフリップフロップ 13A をリセットする。入力セレクタ 15A の入力側がループ側に切り替わった時には、まだ 8 段目の遅延セル 16A の出力は  $L$  なので、今度はこの立下りエッジが遅延セル 16A を伝わっていくことになるが、しばらくすると、立上りエッジがループされて戻ってくるため、結果として、立上りエッジと立下りエッジがこのループをぐるぐる巡回し、その巡回回数分をカウンタ 18A がカウントする。20

#### 【0019】

カウンタ 18A は、ループ巡回回数設定回路 23 によって予めプリセットされたカウント値に達すると、その旨をループ切替制御回路 17A に通知し、これによりループ切替制御回路 17A は入力セレクタ 15A の入力側をフリップフロップ 13A の側に切り替え、且つこのフリップフロップ 13A のリセットを解除して、遅延セル 16A のループとフリップフロップ 13A は初期状態となり、次のクロックの立上りエッジを待つ。

#### 【0020】

それと同時にカウンタ 18A は、後段のアンドゲート 20A に立上りエッジ（正確には出力段のフリップフロップ 14 のクロックとして十分な  $H$  幅を持ったパルス）を流し、ゲートを開いているアンドゲート 20A を介して所定段数の遅延セル 19A を経由して又は遅延セル 19A を経由せず、出力セレクタ 21A からフリップフロップ 14 のクロック端子に入力する。これにより、フリップフロップ 14 はその出力  $Q$  を  $H$  にして、入力端子 11 に入力したクロックの立上りエッジに基づく一連の位相シフト動作が完了する。30

#### 【0021】

入力端子 11 に入力されるクロックの立下りエッジは、フリップフロップ 13B に入力し、前記した立上りエッジ側の位相シフト部 A と同様に、立下り側の位相シフト部 B において、同様に遅延を受け、出力セレクタ 21B からフリップフロップ 14 のリセット信号として入力され、フリップフロップ 14 の出力  $Q$  を  $L$  にする。これにより、フリップフロップ 14 の出力  $Q$  からは、入力端子 11 に入力したクロックと同じパルス幅で且つ所定の遅延を受けたパルスが出力端子 12 に出力する。40

#### 【0022】

位相シフト回路のような遅延セルの多段接続が必要な回路におけるデューティ維持の最大の難題は、遅延セル 1 段分の  $T_{dIh}$ （立上り遅延）と  $T_{dhI}$ （立下り遅延）の差が遅延段数分だけ累積されてしまう点をどのように解決するかである。従来のように遅延セルを 1 列に並べただけの構成では  $T_{dIh}$  と  $T_{dhI}$  の差が直接デューティ維持に響いてしまい、使用条件による変動も大きくなってしまうのだが、本実施例の構成では入力クロックの立上りエッジと立下りエッジが共に、遅延セルを通っている時には  $T_{dIh}$  だけが位相シフト時間に関係しているため、デューティ崩れの累積は全く心配ない。50

## 【0023】

もちろん、本実施例の位相シフト回路においても、デューティ崩れが全くないわけではない。出力側のフリップフロップ14では、出力Qのクロックの立上りエッジは出力セレクタ21Aの出力信号の立上りエッジからQ出力の立上りエッジまでの遅延、立下りエッジは出力セレクタ21Bの出力信号の立下りエッジからQ出力の立下りエッジの遅延を含めて生成されており、デューティ崩れの原因となり得る。しかしながら、これらの部分は、入力周波数や位相シフト量などの条件に依存しない固定的なデューティ崩れであり、遅延時間調整などで比較的容易に調整することができるため、あまり問題にならない。このように、本実施例の位相シフト回路では、入力端子11に入力されるクロックのデューティを維持して出力端子12に出力させることが容易であるという特徴をもつ。

10

## 【0024】

なお、本実施例の位相シフト回路では、立上りエッジ側の位相シフト部Aと立下りエッジ側の位相シフト部Bとで遅延ラインが分かれているが、これは柔軟な（幅広い）シフト量に対応するには不可避な構成である。例えば、入力端子11に入力するクロックのH/Lの幅が50/50のクロックでかつ270度の位相シフトをしたい場合は、遅延ループが立上りエッジのシフト動作を行なっている最中に立下りエッジが入力されてしまうので、立上り側と立下り側で異なる遅延ラインが必要となるのである。回路内で立上りエッジ、立下りエッジが干渉しない、例えば、90度シフト限定の位相シフト回路であれば、入出力部を工夫することにより、遅延セル16A, 19Aを遅延セル16B, 19Bと共に通にすることもできる。

20

## 【0025】

また、ループさせる遅延セル16A, 16Bの段数は8段に限られるものではない。この段数は、遅延ループの周辺回路、具体的にはカウンタ18A, 18Bと、ループ切替制御回路17A, 17Bが正常に動作できるぎりぎりの少ない段数に設定されることが好ましく、偶数段である必要もない。

## 【0026】

また、ループへの立下りエッジの投入タイミングは、遅延セル16A, 16Bの段数のちょうど半分の4段目出力が立ち上がった時を契機にしているが、これも「半分」という点に限定ではなく、終段以外のいずれかの遅延セルの出力が立ち上がった時を契機にすればよい。通常、回路を立上りエッジが通る時間T<sub>dIh</sub>と立下りエッジが通る時間T<sub>dhl</sub>はイコールではないため、遅延セル16A, 16Bのループ回路において、立上りエッジと立下りエッジのループを放っておくと、H幅かL幅どちらかが徐々に狭くなり、ついにはパルスがなくなってしまう。従って、対応すべきループ回数だけ立上りエッジと立下りエッジが回っても信号がなくなるような、最適点に立下りエッジが投入されるべきである。

30

## 【0027】

この最適点は、入力セレクタ15A, 15Bを含めた遅延ループのデューティ維持特性（T<sub>dIh</sub>とT<sub>dhl</sub>の時間差）、カウンタ18A, 18Bが正常動作するHパルス幅、ループ切替制御回路17A, 17Bが入力セレクタ15A, 15Bを切り替えるために必要な遅延時間などを総合的に考慮して決定されることになり、それ以外の縛りはない。

## 【0028】

さらに、現在主流のプロセスにおいては、何の工夫もない論理ゲートを組み合わせただけの遅延セル（しかも正転なので最低2段のインバータを通る）では、あらゆる条件下で数10ps以内の遅延時間を保証することは難しいため、論理ゲート段数の切り替えだけでは刻めない時間差（分解能）を、例えばインバータ出力にぶら下げた容量値を切り替えるなどして実現しており、「微調整部」、「ファイン調整部」などと呼ばれている。

40

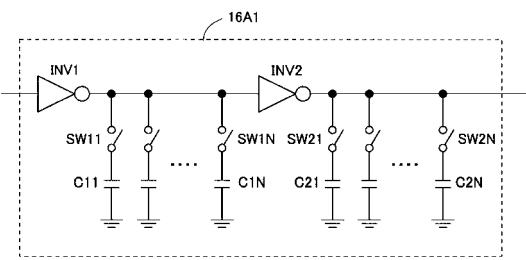

## 【0029】

この点について、本実施例で対象としている遅延セルは、粗いステップを刻むための「粗調整部」、「コース調整部」に当たることになる。微調整部は、通常は粗調整部とは別に設けられており面積も大きくはないため図1の構成には含めていないが、必要ならば特定の段の遅延セル16Aを図2に示すようにな微調整部をもつ遅延セル16A1に置き換

50

えればよい。他の遅延セル 16B, 19A, 19Bについても同様である。図2において、INV1, INV2はインバータ、SW11～SW1N, SW21～SW2Nはスイッチ、C11～C1N, C21～C2Nは容量である。スイッチ SW11～SW1N, SW21～SW2Nの1以上を選択的にオンさせることで、遅延時間の微調整が可能となる。

#### 【0030】

なお、当然ながら、プロセス進化により、遅延セルの段数の切り替えだけで数10psの分解能を達成できる可能性は十分にあるので、そういう意味で微調整部は必須の構成ではない。

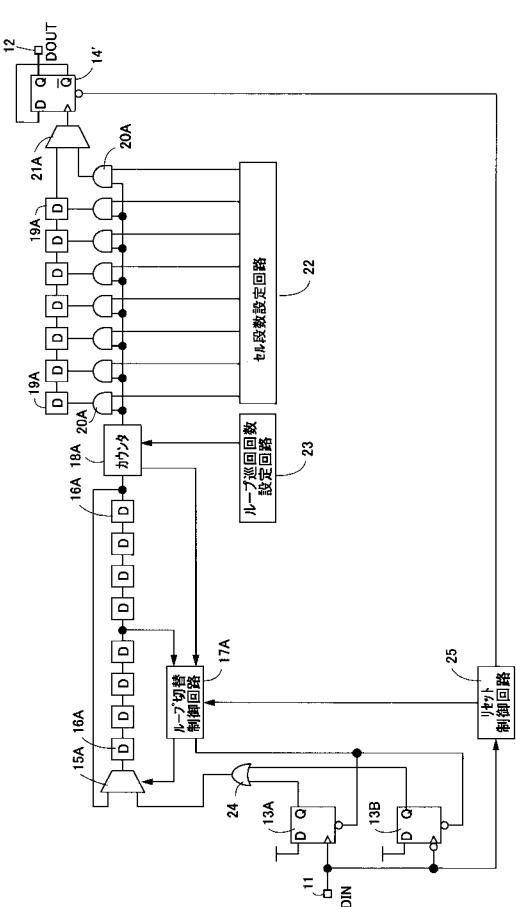

#### 【0031】

図3は遅延セル 16A, 19Aを遅延セル 16B, 19Bと共にした本発明の別の実施例の位相シフト回路の構成を示す図である。14'は出力側のフリップフロップ、24はフリップフロップ 13A, 13Bの出力を入力して入力セレクタ 15Aに入力させるオア回路、25は入力クロックの立上りエッジを検出してリセット信号を生成するリセット制御回路である。ここでは、図1における立下り側位相シフト部B(ただし、フリップフロップ 13Bを除く)を削除している。

10

#### 【0032】

入力端子 11に入力するクロックの立上りエッジではフリップフロップ 13Aの出力がHになり、立下がりエッジではフリップフロップ 13BがHになって、いずれの場合もオア回路 24の出力がHになり、遅延素子 16Aのループの動作が開始し、位相シフトが行われる。すなわち、入力クロックの立上りエッジ、立下りエッジの一方が到来すれば、遅延処理が行われる。ただ、ループ動作(指定されたループ回数)が完了しないうちに入力端子 11に逆のエッジが来ると誤動作を起こすので、位相シフト量には制限がある。出力側のフリップフロップ 14'は、反転Q出力がD入力に接続されるシンプルな2分周回路(T型フリップフロップ)を構成している。なお、出力信号 DOUT の論理が入力信号 DIN と合うように、フリップフロップ 14'のリセットには注意が必要であり、ここでは、リセット制御回路 25で入力クロックをモニタし、回路が必ず入力クロックの立上りエッジから動き始めるようにしている。その他は、図1の位相シフト回路と同じである。

20

#### 【図面の簡単な説明】

#### 【0033】

【図1】本発明の実施例の位相シフト回路の構成を示すブロック図である。

30

【図2】同実施例の微調整部を持つ遅延セルの回路図である。

【図3】本発明の別の実施例の位相シフト回路の構成を示すブロック図である。

#### 【符号の説明】

#### 【0034】

11：入力端子

12：出力端子

13A, 13B, 14, 14'：フリップフロップ

15A, 15B：入力セレクタ

16A, 16B：遅延セル

17A, 17B：ループ切替制御回路

40

18A, 18B：カウンタ

19A, 19B：遅延セル

20A, 20B：アンドゲート

21A, 21B：出力セレクタ

22：セル段数設定回路

23：ループ巡回回数設定回路

24：オア回路

25：リセット制御回路

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特開昭59-181819(JP,A)

特開平9-5408(JP,A)

特開平11-298307(JP,A)

特開2001-91587(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 5/13

H03K 5/1532