(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7280027号**

**(P7280027)**

(45)発行日 令和5年5月23日(2023.5.23)

(24)登録日 令和5年5月15日(2023.5.15)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 12/06 (2006.01) | F I | G 0 6 F | 12/06 | 5 1 5 H |

| G 0 6 F | 12/00 (2006.01) |     | G 0 6 F | 12/00 | 5 6 4 B |

|         |                 |     | G 0 6 F | 12/00 | 5 9 7 U |

請求項の数 9 (全25頁)

(21)出願番号 特願2018-180268(P2018-180268)

(22)出願日 平成30年9月26日(2018.9.26)

(65)公開番号 特開2019-75105(P2019-75105A)

(43)公開日 令和1年5月16日(2019.5.16)

審査請求日 令和3年9月17日(2021.9.17)

(31)優先権主張番号 10-2017-0132752

(32)優先日 平成29年10月12日(2017.10.12)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人 110000051

弁理士法人共生国際特許事務所

全秀昶

(72)発明者 大韓民国 ソウル特別市 瑞草区 孝寧路

49街 57 201棟 806号

最終頁に続く

(54)【発明の名称】 メモリプレーンを含む不揮発性メモリ装置及びその動作方法

**(57)【特許請求の範囲】****【請求項1】**

メモリチップを備え、

前記メモリチップは、

入力信号及び出力信号を通信するように構成されたパッドを共有する複数のメモリプレーンを含むメモリセルアレイを含む第1半導体層と、

前記複数のメモリプレーンの動作をモニタリングしてモニタリング結果を取得し、前記複数のメモリプレーンの複数のピーク電力区間が少なくとも部分的に分散されるように、前記モニタリング結果に基づいて前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作を制御するように構成された制御回路を含む第2半導体層と、を含み、

前記第1半導体層は、前記第2半導体層の上部に配置され、

前記メモリチップは、COP(Cell Over Periphery)構造を有し、

前記制御回路は、前記複数のメモリプレーンの各々の動作が前記複数のピーク電力区間のうちの該当するピーク電力区間に進入するか否かをモニタリングし、前記モニタリングの結果に基づいてモニタリング信号を生成するように更に構成されることを特徴とする不揮発性メモリ装置。

**【請求項2】**

前記制御回路は、前記複数のメモリプレーンのうちの少なくとも一部のメモリプレーンの前記複数のピーク電力区間が互いに重畠する場合、前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作を遅延させるように更に構成されることを特徴と

する請求項 1 に記載の不揮発性メモリ装置。

**【請求項 3】**

前記複数のピーク電力区間は、プログラム動作のためのビットラインセットアップ区間、読み出動作のためのビットラインプリチャージ区間、又は前記プログラム動作若しくは前記読み出動作の前のラッチ初期化区間のうちの少なくとも 1 つに該当することを特徴とする請求項 1 に記載の不揮発性メモリ装置。

**【請求項 4】**

前記制御回路は、各々が前記複数のメモリプレーンのそれぞれのメモリプレーンに対応する複数の制御ロジックを含み、

前記複数の制御ロジックの各々は、前記それぞれのメモリプレーンの動作が前記複数のピーク電力区間のうちの 1 つのピーク電力区間に進入するか否かをモニタリングしてそれぞれのモニタリング結果を取得し、前記それぞれのモニタリング結果に基づいてそれぞれのモニタリング信号を生成し、前記それぞれのモニタリング信号を前記複数の制御ロジックの他の制御ロジックに提供するように構成されることを特徴とする請求項 1 に記載の不揮発性メモリ装置。

10

**【請求項 5】**

前記複数の制御ロジックの各々は、優先順位情報を用いて前記複数のメモリプレーンの各々の優先順位を決定し、前記複数のメモリプレーンのうちの少なくとも 1 つのメモリプレーンよりも高い優先順位を有する前記複数のメモリプレーンのうちの他のメモリプレーンに関連するモニタリング信号に基づいて前記複数のメモリプレーンのうちの少なくとも 1 つのメモリプレーンの動作を制御するように更に構成されることを特徴とする請求項 4 に記載の不揮発性メモリ装置。

20

**【請求項 6】**

前記複数のメモリプレーンは、第 1 メモリプレーン及び第 2 メモリプレーンを含み、

前記複数の制御ロジックは、前記第 1 メモリプレーンに対応する第 1 モニタリング信号を生成するように構成された第 1 制御ロジック、及び前記第 2 メモリプレーンに対応する第 2 モニタリング信号を生成するように構成された第 2 制御ロジックを含み、

前記第 1 制御ロジックは、前記第 1 メモリプレーンの動作が前記複数のピーク電力区間のうちの 1 つのピーク電力区間に進入すると、前記第 2 モニタリング信号に基づいて前記第 1 メモリプレーンの動作を制御することを特徴とする請求項 5 に記載の不揮発性メモリ装置。

30

**【請求項 7】**

メモリチップを備え、

前記メモリチップは、

入力信号及び出力信号を通信するように構成されたパッドを共有する複数のメモリプレーンを含むメモリセルアレイと、

前記複数のメモリプレーンの複数のピーク電力区間が少なくとも部分的に分散されるように、前記複数のメモリプレーンのうちの少なくとも 1 つのメモリプレーンの動作を制御するように構成された制御回路と、を含み、

前記制御回路は、各々が前記複数のメモリプレーンのそれぞれのメモリプレーンに対応する複数の制御ロジックを含み、

40

前記複数のメモリプレーンは、第 1 メモリプレーン及び第 2 メモリプレーンを含み、

前記複数の制御ロジックは、前記第 1 メモリプレーンに対応する第 1 モニタリング信号を生成するように構成された第 1 制御ロジック、及び前記第 2 メモリプレーンに対応する第 2 モニタリング信号を生成するように構成された第 2 制御ロジックを含み、前記第 1 制御ロジックは、前記第 1 メモリプレーンの動作が前記複数のピーク電力区間のうちの 1 つのピーク電力区間に進入すると、前記第 2 モニタリング信号に基づいて前記第 1 メモリプレーンの動作を制御することを特徴とする不揮発性メモリ装置。

**【請求項 8】**

前記複数の制御ロジックの各々は、優先順位情報を用いて前記複数のメモリプレーンの各

50

タの優先順位を決定し、前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンよりも高い優先順位を有する前記複数のメモリプレーンのうちの他のメモリプレーンに

関連するモニタリング信号に基づいて前記複数のメモリプレーンのうちの少なくとも1

つのメモリプレーンの動作を制御するように更に構成されることを特徴とする請求項7に

記載の不揮発性メモリ装置。

【請求項9】

メモリチップを含む不揮発性メモリ装置の制御回路によって行われる動作方法であって、

前記メモリチップに含まれる複数のメモリプレーンの動作をモニタリングする段階と、

前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作がピーク電力区間に該当するか否かを判断する段階と、

前記複数のメモリプレーンの各々の優先順位情報に基づいて前記複数のメモリプレーン

のうちの他のメモリプレーンを決定する段階と、

前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作が前記ピーク電力区間に該当する場合、前記複数のメモリプレーンのうちの他のメモリプレーンの動作が前記ピーク電力区間に該当するか否かを判断する段階と、

前記他のメモリプレーンの動作が前記ピーク電力区間に該当する場合、前記ピーク電力区間を含む複数のピーク電力区間が少なくとも部分的に分散されるように、前記複数のメモリプレーンの動作を制御する段階と、を有することを特徴とする方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリ装置に関し、より詳細には、メモリプレーンのピーク電力区間を制御する不揮発性メモリ装置及びその動作方法に関する。

【背景技術】

【0002】

メモリ装置は、データの保存に使用され、揮発性メモリ装置と不揮発性メモリ装置とに分けられる。不揮発性メモリ装置の一例として、フラッシュメモリ装置は、携帯電話、デジタルカメラ、携帯用情報端末機（PDA）、移動式コンピュータ装置、固定式コンピュータ装置、及びその他の装置で使用される。最近、情報通信装置の多機能化によってメモリ装置の大容量化及び高集積化が要求されている。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2014-137841号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、メモリプレーンのピーク電力区間の重疊を回避する不揮発性メモリ装置及びその動作方法を提供する。

【課題を解決するための手段】

【0005】

上記目的を達成するためになされた本発明の一態様による不揮発性メモリ装置は、メモリチップを備え、前記メモリチップは、入力信号及び出力信号を通信するように構成されたパッドを共有する複数のメモリプレーンを含むメモリセルアレイと、前記複数のメモリプレーンのそれぞれの動作をモニタリングし、前記モニタリングの結果に基づいて前記複数のメモリプレーンのそれぞれのピーク電力区間が少なくとも部分的に分散されるように、前記複数のメモリプレーンのうちの少なくとも1つの動作を制御する制御回路と、を含む。

【0006】

上記目的を達成するためになされた本発明の他の態様による不揮発性メモリ装置は、メ

10

20

30

40

50

モリチップを備え、前記メモリチップは、入力信号及び出力信号を通信するように構成されたパッドを共有する複数のメモリプレーンを含むメモリセルアレイと、前記複数のメモリプレーンのそれぞれのピーク電力区間が少なくとも部分的に分散されるように、前記複数のメモリプレーンのうちの少なくとも1つの動作を制御する制御回路と、を含み、前記制御回路は、前記複数のメモリプレーンのそれぞれに対応する複数の制御ロジックを含み、前記複数の制御ロジックのそれぞれは、対応するメモリプレーンの動作がピーク電力区間に進入するか否かをモニタリングし、前記モニタリングの結果に基づいてモニタリング信号を生成し、前記生成されたモニタリング信号を前記複数の制御ロジックの他の制御ロジックに提供する。

## 【0007】

10

上記目的を達成するためになされた本発明の一態様によるメモリチップを含む不揮発性メモリ装置の制御回路によって行われる動作方法は、前記メモリチップに含まれる複数のメモリプレーンの動作をモニタリングする段階と、前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作がピーク電力区間に該当するか否かを判断する段階と、前記複数のメモリプレーンのうちの少なくとも1つのメモリプレーンの動作が前記ピーク電力区間に該当する場合、前記複数のメモリプレーンのうちの他のメモリプレーンの動作が前記ピーク電力区間に該当するか否かを判断する段階と、前記他のメモリプレーンの動作が前記ピーク電力区間に該当する場合、ピーク電力区間が少なくとも部分的に分散されるように、前記複数のメモリプレーンの動作を制御する段階と、を含む。

## 【発明の効果】

20

## 【0008】

本発明によれば、メモリチップに含まれる複数のメモリプレーンが同時に動作する場合、複数のメモリプレーンの動作をモニタリングすることで、複数のメモリプレーンのピーク電力区間を少なくとも部分的に分散させることができる。これにより、メモリチップで消耗される電流又は電力がPMIC(電力管理IC)の最大電流限界又は最大電力限界を超えず、メモリチップの信頼性を向上させることができる。

## 【図面の簡単な説明】

## 【0009】

【図1】本発明の一実施形態によるメモリシステムを概略的に示すブロック図である。

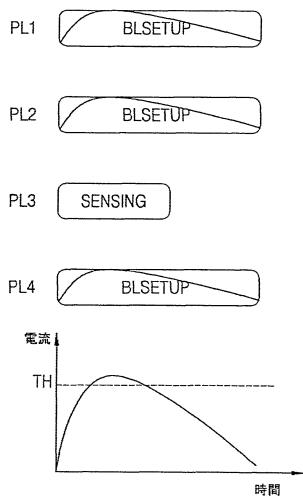

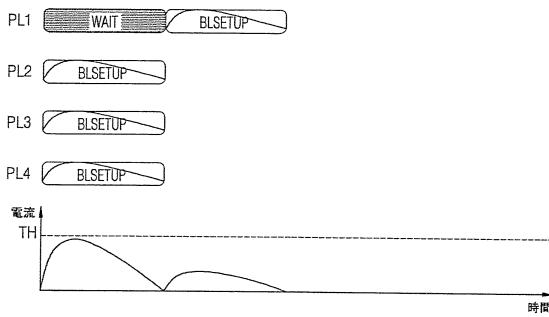

【図2A】図1のメモリ装置のピーク制御動作の第1例を示す図である。

30

【図2B】図1のメモリ装置のピーク制御動作の第2例を示す図である。

【図2C】図1のメモリ装置のピーク制御動作の第3例を示す図である。

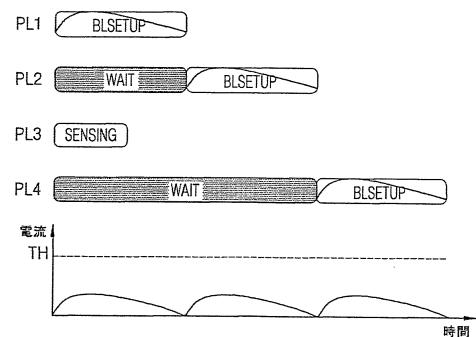

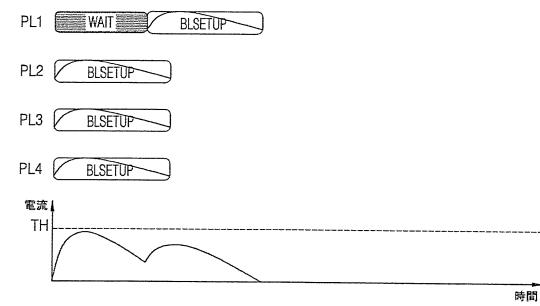

【図3A】図1のメモリ装置のピーク制御動作の第4例を示す図である。

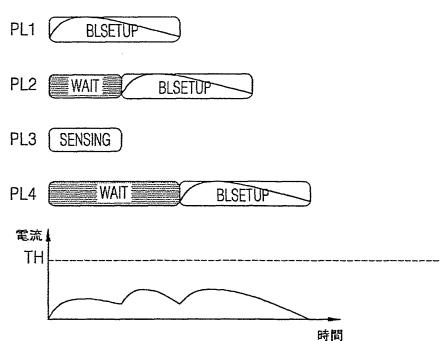

【図3B】図1のメモリ装置のピーク制御動作の第5例を示す図である。

【図3C】図1のメモリ装置のピーク制御動作の第6例を示す図である。

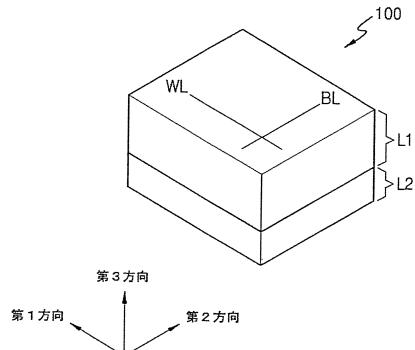

【図4】図1のメモリ装置の構造を概略的に示す図である。

【図5】図4の第2半導体層の上面を示す平面図である。

【図6】図1の第1メモリプレーンを示す図である。

【図7A】図6の第1メモリプロックの等価回路図である。

40

【図7B】図6の第1メモリプロックを示す斜視図である。

【図8】図5のメモリ装置を示す断面図である。

【図9】本発明の他の実施形態によるメモリシステムを概略的に示すブロック図である。

【図10】図9のメモリ装置を示すブロック図である。

【図11】図4の第2半導体層の一例の上面を示す平面図である。

【図12A】図9のメモリ装置のピーク制御動作の第1例を示す図である。

【図12B】図9のメモリ装置のピーク制御動作の第2例を示す図である。

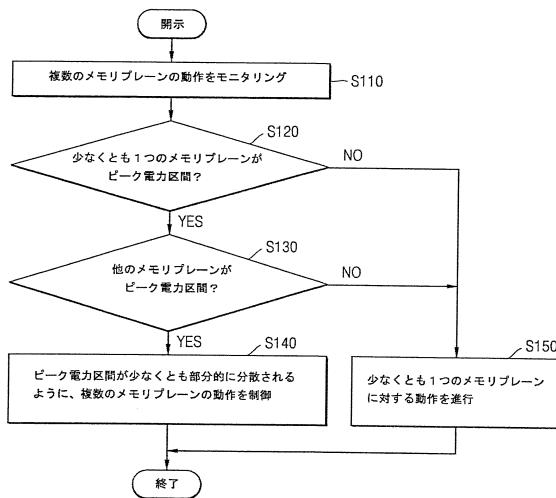

【図13】本発明の一実施形態によるメモリ装置の動作方法を示すフローチャートである。

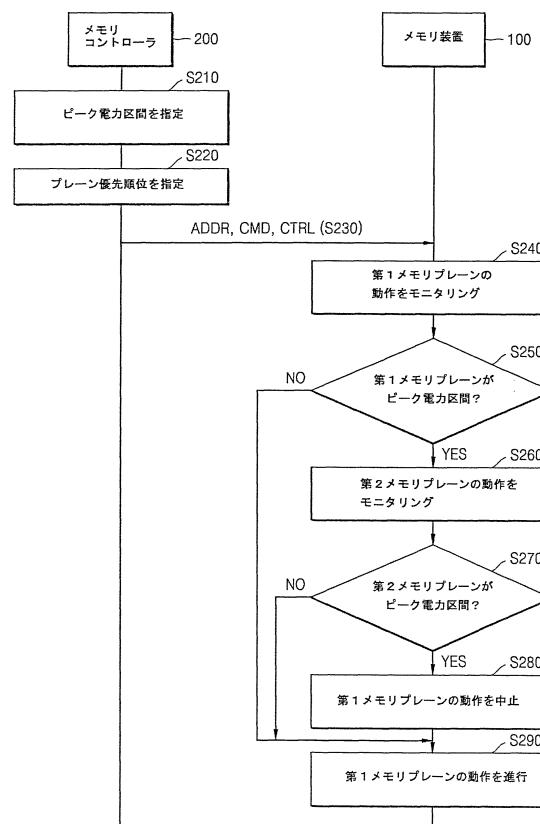

【図14】本発明の一実施形態によるメモリコントローラとメモリ装置との間の動作を示すフローチャートである。

【図15】本発明の一実施形態によるメモリ装置をSSDシステムに適用した例を示すブ

50

ロック図である。

【発明を実施するための形態】

【0010】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

【0011】

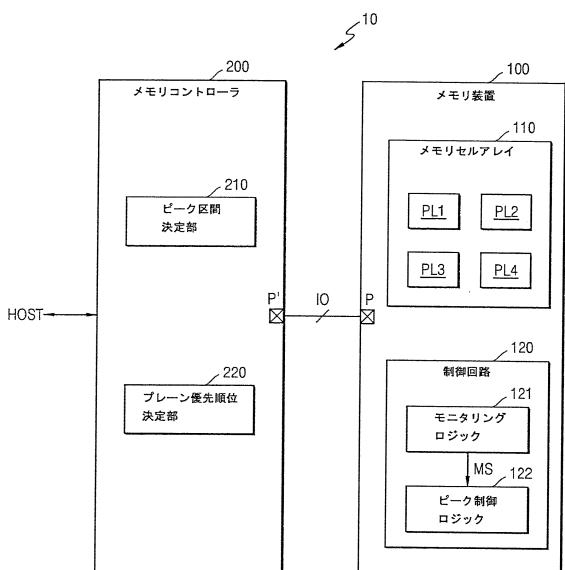

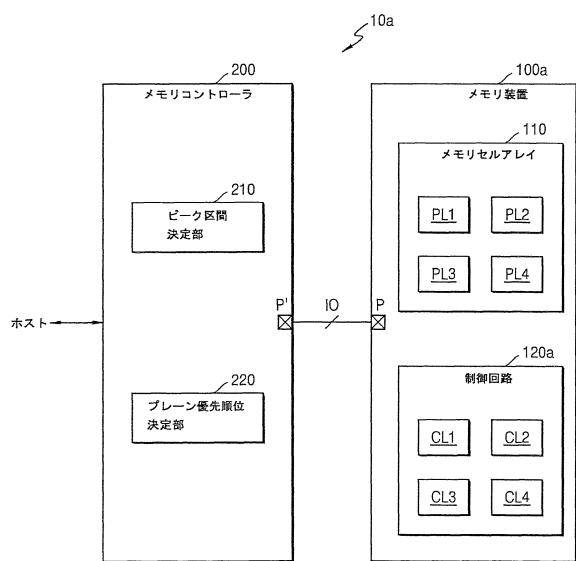

図1は、本発明の一実施形態によるメモリシステム10を概略的に示すブロック図である。

【0012】

図1を参照すると、メモリシステム10は、メモリ装置100及びメモリコントローラ200を含む。メモリ装置100は、不揮発性メモリ装置であり、メモリチップとして具現される。メモリ装置100はメモリセルアレイ110及び制御回路120を含み、メモリセルアレイ110及び制御回路120は単一メモリチップとして具現される。以下、メモリ装置100とメモリチップとを実質的に同一概念として説明する。しかし、本発明はこれに限定されず、メモリ装置は複数のメモリチップを含むメモリパッケージとして具現され、メモリシステム10は複数のメモリチップ又は複数のメモリパッケージを含む。

10

【0013】

一実施例において、メモリシステム10は、電子装置に内蔵される内部メモリとして具現され、例えばエンベデッドUFS(Universal Flash Storage)メモリ装置、eMMC(embedded Multi-Media Card)、又はSD(Solid State Drive)である。一実施例において、メモリシステム10は、電子装置に着脱自在な外装メモリとして具現され、例えばUFSメモリカード、CF(Compact Flash)、SD(Secure Digital)、Micro-SD(Micro Secure Digital)、Mini-SD(Mini Secure Digital)、xD(extreme Digital)又は、メモリスティック(Memory Stick)である。

20

【0014】

メモリコントローラ200は、ホスト(HOST)からの読み出/書き込み要請に応答して、メモリ装置100に保存されたデータを読み出すように、又はメモリ装置100にデータをプログラムするように、メモリ装置100を制御する。具体的に、メモリコントローラ200は、メモリ装置100にアドレス、コマンド、及び制御信号を提供することにより、メモリ装置100に対するプログラム、読み出、及び消去動作を制御する。また、プログラムのためのデータ及び読み出されたデータがメモリコントローラ200とメモリ装置100との間で送受信される。

30

【0015】

例えば、アドレス、コマンド、及びデータは、入出力ライン又は入出力バスI/Oを介してメモリコントローラ200とメモリ装置100との間で送受信される。メモリ装置100は入出力バスI/Oにそれぞれ連結される複数の入出力パッドPを含み、例えば複数の入出力パッドPはメモリ装置100が具現されたメモリチップ上に露出される。メモリコントローラ200は入出力バスI/Oにそれぞれ連結される複数の入出力パッドP'を含み、例えば複数の入出力パッドP'はメモリコントローラ200が具現されたコントローラチップ上に露出される。

40

【0016】

メモリセルアレイ110は、第1～第4メモリプレーン(PL1～PL4)を含み、第1～第4メモリプレーン(PL1～PL4)は、入出力パッドPを共有する。しかし、メモリセルアレイ110に含まれるメモリプレーンの個数は、4個に限定されず、実施例によって多様に変更される。例えば、メモリセルアレイ110は、8個のメモリプレーンを含む。

【0017】

一実施例において、メモリセルアレイ110は、フラッシュメモリを含む。以下、メモリセルアレイ110がNANDフラッシュメモリを含む場合を例として、本発明の実施例

50

を詳述する。しかし、本発明はこれに限定されず、メモリセルアレイ 110 は、ReRAM (resistive RAM)、PRAM (phase change RAM)、又はMRAM (magnetic RAM) のような抵抗型メモリ装置を含む。

#### 【0018】

一実施例において、メモリセルアレイ 110 は 2 次元メモリセルアレイを含み、2 次元メモリセルアレイは行及び列方向に沿って配置された複数の NAND ストリングを含む。一実施例において、メモリセルアレイ 110 は 3 次元メモリセルアレイを含み、3 次元メモリセルアレイは複数の NAND ストリングを含み、各 NAND ストリングは基板上に垂直に積層されたワードラインにそれぞれ連結されたメモリセルを含み、これについては、図 6、図 7A、及び図 7B を参照して詳述する。米国特許第 7,679,133 号、米国特許第 8,553,466 号、米国特許第 8,654,587 号、米国特許第 8,559,235 号、及び米国特許出願公開第 2011/0233648 号は、3 次元メモリアレイが複数レベルで構成され、ワードライン及び / 又はビットラインがレベル間に共有される 3 次元メモリアレイに対する適切な構成を詳述するものであって、本明細書に引用形式で結合される。10

#### 【0019】

第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) の動作は、それぞれ独立して行われる。例えば、第 1 メモリプレーン PL 1 に対してプログラム動作が行われ、第 2 ~ 第 4 メモリプレーン (PL 2 ~ PL 4) に対して読み出動作が行われる。これにより、メモリ装置 10 は、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) を含むことで、入出力バス I/O を共有する 4 個のメモリチップを備えたような類似した効果が得られ、メモリシステム 10 の性能を向上させる。また、メモリ装置 100 は、ホストからの要請が受信された後のレイテンシーを減少させる。20

#### 【0020】

このような第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) の独立した同時動作によって、メモリ装置 100 で消耗される電力が非常に高くなる。例えば、第 1 メモリプレーン PL 1 の動作のために要求される電圧又は電流が高い場合、即ち第 1 メモリプレーン PL 1 の動作が高電力動作である場合、第 1 メモリプレーン PL 1 と同時に動作する第 2 メモリプレーン PL 2 の動作のために要求される電圧又は電流も高くなる。この時、メモリシステム 10 を含む電子装置に含まれる電力管理モジュール、例えば PMIC (Power Management Integrated Circuit) で提供可能な電流又は電力の範囲を超えることによりメモリシステム 10 の信頼性が低下する虞がある。30

#### 【0021】

制御回路 120 は、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれの動作をモニタリングし、モニタリングの結果に基づいて第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれのピーク電力区間が少なくとも部分的に分散されるように、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のうちの少なくとも 1 つの動作を制御する。例えば、制御回路 120 は、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のうちの少なくとも一部のメモリプレーンのピーク電力区間が互いに重複する場合、一部のメモリプレーンのうちの少なくとも 1 つのメモリプレーンの動作を遅延 (delay) させることで、ピーク電力区間を分散させる。40

#### 【0022】

ここで、「ピーク電力区間」は、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれの動作によって消耗する電力が臨界値以上の区間である。「ピーク電力区間」は、ピーク電流区間又はピーク制御区間とも称される。例えば、ピーク電力区間は、プログラム動作のためのビットラインセットアップ (setup) 区間、読み出動作のためのビットラインプリチャージ (precharge) 区間、及びプログラム動作又は読み出動作前のラッチ初期化 (latch initialization) 区間のうちの少なくとも 1 つに該当する。

#### 【0023】

ピーク電力区間は、メモリコントローラ 200 のピーク区間決定部 210 によって決定され、メモリコントローラ 200 は、セットフィーチャー (set feature) コマンドを介してピーク区間情報をメモリ装置 100 に提供する。例えば、ピーク区間決定部 210 は、ハードウェア、ソフトウェア、又はファームウェアとして具現される。一実施例において、ピーク電力区間は、メモリ装置 100 の出荷時に決定され、メモリセルアレイ 110 の一部領域にプログラムされる。メモリコントローラ 200 は、IDR (Information Data Read) を介してメモリセルアレイ 110 からピーク電力区間にに関する情報を読出す。第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) 間の優先順位は、メモリコントローラ 200 のプレーン優先順位決定部 220 によって決定される。一実施例において、ピーク区間決定部 210 及びプレーン優先順位決定部 220 のうちの一部又は全部によって行われるものとして記載した動作は、ハードウェア (例えば、プロセッサ、ASIC など) の形態として具現されるソフトウェア及び / 又は多様なハードウェアのような、上記動作が行われる任意の適切な手段によって行われる。例えば、上記動作は、上記動作に対応する命令語を含むプログラムコードを実行する少なくとも 1 つのプロセッサ (例えば、メモリコントローラ 200) によって行われる。命令語は、メモリに保存される。本明細書において「プロセッサ」という用語は、例えばプログラムに含まれるコード及び / 又は命令語で表示される動作を含む所定の動作を実行するために、物理的に構成された回路を有するハードウェア具現のデータ処理装置を称する。少なくとも一実施例において、ハードウェア具現のデータ処理装置は、コントローラ、マイクロプロセッサ、CPU、プロセッサコア、マルチコアプロセッサ、マルチプロセッサ、ASIC、及び FPGA を含むが、それらに限定されない。

#### 【0024】

制御回路 120 は、モニタリングロジック 121 及びピーク制御 (Peak Control) ロジック 122 を含む。モニタリングロジック 121 は、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれの動作がピーク電力区間に進入するか否かをモニタリングし、モニタリングの結果によって、モニタリング信号 (Monitoring Signal) MS を生成する。ピーク制御ロジック 122 は、モニタリング信号 MS に基づいて第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれのピーク電力区間が少なくとも部分的に分散されるように、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のうちの少なくとも 1 つのピーク電力区間を遅延又は中止 (suspend) させる。一実施例において、制御回路 120、モニタリングロジック 121、及びピークロジック 122 の動作は、ハードウェアの形態として具現されるソフトウェア及び / 又は多様なハードウェアのような、上記動作を行う任意の適切な手段によって行われる。例えば、制御回路 120 は、ハードウェアを用いて具現され、モニタリングロジック 121 及びピーク制御ロジック 122 の一部又は全部によって行われるものとして記載した動作は、対応するハードウェアによって行われる。一実施例において、制御回路 120 はプロセッサであり、モニタリングロジック 121 及びピーク制御ロジック 122 のうちの一部又は全部によって行われるものとして記載した動作は、上記動作に対応する命令語を含むプログラムコードを実行する少なくとも 1 つのプロセッサ (例えば、制御回路 120) によって行われる。

#### 【0025】

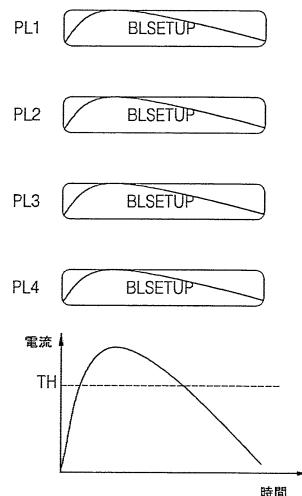

図 2A ~ 図 2C は、図 1 のメモリ装置 100 のピーク制御動作の多様な例を示す図である。

#### 【0026】

図 2A を参照すると、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) の動作がいずれもピーク電力区間に該当する。例えば、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) の動作がいずれもビットラインセットアップ区間 BLSETUP に対応する。この時、第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のそれぞれの動作に要求される電流量は、ビットラインセットアップ区間 BLSETUP の初期にピーク値を有する。

#### 【0027】

このように第 1 ~ 第 4 メモリプレーン (PL 1 ~ PL 4) のビットラインセットアップ

10

20

30

40

50

区間 B L S E T U P が重畠する場合、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) を含むメモリ装置 1 0 0 の全体電流量がピーク値を有し、この時、ピーク値は、臨界電流量 T H よりも高い。その結果、メモリ装置 1 0 0 で消耗される電力は、外部の電力管理モジュール、例えば P M I C で提供可能な最大電流限界又は最大電力限界を超過してしまうため、メモリ装置 1 0 0 の正常動作を保証することが難しい。

#### 【 0 0 2 8 】

図 2 B を参照すると、制御回路 1 2 0 は、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) のビットラインセットアップ区間 B L S E T U P が重畠しないように、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) の動作を時間的に分散させる。一実施例において、制御回路 1 2 0 は、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) のビットラインセットアップ区間 B L S E T U P が全く重畠しないように、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) の動作を時間的に完全に分散させる。これにより、メモリ装置 1 0 0 の全体電流量は臨界電流量 T H よりも十分に低く、メモリ装置 1 0 0 で消耗される電力は P M I C で提供可能な最大電力限界よりも十分に低い。

10

#### 【 0 0 2 9 】

例えば、第 1 メモリプレーン P L 1 のビットラインセットアップ区間 B L S E T U P の間、第 1 メモリプレーン P L 1 に対してビットラインセットアップ動作を正常に行わせ、第 2 ~ 第 4 メモリプレーン ( P L 2 ~ P L 4 ) に対するビットラインセットアップ動作を中止させる。次いで、第 1 メモリプレーン P L 1 のビットラインセットアップ区間 B L S E T U P が終了すると、第 2 メモリプレーン P L 2 に対してビットラインセットアップ動作を再開 ( r e s u m e ) させ、第 3 及び第 4 メモリプレーン ( P L 3 、 P L 4 ) に対するビットラインセットアップ動作を継続して中止させる。次いで、第 2 メモリプレーン P L 2 のビットラインセットアップ区間 B L S E T U P が終了すると、第 3 メモリプレーン P L 3 に対してビットラインセットアップ動作を再開させ、第 4 メモリプレーン P L 4 に対するビットラインセットアップ動作を継続して中止させる。次いで、第 3 メモリプレーン P L 3 のビットラインセットアップ区間 B L S E T U P が終了すると、第 4 メモリプレーン P L 4 に対してビットラインセットアップ動作を再開させる。

20

#### 【 0 0 3 0 】

図 2 C を参照すると、制御回路 1 2 0 は、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) のビットラインセットアップ区間 B L S E T U P が完全に重畠しないように、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) の動作を、時間的に部分的に分散させる。図 2 A を参照して上述したように、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) のそれぞれの動作に要求される電流量は、ビットラインセットアップ区間 B L S E T U P の初期にピーク値を有する。従って、制御回路 1 2 0 は、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) のビットラインセットアップ区間 B L S E T U P の初期区間が重畠しないように、第 1 ~ 第 4 メモリプレーン ( P L 1 ~ P L 4 ) の動作を時間的に分散させる。これにより、メモリ装置 1 0 0 の全体電流量は臨界電流量 T H よりも十分に低く、メモリ装置 1 0 0 で消耗される電力は P M I C で提供可能な最大電力限界よりも十分に低い。

30

#### 【 0 0 3 1 】

例えば、第 1 メモリプレーン P L 1 のビットラインセットアップ区間 B L S E T U P の間、第 1 メモリプレーン P L 1 に対してビットラインセットアップ動作を正常に行わせ、第 1 メモリプレーン P L 1 のビットラインセットアップ区間 B L S E T U P のうちの初期の一部区間の間、第 2 ~ 第 4 メモリプレーン ( P L 2 ~ P L 4 ) に対するビットラインセットアップ動作を中止させる。次いで、第 1 メモリプレーン P L 1 のビットラインセットアップ区間 B L S E T U P のうちの初期の一部区間が終了すると、第 2 メモリプレーン P L 2 に対してビットラインセットアップ動作を再開させ、第 3 及び第 4 メモリプレーン ( P L 3 、 P L 4 ) に対するビットラインセットアップ動作を継続して中止させる。次いで、第 2 メモリプレーン P L 2 のビットラインセットアップ区間 B L S E T U P の初期の一部区間が終了すると、第 3 メモリプレーン P L 3 に対してビットラインセットアップ動作を再開し、第 4 メモリプレーン P L 4 に対するビットラインセットアップ動作を継続して

40

50

中止させる。次いで、第3メモリプレーンPL3のビットラインセットアップ区間BLSETUPの初期の一部区間が終了すると、第4メモリプレーンPL4に対してビットラインセットアップ動作を再開させる。

#### 【0032】

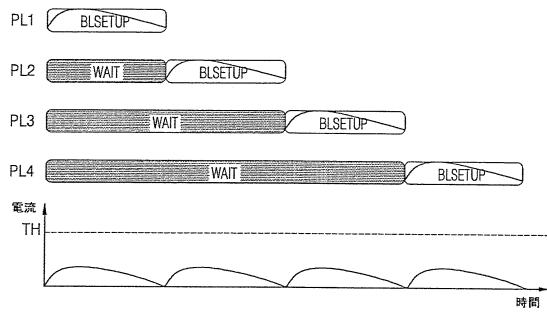

図3A～図3Cは、図1のメモリ装置100のピーク制御動作の更に多様な例を示す図である。

#### 【0033】

図3Aを参照すると、第1～第4メモリプレーン(PL1～PL4)の動作のうちの一部の動作がピーク電力区間に対応する。例えば、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)の動作がビットラインセットアップ区間BLSETUPに対応し、第3メモリプレーンPL3の動作はセンシング区間SENSINGに対応する。ここで、センシング区間SENSINGは、読出動作のうちのプリチャージ区間、ディベロップ区間の後の区間に対応し、センシング区間SENSINGの電流又は電力消費量は相対的に大きくない。ここで、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のそれぞれの動作に要求される電流量は、ビットラインセットアップ区間BLSETUPの初期にピーク値を有する。

10

#### 【0034】

このように第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のビットラインセットアップ区間BLSETUPが重畠する場合、第1～第4メモリプレーン(PL1～PL4)を含むメモリ装置100の全体電流量がピーク値を有し、この時、ピーク値は臨界電流量THよりも高い。その結果、メモリ装置100で消耗される電力は、外部の電力管理モジュール、例えばPMICで提供可能な最大電流限界又は最大電力限界を超過することがあり、メモリ装置100の正常動作を保証することが難しい。

20

#### 【0035】

図3Bを参照すると、制御回路120は、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のビットラインセットアップ区間BLSETUPが重畠しないように、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)の動作を時間的に分散させる。制御回路120は、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のビットラインセットアップ区間BLSETUPが全く重畠しないように、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)の動作を時間的に完全に分散させる。この時、制御回路120は、第3メモリプレーンPL3の動作を正常に行わせ、これにより、第1メモリプレーンPL1のビットラインセットアップ区間BLSETUPと第3メモリプレーンPL3のセンシング区間SENSINGとは重畠する。従って、メモリ装置100の全体電流量は臨界電流量THよりも十分に低く、メモリ装置100で消耗される電力はPMICで提供可能な最大電力限界よりも十分に低い。

30

#### 【0036】

例えば、第1メモリプレーンPL1のビットラインセットアップ区間BLSETUPの間、第1メモリプレーンPL1に対してビットラインセットアップ動作を正常に行わせ、第3メモリプレーンPL3に対してセンシング動作を正常に行わせ、第2及び第4メモリプレーン(PL2、PL4)に対するビットラインセットアップ動作を中止させる。次いで、第1メモリプレーンPL1のビットラインセットアップ区間BLSETUPが終了すると、第2メモリプレーンPL2に対してビットラインセットアップ動作を再開させ、第4メモリプレーンPL4に対するビットラインセットアップ動作を継続して中止させる。次いで、第2メモリプレーンPL2のビットラインセットアップ区間BLSETUPが終了すると、第4メモリプレーンPL4に対してビットラインセットアップ動作を再開させる。

40

#### 【0037】

図3Cを参照すると、制御回路120は、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のビットラインセットアップ区間BLSETUPが完全に重畠しないように、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)の動作を、

50

時間的に部分的に分散させる。図3Aを参照して上述したように、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のそれぞれの動作に要求される電流量は、ビットラインセットアップ区間BLSETUPの初期にピーク値を有する。従って、制御回路120は、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)のビットラインセットアップ区間BLSETUPの初期区間が重畠しないように、第1、第2、及び第4メモリプレーン(PL1、PL2、PL4)の動作を時間的に分散させる。これにより、メモリ装置100の全体電流量は臨界電流量THよりも十分に低く、メモリ装置100で消耗される電力はPMICで提供可能な最大電力限界よりも十分に低い。

#### 【0038】

例えば、第1メモリプレーンPL1のビットラインセットアップ区間BLSETUPの間、第1メモリプレーンPL1に対してビットラインセットアップ動作を正常に行わせ、第3メモリプレーンPL3に対してセンシング動作を正常に行わせ、第2及び第4メモリプレーン(PL2、PL4)に対するビットラインセットアップ動作を中止させる。次いで、第1メモリプレーンPL1のビットラインセットアップ区間BLSETUPのうちの初期の一部区間が終了すると、第2メモリプレーンPL2に対してビットラインセットアップ動作を再開させ、第4メモリプレーンPL4に対するビットラインセットアップ動作を継続して中止させる。次いで、第2メモリプレーンPL2のビットラインセットアップ区間BLSETUPのうちの初期の一部区間が終了すると、第4メモリプレーンPL4に対してビットラインセットアップ動作を再開させる。

#### 【0039】

図4は、図1のメモリ装置100の構造を概略的に示す図である。

#### 【0040】

図4を参照すると、メモリ装置100は第1半導体層L1及び第2半導体層L2を含み、第1半導体層L1は第2半導体層L2上に第3方向に積層される。一実施例において、図1のメモリセルアレイ110は第1半導体層L1に形成され、図1の制御回路120は第2半導体層L2に形成される。これにより、メモリ装置100は、メモリセルアレイ110が制御回路120の上部に配置された構造、即ちCOP(Cell Over Periphery)構造を有する。例えば、メモリセルアレイ110を除いた周辺回路をメモリセルアレイ110下に配置することにより、COP構造は、積層方向に対して垂直な面に占める面積を効果的に減少させ、メモリ装置100の集積度を向上させる。

#### 【0041】

第2半導体層L2は基板を含み、基板上にトランジスタのような半導体素子及び素子を配線するためのパターンを形成することで、第2半導体層L2に制御回路120を含む回路を形成する。第2半導体層L2に回路が形成された後、メモリセルアレイ110を含む第1半導体層L1が形成され、メモリセルアレイ110のワードラインWL及びビットラインBLと第2半導体層L2に形成された回路とを電気的に連結するためのパターンが形成される。

#### 【0042】

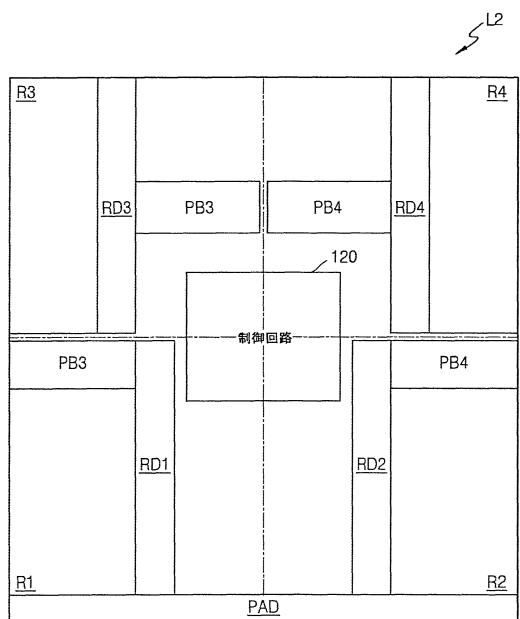

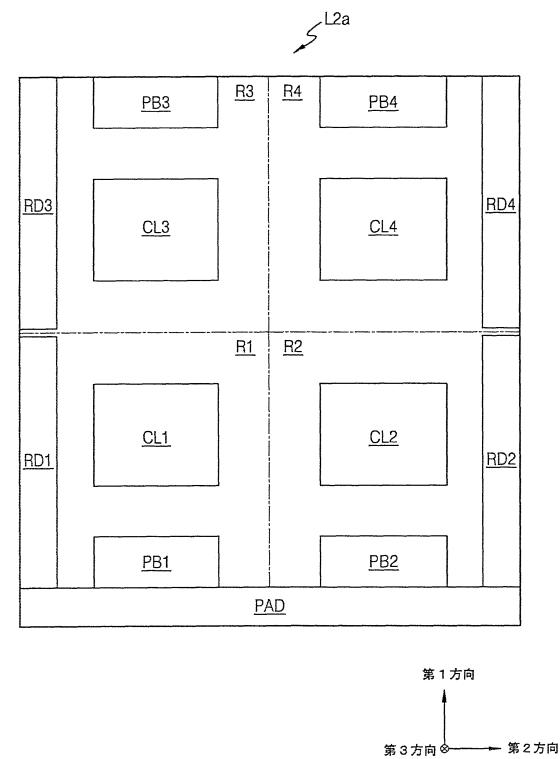

図5は、図4の第2半導体層L2の上面を示す平面図である。

#### 【0043】

図1及び図5を共に参照すると、第2半導体層L2はパッド領域PAD及び周辺回路領域を含み、周辺回路領域は第1～第4領域(R1～R4)を含む。パッド領域PADには複数の入出力パッドPが配置され、複数の入出力パッドPは第2半導体層L2上のメタル配線を介して第1～第4領域(R1～R4)に連結される。第1領域R1の上部には第1メモリプレーンPL1が配置され、第2領域R2の上部には第2メモリプレーンPL2が配置され、第3領域R3の上部には第3メモリプレーンPL3が配置され、第4領域R4の上部には第4メモリプレーンPL4が配置される。

#### 【0044】

第1領域R1には第1ロウデコーダRD1及び第1ページバッファPB1が配置され、第1ロウデコーダRD1及び第1ページバッファPB1は第1メモリプレーンPL1に連

10

20

30

40

50

結される。第2領域R2には第2ロウデコーダRD2及び第2ページバッファPB2が配置され、第2ロウデコーダRD2及び第2ページバッファPB2は第2メモリプレーンPL2に連結される。第3領域R3には第3ロウデコーダRD3及び第3ページバッファPB3が配置され、第3ロウデコーダRD3及び第3ページバッファPB3は第3メモリプレーンPL3に連結される。第4領域R4には第4ロウデコーダRD4及び第4ページバッファPB4が配置され、第4ロウデコーダRD4及び第4ページバッファPB4は第4メモリプレーンPL4に連結される。図5では、第1～第4領域(R1～R4)のそれぞれに1つのロウデコーダ及び1つのページバッファが配置されるものとして図示したが、本発明は、これに限定されない。一実施例において、第1～第4領域(R1～R4)のそれぞれには、複数のロウデコーダ及び複数のページバッファが配置される。

10

#### 【0045】

周辺回路領域の中心領域には、制御回路120が配置される。制御回路120は、第1～第4ロウデコーダ(RD1～RD4)に連結され、第1～第4ページバッファ(PB1～PB4)に連結される。これにより、制御回路120は、第1～第4メモリプレーン(PL1～PL4)の動作をモニタリングし、モニタリングの結果に基づいて第1～第4メモリプレーン(PL1～PL4)のピーカ電力区間が少なくとも部分的に分散されるよう、第1～第4メモリプレーン(PL1～PL4)の動作を制御する。図5では、制御回路120が周辺回路領域の中心領域に配置されるものとして図示したが、本発明は、これに限定されない。一実施例において、第1～第4領域(R1～R4)のうちの少なくとも1つに制御回路120が配置される。

20

#### 【0046】

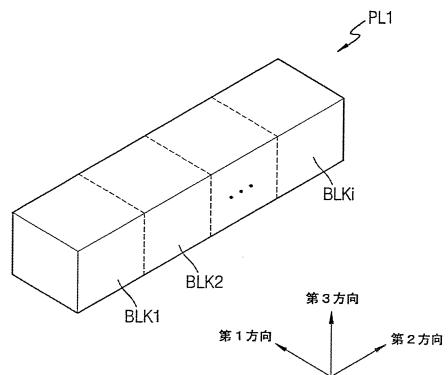

図6は、図1の第1メモリプレーンPL1を示す図である。

#### 【0047】

図6を参照すると、第1メモリプレーンPL1は、複数のメモリプロック(BLK1～BLKi)を含む。複数のメモリプロック(BLK1～BLKi)のそれぞれは、3次元構造(又は垂直構造)を有する。具体的に、複数のメモリプロック(BLK1～BLKi)のそれぞれは、第1又は第2方向に沿って伸びた構造物を含む。例えば、各メモリプロックは、第3方向に沿って伸びた複数のNANDストリングを含む。この場合、複数のNANDストリングは、第1及び第2方向に沿って特定距離ほど離隔して提供される。

30

#### 【0048】

図5及び図6を共に参照すると、複数のメモリプロック(BLK1～BLKi)は、ロウデコーダRD1によって選択される。例えば、ロウデコーダRD1は、メモリプロック(BLK1～BLKi)のうちのプロックアドレスに対応するメモリプロックを選択する。図1の第2～第4メモリプレーン(PL2～PL4)も第1メモリプレーンPL1と実質的に同様に具現され、図6を参照して上述した内容は、第2～第4メモリプレーン(PL2～PL4)に対しても適用される。

#### 【0049】

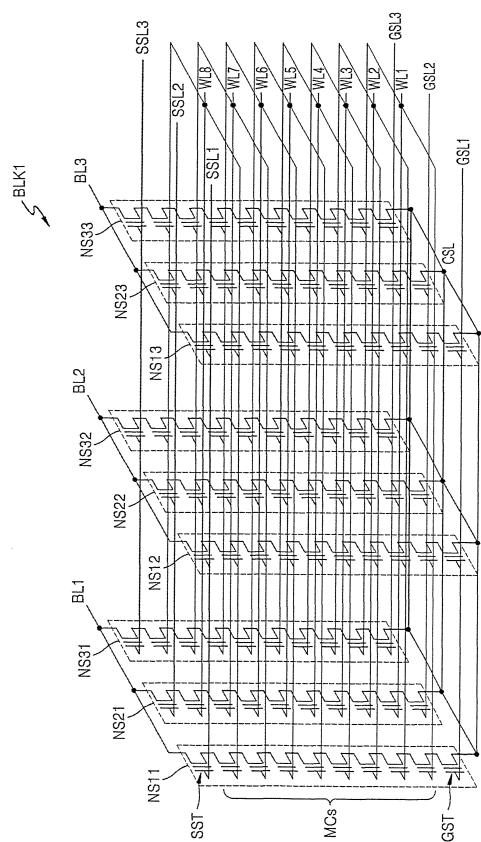

図7Aは、図6の第1メモリプロックBLK1の等価回路図である。

#### 【0050】

図7Aを参照すると、第1メモリプロックBLK1は、複数のNANDストリング(NS11～NS33)、複数のワードライン(WL1～WL8)、複数のビットライン(BL1～BL3)、複数の接地選択ライン(GSL1～GSL3)、複数のストリング選択ライン(SSL1～SSL3)、及び共通ソースラインCSLを含む。ここで、NANDストリングの個数、ワードラインの個数、ビットラインの個数、接地選択ラインの個数、及びストリング選択ラインの個数は、実施例によって多様に変更される。

40

#### 【0051】

第1ビットラインBL1と共にソースラインCSLとの間にNANDストリング(NS11、NS21、NS31)が提供され、第2ビットラインBL2と共にソースラインCSLとの間にNANDストリング(NS12、NS22、NS32)が提供され、第3ビットラインBL3と共にソースラインCSLとの間にNANDストリング(NS13、N

50

S 2 3、N S 3 3) が提供される。各 N A N D ストリング(例えば、N S 1 1)は、直列連結されたストリング選択トランジスタ S S T、複数のメモリセル M C、及び接地選択トランジスタ G S Tを含む。

#### 【0052】

ストリング選択トランジスタ S S Tは、対応するストリング選択ライン(SSL 1 ~ SSL 3)に連結される。複数のメモリセル M Cは、それぞれ対応するワードライン(WL 1 ~ WL 8)に連結される。接地選択トランジスタ G S Tは、対応する接地選択ライン(GSL 1 ~ GSL 3)に連結される。ストリング選択トランジスタ S S Tは対応するビットライン(BL 1 ~ BL 3)に連結され、接地選択トランジスタ G S Tは共通ソースライン C S Lに連結される。

10

#### 【0053】

本実施例において、同じ高さのワードライン(例えば、WL 1)はそれぞれ共通連結され、ストリング選択ライン(SSL 1 ~ SSL 3)はそれぞれ分離されて、接地選択ライン(GSL 1 ~ GSL 3)もそれぞれ分離される。図7では、3本のストリング選択ライン(SSL 1 ~ SSL 3)が同じ高さのワードラインを共有するものとして図示したが、本発明は、これに限定されない。例えば、2本のストリング選択ラインが同じ高さのワードラインを共有する。他の例として、4本のストリング選択ラインが同じ高さのワードラインを共有する。

#### 【0054】

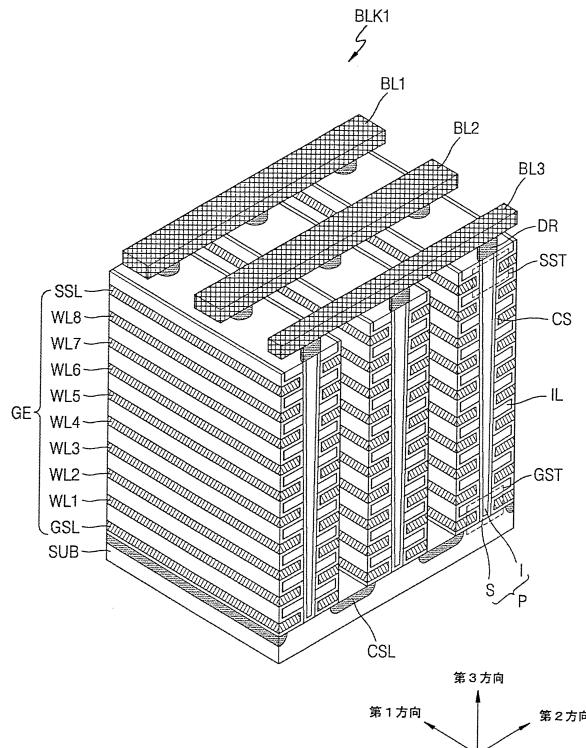

図7Bは、図6の第1メモリブロック B L K 1を示す斜視図である。

20

#### 【0055】

図7Bを参照すると、第1メモリブロック B L K 1は、基板 S U Bに対して垂直方向に形成される。基板 S U Bは、第1導電型(例えば、pタイプ)を有し、基板 S U B上に第1方向に沿って伸び、第2導電型(例えば、nタイプ)の不純物がドーピングされた共通ソースライン C S Lが提供される。隣接する2本の共通ソースライン C S L間の基板 S U B領域上に、第1方向に沿って伸びる複数の絶縁膜 I Lが第3方向に沿って順次に提供され、複数の絶縁膜 I Lが第3方向に沿って特定距離ほど離隔される。例えば、複数の絶縁膜 I Lは、シリコン酸化物のような絶縁物質を含む。

#### 【0056】

隣接する2本の共通ソースライン C S L間の基板 S U B領域上に、第1方向に沿って順次に配置され、第3方向に沿って複数の絶縁膜 I Lを貫通する複数のピラー(pillars)Pが提供される。例えば、複数のピラー Pは、複数の絶縁膜 I Lを貫通して基板 S U Bにコンタクトする。具体的に、各ピラー Pの表面層(surface layer)Sは、第1タイプを有するシリコン物質を含み、チャネル領域として機能する。一方、各ピラー Pの内部層 Iは、シリコン酸化物のような絶縁物質又はエアギャップ(air gap)を含む。

30

#### 【0057】

隣接する2本の共通ソースライン C S L間の領域で、絶縁膜 I L、ピラー P、及び基板 S U Bの露出した表面に沿って電荷保存層(charge storage layer)C Sが提供される。電荷保存層 C Sは、ゲート絶縁層(又は「トンネリング絶縁層」と称する)、電荷トラップ層、及びブロッキング絶縁層を含む。例えば、電荷保存層 C Sは、ONO(oxide-nitride-oxide)構造を有する。また、隣接する2本の共通ソースライン C S L間の領域で、電荷保存層 C Sの露出した表面上に、選択ライン(GSL、SSL)及びワードライン(WL 1 ~ WL 8)のようなゲート電極 G Eが提供される。

40

#### 【0058】

複数のピラー P上には、ドレイン又はドレインコンタクト D Rがそれぞれ提供される。例えば、ドレイン又はドレインコンタクト D Rは、第2導電型を有する不純物がドーピングされたシリコン物質を含む。ドレイン D R上に、第2方向に伸びて第1方向に沿って特定距離ほど離隔して配置されたビットライン(BL 1 ~ BL 3)が提供される。

50

**【 0 0 5 9 】**

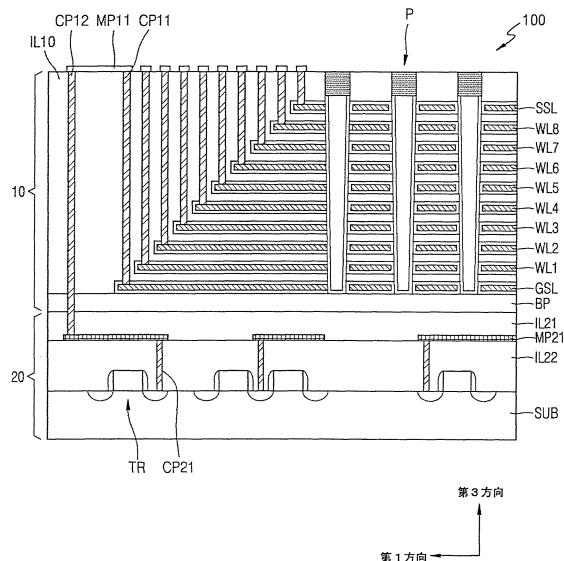

図 8 は、図 5 のメモリ装置 1 0 0 を示す断面図である。

**【 0 0 6 0 】**

図 8 を参照すると、第 2 半導体層 L 2 は、基板 S U B 、第 2 下部絶縁層 I L 2 2 、及び第 1 下部絶縁層 I L 2 1 を含み、第 2 半導体層 L 2 には、図 1 の制御回路 1 2 0 が配置される。基板 S U B は、単結晶シリコン又は単結晶ゲルマニウムのような半導体物質を含む半導体基板であり、シリコンウェーハから製造される。第 1 及び第 2 下部絶縁層 ( I L 2 1 、 I L 2 2 ) は、シリコン酸化物のような絶縁物質を用いて化学気相蒸着 ( c h e m i c a l vapor deposition : C V D ) 工程、スピンドルコートィング工程などを通じて形成される。

10

**【 0 0 6 1 】**

第 2 半導体層 L 2 に含まれる基板 S U B 上に複数の半導体素子、例えばトランジスタ T R が形成され、半導体素子は第 2 下部絶縁層 I L 2 2 を貫通するコンタクトプラグ C P 2 1 を介して第 1 下部絶縁層 I L 2 1 に形成されたメタルパターン M P 2 1 に電気的に連結される。第 2 半導体層 L 2 に形成された半導体素子は、図 5 の第 1 ~ 第 4 ロウデコーダ ( R D 1 ~ R D 4 ) 、第 1 ~ 第 4 ページバッファ ( P B 1 ~ P B 4 ) 、及び制御回路 1 2 0 に対応する回路を構成する。

**【 0 0 6 2 】**

第 1 半導体層 L 1 は第 2 半導体層 L 2 上に積層され、第 1 半導体層 L 1 には図 1 のメモリセルアレイ 1 1 0 が配置される。第 1 半導体層 L 1 は、ベース層 B P 及び上部絶縁層 I L 1 0 を含む。一実施例において、ベース層 B P は、ポリシリコンを使用してスパッタリング工程、C V D 工程、原子層蒸着 ( a t o m i c layer deposition : A L D ) 工程、物理気相蒸着 ( p h y s i c a l vapor deposition : P V D ) 工程などを通じて形成される。一実施例において、ベース層 B P は、第 1 下部絶縁層 I L 2 1 上に非晶質シリコン層を形成した後、熱処理又はレーザビームの照射によって非晶質シリコン層を単結晶シリコン層に変化させて形成され、これによって、ベース層 B P 内の欠陥が除去される。一実施例において、ベース層 B P は、ウェーハボンディング ( w a f e r bonding ) 工程を介して形成され、この場合、第 1 下部絶縁層 I L 2 1 上に、例えば単結晶シリコンウェーハを付着させ、ウェーハの上部を部分的に除去するか平坦化することで、ベース層 B P が形成される。

20

**【 0 0 6 3 】**

また、図 7 B を参照して上述したように、第 1 半導体層 L 1 でストリング選択ライン S S L 、ワードライン ( W L 1 ~ W L 8 ) 、及び接地選択ライン G S L がベース層 B P 上に第 3 方向に積層され、積層されたストリング選択ライン S S L 、ワードライン ( W L 1 ~ W L 8 ) 、及び接地選択ライン G S L を貫通するピラー P が形成される。

30

**【 0 0 6 4 】**

図 9 は、本発明の他の実施形態によるメモリシステム 1 0 a を概略的に示すブロック図である。

**【 0 0 6 5 】**

図 9 を参照すると、メモリシステム 1 0 a は、図 1 のメモリシステム 1 0 の変形実施例に対応し、図 1 ~ 図 8 を参照して上述した内容は、本実施例にも適用される。メモリシステム 1 0 a は、メモリ装置 1 0 0 a 及びメモリコントローラ 2 0 0 を含む。メモリ装置 1 0 0 a は、不揮発性メモリ装置であり、メモリチップとして具現される。メモリ装置 1 0 0 a はメモリセルアレイ 1 1 0 及び制御回路 1 2 0 a を含み、メモリセルアレイ 1 1 0 及び制御回路 1 2 0 a は単一メモリチップとして具現される。本実施例による制御回路 1 2 0 a は、図 1 の制御回路 1 2 0 と異なって具現されるため、以下では、制御回路 1 2 0 a を中心に説明する。

40

**【 0 0 6 6 】**

制御回路 1 2 0 a は、第 1 ~ 第 4 制御ロジック ( c o n t r o l l o g i c s ) ( C L 1 ~ C L 4 ) を含む。第 1 ~ 第 4 制御ロジック ( C L 1 ~ C L 4 ) は、それぞれ第 1 ~

50

第4メモリプレーン(PL1～PL4)に対応し、それぞれ第1～第4メモリプレーン(PL1～PL4)の動作を制御する。以下、図10を参照して第1～第4制御ロジック(CL1～CL4)の具体的な動作について詳述する。

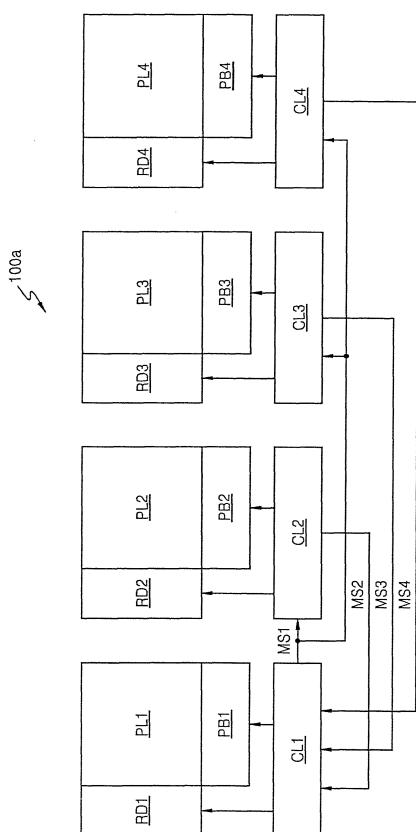

#### 【0067】

図10は、図9のメモリ装置100aを示すブロック図である。

#### 【0068】

図9及び図10を共に参照すると、メモリ装置100aは、第1～第4メモリプレーン(PL1～PL4)を含むメモリセルアレイ110を含み、例えばメモリセルアレイ110は、図4の第1半導体層L1に配置される。また、メモリ装置100aは、第1～第4ロウデコーダ(RD1～RD4)、第1～第4ページバッファ(PB1～PB4)、及び第1～第4制御ロジック(CL1～CL4)を更に含み、例えば第1～第4ロウデコーダ(RD1～RD4)、第1～第4ページバッファ(PB1～PB4)、及び第1～第4制御ロジック(CL1～CL4)は、図4の第2半導体層L2に配置される。10

#### 【0069】

第1制御ロジックCL1は、第1メモリプレーンPL1の動作をモニタリングすることで第1モニタリング信号MS1を生成し、生成された第1モニタリング信号MS1を第2～第4制御ロジック(CL2～CL4)に提供する。一実施例において、第1メモリプレーンPL1がピーク電力区間に進入した場合、第1モニタリング信号MS1は活性化され、例えばロジックハイレベルを有する。一実施例において、第1メモリプレーンPL1がピーク電力区間に进入していない場合、第1モニタリング信号MS1は、非活性化され、例えばロジックロウレベルを有する。例えば、第1モニタリング信号MS1は、フラグとして具現される。20

#### 【0070】

同様に、第2制御ロジックCL2は、第2メモリプレーンPL2の動作をモニタリングすることで第2モニタリング信号MS2を生成し、生成された第2モニタリング信号MS2を第1、第3及び第4制御ロジック(CL1、CL3、CL4)に提供する。第3制御ロジックCL3は、第3メモリプレーンPL3の動作をモニタリングすることで第3モニタリング信号MS3を生成し、生成された第3モニタリング信号MS3を第1、第2及び第4制御ロジック(CL1、CL2、CL4)に提供する。第4制御ロジックCL4は、第4メモリプレーンPL4の動作をモニタリングすることで第4モニタリング信号MS4を生成し、生成された第4モニタリング信号MS4を第1～第3制御ロジック(CL1～CL3)に提供する。30

#### 【0071】

第1制御ロジックCL1は、第1モニタリング信号MS1に基づいて第1メモリプレーンPL1がピーク電力区間に进入したか否かを判断する。判断の結果、第1メモリプレーンPL1がピーク電力区間に进入した場合、第1制御ロジックCL1は、第2～第4モニタリング信号(MS2～MS4)に基づいて第2～第4メモリプレーン(PL2～PL4)がピーク電力区間に进入したか否かを判断する。

#### 【0072】

判断の結果、第2～第4メモリプレーン(PL2～PL4)のうちの少なくとも1つがピーク電力区間に进入した場合、第1制御ロジックCL1は、第1メモリプレーンPL1の動作を遅延又は中止させる。一実施例において、第1制御ロジックCL1は、活性化された第2～第4モニタリング信号(MS2～MS4)のうちの少なくとも1つが非活性化されると、第2～第4メモリプレーン(PL2～PL4)のうちの少なくとも1つがピーク電力区間から外れたと判断し、第1メモリプレーンPL1の動作を再開させる。一実施例において、第1制御ロジックCL1は、第1メモリプレーンPL1の動作の中止時点から既定の時間が経過すると、第1メモリプレーンPL1の動作を再開させる。40

#### 【0073】

図11は、図4の第2半導体層L2aの一例の上面を示す平面図である。

#### 【0074】

50

図4、図9、図10、及び図11を共に参照すると、第2半導体層L2aはパッド領域PAD及び周辺回路領域を含み、周辺回路領域は第1～第4領域(R1～R4)を含む。パッド領域PADには複数の入出力パッドPが配置され、複数の入出力パッドPは第2半導体層L2上のメタル配線を介して第1～第4領域(R1～R4)に連結される。第1領域R1の上部には第1メモリプレーンPL1が配置され、第2領域R2の上部には第2メモリプレーンPL2が配置され、第3領域R3の上部には第3メモリプレーンPL3が配置され、第4領域R4の上部には第4メモリプレーンPL4が配置される。

#### 【0075】

第1領域R1には、第1ロウデコーダRD1、第1ページバッファPB1、及び第1制御ロジックCL1が配置される。第2領域R2には、第2ロウデコーダRD2、第2ページバッファPB2、及び第2制御ロジックCL2が配置される。第3領域R3には、第3ロウデコーダRD3、第3ページバッファPB3、及び第3制御ロジックCL3が配置される。第4領域R4には、第4ロウデコーダRD4、第4ページバッファPB4、及び第4制御ロジックCL4が配置される。図11では、第1～第4領域(R1～R4)のそれぞれに1つのロウデコーダ及び1つのページバッファが配置されるものとして図示したが、本発明は、これに限定されない。一実施例において、第1～第4領域(R1～R4)のそれぞれには、複数のロウデコーダ及び複数のページバッファが配置される。また、実施例によって、第1～第4領域(R1～R4)のそれぞれでロウデコーダ、ページバッファ、及び制御ロジックの配置は、多様に変更される。

#### 【0076】

第1制御ロジックCL1は、第2～第4制御ロジック(CL2～CL4)に連結され、第2～第4制御ロジック(CL2～CL4)から第2～第4モニタリング信号(MS2～MS4)を受信し、第2～第4制御ロジック(CL2～CL4)に第1モニタリング信号MS1を提供する。第1制御ロジックCL1は、第1ロウデコーダRD1及び第1ページバッファPB1に連結される。これにより、第1制御ロジックCL1は、第1～第4メモリプレーン(PL1～PL4)の動作をモニタリングし、モニタリングの結果に基づいて第1～第4メモリプレーン(PL1～PL4)のピーク電力区間が少なくとも部分的に分散されるように、第1メモリプレーンPL1の動作を制御する。

#### 【0077】

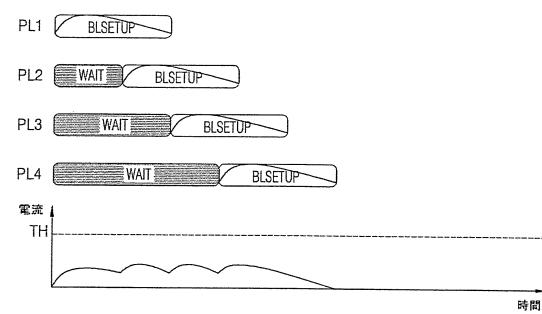

図12A及び図12Bは、図9のメモリ装置100aのピーク制御動作の多様な例を示す図である。

#### 【0078】

第1制御ロジックCL1は、第1～第4モニタリング信号(MS1～MS4)に基づいて第1～第4メモリプレーン(PL1～PL4)の動作がいずれもピーク電力区間に対応すると判断した場合、例えば第1～第4メモリプレーン(PL1～PL4)の動作がいずれもビットラインセットアップ区間BLSETUPに対応する場合、第1制御ロジックCL1は、第1～第4メモリプレーン(PL1～PL4)のビットラインセットアップ区間BLSETUPが重畠しないように、第1メモリプレーンPL1のビットラインセットアップ動作を中止させる。

#### 【0079】

例えば、図12Aを参照すると、第1制御ロジックCL1は、第2～第4メモリプレーン(PL2～PL4)のビットラインセットアップ区間BLSETUPが終了するまで、第1メモリプレーンPL1に対してビットラインセットアップ動作を中止させる。第1制御ロジックCL1は、PMICの最大電力限界を考慮して、第1メモリプレーンPL1に対するビットラインセットアップ動作の再開時点を適応的に決定する。第1制御ロジックCL1は、第2～第4メモリプレーン(PL2～PL4)のビットラインセットアップ区間BLSETUPがいずれも終了すると、第1メモリプレーンPL1に対するビットラインセットアップ動作を再開させる。一実施例において、第1制御ロジックCL1は、第2～第4メモリプレーン(PL2～PL4)のうちの少なくとも1つのビットラインセットアップ区間BLSETUPが終了すると、第1メモリプレーンPL1に対するビットライ

10

20

30

40

50

ンセットアップ動作を再開させる。

**【0080】**

図12Bを参照すると、第1制御ロジックCL1は、第1～第4メモリプレーン(PL1～PL4)のビットラインセットアップ区間BLSETUPが完全に重畠しないように、第1メモリプレーンPL1のビットラインセットアップ動作を中止させる。図2Aを参考して上述したように、第1～第4メモリプレーン(PL1～PL4)のそれぞれの動作に要求される電流量は、ビットラインセットアップ区間BLSETUPの初期にピーク値を有する。従って、第1制御ロジックCL1は、第1～第4メモリプレーン(PL1～PL4)のビットラインセットアップ区間BLSETUPの初期区間が重畠しないように、第1メモリプレーンPL1のビットラインセットアップ動作を中止させる。例えば、第1制御ロジックCL1は、予め決められた一定時間区間、第1メモリプレーンPL1に対するビットラインセットアップ動作を中止させる。

10

**【0081】**

図13は、本発明の一実施形態によるメモリ装置の動作方法を示すフローチャートである。

**【0082】**

図13を参考すると、メモリ装置の動作は、單一メモリチップに含まれる複数のメモリプレーンのピーク電力又はピーク電流を制御する動作に対応し、例えば図1のメモリ装置100又は図9のメモリ装置100aで行われる。図1～図12Bを参考して上述した内容は本実施例にも適用され、重複説明は省略する。

20

**【0083】**

段階S110において、複数のメモリプレーンの動作をモニタリングする。一実施例において、制御回路120のモニタリングロジック121は、複数のメモリプレーンの動作をモニタリングすることでモニタリング信号MSを生成する。一実施例において、第1～第4制御ロジック(CL1～CL4)のそれぞれは対応するメモリプレーンの動作をモニタリングすることで第1～第4モニタリング信号(MS1～MS4)をそれぞれ生成する。

**【0084】**

段階S120において、少なくとも1つのメモリプレーンがピーク電力区間に對応するか否かを判断する。一実施例において、制御回路120のモニタリングロジック121は、複数のメモリプレーンのうちの少なくとも1つがピーク電力区間に進入したか否かを判断する。判断の結果、少なくとも1つのメモリプレーンがピーク電力区間に對応する場合、段階S130を行い、そうではない場合、段階S150を行う。

30

**【0085】**

段階S130において、他のメモリプレーンがピーク電力区間に對応するか否かを判断する。一実施例において、制御回路120のモニタリングロジック121は、複数のメモリプレーンのうちの少なくとも1つの他のメモリプレーンがピーク電力区間に进入したか否かを判断する。判断の結果、他のメモリプレーンがピーク電力区間に對応する場合、段階S140を行い、そうではない場合、段階S150を行う。

**【0086】**

一実施例において、メモリ装置の動作方法は、段階S120とS130との間に、複数のプレーン間の優先順位情報を用いて他のメモリプレーンを決定する段階を更に含む。具体的に、モニタリングロジック121は、段階S120でピーク電力区間に對応すると判断されたメモリプレーンよりも高い優先順位を有するメモリプレーンがピーク電力区間に對応するか否かを判断する。

40

**【0087】**

段階S140において、ピーク電力区間が少なくとも部分的に分散されるように複数のメモリプレーンの動作を制御する。一実施例において、制御回路120のピーク制御ロジック122は、ピーク電力区間が完全に重畠しないように、一部のメモリプレーンの動作を中止させる。一実施例において、制御回路120のピーク制御ロジック122は、ピーク電力区間の初期区間が重畠されないように、一部メモリプレーンの動作を中止させる。

50

段階 S 150において、少なくとも 1 つのメモリプレーンに対する動作を進める。一実施例において、制御回路 120 のピーク制御ロジック 122 は、少なくとも 1 つのメモリプレーンに対する動作が正常に行われるよう、ロウデコーダ及びページバッファなどを制御する。

#### 【 0 0 8 8 】

図 14 は、本発明の一実施形態によるメモリコントローラ 200 とメモリ装置 100 との間の動作を示すフロー チャートである。

#### 【 0 0 8 9 】

図 14 を参照すると、本実施形態は、図 13 の動作方法の一具現例に対応し、図 1 ~ 図 13 を参照して上述した内容は本実施例にも適用され、重複説明は省略する。図 14 では、メモリ装置が図 1 のメモリ装置 100 に対応するものとして図示したが、本発明はこれに限定されず、図 14 のメモリ装置は図 9 のメモリ装置 100a に対応してもよい。

10

#### 【 0 0 9 0 】

段階 S 210において、メモリコントローラ 200 は、ピーク電力区間を指定する。例えば、メモリコントローラ 200 のピーク区間決定部 210 は、ピーク電力区間、ピーク電流区間、又はピーク制御区間を指定する。例えば、ピーク電力区間は、プログラム動作のためのビットラインセットアップ区間、読出動作のためのビットラインプリチャージ区間、及びプログラム動作又は読出動作前のラッチ初期化区間のうちの少なくとも 1 つに該当する。

20

#### 【 0 0 9 1 】

S 220において、メモリコントローラ 200 は、複数のプレーン間の優先順位を指定する。例えば、メモリコントローラ 200 のプレーン優先順位決定部 220 は、複数のプレーン間の優先順位を決定する。一実施例において、段階 S 210 と段階 S 220 は、実質的に同時に行われる。他の実施例において、段階 S 220 が先に行われ、次いで段階 S 210 が行われる。

#### 【 0 0 9 2 】

一実施例において、ピーク電力区間に関する情報及びプレーン優先順位情報は、メモリ装置 100 の出荷時に予め決定され、メモリ装置 100 のメモリセルアレイ 110 にプログラムされる。メモリシステム 10 に電源が印加されると、即ちブーティングの後、メモリコントローラ 200 は、I D R を通じてメモリセルアレイ 110 にプログラムされたピーク電力区間に関する情報を読み出す。

30

#### 【 0 0 9 3 】

段階 S 230において、メモリコントローラ 200 は、メモリ装置 100 にアドレス A D D R 、コマンド C M D 、及び制御信号 C T R L を伝送する。一実施例において、メモリコントローラ 200 は、プログラム動作を行うように、メモリ装置 100 にデータを更に伝送する。一実施例において、メモリコントローラ 200 は、ピーク電力区間に関する情報及び優先順位情報を、セットフィーチャーコマンドを用いてメモリ装置 100 に伝送する。

#### 【 0 0 9 4 】

段階 S 240において、メモリ装置 100 は、第 1 メモリプレーン P L 1 の動作をモニタリングする。例えば、図 1 のモニタリングロジック 121 又は図 9 の第 1 制御ロジック C L 1 は、第 1 メモリプレーン P L 1 の動作がピーク電力区間に応するか否かを判断することで、モニタリング信号を生成する。段階 S 250において、メモリ装置 100 は、第 1 メモリプレーン P L 1 がピーク電力区間に応するか否かを判断する。判断の結果、第 1 メモリプレーン P L 1 がピーク電力区間に応する場合、段階 S 270 を行い、そうではない場合、段階 S 290 を行う。

40

#### 【 0 0 9 5 】

段階 S 260において、メモリ装置 100 は、第 2 メモリプレーン P L 2 の動作をモニタリングする。例えば、図 1 のモニタリングロジック 121 又は図 9 の第 2 制御ロジック C L 2 は、第 2 メモリプレーン P L 2 の動作がピーク電力区間に応するか否かを判断す

50

ることで、モニタリング信号を生成する。段階 S 270において、メモリ装置 100は、第2メモリプレーン PL2がピーク電力区間に對応するか否かを判断する。判断の結果、第2メモリプレーン PL2がピーク電力区間に對応する場合、段階 S 280を行い、そうではない場合、段階 S 290を行う。

#### 【0096】

段階 S 280において、メモリ装置 100は、第1メモリプレーン PL1の動作を中止する。例えば、図1のピーク制御ロジック 122又は図9の第1制御ロジック CL1は、第1メモリプレーン PL1の動作を一定時間中止させる。段階 S 290において、メモリ装置 100は、第1メモリプレーン PL1の動作を進める。例えば、図1のピーク制御ロジック 122又は図9の第1制御ロジック CL1は、第1メモリプレーン PL1の動作を進める。また、段階 S 280の後、一定時間が経過すると、図1のピーク制御ロジック 122又は第1制御ロジック CL1は、第1メモリプレーン PL1の動作を再開させる。

10

#### 【0097】

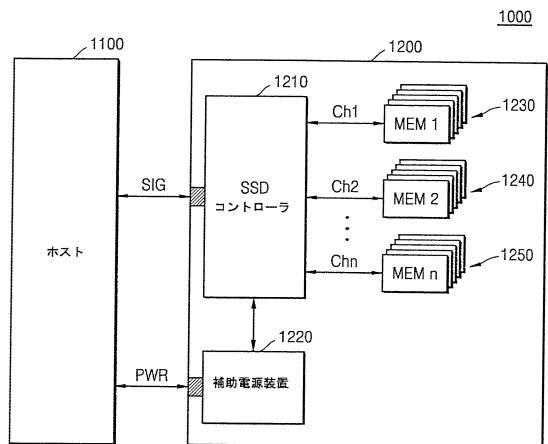

図15は、本発明の一実施形態によるメモリ装置をSSDシステム 1000に適用した例を示すブロック図である。

#### 【0098】

図15を参照すると、SSDシステム 1000は、ホスト 1100及び SSD 1200を含む。SSD 1200は、信号コネクタを通じてホスト 1100と信号を送受信し、電源コネクタを通じて電源が入力される。SSD 1200は、SSDコントローラ 1210、補助電源装置 1220、及びメモリ装置(1230、1240、1250)を含む。メモリ装置(1230、1240、1250)は、垂直積層型NANDフラッシュメモリ装置である。ここで、SSD 1200は、図1～図14を参照して上述した実施例を用いて具現される。

20

#### 【0099】

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【符号の説明】

##### 【0100】

|                         |             |    |

|-------------------------|-------------|----|

| 10、10a                  | メモリシステム     | 30 |

| 100、100a、1230、1240、1250 | メモリ装置       |    |

| 110                     | メモリセルアレイ    |    |

| 120、120a                | 制御回路        |    |

| 121                     | モニタリングロジック  |    |

| 122                     | ピーク制御ロジック   |    |

| 200                     | メモリコントローラ   |    |

| 210                     | ピーク区間決定部    |    |

| 220                     | プレーン優先順位決定部 |    |

| 1000                    | SSDシステム     |    |

| 1100                    | ホスト         | 40 |

| 1200                    | SSD         |    |

| 1210                    | SSDコントローラ   |    |

| 1220                    | 補助電源装置      |    |

| B L、B L1～B L3           | ビットライン      |    |

| B LK1～B LKi             | メモリブロック     |    |

| B P                     | ベース層        |    |

| C L1～C L4               | 第1～第4制御ロジック |    |

| C P11、C P12、C P21       | コンタクトプラグ    |    |

| C S                     | 電荷保存層       |    |

| C S L                   | 共通ソースライン    | 50 |

D R ドレン又はドレンコンタクト

G E ゲート電極

G S L、G S L 1 ~ G L S 3 接地選択ライン

G S T 接地選択トランジスタ

I 内部層

I L 絶縁膜

I L 1 0 上部絶縁層

L 1、L 2 第1、第2半導体層

I L 2 1 第1下部絶縁層

I L 2 2 第2下部絶縁層

L 2 a 第2半導体層

M C メモリセル

M P 2 1 メタルパターン

M S 1 ~ M S 4 第1~第4モニタリング信号

N S 1 1 ~ N S 3 1、N S 1 2 ~ N S 3 2、N S 1 3 ~ N S 3 3 N A N Dストリング

P ピラー

P、P' 入出力パッド

P A D パッド領域

P B 1 ~ P B 4 第1~第4ページバッファ

P L 1 ~ P L 4 第1~第4メモリブレーン

R 1 ~ R 4 第1~第4領域

R D 1 ~ R D 4 第1~第4ロウデコーダ

S 表面層

S S L、S S L 1 ~ S S L 3 ストリング選択ライン

S S T ストリング選択トランジスタ

S U B 基板

T R トランジスタ

W L、W L 1 ~ W L 8 ワードライン

【図面】

【図1】

【図2 A】

30

40

50

【図 2 B】

【図 2 C】

10

【図 3 A】

【図 3 B】

20

【図 3 C】

【図 4】

30

40

50

【図 5】

【図 6】

10

20

第1方向

第3方向

第2方向

【図 7 A】

【図 7 B】

30

40

第3方向

第1方向

第2方向

50

【図 8】

【図 9】

【図 10】

【図 11】

10

20

30

40

50

【図 1 2 A】

【図 1 2 B】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図 1 5】

10

20

30

40

50

---

フロントページの続き

(72)発明者 朴 相 元

大韓民国 ソウル特別市 銅雀区 メ峯路 123 102棟 704号

(72)発明者 沈 ドン 教

大韓民国 ソウル特別市 江南区 永東大路 114街 56 503棟 1101号

(72)発明者 郭 東 勳

大韓民国 京畿道 華城市 東灘公園路 21-40 928棟 1703号

審査官 打出 義尚

(56)参考文献 特開2012-043420 (JP, A)

特開2011-065708 (JP, A)

特開2008-197807 (JP, A)

米国特許出願公開第2016/0307910 (US, A1)

TALLIS, Billy, Micron 3D NAND Status Update, 2016年02月, [https://web.archive.org/web/20160213093225/https://www.anandtech.com/show/10028/micron-3d-nand-status-u](https://web.archive.org/web/20160213093225/https://www.anandtech.com/show/10028/micron-3d-nand-status-update)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 12 / 06

G 06 F 12 / 00