**Demande de brevet déposée pour la Suisse et le Liechtenstein**

Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

**(12) FASCICULE DE LA DEMANDE A3**      (11)

**621917 G**

(21) Numéro de la demande: 7846/77

(71) Requérant(s):

Centre Electronique Horloger S.A., Neuchâtel

(22) Date de dépôt: 27.06.1977

(72) Inventeur(s):

Jean Fellrath, Neuchâtel

Eric Vittoz, Cernier

(42) Demande publiée le: 13.03.1981

(74) Mandataire:

William Blanc & Cie conseils en propriété

industrielle S.A., Genève

(44) Fascicule de la demande

publié le: 13.03.1981

(56) Rapport de recherche au verso

**(54) Dispositif intégré de commande.**

(57) Le dispositif de commande comporte un multiplicateur de tension 1, entièrement intégré, alimenté par des impulsions d'horloge H et connecté par la sortie G à la grille de commande de transistors de puissance T<sub>2</sub>, T<sub>3</sub>. Un circuit de sélection 3 et un transistor T<sub>1</sub> sont agencés pour déclencher le fonctionnement du multiplicateur de tension au début de la durée d'un signal de commande d'entrée E et à court-circuiter la sortie G à la fin de cette durée.

L'invention permet de réduire sensiblement la surface des transistors de puissance et, par conséquent, notamment de réduire le prix de revient des circuits utilisant le présent dispositif de commande.

# RAPPORT DE RECHERCHE

## RECHERCHENBERICHT

Demande de brevet No.:

Patentgesuch Nr.:

CH 7846/77

I.I.B. Nr.:

HO 12738

### Documents considérés comme pertinents Einschlägige Dokumente

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile | Revendications concernées<br>Betrifft Anspruch<br>Nr. |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|                        | <i>US - A - 3818484 (T. NAKAMURA et al.)</i><br>* colonne 3, lignes 15 à 25; figure 2 *                                                                                   | 1                                                     |

|                        | <i>FR - A - 2332646 (J.C. BERNEY S.A.)</i><br>* page 4, revendication; figure unique *                                                                                    | 4                                                     |

|                        | <i>CH - A - 6724/71 (SESCOSEM)</i><br>* col. 3, lignes 31-33; figure 8 *                                                                                                  | 1                                                     |

Domaines techniques recherchés

Recherchierte Sachgebiete

(INT. CL. 2)

G04K 3/00

G04F 5/00

G04C 17/02

G04C 17/00

H02M 3/155

### Catégorie des documents cités Kategorie der genannten Dokumente:

- X: particulièrement pertinent von besonderer Bedeutung

- A: arrière-plan technologique technologischer Hintergrund

- O: divulgation non-écrite nichtschriftliche Offenbarung

- P: document intercalaire Zwischenliteratur

- T: théorie ou principe à la base de l'invention der Erfahrung zugrunde liegende Theorien oder Grundsätze

- E: demande faisant interférence kollidierende Anmeldung

- L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument

- &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; übereinstimmendes Dokument

### Etendue de la recherche/Umfang der Recherche

Revendications ayant fait l'objet de recherches

Recherchierte Patentansprüche:

ensemble

Revendications n'ayant pas fait l'objet de recherches

Nicht recherchierte Patentansprüche:

Raison:

Grund:

Date d'achèvement de la recherche/Abschlussdatum der Recherche

27 février 1978

Examinateur I.I.B./I.I.B Prüfer

## REVENDICATIONS

1. Dispositif intégré de commande à transistor à effet de champ et à grille isolée, comportant au moins un transistor de puissance, dont le chemin de conduction est connecté en série avec un dispositif à commander, entre les bornes d'une source de tension, et un circuit de commande ayant au moins une entrée connectée à une source de signaux de commande d'entrée, et ayant au moins une sortie connectée à la grille dudit transistor de puissance pour lui fournir des signaux de commande à une tension plus élevée que celle des signaux de commande d'entrée, et que celle de la source de tension, caractérisé en ce que le circuit de commande (1, 2, 3, 3', T<sub>1</sub>) comporte au moins un multiplicateur de tension (1) formé par une chaîne d'éléments redresseurs (D) dont les chemins de conduction sont connectés en série, dans le même sens, entre une première connexion d'entrée (P) et une connexion de sortie (G) du multiplicateur de tension, et par des capacités de stockage (C) connectées entre les points de connexion communs consécutifs de ces éléments redresseurs et, alternativement, ladite première (P) et une deuxième ( $\bar{P}$ ) connexion d'entrée du multiplicateur de tension, ces deux connexions d'entrée étant munies de moyens (2) pour assurer que les signaux qui leur sont appliqués soient en opposition de phase, et en ce que le circuit de commande comporte un dispositif de commande du multiplicateur de tension (3, T<sub>1</sub>) qui comprend au moins un circuit de sélection (3) ayant au moins deux connexions d'entrée (E, H) et une connexion de sortie (P), une première connexion d'entrée (E) étant reliée à ladite source de signaux de commande d'entrée, et la deuxième connexion (H) étant reliée à une source de tension de commande périodique d'une période au moins plusieurs fois plus courte que la durée d'un signal de commande d'entrée, ledit circuit de sélection étant monté, par sa deuxième connexion d'entrée (H) et sa connexion de sortie (P), en série avec ladite chaîne d'éléments redresseurs, entre ladite source de tension de commande périodique et la grille du transistor de puissance (T<sub>2</sub>), le dispositif de commande (3, T<sub>1</sub>) du multiplicateur de tension étant agencé de façon à déclencher le fonctionnement du multiplicateur de tension au début de la durée de chaque signal de commande d'entrée et à court-circuiter la sortie (G) du circuit de commande à la fin de la durée de chaque signal de commande d'entrée.

2. Dispositif selon la revendication 1, caractérisé en ce que le circuit de sélection est un circuit logique de coïncidence dont la deuxième entrée est connectée à la sortie du dispositif fournitant ladite tension de commande périodique et dont la sortie est connectée à la première entrée du multiplicateur de tension, la sortie de ce dernier étant connectée à la grille du transistor de puissance à commander, un transistor de décharge étant connecté, par son chemin de conduction, dans le circuit de grille du transistor de puissance, et, par sa grille, à ladite source de signaux de commande d'entrée, de manière à décharger la capacité de grille du transistor de puissance à la fin de chacun des signaux de commande.

3. Dispositif selon la revendication 1, comportant au moins deux transistors de puissance à canal p, caractérisé en ce que le circuit de commande comporte au moins deux circuits de sélection formés chacun par deux paires de transistors MOS complémentaires connectées entre la sortie d'un multiplicateur de tension commun aux circuits de sélection et agencé pour fournir une tension négative, et, d'autre part, la borne positive de la source de tension d'alimentation, la grille du transistor n de chaque paire étant connectée au point de connexion commun des drains des transistors n et p de l'autre paire, les grilles des transistors p étant munies de moyens pour assurer que les signaux de commande d'entrée leur soient appliqués en opposition de phase, et les drains d'une des paires de transistors étant connectés à la grille du transistor de puissance correspondant, le multiplicateur de tension

étant connecté par ses entrées au dispositif fourni la tension de commande périodique.

4. Dispositif selon la revendication 1, comportant au moins deux transistors de puissance à canal n, caractérisé en ce que le circuit de commande comporte au moins deux circuits de sélection comprenant chacun un transistor d'aiguillage à canal n dont le drain est connecté à la sortie d'un multiplicateur de tension commun aux circuits de sélection et agencé pour fournir une tension positive, la source de ce transistor étant reliée à sa grille par l'intermédiaire d'une diode et sa grille étant connectée, d'autre part, par l'intermédiaire d'une capacité, à la sortie d'un circuit logique de coïncidence, deux entrées dudit circuit de coïncidence étant connectées respectivement au dispositif fourni la tension de commande périodique et à la source de signaux de commande d'entrée, deux transistors de décharge à canal n étant connectés dans chaque circuit de sélection et étant reliés par leur grille à la source de signaux de commande d'entrée, de manière à décharger respectivement la capacité de grille du transistor d'aiguillage et la capacité reliée au circuit de coïncidence, la source du transistor d'aiguillage formant la sortie du circuit de sélection et étant connectée à la grille du transistor de puissance correspondant, le multiplicateur de tension étant connecté par ses entrées au dispositif fourni la tension de commande périodique.

5. Dispositif selon la revendication 2, comportant au moins deux paires de transistors de puissance de même type de conduction, dont les chemins de conduction sont, dans chaque paire, montés en série dans le même sens, entre les bornes de la source de tension d'alimentation, les points de connexion communs de chaque paire étant connectés au dispositif à commander, caractérisé en ce que le circuit de commande comporte deux circuits de sélection et présente deux sorties reliées chacune aux grilles de deux transistors de puissance ne faisant pas partie de la même paire et étant connectées à des bornes opposées de la source de tension d'alimentation.

6. Dispositif selon la revendication 1, caractérisé en ce que le multiplicateur de tension est réalisé en technologie de transistors MOS complémentaires à grille de silicium, les capacités de stockage étant obtenues par la mise en parallèle des capacités silicium polycristallin/caisson sur oxyde mince et silicium polycristallin/métal.

45 La présente invention concerne un dispositif intégré de commande à transistor à effet de champ et à grille isolée, comportant au moins un transistor de puissance, dont le chemin de conduction est connecté en série avec le dispositif à commander, entre les bornes d'une source de tension, et un circuit de commande ayant au moins une entrée connectée à une source de signaux de commande d'entrée, et ayant une sortie connectée à la grille dudit transistor de puissance pour lui fournir des signaux de commande à une tension plus élevée que celle des signaux de commande d'entrée et que celle de la source de tension.

55 De nombreux circuits pour appareils de petit volume tels que les montres et les calculatrices de poche sont alimentés par des batteries. La tension est alors limitée à quelques volts si l'on ne veut pas occuper trop de place avec les batteries. Les dispositifs d'affichage, par exemple micromoteur de la montre ou les diodes électroluminescentes de l'affichage de la calculatrice, nécessitent des courants relativement grands.

Les transistors de puissance utilisés pour la commande à courant élevé d'un dispositif extérieur, tel que par exemple un micromoteur pas à pas ou un affichage LED, sont habituellement commandés eux-mêmes par un dispositif fourni des signaux de commande à tension relativement basse. De tels transistors de puissance, conçus pour une commande à basse tension, occupent une grande partie de la surface totale du circuit intégré, ce qui est

un inconvénient majeur, quant au coût et au rendement de fabrication.

On a déjà proposé (brevet français N° 2332646), pour commander des transistors MOS de type n, d'élèver la tension de commande au moyen d'un circuit de commande comportant une capacité de stockage. Ce circuit nécessite cependant une capacité d'une valeur largement supérieure aux capacités des grilles des transistors à commander, de sorte qu'elle ne se prête pas, dans la pratique, à une intégration. D'autre part, l'élévation de tension qui peut ainsi être réalisée est limitée.

On connaît par ailleurs, dans des dispositifs de commande intégrés pour dispositifs d'affichage à cristaux liquides, des multiplicateurs de tension utilisant des diodes Schottky et des capacités extérieures (brevet USA N° 3818484). Ces multiplicateurs sont conçus pour délivrer l'énergie d'alimentation nécessaire pour ces dispositifs d'affichage et leurs circuits de commande, ce qui conditionne leur mode de réalisation et rend très important le rendement énergétique obtenu.

L'invention vise à fournir un dispositif de commande permettant de réduire dans une large mesure la surface nécessaire pour les transistors de puissance et de fabriquer ceux-ci avec un bon rendement, comme des transistors de dimensions courantes, et permettant d'utiliser des circuits entièrement intégrés pour la commande de ces transistors.

A cet effet, le dispositif précédemment mentionné est construit comme cela est enseigné par la caractéristique de la revendication 1.

La dimension des transistors de puissance peut être considérablement réduite si l'on élève la tension de commande de la grille de ces transistors. Cela est obtenu, selon l'invention, au moyen de multiplicateurs de tension utilisant des capacités très faibles et réalisés entièrement en technologie intégrée. Ces multiplicateurs permettent une élévation importante de la tension de commande et, du fait qu'ils commandent la grille des transistors MOS, ils ne doivent fournir pratiquement aucune énergie.

Il est à noter que l'utilisation de multiplicateurs de tension selon l'invention ralentit le temps d'établissement du signal de commande des transistors de puissance. Au cas où l'on effectue un aiguillage de la tension élevée produite dans un multiplicateur de tension sur différents transistors de puissance, il se produit une chute momentanée de la tension élevée à chaque commande. Or, il s'avère que, par exemple, dans la commande d'un affichage, le temps de montée du signal de commande des transistors de puissance peut être prolongé passablement par rapport aux signaux de commande habituels. L'optimisation du circuit intégré de commande permet donc de satisfaire aux spécifications imposées par l'affichage, tout en réalisant une très importante réduction de place.

Les avantages obtenus par l'invention sont notamment les suivants : réduction en surface des transistors de puissance d'un facteur voisin de 4, permettant de loger un plus grand nombre de circuits sur une plaque et d'accroître notablement le rendement de fabrication (en effet, la probabilité de défaut sur un circuit est une fonction rapidement croissante de sa surface). Il en résulte une diminution importante du coût de fabrication des circuits. De plus, certains circuits, comportant un grand nombre de transistors de puissance, devaient précédemment être réalisés en plusieurs puces. L'invention permet de réaliser le même circuit sur un nombre réduit de puces, souvent même sur une seule puce. La diminution des contacts qui en résulte contribue à une nouvelle réduction de prix et à une augmentation de la fiabilité.

Différentes formes d'exécution du dispositif selon l'invention sont décrites ci-après, à titre d'exemples, et sont illustrées dans le dessin annexé, dans lequel :

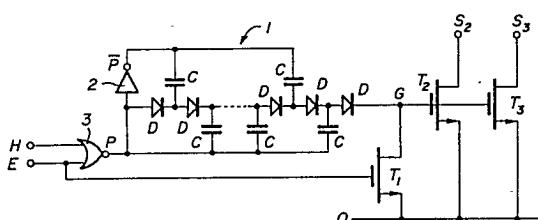

la fig. 1 est le schéma d'un dispositif à commande directe de transistors de puissance à partir d'un multiplicateur de tension ;

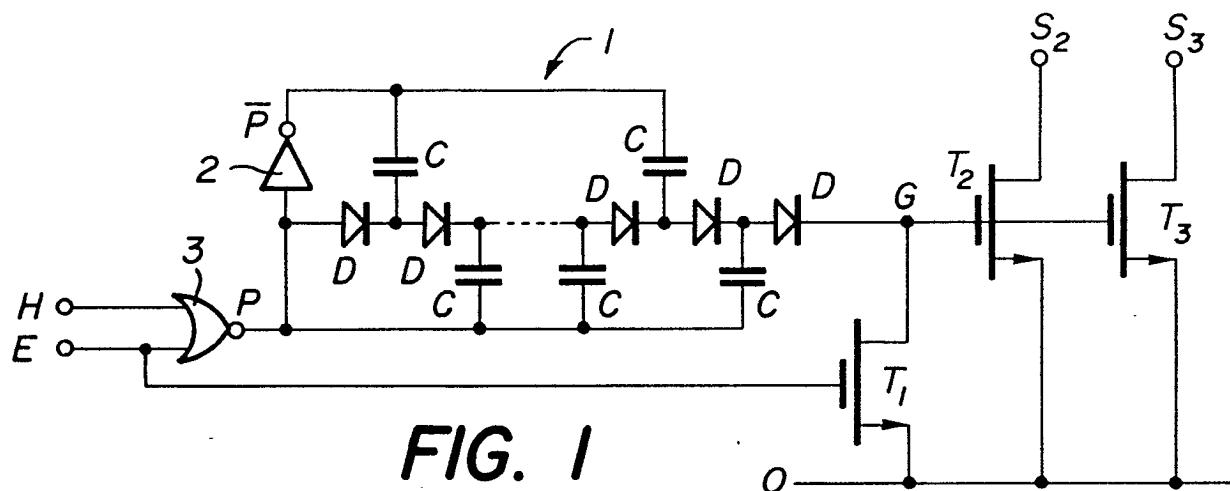

la fig. 2 est une représentation de signaux apparaissant en différents points du dispositif de la fig. 1 ;

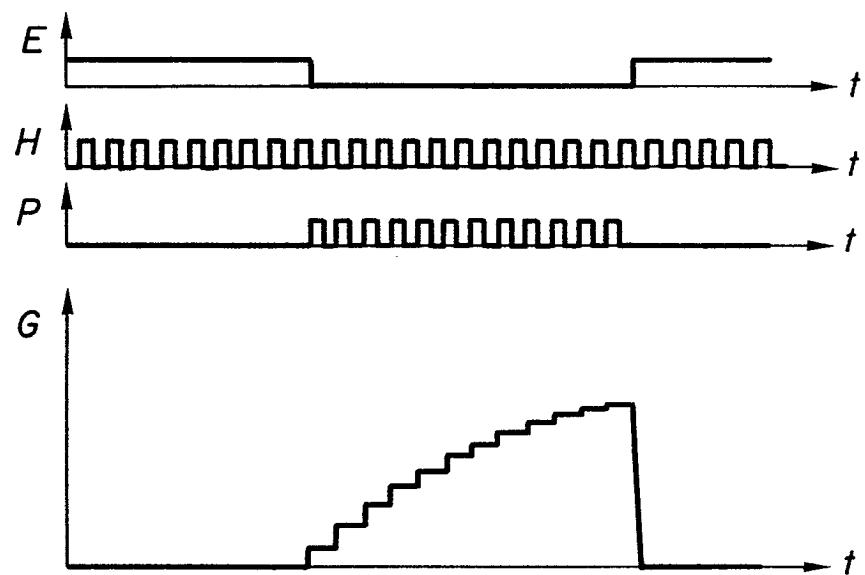

la fig. 3 est le schéma d'un dispositif de commande d'un moteur pas à pas ;

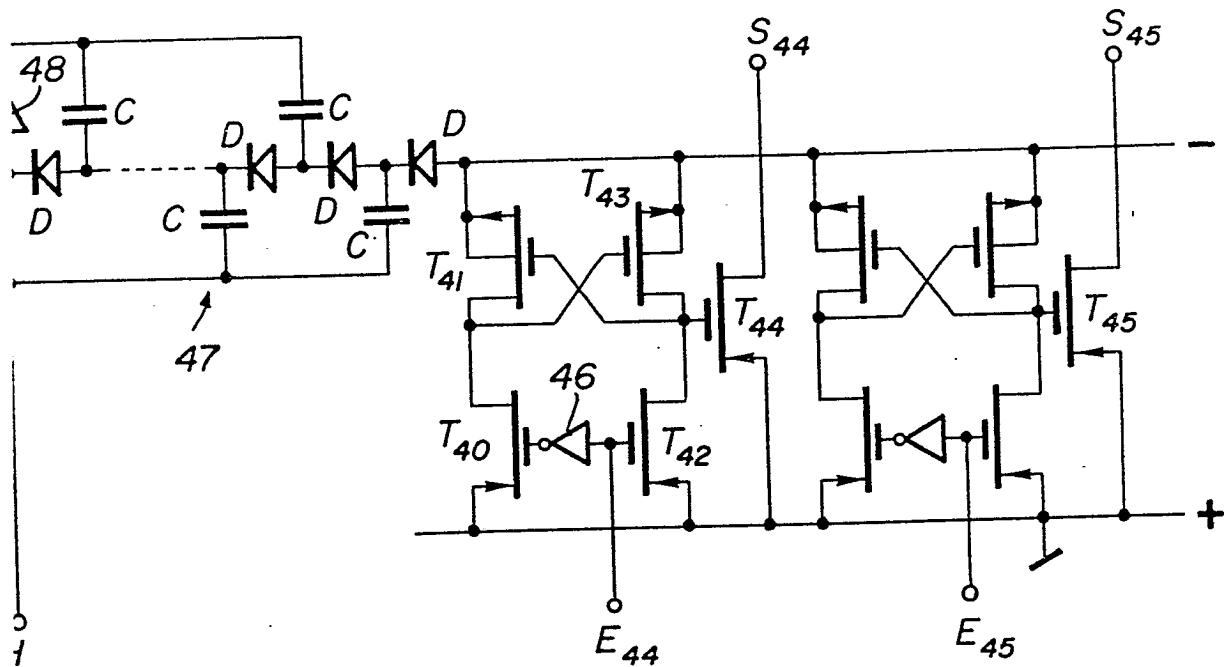

la fig. 4 est le schéma d'un dispositif avec aiguillage de la tension de commande sur différents transistors de puissance à canal p ;

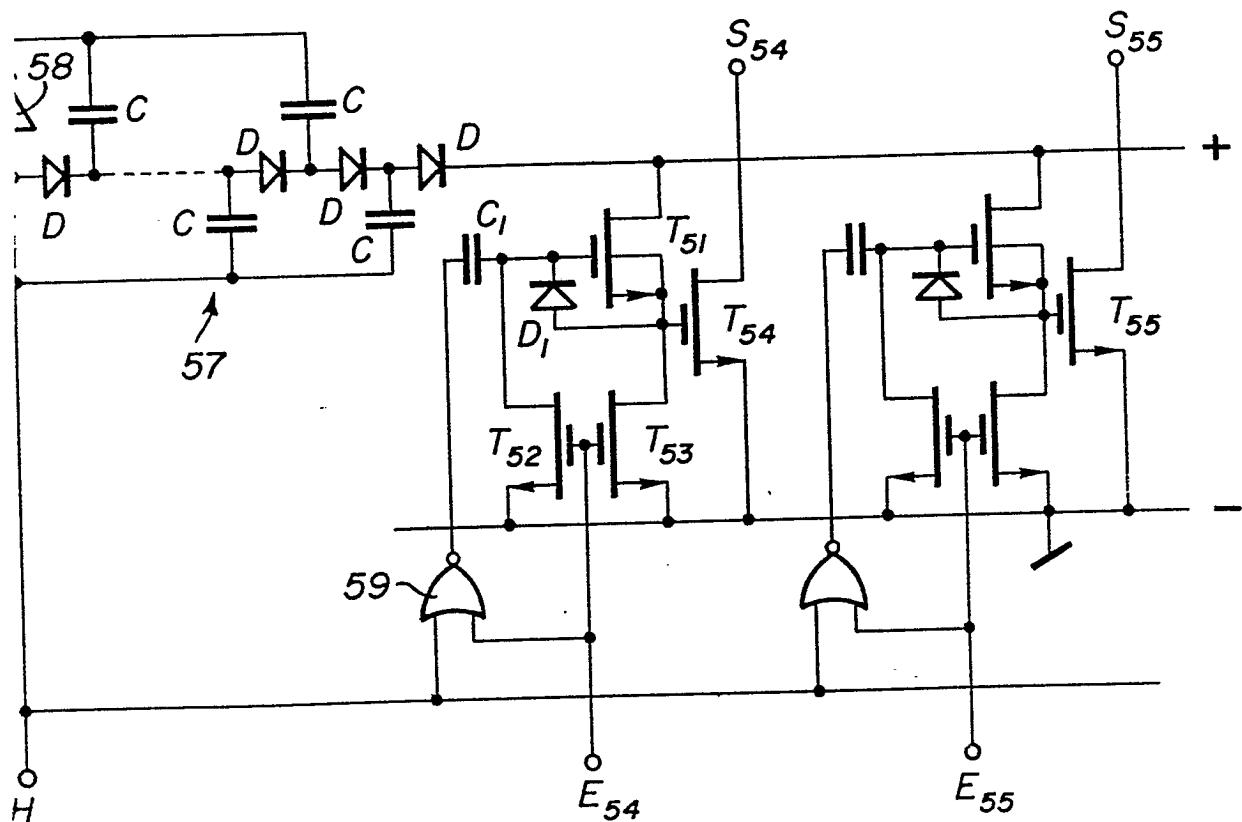

la fig. 5 est le schéma d'un dispositif similaire avec aiguillage de la tension de commande sur différents transistors de puissance à canal n ;

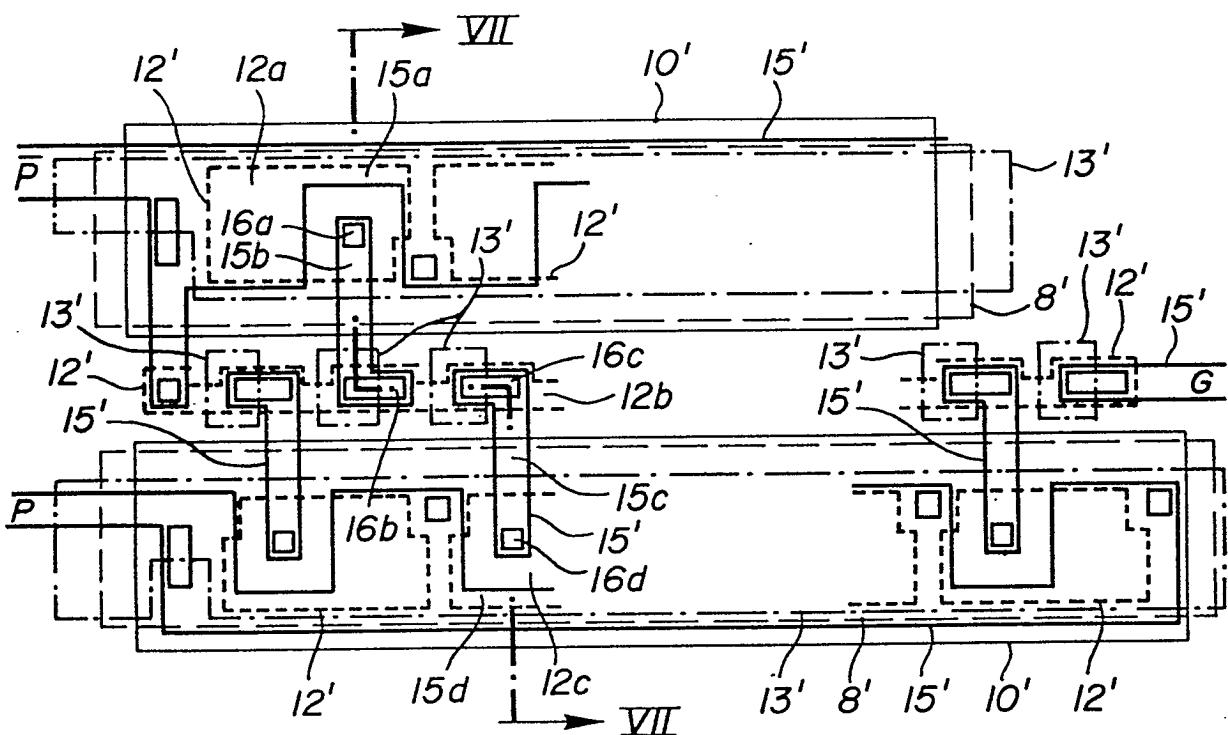

la fig. 6 est un plan de masque utilisable pour la fabrication du 10 multiplicateur de tension faisant partie du dispositif de la fig. 1, ce plan de masque constituant également une vue de dessus schématique de ce multiplicateur, et

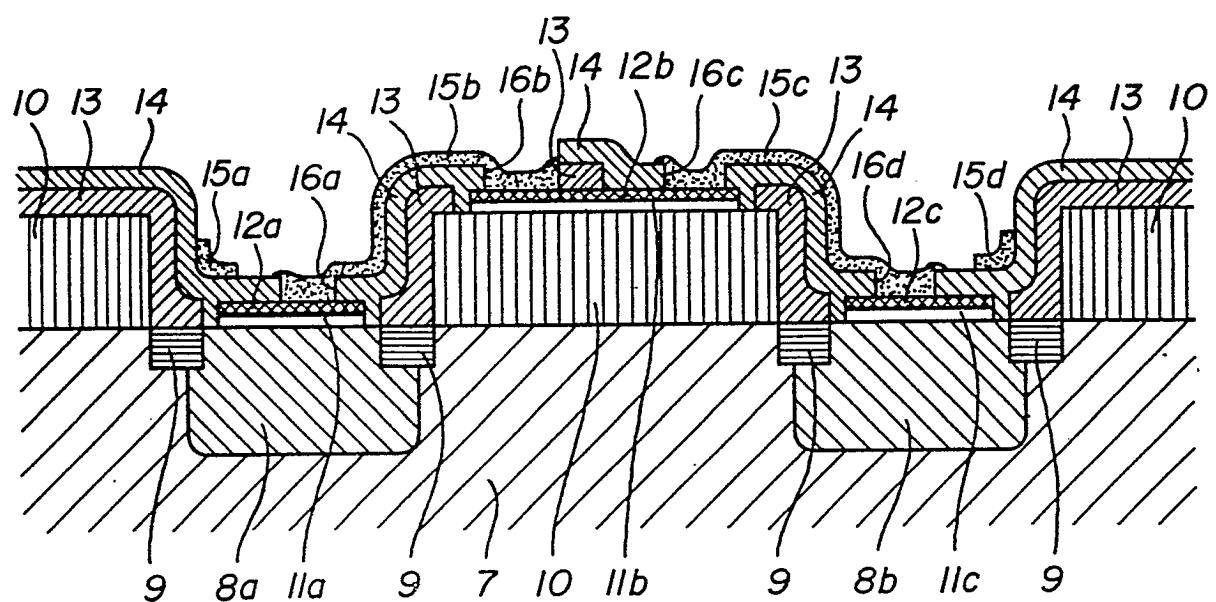

la fig. 7 est une coupe schématique, selon la ligne VII-VII du 15 multiplicateur de tension représenté à la fig. 6.

Le dispositif montré à la fig. 1 comporte deux transistors de puissance T<sub>2</sub>, T<sub>3</sub>, dont les chemins de conduction sont connectés respectivement aux points S<sub>2</sub> et S<sub>3</sub>, en série avec un dispositif à commander, représenté par un bloc S, entre les bornes 0 et + d'une source de tension d'alimentation.

Les grilles de ces transistors de puissance à canal n sont connectées ensemble en un point G à la sortie d'un multiplicateur de tension 1 fournit une tension positive. Ce multiplicateur est formé par une chaîne de diodes D et des capacités de stockage C, connectées entre les points de connexion communs des diodes, et, alternativement, à deux connexions d'entrée P,  $\bar{P}$ . Le principe d'un tel multiplicateur de tension est décrit dans l'article de John F. Dickson, «On-Chip High-Voltage Generation in MNOS Integrated Circuits Using an Improved Voltage Multiplier Technique», paru dans «IEEE Journal of Solid-State Circuits», 30 vol. SC-11, N° 3, juin 1976, pp. 374-378.

Les deux entrées P,  $\bar{P}$  sont reliées entre elles par l'intermédiaire d'un inverseur 2 qui assure que les signaux appliqués à l'entrée P apparaissent en opposition de phase à l'entrée  $\bar{P}$ . L'entrée P est connectée à la sortie d'un circuit de sélection 3 constitué par un 35 circuit logique de coïncidence du type NAND ayant deux entrées H et E. L'entrée H est reliée à un dispositif 3' fournit une tension de commande à fréquence élevée et l'entrée E est connectée à une source 3'' de signaux de commande d'entrée à basse tension. Ces signaux sont en outre appliqués à la grille d'un 40 transistor de décharge T<sub>1</sub> dont le chemin de conduction est connecté entre le point G et la borne O de la source de tension.

Le fonctionnement du circuit est illustré par les chronogrammes de la fig. 2. La ligne E montre un signal de commande d'entrée à basse tension appliqué à l'entrée E sous la forme d'une 45 impulsion rectangulaire à flanc avant descendant. La deuxième entrée H est reliée à la source de tension de commande 3' fournit, par exemple, des impulsions rectangulaires à fréquence élevée. A la sortie P du circuit de sélection apparaît alors un signal à basse tension représenté à la ligne P, ayant la même durée 50 que le signal en E et étant formé d'une salve d'impulsions à fréquence élevée. Le multiplicateur de tension fournit à sa sortie G un signal de commande à tension élevée ayant la forme montrée à la ligne G. Le temps de montée de ce signal est inversement proportionnel à la fréquence du signal appliquée en H et à la 55 capacité C du multiplicateur.

Il s'avère qu'il existe, pour un temps de montée donné, un facteur de multiplication optimal qui correspond à un minimum de la surface occupée par l'ensemble du dispositif de commande. D'autre part, on choisira, pour la fréquence du signal de commande appliquée au multiplicateur, une valeur aussi élevée que possible. Dans certains cas, cette fréquence est déjà disponible dans l'appareil comportant le dispositif de commande et parfois même les deux phases opposées sont disponibles directement, de sorte que, dans certaines formes d'exécution du présent dispositif, 60 l'inverseur aux entrées du multiplicateur peut être supprimé. On peut également envisager l'utilisation d'un oscillateur séparé, qui permet alors de choisir librement la fréquence du signal de commande.

Le gain de surface du circuit intégré du présent dispositif de commande peut être illustré par un exemple pratique de commande d'un moteur par un circuit selon la fig. 1. Dans cet exemple, la fréquence du signal de commande est de 32 kHz, le nombre d'étages du multiplicateur de tension est de 10, la capacité de stockage  $C=0,5 \text{ pF}$ , la tension  $V_m$  du signal de sortie du multiplicateur est de 10 V avec un temps de montée de 6 ms, et une résistance interne équivalente de  $550 \text{ M}\Omega$ . Le courant du moteur est de 0,75 mA, la tension d'alimentation de 1,35 V et la conductance opposée par le transistor ne doit pas être inférieure à 0,01 S. Un transistor, dont la tension de seuil est  $V_T$  et le gain  $\beta$ , est l'équivalent d'une conductance  $G_D = \beta (V_G - V_T)$  si la tension de drain est petite ( $<0,1 \text{ V}$ ) et si on lui applique une tension de grille  $V_G$ .

Considérons le cas d'un premier transistor de gain  $\beta_1$  commandé de la manière habituelle. La tension de grille  $V_G$  ne peut dépasser la tension d'alimentation  $V_{DD} = 1,35 \text{ V}$ . La tension de seuil  $V_T$  est voisine de 0,7 V. Le gain  $\beta_1$  doit donc valoir  $\beta_1 = G_D / (V_{DD} - V_T) = 15,4 \text{ mA/V}$ .

Considérons maintenant un second transistor attaqué à une tension plus élevée  $V_m = 10 \text{ V}$  obtenue à l'aide d'un multiplicateur de tension. Il aura la même conductance que le premier si son gain est  $\beta_2 = G_D / (V_m / V_m - V_T) = 1,08 \text{ mA/V}$ . Le rapport des gains de ces 2 transistors est donc  $\beta_2 / \beta_1 = (V_{DD} - V_T) / (V_m - V_T) = 0,07$ .

Le rapport des surfaces de ces deux transistors sera sensiblement le même que celui des gains. Dans cet exemple, la surface totale occupée par un transistor de puissance et le multiplicateur de tension est égale à environ 25% de la surface nécessaire pour un transistor de puissance fonctionnant à basse tension de commande.

La fig. 3 montre un exemple de réalisation particulièrement avantageux, dans lequel le dispositif de commande comporte des paires de transistors de puissance de même type à canal n au lieu de transistors complémentaires. On sait que les transistors à canal n occupent une surface plus petite que des transistors à canal p, à courant de drain et tension de grille donnés. Le dispositif est agencé pour la commande d'un moteur pas à pas, au moyen de deux paires de transistors  $T_{31}, T_{33}$  et  $T_{32}, T_{34}$  connectés en série entre les bornes +, 0 d'une source de tension d'alimentation. La bobine 4 du moteur est connectée aux points de connexion communs des transistors de chaque paire et les transistors  $T_{32}, T_{33}$  et  $T_{31}, T_{34}$ , appartenant à des paires différentes et étant connectés à des bornes de la source de tension différentes, sont commandés simultanément par des ensembles respectifs 5 et 6. Chaque ensemble comporte un multiplicateur de tension et un circuit de sélection sous la forme d'une porte de coïncidence telle que mentionnée en rapport avec la fig. 1. Une tension de commande à fréquence élevée est appliquée en H simultanément aux entrées correspondantes de 5 et 6, et des signaux de commande d'entrée à basse tension sont appliqués à ces ensembles aux entrées  $E_5$  et  $E_6$  respectives.

Cette solution n'utilise donc que deux multiplicateurs de tension au lieu de quatre pour quatre transistors de puissance, qui sont, en outre, tous du même type.

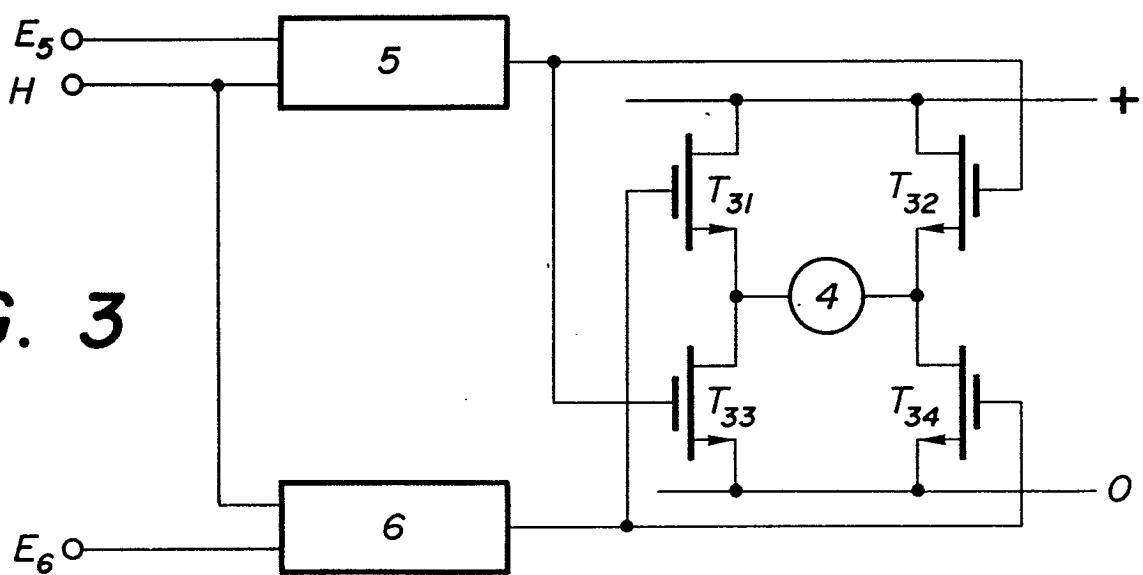

Les fig. 4 et 5 illustrent une autre conception du dispositif de commande, selon laquelle un seul multiplicateur de tension est utilisé pour différents transistors de puissance qui ne sont pas commandés simultanément. Le signal de commande à tension élevée est donc aiguillé à partir de ce multiplicateur de tension au moyen de circuits de sélection. Selon qu'il s'agit de transistors de puissance à canal p ou à canal n, la forme d'exécution préférentielle de ces circuits est différente. En effet, dans la technologie CMOS utilisée, les transistors p sont réalisés dans le substrat et les transistors n dans un caisson, le caisson pouvant être mis à des potentiels différents, alors que le substrat est toujours commun.

La fig. 4 montre un dispositif muni de transistors de puissance à canal p,  $T_{44}, T_{45}, \dots$  dont la source est connectée au pôle + de la source de tension, correspondant dans ce cas à la masse. Les connexions de drain de ces transistors, auxquelles est connecté le dispositif à commander, sont désignées par  $S_{44}, S_{45}, \dots$

Les différents signaux de commande d'entrée à basse tension sont appliqués en  $E_{44}, E_{45}, \dots$ , aux circuits de sélection associés aux transistors de puissance respectifs. Ces circuits de sélection sont constitués chacun par deux paires de transistors complémentaires tels que  $T_{40}, T_{41}$  et  $T_{42}, T_{43}$  formant une bascule bistable. La grille de chacun des transistors à canal n, tels que  $T_{41}, T_{43}$ , est connectée au drain de l'autre de ces transistors et les grilles des transistors à canal p tels que  $T_{40}, T_{42}$ , sont connectées, respectivement par l'intermédiaire d'un inverseur 46 et directement, à la connexion d'entrée basse tension  $E_{44}$ . Les transistors à canal p sont réalisés dans un caisson séparé relié à leurs sources et à la sortie d'un multiplicateur de tension 47 similaire à celui de la fig. 1, avec une polarité inverse des diodes, de manière à fournir une tension élevée négative. La tension de commande à fréquence élevée est appliquée en H aux entrées de ce multiplicateur, reliées entre elles par un inverseur 48, si la tension de commande n'est pas disponible sous forme directe et sous forme inverse.

Lors du fonctionnement, lorsqu'un potentiel négatif est appliqué par exemple en  $E_{44}$ , les transistors  $T_{42}$  et  $T_{41}$  sont conducteurs, tandis que  $T_{40}$  et  $T_{43}$ , et par conséquent  $T_{44}$ , sont bloqués. Lorsqu'un potentiel positif est appliqué en  $E_{44}$ , les transistors  $T_{42}$  et  $T_{41}$  sont bloqués,  $T_{40}$  et  $T_{43}$  sont conducteurs et la tension élevée du multiplicateur de tension apparaît à la grille de  $T_{44}$ . Cette tension tombe jusqu'au point où le basculement dans l'autre état stable s'effectue et remonte ensuite avec une constante de temps déterminée par les éléments du circuit et la fréquence de la tension appliquée en H.

Le multiplicateur de tension ayant une résistance interne élevée, le fonctionnement du circuit de sélection est assuré pour des transistors de dimensions minimales.

Le dispositif de la fig. 5 permet d'aiguiller une tension de commande positive produite par un multiplicateur de tension sur les grilles de transistors de puissance à canal n, tels que  $T_{54}, T_{55}$ , sous la commande de signaux de commande d'entrée à basse tension, appliqués à des connexions d'entrée  $E_{54}, E_{55}$ . Les transistors  $T_{54}$  et  $T_{55}$  ont leurs sources connectées à la masse, correspondant ici au pôle négatif de la source de tension, les drains de ces transistors étant connectés en  $S_{54}, S_{55}$  au dispositif à commander.

Les dispositifs de sélection associés aux transistors de puissance respectifs comportent chacun un premier transistor à canal p tel que  $T_{51}$ , dont le drain est connecté à la sortie du multiplicateur de tension, une diode  $D_1$  connectée entre la grille et la source de  $T_{51}$ , et une capacité  $C_1$  connectée à la grille de  $T_{51}$ , ainsi que deux transistors de décharge  $T_{52}$  et  $T_{53}$ , à canal p, dont les chemins de conduction sont connectés entre la masse, d'une part, et respectivement la grille et la source de  $T_{51}$ , d'autre part.

Le signal de commande d'entrée est appliquée aux grilles de  $T_{52}$  et  $T_{53}$  ainsi qu'à l'une des deux entrées d'un circuit de coïncidence 59. L'autre entrée de 59 est connectée en H au dispositif fournissant une tension de commande à fréquence élevée. De même, les entrées du multiplicateur de tension, reliées entre elles par l'intermédiaire d'un inverseur 58, sont connectées à l'entrée H. La sortie de 59 est connectée, par l'intermédiaire de la capacité  $C_1$ , à la grille de  $T_{51}$ .

Dans le dispositif de la fig. 5, le signal de commande d'entrée à basse tension est ainsi appliquée sous forme hachée à la fréquence de la tension fournie en H à la grille de  $T_{51}$ . La capacité  $C_1$  peut être petite, mais doit être plus grande que la capacité de grille de  $T_{51}$ . Ce signal de commande haché est verrouillé à l'aide de  $D_1$  au niveau de la tension de grille de  $T_{54}$ . Le transistor  $T_{51}$  conduit alors et charge la capacité de grille source de  $T_{54}$  (non représentée) par effet bootstrap, au niveau de la tension élevée fournie par le multiplicateur de tension. Du fait de la résistance interne élevée

du multiplicateur, sa tension de sortie tombe pratiquement à zéro au moment d'une commande, puis elle remonte jusqu'à sa valeur nominale.

Les fig. 6 et 7 illustrent, à titre d'exemple, une forme d'exécution du multiplicateur de tension correspondant au schéma indiqué dans la fig. 1, réalisée à l'aide d'une technologie de circuit intégré connue par l'article «Silicon Gate CMOS Frequency Divider for the Electronic Wrist Watch» de E. Vittoz, B. Gerber et F. Leuenberger, dans «IEEE Journal of Solid State Circuits», 7, 100 (1972). Cette technologie permet la réalisation de transistors MOS complémentaires à grille de silicium polycristallin. Des oxydes dopés sont utilisés pour doper sélectivement les régions source, drain et grille des transistors. Lorsqu'une couche de silicium polycristallin est située sous une région limitrophe entre un oxyde dopé au bore et un oxyde dopé au phosphore, il se forme à cette limite une diode flottante, tel que décrit dans le brevet USA N° 4041522.

L'ensemble du multiplicateur, représenté aux fig. 6 et 7, comprend un substrat de silicium monocristallin 7 dopé n contenant deux caissons 8a et 8b, dopés p, qui sont obtenus, de manière connue en soi, en utilisant un masque percé d'ouvertures dont les contours sont indiqués par les lignes 8' à la fig. 6.

Le substrat 7 est recouvert par une couche d'oxyde de silicium 10, ayant une épaisseur approximative de 1  $\mu$ , dans laquelle ont été pratiqués deux évidements de forme rectangulaire, par attaque de cette couche de manière également connue en soi, les parties à conserver ayant été recouvertes d'un masque percé d'ouvertures dont les contours sont indiqués par les lignes 10' à la fig. 6.

La couche 10 est partiellement recouverte par une couche 13 d'oxyde de silicium dopé au bore (oxyde dopé de type p) ayant une épaisseur approximative de 0,2  $\mu$ , obtenue, de manière connue en soi, en utilisant un masque laissant à découvert les plages extérieures à celles dont les contours sont indiqués par les lignes 13' de la fig. 6.

Deux bandes de diffusion 9, de type p<sup>+</sup>, sont formées dans le substrat 7 et les caissons 8a et 8b, de chaque côté de chacun de ces caissons, dans la partie de la surface du substrat délimitée entre les lignes 10' et 13' (fig. 6).

Les caissons 8a et 8b et la partie de la couche 10 comprise entre ces caissons sont respectivement partiellement recouverts par une couche d'oxyde de silicium non dopé 11a, 11c et 11b jouant le rôle d'oxyde de grille. Les couches 11a, 11b et 11c sont elles-mêmes respectivement recouvertes par des électrodes de silicium polycristallin 12a, 12b et 12c, déposées en utilisant un masque percé d'ouvertures dont les contours sont indiqués par les lignes 12' à la fig. 6.

Une couche 14, d'oxyde de silicium dopé au phosphore (oxyde dopé de type n), recouvre la couche 13, ainsi que les couches 12a, 12b, 12c (sauf à certains emplacements tels que 16a, 16b, 16c et 16d où sont ménagées des ouvertures de contact) et les parties

de la surface des caissons 8a et 8b et de la couche 10 non recouvertes par les couches d'oxyde de silicium 11a, 11b et 11c.

Une couche métallique en un métal bon conducteur et peu oxydable, comme l'aluminium, formée de plages distinctes telles que 15a, 15b, 15c et 15d, assure les interconnexions électriques entre les électrodes de silicium polycristallin 12a, 12b et 12c. Cette couche métallique peut être obtenue par métallisation sous vide, de manière connue en soi, en utilisant un masque percé d'ouvertures dont les contours sont indiqués par les lignes 15' de la fig. 6.

La plage 15a et la plage 15d de cette couche métallique sont respectivement reliées à la connexion d'entrée  $\bar{P}$  et à la connexion d'entrée P du multiplicateur de tension 1 (fig. 1), l'électrode 12b étant reliée au point de sortie G du multiplicateur de tension 1 par l'intermédiaire d'une plage 15e de cette même couche métallique, connectée à l'extrémité de cette électrode opposée au côté des connexions  $\bar{P}$  et P.

La comparaison entre la fig. 1 et les fig. 6 et 7 montre que l'électrode 12b connecte en série une ligne de diodes au silicium polycristallin dont chacune est localisée dans une ouverture de contact telle que 16b et 16c. On voit également que les caissons 8a et 8b forment les électrodes communes des deux groupes de capacités du multiplicateur 1, dont les électrodes telles que 12a et 12c constituent les autres électrodes.

On constate aussi que les diélectriques de capacités C (fig. 1) sont constitués par les couches d'oxyde de silicium telles que 11a et 11c. Ces dernières couches ont, de préférence, une très faible épaisseur, par exemple de l'ordre de 0,1  $\mu$ , ce qui permet l'obtention d'une capacité spécifique élevée pour les capacités C. La présence de la couche de métallisation 15b, 15c au-dessus des couches de silicium polycristallin 12a, 12c contribue également à augmenter la valeur de cette capacité spécifique.

On voit en outre que les diodes D (fig. 1) sont placées au-dessus d'une épaisse couche 10 d'oxyde de silicium (oxyde de champ) et sont ainsi très bien isolées du reste du circuit.

Enfin, la coupe représentée à la fig. 7 montre que la formation d'un canal parasite, court-circuitant les caissons 8a et 8b, du fait de l'existence d'un transistor parasite ayant pour source et drain ces deux caissons et pour grille la métallisation et les diodes, est empêchée grâce à la présence des bandes de diffusion 9 qui fonctionnent comme channel stoppers.

La technologie de transistors MOS complémentaires à grille de silicium permet donc de résoudre de manière particulièrement avantageuse le problème de la réalisation du multiplicateur de tension utilisé dans le présent dispositif. On emploie notamment des diodes de silicium polycristallin qui sont flottantes. Les capacités de stockage C du multiplicateur sont obtenues par la mise en parallèle des capacités silicium polycristallin/caisson sur oxyde mince et silicium polycristallin/métal. Les seules capacités parasites qui apparaissent sont les capacités caisson/substrat qui chargent le dispositif fournit le signal de commande à fréquence élevée, sans perturber le fonctionnement du multiplicateur.

**FIG. 2**

**FIG. 3**

*FIG. 4*

*FIG. 5*

**FIG. 6**

**FIG. 7**