**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                                                                                       |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| (51) Int. Cl. <sup>6</sup><br>H01L 21/00                                                                                                                              | (45) 공고일자<br>2001년03월15일   |

| (21) 출원번호<br>10-1994-0009081                                                                                                                                          | (11) 등록번호<br>특0284989      |

| (22) 출원일자<br>1994년04월28일                                                                                                                                              | (24) 등록일자<br>2000년12월27일   |

| (30) 우선권주장<br>93-102761 1993년04월28일 일본(JP)<br>94-62610 1994년03월31일 일본(JP)                                                                                             | (65) 공개번호<br>특1994-0024886 |

|                                                                                                                                                                       | (43) 공개일자<br>1994년11월19일   |

| (73) 특허권자<br>텍사스 인스트루먼츠 인코포레이티드 월리엄 비. 캠플러<br>미국 텍사스주 75265 달라스 노스센트럴 익스프레스웨이 13500린텍 가부시키<br>가이샤 쇼지 고메이<br>일본 도쿄도 이따바시구 훈쪼 23-23                                     |                            |

| (72) 발명자<br>마사쓰미 아마가이<br>일本国 300-12 이바라끼겐 우시꾸시 미나미 1-29-19<br>가즈요시 애베<br>일本国 351-01 사이따마肯 와꼬우시 수와하라단찌 2-6-505<br>히데오 세누<br>일本国 349-02 사이따마肯 시라오까군 시라오까마찌 시모노다 1375-19 |                            |

| (74) 대리인<br>주성민                                                                                                                                                       |                            |

**심사관 : 장현근**

---

**(54) 웨이퍼용 접착 시트 및 그를 사용한 반도체 장치 제조 공정**

---

**요약**

웨이퍼용 접착 시트가 기판 막 및 기판 막 상에 형성된 방사 경화가능 접착층을 포함하고, 상기 접착 시트가 전면에 회로들을 형성한 웨이퍼의 배면을 방사 경화가능 접착층 위에 접착하는 단계, 웨이퍼를 칩들로 다이싱하는 단계, 방사 에너지를 방사 경화 가능 접착층에 조사하여 상기 접착층을 경화시키는 단계, 필요에 따라 상기 칩들을 서로 분리시키기 위해 접착 시트를 팽창시키는 단계, 상기 칩들을 픽업하는 단계, 상기 칩들을 리드 프레임상에 탑재 및 결합하는 단계, 및 상기 칩들의 배면이 부분적으로 또는 전체적으로 패키지 성형 수지와 접촉하는 구조가 되도록 성형하는 단계를 포함하는 반도체 장치 제조 공정에 사용되고, 상기 방사 경화가능 접착층이 아크릴계 에스테르 및 애기-함유 종합가능 단위체의 혼성 종합체로 구성된 100 중량부의 아크릴계 접착제 및 2개 이상의 불포화 결합들을 갖는 50-200 중량부의 방사 종합가능 화합물을 포함하고, 방사 에너지로의 조사에 의한 경화 후에 적어도  $1 \times 10^9$  dyn/cm<sup>2</sup>의 탄성 계수를 갖는 것이 개시된다.

**대표도**

**도1**

**영세서**

[발명의 명칭]

웨이퍼용 접착 시트 및 그를 사용한 반도체 장치 제조 공정

[도면의 간단한 설명]

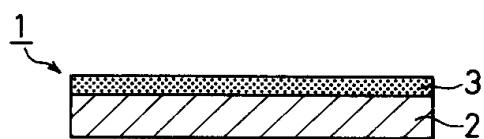

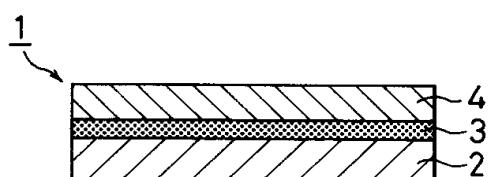

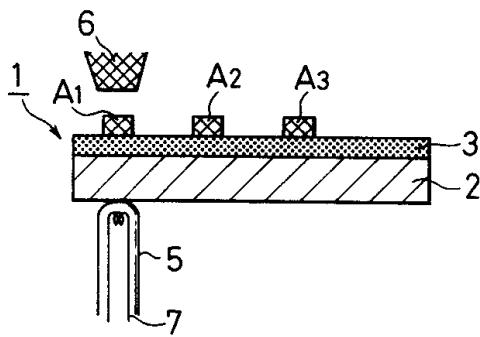

제1도는 본 발명에 따르는 웨이퍼용 접착 시트의 개략적인 단면도.

제2도는 본 발명에 따르는 웨이퍼용 다른 접착 시트의 개략적인 단면도.

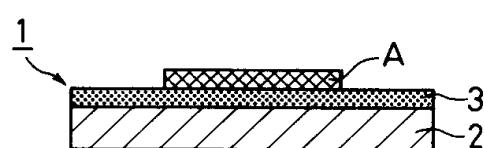

제3도는 웨이퍼가 웨이퍼용 접착 시트에 인가되는 상태를 도시한 도면.

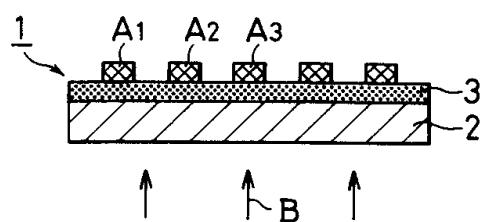

제4도는 웨이퍼가 칩들로 다이스되고, 접착 시트가 팽창되며, 시트가 방사 에너지 조사된 상태를 도시한 도면.

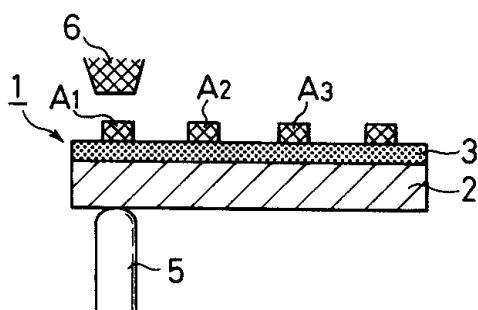

제5도는 칩들의 다른 픽업 단계를 도시한 도면.

제6도는 칩들의 또 다른 픽업 단계를 도시한 도면.

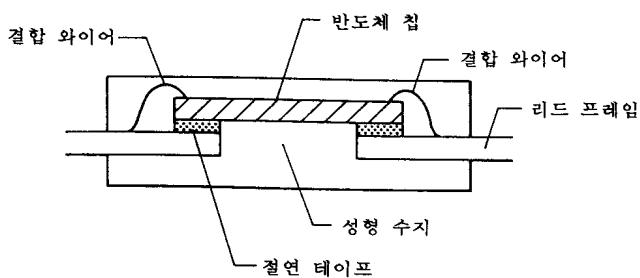

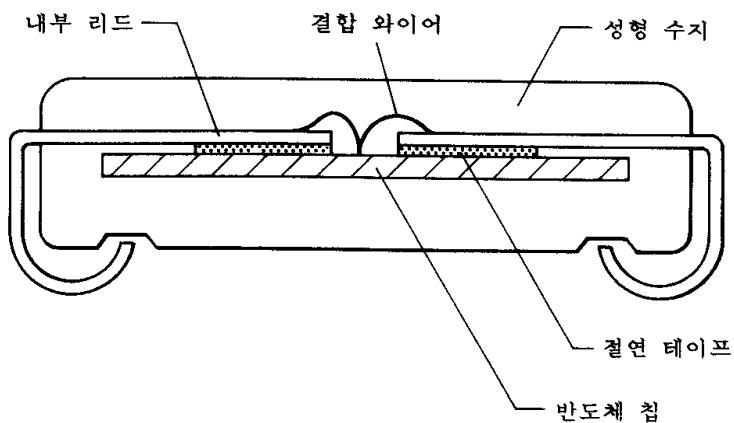

제7도는 LOC 구조를 갖는 반도체 장치의 단면도.

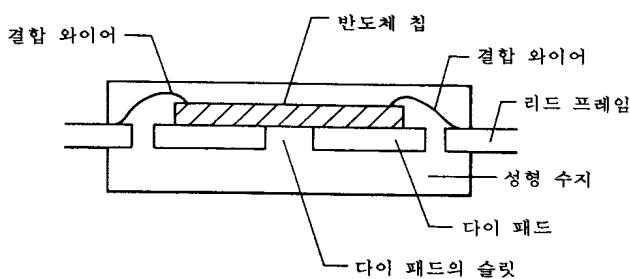

제8도는 다이 패드가 슬릿을 갖는 구조를 가지는 반도체 장치의 단면도.

제9도는 COL(Chip On Lead) 구조를 갖는 반도체 장치의 단면도.

\* 도면의 주요부분에 대한 부호의 설명

- |                 |            |

|-----------------|------------|

| 1 : 접착 시트       | 2 : 기판 막   |

| 3 : 방사 경화가능 접착층 | 4 : 릴리스 시트 |

| 5 : 푸싱 봉        | 6 : 흡인 콜렛  |

| 7 : 방사원         |            |

[발명의 상세한 설명]

본 발명은 반도체 웨이퍼(이후로는 “웨이퍼”로 기술됨)용 접착 시트 및 이 접착 시트를 사용한 반도체 장치 제조 공정에 관한 것이다. 특히, 본 발명은 칩의 배면이 부분적으로 또는 전체적으로 패키지 성형 수지(밀봉 수지)와 접촉한 구조를 갖는 반도체 장치 제조 공정에서, 웨이퍼를 소자 칩들(이후로는 “칩”으로 기술됨)로 다이스하기 위한 웨이퍼 가공된 웨이퍼를 위에 도포하여 고정시키는데 사용되는 접착 시트와, 이 접착 시트를 사용하여 반도체 장치를 제조하는 공정에 관한 것이다.

메모리의 고집적화에 따라, 사용자들은 반도체 장치에 대해 다양한 요구, 예를 들어, 고속 응답, 전력 소모량의 감소, 출력 단어 구조의 확대 및 패키지의 보다 큰 가변성을 요구하고 있다.

상기 요구들을 만족시키기 위해, 예를 들어 “닉케이 마이크로디바이스(Nikkei Microdevices)” (pp. 89-97. 1991년 2월) 및 일본국 특허 공개 번호 제246125/1990에서 기술된 것과 같은 LOC(Lead On Chip) 구조의 반도체 장치들이 제안되었다. LOC 구조는 크기의 소형화, 고속 응답, 잡음 감소 및 배치의 용이함과 같은 여러가지 장점을 가지므로, LOC 구조가 미래에 개발이 기대되는 대규모 반도체 장치들에 가장 적합하게 이용될 수 있다고 생각되고 있다.

제7도에 도시되는 바와 같이, LOC 구조에는 반도체 장치 리드 프레임(이후로는 “리드 프레임”으로 기술됨)의 복수의 내부 리드들이 그 위에 회로가 형성되어 있는 칩의 표면상에 내부 리드들이 칩과 전기적으로 절연시키는 절연 테이프에 의해 고정되고, 내부 리드들은 결합 와이어에 의해 칩과 전기적으로 접속된다. 이 반도체 장치는 성형 수지를 사용하여 밀봉되고, 칩의 배면은 성형 수지와 접촉한다.

상기되는 바와 같이 LOC 구조는 여러가지 장점들을 가지지만, LOC 구조가 종래의 패키지 구조와 완전히다르기 때문에 해결되어야 할 문제들도 포함한다. 해결되어야 할 문제들중 하나는 칩과 성형 수지 사이의 이격 및 패키지 균열등에 의한 신뢰성의 저하이다.

팩키지 균열의 발생등에 의한 신뢰성의 저하는 LOC 구조를 갖는 반도체 장치의 고유 문제가 아니라 제8도 및 제9도에 도시된 것과 같은 칩의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉한 구조를 가지는 모든 반도체 장치들에 대한 매우 심각한 문제이다. 제8도는 다이 패드가 슬릿(slit)을 갖는 구조를 가지는 반도체 장치를 도시한다. 제9도는 COL(Chip On Lead) 구조를 가지는 반도체 장치를 도시한다.

칩과 성형 수지 사이의 이격 또는 패키지 균열의 발생에 대한 메카니즘이 지금까지 다양하게 보고되었다.

이들 현상에 대한 메카니즘중의 하나는 IC 패키지로의 습기의 침입이다.

IC 패키지로의 습기의 침입 경로들은 광범위하게는 다음과 같이 분류된다.

(1) 리드 프레임과 수지 사이의 계면을 통한 침입, (2) 수지와 수지내에 채워진 필터 사이의 계면을 통한 침입 및 (3) 수지 벌크(bulk)를 통한 침입.

이들 침입들은 모세관 현상이나 확산에 의해 발생하거나, IC 패키지가 방치되는 곳의 주변 온도 또는 습기의 증가에 따라, IC 패키지가 보다 용이하게 습기를 흡수하기 때문에 발생한다. 또한, 주변 온도가 증가함에 따라, 초기 단계에서의 습기 확산율이 보다 높아지고 습기 흡수도 포화점에 보다 급격하게 도달한다. 예를 들어, IC 패키지가 85°C 및 85%RH(RH : 상대 습도)에 방치되고 습기 흡수가 허용될 때, 대략 168 시간 경과 후의 습기 흡수는 포화점의 80 내지 90%에 도달함이 보고되었다. 더우기, 상온 및 75%RH상의 정상 대기에서 조차도 습기는 예를 들어 에폭시 수지와 같은 IC 패키지의 성형 수지 재료를 쉽게 통과한다.

SOJ나 QFP와 같은 IC 패키지에서, 일반적으로 땀질은, 적외선에 의해 가열되는 IR 리플로잉(reflowing), 또는 불활성 액체를 기화시켜 IC 패키지를 고온의 증기에 노출시키는 기체 리플로잉에 의해 수반되는데, 이는 이들 두가지 리플로잉 방법들이 대량 생산에 적합하기 때문이다. 전자의 방법인 IR 리플로잉에서, IC 패키지는 240°C 내지 250°C의 고온에 노출되므로, 상기된 것과 같이 IC 내부로 침입한 습기는 리플로잉 동안 고온에 의해 급격히 팽창되어, 그에 의한 수증기 압이 에폭시 수지와 리드 프레임 사이의 계면 사이에 인가되어 그 사이에 계면 이격이 발생하게 된다. 결과적으로, 패키지 균열이 발생한다.

IR 리플로잉에 기인한 패키지 균열은, 비록 그것이 패키지내의 리드 프레임의 형상이나 칩의 표면 면적등에 따라 다소의 차이는 있지만 패키지가 대략 168 시간동안 상온에 방치될 때에도 종종 관찰된다.

계면 이격이 촉진되는 한가지 이유는 패키지의 밀봉에 사용된 수지 재료 예를 들어, 에폭시 수지와 칩의 접촉 표면 사이의 접착 강도의 감소이다. 접착 강도는 접착 표면의 평탄도에 크게 영향 받는다. 예를 들어, 접착 강도는 접착 표면상에 남아있는 Å 레벨 두께의 이물질에 대해서도 매우 민감하여 접착 강도가 감소되므로, 패키지 안으로의 습기의 침입 및 보유가 쉽게 이루어져 결국 패키지의 균열이 발생된다.

그런, 실리콘 및 갈륨-비소 화합물등의 반도체 웨이퍼들은 일반적으로 큰 직경으로 생산되고, 이 웨이퍼들이 칩들로 다이스된 후에 후속 탑재 단계로 이동된다. 이때, 반도체 웨이퍼들은 다이싱, 행굼

(rinsing), 건조 공정, 및 반도체 웨이퍼가 접착 시트에 접착된 상태에서 접착 시트의 접착층을 경화시키기 위한 방사 조사와 같은 공정을 거치게 된다. 그 다음으로, 만일 필요하면 접착 시트의 팽창 공정이 수행되고, 그 후에 칩을 픽업(pick up)하여 칩을 탑재하는 공정이 실행된다.

다이싱 단계에서 픽업 단계까지의 웨이퍼 공정 단계에 사용하기 위한 접착 시트들은 다이싱 단계에서 픽업 단계까지의 과정에서 웨이퍼 및/또는 칩을 위에 보유하기에 충분한 접착력을 갖는 것이 요구되지만, 픽업 단계에서는, 어떠한 접착제도 픽업된 웨이퍼 칩상에 남아있지 않을 정도의 접착력만을 유지하는 것이 요구된다. 상기된 것과 같이, 웨이퍼를 위에 도포하기 위한 접착 시트로서는 예를 들어 일본국 특허 공보 제56112/1989호에 기술된 것들이 일반적으로 사용되어 왔으며, 종래 형태의 반도체 장치의 제조에서 발생하는 문제들없이 사용될 수 있다.

그러나, 칩의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉하는 구조를 갖는 반도체 장치들의 제조에서는, 패키지 균열이 발생한다는 문제가 관찰되어 반도체 장치의 신뢰성이 감소된다.

본 발명은 종래의 상기 기술들에 비추어 만들어졌고, 본 발명의 목적은 칩의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉하고 그에 의한 패키지 균열의 발생을 방지하여 반도체 장치의 신뢰성을 향상시키는 구조를 갖는 반도체 장치들의 제조에 사용되는 웨이퍼용 접착 시트(이후로는 웨이퍼용 접착 시트로 기술됨)을 제공하는 것이다. 본 발명의 다른 목적은 이 접착 시트를 사용하는 반도체 장치 제조 공정을 제공하는 것이다.

본 발명에 따르는 웨이퍼용 접착 시트는 기판 막 및 기판 막 상에 형성된 방사 경화가능 접착층을 포함하는 웨이퍼용 접착 시트이고, 상기 접착 시트는 전면에 회로들이 형성되어 있는 웨이퍼의 배면을 방사 경화가능 접착층 위에 접착하는 단계, 웨이퍼를 칩들로 다이싱하는 단계, 상기 접착층을 경화시키기 위해 방사 에너지를 방사 경화 가능 접착층에 조사하는 단계, 만일 필요하면 칩들을 서로 분리시키기 위해 접착 시트를 팽창시키는 단계, 칩들을 픽업하는 단계, 칩들을 리드 프레임상에 탑재하는 단계, 결합하는 단계, 및 칩들의 배면이 부분적으로 또는 전체적으로 패키지 성형 수지와 접촉하는 구조가 되도록 성형(밀봉)하는 단계를 포함하는 반도체 장치 제조 공정에 사용된다.

상기 방사 경화가능 접착층은 아크릴계 에스테르(acrylic ester) 및 애기-함유 종합가능 단위체의 혼성 종합체로 구성된 100 중량부(parts by weight)의 아크릴계 접착제 및 2개 이상의 불포화 결합들을 갖는 50-200 중량부의 방사 종합가능 화합물을 포함하고, 방사 경화가능 접착층은 방사 에너지로 조사에 의한 경화 후에 적어도  $1 \times 10^9$  dyn/cm<sup>2</sup>의 탄성 계수를 갖는다.

본 발명에 따르는 반도체 장치 제조 공정은 기판 막 및 기판 막상에 제공된 아크릴계 에스테르 및 애기-함유 종합가능 단위체의 혼성 종합체로 구성된 100 중량부의 아크릴계 접착제와 2개 이상의 불포화 결합들을 갖는 50-200 중량부의 방사 종합가능 화합물을 포함하는 웨이퍼용 접착층을 포함하는 웨이퍼용 접착 시트를 사용하고, 공정은 전면에 회로들이 형성되어 있는 웨이퍼의 배면을 방사 경화가능 접착층 위에 접착하는 단계, 웨이퍼를 칩들로 다이싱하는 단계, 상기 접착층을 경화시키기 위해 방사 에너지를 방사 경화가능 접착층에 조사하는 단계, 만일 필요하면 칩들을 서로 떨어뜨리기 위해 접착 시트를 팽창시키는 단계, 칩들을 픽업하는 단계, 칩들을 리드 프레임상에 탑재하는 단계, 결합하는 단계 및 칩들의 배면이 부분적으로 또는 전체적으로 패키지 성형 수지와 접촉하는 구조가 되도록 성형(밀봉)하는 단계를 포함한다.

본 발명에 있어서, 2개 이상의 불포화 결합들을 갖는 방사 종합가능 화합물의 중량비가 20 내지 80%가 4 개 이상의 불포화 결합들을 가지는 것이 바람직하다.

본 발명에 따른 웨이퍼용 접착 시트 및 이 웨이퍼용 접착 시트를 사용한 반도체 장치 제조 공정이 다음에 상세히 기술된다.

제1도 내지 제6도에 도시되는 바와 같이, 본 발명의 웨이퍼용 접착 시트(1)은 기판 막(2), 및 기판 막 상에 제공된 방사 경화가능 접착층(3)을 포함한다. 접착 시트(1)은 칩의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉한 구조를 가지는 반도체 장치 제조에 사용된다. 이 공정은 방사 경화가능 접착층(3)상에서의 웨이퍼 처리를 거친 웨이퍼 A를 접착하는 단계, 이 상태의 웨이퍼를 복수의 칩들로 다이싱하는 단계, 린싱 단계, 건조 단계, 총의 접착력을 감소시키기 위해 접착층을 경화시키는 방사 에너지를 방사 경화가능 접착층에 조사하는 단계, 만일 필요하면 칩들을 서로 떨어뜨리기 위해 접착 시트를 팽창시키는 단계, 방사 경화가능 접착층(3)으로부터 칩들을 픽업하는 단계, 칩들을 주어진 지지 기판 예를 들어, 리드 프레임상에 탑재하는 단계 및 마지막으로 수지를 사용하여 성형하는 단계를 포함한다.

제1도에 도시된 단면도로부터 알 수 있는 바와 같이, 본 발명의 웨이퍼용 접착 시트는 기판 막(2), 및 기판 막의 표면상에 제공된 방사 경화가능 접착층(3)을 포함한다. 이 접착 시트를 사용하기 전에, 제2도에 도시되는 바와 같이, 접착층(3)을 보호하기 위해 방사 경화가능 접착층(3)에 릴리스(release) 시트(4)를 일시적으로 도포하는 것이 바람직하다.

본 발명의 웨이퍼용 접착 시트(1)은 테이프형, 레이블 형태 등의 어느 형태로도 형상될 수 있다. 기판 막(2)으로서는 방수성 및 내열성이 우수한 재료가 적합하고, 이와 같은 점에서, 합성 수지 막들이 특히 적합하다. 뒤에 기술되는 바와 같이, 본 발명의 웨이퍼용 접착 시트는 전자 비임(EB) 또는 자외선 광(UV)과 같은 방사 에너지가 조사되고, 기판 막(2)는 접착 시트가 EB 조사될 때에는 투과성일 것이 필요하지 않지만, 접착 시트가 UV 조사될 때에는 착색되더라도 투과하여야 한다.

기판 막(2)로서 이용가능한 것은 폴리에틸렌, 폴리프로필렌, 폴리염화 비닐, 폴리에틸렌 테레프탈산기, 폴리부틸렌 테레프탈산기, 폴리부탄(polybutene), 폴리부타디엔, 폴리우레탄, 폴리메틸펜탄(polymethylpentene), 에틸렌/비닐 아세테이트 혼성 종합체, 에틸렌/(메타)아크릴산 혼성 종합체, 에틸렌/메틸(메타)아크릴산 혼성 종합체 및 에틸렌/에틸(메타)아크릴산 혼성 종합체 등과 같은 합성 수지들의 막이다. 이들 막들의 적층도 또한 이용될 수 있다. 기판 막(2)의 두께는 일반적으로 약 10~300μm의 범위이고, 50~200μm가 바람직하다.

접착 시트가 웨이퍼의 다이싱 후에 확장 처리될 것이 필요한 경우, 종래에 사용되는 폴리염화 비닐 막 또

는 폴리에틸렌 막과 같이 세로 방향 및 가로 방향의 확장성을 갖는 합성 수지 막이 기판 막으로 사용되는 것이 바람직하다.

본 발명의 웨이퍼용 접착 시트(1)은 상기된 기판 막(2) 및 기판 막(2)상에 형성된 방사 경화가능 접착층(3)을 포함한다. 방사 경화가능 접착층(3)은 방사 에너지로 조사에 의한 경화 후에 적어도  $1 \times 10^9$  dyn/cm<sup>2</sup>의 탄성계수를 갖고, 바람직하게는  $1 \times 10^9$  dyn/cm<sup>2</sup> 내지  $1 \times 10^{10}$  dyn/cm<sup>2</sup>의 탄성 계수를 가진다.

본 명세서에 기술된 탄성 계수는 다음의 방식으로 결정된다. 즉, 50mm의 길이, 4mm의 폭, 0.2mm의 두께를 가지는 접착 시트(3)를 형성하는 작은 시편이 준비된다. 이 시편은 80W/cm의 고압 수은 램프 밑에 위치되어 1초 동안 방사 조사되어 경화된다. 경화 후, 이 시편은 탄성 계수 그래프를 얻기 위해 접탄성 측정 장치[오리엔틱 케이. 케이.(Oriental K.K.)에 의해 제조된 Rheovibron DDV-II-EP]를 사용하여 3.5Hz에서 탄성 계수가 측정되고, 이 그래프로부터 25°C에서의 값이 접착층의 탄성 계수로서 구해진다.

기판 막(2) 상에 형성된 방사 중합가능 접착층(3)은 접착제 및 방사 중합가능 화합물을 포함한다. 접착제로 적합한 것은 아크릴계 에스테르 및 애기-함유 중합가능 단위체의 혼성 중합체로 구성된 아크릴계 접착제이다. 아크릴계 접착제는 아크릴계 에스테르에서 추출되는 반복 단위들 및 애기-함유 중합가능 단위체로부터 추출되는 반복 단위들을 함유하는 혼성 중합체이다. 애기-함유 중합가능 단위체 단위들은 몰비로 0.5~30%의 양, 바람직하게는 8~30 %, 보다 바람직하게는 20~30%가 혼성 중합체내에 함유된다.

사용되기에 적합한 아크릴계 에스테르의 예들로는 1~10개의 탄소 원자를 갖는 알킬 알콜의 아크릴계 에스테르 및 1~10개의 탄소 원자를 갖는 알킬 알콜의 메타아크릴산 에스테르가 포함된다.

사용되기에 적합한 애기 함유 중합가능 단위체의 예들로는 2-하이드록시 아크릴레이트(2-hydroxyethyl acrylate), 2-하이드록시에틸 메타사이클린산, 하이드록시프로필 아크릴레이트 및 하이드록시 프로필 메타아크릴산이 바람직하다.

이들 단위체들은 혼성 중합시켜 얻어진 혼성 중합체는  $1.0 \times 10^5$ ~ $10.0 \times 10^5$ , 바람직하게는  $4.0 \times 10^5$ ~ $8.0 \times 10^5$ 의 분자량을 갖는다.

상기된 성분 단위들에 부가하여, 아크릴계 접착제들은 본 발명의 목적을 저해하지 않으면, 비닐 아세테이트, 아크릴로니트릴 및 비닐 알킬 에테르등으로부터 추출된 것들과 같은 다른 성분 단위들도 함유할 수 있다.

아크릴계 접착제의 접착력 및 접착력은 교차결합제를 사용하여 선택적으로 결정될 수 있다. 교차결합제의 예로서는 다가(polyvalent) 이소시안산염 화합물, 다가 에폭시 화합물, 다가 아지리딘(aziridine) 화합물 및 칠레이트(chelate) 화합물이 포함된다. 다가 이소시안 화합물들의 구체적인 예들로는 툴리렌 디이소시안화물, 디페닐 메탄 디이소시안화물, 헥사메틸렌 디이소시안화물, 이소포론 디이소시안화물, 및 그 부가물을 포함한다. 다가 에폭시 화합물의 구체에는 에틸렌 글리콜 디글리시딜 에테르 및 디글리시딜 테레프탈레이트(diglycidyl terephthalate)가 포함된다. 다가 아지리딘 화합물들의 구체적인 예들로는 트리스(tris)-2,4,6-(1-아지리디닐)-1,3,5-트리아진, 트리스[1-(2-메틸)-아지르디닐] 산화 포스핀 및 헥사(hexa)[1-(2-메틸)-아지르디닐] 트리포스파트리아진(triphosphatriazine)이 포함된다. 칠레이트 화합물들의 구체 예로서는 아세토아세테이트(acetoacetate) 알루미늄 디이소프로필레이트(diisopropylate) 및 알루미늄 트리스(에틸아세토아세테이트)가 포함된다.

방사 경화가능 접착층(3)용 방사 중합가능 화합물로는, 예를 들어 일본국 특허 공개 제196956/1985호 및 제223139/1985호에 기술된 것과 같은, 광 조사시 3 기능성 네트워크를 형성할 수 있는 분자들에 적어도 2개의 광중합가능 탄소-탄소 이중 결합을 갖는 저분자량의 화합물들이 광범위하게 사용될 수 있다. 이같은 저분자량 화합물들의 구체적인 예들로는 트리메틸올프로판(trimethyloolpropane) 트리아크릴레이트, 테트라메틸올메탄 테트라아크릴레이트, 펜타에리트리톨(pentaerythritol) 트리아크릴레이트, 펜타에리트리톨 테트라아크릴레이트, 디펜타에리트리톨 모노하이드록시펜타아크릴레이트, 디펜타에리트리톨 헥사아크릴레이트, 1,4-부틸렌 글리콜 디아크릴레이트, 1-6-헥산디올(hexanediol) 디아크릴레이트, 폴리에틸렌 글리콜 디아크릴레이트 및 상업적으로 이용가능한 올리고에스테르(oligoester) 아크릴레이트가 포함된다.

상기된 아크릴레이트 화합물들에 부가하여, 우레탄 아크릴 소중합체(oligomers)들이 또한 방사 중합가능 화합물로서 이용가능하다. 우레탄 아크릴레이트 소중합체들은 하이드록실기 예를 들어, 2-하이드록시에틸 아크릴레이트, 2-하이드록시에틸 메타크릴레이트, 2-하이드록시프로필 아크릴레이트, 2-하이드록시프로필 메타크릴레이트, 폴리에틸렌 글리콜 아크릴레이트 및 폴리에틸렌 글리콜 메타크릴레이트를 갖는 아크릴레이트 또는 크릴레이트와 나중에 반응되는 이소시안산염 우레탄 프리폴리머(prepolymer)를 얻기 위해, 폴리에테르 또는 또는 폴리에스테르형 폴리올(polyol) 화합물을 예를 들어, 2,4-토릴렌(tolylene) 디이소시안산염, 2,6-토릴렌 디이소시안산염, 1,3-크실렌(xylene) 디이소시안산염, 1,4-크실렌 이소시안산염 및 디페닐메탄(diphenylmethane)-4,4-디이소시안산염과 같은 다가 이소시안산염 화합물과 반응시켜 준비된다.

이들 우레탄 아크릴레이트 소중합체들 중에서, 이들 우레탄 아크릴레이트 소중합체들을 함유하는 접착제가 비록 웨이퍼의 배면이 거칠지라도 픽업 단계에서 침의 배면을 접착하지 않기 때문에 3,000~30,000의 분자량, 바람직하게는 3,000~10,000의 분자량, 보다 바람직하게는 4,000~8,000의 분자량을 갖는 것들이 사용된다. 또한, 우레탄 아크릴레이트 소중합체들은 적어도 2개의 탄소-탄소 이중 결합을 갖는 것이 바람직하고, 2개의 탄소-탄소 이중 결합(즉, 2 기능성)을 갖는 것이 보다 바람직하다. 또한, 우레탄 아크릴레이트 소중합체들을 방사 중합가능 화합물로서 사용하는 경우에, 일본국 특허 공개 제196956/1985에 개시된 바와 같이 분자들에 적어도 2개의 광중합가능 탄소-탄소 이중 결합을 가지는 저분자량 화합물만을 사용하는 경우와 비교하여 극히 뛰어난 접착 시트를 얻을 수 있다. 다시 말해, 이렇게 얻어진 접착 시트는 방사 에너지로 조사하기 전에 충분히 높은 접착력을 갖지만, 조사 후에는 시트의 접착력이 침의 픽업 단계에서는 침의 배면에 어떠한 접착제도 남아 있지 않는 레벨로 감소한다.

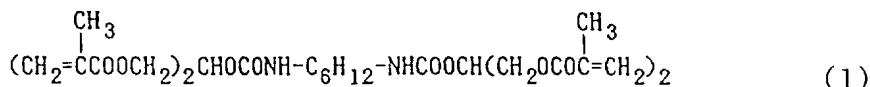

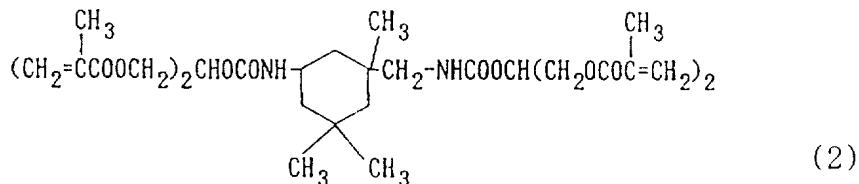

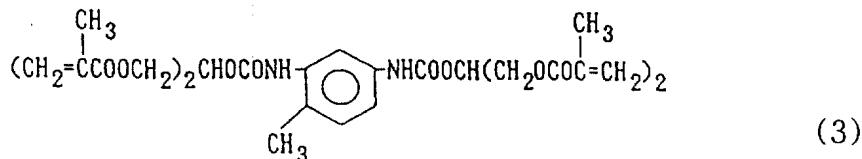

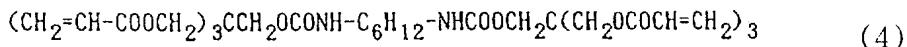

본 발명에서는, 복수의 방사 중합가능 화합물을 혼합하여 사용하는 것이 바람직하다. 예를 들어, 방사 중합가능 화합물의 중량비가, 약 20 내지 80%, 바람직하게는 중량비가 약 30 내지 70%가 4개 이상의 불포화 결합을 갖는 것이 바람직하다. 4개 이상의 불포화 결합을 갖는 방사 중합가능 화합물의 구체적인 예들은 펜타에리트리톨 테트라아크릴레이트, 1,6-비스(글리세릴 우레탄)헥산 테트라메타크릴레이트(1),

비스(글리세릴 우레탄)이소포론 테트라메타크릴레이트(2), 및

비스(글리세릴 우레탄)톨루엔 테트라메타크릴레이트(3)

을 포함한다.

이같은 4개 이상의 불포화 결합을 갖는 방사 중합가능 화합물이 방사 중합가능 화합물의 100%에 근거한 중량비 20 내지 80%의 양이 사용되면, 방사 경화가능 접착층은 방사 에너지로의 조사에 의해 충분히 경화되고 접착제의 접착력은 감소되지 않는다.

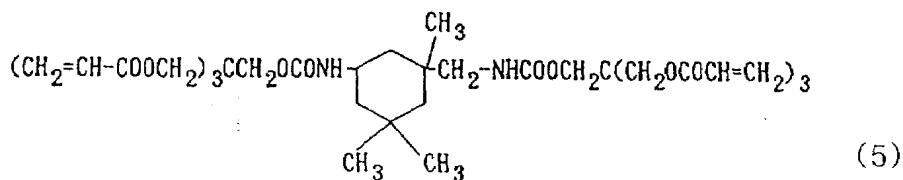

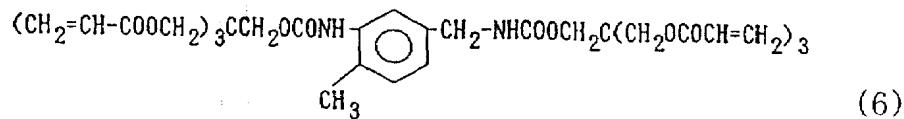

또한, 2개 이상의 불포화 결합을 갖는 방사 중합가능 화합물이 서로 혼합되어 사용되는데, 여기서, 4개 이상의 불포화 결합을 갖는 것의 중량이 20 내지 80%, 바람직하게는 30 내지 70% 및 6개 이상의 불포화 결합을 갖는 것의 20 내지 60%, 바람직하게는 30 내지 50%가 2개 이상의 불포화 결합을 갖는 방사 중합가능 화합물의 총량에 존재한다. 6개 이상의 불포화 결합을 갖는 방사 중합가능 화합물의 예들은 디펜타에리트리톨 헥사아크릴레이트, 디펜타에리트리톨 헥사메타아크릴레이트, 1,6-비스(펜타에리트리톨 우레탄)헥산 헥사아크릴레이트(4),

비스(펜타에리트리톨 우레탄)이소포론 헥사아크릴레이트(5), 및

비스(펜타에리트리톨 우레тан)톨루엔 헥사아크릴레이트(6)

을 포함한다.

특히 바람직하게 사용되는 방사 중합가능 화합물들의 혼합 예들이 아래에 주어지나, 본 발명에 이용가능한 혼합물들이 이들 예들에 국한되지는 않는다.

1. 2 기능성 우레탄 아크릴레이트 소중합체와 4 기능성이 펜타에리트리톨 아크릴레이트의 혼합.

2. 2 기능성 우레탄 아크릴레이트 소중합체와 6 기능성이 디펜타에리트리톨 헥사아크릴레이트의 혼합.

3. 2 기능성 우레탄 아크릴레이트 소중합체와 비스(펜타에리트리톨 우레탄)헥산 헥사아크릴레이트의 혼합.

접착층내의 아크릴계 접착제와 방사 중합가능 화합물 사이의 비에 관하여, 방사 중합가능 화합물은 아크릴계 접착제의 100 중량부를 기초로, 50 내지 200의 중량부가 일반적으로 사용되고, 바람직하게는 50 내지 150 중량부, 보다 바람직하게는 70 내지 120 중량부가 흔히 사용된다. 이같은 비율의 아크릴계 접착제 및 방사 중화가능 화합물을 함유하는 접착 시트는 높은 초기 접착력을 가지며, 더욱이 초기 접착력은 방사 에너지로의 조사 후에 크게 감소되어 접착 시트로부터 침들을 용이하게 픽업할 수 있다.

만일 방사 중합 가능 화합물의 양이 50 중량부 미만이면, 화합물이 방사 조사에 의해 경화된 후에 많은 양의 접착제가 침들의 배면을 접착하게 되어, 패키지가 수지를 사용하여 밀봉될 때 패키지 균열이 발생한다. 한편, 만일 방사 중합 가능 화합물의 양이 200 중량부 이상이면, 접착제의 접착력이 낮아져 패키지 균열의 발생이 억제되더라도 다른 문제(즉, 프레임으로부터 접착 시트의 분리)가 야기된다.

상기되는 바와 같이 기판 막(2) 및 방사 경화가능 접착층(3)을 포함하는 웨이퍼용 접착 시트(1)은 방사 에너지로의 조사 전에는 접착을 위한 충분한 접착력을 갖지만 방사 에너지로의 조사 후에는 접착력이 현저하게 감소한다. 보다 정확히, 방사 에너지 조사전에는 접착 시트가 예를 들어, 미러(mirror) 표면 처리된 스테인레스 강에 대해 적어도 200g/25mm의 접착력을 갖지만, 방사 에너지로의 조사후에는 접착력이 많아야 20g/25mm까지 감소한다.

만일 필요하면, 방사 경화가능 접착층(3)은 상기된 접착제 및 방사 중합가능 화합물 이외에 방사 커러 현상가능 화합물(방사시 커러를 현상하는 화합물)을 함유할 수 있다. 방사 경화가능 접착층(3)에로 방사 커러 현상가능 화합물을 일체화시킴으로써, 접착 시트가 방사 에너지 조사후에 커러화되어 광센서로 침을 검출할때 검출 정확도가 항상되고 침의 픽업 공정시 발생가능한 실수도 방지된다. 또한, 접착 시트가 방사 에너지 조사되었는 지의 여부를 즉시 육안으로 확인할 수 있다는 장점도 얻어질 수 있다.

방사 커러 현상가능 화합물들은 조사전에는 무색 또는 담백색이지만 조사시에는 커러를 현상하는 화합물들이고, 이같은 화합물들의 바람직한 한 예가 류코(Leuco) 염료들이다. 류코 염료들로서 바람직하게 이용 가능한 것은 트리페닐메탄형, 플루오란(fluoran)형, 페노티아진(phenothiazine)형, 오오러민(auramine)형 및 스피로피란(spiropyran)형과 같은 종래에 사용되는 것들이다. 이들 염료들의 구체적인 예들은 3-[N-(p-톨리라미노)]-7-아닐리노플루오란(anilinofluoran), 3-[N-(p-톨릴)-N-메틸라미노]-7-아닐리노플루오란, 3-[N-(p-톨릴)-N-에틸라미노]-7-아닐리노플루오란, 3-디에틸라미노-6-메틸-7-아닐리노플루오란, 크리스탈 바이올렛(violet) 락톤(lactone), 4,4',4"-트리스디메틸아미노트리페닐메탄올(trisdimethylaminotriphenylmethanol) 및 4,4',4"-트리스디메틸아미노트리페닐메탄을 포함한다.

상기된 류코 염료들과 혼합하여 바람직하게 사용되는 현상제들은 페놀-포르말린 수지의 초기 중합체, 방향족 카르복시산 유도체 및 전자 수용체 예를 들어, 활성 점토와 같이 종래에 사용되는 것들이다. 커러톤(tone)을 변화시키기 위해, 여러가지 공지된 커러 형성제들도 또한 혼합하여 사용될 수 있다.

방사 커러 현상가능 화합물들은 방사 경화가능 접착층에 유기 용매의 형태 또는 미세 입자의 용액 형태로 함유될 수 있다. 방사 경화가능 접착층에 일체화되는 화합물의 양은 흔히 0.01 내지 10% 범위, 바람직하게 0.5 내지 5%의 범위의 중량이 바람직하다. 만일 방사 경화가능 접착층에 일체화되는 화합물의 양이 10%를 초과하면, 접착층에 조사되는 방사가 화합물에 의해 지나치게 흡수되어, 방사 경화가능 접착층이 때로는 불충분하게 경화된다. 한편, 만일 방사 경화가능 접착층에 일체화되는 화합물의 양이 0.01% 중량 미만이면, 접착 시트는 조사시에 충분하게 착색되지 못하므로, 침을 픽업하는 공정시의 실수가 쉽게 발생한다.

임의의 상황하에서는, 방사 경화가능 접착층(3)은 상기된 접착제 및 방사 중합가능 화합물 이외에 광산란 무기 화합물 분말을 함유할 수 있다. 방사 경화가능 접착층(3)에 광산란 무기 화합물 분말을 일체화시킴으로써, 웨이퍼의 접착면이 어떤 이유로 회색화 또는 암흑화되어도, 접착층의 접착력은 자외선 광과 같은 방사 에너지 조사에 의해 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 위치들에서도 충분히 감소되므로, 접착층이 조사전에는 충분한 접착력을 갖지만, 침의 픽업 단계 동안에 어떠한 접착제도 침의 배면 상에 남지 않는다.

상기된 광산란 무기 화합물은 이 화합물이 자외선 광(UV) 또는 전자 비임(EB)과 같은 방사으로 조사될 때, 방사를 불규칙하게 반사시킬 수 있는 화합물들이다. 광산란 무기 화합물 분말의 구체적인 예들에는 실리카(silica) 분말, 알루미나 분말, 실리카 알루미나 분말 및 운모 분말이 포함된다. 광산란 무기 화합물로서, 상기된 것과 같은 방사를 거의 완전하게 반사시키는 것들이 바람직하게 이용되지만, 상기 방사를 어느 정도 흡수하는 것들도 또한 이용될 수 있다.

광산란 무기 화합물은 분말 형태가 바람직하고, 1 내지 100 $\mu\text{m}$ , 바람직하게는 1 내지 20 $\mu\text{m}$ 의 입자 지름을 가진다. 방사 경화가능 접착층에 있어서, 광산란 무기 화합물은 0.1 내지 10%, 바람직하게는 1 내지 4% 중량의 양이 사용되는 것이 바람직하다. 만일 광산란 무기 화합물이 10% 중량을 초과하는 양의 방사 경화 가능 접착층이 사용되면, 방사 경화가능 접착층의 접착력이 때때로 감소한다. 한편, 만일 이 화합물이 0.1% 중량 미만으로 사용되면, 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 접착층 부분에 조사 후에 접착층의 접착력이 충분히 감소되지 않으므로, 접착이 침의 픽업 단계에서 침의 배면상에 접착하거나 남아 있을 수 있다.

상기되는 바와 같이, 광산란 무기 화합물 분말을 함유하는 방사 경화가능 접착층을 포함하는 접착 시트를 사용함으로써, 웨이퍼의 접착 면이 어떤 이유로 회색화되거나 암흑화되어도, 접착층의 접착력은 방사 에너지로의 조사에 의해 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 부분에서도 충분히 감소된다. 이에 대한 이유는 다음과 같이 생각된다. 즉, 본 발명의 접착 시트(1)이 방사 경화가능 접착층(3)을 갖고, 이 방사 경화가능 접착층(3)이 방사 에너지 조사되면, 접착층(3)내에 함유된 방사 중합가능 화합물이 접착층의 접착력을 감소시키도록 경화된다. 그러나, 웨이퍼 표면은 때때로 어떤 이유로 회색화 또는 암흑화된 부분을 갖는다. 방사 경화가능 접착층(3)이 방사 에너지 조사되면, 방사는 방사 경화가능 접착층(3)을 통하여 웨이퍼 표면에 도달하도록 진행한다. 그러나, 만일 웨이퍼 표면이 회색화 또는 암흑화된 부분을 가지면, 방사는 상기 부분에 의해 흡수되어 반사되지 않는다. 그러므로, 방사 경화가능 접착층(3)을 경화하는데 사용되는 방사가 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 부분들에 의해

흡수되므로, 방사 경화가능 접착층(3)의 경화가 불충분하게 되고 접착층의 접착력이 충분하게 감소되지 않는다. 따라서, 칩의 픽업 단계에서 접착제가 칩의 배면상에 접착하거나 잔류하는 것으로 생각된다.

그러나, 방사 경화가능 접착층(3)에 광 산란 무기 화합물 분말이 일체화되면, 방사가 이 화합물에 의해 불규칙하게 반사되고 웨이퍼 표면에 도달하기 전에 그 방향이 변경된다. 이러한 이유로, 비록 회색화 또는 암흑화된 부분들이 웨이퍼 표면상에 존재하여도, 불규칙하게 반사된 방사가 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 부분들의 상부 영역으로 충분하게 침투하여, 접착층의 대응 부분들이 충분하게 경화된다. 광 산란 무기 화합물 분말을 방사 경화가능 접착층에 일체화시킴으로써 회색화 또는 암흑화된 부분이 어떤 이유로 웨이퍼 표면상에 존재하더라도, 접착층의 경화는 웨이퍼 표면의 회색화 또는 암흑화된 부분에 대응하는 부분에서 불충분하게 되지 않고, 따라서 칩의 픽업 단계에서 칩의 배면상에 접착제가 접착하거나 남아 있지 않게 된다.

본 발명에 있어서, 연마 입자들이 기판 막에 분산될 수 있다. 연마 입자는 0.5 내지 100 $\mu\text{m}$ , 바람직하게는 1 내지 50 $\mu\text{m}$ 의 입자 지름을 가지며 6내지 10, 바람직하게는 7 내지 10의 모오스(Mohs) 경도를 가진다. 연마 입자들의 구체적인 예들에는 생 금강사(green carborundum), 인조 금강사(artificial corundum), 광 금강사(optical emery), 백 알런덤(white alundum), 탄화 봉소, 크롬(III) 산화물, 세리움(cerium) 산화물 및 다이아몬드 분말이 포함된다. 이를 연마 입자들은 무색이거나 백색인 것이 바람직하다. 연마 입자들은 기판 막(2)내에 0.5 내지 70%의 중량, 바람직하게는 5 내지 50%의 중량이 사용된다. 연마 입자들의 사용은 다이싱 날이 웨이퍼를 통과하여 기판 막(2)에 도달하는 방식으로 사용되면 특히 바람직하다.

연마 입자들을 기판 막에 일체화시킴으로써, 비록 다이싱 날이 기판 막에 도달하여 접착제가 날에 달라붙더라도, 연마 입자들의 연마 효과 때문에 접착제가 쉽게 제거될 수 있다.

또한, 상기된 접착층은, 접착층이 UV 조사에 의해 경화될 때 UV 조사에 의한 중합 경화 시간을 단축하고 UV 조사량을 최소화하기 위해 UV 경화 촉진제를 함유할 수도 있다.

이와 같은 UV 촉진제의 구체적인 예로는 벤조인(benzoin), 벤조인 메틸 에테르, 벤조인 에틸 에테르, 벤조인 이소프로필 에테르, 벤질디페닐(benzyl diphenyl) 황화물, 테트라메틸티오람(tetramethylthiurum) 모노설파이드(monosulfide), 아조비스이소부티로니트릴(azobisisobutyronitrile), 디벤질(dibenzyl), 디아세틸(diacetyl) 및  $\beta$ -클로로안트라퀴논( $\beta$ -chloroanthraquinone)이 포함된다.

본 발명에 따르는 반도체 장치 제조 공정에서, 상기되는 바와 같이 웨이퍼용 접착 시트상에 웨이퍼 처리된 반도체 웨이퍼가 도포되고, 그 다음에 이 상태에서 웨이퍼가 칩들로 다이스되어 반도체 장치가 제조된다.

본 발명에 따르는 상기된 웨이퍼용 접착 시트를 사용하는 반조체 장치 제조 공정이 아래에 기술된다.

릴리스 시트(release sheet)(4)가 제2도에 도시되는 바와 같이 접착 시트(1) 상에 제공되는 경우, 릴리스 시트(4)가 먼저 제거되어, 접착층(3)이 위를 향하도록 접착 시트(1)가 놓인다. 방사 경화가능 접착층(3)의 표면에는, 제3도에 도시되는 바와 같이 다이스 될 웨이퍼 A가 도포된다. 다음 웨이퍼 A가 이 상태에서 다이싱 처리되고, 만일 필요하다면 린싱 및 건조 처리된다. 이같은 경우, 웨이퍼 칩들이 방사 경화가능 접착층(3)에 의해 접착 시트(1)에 충분히 접착 유지되기 때문에, 각각의 다이싱, 린싱 및 건조 공정 동안 웨이퍼 칩들이 접착 시트(1)로부터 분리되지 않는다.

그 결과로, 웨이퍼 칩들이 접착 시트로부터 픽업되고 지지 기판 예를 들어, 리드 프레임상에 탑재된다. 제4도에 도시되는 바와 같이, 픽업 공정 전이나 픽업 공정과 동시에, 접착 시트(1)의 방사 경화가능 접착층(3)이 방사 경화가능 접착층(3)내에 함유된 방사 중합가능 화합물을 중합하고 경화시키기 위해 자외선 광(UV) 또는 전자 비임(EB)과 같은 이온화 방사 B로 조사된다. 방사 경화가능 접착층(3)내에 함유된 방사 중합가능 화합물이 접착층(3)을 방사 에너지로 조사함으로써 중합 및 경화되면, 접착층내에 함유된 접착력이 단지 경미한 접착력만을 남기면 크게 감소한다.

접착 시트(1)에 대한 조사는 방사 경화가능 접착층(3)이 위에 제공되지 않는 기판 막(2)의 자유측에서부터 실행하는 것이 바람직하다. 따라서, 상기되는 바와 같이, UV가 방사원으로 사용될 때에는 기판 막(2)는 광투과 특성을 가지는 것이 요구되지만, EB가 방사원으로 사용될 때에는 기판 막(2)가 광투과 특성을 가지는 것이 반드시 요구되지는 않는다.

이제 기술되는 바와 같이, 웨이퍼 칩들 A<sub>1</sub>, A<sub>2</sub> …이 위에 제공된 방사 경화가능 접착층(3)이 방사 경화가능 접착층(3)의 접착력을 감소시키도록 방사 에너지로 조사되고, 만일 필요하다면 선정된 비율로 접착 시트를 팽창시킨다. 접착 시트의 팽창에 의해, 칩들간의 거리가 넓어지게 되어, 칩들이 접착 시트로부터 쉽게 픽업될 수 있다. 종래의 방식에 따라 후속 공정이 수행된다. 제5도에 도시되는 바와 같이, 픽업될 칩들 A<sub>1</sub>, A<sub>2</sub> …의 각각이 푸싱 로드(push rod)(5)에 의해 기판 막(2)의 하부로부터 밀어 옮겨지고, 예를 들어, 흡인 콜렛(collet)(6)에 의해 픽업되며, 그 다음에 지지 기판 예를 들어, 리드 프레임상에 탑재된다. 이러한 방식으로 웨이퍼 칩들 A<sub>1</sub>, A<sub>2</sub> …를 픽업함으로써 칩들이 쉽게 픽업되고, 얹어진 칩들도 어떠한 오염없는 우수한 품질을 갖는다. 방사 에너지 조사는 또한 픽업 단계에서도 실행될 수 있다.

웨이퍼 A의 전체 표면상에서 한번에 조사를 수행하는 것이 반드시 필요한 것은 아니고, 부분적으로 예를 들어, 조사된 부분에 대응하는 접착제의 접착력을 감소시키기 위해 조사 관으로써 기판 막(2)의 배면으로부터 각각의 웨이퍼 칩들 A<sub>1</sub>, A<sub>2</sub> …에 대응하는 기판 막의 부분에만 여러번 조사가 수행된 다음에 웨이퍼 칩들 A<sub>1</sub>, A<sub>2</sub> …이 푸싱 로드(5)에 의해 연속적으로 밀어 옮겨진 다음, 밀어 옮겨진 칩들 각각을 픽업한다. 제6도는 방사 공정 및 픽업 공정이 동시에 실행될 수 있도록 푸싱 로드(5)가 비워지고, 푸싱 로드(5)의 공동부에 방사원(7)이 제공되어, 이에 의해 장치가 간단해지고 픽업 공정에 요구되는 시간이 단축될 수 있는 상기된 조사 방식의 변형을 도시한다.

본 발명에 따르는 반도체 장치 제조 공정에서, 상기 방식으로 얹어진 칩들은 리드 프레임과 같은 지지 기판상에 탑재되고, 그 다음으로 종래 방식에 따라 성형 수지를 사용하는 결합 공정 및 밀봉 공정을 거치게

된다. 이렇게 제조된 반도체 장치는 제7도 내지 제9도에 도시되는 바와 같이 칩들의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉한 구조를 갖는다. 본 발명의 공정에 따르면, 패키지 균열이 발생하지 않는 반도체 장치가 얻어질 수 있어 신뢰성이 향상될 수 있다.

본 명세서에 사용된 성형 수지로 바람직한 것은 주성분으로 크레졸(cresol) 노볼락(novolak)형 에폭시 수지, 나프탈렌(naphthalene)형 에폭시 수지, 바이페닐(biphenyl)형 에폭시 수지 또는 방향족 다기능형 에폭시 수지를 함유하는 수지 조성물, 및 종래에 사용된 경화제(예를 들어, 페놀 노볼락), 실리카, 탄소 및 필러(fillers)와 같은 부가물을 함유하는 것이 바람직하다.

본 발명의 웨이퍼용 접착 시트는 칩들의 배면이 부분적으로 또는 전체적으로 성형 수지와 접촉하는 구조, 전형적으로 LOC 구조를 갖는 반도체 장치 제조에 사용된다. 접착 시트의 사용에 있어서, 웨이퍼 처리된 웨이퍼가 접착 시트상에 접착되어 칩들로 다이스된다. 이 칩들을 사용하여 상기된 구조를 갖는 반도체 장치가 제조된다. 본 발명의 공정에 따라 제조된 반도체 장치는 패키지 균열이 발생하지 않으므로, 제조된 제품의 신뢰성이 향상될 수 있다.

본 발명이 예들을 참조하여 아래에 기술되지만, 본 발명이 이들 예들에 국한되지는 않는다.

다음의 예들 및 비교 예들에서, “탄성 계수” 및 “패키지 균열 발생률”이 다음과 같이 계산된다.

#### [탄성 계수]

50mm의 길이, 4mm의 폭 및 0.2mm의 두께를 갖는 작은 접착제 시편이 방사 경화가능 접착제로부터 준비된다. 이 시편이 80W/cm<sup>2</sup>의 고압 수은 램프 밑에 위치되어 1초 동안 방사 에너지로 조사되어 경화된다. 경화 후, 이 시편이 점탄성 측정 장치[오리엔틱 케이. 케이.에 의해 제조된 Rheovibron DDV-II-EP]를 사용하여 3.5Hz에서 탄성 계수를 측정하여 탄성 계수 그래프를 얻고, 이 그래프로부터 25°C에서의 값이 이 접착층의 탄성 계수로서 구해진다.

#### [패키지 균열 발생률]

다이싱 후에, 칩들이 방사 에너지 조사된 접착 시트로부터 픽업된다. 이 칩들이 리드 프레임상에 탑재되고, 그 후 결합되어 고압하에서 성형 수지[오르토크레졸(orthocresol)형 에폭시 수지]로 밀봉된다. 그 다음으로, 성형 수지가 5시간 이상 175°C에 열적으로 가열되어 칩을 포함한 패키지를 제조한다. 그 다음으로 패키지가 85°C 및 85%RH의 분위기에서 504 시간 동안 방치된다. 그 후에, 이 패키지가 3회 IR 리플로 잉(요구되는 시간 : 1분)되고, 밀봉된 수지가 주사 아코모스틱 토모그라피(scanning acomostic tomography ; SAT)에 의해 균열 발생이 검사된다. 테스트된 전체 패키지 수에 대한 균열을 갖는 패키지 수의 백분율이 패키지 균열 발생률로 결정된다.

#### [예 1]

##### [방사 경화 가능 접착제 제조]

100 중량부의 아크릴계 접착제[하이드록시에틸 아크릴레이트 및 부틸 아크릴레이트의 혼성 중합체, 하이드록시에틸 아크릴레이트의 중량 : 중량비 9%(몰비 9.8%)], 약 6,000의 분자량을 갖는 70 중량부의 2기능성 우레탄 아크릴레이트 소중합체[다이니찌세이까 컬러 & 케미컬 콤파니, 리미티드(Dainichiseika Color & Chemicals Co., Ltd.)로부터 입수가능)], 30 중량부의 4 기능성 폴리에스테르 소중합체 및 10 중량부의 방향족 이소시안산염[토요 잉크 콤파니, 리미티드(Toyo Ink Co., Ltd.)]로부터 입수가능]이 방사 경화 가능 접착제를 제조하기 위해 혼합된다.

이 방사 경화가능 접착제의 탄성 계수가 측정된다. 그 결과가 표 1에 도시된다.

#### [웨이퍼용 접착 시트의 제조]

100μm의 두께를 갖는 폴리에틸렌 막상에, 상기 제조된 방사 경화가능 접착제가 10 g/cm<sup>2</sup>의 양 도포되어 방사 경화 가능 접착층을 형성한다. 이 방사 경화가능 접착층 상에, 실리콘으로 처리된 두께 38μm의 PET 막이 릴리스 시트로서 적층되어 웨이퍼용 접착 시트 제조한다.

#### [LOC 구조의 반도체 장치 제조]

편평한 프레임에 의해 고정된 상기 얻어진 웨이퍼용 접착 시트상에, 테스트칩을 갖는 6인치(15.24 cm) 실리콘 웨이퍼가 접착되고, 이 웨이퍼가 12.2mm x 21.3mm 크기의 칩들로 다이스된다. 이 칩들을 사용하여 LOC 밀봉 구조의 반도체 장치가 제조된다. 이 반도체 장치의 패키지 균열 발생률이 측정된다. 그 결과가 표 1에 도시된다.

#### [예 2]

30 중량부의 4 기능성 폴리에스테르 소중합체 대신에 30 중량부의 6 기능성 폴리에스테르 아크릴레이트 소중합체[닛본 가야꾸 콤파니, 리미티드(Nippon Kayaku Co., Ltd.)로부터 입수가능]를 사용하는 것 이외에는 예 1의 절차가 반복된다. 그 결과가 표 1에 도시된다.

#### [예 3]

예 1에서 사용된 아크릴계 접착제 대신에 아크릴계 접착제[하이드록시에틸 아크릴레이트 및 부틸 아크릴레이트의 혼성 중합체, 25 중량%(몰비 26.9%)의 하이드록시에틸 아크릴레이트 함량]를 사용하는 것 이외에는 예 1의 절차가 반복된다. 그 결과가 표 1에 도시된다.

#### [예 4]

##### [방사 경화 가능 접착제 제조]

100 중량부의 아크릴계 접착제[하이드록시에틸 아크릴레이트 및 부틸 아크릴레이트의 혼성 중합체, 하이드록시에틸 아크릴레이트의 함량 : 중량비 25%(몰비 26.9%)], 약 6,000의 분자량을 갖는 70 중량부의 2기

능성 우레탄 아크릴레이트 소중합체(다이니찌세이까 컬러 & 케미컬 콤파니, 리미티드로부터 입수 가능), 30 중량부의 6 기능성 폴리에스테르 소중합체[닛본 가야꾸 콤파니, 리미티드로부터 입수 가능] 및 10 중량부의 방향족 이소시안산염(토요 잉크 콤파니, 리미티드로부터 입수 가능)이 방사 경화가능 접착제를 제조하기 위해 혼합된다.

이 방사 경화가능 접착제의 탄성 계수가 측정된다. 그 결과가 표 1에 도시된다.

그 다음에, 예 1의 절차가 예 1에서 사용된 방사 경화가능 접착제 대신에 이 방사 경화가능 접착제를 사용하는 것 이외에는 반복된다.

그 결과가 표 1에 도시된다.

#### [비교예 1]

예 1의 절차가 100 중량부 양의 아크릴계 접착제로서 아크릴산 및 부틸 아크릴레이트의 혼성 중합체[아크릴의 함량: 중량 9%]을 사용하는 것 이외에는 반복된다. 그 결과가 표 1에 도시된다.

#### [비교예 2]

예 1의 절차가 100 중량부로 2 기능성 우레탄 아크릴레이트 소중합체의 양을 변경시켜 어떠한 4기능성 폴리에스테르 소중합체도 사용하지 않는다는 것 이외에는 반복된다. 그 결과가 표 1에 도시된다.

#### [표 1]

|       | 탄성 계수             | 팩키지 균열 발생률 |

|-------|-------------------|------------|

| 예 1   | $3.8 \times 10^9$ | 0 %        |

| 예 2   | $6.3 \times 10^9$ | 0 %        |

| 예 3   | $4.0 \times 10^9$ | 0 %        |

| 예 4   | $6.5 \times 10^9$ | 0 %        |

| 비교예 1 | $5.6 \times 10^9$ | 4 %        |

| 비교예 2 | $8.7 \times 10^9$ | 67 %       |

### (57) 청구의 범위

#### 청구항 1

기판 막, 및 상기 기판 막 상에 형성된 방사 경화가능 접착층을 포함하는 웨이퍼용 접착 시트에서, 상기 접착 시트가 전면에 회로가 형성되어 있는 웨이퍼의 배면을 상기 방사 경화가능 접착층 상에 접착하는 단계, 상기 웨이퍼를 칩들로 다이스(dicing)하는 단계, 방사 에너지를 상기 방사 경화 가능 접착층에 조사하여 상기 접착층을 경화시키는 단계, 필요에 따라 상기 칩들이 서로 분리되도록 상기 접착 시트를 팽창시키는 단계, 상기 칩들을 픽업하는 단계, 상기 칩들을 리드 프레임상에 탑재 및 결합하는 단계, 및 상기 칩들의 배면들이 부분적으로 또는 전체적으로 패키지 성형 수지와 접촉하는 구조가 되도록 성형하는 단계를 포함하는 반도체 장치 제조 공정에 사용되고, 상기 방사 경화가능 접착층이 아크릴계 에스테르 및 아기-함유 중합가능 단위체의 혼성 중합체로 구성된 100 중량부의 아크릴계 접착제, 및 2개 이상의 불포화 결합들을 갖는 50-200 중량부의 방사 중합가능 화합물을 포함하고, 상기 방사 에너지 조사에 의한 경화 후에 적어도  $1 \times 10^9 \text{ dyn/cm}^2$ 의 탄성 계수를 갖는 것을 특징으로 하는 웨이퍼용 접착 시트.

#### 청구항 2

제1항에 있어서, 2개 이상의 불포화 결합들을 갖는 20 내지 80% 중량비의 상기 방사 중합가능 화합물이 4개 이상의 불포화 결합들을 갖는 것들인 것을 특징으로 하는 웨이퍼용 접착 시트.

#### 청구항 3

기판 막, 및 기판 막 상에 형성된 방사 경화가능 접착층 - 상기 방사 경화가능 접착층이 아크릴계 에스테르 및 아기-함유 중합가능 단위체의 혼성 중합체로 구성된 100 중량부의 아크릴계 접착제와 2개 이상의 불포화 결합들을 갖는 50-200 중량부의 방사 중합가능 화합물을 포함하고, 상기 에너지로의 조사에 의한 경화 후에 적어도  $1 \times 10^9 \text{ dyn/cm}^2$ 의 탄성 계수를 가짐 -을 포함하는 웨이퍼용 접착 시트를 사용한 반도체 장치의 제조 공정에 있어서, 전면에 회로가 형성되어 있는 웨이퍼의 배면을 상기 방사 경화가능 접착층 위에 접착하는 단계, 상기 웨이퍼를 칩들로 다이싱하는 단계, 방사 에너지를 상기 방사 경화 가능 접착층에 조사하여 상기 접착층을 경화시키는 단계, 필요에 따라 상기 칩들을 서로 분리하기 위해 상기 접착 시트를 팽창시키는 단계, 상기 칩들을 픽업하는 단계, 상기 칩들을 리드 프레임상에 탑재 및 결합하는 단계, 및 상기 칩들의 배면이 부분적으로 또는 전체적으로 패키지 성형 수지와 접촉하는 구조가 되도록 성형하는 단계를 포함하는 것을 특징으로 하는 웨이퍼용 접착 시트를 사용한 반도체 장치의 제조 공정.

#### 청구항 4

제3항에 있어서, 2개 이상의 불포화 결합들을 갖는 20 내지 80% 중량의 방사 중합가능 화합물이 4개 이상의 불포화 결합들을 갖는 것을 특징으로 하는 웨이퍼용 접착 시트를 사용한 반도체 장치의 제조 공정.

도면

도면1

도면2

도면3

도면4

도면5

## 도면6

도면7

도면8

도면9