(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4451095号

(P4451095)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

H01L 21/8242 (2006.01)

H01L 27/108 (2006.01)

G11C 11/401 (2006.01)

F 1

H01L 27/10 321

G11C 11/34 352Z

請求項の数 4 (全 16 頁)

(21) 出願番号 特願2003-284369 (P2003-284369)

(22) 出願日 平成15年7月31日 (2003.7.31)

(65) 公開番号 特開2005-51186 (P2005-51186A)

(43) 公開日 平成17年2月24日 (2005.2.24)

審査請求日 平成18年7月4日 (2006.7.4)

(73) 特許権者 308014341

富士通マイクロエレクトロニクス株式会社

東京都新宿区西新宿二丁目7番1号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 吉田 英司

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 田中 徹

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 正山 旭

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

凹部が形成された絶縁膜と、

前記凹部上に形成された第1導電型のシリコン層と、

前記絶縁膜上において前記凹部の外側に形成され、それらの間に前記シリコン層を挟む

第2導電型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

を有し、

前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っており、

前記ドレイン拡散層の不純物濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上であり、

前記シリコン層の厚さは、データを書き込むための電圧が前記ゲート電極に印加された

時に前記シリコン層が部分空乏化する厚さであることを特徴とする半導体記憶装置。

## 【請求項 2】

絶縁膜と、

前記絶縁膜上に形成された第1導電型のシリコン層と、

前記絶縁膜上に形成され、それらの間に前記シリコン層を挟む第2導電型のソース拡散

層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

10

20

を有し、

前記ドレイン拡散層は、

平面視で前記ゲート電極と重なり合い、不純物濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以上の第 1 の不純物拡散層と、

前記第 1 の不純物拡散層の下に形成され、前記シリコン層に接し、その不純物濃度が前記第 1 の不純物拡散層のそれよりも低い第 2 の不純物拡散層と、

を有し、

前記シリコン層の厚さは、データを書き込むための電圧が前記ゲート電極に印加された時に前記シリコン層が部分空乏化する厚さであり、

前記ドレイン拡散層は、更に、前記第 1 の不純物拡散層の下に形成され、前記シリコン層との間で前記第 2 の不純物拡散層を挟む第 3 の不純物拡散層を有し、 10

前記第 3 の不純物拡散層の不純物濃度は、前記第 2 の不純物拡散層のそれよりも高いことを特徴とする半導体記憶装置。

【請求項 3】

前記第 1 導電型が P 型であり、

前記第 2 導電型が N 型であり、

前記ゲート電極が P 型半導体からなることを特徴とする請求項 1 又は 2 に記載の半導体記憶装置。

【請求項 4】

前記第 1 導電型が P 型であり、 20

前記第 2 導電型が N 型であり、

前記ゲート電極が金属からなることを特徴とする請求項 1 又は 2 に記載の半導体記憶装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、S O I 基板を用いた半導体記憶装置に関する。

【背景技術】

【0002】

従来の D R A M セルとしては、情報を記憶するキャパシタと情報を読み取るトランジスタから構成されたものが主に用いられている。また、そのメモリ動作は、キャパシタに電荷が溜まっているときを "1" 、溜まっていないときを "0" と識別することで機能している。 30

【0003】

このような D R A M セルでは、メモリセルを微細化し高密度化するためには、トランジスタ及びキャパシタの微細化が必要である。しかし、単にトランジスタ及びキャパシタを微細化しただけでは、蓄積される電荷量が減少してしまい、D R A M 動作に必要とされる電荷量を確保できなくなる。このため、蓄積できる電荷量を減少させることなくキャパシタの寸法を微細化することが求められている。このような状況の下で、近年、三次元構造や高誘電率膜の採用によって、蓄積できる電荷量を減らさずにキャパシタ寸法をある程度まで微細化できるようになってきているが、その複雑なプロセス工程のために製造コストが高くなるという問題がある。 40

【0004】

そこで、キャパシタを用いることなくトランジスタのみで D R A M 機能を実現しようとする提案が、例えば特開 2002 - 260381 号公報（特許文献 1）、特開 2002 - 343886 号公報（特許文献 2）や、IEEE electron letters vol.23 NO.2, February 2002（非特許文献 1）に記載されている。これらの提案では、S O I 基板上に作製したトランジスタのボディ領域に多数のキャリアが蓄積している時と蓄積していない時とを、夫々 "1" 、 "0" と識別することにより D R A M 機能を実現している。また、キャリアの蓄積のためにインパクトイオン化電流を用いている。更に、特許文献 1 及び 2 には、G I 50

D L 電流 (Gate Induced Drain Leakage) を用いてデータを書き込むことも記載されている。

【 0 0 0 5 】

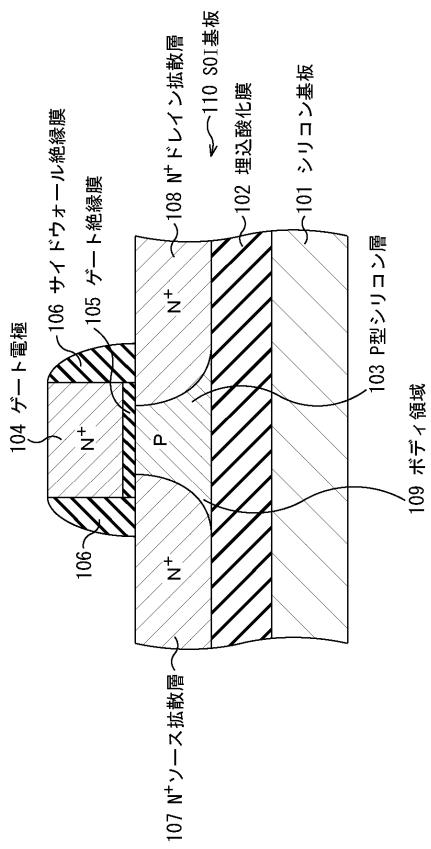

図 15 は、従来の半導体記憶装置 (D R A M ) の構造を示す断面図である。従来の D R A M では、シリコン基板 101 上に埋込酸化膜 102 が形成され、更にその上に P 型シリコン層 103 が形成されて S O I 基板 110 が構成されている。そして、メモリセル毎に、P 型シリコン層 103 とゲート電極 104 (ワード線)との間に、ゲート絶縁膜 105 が形成されている。また、ゲート電極 104 の側方にはサイドウォール絶縁膜 106 が形成されている。そして、P 型シリコン層 103 には、メモリセル毎に、埋込酸化膜 102 まで達する N<sup>+</sup>ソース拡散層 107 及び N<sup>+</sup>ドレイン拡散層 108 が形成され、ゲート絶縁膜 105 の下で N<sup>+</sup>ソース拡散層 107 及び N<sup>+</sup>ドレイン拡散層 108 に挟まれた領域がボディ領域 109 となっている。N<sup>+</sup>ドレイン拡散層 108 は、コンタクトプラグ (図示せず) 等を介してビット線に接続されており、N<sup>+</sup>ソース拡散層 107 には、コンタクトプラグ (図示せず) 等を介して接地電位が供給される。

【 0 0 0 6 】

しかしながら、書き込み動作にインパクトイオン化電流を用いる場合には、書き込み時に高電圧を用いて大きなドレイン電流を流す必要があり消費電力が大きくなってしまうという問題がある。

【 0 0 0 7 】

【特許文献 1】特開 2002 - 260381 号公報

20

【特許文献 2】特開 2002 - 343886 号公報

【非特許文献 1】アイ・イー・イー・イー・エレクトロン・レターズ (IEEE electron letters) 、2002 年 2 月、第 30 卷、第 2 号

【発明の開示】

【発明が解決しようとする課題】

【 0 0 0 8 】

本発明は、G I D L 電流を用いたデータの書き込みを高い効率で行うことができる半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

【 0 0 0 9 】

30

本願発明者は、前記課題を解決すべく鋭意検討を重ねた結果、以下に示す発明の諸態様に想到した。

【 0 0 1 0 】

本願発明に係る第 1 の半導体記憶装置は、絶縁膜と、前記絶縁膜上に形成された第 1 導電型のシリコン層と、前記絶縁膜上に形成され、それらの間に前記シリコン層を挟む第 2 導電型のソース拡散層及びドレイン拡散層と、前記シリコン層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、を有する半導体記憶装置を対象とする。そして、前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合い、不純物濃度が  $1 \times 10^{19} \text{ cm}^{-3}$  以上の第 1 の不純物拡散層と、前記第 1 の不純物拡散層の下に形成され、前記シリコン層に接し、その不純物濃度が前記第 1 の不純物拡散層のそれよりも低い第 2 の不純物拡散層と、を有している。更に、前記シリコン層の厚さは、データを書き込むための電圧が前記ゲート電極に印加された時に前記シリコン層が部分空乏化する厚さである。また、前記ドレイン拡散層は、更に、前記第 1 の不純物拡散層の下に形成され、前記シリコン層との間で前記第 2 の不純物拡散層を挟む第 3 の不純物拡散層を有し、前記第 3 の不純物拡散層の不純物濃度は、前記第 2 の不純物拡散層のそれよりも高い。

40

【 0 0 1 1 】

本願発明に係る第 2 の半導体記憶装置には、凹部が形成された絶縁膜と、前記凹部上に形成された第 1 導電型のシリコン層と、前記絶縁膜上において前記凹部の外側に形成され、それらの間に前記シリコン層を挟む第 2 導電型のソース拡散層及びドレイン拡散層と、前記シリコン層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート

50

電極と、が設けられている。そして、前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っており、前記ドレイン拡散層の不純物濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上であり、前記シリコン層の厚さは、データを書き込むための電圧が前記ゲート電極に印加された時に前記シリコン層が部分空乏化する厚さである。

【発明の効果】

【0012】

第1の半導体記憶装置では、ドレイン拡散層が第1及び第2の不純物拡散層から構成され、第1の不純物拡散層の不純物濃度が適切に規定されているため、GIDL電流が十分に流れ、高速な書き込みが可能となる。また、第2の不純物拡散層の存在により、シリコン層との間のpn接合にかかる電界が緩和されるため、接合リーキ電流の増加を回避することができる。

10

【0013】

また、ドレイン拡散層とゲート電極との間で導電型が相違している場合には、効果的にGIDL電流を流すことができる。このような効果は、Mo、Ni、Al又はCo等の金属からゲート電極が形成されている場合や、ボロンが導入されたCosi又はNisi等のシリサイドからゲート電極が形成されている場合にも得られる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施形態について添付の図面を参照して具体的に説明する。

20

【0015】

(第1の実施形態)

先ず、本発明の第1の実施形態について説明する。第1の実施形態では、SOI基板を用いたNチャネルMOSトランジスタのゲート電極としてN型半導体を用いている。図1は、本発明の第1の実施形態に係る半導体記憶装置(DRAM)の構造を示すレイアウト図であり、図2は、図1中のI-I線に沿った断面図である。

【0016】

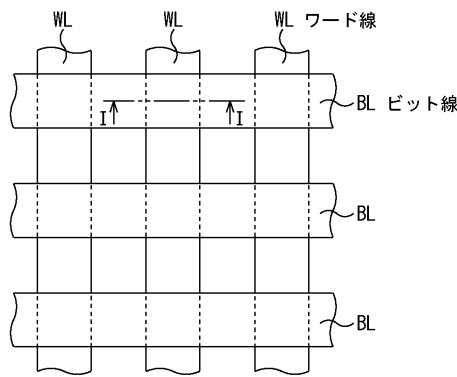

第1の実施形態では、例えば複数本のワード線WLと複数本のビット線BLとが互いに直交して配置されている。そして、ワード線WLとビット線BLとの交点毎に、その周囲にわたってメモリセル(DRAMセル)が形成されている。ワード線WLはN<sup>+</sup>ポリシリコン層から構成されており、各メモリセルにおいてゲート電極4として機能する。なお、ビット線BLは、簡潔化のため図2では省略している。

30

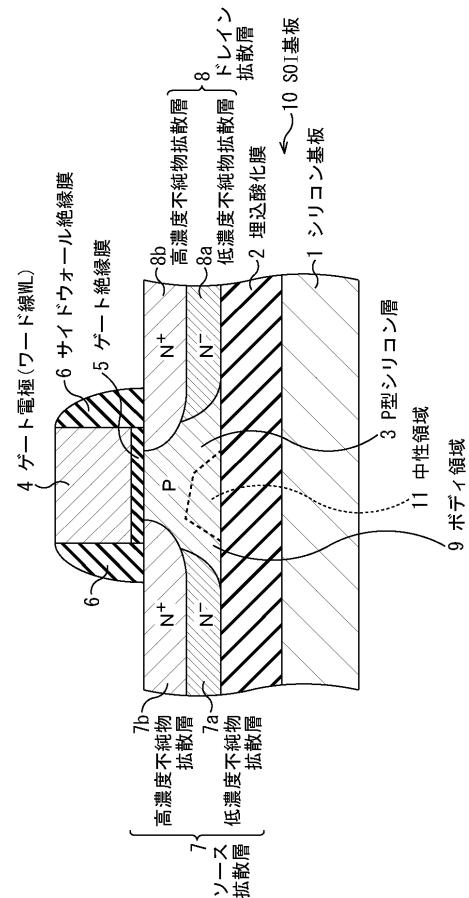

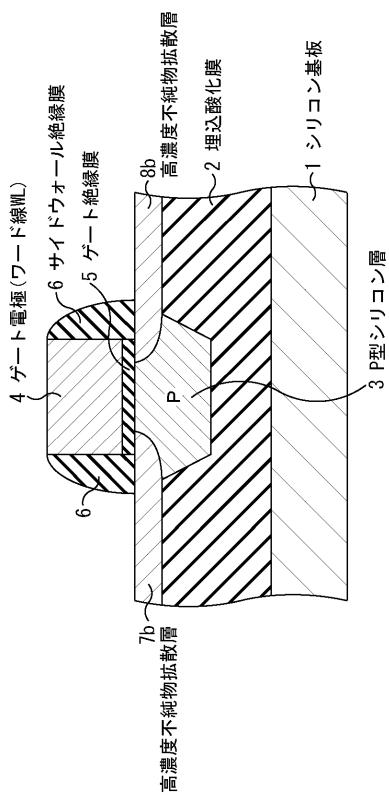

【0017】

また、シリコン基板1上に埋込酸化膜2が形成され、更にその上にP型シリコン層3が形成されてSOI基板10が構成されている。そして、メモリセル毎に、P型シリコン層3とゲート電極4(ワード線WL)との間に、ゲート絶縁膜5が形成されている。また、ゲート電極4(ワード線WL)の側方にはサイドウォール絶縁膜6が形成されている。そして、P型シリコン層3には、メモリセル毎に、埋込酸化膜2まで達するN型のソース拡散層7及びドレイン拡散層8が形成され、ゲート絶縁膜5の下でソース拡散層7及びドレイン拡散層8に挟まれた領域がボディ領域9となっている。ソース拡散層7は、例えば、埋込酸化膜2上に形成されたN型低濃度不純物拡散層7aと、その上に形成されたN型高濃度不純物拡散層7bとから構成され、ドレイン拡散層8は、例えば、埋込酸化膜2上に形成されたN型低濃度不純物拡散層8aと、その上に形成されたN型高濃度不純物拡散層8bとから構成されている。これらの拡散層のうち、本実施形態では、高濃度不純物拡散層7b及び8bのみが、平面視でゲート電極4と重なり合っている。高濃度不純物拡散層8bの不純物濃度は $1.00 \times 10^{19} \text{ cm}^{-3}$ 以上であり、 $1.00 \times 10^{20} \text{ cm}^{-3}$ 以上であることが好ましい。

40

【0018】

また、P型シリコン層3の厚さは、後述の動作によっても完全空乏化せず部分空乏化となる程度である。例えば、埋込酸化膜2の厚さは150nm程度であり、P型シリコン層3の厚さは70nm程度である。また、例えば、ゲート長は0.2μm程度であり、ゲー

50

ト絶縁膜 5 の厚さは 5 . 8 nm 程度である。N<sup>+</sup>ドレイン拡散層 8 は、コンタクトプラグ（図示せず）等を介してビット線 B L に接続されており、N<sup>+</sup>ソース拡散層 7 には、コンタクトプラグ（図示せず）等を介して一定電位、例えば接地電位が供給される。

#### 【 0 0 1 9 】

このように構成された第 1 の実施形態において、データ“ 1 ”を書き込む場合には、書き込もうとするメモリセルに対して、ゲート電極 4 を負にバイアスし、ドレイン拡散層 8 を正にバイアスする。例えば、ゲート電極 4 (ワード線 W L ) に - 2 . 4 V を印加し、ビット線 B L からドレイン拡散層 8 に 0 . 2 V を印加する。この結果、ゲート電極 4 とドレイン拡散層 8 との重なり領域（平面視で、ゲート電極 4 と高濃度不純物拡散層 8 b とが重なり合う領域）でエネルギーバンドの曲がりが大きくなり、荷電子帯の電子が伝導帯にトンネルすることにより G I D L 電流が発生する。そして、G I D L 電流の発生に伴って、余剰ホール（正孔）が発生し、この余剰ホールがボディ領域 9 の中性領域 1 1 に蓄積し、しきい値電圧が低下する。10

#### 【 0 0 2 0 】

一方、データ“ 0 ”を書き込む場合には、書き込もうとするメモリセルに対して、ドレイン拡散層 8 を負にバイアスして、ドレイン拡散層 8 とボディ領域 9 との p n 接合を順方向にバイアスすることにより、蓄積していたホールをドレイン拡散層 8 に放出する。例えば、ゲート電極 4 (ワード線 W L ) に 0 . 8 V を印加し、ビット線 B L からドレイン拡散層 8 に - 1 . 5 V を印加する。この結果、中性領域 1 1 中のホールが消失し、しきい値電圧が上昇する。20

#### 【 0 0 2 1 】

そして、書き込まれたデータを読み出す場合には、書き込もうとするメモリセルに対して、例えば、ゲート電極 4 (ワード線 W L ) に 0 . 8 V を印加し、ビット線 B L からドレイン拡散層 8 に 0 . 2 V を印加する。この結果、N チャネル M O S トランジスタのしきい値電圧に応じたドレイン電流が流れ、そのメモリセルに記憶されていたデータを判別できる。

#### 【 0 0 2 2 】

また、本実施形態では、ドレイン拡散層 8 を構成する高濃度不純物拡散層 8 b が平面視でゲート電極 4 と重なり合っているだけでなく、高濃度不純物拡散層 8 b の不純物濃度を  $1 . 0 0 \times 1 0^{19} \text{ c m}^{-3}$  以上、好ましくは  $1 . 0 0 \times 1 0^{20} \text{ c m}^{-3}$  以上としているため、効果的に G I D L 電流が流れる。30

#### 【 0 0 2 3 】

なお、ドレイン - ボディ間の p n 接合に強い電界がかかると、接合リーケ電流が増大してデータの保持時間（リテンション時間）が短くなってしまう。しかし、本実施形態では、高濃度不純物拡散層 8 b と埋込酸化膜 2 との間に低濃度不純物拡散層 7 b が P 型シリコン層 3 と接するようにして存在しているため、ドレイン - ボディ間の p n 接合に強い電界がかかることが避けられる。従って、このようなリーケ電流の増加に伴うデータ保持時間の短縮を回避することができる。

#### 【 0 0 2 4 】

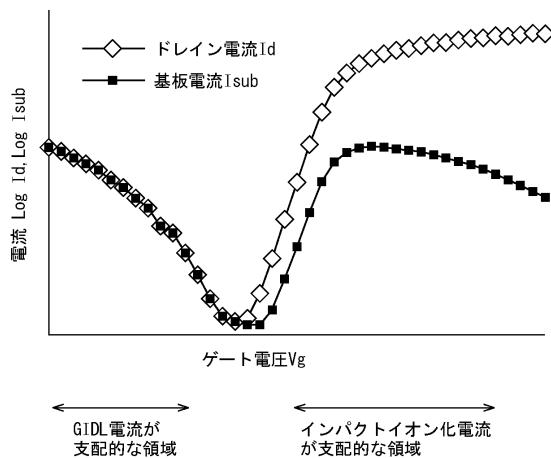

また、インパクトイオン化電流を用いた場合と比較すると、消費電力を低減することができる。図 3 に示すように、インパクトイオン化によって生じるホール電流は、N<sup>+</sup>ドレイン拡散層 8 に流れる電流に対してかなり小さい。これに対して、G I D L 電流は N<sup>+</sup>ドレイン拡散層 8 に流れる電流とほぼ同等の大きさである。即ち、インパクトイオン化電流を用いた書き込みでは、余分なドレイン電流を流す必要があるのに対し、G I D L 電流を用いた書き込みでは、そのような余分なドレイン電流をほとんど流す必要がない。この結果、インパクトイオン化電流を用いた場合と比較すると、G I D L 電流を書き込みに用いた本実施形態では低消費電力で書き込み動作を行うことができる。 40

#### 【 0 0 2 5 】

これは、次のような理由による。インパクトイオン化電流を用いた書き込みの場合には、大きなドレイン電流を流すことによって、インパクトイオン化を生じさせて、ホールを50

発生させる。従って、発生するホール量よりも何桁も大きい無駄なドレイン電流を流す必要がある。これに対し、GIDL電流を用いた書き込みでは、書き込みに必要なホールはバンド間トンネルによって発生しているため、発生させたホールとほぼ同等の電子はドレインに流れるのである。従って、無駄な電力の消費はほとんどない。

【0026】

また、前述のように、GIDL電流を発生させるためには、ゲート電極4に負バイアス、ドレイン拡散層8に正バイアスを印加する。GIDL電流の量はゲート-ドレイン間の電位差によって決まるため、ゲートの負バイアスを強くすることにより、GIDL電流が増大し、書き込み速度が速くなる。また、ゲートの負バイアスを強くすることにより、ゲート-ボディ間の容量結合によってボディ領域9も強く負バイアスされることになる。この結果、ソース-ボディ間のpn接合障壁が高くなり、ボディ領域9に蓄積可能なホールの量が増大される。更に、ドレイン-ボディ間及びソース-ボディ間に逆バイアスが強く印加されることになるため、pn接合空乏層領域からのホールの生成量が増大し、そのホールの移動が書き込み電流として寄与するため、書き込み速度が速くなる。

【0027】

(第2の実施形態)

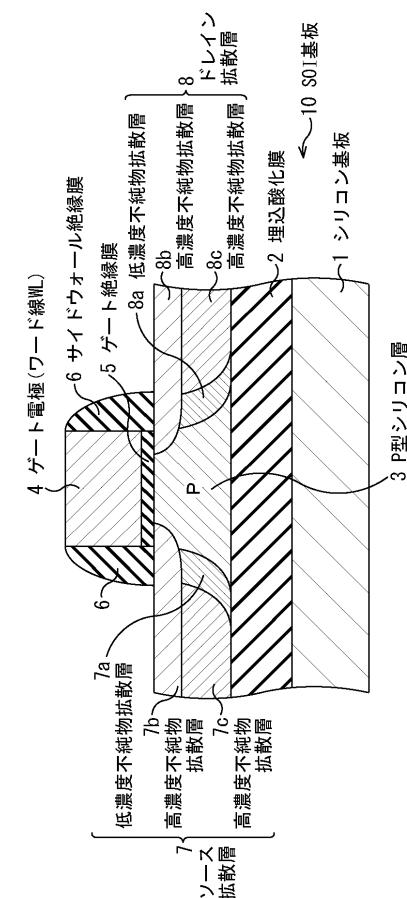

次に、本発明の第2の実施形態について説明する。第2の実施形態では、第1の実施形態における低濃度不純物拡散層7a及び8aの一部が高濃度不純物拡散層に置き換えられている。図4は、本発明の第2の実施形態に係る半導体記憶装置の構造を示す断面図であり、図2と同様に、図1中のI-I線に沿った断面図に相当する。

【0028】

本実施形態では、図4に示すように、高濃度不純物拡散層7b及び8bと埋込酸化膜2との間に、低濃度不純物拡散層7a及び8aだけでなく、夫々、高濃度不純物拡散層7c、8cが形成されている。低濃度不純物拡散層7a及び8aは、サイドウォール絶縁膜6の下方及びその近傍に形成されており、高濃度不純物拡散層7c及び8cは、夫々低濃度不純物拡散層7a、8aよりもゲート電極4から離間した位置に形成されている。

【0029】

このように構成された第2の実施形態では、第1の実施形態と比較すると、ソース拡散層7及びドレイン拡散層8の不純物濃度がより高くなっているので、コンタクト抵抗等の寄生抵抗がより低減される。

【0030】

(第3の実施形態)

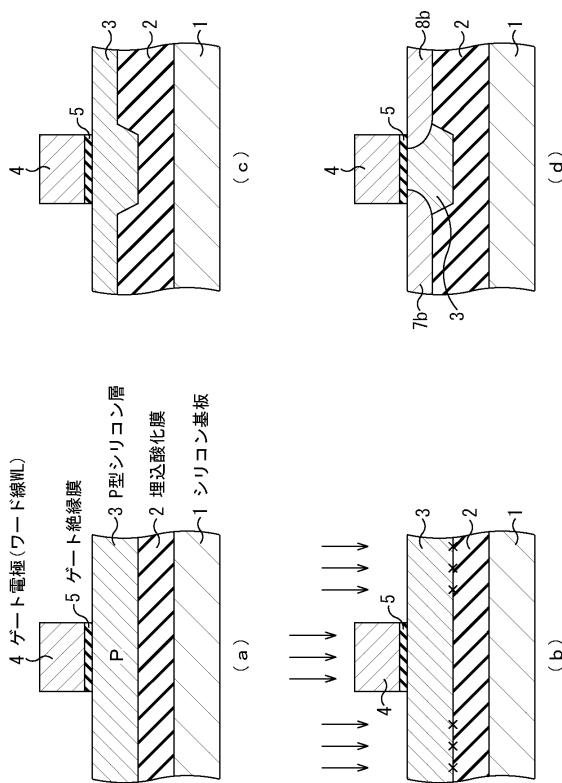

次に、本発明の第3の実施形態について説明する。第3の実施形態では、実質的に、第1の実施形態における低濃度不純物拡散層7a及び8aが埋込酸化膜で置き換えられている。図5は、本発明の第3の実施形態に係る半導体記憶装置の構造を示す断面図であり、図2と同様に、図1中のI-I線に沿った断面図に相当する。

【0031】

本実施形態では、図5に示すように、ソース拡散層が高濃度不純物拡散層7bから構成され、ドレイン拡散層が高濃度不純物拡散層8bから構成されている。即ち、低濃度不純物拡散層7a及び8a等が形成されていない。また、P型シリコン層3の厚さは、第1及び第2の実施形態のものと同程度である。更に、埋込酸化膜2については、P型シリコン層3の下方では、その厚さが第1の実施形態と同様であるが、高濃度不純物拡散層7b及び8bの下方では、その厚さが第1の実施形態よりも厚くなっているが、埋込酸化膜2が高濃度不純物拡散層7b及び8bと直接接している。

【0032】

このように構成された第3の実施形態では、第1及び第2の実施形態と比較すると、pn接合の接合長が短くなるため、接合リーケ電流が減少してリテンション時間が長くなる。

【0033】

但し、P型シリコン層3を薄くすることのみによって高濃度不純物拡散層7b及び8b

10

20

30

40

50

と埋込酸化膜2とが直接接するようにしたのでは、完全空乏化トランジスタになる虞がある。完全空乏化トランジスタになると、ホール(電荷)が蓄積されなくなってしまう。

【0034】

ここで、第3の実施形態に係る半導体記憶装置を製造する方法について説明する。図6(a)乃至(d)は、本発明の第3の実施形態に係る半導体記憶装置を製造する方法を工程順に示す断面図である。

【0035】

この方法では、図6(a)に示すように、シリコン基板1、埋込酸化膜2及びP型シリコン層3からなるSOI基板を用意し、その上に、ゲート絶縁膜5及びゲート電極4を形成する。このとき、P型シリコン層3の厚さは、第1及び第2の実施形態のものと同程度とする。

【0036】

次に、図6(b)に示すように、ゲート電極4をマスクとして用い、自己整合的に酸素イオンを埋込酸化膜2とP型シリコン層3との界面近傍に注入する。

【0037】

次いで、アニールを施すことにより、P型シリコン層3の酸素イオンが注入された領域近傍において酸化反応を生じさせる。この結果、図6(c)に示すように、埋込酸化膜2の平面視でゲート電極4から外れた部分が厚くなり、その分だけP型シリコン層3が薄くなる。

【0038】

その後、ゲート電極4をマスクとして用い、自己整合的にN型不純物をP型シリコン層3中に注入し、この不純物を活性化することにより、高濃度不純物拡散層7b及び8bを形成する。

【0039】

そして、層間絶縁膜及び配線等の形成を行って半導体記憶装置を完成させる。

【0040】

(第4の実施形態)

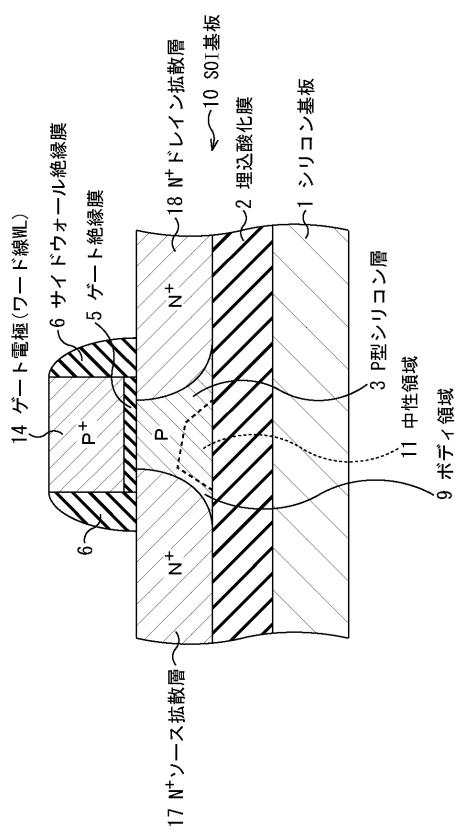

次に、本発明の第4の実施形態について説明する。第4の実施形態では、SOI基板を用いたNチャネルMOSトランジスタのゲート電極としてP型半導体を用いている。図7は、本発明の第4の実施形態に係る半導体記憶装置(DRAM)の構造を示す断面図であり、図2と同様に、図1中のI-I線に沿った断面図に相当する。ここでは、主に第1の実施形態との相違点について説明する。

【0041】

第4の実施形態では、図7に示すように、ワード線WLがP<sup>+</sup>ポリシリコン層から構成されており、各メモリセルにおいてゲート電極14として機能する。

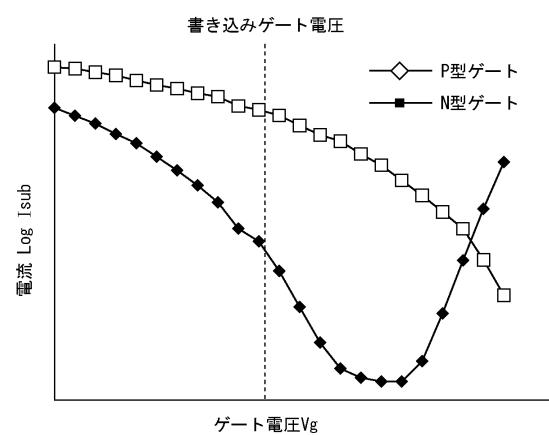

【0042】

一般に、GIDL電流は、ゲートとドレインとの電位差が大きいほど大量に流れる。第4の実施形態では、ゲートとドレインとの導電型を相違させているため、第1の実施形態と同様の書き込み電圧を用いた場合には、図8に示すように、GIDL電流がより大量に流れるため、より高速な書き込みが可能となる。逆に、第1の実施形態と同程度の書き込み速度を達成しようとする場合には、より低い書き込み電圧を用いることになるため、消費電力を低減することができる。

【0043】

なお、このような効果は、ゲートとドレインとの電位差が大きくなるように、Mo、Ni、Al、Co等の金属材料からゲート電極14を形成した場合にも得られる。更に、ボロンが導入されたCosi、Nisi等のシリサイド材料からゲート電極14を形成した場合にも同様の効果が得られる。

【0044】

その他、1つの半導体装置内にロジック回路又は他の不揮発性メモリ等と混載形成することで、キャパシタの形成が不要で製造工程を簡略化することが可能な半導体記憶装置を

10

20

30

40

50

提供することもできる。

【実施例 1】

【0045】

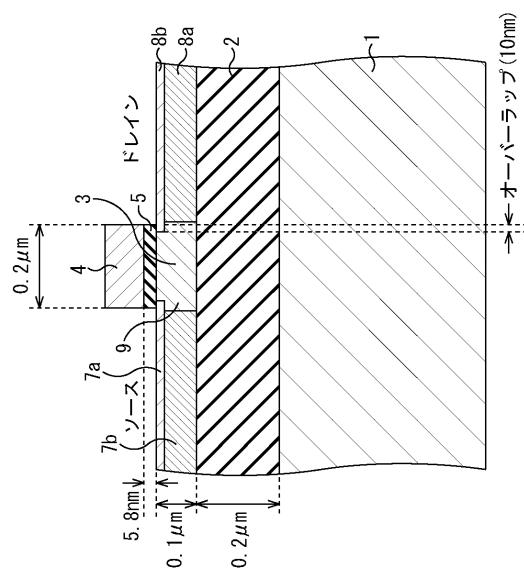

次に、本願発明者が実際に行ったシミュレーションの結果について説明する。このシミュレーションでは、図9に示すように、埋込酸化膜2の厚さを0.2μm、P型シリコン層3の厚さを0.1μm、ゲート絶縁膜5の厚さを5.8nm、ゲート長を0.2μm、重なり領域の長さ（オーバーラップ）を10nmとした。

【0046】

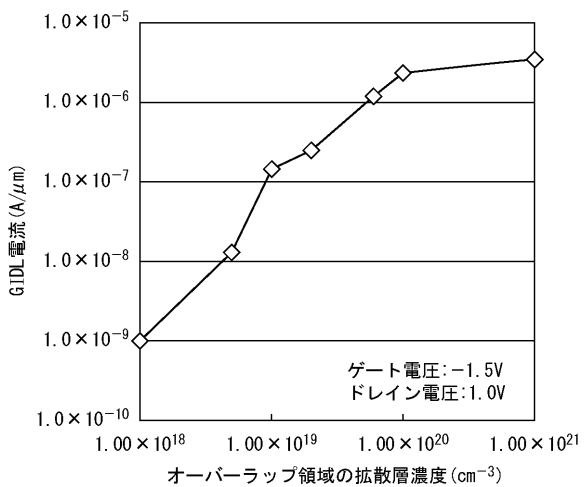

そして、高濃度不純物拡散層7b及び8b中の不純物濃度を変化させてGIDL電流の値をシミュレーションした。ここでは、データの書き込み時に、ゲート電極4に-1.5Vを印加し、ドレイン拡散層に1.0Vを印加することとした。

10

【0047】

このシミュレーションの結果、図10に示すように、高濃度不純物拡散層7b及び8b中の不純物濃度（オーバーラップ領域の拡散層濃度）が高いほどGIDL電流が高くなつた。特に、不純物濃度が $1.00 \times 10^{19} \text{ cm}^{-3}$ 以上のときに、十分なGIDL電流を得ることができた。GIDL電流は $1.0 \times 10^{-7} \text{ A} / \mu\text{m}$ 以上になると高速なメモリ書き込みが可能となるため、不純物濃度が $1.00 \times 10^{19} \text{ cm}^{-3}$ 以上であればよく、GIDL電流が実質的に飽和する $1.00 \times 10^{20} \text{ cm}^{-3}$ 以上であることが好ましい。

【実施例 2】

【0048】

20

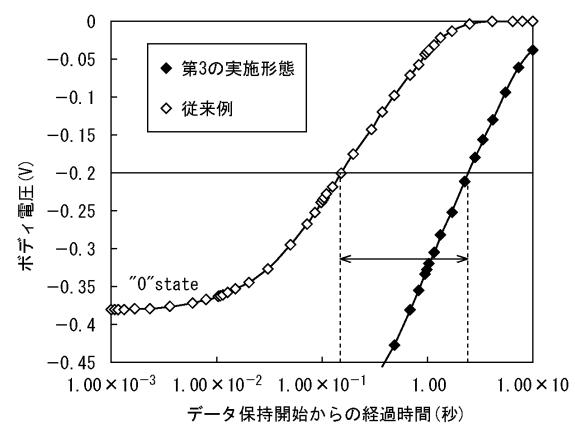

また、第1乃至第3の実施形態について、リテンション時間の測定（シミュレーション）を行つた。図11は、データ“0”を書き込み、保持するときの各電圧の変化を示すタイミングチャートである。

【0049】

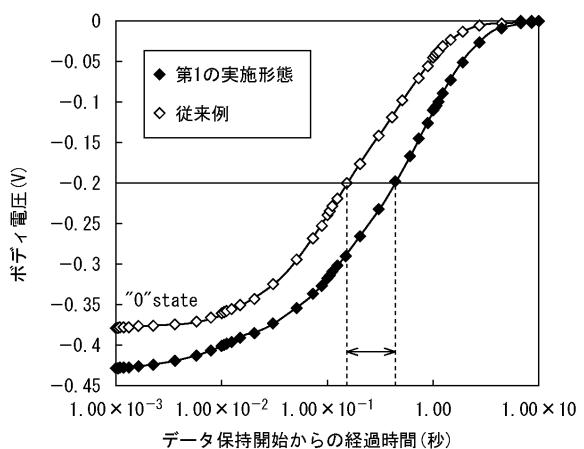

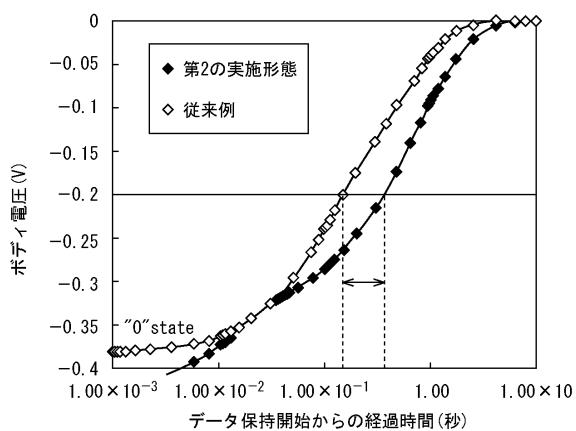

データ“0”を保持している状態では、ボディ電圧が負になるため、ソース-ボディ間及びドレイン-ボディ間のpn接合が逆バイアスされる。そして、この逆バイアスにより、ホールがボディ領域に徐々に注入され、次第にデータ“0”が消失する。従つて、データの保持を開始してからの経過時間に対するボディ電圧の変化をプロットすれば、データ“0”を保持することが可能な時間が算出される。このシミュレーションでは、ボディ電圧が-0.2Vに達するまでの経過時間をデータの保持が可能な時間（リテンション時間）とした。

30

【0050】

第1の実施形態の構造において高濃度不純物拡散層7b及び8bの不純物濃度を $1 \times 10^{20} \text{ cm}^{-3}$ 、低濃度不純物拡散層7a及び8aの不純物濃度を $6 \times 10^{18} \text{ cm}^{-3}$ とした場合、図12に示すように、リテンション時間は0.42秒間だった。これに対し、ドレイン拡散層の不純物濃度を $1 \times 10^{20} \text{ cm}^{-3}$ とした従来の構造のものでは、リテンション時間が0.15秒間であった。即ち、第1の実施形態によれば、リテンション時間を約2.8倍延ばすことができた。

【0051】

第2の実施形態の構造において高濃度不純物拡散層7b及び8bの不純物濃度を $1 \times 10^{20} \text{ cm}^{-3}$ 、低濃度不純物拡散層7a及び8aの不純物濃度を $6 \times 10^{18} \text{ cm}^{-3}$ とした場合には、図13に示すように、リテンション時間は0.37秒間だった。

40

【0052】

第3の実施形態の構造において高濃度不純物拡散層7b及び8bの不純物濃度を $1 \times 10^{20} \text{ cm}^{-3}$ とした場合には、図14に示すように、リテンション時間は2.3秒間と極めて長くなった。

【0053】

以下、本発明の諸態様を付記としてまとめて記載する。

（付記1）

絶縁膜と、

50

前記絶縁膜上に形成された第1導電型のシリコン層と、

前記絶縁膜上に形成され、それらの間に前記シリコン層を挟む第2導電型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

を有し、

前記ドレイン拡散層は、

平面視で前記ゲート電極と重なり合い、不純物濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上の第1の不純物拡散層と、

前記第1の不純物拡散層の下に形成され、前記シリコン層に接し、その不純物濃度が前記第1の不純物拡散層のそれよりも低い第2の不純物拡散層と、

を有することを特徴とする半導体記憶装置。

【0054】

(付記2)

前記ドレイン拡散層は、更に、前記第1の不純物拡散層の下に形成され、前記シリコン層との間で前記第2の不純物拡散層を挟む第3の不純物拡散層を有し、

前記第3の不純物拡散層の不純物濃度は、前記第2の不純物拡散層のそれよりも高いことを特徴とする付記1に記載の半導体記憶装置。

【0055】

(付記3)

凹部が形成された絶縁膜と、

前記凹部上に形成された第1導電型のシリコン層と、

前記絶縁膜上において前記凹部の外側に形成され、それらの間に前記シリコン層を挟む第2導電型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

を有し、

前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っており、

前記ドレイン拡散層の不純物濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上であることを特徴とする半導体記憶装置。

【0056】

(付記4)

前記シリコン層の厚さは、データを書き込むための電圧が前記ゲート電極に印加された時に前記シリコン層が部分空乏化する厚さであることを特徴とする付記1乃至3のいずれか1項に記載の半導体記憶装置。

【0057】

(付記5)

絶縁膜と、

前記絶縁膜上に形成されたP型のシリコン層と、

前記絶縁膜上に形成され、それらの間に前記シリコン層を挟むN型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたP型半導体からなるゲート電極と、

を有し、

前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っていることを特徴とする半導体記憶装置。

【0058】

(付記6)

絶縁膜と、

前記絶縁膜上に形成されたP型のシリコン層と、

10

20

30

40

50

前記絶縁膜上に形成され、それらの間に前記シリコン層を挟むN型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、金属からなるゲート電極と、

を有し、

前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っていることを特徴とする半導体記憶装置。

【0059】

(付記7)

前記ゲート電極は、Mo、Ni、Al及びCoからなる群から選択された1種の金属からなることを特徴とする付記6に記載の半導体記憶装置。 10

【0060】

(付記8)

絶縁膜と、

前記絶縁膜上に形成されたP型のシリコン層と、

前記絶縁膜上に形成され、それらの間に前記シリコン層を挟むN型のソース拡散層及びドレイン拡散層と、

前記シリコン層上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、ボロンが導入されたシリサイドからなるゲート電極と

、 20

を有し、

前記ドレイン拡散層は、平面視で前記ゲート電極と重なり合っていることを特徴とする半導体記憶装置。

【0061】

(付記9)

前記シリサイドは、CoSi及びNiSiからなる群から選択された1種であることを特徴とする付記8に記載の半導体記憶装置。 30

【0062】

(付記10)

基板、酸化膜及び第1導電型のシリコン層からなるSOI基板に対し、前記シリコン層上にゲート絶縁膜及びゲート電極を形成する工程と、 30

前記ゲート電極をマスクとして、前記酸化膜と前記シリコン層との界面に向けて酸素イオンを注入する工程と、

熱処理によって前記シリコン層の前記酸化膜側の部分を酸化することにより、前記酸化膜を厚くする工程と、

前記ゲート電極をマスクとして、前記シリコン層に第2導電型の不純物のイオンを注入する工程と、

熱処理によって前記第2導電型の不純物を活性化させることにより、前記酸化膜まで達するソース拡散層及びドレイン拡散層を形成する工程と、

を有することを特徴とする半導体記憶装置の製造方法。 40

【図面の簡単な説明】

【0063】

【図1】本発明の第1の実施形態に係る半導体記憶装置の構造を示すレイアウト図である。

【図2】図1中のI-I線に沿った断面図である。

【図3】ゲート電圧と電流との関係を示すグラフである。

【図4】本発明の第2の実施形態に係る半導体記憶装置の構造を示す断面図である。

【図5】本発明の第3の実施形態に係る半導体記憶装置の構造を示す断面図である。

【図6】本発明の第3の実施形態に係る半導体記憶装置を製造する方法を工程順に示す断面図である。 50

【図7】本発明の第4の実施形態に係る半導体記憶装置の構造を示す断面図である。

【図8】ゲートの導電型と電流との関係を示すグラフである。

【図9】シミュレーションの対象とした構造を示す図である。

【図10】拡散層の不純物濃度とGIDL電流との関係を示すグラフである。

【図11】データ“0”を書き込み、保持するときの各電圧の変化を示すタイミングチャートである。

【図12】第1の実施形態における経過時間とボディ電圧との関係を示すグラフである。

【図13】第2の実施形態における経過時間とボディ電圧との関係を示すグラフである。

【図14】第3の実施形態における経過時間とボディ電圧との関係を示すグラフである。

【図15】従来の半導体記憶装置(DRAM)の構造を示す断面図である。

10

【符号の説明】

【0064】

1：シリコン基板

2：埋込酸化膜

3：P型シリコン層

4、14：ゲート電極

5：ゲート絶縁膜

6：サイドウォール絶縁膜

7：ソース拡散層

7a：低濃度不純物拡散層

7b、7c：高濃度不純物拡散層

8：ドレイン拡散層

8a：低濃度不純物拡散層

8b、8c：高濃度不純物拡散層

9：ボディ領域

10：SOI基板

11：中性領域

BL：ビット線

WL：ワード線

20

【 図 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2003-031696(JP,A)

特開2002-260381(JP,A)

特開平08-213624(JP,A)

特開平04-067682(JP,A)

特開2003-158198(JP,A)

特開2001-007338(JP,A)

特表2006-505948(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

G11C 11/401

H01L 27/108

H01L 29/786

H01L 29/78