【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成28年3月17日(2016.3.17)

【公開番号】特開2014-229227(P2014-229227A)

【公開日】平成26年12月8日(2014.12.8)

【年通号数】公開・登録公報2014-067

【出願番号】特願2013-110560(P2013-110560)

【国際特許分類】

G 0 6 T 1/60 (2006.01)

【F I】

G 0 6 T 1/60 4 5 0 F

【手続補正書】

【提出日】平成28年1月28日(2016.1.28)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0 0 3 6

【補正方法】変更

【補正の内容】

【0 0 3 6】

撮像素子31からの1ライン目の画素データのリード後、わずかなブランクを挟み水平同期信号のパルスが生成されると(タイミングt2)、2ライン目の画素データが、並列化部11で並列データとなり、図4のようなセンサ入力IN1～IN4としてRAM41にライトされる。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 1

【補正方法】変更

【補正の内容】

【0 0 4 1】

これに対して、第1の実施の形態の画像データ処理装置10では、N×N個の記憶部12, 12a, 12bを用いて、前述したようなライト及びリードの制御を行うことで、データ破壊の発生を抑制できる。また、記憶部12a, 12b以外の大部分の記憶部12に1ポートRAMを用いることができる。そのため、並列の画素データの並べ替え時のデータ破壊の発生を小規模な回路で抑制できる。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 3

【補正方法】変更

【補正の内容】

【0 0 4 3】

撮像装置50は、撮像部60、画像データ処理装置70を有している。

撮像部60は、レンズや反射鏡などの撮像光学系61、CCD(Charge Coupled Device)などである撮像素子62、アンプやフィルタ、ADC(Analog to Digital Converter)などを含むアナログフロントエンド63(図6ではAFEと表記されている)を有する。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 4

【補正方法】変更

【補正の内容】

【0044】

画像データ処理装置70は、たとえば、ISPであり、CPU(Central Processing Unit)71により各部が制御される。画像データ処理装置70は、並列データ生成/処理部72、色処理部73、他画像処理部74、表示インターフェース(以下表示I/Fと表記する)75、メモリカードI/F76、静止画コーデック部77、DMA(Direct Memory Access)調停部78、SDRAM(Synchronous Dynamic Random Access Memory)コントローラ79を有している。また、並列データ生成/処理部72、色処理部73、他画像処理部74、表示I/F75、メモリカードI/F76、静止画コーデック部77は、DMAコントローラ72a, 73a, 74a, 75a, 76a, 77aを有しており、内部バス80に接続されている。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0055

【補正方法】変更

【補正の内容】

【0055】

WCNTカウント用レジスタ91eは、比較部91dがイネーブル信号をアサートするごとにカウント値WCNTをインクリメントする。カウント値WCNTは、ライトが行われるRAMを示す。また、WCNTカウント用レジスタ91eは、N回ライトアドレスWADが閾値RAMTHに達すると1ライン分の書き込みが完了したことになるので、ライトイネーブル信号WENをネガートさせる。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0057

【補正方法】変更

【補正の内容】

【0057】

読み出し制御部92は、REN生成部92a、タイミング調整用カウンタ92b、AND回路92c、RADカウント用レジスタ92d、比較部92e、RCNTカウント用レジスタ92fを有する。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0062

【補正方法】変更

【補正の内容】

【0062】

RCNTカウント用レジスタ92fは、比較部92eがイネーブル信号をアサートするごとにカウント値RCNTをインクリメントする。カウント値RCNTは、リードが行われるRAMを示す。また、RCNT用レジスタ92fは、N回、リードアドレスRADが閾値RAMTHに達すると読み出しが完了したことになるので、リードイネーブル信号RENをネガートさせる。

【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0065

【補正方法】変更

【補正の内容】

【0065】

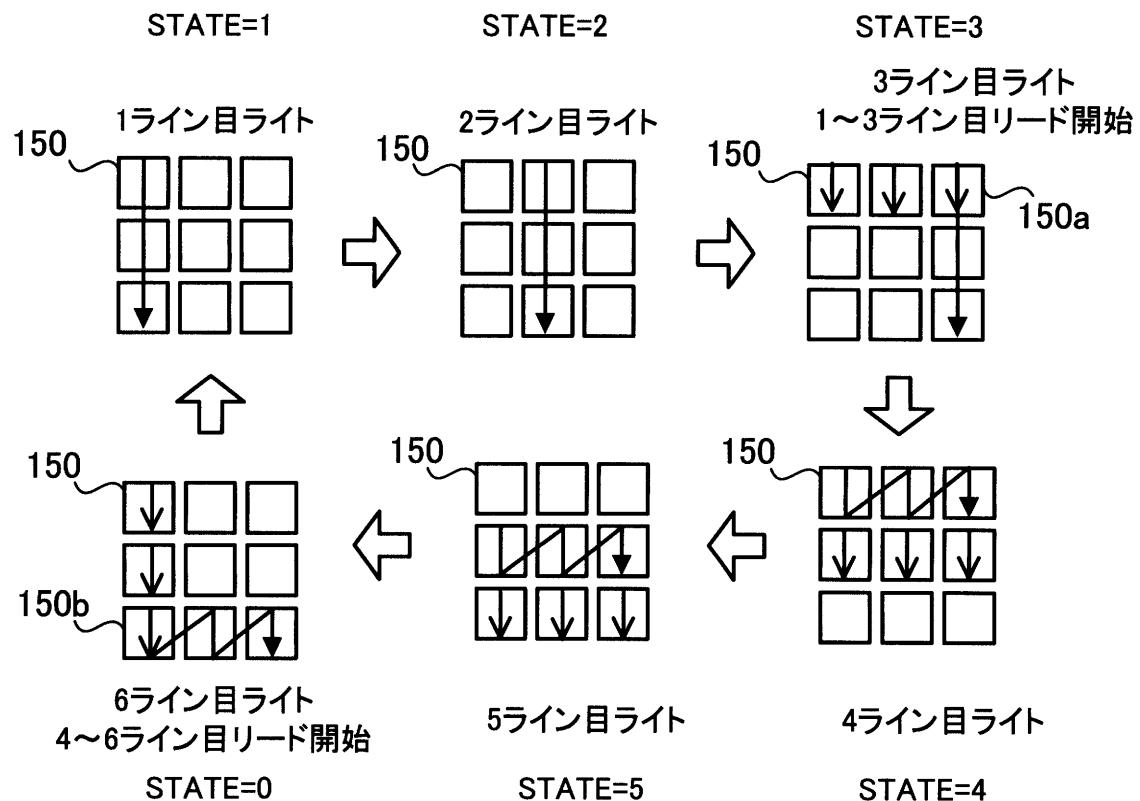

入力信号制御部90bは、STATEカウント用レジスタ91aの3ビットのカウント

値 S T A T E を入力する。また、入力信号制御部 9 0 b は、W C N T カウント用レジスタ 9 1 e の 2 ビットのカウント値 W C N T 、 R C N T カウント用レジスタ 9 2 f の 2 ビットのカウント値 R C N T 、ライトイネーブル信号 W E N 、リードイネーブル信号 R E N を入力する。入力信号制御部 9 0 b は、これらの信号をもとに、それぞれ 4 ビットの、ライト用の列選択信号 W S E L \_ C 、行選択信号 W S E L \_ L 、リード用の列選択信号 R S E L \_ C 、行選択信号 R S E L \_ L を生成して出力する。

#### 【手続補正 9】

【補正対象書類名】明細書

【補正対象項目名】0 0 6 9

【補正方法】変更

【補正の内容】

#### 【0 0 6 9】

たとえば、カウント値 S T A T E が“0 0 1”的ときは、ライト用の列選択信号 W S E L \_ C は“1 0 0 0”、行選択信号 W S E L \_ L は、カウント値 W C N T となる。また、リード用の列選択信号 R S E L \_ C は、カウント値 R C N T 、行選択信号 R S E L \_ L “1 1 1 1”となる。

#### 【手続補正 10】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 2

【補正方法】変更

【補正の内容】

#### 【0 0 8 2】

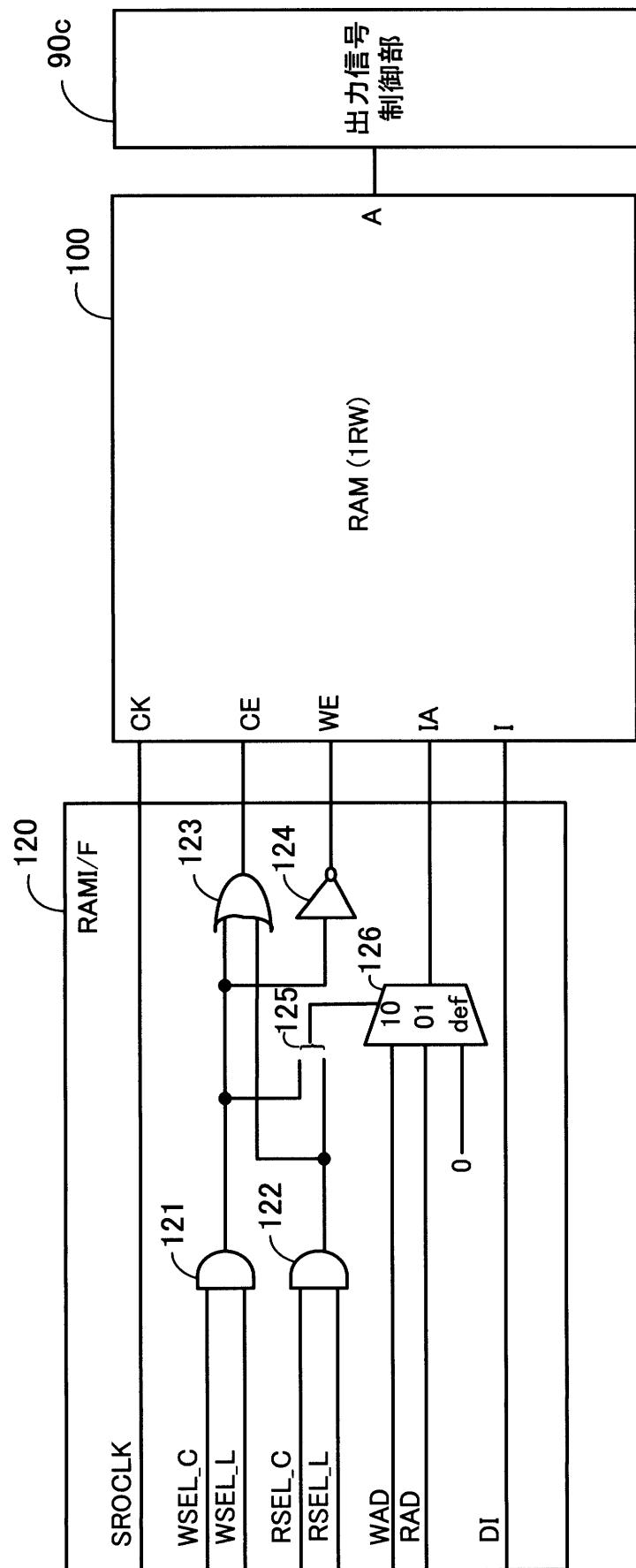

R A M I / F 1 2 0 は、A N D 回路 1 2 1 , 1 2 2 、O R 回路 1 2 3 、インバータ回路 1 2 4 、ビット連結回路 1 2 5 、選択回路 1 2 6 を有している。

A N D 回路 1 2 1 の 2 つの入力端子には、ライト用の列選択信号 W S E L \_ C と行選択信号 W S E L \_ L が入力される。A N D 回路 1 2 2 の 2 つの入力端子には、リード用の列選択信号 R S E L \_ C と行選択信号 R S E L \_ L が入力される。O R 回路 1 2 3 の 2 つの入力端子には、A N D 回路 1 2 1 , 1 2 2 の出力信号が入力され、O R 回路 1 2 3 の出力信号は、R A M 1 0 0 のチップイネーブル端子 C E に入力される。インバータ回路 1 2 4 には、A N D 回路 1 2 1 の出力信号が入力され、インバータ回路 1 2 4 の出力信号は、R A M 1 0 0 のライトイネーブル端子 W E に入力される。

#### 【手続補正 11】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 3

【補正方法】変更

【補正の内容】

#### 【0 0 8 3】

ビット連結回路 1 2 5 は、A N D 回路 1 2 1 , 1 2 2 の出力信号を連結して 2 ビットの選択信号を選択回路 1 2 6 に供給する。選択回路 1 2 6 は、ライトアドレス W A D とリードアドレス R A D と値“0”を入力し、入力される選択信号が“1 0”的ときにはライトアドレス W A D を出力し、選択信号が“0 1”的ときにはリードアドレス R A D を出力する。また、選択回路 1 2 6 は、選択信号が“1 0”, “0 1”以外の値 d e f のときには、“0”を出力する。選択回路 1 2 6 の出力信号は、R A M 1 0 0 のアドレス端子 I A に入力される。その他、R A M 1 0 0 のクロック端子 C K には、図示しないクロック供給部からのクロック S R O C L K が入力され、ライトデータ入力端子 I には、入力データ D I が入力される。また、R A M 1 0 0 のリードデータ出力端子 A から読み出されたリードデータは、出力信号制御部 9 0 c に供給される。

#### 【手続補正 12】

【補正対象書類名】明細書

【補正対象項目名】0 1 1 6

【補正方法】変更

【補正の内容】

【0 1 1 6】

一方、4行目のRAM112～115に対するライトが完了し、次に、タイミングt20において、水平同期信号のパルスが生成されると、9ライン目の画素データが、リードが完了した1列目のRAM100, 104, 108, 112に順にライトされる。つまり、ライトされるRAMの選択方向が、行方向から列方向に変わる。

【手続補正13】

【補正対象書類名】明細書

【補正対象項目名】0 1 2 6

【補正方法】変更

【補正の内容】

【0 1 2 6】

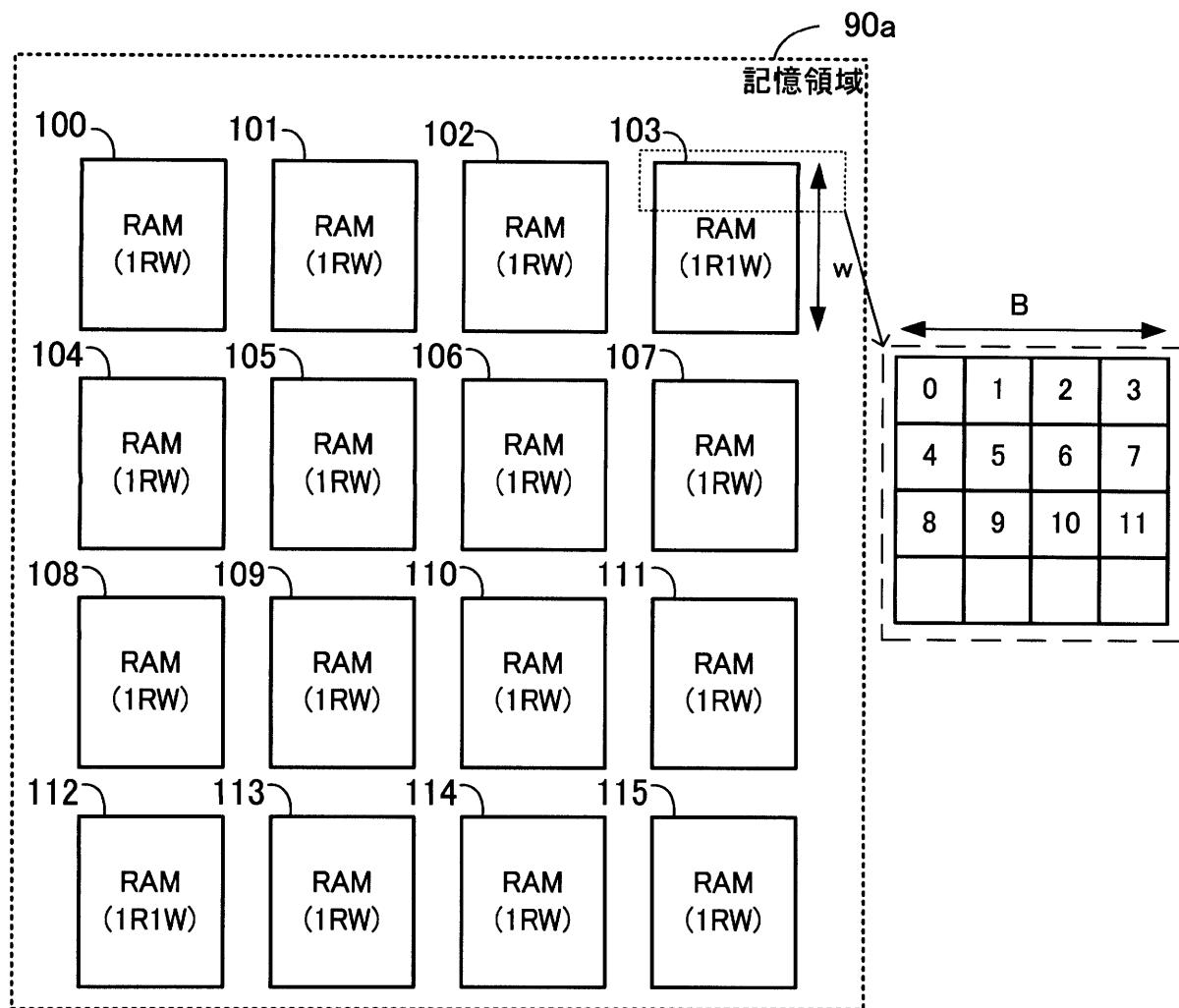

RAMに関してはプロセスによりサイズが異なるが、一例として65nmテクノロジー、水平方向最大サイズ=6784画素、1画素=14ビットとしたとき、1ライン分の1RWの容量は7Mバイトである。たとえば、2並列処理を行う場合に、2ライン分の1RWのRAMを用いると、 $7 \times 2 = 14$ Mバイトの容量となる。4並列処理を行う場合に、データ破壊を回避するために、6ライン分の画素データを保持するように、1RWのRAMを6つ使用すると、 $7 \times 6 = 42$ Mバイトの容量となる。

【手続補正14】

【補正対象書類名】明細書

【補正対象項目名】0 1 2 7

【補正方法】変更

【補正の内容】

【0 1 2 7】

これに対し、本実施の形態の画像データ処理装置70において4並列処理を行う場合、RAM100～115は、それぞれ1/4ライン分の画素データを保持し、容量は1RWのRAMで1.7Mバイト、1RWのRAMで0.9Mバイトとなる。前述したように16個のRAM100～115のうち、RAM103, 112以外は、1RWのRAMを適用できるので、トータルの容量は、 $1.7 \times 2 + 0.9 \times 14 = 16$ Mバイトとなる。このように、1RWのRAMを6つ使用する場合よりも大幅に、RAM容量を削減でき、面積を小さくすることができる。また、2並列処理を行うために、2ライン分の1RWのRAMを使う場合に対しても、4並列処理を行っても、本実施の形態の画像データ処理装置70によれば14%の容量増加に抑えができる。

【手続補正15】

【補正対象書類名】図面

【補正対象項目名】図11

【補正方法】変更

【補正の内容】

【図 1 1】

【手続補正 1 6】

【補正対象書類名】図面

【補正対象項目名】図 1 2

【補正方法】変更

【補正の内容】

【図 12】

【手続補正 17】

【補正対象書類名】図面

【補正対象項目名】図 1 9

【補正方法】変更

【補正の内容】

【図 1 9】