【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成19年5月31日(2007.5.31)

【公開番号】特開2006-24601(P2006-24601A)

【公開日】平成18年1月26日(2006.1.26)

【年通号数】公開・登録公報2006-004

【出願番号】特願2004-198932(P2004-198932)

【国際特許分類】

H 01 L 29/78 (2006.01)

H 01 L 27/06 (2006.01)

H 01 L 29/866 (2006.01)

H 01 L 21/822 (2006.01)

H 01 L 27/04 (2006.01)

【F I】

H 01 L 29/78 3 0 1 K

H 01 L 27/06 3 1 1 B

H 01 L 29/90 D

H 01 L 27/04 H

【手続補正書】

【提出日】平成19年4月9日(2007.4.9)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなるPN接合ダイオードと、

前記ゲート電極及び前記PN接合ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記PN接合ダイオードのN型領域とを接続する第1の金属電極配線と、

前記PN接合ダイオードのP型領域と前記半導体基板に設けられた高濃度のP型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッショント型MOSトランジスタ。

【請求項2】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなる、2つのP型領域の間にN型領域が挟まれた双方向ダイオードと、

前記ゲート電極及び前記双方向ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記双方向ダイオードの一方のP型領域とを接続する第1の金属電極

配線と、

前記双方向ダイオードの他方のP型領域と前記半導体基板に設けられた高濃度のP型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッショーン型MOSトランジスタ。

【請求項3】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなる、2つのN型領域の間にP型領域が挟まれた双方向ダイオードと、

前記ゲート電極及び前記双方向ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記双方向ダイオードの一方のN型領域とを接続する第1の金属電極配線と、

前記双方向ダイオードの他方のN型領域と前記半導体基板に設けられた高濃度のP型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッショーン型MOSトランジスタ。

【請求項4】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなる、3つ以上の奇数のP型領域とそのおのののP型領域の間に挟まれた偶数のN型領域からなる双方向ダイオードと、

前記ゲート電極及び前記双方向ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記双方向ダイオードの一方のP型領域とを接続する第1の金属電極配線と、

前記双方向ダイオードの他方のP型領域と前記半導体基板に設けられた高濃度のP型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッショーン型MOSトランジスタ。

【請求項5】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなる、3つ以上の奇数のN型領域とそのおのののN型領域の間に挟まれた偶数のP型領域からなる双方向ダイオードと、

前記ゲート電極及び前記双方向ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記双方向ダイオードの一方のN型領域とを接続する第1の金属電極配線と、

前記双方向ダイオードの他方のN型領域と前記半導体基板に設けられた高濃度のP型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッショーンMOSトランジスタ。

【請求項6】

P型半導体基板と、

前記半導体基板上に形成されたN型の高濃度ソース・ドレイン領域と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された第1の多結晶シリコンからなるゲート電極と

前記半導体基板上に形成された第2の多結晶シリコンからなるPN接合ダイオードと、

前記ゲート電極及び前記PN接合ダイオードの上に形成された中間絶縁膜と、

前記ゲート電極と前記PN接合ダイオードのP型領域とを接続する第1の金属電極配線と、

前記PN接合ダイオードのN型領域と前記半導体基板に設けられた高濃度のN型領域とを接続する第2の金属電極配線と、

前記金属配線上に形成する窒化膜からなる保護膜とを有する事を特徴とするデプレッション型MOSトランジスタ。

【請求項7】

前記窒化膜からなる保護膜が、前記第2の多結晶シリコン上のみ形成されていない事を特徴とする、請求項1から6記載のデプレッション型MOSトランジスタ。

【手続補正2】

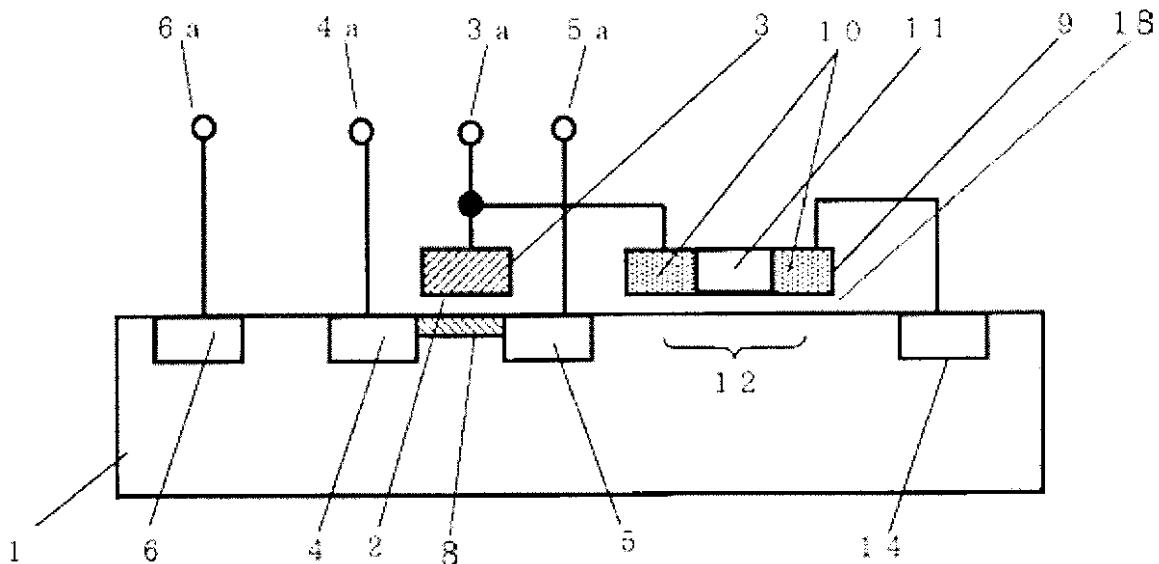

【補正対象書類名】図面

【補正対象項目名】図3

【補正方法】変更

【補正の内容】

【図3】