Brevet N° **87566**

du 2 août 1989

Titre délivré 28 JAN. 1990

GRAND-DUCHÉ DE LUXEMBOURG

Monsieur le Ministre

de l'Économie et des Classes Moyennes

Service de la Propriété Intellectuelle

LUXEMBOURG

## Demande de Brevet d'Invention

(1)

### I. Requête

La société dite: SIEMENS AKTIENGESELLSCHAFT Berlin und (2)

München, Wittelsbacherplatz 2, D-8000 MÜNCHEN

(République Fédérale d'Allemagne) représentée par Monsieur

Jacques de Muyser agissant en qualité de mandataire (3)

dépose(nt) ce deux août 1990 quatre-vingt neuf (4)

à heures, au Ministère de l'Économie et des Classes Moyennes, à Luxembourg:

- la présente requête pour l'obtention d'un brevet d'invention concernant:

"Breitbandsignal-Koppeleinrichtung." (5)

2. la description en langue allemande de l'invention en trois exemplaires;

3. 3 planches de dessin, en trois exemplaires;

4. la quittance des taxes versées au Bureau de l'Enregistrement à Luxembourg, le 2 août 1989 :

5. la délégation de pouvoir, datée de München le 18 juillet 1989 :

6. le document d'ayant cause (autorisation);

déclare(nt) en assumant la responsabilité de cette déclaration, que l'(es) inventeur(s) est (sont): (6)

- Dr. Ruediger Hofmann, Fürstenfelder Weg 12,

D-8031 GILCHING (République Fédérale d'Allemagne)

revendique(nt) pour la susdite demande de brevet la priorité d'une (des) demande(s) de (7)

brevet déposée(s) en (8) République Fédérale d'Allemagne

le (9) 22 mars 1989

sous le N° (10) P3909550.9

au nom de (11) la déposante

élit(é)sent domicile pour lui (elle) et, si désigné, pour son mandataire, à Luxembourg

35 Boulevard Royal (12)

sollicite(nt) la délivrance d'un brevet d'invention pour l'objet décrit et représenté dans les annexes susmentionnées.

avec ajournement de cette délivrance à / mois. (13)

Le déposant / mandataire: (14)

### II. Procès-verbal de Dépôt

La susdite demande de brevet d'invention a été déposée au Ministère de l'Économie et des Classes Moyennes.

Service de la Propriété Intellectuelle à Luxembourg, en date du: 2 août 1989

à 15 heures

Pr. le Ministre de l'Économie et des Classes Moyennes,

p.d.

Le chef du service de la propriété intellectuelle,

A 68007

EXPLICATIONS RELATIVES AU FORMULAIRE DE DÉPÔT

(1) s'il y a lieu "Demande de certificat d'addition au brevet principal, à la demande de brevet principal N° .....". (2) inscrire les nom, prénom, profession, adresse du demandeur. lorsque celui-ci est un particulier ou les dénomination sociale, forme juridique, adresse du siège social, lorsque le demandeur est une personne morale - (3) inscrire les nom, prénom, adresse du mandataire agréé, conseil en propriété industrielle, munie d'un pouvoir spécial, s'il y a lieu: "représente par ..... agissant en qualité de mandataire" - (4) date de dépôt en toutes lettres - (5) titre de l'invention - (6) inscrire les noms, prénoms, adresses des inventeurs ou l'indication " (voir) désignation séparée (suivra)", lorsque la désignation se fait ou se fera dans un document séparé, ou encore l'indication "ne pas mentionner", lorsque l'inventeur signe ou signera un document de non-mention à joindre à une désignation séparée présente ou future - (7) brevet, certificat d'addition, modèle d'utilité, brevet européen (CBE), protection internationale (PCT) - (8) Etat dans lequel le premier dépôt a été effectué ou, le cas échéant, Etats désignés dans la demande européenne ou internationale prioritaire - (9) date du premier dépôt - (10) numéro du premier dépôt complet, le cas échéant, par l'indication de l'office récepteur CBE/PCT - (11) nom du titulaire du premier dépôt - (12) adresse du domicile effectif ou élu au Grand-Duché de Luxembourg - (13) 2, 6, 12 ou 18 mois - (14) signature du demandeur ou du mandataire agréé.

**BEANSPRUCHUNG DER PRIORITY**

der Patent/Gbm. --Anmeldung

In: der BUNDESREPUBLIK DEUTSCHLAND

Vom: 22. März 1989 (Nr. P3909550.9)

**PATENTANMELDUNG**

in

**Luxemburg**

Anmelder : SIEMENS AKTIENGESELLSCHAFT Berlin und München

8000 München (Bundesrepublik Deutschland)

Betr. : "Breitbandsignal-Koppeleinrichtung"

1 Siemens Aktiengesellschaft

Breitbandsignal-Koppeleinrichtung

- 5 Läßt sich die ECL-Technik durch Eigenschaften wie hohe Arbeitsgeschwindigkeit, (mittel-)hoher Integrationsgrad und (mittel-) hohe Verlustleistung charakterisieren, so zeichnet sich die FET-Technik - bei demgegenüber allerdings nur mittleren Arbeitsgeschwindigkeiten - durch einen sehr hohen Integrationsgrad und

- 10 sehr niedrige Verlustleistungen aus. Diese letzteren Eigenschaften führen zu dem Bemühen, mit integrierten Schaltungen in FET-Technik auch in bislang der Bipolar-Technik vorbehaltene Geschwindigkeitsbereiche vorzudringen.

- 15 Für eine Breitbandsignal-Koppeleinrichtung mit einer Koppelpunktmatrix, die jeweils mit zwei Signalleitern gebildete Matrixeingangsleitungen aufweist, welche einerseits jeweils an zwei Differenz-(Komplementär-)ausgänge einer Eingangsdigitalsignalschaltung angeschlossen sind und andererseits über Koppelpunkte

- 20 mit ebenfalls jeweils mit zwei Signalleitern gebildeten Matrixausgangsleitungen verbindbar sind, welche jeweils mit ihren beiden Signalleitern zu den beiden Signaleingängen einer mit einem Differenzverstärker gebildeten Ausgangsverstärkerschaltung führen, ist in diesem Zusammenhang (aus EP-A-0 264 046) eine in

- 25 FET-Technik ausgebildete Koppelpunktmatrix mit in den Koppelpunkten vorgesehenen, jeweils mit zwei jeweils an der Steuerelektrode mit einem Durchschalte-bzw. Sperrsignal beaufschlagten Schalter-Transistoren gebildeten Koppelementpaaren bekannt, deren Schalter-Transistoren jeweils mit einer Hauptelektrode an

- 30 den einen bzw. anderen Signalleiter der zugehörigen Matrixausgangsleitung angeschlossen sind, die ihrerseits mit einem Ausgangs-Differenzverstärker mit Kippverhalten versehen ist, wobei die Koppelementpaare jeweils zwei jeweils mit einem Schalter-Transistor eine Serienschaltung bildende Vorschalt-Transistoren

- 35 aufweisen,

- die jeweils mit der Steuerelektrode an den einen bzw. den anderen Signalleiter der zugehörigen Matrixeingangsleitung angeschlossen sind und deren jeweilige der Serienschaltung abge-

- 2 -

- 1 wandte Hauptelektrode über einen Abtast-Transistor mit dem einen

Anschluß (Masse) der Betriebsspannungsquelle verbunden ist, mit

deren anderen Anschluß jeder Signalleiter der jeweiligen Matrix-

ausgangsleitung jeweils über einen Vorlade-Transistor verbunden

5 ist,

und wobei Vorlade-Transistoren und Abtast-Transistor gegensinnig

zueinander jeweils an ihrer Steuerelektrode mit einem eine Bit-

Durchschaltezeitspanne in eine Vorladephase und die eigentliche

Durchschaltephase unterteilenden Koppelfeld-Ansteuer-Takt beauf-

10 schlagt sind, so daß in jeder Vorphase bei gesperrtem Abtast-

Transistor beide Signalleiter der Matrixausgangsleitung über den

jeweiligen Vorlade-Transistor zumindest angenähert auf das an

dem genannten anderen Anschluß der Betriebsspannungsquelle

herrschende Potential geladen werden.

15 Diese bekannte Breitbandsignal-Koppeleinrichtung bringt zusätz-

lich zu den Vorteilen, die mit einer in FET-Technik gehaltenen

Koppelpunktmatrix verbunden sind, den weiteren Vorteil mit sich,

daß einerseits - bei gesperrtem Koppelpunkt - auch ohne zusätz-

liche Dämpfungsmaßnahmen keine störende Signale über den Koppel-

20 punkt zum Matrixausgang gelangen und daß andererseits - bei lei-

tendem Koppelpunkt - bei der eigentlichen Bitdurchschaltung ggf.

stattfindende Umladungen der Matrixausgangsleitung stets von dem

dem einen Signalzustand entsprechenden einen Betriebspotential

ausgehend in nur einer Umladerichtung vor sich gehen und somit

25 bereits mit einer (dem Überschreiten einer diesem Betriebspoten-

tialwert benachbarten, dem Kippunkt des Differenzverstärkers

entsprechenden Schwelle entsprechenden) kleinen Umladung - und

damit entsprechend schnell - ein eindeutiger Übergang des am

Ausgang der Koppeleinrichtung auftretenden, durchgeschalteten

30 Digitalsignals von dem einen in den anderen Signalzustand ver-

bunden ist.

Bei einer solchen Breitbandsignal-Koppeleinrichtung kann eine

weitere Erhöhung der Arbeitsgeschwindigkeit dadurch ermöglicht

35 werden, daß die beiden Vorlade-Transistoren an ihren der jewei-

lichen Matrixausgangsleitung zugewandten Hauptelektroden mitein-

ander über einen Quertransistor verbunden sind, dessen Steuer-

elektrode mit den Steuerelektroden der Vorlade-Transistoren ver-

- 3 -

1 bunden ist (DE-P 3819491.0); dies bringt in Verbindung mit dem

Vorteil einer Beschleunigung der Vorladung der Matrixausgangs-

leitungen den weiteren Vorteil einer sehr frühzeitigen Potential-

symmetrierung der Matrixausgangsleitungen mit sich, so daß auch

5 entsprechend frühzeitig die Anfangsbedingungen für eine sichere

Verstärkung durch einen nachfolgenden Differenzverstärker gege-

ben sind.

10 Eine weitere Erhöhung der Arbeitsgeschwindigkeit der Breitband-

signal-Koppeleinrichtung erhält man, wenn neben einem matrixein-

gangsleitungs-individuellen Abtast-Transistor ein matrixeingangs-

leitungs-individueller Vorlade-Transistor oder, alternativ dazu,

neben einem matrixausgangsleitungs-individuellen Abtast-Transi-

stор ein matrixausgangsleitungs-individueller Vorlade-Tran-

sistor vorgesehen ist (DE-P 3819491.0).

15 Die hinsichtlich Verlustleistungsbedarf und Arbeitsgeschwindig-

keit erreichbaren Vorteile einer solchen bekannten Breitband-

Koppeleinrichtung, die jeweils mit zwei Signalleitern gebildete

20 Matrixeingangsleitungen aufweist, sind mit einem entsprechenden

Platzbedarf für solche jeweils zwei Signalleiter der Matrixein-

gangsleitungen verbunden. Die Erfindung zeigt demgegenüber einen

Weg, diesen Platzbedarf merklich zu verringern.

25 Die Erfindung betrifft eine Breitbandsignal-Koppeleinrichtung

mit einer Koppelpunktmatrix in FET-Technik, deren Matrixeingangs-

leitungen über jeweils mit Koppelementpaaren gebildete Koppel-

punkte mit jeweils mit zwei Signalleitern gebildeten Matrixaus-

gangsleitungen verbindbar sind, an deren beiden Signalleiter

30 jeweils die beiden Signaleingänge einer mit einem Differenzver-

stärker mit Kippverhalten gebildeten Ausgangsverstärkerschaltung

anschließbar sind,

wobei die Koppelementpaare jeweils mit zwei jeweils an der

35 Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal beauf-

schlagten und mit einer Hauptelektrode an den einen bzw. anderen

Signalleiter der zugehörigen Matrixausgangsleitung angeschlos-

senen Schalter-Transistoren und zwei jeweils mit einem Schalter-

Transistor eine Serienschaltung bildenden Vorschalt-Transistor

- 1 gebildet sind,

die jeweils mit der Steuerelektrode an einen Signalleiter der

zugehörigen Matrixeingangsleitung angeschlossen sind und deren

jeweilige der Serienschaltung abgewandte Hauptelektrode über

5 einen koppelement-, matrixeingangsleitungs- oder matrixaus-

gangsleitungs-individuellen Abtast-Transistor mit dem einen

Anschluß der Betriebsspannungsquelle verbunden ist, mit deren

anderen Anschluß jeder Signalleiter der jeweiligen Matrixaus-

gangsleitung jeweils über einen Vorlade-Transistor verbunden

10 ist,

wobei Vorlade-Transistoren und Abtast-Transistor gegensinnig

zueinander jeweils an ihrer Steuerelektrode mit einem eine Bit-

Durchschaltezeitspanne in eine Vorladephase und die eigentliche

Durchschaltephase unterteilenden Koppelfeld-Ansteuer-Takt beauf-

15 schlagt sind, so daß in jeder Vorphase bei gesperrtem Abtast-

Transistor beide Signalleiter der Matrixausgangsleitung über

den jeweiligen Vorlade-Transistor zumindest angenähert auf das

an dem genannten anderen Anschluss der Betriebsspannungsquelle

herrschende Potential geladen werden,

20 und wobei die beiden Vorlade-Transistoren an ihren der jeweiligen

Matrixausgangsleitung zugewandten Hauptelektroden miteinander

Über einen Quertransistor verbunden sind, dessen Steuerelektrode

mit den Steuerelektroden der Vorlade-Transistoren verbunden ist;

diese Breitbandsignal-Koppeleinrichtung ist erfindungsgemäß da-

25 durch gekennzeichnet, daß die Koppelementpaare jeweils zwei

Vorschalt-Transistoren unterschiedlichen Kanaltyps aufweisen,

die mit ihrer Steuerelektrode an ein und denselben Signalleiter

der zugehörigen Matrixeingangsleitung angeschlossen sind.

30 Die Erfindung bringt den Vorteil mit sich, je Matrixeingangs-

leitung nur einen einzigen Signalleiter - mit entsprechend ver-

ringertem Platzbedarf - zu benötigen, zugleich aber die sonstigen

Besonderheiten und vorteilhaften Eigenschaften der eingangs

erwähnten bekannten Breitband-Koppeleinrichtung beizubehalten.

35 Eine noch deutlichere Verringerung des Flächenbedarfs erzielt

man, wenn in weiterer Ausgestaltung der Erfindung die Koppel-

elementpaare jeweils zwei Schalter-Transistoren unterschied-

- 5 -

1 lichen Kanaltyps aufweisen, die jeweils mit einem Vorschalt-

Transistor desselben Kanaltyps eine Serienschaltung bilden.

5 Um dabei eine unsymmetrische Belastung der beiden Signalleiter

der Matrixausgangsleitungen und damit auch eine unsymmetrische

Belastung der beiden Eingänge eines nachfolgenden Differenzver-

stärkers zu vermeiden, kann die Breitbandsignal-Koppeleinrich-

tung gemäß der Erfindung weiterhin dahingehend ausgestaltet

sein, daß nur bei einem Teil der zu ein und derselben Matrixaus-

10 gangsleitung führenden Koppelementpaare jeweils die Transistor-

Serienschaltung des einen Kanaltyps mit dem einen Signalleiter

und die Transistor-Serienschaltung des anderen Kanaltyps mit dem

anderen Signalleiter der Matrixausgangsleitung verbunden ist,

während bei dem anderen Teil der zu der betreffenden Matrixaus-

15 gangsleitung führenden Koppelementpaare jeweils die Transistor-

Serienschaltung des genannten anderen Kanaltyps mit dem genannten

einen Signalleiter und die Transistor-Serienschaltung des ge-

nannten einen Kanaltyps mit dem genannten anderen Signalleiter

der Matrixausgangsleitung verbunden ist; dies kann insbesondere

20 in der Weise geschehen, daß in der einen bzw. in der anderen

Weise mit den Signalleitern der zugehörigen Matrixausgangsleitung

verbundene Koppelementpaare in der betreffenden Matrixreihe

abwechselnd aufeinanderfolgen.

25 Weitere Besonderheiten der Erfindung werden aus der nachfolgenden

näheren Erläuterung der Erfindung anhand der Zeichnung ersicht-

lich. Dabei zeigt

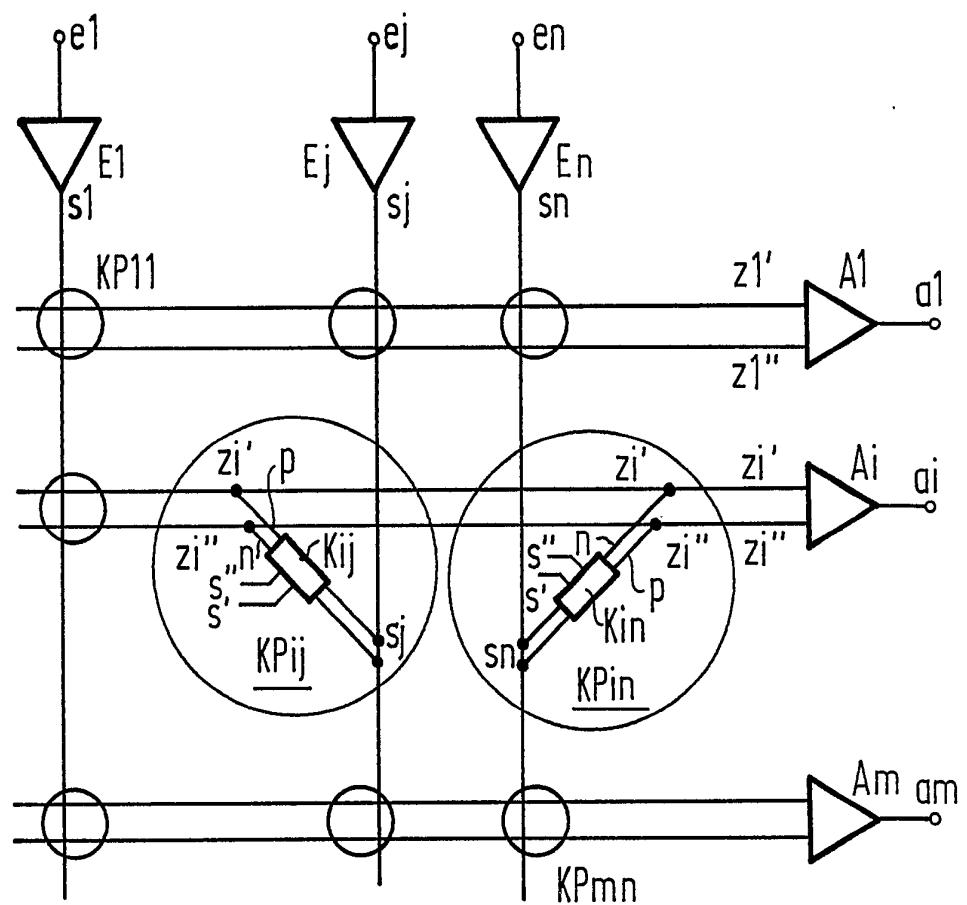

30 FIG 1 das Schema einer Breitbandsignal-Koppeleinrichtung gemäß

der Erfindung;

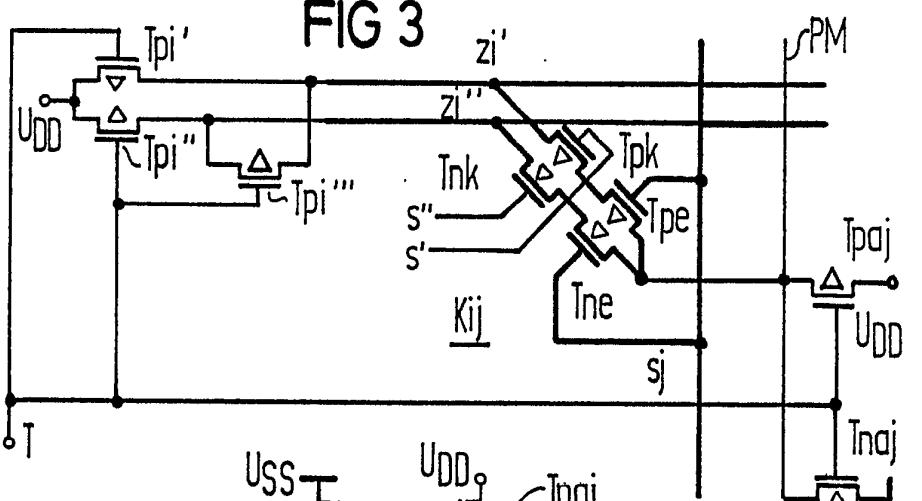

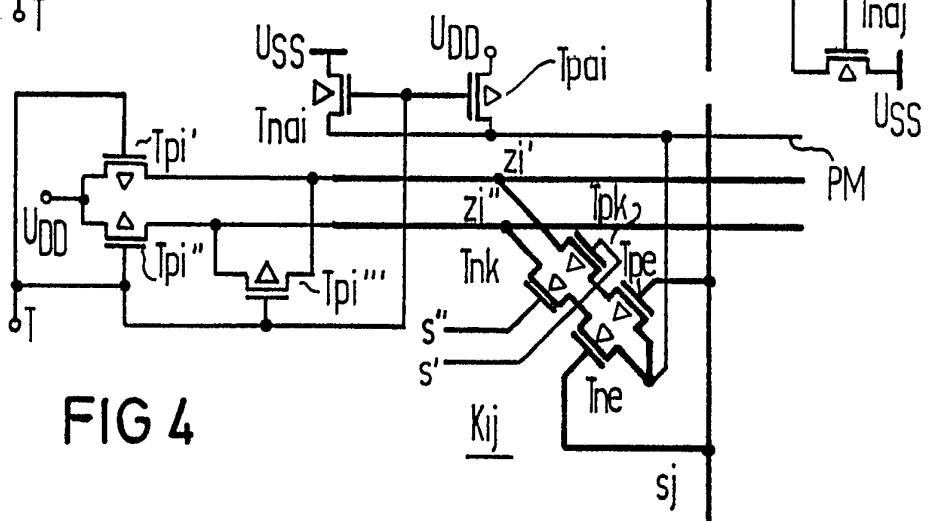

FIG 2, FIG 3 und FIG 4 zeigen Beispiele der schaltungstechnischen

Realisierung ihrer Koppelemente, und

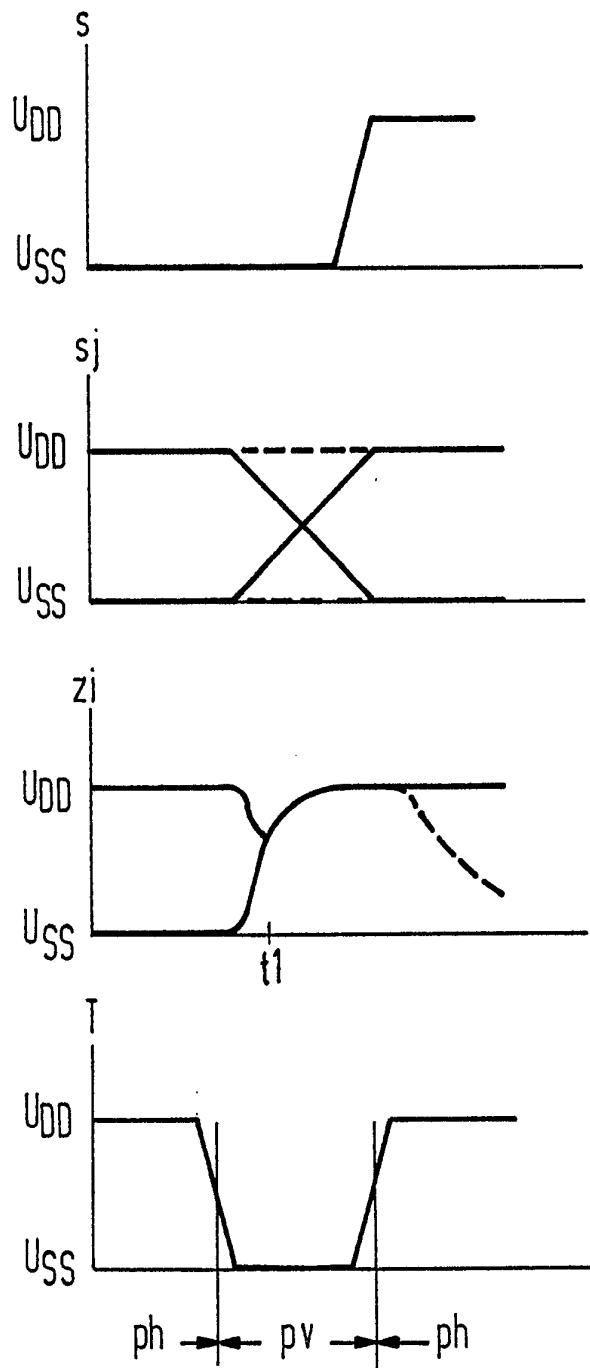

FIG 5 verdeutlicht Signalverläufe darin.

35 In der Zeichnung FIG 1 ist schematisch in zum Verständnis der

Erfindung erforderlichem Umfange eine Breitbandsignal-Koppelein-

richtung skizziert, an deren zu Spaltenleitungen s1...sj...sn

einer Koppelpunktmatrix führenden Eingängen e1...ej...en Ein-

- 6 -

- 1 gangsdigitalsignalen E1...Ej...En vorgesehen sind und

deren von Zeilenleitungen z1...zi...zm der Koppelpunktmatrix

erreichte Ausgänge a1...ai...am mit Ausgangsverstärkerschaltun-

gen A1...Ai...Am versehen sind. Die Koppelpunktmatrix weist

5 Koppelpunkte KP11...KPij...KPmn auf, deren Koppelemente, wie

dies beim Koppelpunkt KPij für ein Koppelementepaar Kij weiter

ins Einzelne gehend angedeutet ist, jeweils an Steuereingängen

s', s" von einem (in der Zeichnung nicht mehr dargestellten)

Adressendecoderelement oder Halte-Speicherelement gesteuert sein

10 können, was hier indessen nicht weiter erläutert werden muss, da

derartige Ansteuerungen von Koppelementen allgemein bekannt

sind und entsprechende Erläuterungen sich im Übrigen auch schon

an anderer Stelle finden (EP-A1-0 262 479).

- 15 Die jeweils mit nur einem Signalleiter gebildeten Matrixeingangs-

leitungen (Spaltenleitungen) sind über mit Koppelementepaaren

(Kij beim Koppelpunkt KPij in FIG 1) gebildete Koppelpunkte

KP11,...,KPij,...,KPnm mit Matrixausgangsleitungen (Zeilenlei-

tungen) verbunden, die jeweils mit zwei Signalleitern z1',z1";

20 ...;zi',zi"; ...;zm',zm" gebildet sind und mit diesen jeweils zu

den beiden Signaleingängen einer mit einem Differenzverstärker

mit Kippverhalten gebildeten Ausgangsverstärkerschaltung A1,..,

Ai,...,Am führen.

- 25 Ein solcher Differenzverstärker mit Kippverhalten kann mit einem

sog. gated flip-flop realisiert werden, wie es im Prinzip (aus

|a| IEEE Journal of Solid-State Circuits, Oct. 1973, 319...323,

Fig.6) und auch schon in verschiedenen Modifikationen (beispiels-

weise aus |b| DE-OS 24 22 136, Fig.3 (16') und aus |c|

30 DE-OS 26 08 119, FIG.5) bekannt ist, wobei ein dort vorgesehener

Symmetriertransistor (in |a| und |b|) ebenso wie dort vorgesehene

Vorladetransistoren (in |b|) bzw. Lasttransistoren (in |c|) zweck-

mäßigerweise als p-Kanal-Transistor auszubilden ist; eine weitere

Realisierungsmöglichkeit ist aus EP-A-0 264 046, FIG 5, bekannt.

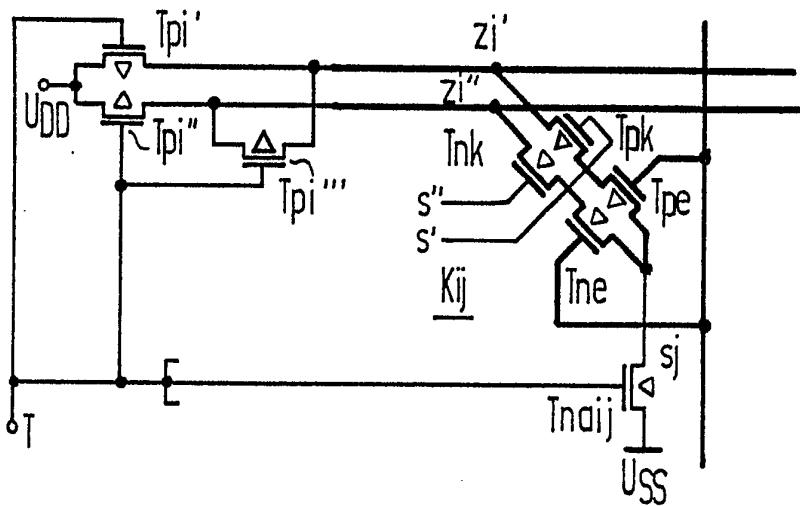

- 35 Wie die Koppelementepaare ...Kij... schaltungstechnisch reali-

siert sein können, wird in FIG 2, FIG 3 und FIG 4 verdeutlicht:

Die Koppelementepaare ... Kij... sind jeweils mit zwei jeweils

- 7 -

1 an der Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal

beaufschlagten und mit einer Hauptelektrode an den einen bzw.

den anderen Signalleiter  $z_i', z_i''$  der zugehörigen Matrixausgangs-

leitung angeschlossenen Schalter-Transistoren  $T_{pk}$ ,  $T_{nk}$  und zwei

5 jeweils mit einem Schalter-Transistor  $T_{pk}$  bzw.  $T_{nk}$  eine Serien-

schaltung bildenden Vorschalt-Transistoren  $T_{pe}$  und  $T_{ne}$  unter-

schiedlichen Kanaltyps gebildet, die jeweils mit der Steuer-

elektrode an den (einzig) Signalleiter  $s_j$  der zugehörigen

Matrixeingangsleitung (Spaltenleitung) ...  $s_j...$  angeschlossen

10 sind; sind dabei, wie dies aus FIG 2, FIG 3 und FIG 4 ersicht-

lich ist, auch die beiden Schalter-Transistoren  $T_{pk}$ ,  $T_{nk}$  von

unterschiedlichem Kanaltyp, so bilden jeweils ein Schalter-Transi-

stör  $T_{pk}$  (bzw.  $T_{nk}$ ) und ein Vorschalt-Transistor  $T_{pe}$  (bzw.  $T_{ne}$ )

dieselben Kanaltyps eine Serienschaltung. Mit ihrer der Serien-

15 schaltung abgewandten Hauptelektrode sind die Vorschalt-Transi-

storen  $T_{pe}$  und  $T_{ne}$  über einen Abtast-Transistor  $T_{na}$  (nämlich

$T_{naij}$  in FIG 2 bzw.  $T_{naj}$  in FIG 3 bzw.  $T_{nai}$  in FIG 4) mit dem

einen Anschluß  $U_{SS}$  (Masse) der Betriebsspannungsquelle verbunden.

Mit dem anderen Anschluß  $U_{DD}$  der Betriebsspannungsquelle sind

20 die beiden Signalleiter ( $z_i', z_i''$ ) der jeweiligen Matrixausgangs-

leitung (Zeilenleitung) ...  $z_i...$  jeweils über einen Vorlade-

Transistor  $T_{pi'}$  bzw.  $T_{pi''}$  verbunden; an ihren der jeweiligen

Matrixausgangsleitung ( $z_i', z_i''$ ) zugewandten Hauptelektroden

sind die beiden Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$  miteinander über

25 einen Quertransistor  $T_{pi'''}$  verbunden, dessen Steuerelektrode

mit den Steuerelektroden der Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$

verbunden ist.

Wie dies auch FIG 2 verdeutlicht, kann jeweils ein Koppelemente-

30 paar-individueller Abtast-Transistor  $T_{naij}$  vorgesehen sein;

alternativ kann aber auch, wie dies FIG 3 zeigt, jeweils für

alle an ein und derselben Matrixeingangsleitung (Spaltenleitung)

..  $s_j...$  liegenden Koppelementepaare ein gemeinsamer und damit

matrixeingangsleitungs-individueller Abtast-Transistor ( $T_{naj}$  in

35 FIG 3) vorgesehen sein, oder es kann, wie die aus FIG 4 ersicht-

lich ist, jeweils ein allen an ein und derselben Matrixausgangs-

leitung (Zeilenleitung) ...  $z_i...$  liegenden Koppelementepaaren

gemeinsamer und damit matrixausgangsleitungs-individueller Ab-

- 8 -

- 1 tast-Transistor (Tnai in FIG 4) vorgesehen sein. Dabei kann, wie dies aus FIG 3 ersichtlich wird, neben einem matrixeingangsleitungs-individuellen Abtast-Transistor Tnaj ein matrixeingangsleitungs-individueller Vorlade-Transistor Tpaj vorgesehen sein, und

- 5 es kann, wie dies aus FIG 4 ersichtlich wird, neben einem matrixausgangsleitungs-individuellen Abtast-Transistor Tnai ein matrixausgangsleitungs-individueller Vorlade-Transistor Tpai vorgesehen sein.

- 10 Wie dies auch in FIG 2 bis FIG 4 angedeutet ist, können in der in CMOS-Technik gehaltenen Koppelpunktmatrix jeweils der Schalter-Transistor Tnk und der Vorschalt-Transistor Tne der einen Serienschaltung Tne-Tnk ebenso wie der zugehörige Abtast-Transistor Tna n-Kanal-Transistoren sein, während der Schalter-Transistor Tpk und der Vorschalt-Transistor Tpe der anderen Serienschaltung Tpe-Tpk ebenso wie die Vorlade-Transistoren Tpi p-Kanal-Transistoren sind.

Da p-Kanal-Transistoren (bei gleicher Stromausbeute) doppelt so breit ausgelegt sein müssen wie n-Kanal-Transistoren, ist es - zur Vermeidung hieraus resultierender unsymmetrischer Belastungen der beiden Signalleiter  $z_i'$ ,  $z_i''$  einer Matrixausgangsleitung - bei der aus FIG 2 bis FIG 4 ersichtlichen Realisierung der Koppellementepaare mit jeweils zwei Transistor-Serienschaltungen unterschiedlichen Kanaltyps zweckmäßig, daß nur bei einem Teil der zu ein und derselben Matrixausgangsleitung führenden Koppellementepaare die Transistor-Serienschaltung (Tpe, Tpk) des einen Kanaltyps mit dem einen Signalleiter ( $z_i'$ ) und die Transistor-Serienschaltung (Tne, Tnk) des anderen Kanaltyps mit dem anderen Signalleiter ( $z_i''$ ) der Matrixausgangsleitung verbunden ist, während bei dem anderen Teil der zu der betreffenden Matrixausgangsleitung führenden Koppelementepaare die Transistor-Serienschaltung (Tne, Tnk) des genannten anderen Kanaltyps mit dem genannten einen Signalleiter ( $z_i'$ ) und die Transistor-Serienschaltung (Tpe, Tpk) des genannten einen Kanaltyps mit dem genannten anderen Signalleiter ( $z_i''$ ) der Matrixausgangsleitung verbunden ist; insbesondere können dabei in der einen bzw. in der anderen Weise mit den Signalleitern der zugehörigen Matrix-

- 9 -

1 ausgangsleitung verbundene Koppelementepaare in der betreffenden Matrixreihe abwechselnd aufeinanderfolgen.

5 Solche abwechselnd aufeinanderfolgende Koppelemente sind auch

in FIG 1 angedeutet: Beim Koppelpunkt KPij ist der Ausgang p der

p-Kanal-Transistor-Serienschaltung (Tpe-Tpk in FIG 2) an den

einen Signalleiter zi' der zugehörigen Matrixausgangsleitung an-

geschlossen und der Ausgang n der n-Kanal-Transistor-Serienschal-

tung (Tne-Tnk in FIG 2) an den anderen Signalleiter zi". In FIG

10 1 ist dann angedeutet, daß in entsprechender Weise auch die

Übrigen an der Matrixeingangsleitung sj liegenden Koppelpunkte

an die Übrigen Matrixausgangsleitungen angeschlossen sind. Zu-

gleich ist in FIG 1 angedeutet, daß bei den an der Matrixein-

gangsleitung sn liegenden Koppelpunkten die Koppelement-Aus-

15 gänge in umgekehrtem Sinne an die beiden Signalleiter der jewei-

ligen Matrixausgangsleitung angeschlossen sind: Wie dies in FIG 1

für den Koppelpunkt KPin genauer dargestellt ist, ist in dieser

Matrixspalte jeweils der Ausgang n (siehe auch FIG 2) der n-Kanal-

Transistor-Serienschaltung des jeweiligen Koppelementepaars

20 (z.B. Kin) mit dem einen Signalleiter (zi' in FIG 1) verbunden,

während der Ausgang p (siehe auch FIG 2) der p-Kanal-Transistor-

Serienschaltung des jeweiligen Koppelementepaars (z.B. Kin)

mit dem anderen Signalleiter (zm" in FIG 1) der jeweiligen Matrix-

ausgangsleitung verbunden ist. In entsprechender Weise können

25 die Koppelemente aller von unterschiedlichen Matrixeingangslei-

tungen sl...sn (in FIG 1) zu ein und derselben Matrixausgangslei-

tung (z.B. zi', zi") führenden Koppelpunkte mit ihrem n-Kanal-

Zweig von Matrixspalte zu Matrixspalte abwechselnd an den einen

Signalleiter (zi') und den anderen Signalleiter (zi") der betref-

30 fenden Matrixausgangsleitung und mit ihrem p-Kanal-Zweig abwech-

selnd an diesen anderen Signalleiter (zi") und den zuvor genann-

ten einen Signalleiter (zi') der betreffenden Matrixausgangslei-

tung angeschlossen sein.

35 In FIG 2 bis FIG 4 ist noch angedeutet, daß die Vorlade-Tran-

sistoren Tpi und die Abtast-Transistoren Tna gegensinnig zuein-

ander jeweils an ihrer Steuerelektrode mit einem eine Bit-Durch-

schaltezeitspanne in in FIG 5, unten, angedeuteter Weise in eine

- 10 -

- 1 Vorphase  $p_v$  und eine Hauptphase  $p_h$  unterteilenden Takt  $T$  beaufschlagt sind, wie er in FIG 5 in Zeile  $T$  angedeutet ist.

5 Während der Vorphase  $p_v$  (siehe FIG 5, unten) werden jeweils die beiden Signalleiter ( $z_i'$ ,  $z_i''$ ) der Matrixausgangsleitungen (Zeilenleitungen) ... $z_i...$  über den jeweiligen Vorlade-Transistor ( $T_{pi}'$  bzw.  $T_{pi}''$  in FIG 2 bis FIG 4) zumindest angenähert auf das  $U_{DD}$ -Betriebspotential geladen, wozu die im Beispiel durch p-Kanal-Transistoren gebildeten Vorlade-Transistoren  $T_{pi}'$ ,  $T_{pi}''$  im Beispiel durch ein "Low"-Taktsignal  $T$  (siehe FIG 5, Zeile  $T$ ) leitend gemacht werden.

10 Dabei wird mit der fallenden Flanke des Taktsignals  $T$  zugleich auch der zwischen den beiden Signalleitern  $z_i'$ ,  $z_i''$  liegende Quertransistor  $T_{pi}'''$  leitend mit der Folge eines Kurzschlusses der beiden Signalleiter  $z_i'$ ,  $z_i''$ , aufgrund dessen es zu Beginn der Vorphase sehr schnell (Zeitpunkt  $t_1$  in FIG 5, Zeile  $z_i$ ) zunächst einmal zu einem Potentialausgleich der beiden Signalleiter  $z_i'$ ,  $z_i''$  kommt; danach werden dann beide (nun potentialmäßig ausgeglichenen) Signalleiter  $z_i'$ ,  $z_i''$  über die beiden Vorlade-Transistoren  $T_{pi}'$ ,  $T_{pi}''$  auf das  $U_{DD}$ -Betriebspotential hin geladen, wobei sich die Ladedauer insgesamt dadurch verkürzt, daß nach dem durch den Quertransistor  $T_{pi}'''$  herbeigeführten Potentialausgleich nun beide Vorlade-Transistoren  $T_{pi}'$ ,  $T_{pi}''$  in den Aufladungsvorgang einbezogen sind.

15 25 Zugleich mit der Entriegelung der Vorlade-Transistoren  $T_{pi}'$ ,  $T_{pi}''$  und des Quertransistors  $T_{pi}'''$  werden die durch n-Kanal-Transistoren gebildeten Abtast-Transistoren  $T_{na}$  ( $T_{naj}$  in FIG 2,  $T_{naj}$  in FIG 3,  $T_{nai}$  in FIG 4) im Beispiel durch das gleiche "Low"-Taktsignal  $T$  im entgegengesetzten Sinne ausgesteuert, d.h. gesperrt, so daß die Aufladung der jeweils beiden Signalleiter ( $z_i'$ ,  $z_i''$ ) der Matrixausgangsleitungen (Zeilenleitungen) ... $z_i...$  unabhängig von der Ansteuerung der jeweiligen Schalter-Transistoren  $T_{pk}$ ,  $T_{nk}$  (in FIG 2 bis FIG 4) und der jeweiligen Vorschalt-Transistoren  $T_{pe}$ ,  $T_{ne}$  (in FIG 2 bis FIG 4) der einzelnen Koppel-30 elementepaare ... $K_{ij}...$  vor sich gehen kann. Auf der jeweiligen Matrixeingangsleitung (Spaltenleitung) ... $s_j...$  kann sich dabei ggf. schon das dem jeweils durchzuschaltenden Bit entsprechende Potential aufbauen (bzw. beibehalten werden), wie dies Zeile  $s_j$

1 in FIG 5 verdeutlicht.

Ist neben einem matrixeingangsleitungs-individuellen Abtast-Transistor Tnaj ein matrixeingangsleitungs-individueller Vorlade-Transistor Tpaj vorgesehen, wie dies in FIG 3 dargestellt ist, 5 oder ist neben einem matrixausgangsleitungs-individuellen Abtast-Transistor Tnai ein matrixausgangsleitungs-individueller Vorlade-Transistor Tpai vorgesehen, wie dies in FIG 4 dargestellt ist, so wird während der Vorphase  $p_V$  über diesen Vorlade-Transistor (Tpaj in FIG 3; Tpai in FIG 4) die Pseudo-Masseleitung PM 10 aufgeladen, womit das jeweilige Koppelementepaar ...Kij... insoweit entlastet wird. Dies führt insbesondere bei umfangreichen Koppelpunktmatrizen mit einer Vielzahl von an die Pseudo-Masseleitung PM angeschlossenen Koppelementepaaren ...Kij... zu einer merklichen Ladezeitverkürzung, die ihrerseits voll in 15 eine entsprechende Erhöhung der Arbeitsgeschwindigkeit eingeht.

Aufgrund der durch den Quertransistor  $T_{pi}'''$  herbeigeführten 20 Potentialgleichheit der beiden Signalleiter  $z_i'$ ,  $z_i''$  sind die Anfangsbedingungen für eine sichere Verstärkung durch den Differenzverstärker  $A_i$  (in FIG 1) entsprechend früher gegeben, so daß bereits zu einem entsprechend früheren Zeitpunkt die darauf-folgende Hauptphase  $p_H$  (siehe FIG 5, unten) einsetzen kann. In dieser Hauptphase  $p_H$  (siehe FIG 5, unten), werden im Beispiel durch ein "High"-Taktsignal  $T$  (siehe FIG 5 Zeile  $T$ ) Vorlade-Transistoren  $T_{pi}', T_{pi}''$  und Quertransistor  $T_{pi}'''$  (in FIG 2 bis FIG 4) gesperrt und zugleich die Abtast-Transistoren  $T_{na}$  ( $T_{naij}$  in FIG 2,  $T_{naj}$  in FIG 3,  $T_{nai}$  in FIG 4) entriegelt. Sind nun in einem 25 Koppelementepaar ...Kij... dessen Schalt-Transistoren  $T_{pk}, T_{nk}$  (in FIG 2 bis FIG 4) aufgrund eines am Steuereingang  $s'$  anliegenden (im Beispiel "Low"-)Durchschaltesignals und eines am Steuereingang  $s''$  anliegenden (im Beispiel "High"-)Durchschaltesignals (siehe FIG 5, Zeile  $s$ ) leitend und befindet sich damit der Koppelpunkt im Durchschaltezustand, so werden jetzt je nach dem dem durchzuschaltenden Bit entsprechenden, auf der betreffenden Matrixeingangsleitung (Spaltenleitung) ... $s_j$ ... herrschenden Signalzustand die Signalleiter  $z_i', z_i''$  der mit dieser Matrixeingangsleitung (Spaltenleitung) ... $s_j$ ... über das betreffende Koppelement ..Kij.. verbundene Matrixausgangsleitung (Zeilen-

- 12 -

1 leitung) ...zi... entladen werden bzw. auf dem in der Vorphase

5 pv angenommenen  $U_{DD}$ -Potential verbleiben:

5 Herrscht auf der betreffenden Matrixeingangsleitung (Spaltenlei-

10 tung) sj der "Low"-Signalzustand und ist dementsprechend der

n-Kanal-Vorschalt-Transistor Tne (in FIG 2 bis FIG 4) des betref-

fenden Koppelementepaars Kij gesperrt, so wird der betreffende

15 Signalleiter zi" der Matrixausgangsleitung (Zeilenleitung) zi

über das betreffende Koppelement dieses Koppelementepaars

20 Kij nicht entladen, sondern behält, sofern kein anderer zu dieser

Matrixausgangsleitung (Zeilenleitung) zi führender Koppelpunkt

sich im Durchschaltezustand befindet, den  $U_{DD}$ -Potentialzustand

bei.

15 Gleichzeitig ist der Vorschalt-Transistor Tpe (in FIG 2 bis FIG

20 4) des betrachteten Koppelementepaars Kij ebenso wie der

Schalter-Transistor Tpk und der zugehörige Abtast-Transistor Tna

leitend, so daß der zugeordnete Signalleiter zi' der Matrixaus-

25 gangsleitung (Zeilenleitung) zi über dieses Koppelement des

Koppelementepaars Kij entladen und auf das  $U_{SS}$ -Potential ge-

zogen wird.

25 Herrscht dagegen auf der gerade betrachteten Matrixeingangslei-

tung sj der "High"-Signalzustand und ist dementsprechend der

n-Kanal-Vorschalt-Transistor Tne (in FIG 2 bis FIG 4) des betref-

fenden Koppelementepaars Kij leitend, so wird der betreffende

30 Signalleiter zi" der Matrixausgangsleitung (Zeilenleitung) zi

über das betreffende Koppelement dieses Koppelementepaars

Kij entladen und auf das  $U_{SS}$ -Potential gezogen.

30 Gleichzeitig ist dann der Vorschalt-Transistor Tpe (in FIG 2 bis

FIG 4) des betrachteten Koppelementepaars Kij nichtleitend,

so daß der zugeordnete Signalleiter zi' der Matrixausgangslei-

tung (Zeilenleitung) über dieses Koppelement des Koppel-

elementepaars Kij nicht entladen wird, sondern, sofern kein

35 anderer zu dieser Matrixausgangsleitung (Zeilenleitung) zi füh-

render Koppelpunkt sich im Durchschaltezustand befindet, den

$U_{DD}$ -Potentialzustand beibehält.

- 13 -

1 In den im vorstehenden anhand von FIG 2 bis FIG 4 erläuterten

Ausführungsbeispielen sind die Vorlade-Transistoren ( $T_{pi}'$ ,  $T_{pi}''$ )

durch p-Kanal-Transistoren gebildet, wobei diese p-Kanal-Vorlade-

Transistoren ( $T_{pi}$ ) und die durch n-Kanal-Transistoren gebildeten

5 Abtast-Transistoren ( $T_{na}$ ), durch den unterschiedlichen Kanal-

typus bedingt, durch ein und dasselbe Signal ( $T$ ) gegensinnig

zueinander gesteuert werden. In Abweichung hiervon ist es aber

auch möglich, die Vorlade-Transistoren mit n-Kanal-Transistoren

zu realisieren, so daß, wenn auch die Schalter-Transistoren

10 ( $T_{nk}$ ), die Vorschalt-Transistoren ( $T_{ne}$ ) und die Abtast-Transi-

storen ( $T_{na}$ ) n-Kanal-Transistoren sind, nur Transistoren ein

und desselben Kanaltyps zur Anwendung kommen; damit dann Vor-

lade-Transistoren und Abtast-Transistoren wiederum gegensinnig

15 zueinander jeweils an ihrer Steuerelektrode mit dem Koppelfeld-

Ansteuer-Takt beaufschlagt werden, ist den Abtast-Transistoren

( $T_{na}$ ) wiederum, wie in den anhand von FIG 2 bis FIG 4 beschrie-

benen Ausführungsbeispielen, das Koppelfeld-Ansteuer-Taktsignal

( $T$ ) direkt zuzuführen, den (n-Kanal-)Vorlade-Transistoren da-

gegen das invertierte Koppelfeld-Ansteuer-Taktsignal.

20

6 Patentansprüche

5 FIG

25

30

35

## 1 Patentansprüche

1. Breitbandsignal-Koppeleinrichtung mit einer Koppelpunktmatrix in FET-Technik, deren Matrixeingangsleitungen (sj) über jeweils 5 mit Koppelementpaaren (Kij) gebildete Koppelpunkte (KPij) mit jeweils mit zwei Signalleitern (zi', zi") gebildeten Matrixausgangsleitungen (zi) verbindbar sind, an deren beiden Signalleiter (zi', zi") jeweils die beiden Signaleingänge einer mit einem Differenzverstärker mit Kippverhalten gebildeten Ausgangsver-10 stärkerschaltung (Ai) anschließbar sind,

wobei die Koppelementpaare (Kij) jeweils mit zwei jeweils an der Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal beaufschlagten und mit einer Hauptelektrode an den einen bzw. anderen Signalleiter (zi', zi") der zugehörigen Matrixausgangs-15 leitung (zi) angeschlossenen Schalter-Transistoren (Tpk, Tnk) und zwei jeweils mit einem Schalter-Transistor (Tpk, Tnk) eine Serienschaltung bildenden Vorschalt-Transistoren (Tpe, Tne) gebildet sind,

die jeweils mit der Steuerelektrode an einen Signalleiter (sj) 20 der zugehörigen Matrixeingangsleitung (sj) angeschlossen sind und deren jeweilige der Serienschaltung abgewandte Hauptelektrode über einen koppelement-, matrixeingangsleitungs- oder matrixausgangsleitungs-individuellen Abtast-Transistor (Tna) mit dem einen Anschluß (U<sub>SS</sub>, Masse) der Betriebsspannungsquelle ver-25 bunden ist, mit deren anderen Anschluß (U<sub>DD</sub>) jeder Signalleiter (zi', zi") der jeweiligen Matrixausgangsleitung (zi) jeweils über einen Vorlade-Transistor (Tpi', Tpi") verbunden ist,

wobei Vorlade-Transistoren (Tpi', Tpi") und Abtast-Transistor (Tna) gegensinnig zueinander jeweils an ihrer Steuerelektrode 30 mit einem eine Bit-Durchschaltezeitspanne in eine Vorladephase (pv) und die eigentliche Durchschaltephase (ph) unterteilenden Koppelfeld-Ansteuer-Takt (T) beaufschlagt sind, so daß in jeder Vorphase (pv) bei gesperrtem Abtast-Transistor (Tna) beide Signalleiter der Matrixausgangsleitung (zi) über den jeweiligen 35 Vorlade-Transistor (Tpi', Tpi") zum mindest angenähert auf das an dem genannten anderen Anschluß (U<sub>DD</sub>) der Betriebsspannungsquelle herrschende Potential geladen werden,

und wobei die beiden Vorlade-Transistoren (Tpi', Tpi") an ihren

- 15 -

- 1 der jeweiligen Matrixausgangsleitung (zi) zugewandten Hauptelektroden miteinander über einen Quertransistor (Tp<sup>i'''</sup>) verbunden sind, dessen Steuerelektrode mit den Steuerelektroden der Vorlade-Transistoren (Tp<sup>i'</sup>, Tp<sup>i''</sup>) verbunden ist,

- 5 dadurch gekennzeichnet, daß die Koppelementpaare (K<sub>ij</sub>) jeweils zwei Vorschalt-Transistoren (Tp<sub>e</sub>, T<sub>ne</sub>) unterschiedlichen Kanaltyps aufweisen, die mit ihrer Steuerelektrode an ein und denselben Signalleiter (s<sub>j</sub>) der zugehörigen Matrixeingangsleitung (s<sub>j</sub>) angeschlossen sind.

- 10 2. Breitbandsignal-Koppeleinrichtung nach Anspruch 1, dadurch gekennzeichnet, daß die Koppelementpaare (K<sub>ij</sub>) jeweils zwei Schalter-Transistoren (Tp<sub>k</sub>, T<sub>nk</sub>) unterschiedlichen Kanaltyps aufweisen, die jeweils 15 mit einem Vorschalt-Transistor (Tp<sub>e</sub>, T<sub>ne</sub>) desselben Kanaltyps eine Serienschaltung bilden.

3. Breitbandsignal-Koppeleinrichtung nach Anspruch 2, dadurch gekennzeichnet, 20 daß nur bei einem Teil der zu ein und derselben Matrixausgangsleitung (zi) führenden Koppelementpaare (K<sub>ij</sub>) die Transistor-Serienschaltung (Tp<sub>e</sub>, Tp<sub>k</sub>) des einen Kanaltyps mit dem einen Signalleiter (zi') und die Transistor-Serienschaltung (T<sub>ne</sub>, T<sub>nk</sub>) des anderen Kanaltyps mit dem anderen Signalleiter (zi'') der 25 Matrixausgangsleitung (zi) verbunden ist und bei dem anderen Teil der zu der betreffenden Matrixausgangsleitung (zi) führenden Koppelementpaare die Transistor-Serienschaltung des genannten anderen Kanaltyps mit dem genannten einen Signalleiter (zi') und die Transistor-Serienschaltung (T<sub>ne</sub>, T<sub>nk</sub>) des genannten einen Kanaltyps mit dem genannten anderen Signalleiter (zi'') der Matrixausgangsleitung (zi) verbunden ist.

4. Breitbandsignal-Koppeleinrichtung nach Anspruch 3, dadurch gekennzeichnet, 35 daß in der einen bzw. in der anderen Weise mit den Signalleitern (zi', zi'') der zugehörigen Matrixausgangsleitung verbundene Koppelementpaare in der betreffenden Matrixreihe abwechselnd aufeinanderfolgen.

- 16 -

1 5. Breitbandsignal-Koppeleinrichtung nach einem der Ansprüche

1 bis 4,

d a d u r c h g e k e n n z e i c h n e t ,

daß neben einem matrixeingangsleitungs-individuellen Abtast-

5 Transistor (Tnaj) ein matrixeingangsleitungs-individueller Vor-

lade-Transistor (Tpaj) vorgesehen ist.

6. Breitbandsignal-Koppeleinrichtung nach einem der Ansprüche

1 bis 4,

10 d a d u r c h g e k e n n z e i c h n e t ,

daß neben einem matrixausgangsleitungs-individuellen Abtast-

Transistor (Tnai) ein matrixausgangsleitungs-individueller Vor-

lade-Transistor (Tpai) vorgesehen ist.

15

20

25

30

35

FIG 1

FIG 2

FIG 3

FIG 4

FIG 5