**【特許請求の範囲】****【請求項 1】**

双方向にデータを転送可能な信号線と、

前記信号線を終端する少なくとも一つの終端素子と

を備え、

前記少なくとも一つの終端素子のインピーダンスは、前記データが転送される方向に応じて可変であるデータバス。

**【請求項 2】**

前記信号線に対して直列に接続された可変インピーダンス素子

を更に備え、

前記可変インピーダンス素子のインピーダンスは、前記データが転送される方向に応じて可変である請求項 1 記載のデータバス。

**【請求項 3】**

双方向にデータを転送可能な信号線と、

前記信号線に対して直列に接続された可変インピーダンス素子と

を備え、

前記可変インピーダンス素子のインピーダンスは、前記データが転送される方向に応じて可変であるデータバス。

**【請求項 4】**

前記信号線は、第 1 端及び第 2 端と、前記第 1 端と前記第 2 端との間から分岐する少なくとも一つの第 3 端とを有し、

前記少なくとも一つの第 3 端の各々には前記データの読み出し / 書き込みが可能なメモリが接続され、

前記少なくとも一つの終端素子は、前記第 2 端に接続されて前記読み出し / 書き込み動作に応じて異なる抵抗値を探る第 1 の終端可変抵抗を有する、請求項 1 及び請求項 2 のいずれか一つに記載のデータバス。

**【請求項 5】**

前記第 1 端には、前記メモリに対する書き込みデータの送信と、前記メモリからの読み出しデータの受信とを行うメモリコントローラが接続され、

前記書き込みの際には前記読み出しの際よりも、前記第 1 の終端可変抵抗の抵抗値が小さい、請求項 4 記載のデータバス。

**【請求項 6】**

前記少なくとも一つの終端素子は、前記第 1 端に接続されて前記読み出し / 書き込み動作に応じて異なる抵抗値を探る第 2 の終端可変抵抗を更に有する、請求項 4 及び請求項 5 のいずれか一つに記載のデータバス。

**【請求項 7】**

前記第 1 端には、前記メモリに対する書き込みデータの送信と、前記メモリからの読み出しデータの受信とを行うメモリコントローラが接続され、

前記書き込みの際には前記第 2 の終端可変抵抗の抵抗値を無限大にし、前記読み出しの際には前記第 1 の終端可変抵抗の抵抗値を無限大にする、請求項 6 記載のデータバス。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明はデータバスを用いてデータの授受を行う技術に関するものである。

**【0002】****【従来の技術】**

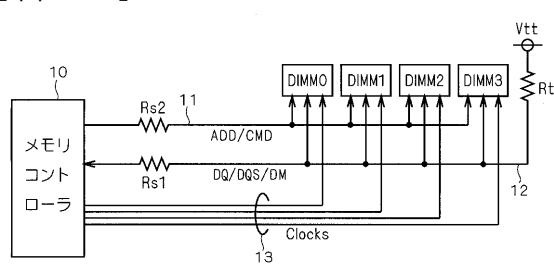

図 15 および図 16 は、コンピュータシステムのマザーボード上に構築される従来のメモリシステムの構成を示す図である。ここでは、メモリシステムの一例として、DRAM (Dynamic Random Access Memory) を搭載したDIMM (Dual Inline Memory Module) を 4 個搭載するメモリシステムを

10

20

30

40

50

示している。同図に示すように、メモリコントローラ 10 と 4 個の D I M M ( D I M M 0 ~ D I M M 3 ) との間は、アドレス / コマンドバス 11 、データバス 12 、クロックライン 13 により接続されている。

#### 【 0 0 0 3 】

メモリコントローラ 10 はアドレス / コマンドバス 11 およびデータバス 12 を介して、4 個の D I M M のそれぞれの動作を制御すると共に、各 D I M M に対してデータの書き込み及び読み出しを行う。アドレス / コマンドバス 11 は、メモリコントローラ 10 が出力する命令信号 ( C M D ) およびアドレス信号 ( A D D ) を各 D I M M に転送するためのバスである。命令信号 ( C M D ) とは、メモリコントローラ 10 がそれぞれの D I M M に対してデータの書き込みあるいは読み出しの指示を行うための信号である。また、アドレス信号 ( A D D ) とは、その書き込みあるいは読み出しの対象となる D R A M のアドレスを指定するための信号である。

10

#### 【 0 0 0 4 】

データバス 12 は、メモリコントローラ 10 と各 D I M M 間のデータの転送を担うバスであり、メモリコントローラ 10 と各 D I M M 間での双方向のデータ転送が可能である。即ち、メモリコントローラ 10 が D I M M に対してデータの書き込みを行う場合、データバス 12 はメモリコントローラ 10 が出力するデータ ( 書き込みデータ ) を D I M M へと転送し、反対にメモリコントローラ 10 が D I M M に対してデータの読み出しを行う場合、D I M M から出力されたデータ ( 読み出しデータ ) をメモリコントローラ 10 へと転送する。

20

#### 【 0 0 0 5 】

また、データバス 12 を介してメモリコントローラ 10 と D I M M との間でやりとりされる信号としては、書き込み及び読み出しの対象そのものであるデータ信号 ( D Q ) の他、メモリコントローラ 10 あるいは D I M M 内の D R A M がデータを取り込む際に用いられるデータストローブ ( D a t a S t r o b e ) 信号 ( D Q S ) や、データをマスクするための信号 ( D M ) 等がある。なお、説明の簡単のために図示は省略したが、アドレス / コマンドバス 11 やデータバス 12 等のメモリバスはそれぞれ複数の信号線によって構成されている。例えば、D Q / D Q S / D M の転送を担うデータバス 12 であれば、108 本程度の信号線により構成されるのが一般的である。

30

#### 【 0 0 0 6 】

また、メモリコントローラ 1 は、メモリシステムの動作タイミングの基準となる基準周波数を有する基準クロック信号を、クロックライン 13 を介してそれぞれの D I M M に送信する。

#### 【 0 0 0 7 】

ここで、図 15 に示した従来のメモリシステムの動作を簡単に説明する。例えば、D I M M へのデータの書き込みを行う場合、まず、メモリコントローラ 10 はアドレス / コマンドバス 11 を介して、D I M M に対しデータの書き込み指示を行う命令信号 ( C M D ) を出力すると共にアドレス信号 ( A D D ) によりその書き込みの対象となるアドレスを指定する。その後、メモリコントローラ 10 がデータバス 12 を介して書き込みデータを D I M M へ転送することで、指定されたアドレスに当該データが書き込まれる。

40

#### 【 0 0 0 8 】

反対に、D I M M からのデータの読み出しを行う場合、まず、メモリコントローラ 10 はアドレス / コマンドバス 11 を介して、D I M M に対しデータの読み出し指示を行う命令信号 ( C M D ) を出力する共にアドレス信号 ( A D D ) によりその読み出しの対象となるアドレスを指定する。すると、D I M M の指定されたアドレスに記憶されたデータが読み出される。そのデータ ( 読み出しデータ ) はデータバス 12 を介してメモリコントローラ 10 へと転送され、メモリコントローラ 10 によって当該読み出しデータが読み込まれる。

#### 【 0 0 0 9 】

ところで、アドレス / コマンドバス 11 やデータバス 12 等のメモリバスにおいてデータ

50

信号の転送の際に反射が生じると、その影響により信号歪みが発生する。従って、反射の発生を抑える目的でメモリバスの信号線路におけるインピーダンス整合をとることは重要である。よって一般に、メモリバスを構成するそれぞれの信号線は所定の終端抵抗により終端される。

【0010】

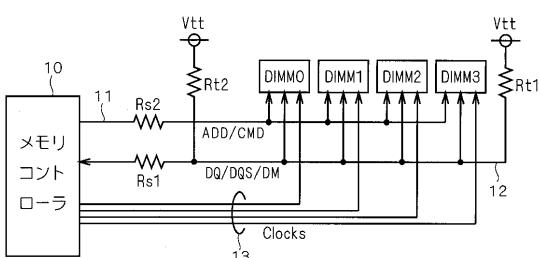

例えば図15では、データバス12には、その信号線に対して直列接続された直列抵抗Rs1と、終端抵抗Rt1が備え付けられている。また、アドレス/コマンドバス11には、その信号線に対して直列接続された直列抵抗Rs2が備え付けられている。また、終端抵抗Rt2は所定の電圧Vttに接続されるが、通常Vttは電源電圧の半分程度の電圧に設定される。なお、上記したようにメモリバスを構成する個々の信号線の図示は省略しているが、終端抵抗はメモリバスを構成する信号線のそれぞれが有している。

10

【0011】

一般的に終端抵抗は、転送される信号の受信側に近い位置に接続させる方が、受信側における信号歪みをより効果的に抑えることができる。上記したようにデータバス12は双方向の信号の転送を担っているので、DIMMからのデータ読み出しの際のデータ転送を考慮し、データバス12の信号線の終端抵抗を図16のような構成としても良い。つまり、データバス12を構成する信号線のうちメモリコントローラ1が接続された第1端側においてDIMMよりもメモリコントローラ10に近い方に（即ち、メモリコントローラ10とDIMMとの間）にも終端抵抗Rt2を備え付けてもよい。それにより、DIMMからの読み出し動作の際に、メモリコントローラ10で受信される信号の歪みを図15の例よりも効果的に抑えることができる。

20

【0012】

近年、メモリシステムの動作の高速化および低消費電力化を図るために、メモリコントローラ10とのDIMM間ににおける信号の振幅は小さく抑えられる傾向にある。それに伴い、信号の振幅のマージンは減少してきており、信号歪みを抑えることの重要性はさらに高まっている。従って、メモリバスを構成する信号線に直列抵抗や終端抵抗を備え付けることでインピーダンス整合を図り、反射の影響による信号歪みを抑えることの重要性はさらに高まっている。

30

【0013】

【発明が解決しようとする課題】

上記の例で示したデータバス12のように、信号線が双方向のデータの転送を担う場合、特に転送する信号の周波数が高くなると、信号の一の方向への転送の際のインピーダンス整合と他の方向への転送の際のインピーダンス整合の両方をバランスよく保つことは困難になる。つまり、データバス12の終端抵抗Rt1、Rt2並びに直列抵抗Rs1が信号歪みを抑える効果が、データの転送方向により異なる場合がある。その場合、DIMMへのデータ書き込み時（メモリコントローラ10からDIMMへのデータ転送時）と、DIMMからのデータ読み出し時（DIMMからメモリコントローラ10へのデータ転送時）とで、直列抵抗や終端抵抗が信号歪みを抑える効果に違いが生じる。

【0014】

従って、例えばDIMMへのデータ書き込み時における信号歪みを抑えるようにインピーダンスを設定された終端抵抗を使用すると、逆に、読み出し時におけるインピーダンス整合が崩れ、読み出し時におけるデータ信号の波形に歪みが生じる。その結果、データバス12で転送される信号の振幅にある程度のマージンを持たせる必要が生じ、メモリシステムの動作の高速化および低消費電力化の妨げとなる。

40

【0015】

本発明は以上のような課題を解決するためになされたものであり、双方向へのデータ転送を担うデータバスを有するメモリシステムにおいて、データ転送の方向を問わず信頼性の高いデータの転送が可能なデータバスを提供することを目的とする。

【0016】

【課題を解決するための手段】

50

請求項 1 に記載のデータバスは、双方にデータを転送可能な信号線と、前記信号線を終端する少なくとも一つの終端素子とを備え、前記少なくとも一つの終端素子のインピーダンスは、前記データが転送される方向に応じて可変である。

【 0 0 1 7 】

請求項 2 に記載のデータバスは、請求項 1 記載のデータバスにおいて、前記信号線に対して直列に接続された可変インピーダンス素子を更に備え、前記可変インピーダンス素子のインピーダンスは、前記データが転送される方向に応じて可変である。

【 0 0 1 8 】

請求項 3 に記載のデータバスは、双方にデータを転送可能な信号線と、前記信号線に対して直列に接続された可変インピーダンス素子とを備え、前記可変インピーダンス素子のインピーダンスは、前記データが転送される方向に応じて可変である。 10

【 0 0 1 9 】

請求項 4 に記載のデータバスは、請求項 1 及び請求項 3 のいずれか一つに記載のデータバスにおいて、第 1 端及び第 2 端と、前記第 1 端と前記第 2 端との間から分岐する少なくとも一つの第 3 端とを有し、前記少なくとも一つの第 3 端の各々には前記データの読み出し／書き込みが可能なメモリが接続され、前記少なくとも一つの終端素子は、前記第 2 端に接続されて前記読み出し／書き込み動作に応じて異なる抵抗値を探る第 1 の終端可変抵抗を有する。

【 0 0 2 0 】

請求項 5 に記載のデータバスは、請求項 4 記載のデータバスにおいて、前記第 1 端には、前記メモリに対する書き込みデータの送信と、前記メモリからの読み出しデータの受信とを行うメモリコントローラが接続され、前記書き込みの際には前記読み出しの際よりも、前記第 1 の終端可変抵抗の抵抗値が小さい。 20

【 0 0 2 1 】

請求項 6 に記載のデータバスは、請求項 4 及び請求項 5 のいずれか一つに記載のデータバスにおいて、前記少なくとも一つの終端素子は、前記第 1 端に接続されて前記読み出し／書き込み動作に応じて異なる抵抗値を探る第 2 の終端可変抵抗を更に有する。

【 0 0 2 2 】

請求項 7 に記載のデータバスは、請求項 6 記載のデータバスにおいて、前記第 1 端には、前記メモリに対する書き込みデータの送信と、前記メモリからの読み出しデータの受信とを行うメモリコントローラが接続され、前記書き込みの際には前記第 2 の終端可変抵抗の抵抗値を無限大にし、前記読み出しの際には前記第 1 の終端可変抵抗の抵抗値を無限大にする。 30

【 0 0 2 3 】

【発明の実施の形態】

<実施の形態 1 >

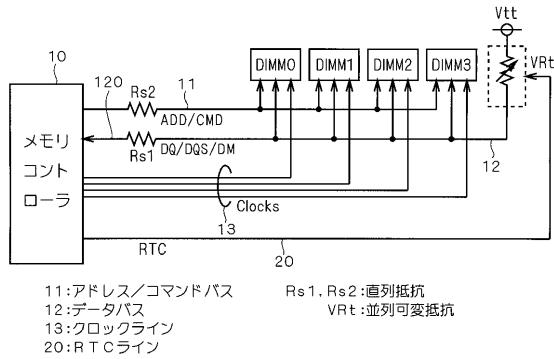

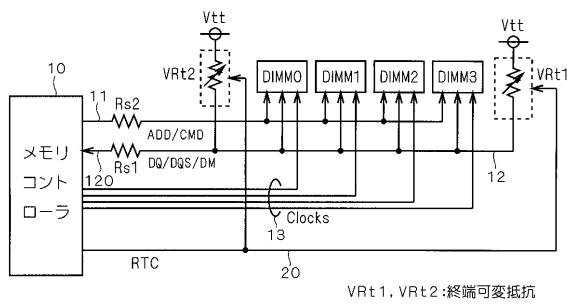

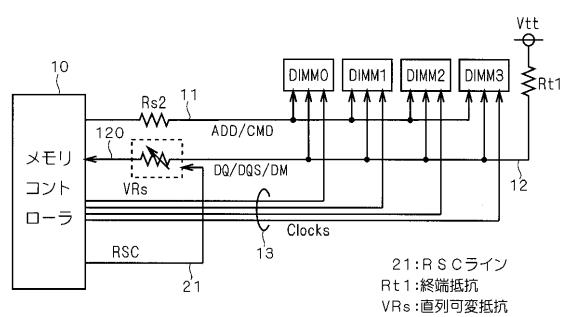

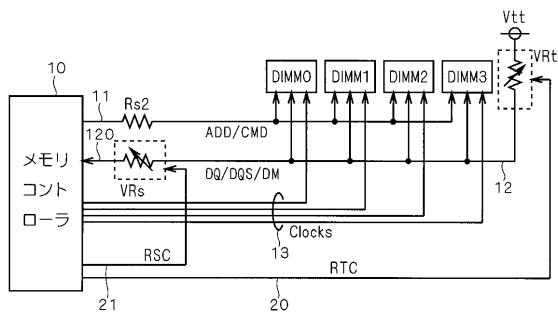

図 1 は本発明の実施の形態 1 に係るデータバスが適用可能なメモリシステムの構成を示す図である。この図において、図 15 と同様の要素については同一符号を付してあるので、それらについての詳細な説明は省略する。同図に示すように、本実施の形態においてはデータバス 12 は信号線 120 と、これを終端する終端素子として可変抵抗 VRt (以下「終端可変抵抗」) と、直列抵抗 R s1 とを備えている。信号線 120 は DIMM に対する書き込みデータの送信と、DIMM からの読み出しデータの受信とを行うメモリコントローラ 10 が直列抵抗 R s1 を介して接続される第 1 端と、終端可変抵抗 VRt が接続される第 2 端とを有している。第 1 端と第 2 端との間からは少なくとも 1 つの第 3 端が分岐し、第 3 端の各々には DIMM が接続されている。 40

【 0 0 2 4 】

終端可変抵抗 VRt のインピーダンス (抵抗値) は、外部から入力される制御信号 (以下「RTC 信号」と称する) により制御可能である。例えば、メモリコントローラ 10 は DIMM に対するデータの書き込みや読み出し動作の制御を行うと共に、RTC 信号を出力してもよい。このようにメモリコントローラ 10 が、終端可変抵抗 VRt のインピーダンス 50

スを制御するインピーダンス制御部としての機能を備えることにより、言い換えると、インピーダンス制御部をメモリコントローラ10に内蔵させることにより、メモリシステムの小型化を図ることができる。RTC信号は、当該RTC信号を伝達するためのRTCライン20を介して終端可変抵抗VRtに入力される。

【0025】

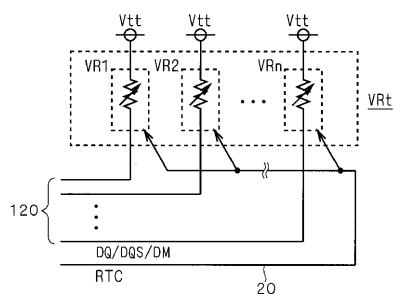

ここで、上記したように通常データバス12等は複数本（例えば108本程度）の信号線によって構成されており、それら信号線のそれぞれが終端抵抗を備える必要がある。従つて、説明の簡単のために図1での図示は省略したが、実際には図2のようにデータバス12の信号線のそれぞれに終端可変抵抗VR1～VRn（nは例えば108）が設けられる。

10

【0026】

なお、以下の実施の形態においてもデータバス12の信号線のそれぞれが終端抵抗を備えることとなるが、説明の簡単のために以降説明する図においてもそれら複数個の終端抵抗を図1と同様に図面上1つにまとめて示す。

【0027】

上述したように、データバス12が信号線が双方向の信号の転送を担う場合、特に転送する信号の周波数が高くなると、DIMMに対するデータの書き込み時（書き込みモード：データはメモリコントローラ10からDIMMへと転送される）および読み出し時（読み出しモード：データはメモリコントローラ10へとDIMMから転送される）の両方でインピーダンス整合をバランスよく保つことは困難になる。そこで、本実施の形態に係るメモリシステムにおいては、それらの動作モードに応じて、即ちデータが転送される方向に応じてメモリコントローラ10が終端可変抵抗VRtのインピーダンスを適切な設定する。

20

【0028】

つまり、メモリコントローラ10は終端可変抵抗VRtのインピーダンスを、書き込みモードでは書き込みモードに適切なインピーダンス（以下「書き込み用インピーダンス」という）に、読み出しモードでは読み出しモードに適切なインピーダンス（以下「読み出し用インピーダンス」という）に切り替える。それにより、データバス12において動作モードを問わず信頼性の高いデータ転送が可能になる。

【0029】

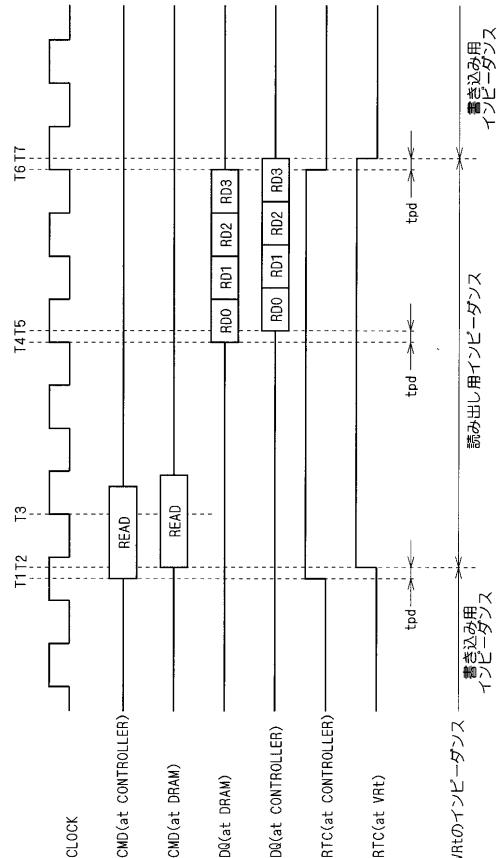

図3は、本実施の形態に係るメモリシステムの動作を示すタイミングチャートである。以下、この図に基づいて本実施の形態に係るメモリシステムの動作について説明する。説明の簡単のため、アドレス/コマンドバス11、データバス12 RTCライン20のいずれにおける伝播遅延も等しくtpdとする。まず、初期状態ではメモリコントローラ10によるRTC信号（RTC）の出力は“0”であり、終端可変抵抗VRtのインピーダンスは書き込み用インピーダンスであるとする。

30

【0030】

そしてメモリシステムが読み出しモードになり、メモリコントローラ10はDIMMに対してデータの読み出しを行うとする。その場合、タイミングT1でメモリコントローラ10は、アドレス/コマンドバス11を介しDIMM内のDRAMへ読み出し指示の命令信号（CMD）“Read”を出力すると共に、読み出しの対象となるアドレスを指定するアドレス信号（不図示）を出力する。さらにそれと同時に、メモリコントローラ10はRTC信号（RTC）のレベルを“1”とし、RTCライン20を介して終端可変抵抗VRtへと出力する。

40

【0031】

タイミングT1でメモリコントローラ10より出力された命令信号“Read”は、伝播遅延tpdだけ遅れてタイミングT2でDRAMに到達する。また、RTC信号“1”もまた同じくタイミングT2で終端可変抵抗VRtに到達する。終端可変抵抗VRtは、RTC信号“1”を受けると、自身のインピーダンスを読み出し用インピーダンスに変化させる。

50

## 【0032】

一方、メモリコントローラ10からDRAMに到達した命令信号"Read"は、タイミングT2の直後で基準クロック信号が立ち上がるタイミングT3でDRAMに認識される。DRAMは命令信号"Read"を認識すると、所定のタイミングT4(図3の例では命令信号"Read"を認識したタイミングT3の2クロック後)で、アドレス信号により指定されたアドレスに記憶されているデータをデータバス12へと出力する。図3の例では、DRAMから連続して4ビットのデータRD0～RD3が出力される。

## 【0033】

DRAMから出力された一連のデータRD0～RD3は、伝播遅延tpdだけ遅れたタイミングT5からメモリコントローラ10に到達し始め、基準クロック信号に同期したタイミング(DQS信号のタイミング)でメモリコントローラ10に順次読み込まれる。このとき、メモリコントローラ10は最後のデータRD3がメモリコントローラ10によって読み込まれるタイミングT6までRTC信号"1"を保持し、その後"0"に戻す。そして、RTC信号"0"は伝播遅延tpdだけ遅れてタイミングT7で終端可変抵抗VRtに到達する。終端可変抵抗VRtは、RTC信号"0"を受けると、自身のインピーダンスを書き込み用インピーダンスに変化させる。

## 【0034】

図3から分かるように、終端可変抵抗VRtのインピーダンスは、タイミングT2～T7の間は読み出し用インピーダンスとなる。つまり、DIMMに対して読み出しを行う間は、終端可変抵抗VRtのインピーダンスは読み出し用インピーダンスとなる。

## 【0035】

なお、図示は省略するが、読み出しモード以外の期間(書き込みモードやスタンバイ状態等の期間)では、メモリコントローラ10はRTC信号を"0"の値を維持し、終端可変抵抗VRtに書き込み用インピーダンスを維持させる。従って、メモリシステムが書き込みモードになり、メモリコントローラ10がDIMMに対してデータの書き込みを行う間は、終端可変抵抗VRtのインピーダンスは書き込み用インピーダンスとなる。

## 【0036】

以上のように、本実施の形態に係るデータバスよれば、終端可変抵抗VRtのインピーダンスは、読み出しモードの間は読み出し用インピーダンスとなり、それ以外の動作の間は書き込み用インピーダンスとなる。つまり、終端可変抵抗VRtのインピーダンスは、読み出しモードの間は読み出し用インピーダンスとなり、書き込みモードの間は書き込み用インピーダンスとなる。従って、読み出しモード、書き込みモードの動作モードを問わず、即ちデータの転送される方向を問わず、データバス12において信頼性の高いデータの転送が可能になる。

## 【0037】

なお、読み出しモード、書き込みモードのそれぞれの動作モードにおける終端可変抵抗VRtのインピーダンスの値は、例えば、実験やコンピュータシミュレーションによる解析によって得られる値や、所定の規格に基づいて得られる値等にすることが考えられる。但し、その決定の仕方は、それぞれの動作モードごとに終端抵抗を設ける目的によって異なる場合もある。

## 【0038】

例えば、読み出しモードおよび書き込みモードの両方で、反射による信号歪みを抑えることを目的とする場合は、それらの動作モード両方でインピーダンス整合がとれるように、終端可変抵抗VRtの読み出し用インピーダンスおよび書き込み用インピーダンスの値を決定すればよい。

## 【0039】

また例えば、読み出しモードにおいては信号波形の振幅を大きくして動作マージンを稼ぐことを主目的とし、書き込みモードにおいては反射による信号歪みを抑えることを主目的とする場合は、終端可変抵抗VRtにおける書き込み用インピーダンスの値はインピーダンス整合がとれる値、読み出し用インピーダンスの値は書き込み用インピーダンスよりも

10

20

30

40

50

比較的大きめの値にそれぞれ決定すればよい。

【0040】

なお、本発明の適用は、図1に示した構成のメモリシステムに限定されるものではなく、双方向のデータ転送を担う信号線を有するデータバスを備えるあらゆるデータ転送システムに対して広く適用可能であることは明らかである。

【0041】

また、図4は実施の形態1に係るメモリシステムの変形例を示す図である。データバス12の信号線120の第1端には直列抵抗Rs1と共に、信号線120を終端する終端可変抵抗VRt2をさらに備えている。言い換えれば、終端素子は、信号線120の第2端に接続された終端可変抵抗VRt1および信号線120の第1端に接続された終端可変抵抗VRt2とを含む。終端可変抵抗VRt1, VRt2のそれぞれのインピーダンスは共にRTC信号により制御される。それ以外の構成は、図1に示したメモリシステムと同様である。

【0042】

上述したように、終端抵抗は信号線上において信号の受信側に近い位置に接続させる方が、受信側における信号歪みをより効果的に抑えることができるので、この変形例によれば図1に示したメモリシステムよりもさらに、読み出しモードにおける信号歪みを効果的に抑えることができる。

【0043】

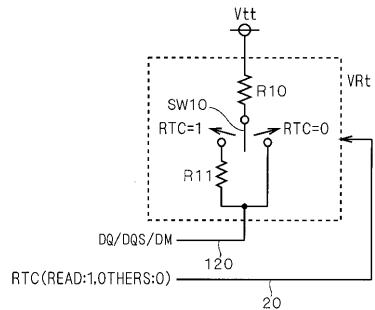

<実施の形態2>

本実施の形態では、上記した実施の形態1における終端可変抵抗VRtの構成のより具体的な例を示す。本実施の形態におけるメモリシステム全体の構成および動作は、実施の形態1で説明した図1～図3と同様であるのでここでの説明は省略する。

【0044】

ここでは上述した例のように、読み出しモードにおいては信号波形の振幅を大きくして動作マージンを稼ぐことを主目的とし、一方書き込みモードにおいては反射による信号歪みを抑えることを主目的とする場合を考える。この場合は、終端可変抵抗VRtにおける書き込み用インピーダンスの値として書き込み動作時にインピーダンス整合がとれる値、読み出し用インピーダンスの値として書き込み用インピーダンスよりも大きい値に決定すればよい。その場合、終端可変抵抗VRtは例えば図5に示すような構成とできる。

【0045】

図5において、抵抗R10は書き込み用インピーダンス（ここでは、書き込み動作時にインピーダンス整合がとれる抵抗値）を有すし、抵抗R11は所定のインピーダンス（抵抗値）を有し、リレーSW10はメモリコントローラ10からのRTC信号に応じて切り替わる。同図に示すように、リレーSW10はRTC信号が”1”（即ち、読み出し動作時）のとき抵抗R10を抵抗R11側に接続させ、RTC信号が”0”（即ち、読み出し動作時以外）のときは抵抗R10を直接データバス12の信号線120に接続させる。

【0046】

終端可変抵抗VRtのインピーダンスは、終端可変抵抗VRtを図5のように構成することで、書き込み動作時にはインピーダンス整合がとれる値になり、読み出し動作時には書き込み用インピーダンスよりも大きい値になる。よって、確実且つ容易に、読み出しモードで充分な動作マージンを得ることができる共に、書き込みモードの信号歪みを抑えることができる。

【0047】

また、この例からも明らかかなように本発明に係るメモリシステムによれば、読み出しモードと書き込みモードとで終端抵抗によるそれぞれ異なる効果を得ることが可能である。

【0048】

<実施の形態3>

本実施の形態においては、メモリシステムにおける終端可変抵抗VRtの制御に係る動作

10

20

30

40

50

の他の一例を示す。なお、本実施の形態に係るメモリシステムの構成は、図1および図2に示したものと同様であるので、ここでの詳細な説明は省略する。

【0049】

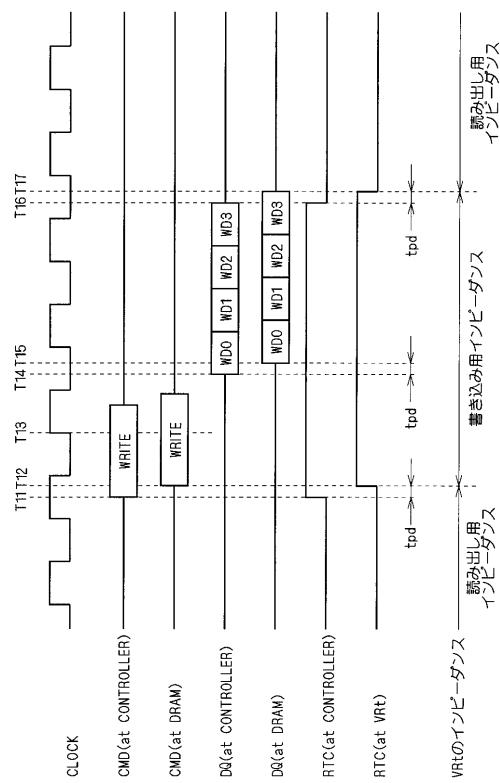

図6は、本実施の形態に係るメモリシステムの動作を示すタイミングチャートである。以下、この図に基づいて本実施の形態に係るメモリシステムの動作について説明する。まず、初期状態ではメモリコントローラ10によるRTC信号(RTC)の出力は"0"であり、終端可変抵抗VRtのインピーダンスは読み出し用インピーダンスであるとする。

【0050】

そして、メモリシステムが書き込みモードになり、メモリコントローラ10がDIMMに対してデータの書き込みを行う場合、タイミングT11でメモリコントローラ10は、アドレス/コマンドバス11を介しDIMM内のDRAMへ書き込み指示の命令信号(CMD)"Write"を出力すると共に、当該書き込みの対象となるアドレスを指定するアドレス信号(不図示)を出力する。さらにそれと同時に、メモリコントローラ10はRTC信号(RTC)のレベルを"1"とし、RTCライン20を介して終端可変抵抗VRtへと出力する。

【0051】

タイミングT11でメモリコントローラ10より出力された命令信号"Write"は、伝播遅延tpdだけ遅れてタイミングT12でDRAMに到達する。また、RTC信号"1"もまた同じくタイミングT12で終端可変抵抗VRtに到達する。終端可変抵抗VRtは、RTC信号"1"を受けると、自身のインピーダンスを書き込み用インピーダンスに変化させる。

【0052】

一方、メモリコントローラ10からDRAMに到達した命令信号"Write"は、タイミングT12の直後で基準クロックが立ち上がるタイミングT13でDRAMに認識される。メモリコントローラ10は命令信号"Write"を出力した後、さらに所定のタイミングT14で、書き込みを行うデータ(DQ)をデータバス12へと出力する。図6の例では、メモリコントローラ10から連続して4ビットのデータWD0~WD3が出力される。

【0053】

メモリコントローラ10から出力された一連のデータWD0~WD3は、伝播遅延tpdだけ遅れてタイミングT15からDIMM内のDRAMに到達し始める。DIMMは、基準クロック信号に同期したタイミング(DQS信号のタイミング)で一連のデータを読み取り、アドレス信号により指定されたアドレスに書き込む。このとき、メモリコントローラ10は最後のデータWD3の出力を終了するタイミングT16まではRTC信号"1"を保持し、その後"0"に戻す。そして、RTC信号"0"は伝播遅延tpdだけ遅れてタイミングT17で終端可変抵抗VRtに到達する。終端可変抵抗VRtは、RTC信号"0"を受けると、自身のインピーダンスを読み出し用インピーダンスに変化させる。

【0054】

図6から分かるように、終端可変抵抗VRtのインピーダンスは、タイミングT12~T17の間書き込み用インピーダンスとなる。つまり、終端可変抵抗VRtのインピーダンスは、DRAMにおける書き込み動作の間は書き込み用インピーダンスとなる。

【0055】

なお、図示は省略するが、メモリシステムが書き込みモード以外の期間(例えば読み出しモードやスタンバイ状態等の期間)では、メモリコントローラ10はRTC信号として"0"の値を維持し、終端可変抵抗VRtは読み出し用インピーダンスを維持する。従って、メモリシステムが読み出しモードになり、メモリコントローラ10がDIMMに対してデータの読み出しを行う間は、終端可変抵抗VRtのインピーダンスの値は読み出し用インピーダンスとなる。

【0056】

以上のように、本実施の形態に係るデータバスによれば、終端可変抵抗VRtのインピーダンスは、タイミングT12~T17の間書き込み用インピーダンスとなる。

ダンスは、書き込みモードの間は書き込み用インピーダンスとなり、それ以外の動作の間は読み出し用インピーダンスとなる。つまり、終端可変抵抗  $V R t$  のインピーダンスは、読み出しモードの間は読み出し用インピーダンスとなり、書き込みモードの間は書き込み用インピーダンスとなる。従って、読み出しモード、書き込みモードの動作モードを問わず、即ちデータが転送される方向を問わず、データバス 1 2 において信頼性の高いデータの転送が可能になる。

【 0 0 5 7 】

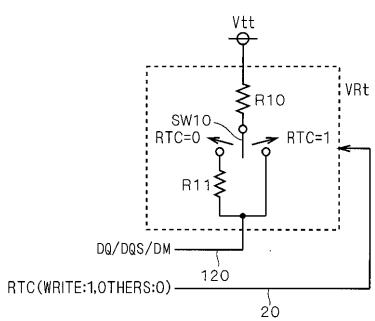

< 実施の形態 4 >

本実施の形態では、上記した実施の形態 3 における終端可変抵抗  $V R t$  の構成のより具体的な例を示す。本実施の形態におけるメモリシステム全体の構成は図 1 と同様であり、動作は図 6 と同様であるのでここでの説明は省略する。

【 0 0 5 8 】

ここでも実施の形態 2 と同様に、読み出しモードにおいては信号波形の振幅を大きくして動作マージンを稼ぐことを主目的とし、一方書き込みモードにおいては反射による信号歪みを抑えることを主目的とする場合を考える。その場合、終端可変抵抗  $V R t$  は例えば図 7 に示すような構成とすることができる。

【 0 0 5 9 】

図 7 においても、抵抗  $R 1 0$  は書き込み用インピーダンス（ここでは、書き込み動作時にインピーダンス整合がとれる抵抗値）を有し、抵抗  $R 1 1$  は所定のインピーダンスを有し、リレー  $S W 1 0$  はメモリコントローラ 1 0 からの  $R T C$  信号に応じて切り替わる。この図から分かるように、本実施の形態に係る終端可変抵抗  $V R t$  の構成はほぼ図 5 と同様である。

【 0 0 6 0 】

但し、実施の形態 3 ではメモリコントローラ 1 0 は書き込み動作時に  $R T C$  信号 " 1 " を出力するので、リレー  $S W 1 0$  の動作は実施の形態 2 と逆になる。即ち  $R T C$  信号が " 1 "（即ち、書き込み動作時）のとき抵抗  $R 1 0$  を直接データバス 1 2 の信号線 1 2 0 に接続させ、 $R T C$  信号が 0（即ち、書き込み動作時以外）のときは抵抗  $R 1 0$  を抵抗  $R 1 1$  側に接続させる。

【 0 0 6 1 】

終端可変抵抗  $V R t$  を図 7 のように構成することで、終端可変抵抗  $V R t$  のインピーダンスは、書き込み動作時にはインピーダンス整合がとれる値になり、書き込み動作時には書き込み用インピーダンスよりも大きい値になる。よって、確実且つ容易に、読み出しモードで充分な動作マージンを得ることができる共に、書き込みモードでの信号歪みを抑えることができる。

【 0 0 6 2 】

また、この例からも明らかなように本発明に係るメモリシステムによれば、読み出しモードと書き込みモードとで終端抵抗によるそれぞれ異なる効果を得ることが可能である。

【 0 0 6 3 】

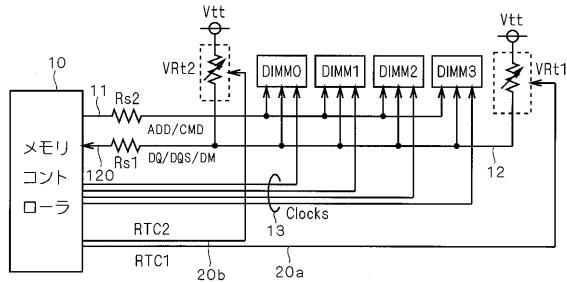

< 実施の形態 5 >

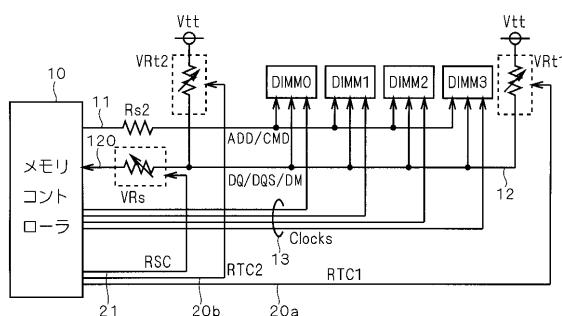

図 8 は実施の形態 5 に係るメモリシステムの構成を示す図である。同図に示すように、データバス 1 2 の信号線 1 2 0 の第 1 端には直列抵抗  $R s 1$  と共に、信号線 1 2 0 を終端する終端可変抵抗  $V R t 2$  をさらに備えている。言い換えれば、本実施の形態に係る終端素子は、信号線 1 2 0 の第 2 端に接続された終端可変抵抗  $V R t 1$  および信号線 1 2 0 の第 1 端に接続された終端可変抵抗  $V R t 2$  を含む。

【 0 0 6 4 】

本実施の形態においては、終端可変抵抗  $V R t 1$  のインピーダンス（抵抗値）を制御するための第 1 の  $R T C$  信号  $R T C 1$  と、終端可変抵抗  $V R t 2$  のインピーダンス（抵抗値）を制御するための第 2 の  $R T C$  信号  $R T C 2$  とが個別に与えられる。つまり、終端可変抵抗  $V R t 1$ 、 $V R t 2$  とはそれぞれ個別に独立して制御される。例えば第 1 および第 2 の  $R T C$  信号  $R T C 1$ 、 $R T C 2$  はメモリコントローラ 1 0 が出力し、図 8 に示すように終

10

20

30

40

50

端可変抵抗 V R t 1 とメモリコントローラ 1 0との間は第 1 の R T C 信号を伝達するための第 1 の R T C ライン 2 0 a により接続され、終端可変抵抗 V R t 2 とメモリコントローラ 1 0との間は、第 2 の R T C 信号を伝達するための第 2 の R T C ライン 2 0 b により接続される。なお、それ以外の構成は、図 1 に示したメモリシステムと同様である。

#### 【 0 0 6 5 】

また、このメモリシステムの動作は、図 3 あるいは図 7 に示したものと同様であってもよい。その場合、第 1 の R T C 信号と第 2 の R T C 信号とは常に同じ値を出力することとなり、実質的に実施の形態 1 において図 4 に示したメモリシステムと同じ構成および動作となる。しかし、メモリコントローラ 1 0 が、終端可変抵抗 V R t 1 , V R t 2 をそれぞれ独立して制御するので、以下に示すような動作も可能である。

10

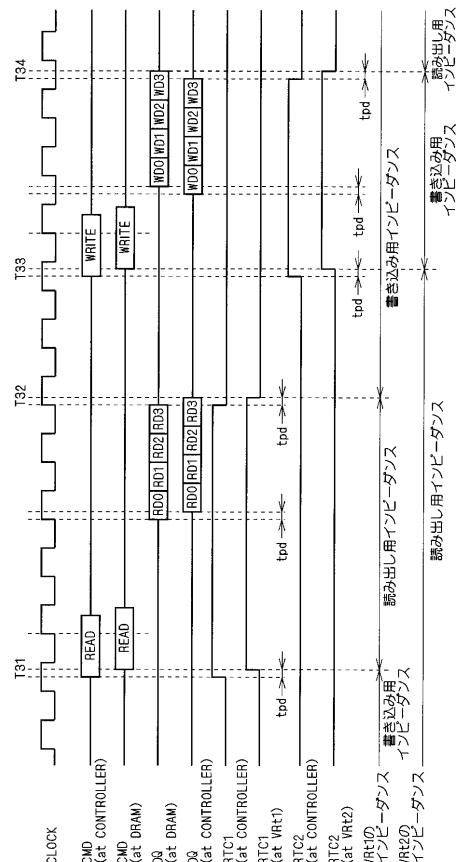

#### 【 0 0 6 6 】

図 9 は、実施の形態 5 に係るメモリシステムの動作の一例を示すタイミングチャートである。同図から分かるように、第 1 の R T C 信号 R T C 1 の出力に関しては図 3 と同様の動作を行い、第 2 の R T C 信号 R T C 2 の出力に関しては図 7 と同様の動作を行う。即ち、終端可変抵抗 V R t 1 のインピーダンスは、D I M M に対するデータの読み出し動作の間（タイミング T 3 1 ~ T 3 2 の間）は読み出し用インピーダンスとなり、それ以外の動作の間は書き込み用インピーダンスとなる。一方、終端可変抵抗 V R t 2 のインピーダンスは、D I M M に対するデータの書き込み動作の間（タイミング T 3 3 ~ T 3 4 の間）は書き込み用インピーダンスとなり、それ以外の動作の間は読み出し用インピーダンスとなる。

20

#### 【 0 0 6 7 】

よって結果的に、終端可変抵抗 V R t 1 , V R t 2 は、読み出し動作の間は共に読み出し用インピーダンスとなり、書き込み動作の間は共に書き込み用インピーダンスとなる。従って、読み出しモード、書き込みモードを問わず、データバス 1 2 において信頼性の高いデータの転送が可能になる。

#### 【 0 0 6 8 】

このように本実施の形態においては、終端可変抵抗 V R t 1 , V R t 2 のインピーダンスをそれぞれ独立して個別に制御するので、制御方法の自由度が増す。また、終端可変抵抗 V R t 1 , V R t 2 のインピーダンスの値の組み合わせにより、様々なインピーダンスの値を得ることも可能である。このことは、例えばメモリシステムが多機能化して、様々な周波数の信号の転送をデータバス 1 2 が担う必要が生じた場合に有効であると言える。

30

#### 【 0 0 6 9 】

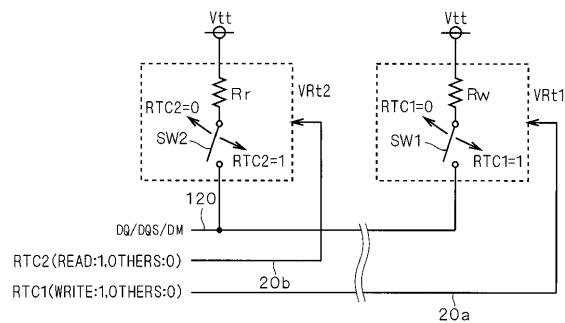

##### < 実施の形態 6 >

本実施の形態では、上記した実施の形態 5 における終端可変抵抗 V R t 1 , V R t 2 の構成のより具体的な例を示す。本実施の形態において、メモリシステム全体としての構成は図 8 と同様であり、その動作は図 9 と同様であるとする。それらの図については、実施の形態 5 で説明したとおりであるのでここでの説明は省略する。

#### 【 0 0 7 0 】

図 1 0 は本実施の形態に係るメモリシステムにおける終端可変抵抗 V R t 1 , V R t 2 の構成並びに動作を説明するための図である。同図に示すように、終端可変抵抗 V R t 1 は、書き込み用インピーダンスを有する抵抗 R w とリレー S W 1 とから成り、終端可変抵抗 V R t 2 は読み出し用インピーダンスを有する抵抗 R r とリレー S W 2 とから成る。リレー S W 1 は第 1 の R T C 信号（R T C 1 ）により制御されており、第 1 の R T C 信号が “1”（書き込み動作時）のとき ON 、 “0”（書き込み動作時以外）のとき OFF となる。一方、リレー S W 2 は第 2 の R T C 信号（R T C 2 ）により制御されており、第 2 の R T C 信号が “1”（読み出し動作時）のとき ON 、 “0”（読み出し動作時以外）のとき OFF となる。

40

#### 【 0 0 7 1 】

よって、D I M M に対する書き込み動作の間は、終端可変抵抗 V R t 1 のインピーダンスは書き込み用インピーダンス、終端可変抵抗 V R t 2 のインピーダンスは無限大となる。

50

対して、読み出し動作の間は、終端可変抵抗  $V_{Rt1}$  のインピーダンスは無限大、終端可変抵抗  $V_{Rt2}$  のインピーダンスは読み出し用インピーダンスとなる。言い換れば、書き込み動作の間は抵抗  $R_w$  のインピーダンスのみが機能し、読み出し動作の間は抵抗  $R_r$  のみが機能する。

【0072】

また、データバス12の信号線に対する終端可変抵抗  $V_{Rt1}$  の接続位置は終端可変抵抗  $V_{Rt2}$  の接続位置よりもDIMMの近くであり、一方、終端可変抵抗  $V_{Rt2}$  の接続位置は終端可変抵抗  $V_{Rt1}$  の接続位置よりもメモリコントローラ10の近くである。

【0073】

上述したように、終端抵抗は信号線上において信号の受信側に近い位置に接続させる方が受信側における信号歪みをより効果的に抑えることができる。よって、本実施の形態によれば、書き込みモードではDIMMに入力される信号の歪みが効果的に抑えられ、読み出しモードではメモリコントローラ10に入力される信号の歪みを効果的に抑えられる。従って、実施の形態5よりも、読み出しモードおよび書き込みモードの信号歪みを効果的に抑えることができる。

【0074】

<実施の形態7>

図11は実施の形態7に係るメモリシステムの構成を示す図である。同図に示すように、本実施の形態においては、図15に示された従来のメモリシステムに対し、直列抵抗  $R_s$  1を可変抵抗  $V_{Rs}$ （以下、「直列可変抵抗」と称する）に置換したメモリシステムについて説明する。つまり、データバス12の信号線120が備える終端抵抗は、直列可変抵抗  $V_{Rs}$  と終端抵抗  $R_t$  とから成る。また、直列可変抵抗  $V_{Rs}$  のインピーダンスは、外部から入力される制御信号（以下「RSC信号」と称する）により制御可能である。

【0075】

また、メモリコントローラ10はDIMMに対するデータの書き込みや読み出し動作の制御を行うことに加え、RSC信号を出力することにより直列可変抵抗  $V_{Rs}$  のインピーダンスを制御してもよい。このように、メモリコントローラ10が、直列可変抵抗  $V_{Rs}$  のインピーダンスを制御するインピーダンス制御部としての機能を備えることにより、言い換れば、インピーダンス制御部をメモリコントローラ10に内蔵することにより、メモリシステムの小型化を図ることができる。RSC信号は、当該RSC信号を伝達するためのRSCライン21を介して直列可変抵抗  $V_{Rs}$  に入力される。

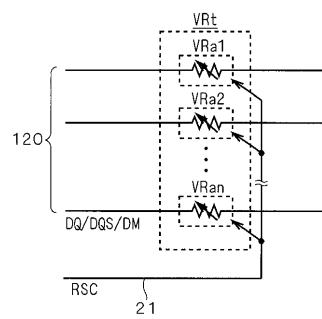

【0076】

ここで、説明の簡単のために図11での図示は省略したが、実際には図12のようにデータバス12の信号線のそれぞれに直列可変抵抗  $V_{Ra1} \sim V_{Ran}$ （nは例えば108）が設けられる。また、以下の説明に用いる図においても、複数個の直列可変抵抗  $V_{Rs}$  を図11のように図面上1つにまとめて示す。

【0077】

なお、本実施の形態においてメモリコントローラ10がRSC信号により直列可変抵抗  $V_{Rs}$  のインピーダンスを制御する動作は、実施の形態1あるいは3において説明したRTC信号による終端可変抵抗  $V_{Rs}$  の制御動作と同様でよい。即ち、直列可変抵抗  $V_{Rs}$  のインピーダンスは、読み出し動作の間は読み出し用インピーダンスとなり、書き込み動作の間は書き込み用インピーダンスとなる。従って、読み出しモード、書き込みモードを問わず、データバス12において信頼性の高いデータの転送が可能になる。

【0078】

<実施の形態8>

実施の形態7においては、データバス12の信号線120が備える終端抵抗のインピーダンスを固定値としたが、上記実施の形態1～6に示したような終端可変抵抗とも組み合わせ可能である。例えば、図13は実施の形態1に係る終端可変抵抗  $V_{Rt1}$  と組み合わせた場合の構成図であり、図14は実施の形態5に係る終端可変抵抗  $V_{Rt1}$ 、 $V_{Rt2}$  と組み合わせた場合の構成図である。

10

20

30

40

50

## 【0079】

このような組み合わせにより、データバス12の信号線120が備える終端可変抵抗および直列可変抵抗のインピーダンスを、読み出し動作の間は読み出し用インピーダンスとし、書き込み動作の間は書き込み用インピーダンスとすることが可能になる。従って、読み出しモード、書き込みモードを問わず、データバス12において信頼性の高いデータの転送が可能になる。

## 【0080】

なお、例えば図14においては、直列可変抵抗VRsおよび終端可変抵抗VRT1、VRT2がそれぞれ、RSC信号および第1、第2のRTC信号によりそれぞれ独立して制御される例を示しているが、それら全てを单一の制御信号により制御するものであっても良い。それにより、インピーダンス制御部の機能を有するメモリコントローラ10の構成を簡略化でき、メモリシステムの小型化並びにコスト削減に寄与できる。

## 【0081】

逆に、メモリコントローラ10が直列可変抵抗VRsおよび終端可変抵抗VRT1、VRT2をそれぞれ独立して制御する場合は、制御方法の自由度が増すと共に、直列可変抵抗VRsおよび終端可変抵抗VRT1、VRT2のインピーダンスの値の組み合わせにより、様々なインピーダンスの値を得ることが可能になるという効果がある。

## 【0082】

## 【発明の効果】

請求項1に記載のデータバスによれば、データが転送される方向に応じて終端素子のインピーダンスを異なる値に設定し、各方向でのデータの転送を適切に行うことができる。

## 【0083】

請求項2に記載のデータバスによれば、データが転送される方向に応じて終端素子及び可変インピーダンス素子のインピーダンスを異なる値に設定し、各方向でのデータの転送を適切に行うことができる。

## 【0084】

請求項3に記載のデータバスによれば、データが転送される方向に応じて可変インピーダンス素子のインピーダンスを異なる値に設定し、各方向でのデータの転送を適切に行うことができる。

## 【0085】

請求項4に記載のデータバスによれば、第1の終端可変抵抗の抵抗値が、書き込みの際と読み出しの際とで、その各々の動作に適した値を探ることで、当該データバスは、読み出し、書き込みのいずれの動作においても、信頼性の高いデータの転送を可能とする。

## 【0086】

請求項5に記載のデータバスによれば、請求項4記載のデータバスにおいて、読み出しの際には第1の終端可変抵抗の抵抗値を大きくし、データを表す信号波形の振幅を大きくしてメモリコントローラの動作マージンを稼ぐ。他方、書き込みの際には第1の終端可変抵抗の抵抗値を小さくし、メモリに与えられる信号波形の歪みを抑制する。

## 【0087】

請求項6に記載のデータバスによれば、請求項4及び請求項5のいずれか一つに記載のデータバスにおいて、第2の終端可変抵抗の抵抗値が、書き込みの際と読み出しの際とで、その各々の動作に適した値を探ることで、当該データバスは、読み出し、書き込みのいずれの動作においても、信頼性の高いデータの転送を可能とする。

## 【0088】

請求項7に記載のデータバスによれば、請求項6記載のデータバスにおいて、書き込み際には第2の終端可変抵抗の値を無限大にすることで第1の終端可変抵抗の抵抗値のみを機能させ、メモリに与えられるデータを表す信号波形の歪みを効果的に抑制する。他方、読み出しの際には第1の終端可変抵抗の値を無限大にすることで第2の終端可変抵抗の抵抗値のみを機能させ、メモリコントローラに与えられる波形の歪みを抑制する。

## 【図面の簡単な説明】

10

20

30

40

50

【図1】実施の形態1に係るメモリシステムの構成を示す図である。

【図2】実施の形態1に係るメモリシステムの構成を示す図である。

【図3】実施の形態1に係るメモリシステムの動作を示すタイミングチャートである。

【図4】実施の形態1に係るメモリシステムの変形例を示す図である。

【図5】実施の形態2に係るメモリシステムにおける終端可変抵抗の構成の一例を示す図である。

【図6】実施の形態3に係るメモリシステムの動作を示すタイミングチャートである。

【図7】実施の形態4に係るメモリシステムにおける終端可変抵抗の構成の一例を示す図である。

【図8】実施の形態5に係るメモリシステムの構成を示す図である。

【図9】実施の形態5に係るメモリシステムの動作の一例を示すタイミングチャートである。

【図10】実施の形態6に係るメモリシステムにおける終端可変抵抗の構成の一例を示す図である。

【図11】実施の形態7に係るメモリシステムの構成を示す図である。

【図12】実施の形態7に係るメモリシステムの構成を示す図である。

【図13】実施の形態8に係るメモリシステムの構成を示す図である。

【図14】実施の形態8に係るメモリシステムの構成を示す図である。

【図15】従来のメモリシステムの構成を示す図である。

【図1.6】従来のメモリシステムの構成を示す図である。

#### 【符号の説明】

[ 1 9 5 9 ] 說 明

10 セミリゴントローリ、11 アドレステコマントバス、12 リーフバス、13 クロッククライン、20, 20a, 20b RTCライン、21 RSCライン、Rt1, Rt2 終端抵抗、Rs1, Rs2 直列抵抗、VRt, VRt1, VRt2 終端可変抵抗、VRs 直列可変抵抗。

【 図 1 】

【 図 2 】

〔 図 3 〕

【 四 4 】

【 四 5 】

【 図 7 】

〔 四 8 〕

20a:第1のRTCライン

20b:第2のRTCライン

【 四 6 】

【 図 9 】

【図10】

【図12】

【図11】

【図13】

【図14】

【図16】

【図15】