(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5527225号

(P5527225)

(45) 発行日 平成26年6月18日(2014.6.18)

(24) 登録日 平成26年4月25日(2014.4.25)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 616V

H01L 21/28 (2006.01)

H01L 29/78 616U

H01L 29/417 (2006.01)

H01L 21/28 301R

H01L 29/50 M

H01L 21/28 301B

請求項の数 2 (全 11 頁)

(21) 出願番号

特願2011-5488 (P2011-5488)

(22) 出願日

平成23年1月14日(2011.1.14)

(62) 分割の表示

特願2008-293043 (P2008-293043)

の分割

原出願日 平成20年11月17日(2008.11.17)

(65) 公開番号

特開2011-86955 (P2011-86955A)

(43) 公開日

平成23年4月28日(2011.4.28)

審査請求日 平成23年1月14日(2011.1.14)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(74) 代理人 100109656

弁理士 三反崎 泰司

(74) 代理人 100130915

弁理士 長谷部 政男

(74) 代理人 100155376

弁理士 田名網 孝昭

(72) 発明者 德永 和彦

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタおよび表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

チャネルを形成する酸化物半導体膜と、

前記酸化物半導体膜の一方の側にゲート絶縁膜を介して配設されたゲート電極と、

ソース電極およびドレイン電極として前記酸化物半導体膜に接して形成され、前記酸化物半導体膜の側から順に、第1金属層、第2金属層および第3金属層をそれぞれ積層してなる一対の電極と、

前記酸化物半導体膜のチャネル上に設けられた保護膜とを備え、

前記第1金属層は、金(Au), 水銀(Hg)または銀(Ag)により構成され、

前記第2金属層はアルミニウム(Al)、前記第3金属層はチタン(Ti)によりそれぞれ構成され、かつ 10

前記第1金属層は、前記保護膜から露出した前記酸化物半導体膜の表面および側面を覆つて形成されている

薄膜トランジスタ。

## 【請求項 2】

表示素子と、前記表示素子を駆動するための薄膜トランジスタを備え、

前記薄膜トランジスタは、

チャネルを形成する酸化物半導体膜と、

前記酸化物半導体膜の一方の側にゲート絶縁膜を介して配設されたゲート電極と、

ソース電極およびドレイン電極として前記酸化物半導体膜に接して形成され、前記酸化 20

物半導体膜の側から順に、第1金属層、第2金属層および第3金属層をそれぞれ積層してなる一対の電極と、

前記酸化物半導体膜のチャネル上に設けられた保護膜とを備え、

前記第1金属層は、金(Au)、水銀(Hg)または銀(Ag)により構成され、

前記第2金属層はアルミニウム(Al)、前記第3金属層はチタン(Ti)によりそれぞれ構成され、かつ

前記第1金属層は、前記保護膜から露出した前記酸化物半導体膜の表面および側面を覆って形成されている

表示装置。

#### 【発明の詳細な説明】

10

#### 【技術分野】

#### 【0001】

本発明は、酸化物半導体膜を用いた薄膜トランジスタおよびこれを用いた表示装置に関する。

#### 【背景技術】

#### 【0002】

近年、酸化物を主成分とした半導体（以下、酸化物半導体という）を活性層に用いた薄膜トランジスタ（TFT：Thin Film Transistor）が注目されている。酸化物半導体は、液晶ディスプレイなどに一般的に用いられているアモルファスシリコン(-Si)と比較して、電子移動度が大きく、優れた電気特性を有することがわかっている。このような酸化物半導体としては、酸化亜鉛(ZnO)を主成分としたもの（特許文献1参照）や、In-M-Zn-O（Mはガリウム(Ga)、アルミニウム、鉄(Fe)のうちの少なくとも1種）を主成分としたもの（特許文献2参照）等が提案されている。特許文献2の薄膜トランジスタでは、酸化物半導体上に形成されるソース電極およびドレイン電極を、特定の仕事関数を有する金属で構成することにより、高いオンオフ比を実現している。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【特許文献1】特開2002-76356号公報

30

【特許文献2】特開2007-134496号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

しかしながら、上記のような酸化物半導体は、製造時や動作時などにおいて経時的に酸素が脱離してしまい、これにより、薄膜トランジスタの電流・電圧特性が劣化して、信頼性の悪化を招いていた。

#### 【0005】

本発明はかかる問題点に鑑みてなされたもので、その目的は、電気特性の劣化を抑制して信頼性を向上させることが可能な薄膜トランジスタおよびこれを用いた表示装置を提供することにある。

40

#### 【課題を解決するための手段】

#### 【0006】

本発明の薄膜トランジスタは、チャネルを形成する酸化物半導体膜と、酸化物半導体膜の一方の側にゲート絶縁膜を介して配設されたゲート電極と、ソース電極およびドレイン電極として酸化物半導体膜に接して形成され、酸化物半導体膜の側から順に、第1金属層、第2金属層および第3金属層をそれぞれ積層してなる一対の電極と、酸化物半導体膜のチャネル上に設けられた保護膜とを備えている。ここで、第1金属層は、金(Au)、水銀(Hg)または銀(Ag)により構成され、第2金属層はアルミニウム(Al)、前記第3金属層はチタン(Ti)によりそれぞれ構成され、かつ第1金属層は、保護膜から露出した酸化物半導体膜の表面および側面を覆って形成されている。

50

## 【0007】

本発明の薄膜トランジスタでは、酸化物半導体膜に接する一対の電極が第1金属層と第2金属層とを積層してなり、酸化物半導体膜に接する第1金属層が、モリブデンよりも大きなイオン化工エネルギーを有する金属、すなわち酸化されにくい金属により構成されている。ここで仮に、酸化物半導体膜に接する金属層が、モリブデンよりもイオン化工エネルギーの小さい、すなわち酸化され易い金属により構成されている場合、金属層の酸化に伴って、酸化物半導体膜中の酸素が金属層の側へ取り込まれ易くなる。このため、酸化され易い金属が酸化物半導体膜に接していると、酸化物半導体膜中の酸素が脱離して欠損し、これによりキャリアが発生し易くなる。従って、酸化物半導体膜に接する第1金属層が上記のような酸化されにくい金属で構成されることにより、酸化物半導体膜において酸素の欠損によるキャリアの発生が抑制される。

10

## 【0008】

本発明の表示装置は、表示素子と上記本発明の薄膜トランジスタとを備えたものである。

## 【発明の効果】

## 【0009】

本発明の薄膜トランジスタおよび表示装置によれば、酸化物半導体膜に接する一対の電極を積層構造とし、酸化物半導体膜側の第1金属層をモリブデンよりも大きなイオン化工エネルギーを有する金属により構成したので、酸素脱離によるキャリアの発生を抑制することができる。これにより、電気特性の劣化を抑制して信頼性を向上させることが可能となる。

20

## 【図面の簡単な説明】

## 【0010】

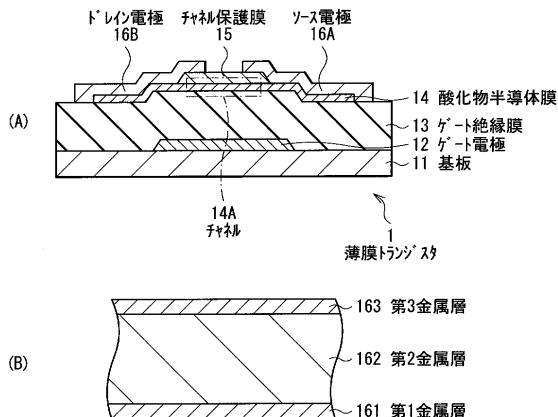

【図1】本発明の一実施の形態に係る薄膜トランジスタの断面構造を表すものである。

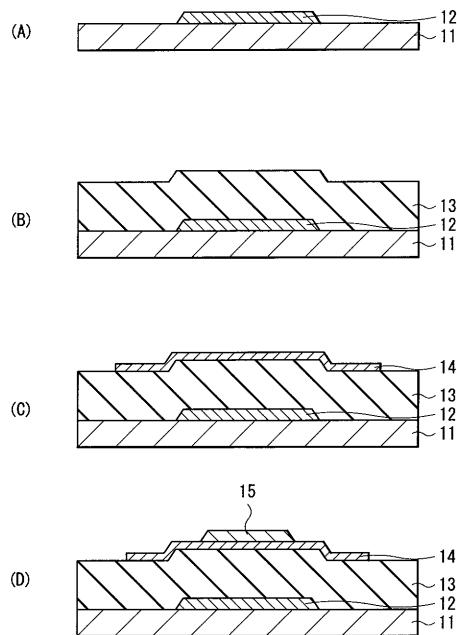

【図2】図1に示した薄膜トランジスタの製造方法を工程順に示す図である。

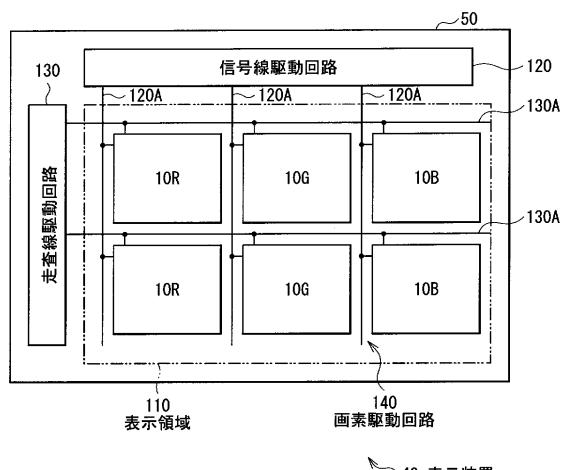

【図3】図1に示した薄膜トランジスタを用いた表示装置の回路構成を示す図である。

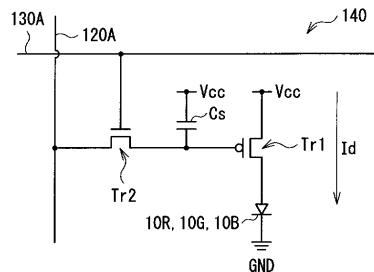

【図4】図3に示した画素駆動回路の一例を表す等価回路図である。

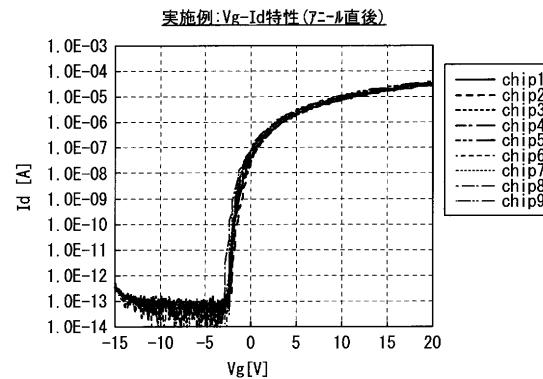

【図5】実施例のアニール直後のVg - Id特性を示す図である。

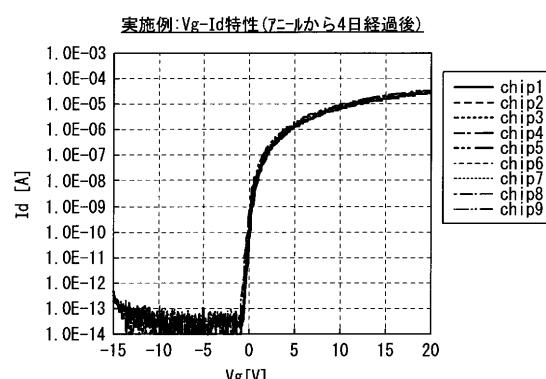

【図6】実施例のアニールから4日経過後のVg - Id特性を示す図である。

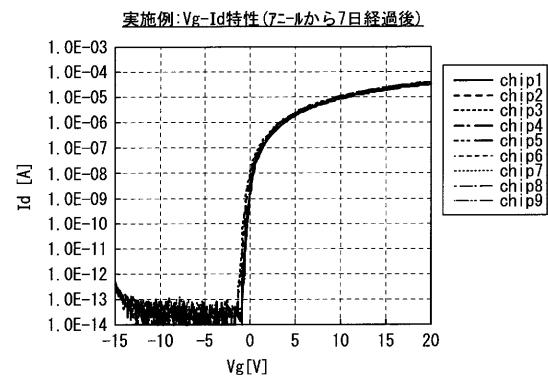

【図7】実施例のアニールから7日経過後のVg - Id特性を示す図である。

30

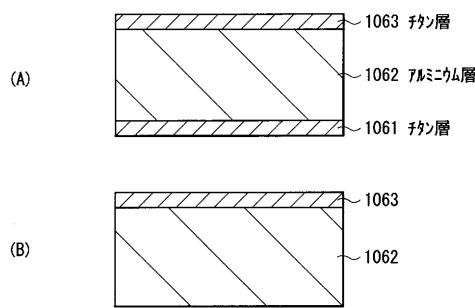

【図8】比較例1, 2のソース電極およびドレイン電極の積層構造を表す図である。

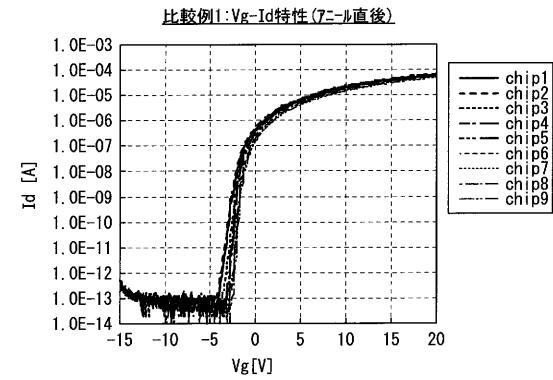

【図9】比較例1のアニール直後のVg - Id特性を示す図である。

【図10】比較例1のアニールから4日経過後のVg - Id特性を示す図である。

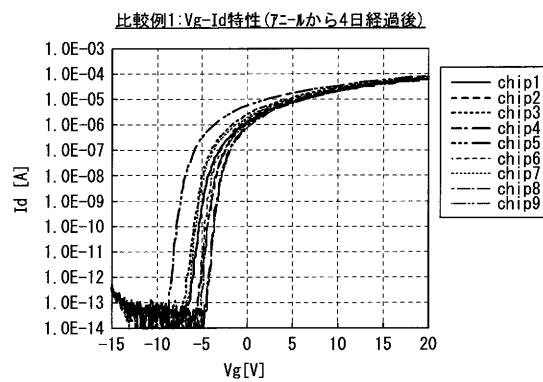

【図11】比較例1のアニールから7日経過後のVg - Id特性を示す図である。

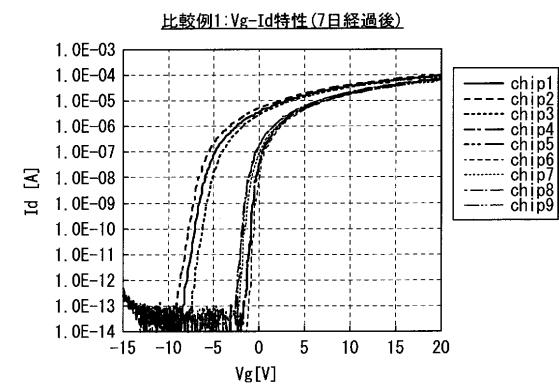

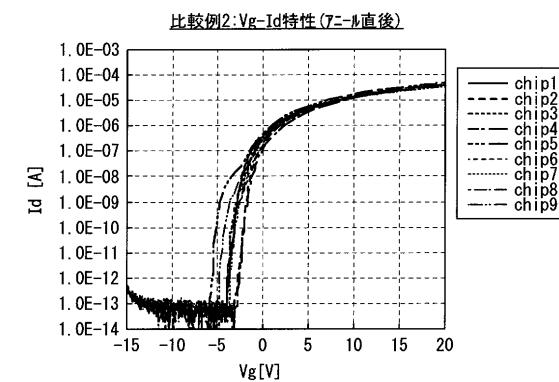

【図12】比較例2のアニール直後のVg - Id特性を示す図である。

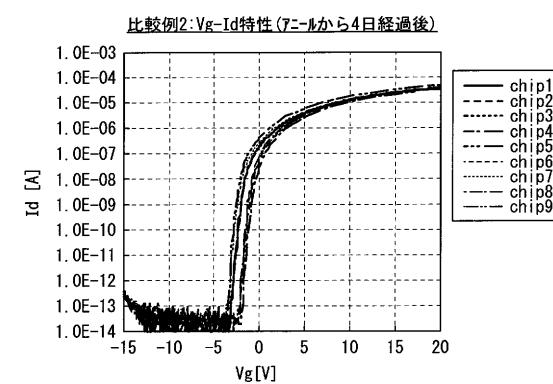

【図13】比較例2のアニールから4日経過後のVg - Id特性を示す図である。

【図14】比較例2のアニールから7日経過後のVg - Id特性を示す図である。

## 【発明を実施するための最良の形態】

## 【0011】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

40

## 【0012】

## [薄膜トランジスタの構成]

図1(A)は、本発明の一実施の形態に係る薄膜トランジスタ1の断面構造を表すものである。図1(B)は、図1(A)に示したソース電極16Aおよびドレイン電極16Bの層構造について説明するための図である。この薄膜トランジスタ1は、例えば液晶ディスプレイや有機EL(Electro Luminescence)ディスプレイなどの表示駆動を行う駆動素子として機能し、例えばボトムゲート型の構造(逆スタガー構造)を有している。

## 【0013】

薄膜トランジスタ1は、ガラスやプラスチックなどよりなる基板11上の選択的な領域にゲート電極12を有しており、このゲート電極12と基板11とを覆うように、ゲート

50

絶縁膜13が形成されている。ゲート絶縁膜13上には酸化物半導体膜14が設けられ、酸化物半導体膜14のゲート電極12に対応する領域にチャネル14Aが形成される。この酸化物半導体膜14に形成されるチャネル14Aの直上には、チャネル保護膜15が設けられている。チャネル保護膜15から露出した酸化物半導体膜15を覆うように、ソース電極16Aおよびドレイン電極16Bが所定のパターンで配設されている。

#### 【0014】

ゲート電極12は、薄膜トランジスタ1にゲート電圧を印加するための電極である。このゲート電極12は、例えばモリブデン(Mo)などから構成されている。

#### 【0015】

ゲート絶縁膜13は、シリコン酸化膜、シリコン窒化膜、シリコン窒化酸化膜および酸化アルミニウム膜等により構成されている。10

#### 【0016】

酸化物半導体膜14は、酸化物半導体を主成分として構成され、ソース電極16Aとドレイン電極16Bとの間に電流を生じさせるチャネル14Aを形成するものである。酸化物半導体としては、例えば酸化亜鉛や、In-M-Zn-O(Mはガリウム、アルミニウム、鉄のうちの少なくとも1種)等が挙げられる。

#### 【0017】

チャネル保護膜15は、酸化物半導体膜14のチャネル14Aの損傷を防止すると共に、酸化物半導体膜14中へ水素などが浸入することを防ぐ役割を果たしている。また、ソース電極16Aおよびドレイン電極16Bを形成する際のレジスト剥離液などから、チャネル14Aを保護する役割をも果たしている。このようなチャネル保護膜15は、例えばシリコン窒化膜やシリコン酸化膜などから構成されている。20

#### 【0018】

ソース電極16Aおよびドレイン電極16Bはいずれも、複数の金属層が積層した多層膜により構成されている。例えば図1(B)に示したように、第1金属層161、第2金属層162および第3金属層163の3層が積層した構造となっている。これらのうち第1金属層161は、酸化物半導体膜14との界面に沿って形成され、この第1金属層161上に第2金属層162および第3金属層163がこの順に形成されている。

#### 【0019】

第1金属層161は、例えばイオン化工エネルギーがモリブデンと同等またはモリブデンよりも大きい金属の単体または合金により構成され、厚みは、例えば30nm~50nmである。但し、イオン化工エネルギーとは、いわゆる第1イオン化工エネルギーを示し、モリブデンのイオン化工エネルギーは684KJ/mol程度である。このような第1金属層161を構成する金属としては、例えばモリブデン、水銀(Hg)、銀(Ag)、白金(Pt)、金(Au)などが挙げられる。なお、第1金属層161は、基板11の全面にわたって形成されていてもよいが、少なくとも、チャネル保護膜15から露出した酸化物半導体膜14の表面および側面を覆って形成されればよい。30

#### 【0020】

第2金属層162は、電気抵抗が小さく導電性に優れた金属材料、具体的にはアルミニウム(Al)、銅(Cu)などにより構成され、厚みは例えば300nm~1000nmである。40

#### 【0021】

第3金属層163は、第2金属層162の表面保護のために配設されるものであり、例えばチタンなどにより構成され、厚みは例えば30nm~50nmである。なお、ソース電極16Aおよびドレイン電極16Bにおいて、この第3金属層163は形成されていないともよく、すなわち第1金属層161および第2金属層162からなる2層構造であつてもよい。

#### 【0022】

##### [薄膜トランジスタの製造方法]

上記薄膜トランジスタ1は、例えば次のようにして製造することができる。すなわち、50

まず、図2(A)に示したように、基板11上の全面にスパッタリング法や蒸着法により金属薄膜を形成したのち、この金属薄膜を、例えばフォトリソグラフィ法を用いて、ゲート電極12をパターニング形成する。

#### 【0023】

続いて、図2(B)に示したように、基板11およびゲート電極12上を覆うようにゲート絶縁膜13を、例えばプラズマCVD(Chemical Vapor Deposition; 化学気相成長)法を用いて形成する。

#### 【0024】

次いで、図2(C)に示したように、上述した材料および厚みからなる酸化物半導体膜14を、例えばスパッタリング法を用いて形成する。このとき、酸化物半導体として酸化インジウムガリウム亜鉛(IGZO)を用いた場合、IGZOのセラミックをターゲットとしたDCスパッタ法を行い、アルゴン(Argon)と酸素(O<sub>2</sub>)の混合ガスを用いたプラズマ放電により、酸化物半導体膜14を形成する。但し、プラズマ放電を行う前に、真空容器内の真圧度が、例えば $1 \times 10^{-4}$ Pa以下になるまで排気したのち、アルゴンと酸素の混合ガスを導入するようにするとよい。こののち、形成した酸化物半導体膜14を、例えばフォトリソグラフィ法を用いてパターニングする。

10

#### 【0025】

続いて、図2(D)に示したように、上述した材料よりなるチャネル保護膜を例えばスパッタリング法を用いて形成したのち、例えばフォトリソグラフィ法を用いて、チャネル14Aに対応して形成されるように、パターニングする。

20

#### 【0026】

次いで、酸化物半導体膜14上にソース電極16Aおよびドレイン電極16Bを形成する。このとき、酸化物半導体膜14およびチャネル保護膜15の形成された領域を覆うように、第1金属層161を例えばスパッタリング法を用いて形成する。こののち、第1金属層161上に第2金属層162および第3金属層163をこの順に形成する。続いて、第1金属層161、第2金属層162および第3金属層163を、例えばフォトリソグラフィ法を用いてパターニングすることにより、ソース電極16Aおよびドレイン電極16Bを形成する。

#### 【0027】

最後に、ソース電極16Aおよびドレイン電極16Bを形成した基板11に対し、酸素雰囲気においてアニール処理を施す。これにより、酸化物半導体膜14中の酸素の欠損を防ぎ、良好な電気特性を確保し易くなる。以上により、図1(A)に示した薄膜トランジスタ1を完成する。

30

#### 【0028】

##### [薄膜トランジスタの作用・効果]

本実施の形態の薄膜トランジスタ1では、図示しない配線層を通じてゲート電極12に所定のしきい値電圧以上の電圧(ゲート電圧V<sub>g</sub>)が印加されると、酸化物半導体膜14にチャネル14Aが形成され、ソース電極16Aとドレイン電極16Bとの間に電流(ドレイン電流I<sub>d</sub>)が流れ、トランジスタとして機能する。

#### 【0029】

40

ここで、本実施の形態では、チャネル14Aを形成する酸化物半導体膜14上には、ソース電極16Aおよびドレイン電極16Bが形成されている。これらソース電極16Aおよびドレイン電極16Bはそれぞれ、酸化物半導体膜14の側から第1金属層161、第2金属層162および第3金属層163を積層してなり、第1金属層161はイオン化工エネルギーがモリブデンと同等以上の金属で構成されている。すなわち、酸化物半導体膜14に接する第1金属層161が酸化されにくい金属により構成されている。

#### 【0030】

このとき逆に、酸化物半導体膜14に接する金属層が、モリブデンよりもイオン化工エネルギーの小さい、すなわち酸化され易い金属により構成されている場合、酸化物半導体膜14中の酸素は、金属層の酸化に伴って金属層の側へ取り込まれてしまう。このため、酸

50

素が酸化物半導体膜14の外部へ脱離し、酸素の欠損により酸化物半導体膜14の内部ではキャリアが発生してしまう。

#### 【0031】

従って、本実施の形態のように、酸化物半導体膜14に接する第1金属層161が上記のような酸化されにくい金属で構成されていることにより、酸化され易い金属で構成されている場合に比べ、第1金属層161へ酸素が取り込まれにくくなる。よって、酸化物半導体膜14からの酸素の脱離が抑制され、酸化物半導体膜14において酸素の欠損によるキャリアの発生が抑制される。

#### 【0032】

以上のように、薄膜トランジスタ1では、酸化物半導体膜14に接するソース電極16Aおよびドレイン電極16Bを積層構造とし、酸化物半導体膜14に接する第1金属層161をイオン化工エネルギーがモリブデンと同等以上の金属により構成している。従って、酸化物半導体膜14中において、酸素の欠損によるキャリアの発生を抑制することができる。これにより、電気特性の劣化を抑制して信頼性を向上させることが可能となる。

#### 【0033】

また、本実施の形態では、ソース電極16Aおよびドレイン電極16Bにおいて、第1金属層161上に更に第2金属層162が設けられ、この第2金属層162が導電性の良好な金属により構成されている。これにより、ソース電極16Aおよびドレイン電極16Bを第1金属層161の単層により構成した場合よりも、電気抵抗を減らして、ソース・ドレインおよび配線としての機能を向上させることができる。

#### 【0034】

特に、第1金属層161がモリブデンにより構成されている場合には、第1金属層161の表面（酸化物半導体膜14側の面）のみが酸化され、酸化被膜が形成される。この場合、形成された酸化被膜が酸素バリア層として機能し、酸化物半導体膜14からの酸素の排出が抑制される。従って、第1金属層161をモリブデンにより構成した場合には、モリブデン自体が酸化されにくい金属であることに加え、上記のような酸化被膜による酸素バリア機能により、酸化物半導体膜14における酸素の欠損が効果的に抑制される。なお、表面の酸化のために第1金属層161の側へ取り込まれる酸素は極微量であるため、薄膜トランジスタの電気特性は十分に維持される。

#### 【0035】

##### [表示装置の構成]

図3は、薄膜トランジスタ1を駆動素子として用いた表示装置（表示装置40）の回路構成を示すものである。表示装置40は、例えば液晶ディスプレイや有機ELディスプレイなどであり、例えば駆動パネル50上に、マトリクス状に配設された複数の画素10R, 10G, 10Bと、これらの画素10R, 10G, 10Bを駆動するための駆動回路とが形成されたものである。画素10R, 10G, 10Bはそれぞれ、赤色（R:Red）、緑色（G:Green）および青色（B:Blue）の色光を発する液晶表示素子や有機EL素子などである。これらのうち隣り合う3つの画素10R, 10G, 10Bが一つのピクセルを構成し、複数のピクセルにより表示領域110が形成されている。駆動回路としては、例えば映像表示用のドライバである信号線駆動回路120および走査線駆動回路130と、画素駆動回路140とが駆動パネル50上に配設されている。なお、駆動パネル50には、図示しない封止パネルが貼り合わせられ、この封止パネルにより画素10R, 10G, 10Bおよび上記駆動回路が封止されている。

#### 【0036】

図4は、画素駆動回路140の等価回路図である。画素駆動回路140は、上記薄膜トランジスタ1として、トランジスタTr1, Tr2が配設されたアクティブ型の駆動回路である。トランジスタTr1, Tr2の間にはキャパシタCsが設けられ、第1の電源ライン（Vcc）および第2の電源ライン（GND）の間において、画素10R（または画素10G, 10B）がトランジスタTr1に直列に接続されている。このような画素駆動回路140では、列方向に信号線120Aが複数配置され、行方向に走査線130Aが複

10

20

30

40

50

数配置されている。各信号線 120A は、信号線駆動回路 120 に接続され、この信号線駆動回路 120 から信号線 120A を介してトランジスタ Tr 2 のソース電極に画像信号が供給されるようになっている。各走査線 130A は走査線駆動回路 130 に接続され、この走査線駆動回路 130 から走査線 130A を介してトランジスタ Tr 2 のゲート電極に走査信号が順次供給されるようになっている。

#### 【0037】

##### (実施例)

上記実施の形態の実施例として、第 1 金属層 161 にモリブデン（膜厚 50 nm）、第 2 金属層 162 にアルミニウム（膜厚 500 nm）および第 3 金属層 163 にチタン（膜厚 50 nm）を用いた薄膜トランジスタ 1 を作製した。このとき、ゲート電極 12 にモリブデン、ゲート絶縁膜 13 に膜厚 200 nm の酸化シリコン（SiO）、酸化物半導体膜 14 に In-Ga-Zn-O、およびチャネル保護膜 15 に膜厚 200 nm の酸化シリコン（SiO）をそれぞれ用いた。また、ソース電極 16A およびドレイン電極 16B 形成後のアニール処理の諸条件については、酸素（O<sub>2</sub>）および窒素（N<sub>2</sub>）を含む雰囲気において酸素濃度を約 40%、熱処理温度を 300°C、処理時間を 2 時間とした。10

#### 【0038】

このような薄膜トランジスタ 1 について、経時的な電気特性の変化を調べるため、アニール処理直後、アニール処理から 4 日経過後および 7 日経過後のゲート電圧 V<sub>g</sub> (V) に対するドレイン電流 I<sub>d</sub> (A) の変化（以下、V<sub>g</sub>-I<sub>d</sub> 特性という）について測定した。これらの結果を図 5～図 7 に示す。なお、図 5～図 7 には、同様の条件で作製した計 9 個の薄膜トランジスタ 1 (chip 1～chip 9) の各結果についてまとめて示している。20

#### 【0039】

また、上記実施例の比較例 1, 2 として、ソース電極およびドレイン電極として酸化物半導体膜 14 に接する金属層に、モリブデンよりもイオン化工エネルギーの小さい金属を用いた薄膜トランジスタを作製した。但し、比較例 1 では、図 8 (A) に示したように、酸化物半導体膜 14 の側から順に、チタン層 1061 (膜厚 50 nm)、アルミニウム層 1062 (膜厚 500 nm) およびチタン層 1063 (膜厚 50 nm) を積層した 3 層構造とした。一方、比較例 2 では、酸化物半導体膜 14 の側から順に、アルミニウム層 1062 (膜厚 500 nm) およびチタン層 1063 (膜厚 50 nm) を積層した 2 層構造とした。すなわち、酸化物半導体膜 14 に接する金属層が、比較例 1 ではチタン、比較例 2 ではアルミニウムによりそれぞれ構成されている（チタンのイオン化工エネルギー > アルミニウムのイオン化工エネルギー）。なお、このような積層構造を有するソース電極およびドレイン電極以外の構成は、上記実施例と同様とした。30

#### 【0040】

これらの比較例 1, 2 の薄膜トランジスタについて、上記実施例と同様、アニール処理後の各時点におけるゲート電圧 V<sub>g</sub> (V) に対するドレイン電流 I<sub>d</sub> (A) の変化について測定した。比較例 1 の結果を図 9～図 11、比較例 2 の結果を図 12～図 14 にそれぞれ示す。

#### 【0041】

図 9～図 11 に示したように、チタン層 1061 を酸化物半導体膜 14 に接して形成した比較例 1 では、V<sub>g</sub>-I<sub>d</sub> 特性が、アニール処理直後から 7 日経過後にかけて経時に劣化しており、また chip 1～9 の間ににおいてばらつきが生じた。また、図 12～図 14 に示したように、アルミニウム層 1062 を酸化物半導体膜 14 に接して形成した比較例 2 では、V<sub>g</sub>-I<sub>d</sub> 特性において、比較例 1 ほど大きな経時的劣化はみられなかったが、chip 1～9 の間ににおいてばらつきが生じた。従って、比較例 1, 2 の薄膜トランジスタでは、ディスプレイなどのパネルに搭載する前の段階で電気特性が劣化し易い。40

#### 【0042】

これに対し、図 5～図 7 に示したように、酸化物半導体膜 14 に接する第 1 金属層 161 をモリブデンにより構成した実施例では、アニール処理直後から 7 日経過後まで、V<sub>g</sub>-I<sub>d</sub> 特性がほぼ一定に保持され、経時的な変動が極めて小さいことがわかる。また、ch50

ip 1 ~ 9 の間においても Vg - Id 特性にほとんど差は見られなかった。

**【0043】**

上記結果から、酸化物半導体膜 14 と接する金属層を、モリブデンと同等以上のイオン化工エネルギーを有する金属、すなわち酸化されにくい金属で構成することにより、電気特性の劣化を抑制可能であることが示された。

**【0044】**

(変形例)

次に、本発明の変形例に係る薄膜トランジスタについて説明する。本変形例の薄膜トランジスタは、ソース電極およびドレイン電極を構成する積層構造のうち、酸化物半導体膜 14 に接する金属層（以下、単に第1金属層という）の構成材料以外は、上記実施の形態の薄膜トランジスタ 1 と同等である。このため、本変形例の薄膜トランジスタでは図示を省略し、各構成要素については上記実施の形態の薄膜トランジスタ 1 の構成要素と同一の符号を用い、適宜説明を省略する。

**【0045】**

本変形例の第1金属層は、酸素バリア性を有する金属材料、具体的には、次に挙げるような金属の窒化物または窒化珪化物により構成されている。例えば、この第1金属層に用いられる金属としては、タンタル(Ta)、バナジウム(V)、チタン、ジルコニウム(Zr)、タングステン(W)、銅(Cu)、アルミニウム、ルテニウム(Ru)、イリジウム(Ir)、ニッケル(Ni)、コバルト(Co)、白金などが挙げられる。

**【0046】**

このように、酸化物半導体膜 14 に接する第1金属層は、上記実施の形態で説明したような所定のイオン化工エネルギーを有する金属に限定されず、酸素バリア性を有する金属の窒化物または窒化珪化物であってもよい。この場合、第1金属層の酸素バリア機能により、酸化物半導体膜 14 から外部へ酸素が脱離することが抑制される。従って、酸化物半導体膜 14 の酸素の欠損によるキャリアの発生を抑制することができ、上記実施の形態と同様の効果を得ることが可能となる。

**【0047】**

以上、実施の形態および変形例を挙げて本発明を説明したが、本発明は上記実施の形態等に限定されず、種々の変形が可能である。例えば、上記実施の形態等では、ソース電極およびドレイン電極を、第1金属層、第2金属層および第3金属層の3層からなる積層構造として説明したが、3層に限らず2層あるいは4層以上であってもよい。2層あるいは4層以上で構成した場合も、酸化物半導体膜に接する金属層が、上述したような所定のイオン化工エネルギーを有する金属もしくは酸素バリア性を有する金属により構成されれば、本発明と同等の効果を得ることができる。

**【0048】**

また、上記実施の形態等では、薄膜トランジスタとして、ボトムゲート構造を例に挙げて説明したが、これに限定されず、トップゲート構造であってもよい。

**【符号の説明】**

**【0049】**

1...薄膜トランジスタ、11...基板、12...ゲート電極、13...ゲート絶縁膜、14...酸化物半導体膜、15...チャネル保護膜、16A...ソース電極、16B...ドレイン電極、161...第1金属層、162...第2金属層、163...第3金属層、40...表示装置、50...駆動パネル、10R, 10G, 10B...画素、110...表示領域、120...信号線駆動回路、130...走査線駆動回路、140...画素駆動回路、Tr1, Tr2...トランジスタ。

10

20

30

40

【 図 1 】

【図2】

【図3】

〔 四 〕

【図5】

〔 6 〕

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

審査官 鈴木 聰一郎

- (56)参考文献 特開2007-123861(JP, A)

国際公開第2007/120010(WO, A1)

特表2009-533884(JP, A)

特開2006-013433(JP, A)

特開2005-181973(JP, A)

特開2008-172243(JP, A)

特開2007-250983(JP, A)

特開2006-186319(JP, A)

(58)調査した分野(Int.Cl., DB名)

- H01L 21/28 - 21/288

H01L 21/329

H01L 21/336

H01L 21/44 - 21/445

H01L 29/40 - 29/49

H01L 29/786

H01L 29/872