(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4236584号

(P4236584)

(45) 発行日 平成21年3月11日(2009.3.11)

(24) 登録日 平成20年12月26日(2008.12.26)

(51) Int.Cl.

H03M 1/12 (2006.01)

F 1

H03M 1/12

C

請求項の数 2 (全 13 頁)

(21) 出願番号 特願2003-555799 (P2003-555799)

(86) (22) 出願日 平成14年12月6日 (2002.12.6)

(65) 公表番号 特表2005-514816 (P2005-514816A)

(43) 公表日 平成17年5月19日 (2005.5.19)

(86) 國際出願番号 PCT/US2002/039258

(87) 國際公開番号 WO2003/055207

(87) 國際公開日 平成15年7月3日 (2003.7.3)

審査請求日 平成17年11月22日 (2005.11.22)

(31) 優先権主張番号 60/339,544

(32) 優先日 平成13年12月11日 (2001.12.11)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 501263810

トムソン ライセンシング

Thomson Licensing

フランス国, エフ-92100 プロ

ニュ ビヤンクール, ケ アルフォンス

ル ガロ, 46番地

46 Quai A. Le Gallio

, F-92100 Boulogne-

Billancourt, France

(74) 代理人 100115864

弁理士 木越 力

(74) 代理人 100121175

弁理士 石井 たかし

最終頁に続く

(54) 【発明の名称】信号を処理する装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

信号を処理する装置であって、

時間軸で整合のとれた第1および第2のアナログ信号を、第1および第2のデジタル信号にそれぞれ変換して、第1の時間間隔中に前記第1のデジタル信号を出力し、第2の時間間隔中に前記第2のデジタル信号を出力するための、アナログ・デジタル変換手段と、

前記第1の時間間隔中にある前記第1のデジタル信号の値の半分を前記第2の時間間隔中にある前記第1のデジタル信号の値の半分に加算して第1の濾波済み信号を生成し、

前記第1の時間間隔中にある前記第2のデジタル信号の値の半分を前記第2の時間間隔中にある第2のデジタル信号の値の半分に加算して第2の濾波済み信号を生成し、

第3の時間間隔中に前記第1および第2の濾波済み信号を、時間軸で整合のとれた形式で出力するための、デジタル濾波手段と、

を備える、前記装置。

## 【請求項 2】

信号を処理する方法であって、

時間軸で整合のとれた第1および第2のアナログ信号を、第1および第2のデジタル信号にそれぞれ変換するステップと、

第1の時間間隔中に前記第1のデジタル信号を出力するステップと、

10

20

第2の時間間隔中に前記第2のデジタル信号を出力するステップと、

前記第1および第2のデジタル信号を濾波して、第1および第2の濾波信号をそれぞれ出力するステップと、を含み

前記第1および第2の濾波信号をそれぞれ出力するステップは、

前記第1の時間間隔中にある前記第1のデジタル信号の値の半分を前記第2の時間間隔中にある前記第1のデジタル信号の値の半分に加算して第1の濾波済み信号を生成するステップと、

前記第1の時間間隔中にある前記第2のデジタル信号の値の半分を前記第2の時間間隔中にある第2のデジタル信号の値の半分に加算して第2の濾波済み信号を生成するステップと、

第3の時間間隔中に前記第1および第2の濾波済み信号を、時間軸で整合のとれた形式で出力するステップと、

を含む、前記方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、ビデオおよび／または音声システムなどのシステムにおける信号処理に関し、より詳細には、このようなシステムでアナログ・デジタル変換器（A D C：Analog - to - Digital Converter）を時分割するための構成であって、特に出力信号間の時間軸における整合（time-alignment）をもたらす装置構成に関する。

【背景技術】

【0002】

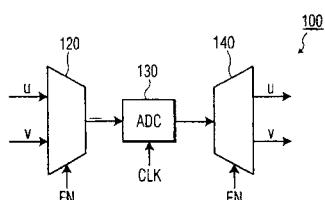

複数の入力信号のためにアナログ・デジタル変換器（A D C）を時分割（タイム・シェアリング）して利用することは、ビデオおよび／または音声システムなどのシステムでA D Cの数を減らす方法として周知である。このようなシステムにおいて、アナログ・デジタル変換器（A D C）を共有する技法の1つは、単純な多重化（m u l t i p l e x i n g）を含むものである。例えば、図1に、単純な多重化を利用する多重化アナログ・デジタル変換器（m u l t i p l e x e d A D C：多重化A D C）構成100を示す。図1では、マルチプレクサ120が、アナログのUとVの入力信号を同時に受け取り、イネーブル（E N）信号に応答して切り換わり、受け取ったアナログのUとVの入力信号のうちの選択された方を交互に出力する。アナログ・デジタル変換器（A D C）130が、マルチプレクサ120からアナログのUとVの出力信号を受け取り、受け取ったUとVの信号をクロック（C L K）信号に応答してデジタル化する。クロック（C L K）信号の各間隔は、単一のクロック・サイクル、即ち時間間隔を定める。図1では、C L K信号の周波数は、例えばE N信号の周波数の2倍である。デマルチプレクサ140が、A D C130から出力されたデジタルのUとVの信号を受け取り、E N信号に応答して切り換わり、デジタルのUとVの信号を出力する。下表1に、多重化A D C構成100の例示的な動作を示す。

【0003】

10

20

30

40

【表1】

| クロック・サイクル | 1  | 2  | 3  | 4  | 5  |

|-----------|----|----|----|----|----|

| アナログU     | 45 | 46 | 47 | 48 | 49 |

| アナログV     | 75 | 76 | 77 | 78 | 79 |

| 多重化位置     | U  | V  | U  | V  | U  |

| ADC 出力    | 45 | 76 | 47 | 78 | 49 |

| 逆多重化済みU   | 45 | 45 | 47 | 47 | 49 |

| 逆多重化済みV   | -- | 76 | 76 | 78 | 78 |

10

## 【0004】

表1に示すように、デマルチブレクサ140からのUとVの出力信号（即ち、逆多重化済みU / 逆多重化済みV）は、マルチブレクサ120への対応する入力信号（即ち、アナログU / アナログV）に対して時間軸で整合がとれておらず、時間がずれている。言い換えれば、デマルチブレクサ140からのUとVの出力信号が、マルチブレクサ120への対応する入力信号に対して時間軸で整合がとれているクロック・サイクルは存在しない。例示および説明のために、表1には、アナログ・ディジタル変換器（ADC）130およびデマルチブレクサ140を介した信号遅延は、示されていないことに留意されたい。また、表1では、デマルチブレクサ140は、各クロック・サイクル中にU出力信号とV出力信号の両方を生成することにも留意されたい。これらのUとVの出力信号の一方は、現在のクロック・サイクル中にADC130から提供された信号であり、これらのUとVの信号の他方は、前のクロック・サイクル中にADC130から提供されたものである。

20

## 【0005】

多くの適用例では、表1に表すように出力信号間に時間軸上での整合関係がないことは、問題を生じない。しかし、あるシステムにおいては、このような時間軸上での整合関係が必要となる。例えば、ピクチャ・イン・ピクチャ（PIP: Picture In Picture）機能を提供するための集積回路（IC）を有する幾つかのデジタル・ビデオ・システムでは、出力信号間の時間軸上での整合が必要な場合がある。

30

## 【0006】

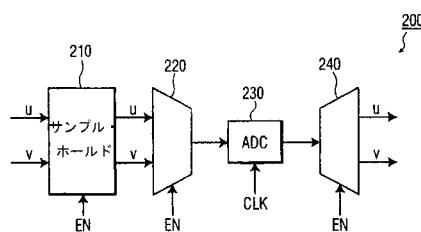

出力信号間の時間軸上での整合をもたらす技法の1つは、信号経路中で、アナログ・ディジタル変換器（ADC）への入力を提供するマルチブレクサの前にアナログのサンプル・ホールド回路を配置するものである。例えば、図2に、サンプル・ホールド回路（Sample and Hold circuit: サンプル・アンド・ホールド回路）を利用する多重化ADC構成200を示す。図2では、サンプル・ホールド（S and H）回路210が、アナログのUとVの信号を受け取り、次のイネーブル（EN）信号まで保持する。マルチブレクサ220が、保持されたアナログのUとVの信号をサンプル・ホールド回路210から同時に受け取り、EN信号に応答して切り換わり、受け取ったアナログのUとVの信号のうちの選択された方を交互に出力する。ADC230が、マルチブレクサ220からアナログのUとVの出力信号を受け取り、受け取ったUとVの信号をクロック（CLK）信号に応答してデジタル化する。CLK信号の各間隔は、単一のクロック・サイクルまたは時間間隔を定める。図2では、CLK信号の周波数は、例えばEN信号の周波数の2倍である。デマルチブレクサ240が、ADC230から出力されたデジタルのUとVの信号を受け取り、EN信号に応答して切り換わり、デジタルのUとVの信号を出力する。下表2に、多重化ADC構成200の例示的な動作を示す。

40

## 【0007】

50

【表2】

| クロック・サイクル | 1  | 2  | 3  | 4  | 5  |

|-----------|----|----|----|----|----|

| アナログU     | 45 | 46 | 47 | 48 | 49 |

| アナログV     | 75 | 76 | 77 | 78 | 79 |

| SアンドH U   | 45 | 45 | 47 | 47 | 49 |

| SアンドH V   | 75 | 75 | 77 | 77 | 79 |

| 多重化位置     | U  | V  | U  | V  | U  |

| ADC 出力    | 45 | 75 | 47 | 77 | 49 |

| 逆多重化済みU   | 45 | 45 | 47 | 47 | 49 |

| 逆多重化済みV   | -- | 75 | 75 | 77 | 77 |

10

## 【0008】

表2に示すように、デマルチプレクサ240からの出力信号（即ち、逆多重化済みU/逆多重化済みV）は、1クロック・サイクルおきに時間軸で整合がとれている。例えば、表2では、デマルチプレクサ240からの出力信号は、クロック・サイクル2およびクロック・サイクル4の間は、時間軸で整合がとれている。例示および説明のために、表2には、アナログ・ディジタル変換器（ADC）230およびデマルチプレクサ240を介した信号遅延は、示されていないことに留意されたい。また、表2では、デマルチプレクサ240は各クロック・サイクル中にU出力信号とV出力信号の両方を生成することにも留意されたい。これらのUとVの出力信号の一方は、現在のクロック・サイクル中にADC230から生成された信号であり、これらのUとVの信号の他方は、前のクロック・サイクル中にADC230から生成されたものである。

20

## 【0009】

図2の多重化ADC構成200は、ある程度の時間軸上での整合をもたらすものの、ICを短期間で設計するために使用される多くの標準セル・ライブラリ中では、サンプル・ホールド回路が利用できないという点で、問題がある。この結果、サンプル・ホールド回路は、設計中の特定のIC向けに設計しなければならないカスタム・アナログ・ブロックと考えられる。一般に、カスタム・アナログ・ブロックは、IC開発において追加の設計時間、費用、リスクを必要とする。

30

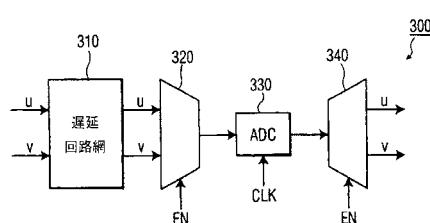

## 【0010】

時間軸上での整合をもたらす別の方法は、多重化アナログ・ディジタル変換器（多重化ADC）の前に、アナログ遅延回路網（アナログ遅延ネットワーク回路）を配置するものである。例えば、図3に、アナログ遅延回路網を利用する多重化ADC構成300を示す。図3では、アナログ遅延回路網310が、アナログのUとVの信号を受け取って出力するが、UとVの信号の一方は、他方の信号に対して（例えば、1クロック・サイクルの間）区別して遅延される。マルチプレクサ320は、アナログ遅延回路網310からアナログのUとVの信号を受け取り（即ち、UとVの信号の一方は遅延されている）、イネーブル（EN）信号に応答して切り換わり、受け取ったアナログのUとVの信号のうちの選択された方を交互に出力する。ADC330が、マルチプレクサ320からアナログのUとVの出力信号を受け取り、受け取ったUとVの信号をクロック（CLK）信号に応答してディジタル化する。CLK信号の各間隔は、单一のクロック・サイクル、即ち時間間隔を定める。図3では、CLK信号の周波数は、例えばEN信号の周波数の2倍である。デマルチプレクサ340が、ADC330から出力されたディジタルのUとVの信号を受け取り、EN信号に応答して切り換わり、ディジタルのUとVの信号を出力する。下表3に、

40

50

多重化 A D C 構成 3 0 0 の例示的な動作を示す。

【 0 0 1 1 】

【表 3】

| クロック・サイクル | 1  | 2  | 3  | 4  | 5  |

|-----------|----|----|----|----|----|

| アナログ U    | 45 | 46 | 47 | 48 | 49 |

| アナログ V    | 75 | 76 | 77 | 78 | 79 |

| 遅延回路網 U   | 45 | 46 | 47 | 48 | 49 |

| 遅延回路網 V   | -- | 75 | 76 | 77 | 78 |

| 多重化位置     | U  | V  | U  | V  | U  |

| ADC 出力    | 45 | 75 | 47 | 77 | 49 |

| 逆多重化済み U  | 45 | 45 | 47 | 47 | 49 |

| 逆多重化済み V  | -- | 75 | 75 | 77 | 77 |

10

20

【 0 0 1 2 】

表 3 に示すように、デマルチプレクサ 3 4 0 からの出力信号（即ち、逆多重化済み U / 逆多重化済み V ）は、図 2 のデマルチプレクサ 2 4 0 から生成された出力信号と同一である。即ち、デマルチプレクサ 3 4 0 からの出力信号は、1 クロック・サイクルおきに時間軸で整合がとれている。例えば、表 3 では、デマルチプレクサ 3 4 0 からの出力信号は、クロック・サイクル 2 およびクロック・サイクル 4 の間は、時間軸で整合がとれている。例示および説明のために、表 3 には、アナログ・ディジタル変換器 ( A D C ) 3 3 0 およびデマルチプレクサ 3 4 0 を介した信号遅延は、示されていないことに留意されたい。また、表 3 では、デマルチプレクサ 3 4 0 は、各クロック・サイクル中に U 出力信号と V 出力信号の両方を生成することにも留意されたい。これらの U と V の出力信号の一方は、現在のクロック・サイクル中に A D C 3 3 0 から提供された信号であり、これらの U と V の信号の他方は、前のクロック・サイクル中に A D C 3 3 0 から提供されたものである。

30

【 0 0 1 3 】

図 3 の多重化アナログ・ディジタル変換器（多重化 A D C ）構成 3 0 0 もある程度の時間軸上での整合をもたらすものの、2 つの入力経路の振幅およびグループ遅延特性が異なるために、望ましくない周波数応答作用における差違が生じる可能性があるという点で、問題がある。この問題は、構成要素の公差によるばらつきにより更に悪化する。

【 0 0 1 4 】

従って、前述の問題を回避し、時間軸で整合のとれた（即ち、同位置の、位置の揃った）出力信号を生成する多重化アナログ・ディジタル変換器（多重化 A D C ）構成が必要とされている。本発明は、これらおよび他の課題に対処するものである。

40

【発明の開示】

【 0 0 1 5 】

本発明によれば、音声および / またはビデオ・システムなどのシステムが、多重化アナログ・ディジタル変換器（多重化 A D C ）構成を備えている。この構成は、第 1 および第 2 のアナログ信号を第 1 および第 2 のデジタル信号にそれぞれ変換して、第 1 の時間間隔中に第 1 のデジタル信号を出力し、第 2 の時間間隔中に第 2 のデジタル信号を出力するための A D C を備えている。第 1 および第 2 のデジタル信号を濾波して第 1 および第 2 の濾波済み信号をそれぞれ生成し、第 3 の時間間隔中に第 1 および第 2 の濾波済み信号を時間的に整列された形式で出力するためのデジタル・フィルタが提供される。

50

## 【0016】

本発明の実施例に関する以下の説明を添付の図面と共に参照することにより、本発明に関する前述のおよび他の特徴、利点、並びにこれらを達成する方法がより明らかになり、本発明がよりよく理解されるであろう。

特許請求の範囲と実施例との対応関係を実施例で使われている参照符号を用いて示すと以下の通りである。

## (請求項1)

信号を処理する装置であって、

第1および第2のアナログ信号を、第1および第2のデジタル信号にそれぞれ変換して、第1の時間間隔中に前記第1のデジタル信号を出力し、第2の時間間隔中に前記第2のデジタル信号を出力するための、アナログ・デジタル変換手段(530)と、

前記第1および第2のデジタル信号を濾波して第1および第2の濾波済み信号をそれぞれ生成し、第3の時間間隔中に前記第1および第2の濾波済み信号を、時間軸で整合のとれた形式で出力するための、デジタル濾波手段(550)と、

を備える、前記装置(500)。

## (請求項2)

信号を処理する方法であって、

第1および第2のアナログ信号を、第1および第2のデジタル信号にそれぞれ変換するステップと、

第1の時間間隔中に前記第1のデジタル信号を出力するステップと、

第2の時間間隔中に前記第2のデジタル信号を出力するステップと、

前記第1および第2のデジタル信号を濾波して、第1および第2の濾波済み信号をそれぞれ生成するステップと、

第3の時間間隔中に前記第1および第2の濾波済み信号を、時間軸で整合のとれた形式で出力するステップと、

を含む、前記方法。

## 【発明を実施するための最良の形態】

## 【0017】

本明細書に述べる例示は、本発明の好ましい実施例を示すものであり、このような例示は、本発明の範囲をどんな方法でも限定するものと考えるべきではない。

## 【0018】

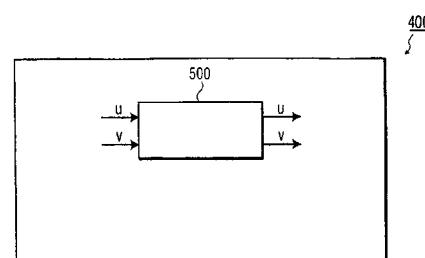

ここで図4を参照すると、本発明の原理による多重化アナログ・デジタル変換器(多重化ADC)構成500を備える例示的なシステム400の図が示されている。図4のシステム400は、例えばテレビジョン信号受信機、セットトップ・ボックス(STB)、ビデオ・カセット・レコーダ(VCR)、デジタル多用途ディスク(DVD)プレーヤ、ビデオ・ゲーム・ボックス(テレビ・ゲーム機)、パーソナル・ビデオ・レコーダ(PVR)などの音声および/またはビデオ・システムとして、或いはその他のビデオおよび/または音声システムとして具体化する。

## 【0019】

図4で、システム400は、多重化アナログ・デジタル変換器(多重化ADC)構成500を備えるが、多重化ADC構成500は、アナログ・デジタル変換器(ADC:図4には示さず)が入力信号UとVの間で時分割されるようにし、更に、このような信号が出力時に時間的に整列するようにする。UとVの入力信号は、例えば、高精細度テレビジョン(HDTV)システムなどのデジタル・ビデオ・システムにおける色差信号を表すものとする。多重化ADC構成500は、例えばIC上に組み込むことができる。図4には示していないが、システム400は、他のICや他の電気的および非電気的構成要素など、その他の構成要素を備えることもできる。

## 【0020】

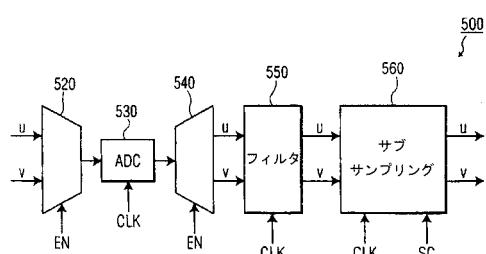

次に、図5を参照すると、図4の多重化アナログ・デジタル変換器(多重化ADC)構成500を更に詳細に示す図が示されている。図5に示すように、多重化ADC構成5

10

20

30

40

50

00は、マルチプレクサ520、ADC530、デマルチプレクサ540、フィルタ550、サブサンプリング・デバイス560を備えている。後述するように、多重化ADC構成500は、ADC530の前でアナログ遅延デバイスを使用することなく、時間軸で整合のとれた出力信号を生成する。

#### 【0021】

動作時、マルチプレクサ520は、アナログのUとVの入力信号を同時に受け取り、イネーブル(EN)信号に応答して切り換わり、受け取ったアナログのUとVの信号のうちの選択された方を交互に出力する。ADC530は、マルチプレクサ520からアナログのUとVの出力信号を受け取り、受け取ったUとVの信号をクロック(CLK)信号に応答してデジタル化する。CLK信号の各間隔は、単一のクロック・サイクル、即ち時間間隔を定める。EN信号およびCLK信号は、クロック発生器またはその他のデバイス(図示せず)により生成する。一実施例によれば、図5のCLK信号の周波数は、EN信号の周波数の2倍とする。例えば、CLK信号は、18MHzの周波数を呈し、EN信号は、9MHzの周波数を呈するものとする。従って、ADC530は、マルチプレクサ520に入力されたUとVの信号を1つおきに受け取ってデジタル化するだけである。即ち、マルチプレクサ520は、入力されたUとVの信号が1つおきに失われるよう切り換わる。このようにしてADC530は、あるクロック・サイクル中にデジタル化済みU信号を出力し、次のクロック・サイクル中にデジタル化済みV信号を出力する。この動作に関するこれ以上の詳細は後述する。

#### 【0022】

デマルチプレクサ540は、アナログ・デジタル変換器(ADC)530から出力されたデジタルのUとVの信号を受け取り、イネーブル(EN)信号に応答して切り換わり、デジタルのUとVの信号を出力する。後述するように、デマルチプレクサ540は、各クロック・サイクル中にデジタルU出力信号とデジタルV出力信号の両方を生成する。これらのデジタルのUとVの出力信号の一方は、現在のクロック・サイクル中にADC530から提供された信号であり、これらのデジタルのUとVの信号の他方は、前の(例えば、直前の)クロック・サイクル中にADC530から提供されたものである。一実施例によれば、デマルチプレクサ540は、前のUとVの信号値を保持し、それにより、あるクロック・サイクル中は現在のU出力信号と前のV出力信号を生成し、次いで、次のクロック・サイクル中は前のU出力信号と現在のV出力信号を生成する。

#### 【0023】

フィルタ550は、デマルチプレクサ540からデジタルのUとVの信号を受け取り、クロック(CLK)信号に応答して、これらに対して濾波(フィルタリング)(例えば、補間)動作を実行し、それにより時間軸で整合のとれた濾波済みU信号とV信号を生成する。具体的には、フィルタ550により生成された濾波済みU信号とV信号は、マルチプレクサ520への対応する入力信号に対して時間軸で整合がとれている。図5では、フィルタ550は、UとVの両方の信号チャネルに作用する単一の濾波デバイスとして示されている。ただし、本発明を実施する際は、フィルタ550は、各信号チャネルごとの専用フィルタなど複数の濾波デバイスで構成されてもよい。従って、フィルタ550は少なくとも1つの濾波デバイスを含んでいる。一実施例によれば、フィルタ550は、各U信号値が、現在のクロック・サイクル中にデマルチプレクサ540から受け取ったU信号値の2分の1と、前の(例えば、直前の)クロック・サイクル中にデマルチプレクサ540から受け取ったU信号値の2分の1とを足した値に等しく設定されるように、濾波動作を実行する。同様に、各V信号値は、現在のクロック・サイクル中にデマルチプレクサ540から受け取ったV信号値の2分の1と、前の(例えば、直前の)クロック・サイクル中にデマルチプレクサ540から受け取ったV信号値の2分の1とを足した値に等しく設定される。この濾波動作に関する更に詳細は、後述する。

#### 【0024】

サブサンプリング・デバイス560は、時間軸で整合のとれた濾波済みU信号とV信号をフィルタ550から受け取り、クロック(CLK)信号およびサブサンプル制御(SC

10

20

30

40

50

: Subsample Control) 信号に応答して、これらに対してサブサンプリング動作を実行し、サブサンプリング済み U 信号と V 信号を時間的に整列された形式で出力する。サブサンプル制御 (SC) 信号は、サブサンプリング・デバイス 560 が、サブサンプリングを実行する際の周波数を制御する。例えば、サブサンプル制御 (SC) 信号は、サブサンプリング・デバイス 560 が、1 クロック・サイクルおきに 1 対の濾波済み U 信号と V 信号に対してサブサンプリング動作を実行するようとする。サブサンプリング・デバイス 560 からの時間軸で整合のとれた U と V の出力信号は、次いで、色補正、色合い補正、サンプル周波数変換、および / またはその他の処理動作など、次の処理に向けて提供される。図 5 では、フィルタ 550 と同様にサブサンプリング・デバイス 560 も、U と V の両方の信号チャネルに作用する単一のサブサンプリング・デバイスとして示されている。ただし、本発明を実施する際は、サブサンプリング・デバイス 560 は、各信号チャネルごとの専用サブサンプリング・デバイスなど複数のサブサンプリング・デバイスで構成されてもよい。従って、サブサンプリング・デバイス 560 は、少なくとも 1 つのサブサンプリング・デバイスを含んでいる。

#### 【0025】

次に、以下の表 4 を参照しながら、多重化 ADC 構成 500 の例示的な動作に関して更に詳細に述べる。

#### 【0026】

##### 【表 4】

| クロック・サイクル | 1  | 2  | 3  | 4  | 5  |

|-----------|----|----|----|----|----|

| アナログ U    | 45 | 46 | 47 | 48 | 49 |

| アナログ V    | 75 | 76 | 77 | 78 | 79 |

| 多重化位置     | U  | V  | U  | V  | U  |

| ADC 出力    | 45 | 76 | 47 | 78 | 49 |

| 逆多重化済み U  | 45 | 45 | 47 | 47 | 49 |

| 逆多重化済み V  | -- | 76 | 76 | 78 | 78 |

| 濾波済み U    | -- | 45 | 46 | 47 | 48 |

| 濾波済み V    | -- | -- | 76 | 77 | 78 |

10

20

30

#### 【0027】

表 4 に示すように、アナログの U と V の信号 ( 即ち、アナログ U と アナログ V ) は、各クロック・サイクル中にマルチプレクサ 520 に同時に入力される。マルチプレクサ 520 の切換え位置 ( 即ち、多重化位置 ) は、あるクロックから次のクロックで交互に、U から V に変化する。例えば、表 4 で、マルチプレクサ 520 は、クロック・サイクル 1 の間は、値 45 のアナログ U 信号を出力するように切り換わり、クロック・サイクル 2 の間は、値 76 のアナログ V 信号を出力するように切り換わる。また、表 4 で、マルチプレクサ 520 への幾つかの U と V の入力信号は、失われることに留意されたい。例えば、クロック・サイクル 1 の間は、値 75 の V 信号が失われる。同様に、クロック・サイクル 2 の間は、値 46 の U 信号が失われる。後述するように、これらの失われた信号は、フィルタ 550 の動作により補償される。

#### 【0028】

アナログ・デジタル変換器 (ADC) 530 は、マルチプレクサ 520 からアナログの U と V の出力信号を受け取り、受け取った U と V の信号をクロック (CLK) 信号に応答してデジタル化する。マルチプレクサ 520 は、入力された U と V の信号が 1 つおき

40

50

に失われるよう切り換わるので、ADC530は、マルチプレクサ520に入力されたUとVの信号を1つおきに受け取ってデジタル化するだけである。例示および説明のために、表4では、ADC530が入力と出力の間で待ち時間(*latency*: レイテンシ)または遅延時間(*delay*: ディレイ)を有さないものとして示す。即ち、表4では、ADC530が、マルチプレクサ520から対応するアナログのUまたはV入力信号を受け取るのと同じクロック・サイクル中に、デジタルのUまたはV出力信号(即ち、ADC出力)を生成するものとして示す。ただし、本発明を実施する際は、ADC530が、マルチプレクサ520からアナログのUまたはV入力信号を受け取る時と、ADC530が、対応するデジタルのUまたはV出力信号を生成する時との間に、いくつかの遅延がある場合がある。例えば、このような遅延は1つまたは複数のクロック・サイクルに等しい場合がある。10

#### 【0029】

デマルチプレクサ540は、デジタル変換されたUとVの信号をアナログ・デジタル変換器(ADC)530から受け取り、イネーブル(EN)信号に応答して切り換わり、デジタルのUとVの信号を同時に出力する。この場合も、例示および説明のために表4では、デマルチプレクサ540が入力と出力の間で遅延を有さないものとして示す。従って、表4では、デマルチプレクサ540が、ADC530から現在のUまたはV信号を受け取るのと同じクロック・サイクル中に、現在のUまたはV出力信号(即ち、逆多重化済みUまたは逆多重化済みV)を生成するものとして示す。ただし、本発明を実施する際には、デマルチプレクサ540がADC530からUまたはV入力信号を受け取る時と、デマルチプレクサ540がUまたはV出力信号を生成する時との間に、いくつかの遅延がある場合がある。例えば、このような遅延は1つまたは複数のクロック・サイクルに等しい場合がある。20

#### 【0030】

上述したように、デマルチプレクサ540は、各クロック・サイクル中にデジタルU出力信号とデジタルV出力信号の両方を生成する。具体的には、デマルチプレクサ540は、前のUとVの信号値を保持し、それにより、所定のクロック・サイクル中に現在のU出力信号と前のV出力信号を生成した後、次のクロック・サイクル中に前のU出力信号と現在のV出力信号を生成する。例えば、表4のクロック・サイクル3の間に、デマルチプレクサ540は、値47の現在U出力信号と、値76の直前クロック・サイクル(即ち、クロック・サイクル2)のV出力信号を生成する。次いで、クロック・サイクル4の間に、デマルチプレクサ540は、値78の現在V出力信号と、値47の直前クロック・サイクル(即ち、クロック・サイクル3)のU出力信号を生成する。このようにして、デマルチプレクサ540は、各クロック・サイクル中にデジタルU出力信号とデジタルV出力信号の両方を生成する。30

#### 【0031】

フィルタ550は、デマルチプレクサ540からデジタルのUとVの信号を受け取り、これらに対して濾波動作を実行して、それにより時間軸で整合のとれた濾波済みU信号とV信号を出力する。上述したように、一実施例によれば、フィルタ550は、各U信号値が、現在のクロック・サイクル中にデマルチプレクサ540から生成されたU信号値の2分の1と、前の(例えば、直前の)クロック・サイクル中にデマルチプレクサ540から生成されたU信号値の2分の1とを足した値に等しく設定されるように、濾波動作を実行する。同様に、各V信号値は、現在のクロック・サイクル中にデマルチプレクサ540から生成されたV信号値の2分の1と、前の(例えば、直前の)クロック・サイクル中にデマルチプレクサ540から生成されたV信号値の2分の1とを足した値に等しく設定される。例えば、表4のクロック・サイクル3の間、フィルタ550は、値46の濾波済みU信号(即ち、濾波済みU)と、値76の濾波済みV信号(即ち、濾波済みV)を出力する。濾波済みU信号の値46は、次のようにして得られる。40

$$1/2(47) + 1/2(45) = 46$$

即ち、表4のクロック・サイクル3では、濾波済みU信号は、現在のクロック・サイク50

ル（即ち、クロック・サイクル3）中にデマルチプレクサ540から提供されたU信号値（即ち、47）の2分の1と、直前のクロック・サイクル（即ち、クロック・サイクル2）中にデマルチプレクサ540から提供されたU信号値（即ち、45）の2分の1を足した値に等しい。同様に、濾波済みV信号の値76も次のようにして得られる。

$$1/2(76) + 1/2(76) = 76$$

即ち、表4のクロック・サイクル3では、濾波済みV信号は、現在のクロック・サイクル（即ち、クロック・サイクル3）中にデマルチプレクサ540から提供されたV信号値（即ち、76）の2分の1と、直前のクロック・サイクル（即ち、クロック・サイクル2）中にデマルチプレクサ540から提供されたV信号値（即ち、76）の2分の1を足した値に等しい。当然、フィルタ550は、本発明の原理により他のタイプの濾波動作を実行してもよい。例えば、フィルタ550は、直前クロック・サイクル以外の前クロック・サイクルからの信号値を利用して、濾波済みU信号とV信号を生成してもよい。10

#### 【0032】

サブサンプリング・デバイス560は、時間軸で整合のとれた濾波済みU信号とV信号をフィルタ550から受け取り、これらに対してサブサンプリング動作を実行して、サブサンプリング済みU信号とV信号を生成する。表4には示していないが、サブサンプリング・デバイス560は、クロック（CLK）信号およびサブサンプル制御（SC）信号に応答して、後続のクロック・サイクル中にサブサンプリング済みU信号とV信号を時間的に整列された形式で出力する。上述したように、サブサンプリング済みU信号とV信号は、色補正、色合い補正、サンプル周波数変換、および／またはその他の処理動作など、次の処理に向けて提供される。20

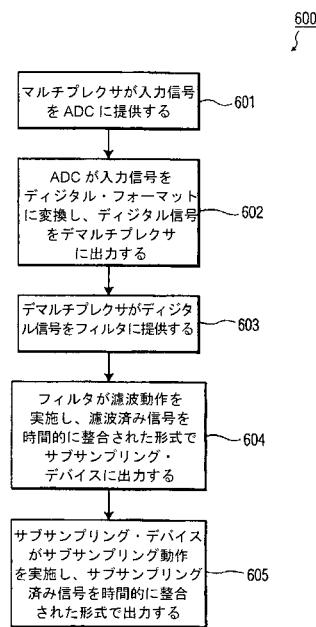

#### 【0033】

次に、図6を参照すると、本発明を実施するための例示的なステップを要約したフローチャート600が示されている。例示および説明のために、図6のステップは、図5の多重化ADC構成500に関して述べる。

#### 【0034】

図6で、プロセス・フロー（流れ）は、ステップ601で開始し、マルチプレクサ520は、イネーブル（EN）信号に応答してアナログのUとVの入力信号を交互にアナログ・ディジタル変換器（ADC）530に提供する。ステップ602で、ADC530は、アナログのUとVの入力信号をディジタル・フォーマットに変換し、CLK信号に応答してディジタルのUとVの信号をデマルチプレクサ540に出力する。CLK信号の各間隔は、単一のクロック・サイクルまたは時間間隔を定める。ステップ603で、デマルチプレクサ540は、EN信号に応答してディジタルのUとVの信号をフィルタ550に提供する。ステップ604で、フィルタ550は、デマルチプレクサ540から提供されたデジタルのUとVの信号に対して濾波（例えば、補間）動作を実行し、CLK信号に応答して、濾波済みU信号とV信号を時間的に整列された形式でサブサンプリング・デバイス560に出力する。次いで、ステップ605で、サブサンプリング・デバイス560は、フィルタ550から提供された濾波済みU信号とV信号に対してサブサンプリング動作を実行し、サブサンプリング済みU信号とV信号を時間的に整列された形式で出力する。次いで、サブサンプリング・デバイス560からの時間軸で整合のとれたUとVの出力信号は、色補正、色合い補正、サンプル周波数変換、および／またはその他の処理動作など、次の処理に向けて提供される。30

#### 【0035】

本明細書に述べたように、本発明では有利にも、時間軸で整合のとれた出力サンプルを発生する多重化ADCシステム中でアナログ遅延手段の必要がない。好ましい実施例を2つの入力信号（即ち、UとV）だけに関して述べたが、3つ以上の入力信号を有するシステムに本発明の原理を適用することもできることは、当業者なら直感的に分かるであろう。従って、本発明の原理を適用して、時間軸で整合のとれた出力信号を伴う任意の数の信号チャネルを提供する。40

#### 【0036】

本明細書に述べた本発明は、表示装置付きまたは表示装置なしの様々な音声および／またはビデオ・システムに特に適用可能である。従って、本明細書で使用した語句「音声」および／または「ビデオ」システム或いは類似の語句は、様々なタイプのシステムまたは装置を含むものとし、限定しないがこれらには、テレビジョン・セットや、表示装置を含めたモニターや、セットトップ・ボックス(STB)、VCR、DVDプレーヤ、ビデオ・ゲーム・ボックス、PVRなどのシステムまたは装置や、表示装置を備えない場合のあるその他のビデオ・システムが含まれる。更に本発明は、ビデオ出力をすることも、有していないこともある音声システムなど、その他のシステムにも適用可能である。

## 【0037】

本発明を好ましい設計を有するものとして述べたが、本発明は、本開示の趣旨および範囲の内で更に変更することもできる。従って本出願は、本発明の一般原理を用いる本発明のどんな変形、使用、または適合もカバーするものとする。更に本出願は、本発明が関係しており特許請求の範囲に含まれる、当技術分野における周知のまたは慣例の実施の範囲内で、本開示からの逸脱もカバーするものとする。

10

## 【図面の簡単な説明】

## 【0038】

【図1】単純な多重化技法を利用する多重化ADC構成の図である。

【図2】サンプル・ホールド回路を利用する多重化ADC構成の図である。

【図3】アナログ遅延フィルタを利用する多重化ADC構成の図である。

【図4】本発明の原理による多重化ADC構成を備える例示的なシステムの図である。

20

【図5】図4の多重化ADC構成を更に詳細に示す図である。

【図6】本発明を実施するための例示的なステップを要約したフローチャートである。

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

---

フロントページの続き

(72)発明者 ラムレイク, マーク フランシス

アメリカ合衆国 インディアナ州 インディアナポリス インディアン・レイク・ブルバード・

サウス 10308

審査官 小曳 満昭

(56)参考文献 特開平04-207716(JP, A)

特開昭60-001939(JP, A)

実開昭59-028734(JP, U)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00- 1/88