## RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE (11) N° de publication : (A n'utiliser que pour les

commandes de reproduction).

2 493 553

PARIS

Α1

## DEMANDE DE BREVET D'INVENTION

N° 80 23404 (21) (54) Appareillage pour la datation précise d'un événement par rapport à une référence de temps. Classification internationale (Int. Cl. 3). G 04 F 10/00. Priorité revendiquée : (41) Date de la mise à la disposition du public de la demande . . . . . . . B.O.P.I. — « Listes »  $n^{\circ}$  18 du 7-5-1982. (71)Déposant : Société dite : ELECTRONIQUE MARCEL DASSAULT, résidant en France. (72)Invention de : Michel Geesen. Titulaire: Idem (71) Mandataire: André Netter, conseil en brevets d'invention,

40, rue Vignon, 75009 Paris.

L'invention a pour objet un appareillage pour dater un évènement par rapport à des signaux d'horloge, notamment un évènement représenté par l'arrivée d'un front d'impulsion en un lieu pourvu d'une horloge.

5

20

25

35

Pour synchroniser deux ou un plus grand nombre d'horloqes espacées à la surface de la terre, par exemple des horloges atomiques, sans déplacer ces horloges, on a proposé d'émettre, à partir du site de chaque horloge, une ou une série d'impulsion(s) laser à des instants qui peuvent être 10 repérés avec une grande précision en référence à l'horloge dudit site. Les impulsions laser en provenance de deux sites distincts sont dirigées vers un objectif commun placé de manière à "voir" simultanément ces deux sites, ledit objectif étant avantageusement un satellite de la terre, et on déter-15 mine l'intervalle de temps séparant l'arrivée sur le satellite d'impulsions laser provenant d'une horloge de celles provenant de l'autre horloge.

La détermination de cet intervalle de temps s'effectue en datant l'arrivée respective de chacune de ces impulsions laser sur le satellite à l'aide d'une horloge dont est muni le satellite et en mesurant l'écart entre les deux dates correspondantes. Cette dernière mesure peut s'effectuer au sol à l'aide des informations retransmises par le satellite sur les dates respectives d'arrivée des deux impulsions.

Dans cette application, la précision de chaque datation doit être exceptionnellement élevée, meilleure que la nanoseconde.

La présente invention résout ce problème et permet d'efrectuer des datations avec une très grande précision d'évè-30 nements tels que l'arrivée d'une impulsion laser sur un satellite.

Conformément à l'invention, il est proposé un dispositif de datation d'un évènement par rapport à une référence de temps fournie par des signaux d'horloge comprenant :

un circuit d'intégration;

des moyens pour produire un signal de charge et un signal de décharge de ce circuit d'intégration dont les amplitudes respectives sont telles que le taux de charge du circuit d'intégration soit grand par rapport à son taux 40 de décharge;

des moyens de commande pour déclencher l'application du signal de charge au circuit d'intégration en réponse à une impulsion représentative dans le temps de l'évènement à dater, et pour interrompre l'application du signal de charge 5 de ce circuit d'intégration et déclencher la décharge de ce dernier en réponse à un signal d'horloge suivant ladite impulsion;

un détecteur propre à détecter qu'un niveau de décharge prédéterminé a été atteint par le circuit d'inté-10 gration; et

un dispositif de mesure du temps écoulé entre le début de la décharge et la détection dudit niveau de décharge prédéterminé,

caractérisé en ce que les moyens pour produire le signal 15 de charge comprennent des moyens propres à faire passer un premier courant prédéterminé dans un premier circuit indépendant du circuit d'intégration, et les moyens de commande de ce signal comportent des moyens de commutation pour diriger ledit courant prédéterminé de ce premier circuit vers le 20 circuit d'intégration en réponse à l'impulsion représentative de l'évènement à dater.

Ainsi, conformément à cette disposition, il est possible d'obtenir une commutation extrêmement précise du début de la charge d'un intégrateur avec un minimum de phénomènes transi-25 toires • En effet, l'application d'un premier courant prédéterminé directement à un circuit d'intégration par un générateur de courant ferait intervenir une période transitoire de stabilisation, relativement importante par rapport à la précision de la datation que l'on cherche à obtenir, pour l'établissement 30 du courant à son niveau nominal de charge. En prévoyant, selon l'invention, que le premier courant est déjà stabilisé à un niveau prédéterminé dans un circuit parallèle au circuit d'intégration, et en commutant ce premier courant vers le circuit d'intégration, on réduit au minimum les transitoires.

De préférence, les moyens de commutation comportent un premier et un deuxième organes de commutation qui sont respectivement placés sur le premier circuit et sur le circuit d'intégration afin de commander le passage du premier courant prédéterminé dans leur circuit respectif associé 40 en opposition.

35

Conformément à une forme de réalisation, le signal de charge est composé par la superposition du premier courant prédéterminé et d'un courant de décharge, d'amplitude beaucoup plus faible et de sens opposé au premier courant, qui est appliqué au circuit d'intégration au début de la période de charge. A la fin de la charge, seul le premier courant prédéterminé est à nouveau commuté pour traverser le premier circuit et le courant de décharge reste appliqué au moins jusqu'à la fin de la période de décharge du circuit d'intégration. La commande de ce courant de décharge en dehors des périodes de charge et de décharge peut être effectuée à l'aide d'un dispositif de commutation qui établit un courtcircuit aux bornes du dispositif d'intégration par lequel s'écoule le courant de décharge en dehors des périodes de fonctionnement de ce dernier.

10

15

20

35

Avantageusement, on prévoit de réguler le premier courant prédéterminé afin de maintenir à un niveau constant le courant traversant le premier circuit à la sortie du premier organe de commutation pour compenser les variations de caractéristiques électriques de ce dernier . Dans la mesure où ces variations sont sensiblement identiques pour le deuxième organe de commutation dont les caractéristiques ont été choisies aussi voisines que possible de celles du premier organe, on assure ainsi indirectement une régulation du niveau de 25 courant à la sortie du deuxième organe de commutation dans le circuit d'intégration pendant les courtes périodes de fonctionnement en charge de ce dernier.

Conformément à un mode de réalisation avantageux de la commande de la commutation, il est prévu un circuit à retard 30 pour retarder l'instant d'interruption de la charge ( et par conséquent le début de la décharge) du circuit d'intégration pendant un temps au moins égal au temps mis par ce dernier pour atteindre un régime de charge linéaire après la réception de'l'impulsion représentative de l'évènement à dater.

Cette réalisation est d'un intérêt particulier lorsqu'on désire déterminer l'intervalle de temps séparant deux évènements. Dans ce cas, en effet, le défaut de linéarité de la charge d'un condensateur au début de son régime n'intervient pas sur la précision de la détermination, dans la mesure 40 où l'interruption de la charge de l'intégrateur n'est

entreprise qu'à partir d'un état où celle-ci est devenue linéaire.

La duvée de décharge du circuit d'intégration fournit une mesure de l'intervalle de temps séparant l'arrivée de l'évènement à dater de l'impulsion d'horloge qui suit immédiatement et qui avait commandé le début de la décharge de l'intégrateur. Avantageusement, on utilise, pour le chronométrage de cette durée de décharge, des moyens de comptage des impulsions de l'horloge de référence employée pour le repérage de l'impulsion représentative de l'évènement à dater. La lecture de la durée de décharge se fait de préférence en laissant cas moyens de comptage fonctionner en permanence et en venant lire l'état instantané du compteur au début et à la fin de la période de décharge en réponse aux signaux correspondants.

L'invention est avantageusement utilisée pour la datation d'impulsions laser reçues par un satellite, en vue notemment de la synchronisation d'horloges atomiques situées en des sites distincts au sol.

D'autres aspects et avantages de l'invention apparaîtront à la lecture de la description qui va suivre, faite à titre d'exemple, en référence aux dessins annexés, dans lesquels :

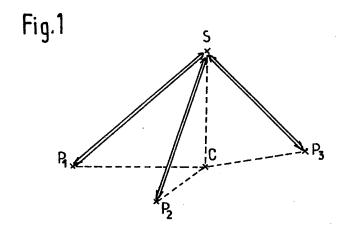

- la figure l'représente schématiquement un satellite et des stations terrestres avec lesquelles il communique en vue de la mise en osuvre de l'invention;

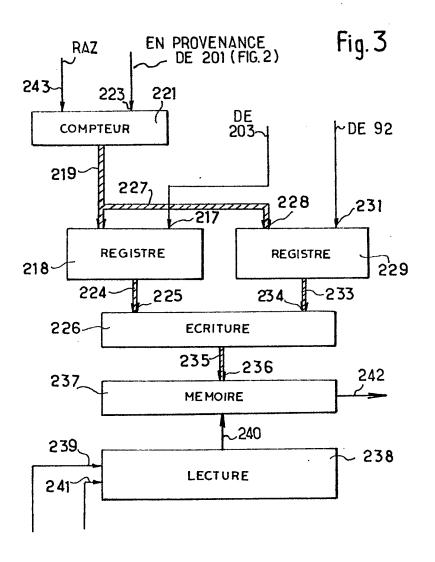

- la figure 2 est un schéma synoptique d'un circuit pour la détermination de la position d'une impulsion laser par rapport à une horloge de référence;

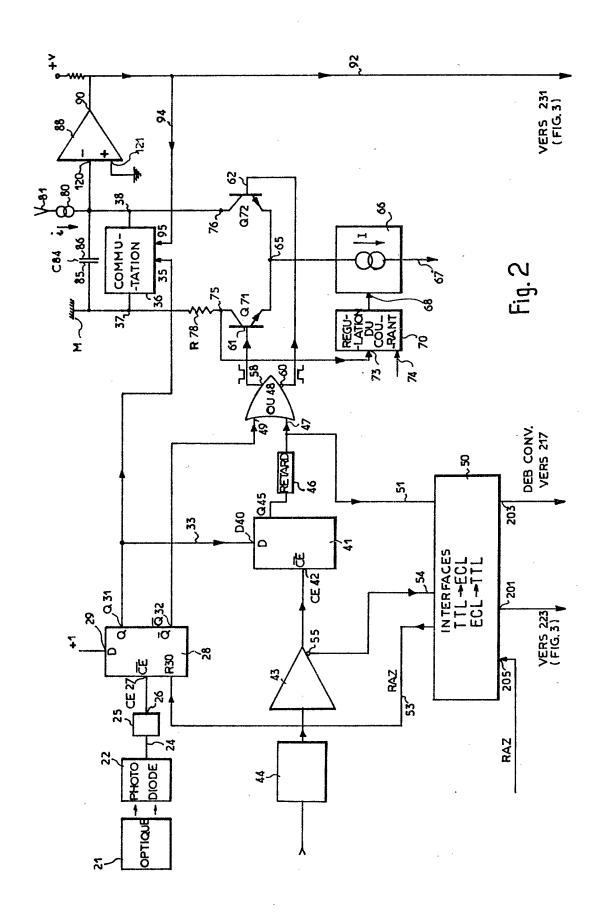

- la figure 3 est un schéma synoptique du circuit de chronométrage utilisé en aval du dispositif de la figure 2;

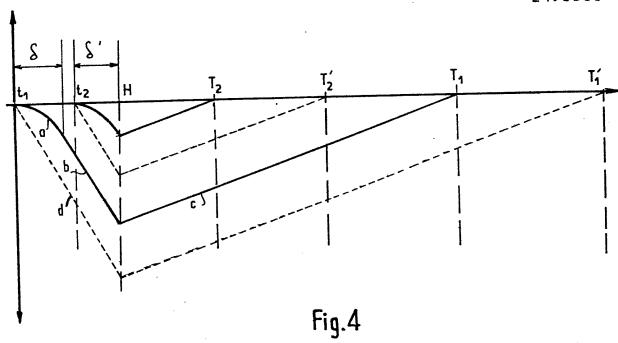

- la figure 4 est un diagramme illustrant le fonctionnement en charge et en décharge d'un circuit d'intégration utilisé pour la datation de l'impulsion laser;

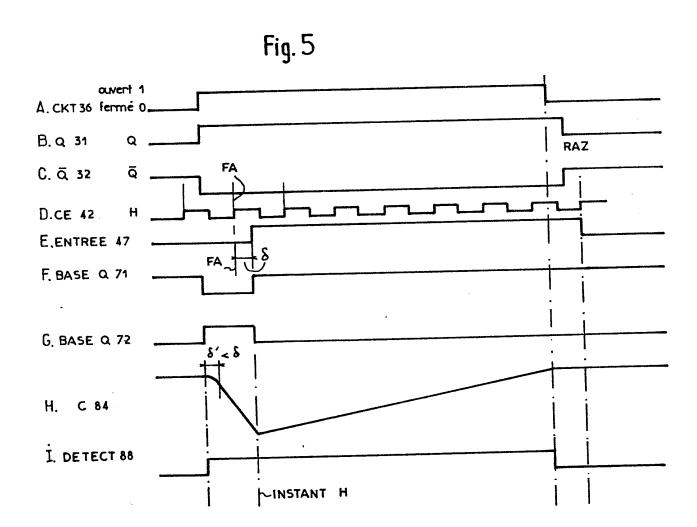

- la figure 5 est un diagramme de signaux illustrant le fonctionnement des différentes parties du circuit de la figure 2; et

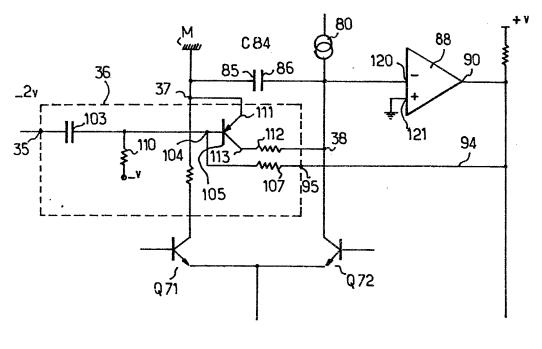

- la figure 6 représente le détail d'un des circuits de la figure 2.

Le satellite S (figure 1), qui peut être un satellite 40 "spinné", c'est-à-dire stabilisé par rotation, comprend un

appareillage optique 21 (figure 2) propre à projeter sur un convertisseur photoélectrique 22 un pinceau laser provement de l'une et/ou de l'autre d'une multiplicité de stations Pl,P2, P3, etc.. équipées chacune d'une horloge, par exemple une horloge atomique. Dans cet exemple, le but de l'installation est de syncrhoniser lesdites horloges en déterminant l'intervalle de temps qui sépare une impulsion d'une horloge d'une impulsion d'une autre horloge, afin de déterminer l'écart de synchronisme entre les horloges.

Le convertisseur 22 peut comprendre une photodiode ou autre cellule photoélectrique unique, comme représenté, ou bien une multiplicité de photodiodes dont chacune est affectée à une longueur d'onde utilisée par une ou plusieurs stations d'émission.

10

15

35

Chaque station Pl émet une impulsion laser dans un créneau de temps qui lui est affecté, et bénéficie avantageusement d'une multiplicité de créneaux, par exemple, une centaine, de manière que la mesure corresponde à une moyenne de mesures.

Les émissions d'impulsions laser par chacune des stations 20 sont datées à l'aide de leur horloge atomique et l'installation portée par le satellite S a pour but de dater l'arrivée d'une impulsion laser émise par un poste et l'arrivée de celle émise par un autre poste de sorte qu'il soit possible de connaître l'intervalle de temps séparant ces arrivées et d'effectuer 25 sur les horloges atomiques de l'un et/ou de l'autre poste les ajustements requis pour amener ces dernières en synchronisme exact pour tenir compte de leur décalage ou bien d'être informé sur la valeur de celui-ci. L'information sur l'instant d'impact de chaque impulsion laser sur le satellite S, instant 30 déterminé par référence à des signaux d'horloge disponibles sur le satellite est, dans ce but, envoyée par télémesure chacune des stations ou bien, de préférence, vers une station centrale C liée par télémesure non seulement au satellite S mais également aux divers postes.

L'appareillage optique 21 comprend un réflecteur pour réfléchir vers chaque station le pinceau laser qu'il reçoit de ladite station. La mesure à chaque station, par exemple à ladite station Pl, de l'intervalle de temps qui sépare l'instant d'émission de l'impulsion de l'écho ainsi reçu par réflexion 40 fournit l'information sur le temps de trajet de l'impulsion

entre ladite station et le satellite.

Outre le réflecteur, non représenté, l'appareillage optique 21 comprend des moyens pour diriger l'énergie laser atteignant le satellite vers une photodiode 22 à travers une optique telle qu'une lentille non représentée.

La sortie électrique 24 de la photodiode 22 est connectée à travers un amplificateur-détecteur 25 à une entrée CE27 d'une bascule 28 de type D, dont l'entrée D29 est fixée à un niveau stable équivalent à un niveau logique l en perma-10 nence. La bascule 28 comporte une entrée de remise à zéro R30 et deux sorties, directe et inverse, respectivement Q 31 et Q 32. La sortie Q 31 de la bascule 28 est reliée, d'une part, à une entrée de commande 35 d'un circuit de commutation 36 propre, dans une première condition, à court-circuiter deux 15 bornes terminales 37 et 38 et, dans une deuxième condition, à interrompre le court-circuit entre les terminaux 37 et 38. La sortie Q 31 est également reliée à l'entrée D 40 d'une bascule 41 de type D, par une liaison 33. La bascule 41 reçoit sur son entrée d'horloge CE42 des signaux de sortie 20 d'un amplificateur 43, lui-même alimenté par un circuit d'horloge 44, fonctionnant dans l'exemple choisi à une fréquence de 15 MHz.

Le circuit de bascule 41 comporte une sortie Q 45 reliée, à travers un circuit à retard 46, qui peut être constitué par 25 un branchement en série de deux portes logiques, à une entrée 47 d'une porte OU 48 dont l'autre entrée 49 est connectée à la sortie Q 32 de la bascule 28. La sortie du circuit à retard 46 est également reliée à un circuit d'interface 50 par une liaison 51 transmettant à ce circuit une information dite de 30 début de conversion. Compte tenu du temps de fonctionnement de l'interface 50, il est également possible de connecter la ligne 51 en amon du circuit de retard 46. De cette interface 50 est issue une ligne 53 de remise à zéro RAZ connectée à l'entrée R 30 de la bascule 28. L'interface 50 reçoit également 35 sur une entrée 54 des signaux issus d'une sortie inverseuse 55 de l'amplificateur de signaux d'horloge 43. Cette interface par ailleurs possède un certain nombre de sorties qui seront explicitées ci-après.

La porte OU 48 comporte une sortie directe 58 et une 40 sortie inverseuse 60, la première sortie 58 étant connectée

à la base 61 d'un transistor de type NPN Q71 tandis que la sortie inverseuse 60 de la porte 0U 48 est reliée à la base 62 d'un transistor Q72 choisi pour avoir des caractéristiques aussi proches que possible de celles du transistor 5 Q71 . Ces deux transistors Q71 . et Q72 . ont leurs émetteurs connectés en commun à une borne 65 d'un générateur de courant réglable 66 fournissant un courant désigné ci-après par la lettre I. A son extrémité 67 opposée à la borne 65, le générateur 66 est raccordé à une source de tension qui, dans 10 l'exemple considéré, est de -15 volts. Le courant nominal du générateur 66 est d'environ 20 milli-ampères dans cet exemple. Le générateur de courant 66 possède une entrée 68 susceptible de recevoir un signal de tension d'un circuit de comparaison 70 commandant le niveau de courant fourni par ce générateur 15 dans un but de régulation comme il sera expliqué ci-après. Le circuit de comparaison 70 reçoit sur son entrée 73 un signal de tension prélevé au collecteur 75 du transistor Q71 auquel cette entrée 73 est raccordée. Le circuit comparateur 70 possède une deuxième entrée 74 susceptible de recevoir une 20 tension de référence stabilisée par diode Zener et fournissant une référence à partir de laquelle le niveau du courant du générateur 66 est régulé.

Le collecteur 75 du transistor Q71 est relié à la masse M par l'intermédiaire d'une résistance R78. Une borne d'entrée 37 du circuit de commutation 36 est également à la masse. 25 Le collecteur 76 du transistor Q72 est relié directement à la borne 38 du circuit de commutation 36, cette borne 38 étant elle-même connectée à une extrémité d'un deuxième générateur à courant constant 80 dont l'autre extrémité 81 30 est reliée à une source de tension, par exemple de +12 volts. Ce générateur 80 æt propre à produire un courant auquel il sera fait référence ci-après sous la désignation i, i étant dans l'exemple choisi d'un ordre de grandeur de 20 microampères, c'est-à-dire environ mille fois plus faible que 35 le courant I. Un condensateur C84 est également connecté entre les bornes 37 et 38, son armature 85 étant reliée à la borne 37 et donc à la masse, tandis que son armature 86 est reliée à la borne 38. Cette armature 86 est également reliée à l'entrée d'un détecteur de niveau 88 dont la sortie 90 est 40 connectée, d'une part à une ligne de fin de conversion 92

propre à transmettre une information lorsque la décharge du condensateur C84 a pris fin, et d'autre part, par l'intermédiaire d'une ligne 94, à une entrée 95 du circuit de commutation 36 afin de rétablir la liaison entre les bornes 37 et 38 dès qu'un signal apparaît sur la sortie 90 du comparateur 88.

L'entrée 35 du circuit de commutation 36 est reliée (figure 6) à une armature d'un condensateur 103, dont l'autre armature est reliée à la base 104 d'un transistor PNP 105 et, à travers une résistance 107 à l'entrée 95 du circuit 36 issue de la sortie 90 du détecteur 88.

10

15

20

40

Une résistance 110 reliée entre une source de potentiel négatif (-v) et la base 104 forme avec la résistance 107 un circuit de polarisation de cette base à une valeur suffisamment basse, lorsque le détecteur 88 est au repos, pour que le transistor 105, dont l'émetteur 111 est relié à la jonction 37 et le collecteur 113 à la jonction 38 à travers une résistance 112, soit passant. Dans cet état, le transistor 105 court-circuite le condensateur C84 en maintenant seulement entre les armatures 85 et 86 une tension résiduelle égale à la chute de potentiel du courant <u>i</u> dans la résistance 112. Cette chute de potentiel est toujours supérieure à la tension de décalage du comparateur 88 afin de permettre une commutation franche de celui-ci lorsqu'un signal de charge du condensateur est appliqué sur son entrée négative 120, l'entrée positive 121 étant reliée à la masse.

Le principe général de fonctionnement est le suivant :

Dès l'arrivée d'une impulsion laser, on commence à charger le condensateur C84 à un taux stable et relativement élevé.

On arrête la charge lors de la réception du premier signal de l'horloge de référence 44 portée par le satellite suivant la réception de l'impulsion laser. A partir de cet instant, on permet la décharge du condensateur C84 à un taux connu, environ mille fois plus faible que le taux de charge et on mesure le temps de décharge de ce condensateur. L'horloge 44 est utilisée pour ce chronométrage, comme il sera indiqué ci-après. La fin de la décharge est détectée par le détecteur 88 qui émet alors un signal de fin de conversion que l'on date pour mesurer le temps écoulé.

Le fonctionnement détaillé sera bien compris si l'on se

réfère à la figure 2 en même temps qu'aux diagrammes de signaux représentés sur la figure 5.

5

15

25

40

Avant la réception d'une impulsion laser, le circuit de commutation 36 est dans sa position fermée (niveau 0 sur le diagramme 5A de la figure 5). La sortie Q31 est à son niveau 0, 232 étant au niveau 1 (figure 5C). L'horloge 44 produit un signal crénelé H, tel que représenté à la figure 5D, sur l'entrée CE42 de la bascule 41; la sortie Q45 de cette bascule se trouve au niveau 0; la base de Q71 est alimentée par la sortie Q32 de la bascule 28 à travers la porte OU 48, ce qui maintient le transistor Q71 à l'état conducteur. La base de Q72 n'est pas alimentée et ce dernier transistor est bloqué (figure 5G). Le condensateur C84 est déchargé, ses armatures étant court-circuitées par le circuit de commutation 36 (figure 5H).

L'arrivée d'une impulsion laser sur la photodiode 22 se traduit par la production d'une impulsion électrique sur la sortie 24 de celle-ci dont le front avant est admis, après amplification, sur l'entrée d'horloge CE27 de la 20 bascule 28 et fait passer la sortie Q31 de cette dernière à un niveau 1, ce qui a pour effet d'ouvrir le circuit de commutation 36, interrompant le court-circuit entre les bornes 37 et 38. Simultanément, le niveau de la sortie  $\overline{Q}$ 32 est passé à O, interrompant ainsi la tension d'alimentation de la base 61 du transistor Q71, qui se trouve bloqué, et provoquant par sa sortie inverseuse 60 la mise en conduction du transistor Q72 dont la base 62 se trouve maintenant alimentée. La borne 38 est donc maintenant reliée au générateur de courant 66 et le condensateur C84, dont les armatures ne sont plus en courtcircuit, commence à se charger négativement (figure 5H) sous l'effet d'un courant égal à (I-i) si l'on fait abstraction pour le moment du courant base-émetteur du transistor Q72.

Le fonctionnement détaillé du circuit de commutation 36 est le suivant : le signal de la sortie Q31 (figure 6) charge le condensateur 103 à un niveau qui provoque la coupure du transistor 105. Sous l'effet de la charge du condensateur C84, le niveau de tension à la sortie du détecteur 88 s'élève et vient confirmer par l'entrée 95 la polarisation en non conduction de la base 104.

En même temps que les sorties Q31 et  $\overline{\mathrm{Q}}$ 32 de la bascule

28 changeaient d'état, l'entrée D40 de la bascule 41 se trouve portée au niveau 1. Cette bascule est donc prête à basculer à la réception du prochain front d'horloge en provenance du circuit 44. Ce front FA est représenté sur la figure 5D. Il 5 provoque le changement d'état de la sortie Q45 lequel est transmis par le circuit à retard 46. (Ce dernier peut être constitué simplement par la mise en série de deux portes dont les délais de transition s'accumulent pour fournir un léger retard, suffisant cependant pour remplir la fonction 10 explicitée ci-après). A l'issue de ce retard désigné par  $\delta$ sur la figure 5E, un signal est présent sur l'entrée 47 de la porte OU 48 qui va rétablir les sorties 58 et 60 dans leur état initial en entraînant la conduction de Q71 et le reblocage de Q72 respectivement. Dès lors, le condensateur 15 C84 commence à se décharger sous l'effet du courant i, le courant I étant dévié par le transistor Q71. Cette décharge est représentée sur la figure 5H par la ligne de pente positive faible qui, dans la réalité est d'environ mille fois moins inclinée que la droite de charge à pente négative la précédant. 20 La durée de cette décharge est chronométrée par des moyens qui seront explicités ci-après.

A la fin de la décharge du condensateur C84, le retour de l'armature 86 a un niveau de potentiel voisin de 0, fait retomber la tension de sortie du détecteur 90. La tension de la base 104 s'abaisse et le transistor 105 laisse passer un courant suffisant pour empêcher le condensateur C84 de se charger sensiblement en sens inverse sous l'action du courant i à un niveau indésirable.

Ita retombée de la tension de sortie du détecteur 90 (signal de fin de conversion) commande le transfert de l'information de datation dans une mémoire décrite ci-après, et à

la fin de celui-ci, la remise à zéro de la bascule 28 dont

les sorties Q31 et Q32 changent d'état et provoquent, d'une

part, la remise à sa tension de repos du condensateur C84

35 et d'autre part, au top d'horloge suivant, la remise de la sortie Q45 à son état initial. La remise à sa tension de repos

du condensateur C84 intervient lorsque la sortie Q31 revient

à son état initial en ramenant la tension de polarisation de

la base 104 à un niveau qui rétablit la pleine conduction du

40 transistor 105 (figure 6).

On conçoit que si la fréquence du signal d'horloge propre au satellite issue du circuit 44 est, à titre d'exemple, de 15 MHz, la période correspondante entre deux fronts d'horloge soit très grande par rapport à la précision, d'une nanoseconde ou moins, requise pour dater l'arrivée des impulsions laser sus-mentionnées. Le circuit qui vient d'être décrit permet de localiser dans le temps la position de l'arrivée d'une telle impulsion entre deux fronts d'horloge successifs, tels que FA sur la figure 5D, en mesurant le temps de décharge du condensateur. Ce temps est, en effet, très long et peut être mesuré par le comptage d'un nombre correspondant de créneaux de cette même horloge. Si, par exemple, le taux de décharge du condensateur est mille fois inférieur au taux de charge de ce dernier, le niveau de charge correspondant à l'intégration continue entre deux créneaux d'horloge successifs sera déchargé sur un intervalle de temps dilaté correspondant à mille créneaux de cette même horloge. Si le temps de décharge chronométré correspond par exemple à 600 créneaux, on en déduit que l'impulsion laser avait été reçue à un instant précédant l'arrivée du signal d'horloge ayant déclenché la décharge d'un intervalle égal à soixante pour cent (60%) de la période de cette horloge à une constante près dépendant du retard  $oldsymbol{\mathcal{J}}$  .

10

15

20

25

30

La courbe représentative de la charge du condensateur C84 est montrée sur la figure 4. Elle présente une partie initiale <u>a</u>, non linéaire, suivie d'une partie <u>b</u>, linéaire. La charge se poursuit jusqu'à l'instant H d'arrivée du signal d'horloge retardé sur l'entrée 47 de la porte OU 48. Le transistor Q72 se bloque, tandis que le transistor Q71 se débloque et le condensateur C84 se décharge linéairement.

On a montré en trait pointillé sur la figure 4, en <u>d</u>

la droite de la charge théorique du condensateur C84 après

l'arrivée de l'impulsion laser au temps <u>t</u><sub>1</sub>. On a représenté

également les courbes de charge et de décharge théoriques

et réelles pour une impulsion laser parvenant au temps

<u>t</u><sub>2</sub>. Les signaux de fin de conversion sont fournis respectivement aux temps T<sub>2</sub> et T<sub>1</sub> pour les courbes réelles (trait

plein) et T'<sub>2</sub> et T'<sub>1</sub> pour les courbes théoriques (trait

pointillé). La datation des impulsions laser s'effectuant

40 par différence, on constante que T<sub>1</sub>-T<sub>2</sub> = T'<sub>1</sub>-T'<sub>2</sub> et donc

que l'information de datation correspond aux conditions théoriques aussi longtemps que le signal d'horloge faisant passer de la charge rapide à la décharge lente se produit sur une partie rectiligne de la courbe de charge.

Le circuit de retard 46 montré sur la figure 2 a pour 5 fonction de retarder l'application sur la porte OU 48 du signal d'horloge suivant immédiatement l'arrivée de l'impulsion laser pendant un temps  $\delta$  au moins égal au temps  $\delta$ '.nécessaire au condensateur C84 pour acquérir un régime de charge 10 linéaire. L'instant H auquel les transistors Q71 et Q72 sont commutés pour aborder la décharge de C84 est donc toujours séparé de l'arrivée de l'impulsion laser d'un intervalle  $\delta$ qui peutlêtre pris par exemple, égal au dixième de la période de l'horloge 44. Ainsi, la décharge ne peut pas débuter en un point d'une portion non linéaire de la courbe de charge du condensateur C84. Si l'impulsion laser suit de très près une impulsion d'horloge, ou un front d'horloge, il est possible que la durée de charge du condensateur soit légèrement supérieure à une période de cette horloge. Dans ces conditions, 20 le nombre d'impulsions comptées pendant la décharge du condensateur pourra être légèrement supérieur à K, K étant le facteur de dilatation de l'échelle des temps utilisé pour effectuer la datation de la réception d'une impulsion laser entre deux impulsions d'horloge.

Grâce à ces dispositions, il est possible d'utiliser sur le satellite une horloge de fréquence relativement basse, de l'ordre de la dizaine de MHz : On obtient cependant une datation avec une précision supérieure à la nanoseconde, de l'ordre de quelques dizaines de picosecondes. La consomma-30 tion en énergie électrique reste modérée et l'équipement du satellite léger. L'invention prévoit des mesures contribuant à l'obtention d'une telle précision.

25

Pour une parfaite stabilité du niveau du courant de charge utilisé - une très faible erreur sur celui-ci pouvant 35 se traduire par des différences considérables de temps de décharge en échelle dilatée-, on utilise des transistors Q71 et Q72 ayant des caractéristiques aussi voisines que possible.

En outre, comme indiqué précédemment, le courant de 40 charge du condensateur C84 n'est pas rigoureusement égal à

la différence (I-i) des courants issus des générateurs 66 et 80, mais à la différence entre le courant de collecteur (point 76) du transistor Q72 et le courant i. Ce courant de collecteur ést lui-même égal à la différence du courant I et du courant base-émetteur du transistor Q72. Le courant baseémetteur de ce transistor pouvant varier, on régule le courant I et, étant donné que le transistor Q72 n'entre en fonctionnement que pendant de brèves durées, on effectue de préférence une régulation du courant de collecteur Q71. Ainsi, pendant les périodes de conduction du transistor Q71, la tension de collecteur (tension au point 75) est prélevée par le comparateur 70 et comparée à une tension de référence admise sur l'entrée 74 de ce comparateur. Le courant du générateur 66 est ajusté en fonction du signal d'erreur appa-15 raissant à la sortie du comparateur 70. Le signal de tension de collecteur est représentatif du courant collecteur traversant la résistance R78. Les transistors Q71 et Q72 étant très voisins l'un de l'autre, tant en ce qui concerne leur environnement que leurs caractéristiques, la compensation du cou-20 rant I, pour tenir compte des variations du courant baseémetteur de l'un, est convenable, à une très faible erreur près, pour tenir compte des variations du courant baseémetteur de l'autre. Lorsque le transistor Q72 entre en conduction, son courant de collecteur, qui assure la charge du condensateur C84 en combinaison avec le courant <u>i</u> est 25 ainsi bien maintenu à une valeur constante, avec une précision dépendant de celle de la tension de référence Zener sur l'entrée 74.

L'interface 50 de la figure 2 a un rôle de conversion ou d'adaptation des signaux produits ou reçus par les circuits représentés, qui sont réalisés en logique ECL, à une logique TTL ou C MOS, dans laquelle se trouvent réalisées les autres portions du système de traitement des informations et de la datation selon l'invention. Ainsi, on applique à l'entrée 205 de l'interface un signal de remise à zéro RAZ, qui entraîne la remise à zéro de la bascule 28 par la ligne 53. Une 'sortie 201 de l'interface 50 fournit les signaux d'horloge à la fréquence des signaux présents sur la ligne 54. Une sortie 203 transmet à l'extérieur de l'interface un signal de début de conversion dès qu'un tel signal apparaît sur la ligne 51. Enfin, la ligne 92 connectée à la sortie du détecteur

30

40

2493553 de niveau 88 transmet un signal de fin de conversion ainsi qu'il est expliqué auparavant.

On se réfère maintenant à la figure 3. Le circuit de mesure représenté sur cette figure est destiné à effectuer le chronométrage de la durée de décharge du circuit du condensateur C84 sous l'action du courant de décharge <u>i</u>.

5

10

15

20

25

30

35

Un compteur 221 est alimenté sur sa sortie 223 par les impulsions d'horloge issues de la sortie 201 de l'interface 50 à la fréquence de ces impulsions à l'entrée de la bascule 41. Ce compteur "tourne" librement, c'est-à-dire qu'il compte en permanence à partir de sa valeur initiale jusqu'à sa capacité maximale, après quoi, il reprend le comptage à sa valeur initiale et ainsi de suite, et cela aussi longtemps qu'il reçoit des impulsions d'horloge. Il est relié, par une liaison multibits 219, à deux registres 218 et 229. Le registre 218 possède une entrée de commande 217 reliée à la sortie 203 de l'interface 50 pour lire dans le registre 218 le contenu du compteur au moment où l'impulsion de début de conversion est engendrée à la sortie 203 de l'interface 50. Le registre 229 est propre à lire l'état des étages de poids les plus faibles, par exemple au nombre de douze, du compteur 221 lorsque son entrée 231 reçoit l'indication du signal de fin de conversion à partir de la ligne 92 de la figure 2. Il enregistre donc l'état instantané de ces étages de poids faibles du compteur 221 au moment où la fin de la décharge est détectée.

Les sorties des registres 218 et 229 sont connectées respectivement aux entrées 225 et 234 d'un dispositif d'écriture qui introduit le contenu de ce registre dans une mémoire 237 par une ligne 235 reliant la sortie du dispositif d'écriture à l'entrée 236 de cette mémoire. La mémoire 237 est associée à un dispositif de lecture 238 qui commande la sortie en série des informations mémorisées sur une sortie 242 par l'intermédiaire d'une ligne de commande 240.Ce circuit de lecture comprend deux entrées, une entrée de cadencement 241 et une entrée d'autorisation de transfert 239 pour permettre la commande par le circuit de lecture du transfert bit à bit hors de la mémoire sur la sortie 242.

Dans l'application aux satellites envisagée, les bits de sortie série sur la ligne 242 sont transmis par télémesure à une station au sol chargée de centraliser les informations nécessaires à la synchronisation des horloges.

La très grande précision de fonctionnement du circuit de datation qui vient d'être décrit permet de tirer parti

5 de rapports de dilatation de l'échelle de temps très importants, supérieurs à 500 et pouvant dépasser mille, pour la mesure du temps séparant l'arrivée de l'impulsion à dater de l'impulsion d'horloge suivante. De tels facteurs de dilatation qui résultent du rapport entre le taux de charge et

10 de décharge du condensateur utilisé pour la dilatation seraient illusoires en l'absence d'une très haute précision dans le temps des opérations de commutation liées à la datation, précisions autorisées par les diverses caractéristiques de réalisation qui ont été décrites.

## REVENDICATIONS

1. Dispositif de datation d'un évènement par rapport à une référence de temps fournie par des signaux d'horloge comprenant :

un circuit d'intégration (C84) ;

5

10

15

40

des moyens (80, 66) pour produire un signal de charge et un signal de décharge de ce circuit d'intégration dont les amplitudes respectives sont telles que la vitesse de charge du circuit d'intégration soit grande par rapport à la vitesse de décharge;

des moyens de commande (28, 41) pour déclencher l'application du signal de charge à ce circuit d'intégration en réponse à une impulsion représentative dans le temps de l'évènement à dater et pour interrompre l'application du signal de charge de ce circuit d'intégration et initier sa décharge en réponse à un signal d'horloge suivant ladite impulsion;

un détecteur (88), propre à détecter qu'un niveau de décharge prédéterminé a été atteint par le circuit d'intégration; et un dispositif de mesure (221, 218, 229) du temps écoulé entre le début de la décharge et la détection dudit niveau de décharge prédéterminé,

- caractérisé en ce que les moyens pour produire le signal de charge comportent des moyens (66, Q71, R78) propres à faire passer un premier courant prédéterminé dans un premier circuit (M, 37, 75) indépendant du circuit d'intégration, et les moyens de commande comportent des moyens de commutation (Q71, Q72) pour diriger ledit premier courant prédéterminé de ce premier circuit vers le circuit d'intégration (C84) en réponse à l'impulsion représentative de l'évènement à dater.

- 2. Dispositif selon la revendication 1, caractérisé en ce que les moyens de commutation comprement un premier et un deuxième organes de commutation (Q71 et Q72) respectivement montés sur le premier circuit et sur le circuit d'intégration, lesdits organes de commutation étant branchés pour fonctionner en opposition en réponse à ladite impulsion représentative de l'évènement à dater et audit signal d'horloge suivant ladite impulsion.

- 3. Dispositif selon la revendication 2, caractérisé en ce que les organes de commutation ont des caractéristiques électriques sensiblement identiques pour affecter le courant prédéterminé de la même façon.

- 4. Dispositif selon l'une des revendications 2 ou 3, caractérisé en ce que les organes de commutation sont respectivement constitués par un premier et un second transistors (Q71, Q72) dont les émetteurs sont connectés en commun à la sortie d'un générateur de courant (66).

- 5. Dispositif selon l'une quelconque des revendications 2 à 4, caractérisé en ce que le générateur (66) de premier courant prédéterminé est réglable et placé sous la commande d'un détecteur de niveau de courant (70) traversant le premier circuit à la sortie du premier organe de commutation pour compenser les éventuelles variations des caractéristiques électriques desdits organes.

- 6. Dispositif selon l'une des revendications l à 5, caractérisé en ce que les moyens pour produire le signal de charge et de décharge comportent un générateur de courant de décharge (80) et les moyens de commande sont propres à appliquer ce courant de décharge dans le circuit d'intégration (C84) en opposition audit premier courant déterminé en réponse à l'impulsion à dater et modifier l'application de ce courant de décharge en réponse à la détection dudit niveau de décharge prédéterminé.

- 7. Dispositif selon la revendication 6, caractérisé en ce que les moyens d'application du courant de décharge comportent un dispositif de commutation (36) du courant de décharge propre à, dans une première position, court-circuiter le circuit d'intégration et, dans une deuxième position, appliquer le courant de décharge audit circuit d'intégration.

- 8. Dispositif selon l'une quelconque des revendications l à 7, caractérisé en ce que les moyens de commande comportent en outre une première bascule (28) déclenchée en réponse à ladite impulsion représentative de l'évènement à dater et une deuxième bascule (41) validée en réponse à ladite impulsion pour basculer en réponse à une impulsion d'horloge suivant immédiatement l'impulsion représentative de l'évènement à dater, lesdits moyens de commutation (Q71, Q72) étant placés sous la commande de ladite première et de ladite deuxième bascules.

- 9. Dispositif selon l'une des revendications l à 7, caractérisé en ce que les moyens de commande comportent un circuit à retard propre à retarder l'interruption de la charge

du circuit d'intégration pour un temps au moins égal au temps

mis par ce dernier pour atteindre un régime de charge linéaire.

- 10. Dispositif selon l'une des revendications précédentes, caractérisé en ce que le dispositif de chronométrage comporte des moyens (221) de comptage des impulsions de l'horloge de référence.

- 11. Dispositif selon la revendication 10, caractérisé en ce que le dispositif de chronométrage comporte en outre des moyens (226) de lecture de l'état instantané desdits moyens de comptage au début et à la fin de la période de décharge sans modifier le fonctionnement desdits moyens de comptage lo en réponse auxdits signaux d'horloge de référence.

- 12. Dispositif selon l'une des revendications précédentes, caractérisé en ce que le rapport entre les taux de charge et de décharge de l'intégrateur est supérieur à cinquents et, de préférence au moins égal à mille.

Fig. 6