(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3871381号

(P3871381)

(45) 発行日 平成19年1月24日(2007.1.24)

(24) 登録日 平成18年10月27日(2006.10.27)

(51) Int.C1.

F1

HO3K 19/0175 (2006.01)

HO3H 11/28 (2006.01)HO3K 19/00 101F

HO3H 11/28

請求項の数 2 (全 17 頁)

(21) 出願番号 特願平8-253815

(22) 出願日 平成8年9月4日(1996.9.4)

(65) 公開番号 特開平9-130229

(43) 公開日 平成9年5月16日(1997.5.16)

審査請求日 平成15年8月25日(2003.8.25)

(31) 優先権主張番号 08/523,165

(32) 優先日 平成7年9月5日(1995.9.5)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国テキサス州78729, オ

ースティン, ウエスト・パーク・レーン

7700

(74) 代理人 100083574

弁理士 池内 義明

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 アリ・レザ・ファーハン

アメリカ合衆国オレゴン州97007、ビ

ーバートン、サウスウエスト・レンド・

ドライブ 7708

最終頁に続く

(54) 【発明の名称】可変出力インピーダンスを有するバッファ回路

## (57) 【特許請求の範囲】

## 【請求項1】

可変出力インピーダンスを有するバッファ回路(20)であつて、

前記バッファ回路(20)の入力端子(30)に結合された抵抗素子(32)、

電源電圧端子に結合された第1の電流電極、制御電極、および前記バッファ回路(20)

の入力端子(30)に結合された第2の電流電極を有する第1のトランジスタ(33)

、

前記抵抗素子(32)の第1の端子に結合された第1の入力端子、基準電圧を受けるための第2の入力端子、および前記第1のトランジスタ(33)の制御電極に結合された出力端子を有するフィードバック増幅器(40)、

前記電源電圧端子に結合された第1の電流電極、前記フィードバック増幅器(40)の出力端子に結合された制御電極、および第2の電流電極を有する第2のトランジスタ(34)、

前記第2のトランジスタ(34)の第2の電流電極に結合され入力電圧を受けるための入力端子、および前記入力電圧の電圧レベルに対応するデジタルコードを提供するための複数の出力端子を有するアナログ・デジタル変換器(24)、そして

各々前記電源電圧端子に結合された第1の電流電極、前記デジタルコードの対応するビットの所定の論理状態に応じてデータ信号を受けるために選択的に結合される制御電極、そして前記出力ドライバ回路の出力端子に結合されて出力信号を提供するための第2の電流電極を有する、複数の2進重み付けトランジスタ(150, 151, 152)を有する

出力ドライバ回路（53）、

を具備することを特徴とする可変出力インピーダンスを有するバッファ回路（20）。

【請求項2】

可変出力インピーダンスを有するバッファ回路（20）であって、

第1の所定の入力電圧を提供するよう結合された抵抗器であって、該抵抗器は前記バッファ回路の外部に設けられかつ所望の出力インピーダンスの倍数の抵抗値を有するもの、

前記第1の所定の入力電圧を受けるための入力端子、および前記第1の所定の入力電圧の電圧レベルに対応するプルアップデジタルコードを提供するための複数の出力端子を有するプルアップアナログ - デジタル変換器（22）、

第2の所定の入力電圧を受けるための入力端子、および前記第2の所定の入力電圧の電圧レベルに対応するプルダウンデジタルコードを提供するための複数の出力端子を有するプルダウンアナログ - デジタル変換器（24）、そして

出力ドライバ回路（53）であって、

各々第1の電源電圧端子に結合された第1の電流電極、前記プルアップデジタルコードの対応するビットの所定の論理状態に応じて第1のデータ信号を受けるよう選択的に結合される制御電極、そして出力端子に結合され出力信号をプルアップするための第2の電流電極を有する、複数の2進重み付けプルアップトランジスタ（150, 151, 152）、そして

各々第2の電源電圧端子に結合された第1の電流電極、前記プルダウンデジタルコードの対応するビットの所定の論理状態に応じて第2のデータ信号を受けるよう選択的に結合される制御電極、そして前記出力端子に結合され前記出力信号をプルダウンするための第2の電流電極を有する、複数の2進重み付けプルダウントランジスタ（153, 154, 155）、

を具備する前記出力ドライバ回路（53）、

を具備することを特徴とする可変出力インピーダンスを有するバッファ回路（20）。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は一般的には回路に関し、かつより特定的には、可変出力インピーダンスを有する出力バッファ回路に関する。

【0002】

【従来の技術】

マイクロプロセッサ、メモリ、その他のような、集積回路においては、信号は伝送ラインを使用して比較的長い距離にわたり導かれことがある。伝送ラインはデジタル信号を伝送するためにバス、プリント回路基板トレース、または他の形式の比較的長い金属ラインとすることができる。典型的には、プリント回路基板トレースは50および75オームの間の特性インピーダンスを有する。該伝送ラインの受信端、または遠端（far end）、は典型的には論理回路の入力に接続され、該論理回路は入力インピーダンスが伝送ラインの特性インピーダンスより高い。もし伝送ラインの遠端に結合されたインピーダンスが伝送ラインのインピーダンスと異なれば、信号は送信端へと反射し戻され、該信号をその論理状態に対して予定された定常状態の電圧をオーバーシュートさせる。該信号は近端（near end）および遠端の間を何回も行き来して反射し、両方の端部において信号の発振的ふるまいを生じさせる。この反復される信号のオーバーシュートおよびアンダーシュートは通常「リングング」として知られ、かつその結果はノイズ耐性の低下、および信号が遠端において有効になり、かつ有効な状態に留まるようになるための時間が増大することになる。

【0003】

【発明が解決しようとする課題】

伝送ラインの長さにわたり信号を「ドライブ」するのに充分な電流を提供するためにドライバ回路が使用される。CMOS（相補型金属酸化物半導体）ドライバ回路は一般に正電

10

20

30

40

50

圧電源端子およびグランド端子の間に直列に接続されたPチャネルトランジスタおよびNチャネルトランジスタを含む。該トランジスタのゲートは入力信号を受け、かつ該ドライバ回路の出力端子は前記トランジスタの間に配置される。Pチャネルトランジスタは「プルアップ」トランジスタとして機能し、かつNチャネルトランジスタは「プルダウン」トランジスタとして機能する。ドライバ回路の出力インピーダンスは該ドライバ回路が反射した信号を吸収しかつインギングを防止するために伝送ラインの特性インピーダンスと整合すべきである。これによってより落ちついた波形、良好なノイズ耐性および改善された信号タイミングマージンを生じる結果となる。しかしながら、ドライバ回路がドライブすることを要求される負荷インピーダンスは該ドライバ回路が導入される特定の用途に応じて変化する。

10

## 【0004】

GTL（ガニングトランシーバロジック：Gunning transceiver Logic）はますます普及しつつあるロジック形式である。GTLはよく知られたECL（エミッタカップルドロジック）ロジック形式と比較し得る論理スイングを有する。しかしながら、GTLは比較的低い電力消費、高速度を有し、かつCMOSプロセスによって実施できる。GTLレベルのような、比較的低い論理スイングを有する論理レベルを使用する集積回路においては、小さな量のリングインギングでもノイズ耐性が大幅に低下することがあり得る。また、例えばCMOS論理レベル、と比較して信号タイミングのマージンが大幅に悪化することがある。

## 【0005】

20

したがって、本発明の目的は、このような従来の装置の不都合を除去することにある。

## 【0006】

## 【課題を解決するための手段】

一般に、本発明は調整可能な出力インピーダンスを有する出力バッファ回路を提供する。外部抵抗が該出力バッファ回路の入力とグランドに結合された電源電圧端子の間に接続される。前記抵抗は出力バッファの所望の出力インピーダンスの倍数の抵抗を有する。出力インピーダンスは前記抵抗にわたって検知された電圧レベルをアナログ・デジタル（A/D）変換器を使用してデジタル符号に変換することにより調整される。該A/D変換器はデジタル信号を2進カウンタに提供するための比較器を含む。前記2進カウンタは前記比較器からのデジタル信号に応じてカウントアップまたはカウントダウンを行ない外部抵抗の抵抗値と整合するよう2進重み付けされたトランジスタアレイの抵抗を調整する。前記カウンタからのデジタル符号はまた出力ドライバのインピーダンスを調整するために提供され、該出力ドライバは複数の2進重み付けプルアップトランジスタおよび2進重み付けプルダウントランジスタを有する。示された実施形態では、複数のプルアップトランジスタのための2進カウンタおよびプルアップA/D変換器ならびに複数のプルダウントランジスタのための2進カウンタおよびプルダウンA/D変換器がある。前記カウンタは出力バッファ回路の出力ノードに結合された、伝送ラインのような、負荷の特性インピーダンスに整合させるため前記プルアップトランジスタおよび前記プルダウントランジスタのドライブ強度およびインピーダンスを調整するために2進重み付けプルアップトランジスタおよび2進重み付けプルダウントランジスタの内の1つまたはそれ以上を選択するためにデジタル符号を提供する。

30

## 【0007】

40

出力バッファ回路のインピーダンスを負荷の特性インピーダンスに整合させることにより反射された信号が吸収されるようにすることができ、したがってリングインギングを防止する。この結果より落ちついた波形、良好なノイズ耐性、および改善された信号タイミングのマージンが得られる。また、前記出力バッファ回路の出力インピーダンスは外部抵抗の抵抗値を変えることにより容易に調整でき、出力バッファ回路を導入した集積回路メモリのような、集積回路が種々の負荷インピーダンスをドライブできるようにする。また、前記A/D変換器はダイの温度および電源電圧の変化を補償するためにフィードバックを使用する。

50

## 【0008】

## 【発明の実施の形態】

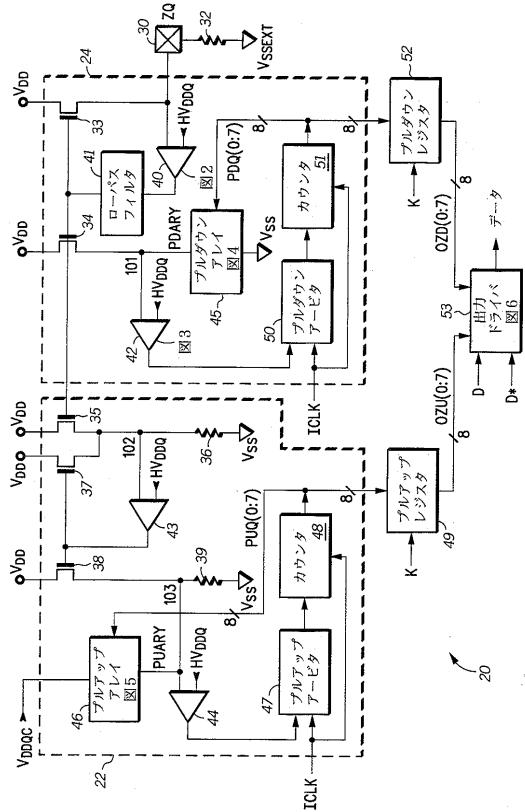

本発明は図1～図6を参照することによりさらに完全に説明することができる。図1は、部分的ブロック図形式、部分的回路図形式、および部分的論理図形式で、本発明の一実施形態に係わる可変出力インピーダンスを有する出力バッファ回路20を示す。出力バッファ回路20はプルアップA/D変換器22、プルダウンA/D変換器24、プルアップレジスタ49、プルダウンレジスタ52、および出力ドライバ53を含む。プルアップA/D変換器22はNチャネルソースフォロアトランジスタ35, 37および38、抵抗36および39、フィードバック増幅器43、比較器44、2進重み付けプルアップトランジスタアレイ46、プルアップアービタ(pull-up arbiter)47、および8ビット2進カウンタ48を含む。プルダウンA/D変換器24はNチャネルソースフォロワトランジスタ33および34、フィードバック増幅器40、ローパスフィルタ41、比較器42、2進重み付けプルダウントランジスタアレイ45、プルダウンアービタ(pull-down arbiter)50、および8ビット2進カウンタ51を含む。

## 【0009】

プルダウンA/D変換器24においては、Nチャネルソースフォロワトランジスタ33は“ $V_{DD}$ ”と名付けられた電源電圧端子に接続されたドレイン(電流電極)、ゲート(制御電極)、および“ $ZQ$ ”と名付けられた電圧を受けるためにパッド30に接続されたソース(電流電極)を有する。抵抗32はパッド30に接続された第1の端子、および“ $V_{SEXT}$ ”と名付けられた電源電圧端子に接続された第2の端子を有する。フィードバック増幅器40はパッド30に接続された第1の入力端子、“ $HV_{DDQ}$ ”と名付けられた基準電圧を受けるための第2の入力端子、および出力端子を有する。ローパスフィルタ41はフィードバック増幅器40の出力端子に接続された入力端子、およびNチャネルトランジスタ33のゲートに接続された出力端子を有する。Nチャネルトランジスタ34は $V_{DD}$ に接続されたドレイン、Nチャネルトランジスタ33のゲートに接続されたゲート、およびノード101に接続されたソースを有する。比較器42はNチャネルトランジスタ34のソースに接続された第1の入力端子、基準電圧 $HV_{DDQ}$ を受けるための第2の入力端子、および出力端子を有する。プルダウンアービタ50は比較器42の出力端子に接続された第1の入力端子、“ $ICLK$ ”と名付けられたクロック信号を受けるための第2の入力端子、および出力端子を有する。8ビット2進カウンタ51はプルダウンアービタ50の出力端子に接続された第1の入力端子、クロック信号 $ICLK$ を受けるための第2の入力端子、および“ $PDQ(0:7)$ ”と名付けられたデジタルカウント値を提供するための複数の出力端子を有する。プルダウントランジスタアレイ45はカウンタ51の複数の出力端子に接続された複数の入力端子、および比較器42の第1の入力に接続され“ $PDARY$ ”と名付けられたプルダウンアレイ電圧を提供するための出力端子を有する。

## 【0010】

プルアップA/D変換器22においては、Nチャネルソースフォロワトランジスタ35は $V_{DD}$ に接続されたドレイン(電流電極)、Nチャネルトランジスタ34のゲートに接続されたゲート(制御電極)、およびノード102に接続されたソース(電流電極)を有する。Nチャネルソースフォロワトランジスタ37は $V_{DD}$ に接続されたドレイン、ゲート、およびノード102においてNチャネルトランジスタ35のソースに接続されたソースを有する。抵抗36はNチャネルトランジスタ35および37のソースに接続された第1の端子、および“ $V_{SS}$ ”と名付けられた電源電圧端子に接続された第2の端子を有する。フィードバック増幅器43はNチャネルトランジスタ35および37のソースに接続された第1の入力端子、および基準電圧 $HV_{DDQ}$ を受けるための第2の入力端子、およびNチャネルトランジスタ37のゲートに接続された出力端子を有する。Nチャネルソースフォロワトランジスタ38は $V_{DD}$ に接続されたドレイン、Nチャネルトランジスタ37のゲートに接続されたゲート、およびノード103に接続されたソースを有する。抵抗39はノード103においてNチャネルトランジスタ38のソースに接続された第1の端子

、および  $V_{S_S}$  に接続された第 2 の端子を有する。比較器 4 4 は N チャネルトランジスタ 3 8 のソースに接続された第 1 の入力端子、  $H V_{D_D Q}$  を受けるための第 2 の入力端子、および出力端子を有する。プルアップアレイ 4 6 は “  $V_{D_D Q_C}$  ” と名付けられた電圧を受けるための入力端子、“  $P U Q (0 : 7)$  ” と名付けられたデジタルカウント値を受けるための複数の入力端子、および比較器 4 4 の第 1 の入力端子に接続された出力端子を有する。プルアップアービタ 4 7 は比較器 4 4 の出力端子に接続された第 1 の入力端子、クロック信号  $I C L K$  を受けるための第 2 の入力端子、および出力端子を有する。8 ビット 2 進カウンタ 4 8 はプルアップアービタ 4 7 の出力端子に接続された第 1 の入力端子、クロック信号  $I C L K$  を受けるための第 2 の入力端子、およびデジタルカウント値  $P U Q (0 : 7)$  を提供するための複数の出力端子を有する。

10

#### 【 0 0 1 1 】

プルダウンレジスタ 5 2 はカウンタ 5 1 の複数の出力端子に接続された複数の入力端子、“  $K$  ” と名付けられたクロック信号を受けるための入力端子、および “  $O Z D (0 : 7)$  ” と名付けられたプルダウンレジスタード ( *reg ister ed* ) デジタルカウント値を提供するための複数の出力端子を有する。プルアップレジスタ 4 9 はカウンタ 4 8 の複数の出力端子に接続された複数の入力端子、クロック信号  $K$  を受けるための入力端子、および “  $O Z U (0 : 7)$  ” と名付けられたプルアップレジスタード ( *reg ister ed* ) デジタルカウント値を提供するための複数の出力端子を有する。出力ドライバ 5 3 はプルアップレジスタ 4 9 の複数の出力端子に接続された第 1 の複数の入力端子、プルダウンレジスタ 5 2 の複数の出力端子に接続された第 2 の複数の入力端子、“  $D$  ” と名付けられたデータ信号を受けるための第 1 の入力端子、“  $D^*$  ” と名付けられたデータ信号を受けるための第 2 の入力端子、および「データ (  $D A T A$  ) 」と名付けられた出力信号を提供するための出力端子を有する。データ信号  $D$  および  $D^*$  は差動データ信号である。

20

#### 【 0 0 1 2 】

出力バッファ回路 2 0 は電圧をデジタル符号に変換するためにアナログ - デジタル ( A / D ) 変換器を使用する。該デジタル符号またはデジタルコードは出力バッファ回路 2 0 によってドライブされる負荷のインピーダンスに整合するため出力バッファ回路 2 0 の出力インピーダンスを調整するために出力ドライバのプルアップおよびプルダウントランジスタ双方の出力ドライブ強度を調整するために使用される。抵抗 3 2 は外部抵抗でありかつ出力バッファ回路 2 0 の入力端子に結合される。該抵抗は出力バッファの所望の出力インピーダンスの倍数となるよう選択される抵抗値を有する。例えば、もし伝送ラインのインピーダンスが 5 0 オームであれば、抵抗 3 2 の抵抗値は 5 0 の 5 倍、または 2 5 0 オームとすることができる。

30

#### 【 0 0 1 3 】

動作においては、出力バッファ回路 2 0 は、伝送ラインのような、負荷を  $G T L$  レベルで入力データ信号に応答してドライブする。出力ドライバ 5 3 の出力インピーダンスは外部抵抗 3 2 における検知された電圧レベルをデジタルコードに変換することにより調整される。該デジタルコードは複数の 2 進重み付けプルアップトランジスタの内の少なくとも 1 つおよび複数の 2 進重み付けプルダウントランジスタの内の少なくとも 1 つを選択して出力ドライバ 5 3 ( 図 6 を参照 ) のドライブ強度を調整する。プルアップドライブ強度は出力ドライバ 5 3 の前記複数の 2 進重み付けプルアップトランジスタの間で選択するためにプルアップ A / D 変換器 2 2 を使用してセットされる。プルダウンドライブ強度は出力ドライバ 5 3 の前記複数の 2 進重み付けプルダウントランジスタの間で選択するためにプルダウン A / D 変換器 2 4 を使用してセットされる。

40

#### 【 0 0 1 4 】

フィードバック增幅器 4 0 、ローパスフィルタ 4 1 、および N チャネルトランジスタ 3 3 はフィードバック增幅器 4 0 の第 1 の入力端子における電圧を基準電圧  $H V_{D_D Q}$  に整合させるために使用される。フィードバック增幅器 4 0 の入力端子の電圧を基準電圧  $H V_{D_D Q}$  にセットすることにより、 N チャネルトランジスタ 3 3 をとある比較的一定の電流が N チャネルトランジスタ 3 4 をとある比較的一定の電流を生じさせる。 N チャネルトラン

50

ジスタ 3 4 をとおりプルダウンアレイ 4 5 に流れる電流はノード 1 0 1 に電圧を生じさせる。ノード 1 0 1 の電圧 P D A R Y は比較器 4 2 の第 1 の入力端子に提供される。比較器 4 2 は基準電圧 H V<sub>D D Q</sub> に対し電圧 P D A R Y の相対振幅の比較を行なう。もしノード 1 0 1 の電圧が基準電圧 H V<sub>D D Q</sub> より大きければ、比較器 4 2 からの論理ハイの出力信号がプルダウンアービタ 5 0 に提供されてカウンタ 5 1 が P D Q ( 0 : 7 ) の値を 1 だけ増大するようにさせる。これはプルダウンアレイ 4 5 の抵抗を減少させ、したがって電圧 P D A R Y の振幅を低減する。カウンタ 5 1 はプルダウンアレイ 4 5 において抵抗値が所定の許容範囲内で抵抗 3 2 の抵抗値に整合するまでカウントアップを行なう。2 進カウンタ 5 0 は同期カウンタである。したがって、プルダウンアービタ 5 0 がカウンタ 5 1 によって受信された信号をクロック信号 I C L K に同期させるために使用される。他の実施形態では、もし 2 進カウンタが同期的なものでなければ、アービタ 4 7 および 5 0 は必要ではなくなる。

#### 【 0 0 1 5 】

もし電圧 P D A R Y が依然として電圧 H V<sub>D D Q</sub> より大きければ、比較器 4 2 の出力信号は論理ハイの電圧でありカウンタ 5 1 を 1 だけカウントアップさせ、プルダウンアレイ 4 5 の抵抗を低下させ、したがって電圧 P D A R Y を低下させる。カウンタ 5 1 の出力ビットはプルダウンアレイ 4 5 の抵抗を低減するためにプルダウンアレイ 4 5 に与えられる。P D Q ( 0 : 7 ) のデジタル値もまたプルダウンレジスタ 5 2 に提供される。クロック信号 K に応答して、プルダウンレジスタ 5 2 は登録されたまたはレジスター ( r e g i s t e r e d ) カウント値 O Z D ( 0 : 7 ) を提供しプルダウントランジスタの出力インピーダンスを調整する。登録されたカウント値 O Z D ( 0 : 7 ) は前記カウント値 P D Q ( 0 : 7 ) に対応する。比較器 4 2 は電圧 P D A R Y が基準電圧 H V<sub>D D Q</sub> に等しくなるまで H V<sub>D D Q</sub> に対して P D A R Y の比較を続ける。

#### 【 0 0 1 6 】

逆に、もし電圧ノード 1 0 1 が基準電圧 H V<sub>D D Q</sub> より低ければ、比較器 4 2 からの論理ローの出力信号がプルダウンアービタ 5 0 に提供されてカウンタ 5 1 に P D Q ( 0 : 7 ) の値を 1 だけ低減させる。これはプルダウンアレイ 4 5 の抵抗を増大させ、したがって電圧 P D A R Y の振幅を増大させる。カウンタ 5 1 はプルダウンアレイ 4 5 において抵抗値が所定の許容範囲内で抵抗 3 2 の抵抗値と整合する値に到達するまでカウントダウンを行なう。2 進カウンタ 4 8 および 5 1 は伝統的な 8 ビット同期カウンタであり 2 進数 0 0 0 0 0 0 0 0 および 1 1 1 1 1 1 1 1 の間でカウントアップおよびカウントダウンを行なうことができるものであるが上限および下限に到達したとき循環 ( w r a p a r o u n d ) しない。

#### 【 0 0 1 7 】

また、出力バッファ回路 2 0 は出力データ信号を G T L レベルでドライブするから、基準電圧 H V<sub>D D Q</sub> は V<sub>D D Q</sub> に提供される電源電圧のほぼ半分である。V<sub>D D Q</sub> は出力ドライバ 5 3 のための電源端子である。もし V<sub>D D</sub> が 3 . 0 ボルトであれば、V<sub>D D Q</sub> は 1 . 2 ボルトでありかつ H V<sub>D D Q</sub> は約 0 . 6 ボルトである。V<sub>D D Q C</sub> は V<sub>D D Q</sub> のローパスろ波されたものであり、かつしたがって約 1 . 2 ボルトに等しい。他の実施形態では、電源および基準電圧レベルは異なるものとすることができます。

#### 【 0 0 1 8 】

プルダウン A / D 変換器 2 4 が出力ドライバ 5 3 の前記複数のプルダウントランジスタのドライブ強度を調整するのと同時に、プルアップ A / D 変換器 2 2 は出力ドライバ 5 3 の前記複数のプルアップトランジスタのドライブ強度を調整している。プルアップ A / D 変換器 2 2 はプルダウン A / D 変換器 2 4 と同様に動作する。N チャネルトランジスタ 3 5 および 3 7 を流れる電流は抵抗 3 6 の間に所定の電圧降下を生じさせる。ノード 1 0 2 において結果として生じる所定の電圧はフィードバック増幅器 4 3 の第 1 の入力端子に提供される。

#### 【 0 0 1 9 】

フィードバック増幅器 4 3 はノード 1 0 2 の電圧を基準電圧 H V<sub>D D Q</sub> と比較し、かつ出

10

20

30

40

50

力信号をNチャネルトランジスタ37および38のゲートに提供してノード102の電圧をほぼ基準電圧 $HV_{DDQ}$ に等しくなるよう調整する。フィードバック増幅器43は図2に示されるフィードバック増幅器40と同様のものである。Nチャネルトランジスタ37を流れる電流はNチャネルトランジスタ38を流れる電流を比較的一定のものにし、それによってノード103に抵抗39における電圧降下を生じさせる。抵抗36および39は整合した抵抗であり、かつ抵抗36および39の抵抗値は示された実施形態ではほぼ等しい。抵抗36および39の値はNチャネルトランジスタ37が全ての動作条件および全てのプロセスのコーナー条件に対してノード102を基準電圧 $HV_{DDQ}$ に等しくするのに充分な電流をドライブするように選択される。“PUARY”と名付けられた、ノード103の電圧は2進重み付けプルアップアレイ46および抵抗39の電圧降下の関数であり、かつ比較器44の第1の入力端子に提供される。プルアップアレイ46によってドライブされる電流は電圧PUARYが基準電圧 $HV_{DDQ}$ に整合するためにNチャネルトランジスタ35と同じ電流をドライブしなければならない。比較器44は電圧PUARYを基準電圧 $HV_{DDQ}$ と比較し、かつそれに応じて、アービタ47を介してデジタルカウント信号を2進カウンタ48に提供する。比較器44は、図3に示された、比較器42と同様のものである。

#### 【0020】

もし電圧PUARYが基準電圧 $HV_{DDQ}$ より大きければ、比較器44は論理ハイの電圧を提供してカウンタ48をカウントダウンさせる。デジタルカウント値 $P_{UQ}(0:7)$ はプルアップアレイ46に提供されてプルアップアレイ46の実効抵抗を増大させ、したがって電圧PUARYの振幅を低減する。デジタルカウント値 $P_{UQ}(0:7)$ もまたプルアップレジスタ49に提供される。レジスタ49はクロック信号Kに応答して登録されたデジタルカウント値 $OZU(0:7)$ を出力ドライバ53の複数のプルアップトランジスタに提供し出力ドライバ53のプルアップ出力インピーダンスを調整する。該プルアップインピーダンスはPUARYが基準電圧 $HV_{DDQ}$ に等しい場合に整合される。

#### 【0021】

もし電圧PUARYが基準電圧 $HV_{DDQ}$ より小さければ、比較器44は論理ローの電圧をプルアップアービタ47をとおしてカウンタ48に提供し2進カウンタ48をカウントアップさせ、プルアップアレイ46の実効抵抗を低減し、かつある増分量だけ電圧PUARYを増大させる。デジタルカウント値 $P_{UQ}(0:7)$ が増分され、かつ対応する登録されたデジタルカウント値 $OZU(0:7)$ がクロック信号Kに応答して増分される。該登録されたデジタルカウント値 $OZU(0:7)$ は出力ドライバ53に提供されて出力ドライバ53の前記複数の2進重み付けプルアップトランジスタのインピーダンスを調整する。上に述べたように、出力ドライバ53はGTLレベルで信号を提供するためのものである。GTLはECL(エミッタカップルドロジック)に比較し得る論理スイングを有する。GTLに対する論理ハイレベルの電圧は1.14および1.26ボルトの間に等しくすることができる。論理ローレベルの電圧はゼロボルトに等しくすることができる。他の実施形態では、出力ドライバ53は、CMOS,ECLまたはTTL(トランジスタ-トランジスタロジック)のような、他の論理レベルで信号を提供することができる。

#### 【0022】

出力バッファ回路20は比較的小さなスイング論理レベルを使用したシステムにおいて動作することを意図したものであるから、特にノイズの影響を低減することが重要である。ローパスフィルタ41は内部電源電圧端子 $V_{SS}$ および外部電源電圧端子 $V_{SSEXT}$ の間に高周波ノイズをろ波除去し、この場合 $V_{SS}$ は内部グランドでありかつ $V_{SSEXT}$ は外部グランドに接続されている。前記高周波ノイズはNチャネルトランジスタ33,34および35のゲート電圧によりかつ、集積回路上の他の回路からのような、他の発生源によって導入される。ローパスフィルタ41はまたフィードバック増幅器40の出力端子からフィードバック増幅器40の第1の入力端子への間のフィードバックループに安定性を加える。さらに、フィードバック増幅器40および43によって提供されるフィードバックはまたNチャネルトランジスタ33,34,35,37および38を通る電流に影響

10

20

30

40

50

を与えるダイの温度および供給電圧の変化に対して補償を行なう。図示された実施形態では、抵抗32は $V_{SSEXT}$ を通して外部グランドに接続されていることに注意を要する。しかしながら、他の実施形態では、抵抗32は該抵抗32を内部グランド( $V_{SS}$ )に結合するためにパッド30および他のパッド(図示せず)の間に結合し、 $V_{SS}$ から $V_{SSEXT}$ へのノイズの問題を除去することができる。 $V_{DDQC}$ および基準電圧 $HV_{DDQ}$ における電源ノイズはローパスフィルタ(図示せず)および $V_{DDQ}$ を $V_{DDQC}$ および $HV_{DDQ}$ に変換するために使用される回路中の单一利得増幅器(図示せず)を通してろ波除去し $V_{DDQ}$ を通過させる。

#### 【0023】

内部 $V_{DD}$ ノイズはカレントミラーとして接続されたPチャネルトランジスタを使用する代わりにソースフォロワ構成のNチャネルトランジスタ33, 34, 35, 37および38を使用することにより低減される。もしソースフォロワ構成のNチャネルトランジスタのドレイン電圧 $V_D$ がゲート電圧 $V_G$ からしきい値電圧 $V_T$ を減算したものより小さければ、 $V_G$ の変調によってソース電圧 $V_S$ に変調を生じさせ、かつNチャネルトランジスタは比較的貧弱な電源ノイズ排除を有することになる。しかしながら、もし $V_D$ が $V_G$ から $V_T$ を減算したものより大きければ、 $V_D$ の変調はソースによって排除され、その結果比較的良好な電源ノイズ排除が得られる。したがって、Nチャネルトランジスタ33, 34, 35, 37および38は $V_G - V_T$ より大きな $V_D$ によって動作する。Nチャネルトランジスタ33, 34, 35, 37および38に対するボディタイ(body ties)(図示せず)はさらに $V_G - V_T$ を低減するために $V_{SS}$ に接続されることに注意を要する。

#### 【0024】

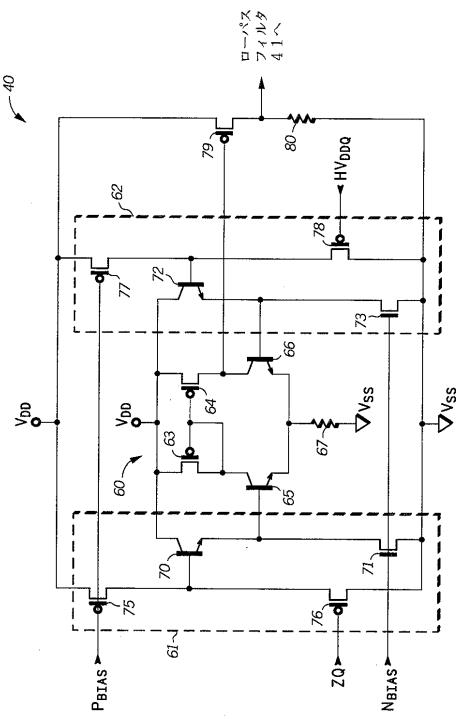

図2は、回路図形式で、図1のフィードバック増幅器40を示す。フィードバック増幅器40は差動増幅器60、レベルシフト回路61および62、Pチャネルトランジスタ79、および抵抗80を含む。差動増幅器60はPチャネルトランジスタ63および64、NPNトランジスタ65および66、そして抵抗67を含む。レベルシフト回路61はPチャネルトランジスタ75および76、NPNトランジスタ70、およびNチャネルトランジスタ71を含む。レベルシフト回路62はPチャネルトランジスタ77および78、NPNトランジスタ72、およびNチャネルトランジスタ73を含む。

#### 【0025】

Pチャネルトランジスタ63は $V_{DD}$ に接続されたソース、および一緒に接続されたゲートおよびドレインを有する。Pチャネルトランジスタ64は $V_{DD}$ に接続されたソース、Pチャネル63のゲートに接続されたゲート、およびドレインを有する。NPNトランジスタ65はPチャネルトランジスタ63のドレインに接続されたコレクタ、ベース、およびエミッタを有する。NPNトランジスタ66はPチャネルトランジスタ64のドレインに接続されたコレクタ、ベース、およびNPNトランジスタ65のエミッタに接続されたエミッタを有する。抵抗67はNPNトランジスタ65および66のエミッタに接続された第1の端子、および $V_{SS}$ に接続された第2の端子を有する。NPNトランジスタ70は $V_{DD}$ に接続されたコレクタ、ベース、およびNPNトランジスタ65のベースに接続されたエミッタを有する。Nチャネルトランジスタ71はNPNトランジスタ70のエミッタに接続されたドレイン、バイアス電圧 $N_{BIA}$ を受けるためのゲート、および $V_{SS}$ に接続されたソースを有する。NPNトランジスタ72は $V_{DD}$ に接続されたコレクタ、ベース、およびNPNトランジスタ66のベースに接続されたエミッタを有する。Nチャネルトランジスタ73はNPNトランジスタ72のエミッタに接続されたドレイン、バイアス電圧 $N_{BIA}$ を受けるためのゲート、および $V_{SS}$ に接続されたソースを有する。Pチャネルトランジスタ75は $V_{DD}$ に接続されたソース、バイアス電圧 $P_{BIA}$ を受けるためのゲート、およびNPNトランジスタ70のベースに接続されたドレインを有する。Nチャネルトランジスタ76はPチャネルトランジスタ75のドレインに接続されたソース、電圧 $ZQ$ を受けるためのゲート、および $V_{SS}$ に接続されたドレインを有する。Pチャネルトランジスタ77は $V_{DD}$ に接続されたソース、バイアス電圧 $P_{BIA}$ を

10

20

30

40

50

受けるためのゲート、およびNPNトランジスタ72のベースに接続されたドレインを有する。Pチャネルトランジスタ78はPチャネルトランジスタ77のドレインに接続されたソース、基準電圧HV<sub>DDQ</sub>を受けるためのゲート、およびV<sub>SS</sub>に接続されたドレインを有する。Pチャネルトランジスタ79はV<sub>DD</sub>に接続されたソース、NPNトランジスタ66のコレクタに接続されたゲート、およびローパスフィルタ41(図1)の入力端子に接続されたドレインを有する。抵抗80はPチャネルトランジスタ79のドレインに接続された第1の端子、およびV<sub>SS</sub>に接続された第2の端子を有する。

#### 【0026】

バイアス電圧P<sub>BIA</sub>はPチャネルトランジスタ75および77のゲートに供給されてPチャネルトランジスタ75および77を比較的一定の電流源として機能させる。同様に、バイアス電圧N<sub>BIA</sub>がNチャネルトランジスタ71および73のゲートに供給されてNチャネルトランジスタ71および73を比較的一定の電流源として機能させる。

10

#### 【0027】

動作においては、フィードバック増幅器40は電圧ZQを基準電圧HV<sub>DDQ</sub>と比較し、かつそれに応じて出力電圧をローパスフィルタ41に提供する。レベルシフト回路61および62は電圧ZQおよびHV<sub>DDQ</sub>を、それぞれ、差動増幅器60によって使用できるレベルにレベルシフトする。差動増幅器60はPチャネルトランジスタ63および64を負荷素子として使用した伝統的な差動増幅器である。電圧ZQが基準電圧HV<sub>DDQ</sub>より低い場合は、NPNトランジスタ65を通るよりも多くの電流がNPNトランジスタ66を通って流れ、かつ差動増幅器60はローの電圧をPチャネルトランジスタ79のゲートに提供し、Pチャネルトランジスタ79がより導通するようにさせる。Pチャネルトランジスタ79のドレインはハイの電圧をローパスフィルタ41(図1に示されている)の入力端子に提供する。抵抗80はNチャネルトランジスタ79のドレイン電圧に対するレベルシフト機能を提供する。Nチャネルトランジスタ33(図1)のゲート電圧が増大し、Nチャネルトランジスタ33のドレイン-ソース電流を増大させ、それによって電圧ZQの電圧レベルを該電圧ZQがほぼ基準電圧HV<sub>DDQ</sub>に等しくなるまで上昇させる。

20

#### 【0028】

もし電圧ZQが基準電圧HV<sub>DDQ</sub>より高ければ、NPNトランジスタ66より多くの電流がNPNトランジスタ65を通って流れ、差動増幅器60は比較的ハイの電圧をPチャネルトランジスタ79のゲートに提供し、Pチャネルトランジスタ79が実質的に非導通となるようにする。Pチャネルトランジスタ79のドレインはローの電圧をローパスフィルタ41の入力端子に提供する。Nチャネルトランジスタ33のゲート電圧が低下し、Nチャネルトランジスタ33のドレイン-ソース電流を減少させ、それによって電圧ZQの電圧レベルを該電圧ZQがほぼ基準電圧HV<sub>DDQ</sub>に等しくなるまで低下させる。

30

#### 【0029】

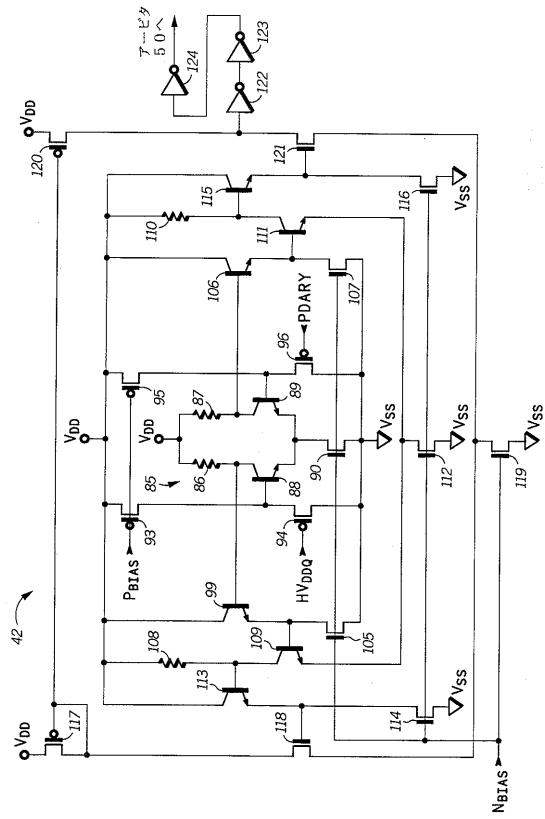

図3は、電気回路図形式で、図1の比較器42を示す。比較器42は差動増幅器85、Pチャネルトランジスタ93, 94, 95, 96, 117および120、Nチャネルトランジスタ105, 107, 112, 114, 116, 118, 119および121、NPNトランジスタ99, 106, 109, 111, 113および115、そしてインバータ122~124を含む。差動増幅器85は抵抗86および87、NPNトランジスタ88および89、およびNチャネルトランジスタ90を含む。

40

#### 【0030】

抵抗86はV<sub>DD</sub>に接続された第1の端子、および第2の端子を有する。抵抗87はV<sub>DD</sub>に接続された第1の端子、および第2の端子を有する。NPNトランジスタ88は抵抗86の第2の端子に接続されたコレクタ、ベース、およびエミッタを有する。NPNトランジスタ89は抵抗87の第2の端子に接続されたコレクタ、ベース、およびNPNトランジスタ88のエミッタに接続されたエミッタを有する。Nチャネルトランジスタ90はNPNトランジスタ88および89のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>を受けるためのゲート、およびV<sub>SS</sub>に接続されたソースを有する。Pチャネルトランジスタ93はV<sub>DD</sub>に接続されたソース、バイアス電圧P<sub>BIA</sub>を受けるためのゲ

50

ート、およびNPNトランジスタ88のベースに接続されたドレインを有する。Pチャネルトランジスタ94はPチャネルトランジスタ93のドレインに接続されたソース、基準電圧HV<sub>DDQ</sub>を受けるためのゲート、そしてV<sub>SS</sub>に接続されたドレインを有する。Pチャネルトランジスタ95はV<sub>DD</sub>に接続されたソース、バイアス電圧P<sub>BIA</sub>Sを受けるためのゲート、NPNトランジスタ89のベースに接続されたドレインを有する。Pチャネルトランジスタ96はPチャネルトランジスタ95のドレインに接続されたソース、プルダウンアレイ電圧P<sub>DARY</sub>を受けるためのゲート、そしてV<sub>SS</sub>に接続されたドレインを有する。NPNトランジスタ99はV<sub>DD</sub>に接続されたコレクタ、NPNトランジスタ88のコレクタに接続されたベース、およびエミッタを有する。Nチャネルトランジスタ105はNPNトランジスタ99のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるためのゲート、そしてV<sub>SS</sub>に接続されたソースを有する。NPNトランジスタ106はV<sub>DD</sub>に接続されたコレクタ、NPNトランジスタ89のコレクタに接続されたベース、およびエミッタを有する。Nチャネルトランジスタ107はNPNトランジスタ106のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるよう接続されたゲート、そしてV<sub>SS</sub>に接続されたソースを有する。

10

### 【0031】

抵抗108はV<sub>DD</sub>に接続された第1の端子、および第2の端子を有する。NPNトランジスタ109は抵抗108の第2の端子に接続されたコレクタ、NPNトランジスタ99のエミッタに接続されたベース、およびエミッタを有する。Nチャネルトランジスタ112はNPNトランジスタ109のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるためのゲート、およびV<sub>SS</sub>に接続されたソースを有する。抵抗110はV<sub>DD</sub>に接続された第1の端子、および第2の端子を有する。NPNトランジスタ111は抵抗110の第2の端子に接続されたコレクタ、NPNトランジスタ106のエミッタに接続されたベース、およびNチャネルトランジスタ112のドレインに接続されたエミッタを有する。NPNトランジスタ113はV<sub>DD</sub>に接続されたコレクタ、NPNトランジスタ109のコレクタに接続されたベース、およびエミッタを有する。Nチャネルトランジスタ114はNPNトランジスタ113のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるためのゲート、およびV<sub>SS</sub>に接続されたソースを有する。NPNトランジスタ115はV<sub>DD</sub>に接続されたコレクタ、NPNトランジスタ111のコレクタに接続されたベース、およびエミッタを有する。Nチャネルトランジスタ116はNPNトランジスタ115のエミッタに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるためのゲート、およびV<sub>SS</sub>に接続されたソースを有する。Pチャネルトランジスタ117はV<sub>DD</sub>に接続されたソース、および一緒に接続されたゲートおよびドレインを有する。Nチャネルトランジスタ118はPチャネルトランジスタ117のゲートおよびドレインに接続されたドレイン、NPNトランジスタ113のエミッタに接続されたゲート、およびソースを有する。Nチャネルトランジスタ119はNチャネルトランジスタ118のソースに接続されたドレイン、バイアス電圧N<sub>BIA</sub>Sを受けるためのゲート、およびV<sub>SS</sub>に接続されたソースを有する。Pチャネルトランジスタ120はV<sub>DD</sub>に接続されたソース、Pチャネルトランジスタ117のゲートに接続されたゲート、およびドレインを有する。Nチャネルトランジスタ121はPチャネルトランジスタ120のドレインに接続されたドレイン、NPNトランジスタ115のエミッタに接続されたゲート、およびNチャネルトランジスタ119のドレインに接続されたソースを有する。インバータ122, 123および124はPチャネルトランジスタ120のドレインとプルダウンアービタ50の第1の入力端子の間に直列に接続されている。

20

30

40

### 【0032】

バイアス電圧P<sub>BIA</sub>SはPチャネルトランジスタ93および95のゲートに提供されて該Pチャネルトランジスタ93および95が比較的一定の電流源として機能するようにさせる。同様に、バイアス電圧N<sub>BIA</sub>SがNチャネルトランジスタ90, 105, 107, 112, 114, 116および119のゲートに供給されて該Nチャネルトランジスタ90, 105, 107, 112, 114, 116および119を比較的一定の電流源とし

50

て機能させる。

【0033】

動作においては、比較器42はフィードバック増幅器40と同様に動作し、かつデジタル信号をアービタ50を介して2進カウンタ51に提供し該カウンタ51をカウントアップまたはカウントダウンさせる。もしプルダウンアレイ電圧P D A R Yが基準電圧H V<sub>D D Q</sub>より高ければ、N P Nトランジスタ89のベース電圧はN P Nトランジスタ88のベース電圧よりも相対的に高く、かつより多くの電流が差動増幅器85のN P Nトランジスタ88よりもN P Nトランジスタ89を通って流れる。N P Nトランジスタ106のベース電圧は低下し、N P Nトランジスタ111のベース電圧を低下させる。抵抗108および110はN P Nトランジスタ109および111からなる差動対のための負荷素子として機能する。N P Nトランジスタ115のベース電圧は増大し、Nチャネルトランジスタ121のゲートの電圧を増大させる。インバータ122の入力端子の電圧は論理ローの電圧へと低下し、かつ直列接続されたインバータ122, 123および124はアービタ50にバッファリングされた論理ハイの電圧を提供する。差動増幅器85は負荷素子として作用する抵抗86および87を有する伝統的な差動増幅器である。 10

【0034】

もしプルダウンアレイ電圧P D A R Yが基準電圧H V<sub>D D Q</sub>より低ければ、N P Nトランジスタ88のベース電圧はN P Nトランジスタ89のベース電圧より高く、かつより多くの電流が差動増幅器85のN P Nトランジスタ85よりもN P Nトランジスタ88を通って流れる。N P Nトランジスタ106のベース電圧が増大し、N P Nトランジスタ111のベース電圧を増大させる。N P Nトランジスタ115のベース電圧は低下し、Nチャネルトランジスタ121のゲート電圧を低下させる。インバータ122の入力端子の電圧は論理ハイの電圧へと増大し、かつ直列接続されたインバータ122, 123および124はバッファリングされた論理ローの電圧をアービタ50に提供する。 20

【0035】

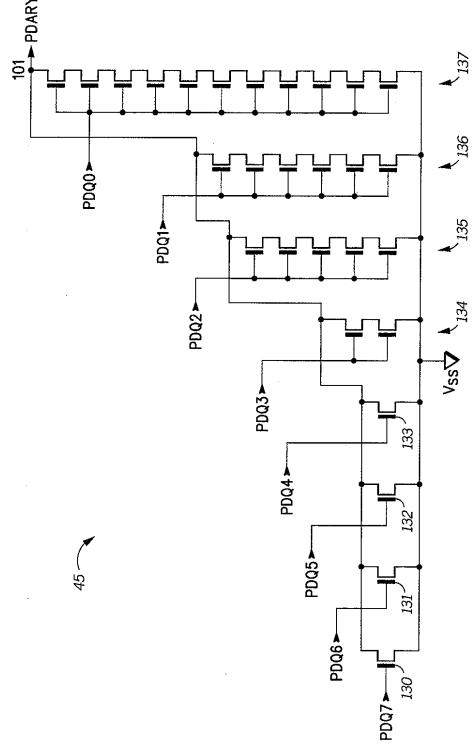

図4は、電気回路図形式で、図1のプルダウン2進重み付けトランジスタアレイ45を示す。プルダウン2進重み付けトランジスタアレイ45はNチャネルトランジスタ130, 131, 132および133、直列接続されたNチャネルトランジスタ134、直列接続されたNチャネルトランジスタ135、直列接続されたNチャネルトランジスタ136、および直列接続されたNチャネルトランジスタ137を含む。 30

【0036】

Nチャネルトランジスタ130はノード101に接続されたドレイン、デジタルカウント値ビットP D Q 7を受けるためのゲート、およびV<sub>S S</sub>に接続されたソースを有する。Nチャネルトランジスタ131はノード101に接続されたドレイン、デジタルカウント値ビットP D Q 6を受けるためのゲート、およびV<sub>S S</sub>に接続されたソースを有する。Nチャネルトランジスタ132はノード101に接続されたドレイン、デジタルカウント値ビットP D Q 5を受けるためのゲート、およびV<sub>S S</sub>に接続されたソースを有する。Nチャネルトランジスタ133はノード101に接続されたドレイン、デジタルカウント値ビットP D Q 4を受けるためのゲート、およびV<sub>S S</sub>に接続されたソースを有する。直列接続されたNチャネルトランジスタ134はノード101とV<sub>S S</sub>の間に接続されている。直列接続されたNチャネルトランジスタ134の各々のゲートはデジタルカウント値ビットP D Q 3を受けるためのものである。直列接続されたNチャネルトランジスタ135はノード101とV<sub>S S</sub>の間に接続されている。各々の直列接続されたNチャネルトランジスタ135のゲートはデジタルカウント値ビットP D Q 2を受けるためのものである。直列接続されたNチャネルトランジスタ136はノード101とV<sub>S S</sub>の間に接続されている。各々の直列接続されたNチャネルトランジスタ136のゲートはデジタルカウント値ビットP D Q 1を受けるためのものである。直列接続されたNチャネルトランジスタ137はノード101とV<sub>S S</sub>の間に接続されている。各々の直列接続されたNチャネルトランジスタ137のゲートはデジタルカウント値ビットP D Q 0を受けるためのものである。ノード101は前記デジタルカウント値P D Q (0:7)の関数としてプルダウンアレ 40

イ電圧 P D A R Y を提供する。

【 0 0 3 7 】

プルダウン 2 進重み付けトランジスタアレイ 4 5 の N チャネルトランジスタはデジタルカウント値 P D Q ( 0 : 7 ) の値に依存してノード 1 0 1 と V<sub>S S</sub> の間に調整可能なインピーダンスを提供するよう寸法が与えられている。ノード 1 0 1 と V<sub>S S</sub> の間のインピーダンスは増大するデジタルカウント値に対して低減され、かつデジタルカウント値の低減に対して増大される。

【 0 0 3 8 】

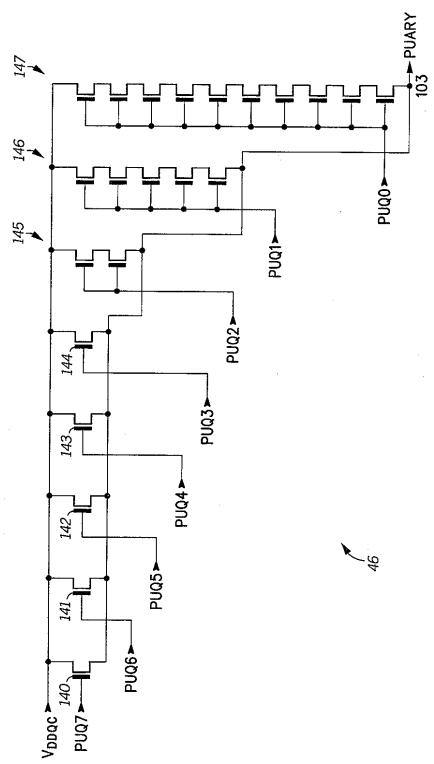

図 5 は、電気回路図形式で、図 1 のプルアップ 2 進重み付けトランジスタアレイ 4 6 を示す。プルアップ 2 進重み付けトランジスタアレイ 4 6 は N チャネルトランジスタ 1 4 0 , 1 4 1 , 1 4 2 , 1 4 3 および 1 4 4 、直列接続された N チャネルトランジスタ 1 4 5 、直列接続された N チャネルトランジスタ 1 4 6 、および直列接続された N チャネルトランジスタ 1 4 7 を含む。 N チャネルトランジスタ 1 4 0 は V<sub>D D Q C</sub> に接続されたドレイン、デジタルカウント値ビット P U Q 7 を受けるためのゲート、およびノード 1 0 3 に接続されたソースを有する。 N チャネルトランジスタ 1 4 1 は V<sub>D D Q C</sub> に接続されたドレイン、デジタルカウント値ビット P U Q 6 を受けるためのゲート、およびノード 1 0 3 に接続されたソースを有する。 N チャネルトランジスタ 1 4 2 は V<sub>D D Q C</sub> に接続されたドレイン、デジタルカウント値ビット P U Q 5 を受けるためのゲート、およびノード 1 0 3 に接続されたソースを有する。 N チャネルトランジスタ 1 4 3 は V<sub>D D Q C</sub> に接続されたドレイン、デジタルカウント値ビット P U Q 4 を受けるためのゲート、およびノード 1 0 3 に接続されたソースを有する。 N チャネルトランジスタ 1 4 4 は V<sub>D D Q C</sub> に接続されたドレイン、デジタルカウント値ビット P U Q 3 を受けるためのゲート、およびノード 1 0 3 に接続されたソースを有する。

【 0 0 3 9 】

直列接続された N チャネルトランジスタ 1 4 5 は V<sub>D D Q C</sub> とノード 1 0 3 の間に接続されている。各々の直列接続された N チャネルトランジスタ 1 4 5 のゲートはデジタルカウント値ビット P U Q 2 を受けるためのものである。直列接続された N チャネルトランジスタ 1 4 6 は V<sub>D D Q C</sub> とノード 1 0 3 の間に接続されている。各々の直列接続された N チャネルトランジスタ 1 4 6 のゲートはデジタルカウント値ビット P U Q 1 を受けるためのものである。直列接続された N チャネルトランジスタ 1 4 7 は V<sub>D D Q C</sub> とノード 1 0 3 の間に接続されている。各々の直列接続された N チャネルトランジスタ 1 4 7 のゲートはデジタルカウント値ビット P U Q 0 を受けるためのものである。ノード 1 0 3 は前記デジタルカウント値 P U Q ( 0 : 7 ) の関数としてプルアップアレイ電圧 P U A R Y を提供する。

【 0 0 4 0 】

プルアップ 2 進重み付けトランジスタアレイ 4 6 の N チャネルトランジスタは前記デジタルカウント値 P U Q ( 0 : 7 ) の値に依存して V<sub>D D Q C</sub> およびノード 1 0 1 の間で調整可能なインピーダンスを提供するような寸法とされる。プルダウン 2 進重み付けトランジスタアレイ 4 5 と同様に、 V<sub>D D Q C</sub> およびノード 1 0 1 の間のインピーダンスはデジタルカウント値の増大に対して低減され、かつデジタルカウント値の低減に対して増大される。

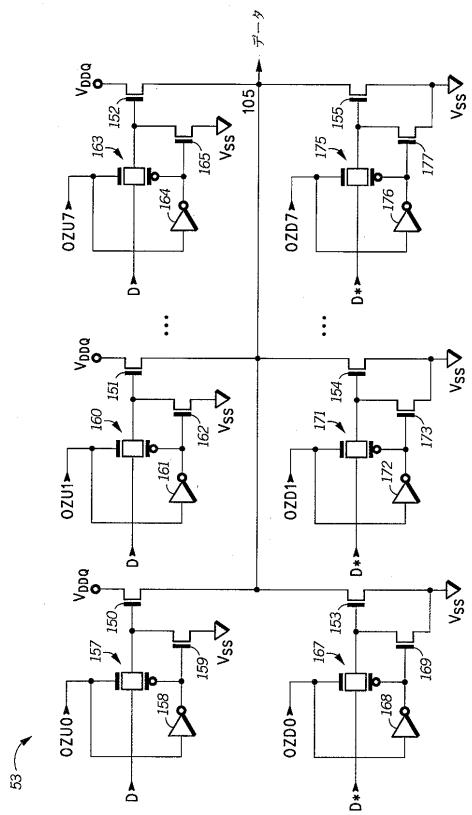

【 0 0 4 1 】

図 6 は、部分的電気回路図形式でかつ部分的論理図形式で、図 1 の出力ドライバ 5 3 を示す。出力ドライバ 5 3 は N チャネルトランジスタ 1 5 0 , 1 5 1 および 1 5 2 を含む複数の N チャネルプルアップトランジスタ、 N チャネルトランジスタ 1 5 3 , 1 5 4 および 1 5 5 を含む複数の N チャネルプルダウントランジスタ、伝送ゲート 1 5 7 , 1 6 0 , 1 6 3 , 1 6 7 , 1 7 1 および 1 7 5 、 N チャネルトランジスタ 1 5 9 , 1 6 2 , 1 6 5 , 1 6 9 , 1 7 3 および 1 7 7 、そしてインバータ 1 5 8 , 1 6 1 , 1 6 4 , 1 6 8 , 1 7 2 および 1 7 6 を含む。 N チャネルプルアップトランジスタ 1 5 0 , 1 5 1 および 1 5 2 は入力データ信号 D およびプルアップ制御信号 O Z U ( 0 : 7 ) の受信に応じて出力データ

10

20

30

40

50

信号 DATA をプルアップするための複数の 2 進重み付けプルアップトランジスタを例示的に表わすものである。プルアップ制御信号 OZU (0 : 7) は出力ドライバ 53 のプルアップトランジスタによりドライブされる負荷と共にインピーダンスを整合するために使用される。N チャネルプルダウントランジスタ 153, 154 および 155 は入力データ信号 D\* およびプルダウン制御信号 OZD (0 : 7) の受信に応じて出力信号 DATA をプルダウンするための複数の 2 進重み付けプルダウントランジスタを例示的に表わしている。プルダウン制御信号 OZD (0 : 7) は出力ドライバ 53 のプルダウントランジスタによってドライブされる負荷とのインピーダンスの整合のために使用される。

【0042】

N チャネルプルアップトランジスタ 150 は  $V_{DDQ}$  に接続されたドレイン、伝送ゲート 157 を介して入力データ信号 D を受けるためのゲート、および出力端子 105 に接続されたソースを有する。プルアップ制御信号 OZU0 は伝送ゲート 157 の伝導度を制御する。N チャネルトランジスタ 159 は N チャネルトランジスタ 150 のゲートに接続されたドレイン、インバータ 158 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

【0043】

N チャネルプルアップトランジスタ 151 は  $V_{DDQ}$  に接続されたドレイン、伝送ゲート 160 を介して入力データ信号 D を受けるためのゲート、および出力端子 105 に接続されたソースを有する。プルアップ制御信号 OZU1 は伝送ゲート 160 の伝導度 (conductivity) を制御する。N チャネルトランジスタ 162 は N チャネルトランジスタ 151 のゲートに接続されたドレイン、インバータ 161 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

【0044】

N チャネルプルアップトランジスタ 152 は  $V_{DDQ}$  に接続されたドレイン、伝送ゲート 163 を介して入力データ信号 D を受けるためのゲート、および出力端子 105 に接続されたソースを有する。プルアップ制御信号 OZU7 は伝送ゲート 163 の伝導度を制御する。N チャネルトランジスタ 165 は N チャネルトランジスタ 152 のゲートに接続されたドレイン、インバータ 164 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

【0045】

N チャネルプルダウントランジスタ 153 は出力端子 105 に接続されたドレイン、入力データ信号 D\* を伝送ゲート 167 を介して受けるためのゲート、および  $V_{SS}$  に接続されたソースを有する。プルダウン制御信号 OZD0 は伝送ゲート 167 の伝導度を制御する。N チャネルトランジスタ 169 は N チャネルトランジスタ 153 のゲートに接続されたドレイン、インバータ 168 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

【0046】

N チャネルプルダウントランジスタ 154 は出力端子 105 に接続されたドレイン、入力データ信号 D\* を伝送ゲート 171 を介して受けるためのゲート、および  $V_{SS}$  に接続されたソースを有する。プルダウン制御信号 OZD1 は伝送ゲート 171 の伝導度を制御する。N チャネルトランジスタ 173 は N チャネルトランジスタ 154 のゲートに接続されたドレイン、インバータ 172 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

【0047】

N チャネルプルダウントランジスタ 155 は出力端子 105 に接続されたドレイン、入力データ信号 D\* を伝送ゲート 175 を介して受けるためのゲート、および  $V_{SS}$  に接続されたソースを有する。プルダウン制御信号 OZD7 は伝送ゲート 175 の伝導度を制御する。N チャネルトランジスタ 177 は N チャネルトランジスタ 155 のゲートに接続されたドレイン、インバータ 176 の出力端子に接続されたゲート、および  $V_{SS}$  に接続されたソースを有する。

10

20

20

30

40

50

## 【0048】

出力ドライバ53の伝送ゲートは結合素子として機能しかつプルアップデジタルカウント値OZU(0:7)およびプルダウンデジタルカウント値OZD(0:7)によってゲーティングされてノード105における出力インピーダンスをノード105に接続された負荷のインピーダンスに調整する。インバータ158, 161, 164, 168, 172および176はそれらの対応するデジタルカウント値を受けかつ前記伝送ゲートのPチャネルトランジスタを対応するデジタルカウント値が論理ハイの電圧になったことに応じて導通させる。

## 【0049】

## 【発明の効果】

出力ドライバ53のノード105のインピーダンスを伝送ラインのインピーダンスに整合させることにより反射信号が吸収でき、したがってリギングを防止する。これはより静かな波形、より良好なノイズ耐性、および改善された信号タイミングマージンを生じる結果となる。また、ノード105のインピーダンスは抵抗32(図1)の抵抗値を変えることにより容易に調整可能であり、出力バッファ20を導入した集積回路メモリのような、集積回路が種々の負荷インピーダンスをドライブできるようにする。

## 【0050】

本発明が好ましい実施形態に関して説明されたが、当業者には本発明は種々の方法で変更できかつ上に特に示しかつ説明したもの以外の数多くの実施形態を取り得ることは明らかであろう。例えば、ソースフォロワNチャネルトランジスタ33, 34, 35, 37および38は同様にノイズに対して敏感でない実施形態においてPチャネルトランジスタと置き換えることができる。また、プルアップレジスタ49およびプルダウンレジスタ52は1つの多ビットレジスタの部分とすることができます。さらに、前記デジタルカウント値は集積回路上の数多くの出力ドライバ回路のインピーダンスを制御するために使用できる。したがって、添付の特許請求の範囲により本発明の真の精神および範囲内に入る発明の全ての変更をカバーすることを意図している。

## 【図面の簡単な説明】

【図1】図1は、本発明の1つの実施形態に係わる可変出力インピーダンスを有する出力バッファ回路を部分的にブロック図形式で、部分的に電気回路図形式で、かつ部分的に論理図形式で示す構成説明図である。

【図2】図1のプルダウンA/D変換器のフィードバック増幅器を示す電気回路図である。

【図3】図1のプルダウンA/D変換器の比較器を示す部分的電気回路図である。

【図4】図1のプルダウン2進重み付けトランジスタアレイを示す電気回路図である。

【図5】図1のプルダウン2進重み付けトランジスタアレイを示す電気回路図である。

【図6】図1の出力ドライバを、部分的に電気回路図形式でかつ部分的に論理図形式で示すブロック回路図である。

## 【符号の説明】

20 出力バッファ回路

22 プルアップA/D変換器

24 プルダウンA/D変換器

30 パッド

32 抵抗

33, 34 Nチャネルソースフォロワトランジスタ

35, 37, 38 Nチャネルソースフォロワトランジスタ

36, 39 抵抗

40 フィードバック増幅器

41 ローパスフィルタ

42 比較器

43 フィードバック増幅器

10

20

30

40

50

## 4.4 比較器

## 4.5 2進重み付けプルダウントランジスタアレイ

## 4.6 2進重み付けプルアップトランジスタアレイ

## 4.7 プルアップアービタ

## 4 8 8 ビット 2 進カウンタ

## 4.9 プルアップレジスタ

## 5.0 プルダウンアービタ

## 5 1 8 ビット 2 進カウンタ

## 5.2 プルダウンレジスタ

### 5.3 出力ドライバ

【 四 1 】

【 义 2 】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 スコット・ジョージ・ノグル

アメリカ合衆国テキサス州78727、オースティン、ミーハン・ドライブ 12811

審査官 宮島 郁美

(56)参考文献 特開平06-260922(JP, A)

特開昭62-038616(JP, A)

特開平07-142985(JP, A)

特開平07-046439(JP, A)

特開平08-321769(JP, A)

特開平08-065123(JP, A)

特開平08-032435(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096

H03H11/00-11/54